# 3.3V ECL/PECL/HSTL/LVDS ÷2/4, ÷4/5/6 Clock Generation Chip

The MC100ES6139 is a low skew  $\pm 2/4$ ,  $\pm 4/5/6$  clock generation chip designed explicitly for low skew clock generation applications. The internal dividers are synchronous to each other, therefore, the common output edges are all precisely aligned. The device can be driven by either a differential or single-ended ECL or, if positive power supplies are used, LVPECL input signals. In addition, by using the V<sub>BB</sub> output, a sinusoidal source can be AC coupled into the device. If a single-ended input is to be used, the V<sub>BB</sub> output should be connected to the CLK input and bypassed to ground via a 0.01  $\mu$ F capacitor.

The common enable  $(\overline{EN})$  is synchronous so that the internal dividers will only be enabled/disabled when the internal clock is already in the LOW state. This avoids any chance of generating a runt clock pulse on the internal clock when the device is enabled/disabled as can happen with an asynchronous control. The internal enable flip-flop is clocked on the falling edge of the input clock, therefore, all associated specification limits are referenced to the negative edge of the clock input.

Upon startup, the internal flip-flops will attain a random state; therefore, for systems which utilize multiple ES6139s, the master reset (MR) input must be asserted to ensure synchronization. For systems which only use one ES6139, the MR pin need not be exercised as the internal divider design ensures synchronization between the  $\pm 2/4$  and the  $\pm 4/5/6$  outputs of a single device. All V<sub>CC</sub> and V<sub>EE</sub> pins must be externally connected to power supply to guarantee proper operation.

The 100ES Series contains temperature compensation.

### Features

Semiconductor, In

**BOSCA**

- Maximum Frequency >1.0 GHz Typical

- 50 ps Output-to-Output Skew

- PECL Mode Operating Range:  $V_{CC} = 3.135$  V to 3.8 V with  $V_{EE} = 0$  V

- ECL Mode Operating Range:  $V_{CC} = 0$  V with  $V_{EE} = -3.135$  V to -3.8 V

- Open Input Default State

- Synchronous Enable/Disable

- Master Reset for Synchronization of Multiple Chips

- V<sub>BB</sub> Output

- LVDS and HSTL Input Compatible

### ORDERING INFORMATION

| Device          | Package  |

|-----------------|----------|

| MC100ES6139DT   | TSSOP-20 |

| MC100ES6139DTR2 | TSSOP-20 |

| MC100ES6139DW   | SO-20    |

| MC100ES6139DWR2 | SO-20    |

### MC100ES6139

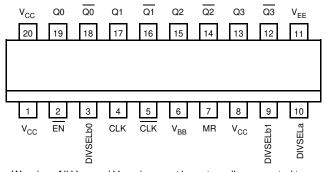

Warning: All V<sub>CC</sub> and V<sub>EE</sub> pins must be externally connected to Power Supply to guarantee proper operation.

### Figure 1. 20-Lead Pinout (Top View)

### Table 1. Pin Description

| Pin                                 | Function                      |

|-------------------------------------|-------------------------------|

| CLK <sup>1</sup> , CLK <sup>1</sup> | ECL Diff Clock Inputs         |

| EN <sup>1</sup>                     | ECL Sync Enable               |

| MR <sup>1</sup>                     | ECL Master Reset              |

| V <sub>BB</sub>                     | ECL Reference Output          |

| Q0, Q1, <u>Q0</u> , <u>Q1</u>       | ECL Diff ÷2/4 Outputs         |

| Q2, Q3, <u>Q2</u> , <u>Q3</u>       | ECL Diff ÷4/5/6 Outputs       |

| DIVSELa <sup>1</sup>                | ECL Freq. Select Input ÷2/4   |

| DIVSELb0 <sup>1</sup>               | ECL Freq. Select Input ÷4/5/6 |

| DIVSELb1 <sup>1</sup>               | ECL Freq. Select Input ÷4/5/6 |

| V <sub>CC</sub>                     | ECL Positive Supply           |

| V <sub>EE</sub>                     | ECL Negative Supply           |

1. Pins will default low when left open.

#### Table 2. Function Tables

| CLK | EN | MR | Function   |

|-----|----|----|------------|

| Z   | L  | L  | Divide     |

| ZZ  | Н  | L  | Hold Q0:3  |

| Х   | Х  | Н  | Reset Q0:3 |

X = Don't Care

Z = Low-to-High Transition

ZZ = High-to-Low Transition

| DIVS             | SELa             | Q0:1 Outputs                                             |

|------------------|------------------|----------------------------------------------------------|

| l                | -<br>1           | Divide by 2<br>Divide by 4                               |

| DIVSELb0         | DIVSELb1         | Q2:3 Outputs                                             |

| L<br>H<br>L<br>H | L<br>L<br>H<br>H | Divide by 4<br>Divide by 6<br>Divide by 5<br>Divide by 5 |

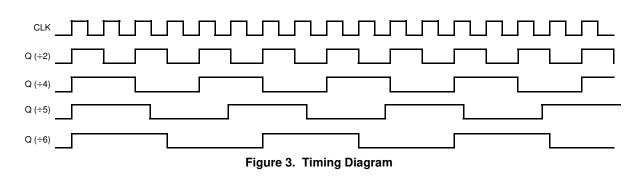

TIMING SOLUTIONS

Figure 4. Timing Diagram

### Table 3. Attributes

| Characteristics                                        | Value         |

|--------------------------------------------------------|---------------|

| Internal Input Pulldown Resistor                       | 75 kΩ         |

| Internal Input Pullup Resistor                         | 75 kΩ         |

| ESD Protection Human Body<br>Machine<br>Charged Device | Model > 200 V |

Meets or exceeds JEDEC Spec EIA/JESD78 IC Latchup Test

### MC100ES6139

## Freescale Semiconductor, Inc.

### Table 4. Maximum Ratings<sup>1</sup>

| Symbol           | Parameter                                         | Condition 1                      | Condition 2                                                           | Rating      | Units        |

|------------------|---------------------------------------------------|----------------------------------|-----------------------------------------------------------------------|-------------|--------------|

| V <sub>CC</sub>  | PECL Mode Power Supply                            | $V_{EE} = 0 V$                   |                                                                       | 3.9         | V            |

| $V_{EE}$         | ECL Mode Power Supply                             | $V_{CC} = 0 V$                   |                                                                       | -3.9        | V            |

| VI               | PECL Mode Input Voltage<br>ECL Mode Input Voltage | $V_{EE} = 0 V$<br>$V_{CC} = 0 V$ | $\begin{array}{l} V_{I} \leq V_{CC} \\ V_{I} \geq V_{EE} \end{array}$ | 3.9<br>_3.9 | V<br>V       |

| I <sub>out</sub> | Output Current                                    | Continuous<br>Surge              |                                                                       | 50<br>100   | mA<br>mA     |

| I <sub>BB</sub>  | V <sub>BB</sub> Sink/Source                       |                                  |                                                                       | ± 0.5       | mA           |

| ТА               | Operating Temperature Range                       |                                  |                                                                       | -40 to +85  | °C           |

| T <sub>stg</sub> | Storage Temperature Range                         |                                  |                                                                       | -65 to +150 | °C           |

| $\theta_{JA}$    | Thermal Resistance (Junction-to-Ambient)          | 0 LFPM<br>500 LFPM               | 20 TSSOP<br>20 TSSOP                                                  | 74<br>64    | °C/W<br>°C/W |

|                  |                                                   | 0 LFPM<br>500 LFPM               | 20 SOIC<br>20 SOIC                                                    | TBD<br>TBD  | °C/W<br>°C/W |

1. Maximum Ratings are those values beyond which device damage may occur.

### Table 5. DC Characteristics (V<sub>CC</sub> = 0 V, V<sub>EE</sub> = -3.8 V to -3.135 V or V<sub>CC</sub> = 3.135 V to 3.8 V, V<sub>EE</sub> = 0 V)<sup>1</sup>

| Symbol           | Characteristic                                |                       | <b>−40°C</b>          |                       |                       | Unit                  |                       |      |

|------------------|-----------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|------|

| Symbol           | Characteristic                                | Min                   | Тур                   | Max                   | Min                   | Тур                   | Max                   | Unit |

| I <sub>EE</sub>  | Power Supply Current                          |                       | 35                    | 60                    |                       | 35                    | 60                    | mA   |

| V <sub>OH</sub>  | Output HIGH Voltage <sup>2</sup>              | V <sub>CC</sub> –1150 | V <sub>CC</sub> -1020 | V <sub>CC</sub> -800  | V <sub>CC</sub> -1200 | V <sub>CC</sub> –970  | V <sub>CC</sub> –750  | mV   |

| V <sub>OL</sub>  | Output LOW Voltage <sup>2</sup>               | V <sub>CC</sub> –1950 | V <sub>CC</sub> -1620 | V <sub>CC</sub> -1250 | V <sub>CC</sub> –2000 | V <sub>CC</sub> -1680 | V <sub>CC</sub> -1300 | mV   |

| V <sub>IH</sub>  | Input HIGH Voltage (Single-Ended)             | V <sub>CC</sub> -1165 |                       | V <sub>CC</sub> -880  | V <sub>CC</sub> -1165 |                       | V <sub>CC</sub> -880  | mV   |

| V <sub>IL</sub>  | Input LOW Voltage (Single-Ended)              | V <sub>CC</sub> –1810 |                       | V <sub>CC</sub> -1475 | V <sub>CC</sub> -1810 |                       | V <sub>CC</sub> -1475 | mV   |

| V <sub>BB</sub>  | Output Reference Voltage                      | V <sub>CC</sub> -1400 |                       | V <sub>CC</sub> -1200 | V <sub>CC</sub> -1400 |                       | V <sub>CC</sub> -1200 | mV   |

| V <sub>PP</sub>  | Differential Input Voltage <sup>3</sup>       | 0.12                  |                       | 1.3                   | 0.12                  |                       | 1.3                   | V    |

| V <sub>CMR</sub> | Differential Cross Point Voltage <sup>4</sup> | V <sub>EE</sub> +0.2  |                       | V <sub>CC</sub> –1.1  | V <sub>EE</sub> +0.2  |                       | V <sub>CC</sub> –1.1  | V    |

| I <sub>IH</sub>  | Input HIGH Current                            |                       |                       | 150                   |                       |                       | 150                   | μA   |

| IIL              | Input LOW Current                             | 0.5                   |                       |                       | 0.5                   |                       |                       | μA   |

1. MC100ES6139 circuits are designed to meet the DC specifications shown in the above table after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse airflow greater than 500 lfpm is maintained.

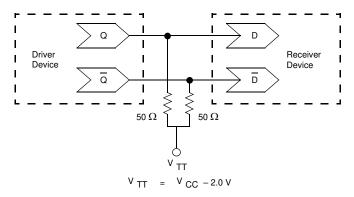

2. All loading with 50  $\Omega$  to V\_CC–2.0 volts.

3.  $V_{PP}$  (DC) is the minimum differential input voltage swing required to maintain device functionality.

4. V<sub>CMR</sub> (DC) is the crosspoint of the differential input signal. Functional operation is obtained when the crosspoint is within the V<sub>CMR</sub> (DC) range and the input swing lies within the V<sub>PP</sub> (DC) specification.

4

| 0                                      | Oh ann a taoi                                           | Characteristic                         |               | –40°C      |                      | 25°C          |            |                      |               | 85°C       |                      |      |

|----------------------------------------|---------------------------------------------------------|----------------------------------------|---------------|------------|----------------------|---------------|------------|----------------------|---------------|------------|----------------------|------|

| Symbol                                 | Character                                               | Stic                                   | Min           | Тур        | Мах                  | Min           | Тур        | Max                  | Min           | Тур        | Max                  | Unit |

| f <sub>max</sub>                       | Maximum Frequency                                       |                                        |               | > 1        |                      |               | > 1        |                      |               | > 1        |                      | GHz  |

| t <sub>PLH</sub> ,<br>t <sub>PHL</sub> | Propagation Delay                                       | CLK, Q (Diff)<br>MR, Q                 | 550<br>400    |            | 850<br>850           | 550<br>400    |            | 850<br>850           | 550<br>400    |            | 850<br>850           | ps   |

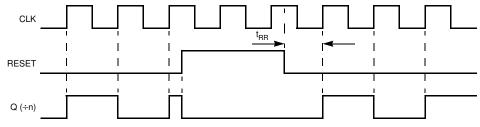

| t <sub>RR</sub>                        | Reset Recovery                                          |                                        | 200           | 100        |                      | 200           | 100        |                      | 200           | 100        |                      | ps   |

| t <sub>s</sub>                         | Setup Time                                              | EN, CLK<br>DIVSEL, CLK                 |               | 120<br>180 |                      | 200<br>400    | 120<br>180 |                      | 200<br>400    | 120<br>180 |                      | ps   |

| t <sub>h</sub>                         | Hold Time                                               | CLK, EN<br>CLK, DIVSEL                 | 100<br>200    | 50<br>140  |                      | 100<br>200    | 50<br>140  |                      | 100<br>200    | 50<br>140  |                      | ps   |

| t <sub>PW</sub>                        | Minimum Pulse Width                                     | n MR                                   | 550           | 450        |                      | 550           | 450        |                      | 550           | 450        |                      | ps   |

| t <sub>SKEW</sub>                      | Within Device Skew<br>Q, Q @ Sa<br>Device-to-Device Ske | Q, Q<br>me Frequency<br>w <sup>2</sup> |               |            | 100<br>50<br>300     |               |            | 100<br>50<br>300     |               |            | 100<br>50<br>300     | ps   |

| t <sub>JITTER</sub>                    | Cycle-to-Cycle Jitter                                   | (RSM 1σ)                               |               |            | 1                    |               |            | 1                    |               |            | 1                    | ps   |

| V <sub>PP</sub>                        | Input Voltage Swing (                                   | Differential)                          | 200           |            | 1200                 | 200           |            | 1200                 | 200           |            | 1200                 | mV   |

| V <sub>CMR</sub>                       | Differential Cross Poi                                  | nt Voltage                             | $V_{EE}$ +0.2 |            | V <sub>CC</sub> -1.2 | $V_{EE}$ +0.2 |            | V <sub>CC</sub> -1.2 | $V_{EE}$ +0.2 |            | V <sub>CC</sub> -1.2 | V    |

| t <sub>r</sub><br>t <sub>f</sub>       | Output Rise/Fall Time<br>(20% – 80%)                    | es Q, Q                                | 50            |            | 300                  | 50            |            | 300                  | 50            |            | 300                  | ps   |

| Table 6. | AC Characteristics (                    | $V_{CC} = 0 V. V_{EE} =$ | 3.8 V to - 3.135 V | or $V_{CC} = 3.135$ V to | $3.8 \text{ V}. \text{ V}_{\text{EE}} = 0 \text{ V})^{1}$ |

|----------|-----------------------------------------|--------------------------|--------------------|--------------------------|-----------------------------------------------------------|

| 14010 01 | / • • • • • • • • • • • • • • • • • • • | •(,(, = • •, • + + + -   |                    | (,,) = 0.100 + 10        | $0.0.1, 1_{\rm FF} = 0.1$                                 |

1. Measured using a 750 mV source, 50% duty cycle clock source. All loading with 50  $\Omega$  to V<sub>CC</sub> –2.0 V.

2. Skew is measured between outputs under identical transitions. Duty cycle skew is defined only for differential operation when the delays are measured from the cross point of the inputs to the cross point of the outputs.

Figure 5. Typical Termination for Output Driver and Device Evaluation

TIMING SOLUTIONS

### MC100ES6139

#### Marking Notes:

| Device Nomenclature | 20-Lead TSSOP Marking | 20-Lead SOIC W/B Marking |

|---------------------|-----------------------|--------------------------|

| MC100ES6139DT       | 6139                  |                          |

| MC100ES6139DW       |                       | MC100ES6139              |

### Trace Code Identification for 20 SOIC: AWLYYWW

"A" - The First character indicates the Assembly location.

"WL" - The Second & Third characters indicate the Source Wafer Lot Tracking Code.

"YY" - The Fourth & Fifth characters indicate the Year device was assembled.

"WW" - The Sixth & Seventh characters indicate the Work Week device was assembled.

#### Trace Code Identification for 20 TSSOP: ALYW

"A" - The First character indicates the Assembly location.

"L" - The Second character indicates the Source Wafer Lot Tracking Code.

"Y" - The Third character indicates the "ALPHA CODE" of the year device was assembled.

"W" - The Fourth character indicates the "ALPHA CODE" of the Work Week device was assembled.

|          | The "Y" Year ALPHA CODES |                | The "W" Work Week ALPHA CODES |                            |  |  |

|----------|--------------------------|----------------|-------------------------------|----------------------------|--|--|

| Year     | Month                    | Work Week Code | 1st 6 Months (WW01 – WW26)    | 2nd 6 Months (WW27 – WW52) |  |  |

| A = 2003 | FIRST 6 MONTHS           | WW01 – WW26    | A = WW01                      | A = WW27                   |  |  |

| B = 2003 | SECOND 6 MONTHS          | WW27 – WW52    | B = WW02                      | B = WW28                   |  |  |

| C = 2004 | FIRST 6 MONTHS           | WW01 – WW26    | C = WW03                      | C = WW29                   |  |  |

| D = 2004 | SECOND 6 MONTHS          | WW27 – WW52    | D = WW04                      | D = WW30                   |  |  |

| E = 2005 | FIRST 6 MONTHS           | WW01 – WW26    | E = WW05                      | E = WW31                   |  |  |

| F = 2005 | SECOND 6 MONTHS          | WW27 – WW52    | F = WW06                      | F = WW32                   |  |  |

| G = 2006 | FIRST 6 MONTHS           | WW01 – WW26    | G = WW07                      | G = WW33                   |  |  |

| H = 2006 | SECOND 6 MONTHS          | WW27 – WW52    | H = WW08                      | H = WW34                   |  |  |

| I = 2007 | FIRST 6 MONTHS           | WW01 – WW26    | I = WW09                      | I = WW35                   |  |  |

| J = 2007 | SECOND 6 MONTHS          | WW27 – WW52    | J = WW10                      | J = WW36                   |  |  |

| K = 2008 | FIRST 6 MONTHS           | WW01 – WW26    | K = WW11                      | K = WW37                   |  |  |

| L = 2008 | SECOND 6 MONTHS          | WW27 – WW52    | L = WW12                      | L = WW38                   |  |  |

| M = 2009 | FIRST 6 MONTHS           | WW01 – WW26    | M = WW13                      | M = WW39                   |  |  |

| N = 2009 | SECOND 6 MONTHS          | WW27 – WW52    | N = WW14                      | N = WW40                   |  |  |

| O = 2010 | FIRST 6 MONTHS           | WW01 – WW26    | O = WW15                      | O = WW41                   |  |  |

| P = 2010 | SECOND 6 MONTHS          | WW27 – WW52    | P = WW16                      | P = WW42                   |  |  |

| Q = 2011 | FIRST 6 MONTHS           | WW01 – WW26    | Q = WW17                      | Q = WW43                   |  |  |

| R = 2011 | SECOND 6 MONTHS          | WW27 – WW52    | R = WW18                      | R = WW44                   |  |  |

| S = 2012 | FIRST 6 MONTHS           | WW01 – WW26    | S = WW19                      | S = WW45                   |  |  |

| T = 2012 | SECOND 6 MONTHS          | WW27 – WW52    | T = WW20                      | T = WW46                   |  |  |

| U = 2013 | FIRST 6 MONTHS           | WW01 – WW26    | U = WW21                      | U = WW47                   |  |  |

| V = 2013 | SECOND 6 MONTHS          | WW27 – WW52    | V = WW22                      | V = WW48                   |  |  |

| W = 2014 | FIRST 6 MONTHS           | WW01 – WW26    | W = WW23                      | W = WW49                   |  |  |

| X = 2014 | SECOND 6 MONTHS          | WW27 – WW52    | X = WW24                      | X = WW50                   |  |  |

| Y = 2015 | FIRST 6 MONTHS           | WW01 – WW26    | Y = WW25                      | Y = WW51                   |  |  |

| Z = 2015 | SECOND 6 MONTHS          | WW27 – WW52    | Z = WW26                      | Z = WW52                   |  |  |

#### 20 TSSOP Tracecode Marking Example:

5ABR

5 | - Assembly Locat

5 | | = Assembly Location

A = First Lot Assembled of this device in the designated

Work Week

- B = 2003 Second 6 Months, WW27 WW52

- R= WW44 of 2003

TIMING SOLUTIONS

MC100ES6139

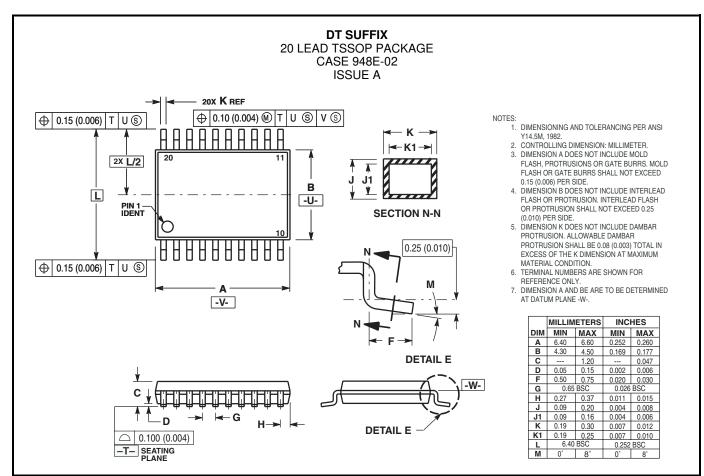

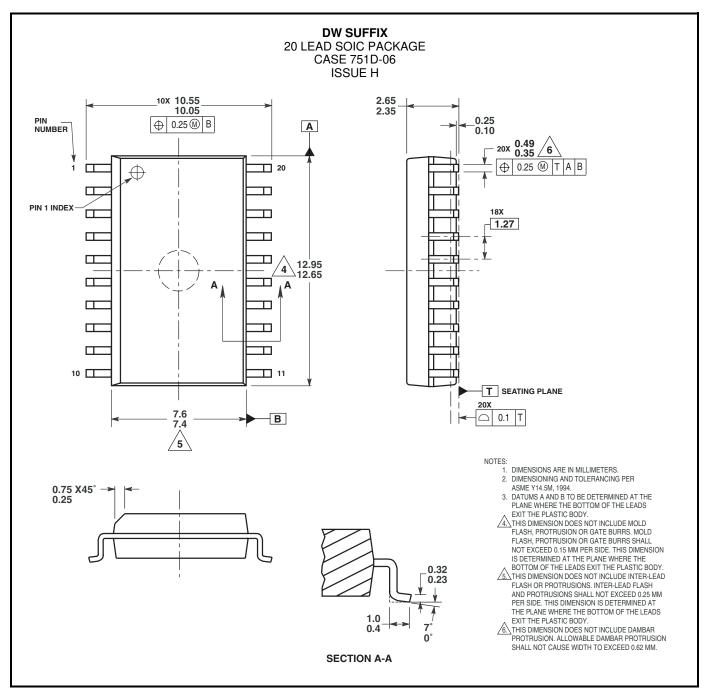

### **OUTLINE DIMENSIONS**

**OUTLINE DIMENSIONS**

L.

MC100ES6139

NOTES

NOTES

MC100ES6139

NOTES

Information in this document is provided solely to enable system and software implementers to use Motorola products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

MOTOROLA and the Stylized M Logo are registered in the US Patent and Trademark Office. All other product or service names are the property of their respective owners.

© Motorola, Inc. 2004

#### HOW TO REACH US:

USA/EUROPE/LOCATIONS NOT LISTED: Motorola Literature Distribution P.O. Box 5405, Denver, Colorado 80217 1-800-521-6274 or 480-768-2130

JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center 3-20-1 Minami-Azabu. Minato-ku, Tokyo 106-8573, Japan 81-3-3440-3569

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong 852-26668334

HOME PAGE: http://motorola.com/semiconductors

MC100ES6139

For More Information On This Product, Go to: www.freescale.com