## DESCRIPTION

The MP20045 is a low-dropout linear regulator supplies up to 1A current with 140mV dropout voltage. The output voltage is set externally which ranges from 1.5V to 5V by operating from +2.5V to +5.5V input or can be preset internally from 1.5V to 5V.

An internal PMOS pass element is used to allow a low 110µA ground current, making the MP20045 suitable for battery-power devices. Other features include low-power shutdown, short-circuit and thermal protection. The MP20045 is available in 8-pin QFN (3mm x 3mm) and SOIC8E packages.

## **FEATURES**

- Up to 1A Output Current

- Low 140mV Dropout at 1A

- Low 110µA Ground Current

- Fixed Output Versions Ranging from 1.5V to 5V and Adjustable Versions

- Open Drain Power-Good Status Output

- 13µV<sub>RMS</sub> Low Noise Output

- 56dB PSRR at 1kHz

- Current Limiting and Thermal Protection

- 3mm×3mm QFN8 and SOIC8E Packages

### **APPLICATIONS**

- Notebook Computers

- Cordless Telephones

- Cellular Phones

- Modems

- Hand-Held Instruments

- PDA and Palmtop Computers

All MPS parts are lead-free, halogen free, and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

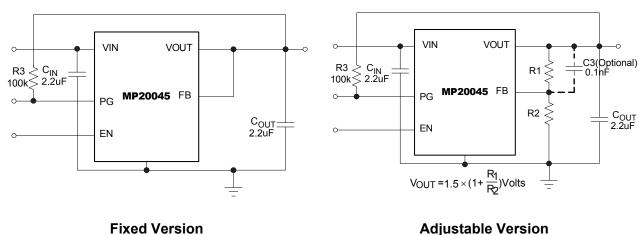

# TYPICAL APPLICATION

| Part Number*   | Output Voltage | Package          | Top Marking | Free Air Temperature (T <sub>A</sub> ) |

|----------------|----------------|------------------|-------------|----------------------------------------|

| MP20045DQ**    | Adjustable     | QFN8 (3mm x 3mm) | 8K          |                                        |

| MP20045DQ-18** | 1.8V           | QFN8 (3mm x 3mm) | 3V          |                                        |

| MP20045DQ-25** | 2.5V           | QFN8 (3mm x 3mm) | 9Z          | -40°C to +85°C                         |

| MP20045DN**    | Adjustable     | SOIC8E           | M20045DN    |                                        |

| MP20045DN-18** | 1.8V           | SOIC8E           | 20045-18    |                                        |

### **ORDERING INFORMATION**

\* For fixed output voltage versions between 1.5V and 5V. Contact factory for availability.

\*\* For Tape & Reel, add suffix –Z (e.g. MP20045DQ–Z, MP20045DN–Z); For RoHS compliant packaging, add suffix –LF (e.g. MP20045DQ–LF–Z, MP20045DN–LF–Z).

## ABSOLUTE MAXIMUM RATINGS (1)

| VIN, EN, PG, FB to GND                 | 0.3V to +6V                            |

|----------------------------------------|----------------------------------------|

| OUT to GND0                            | .5V to V <sub>IN</sub> + 0.5V          |

| Continuous Power Dissipation           | (T <sub>A</sub> =+25°C) <sup>(2)</sup> |

| QFN8 (3x3)                             | 2.0W                                   |

| SOIC8E                                 | 2.0W                                   |

| Free Air Temperature (T <sub>A</sub> ) | 40°C to 85°C                           |

| Storage Temperature Range              | 65°C to 150°C                          |

| Lead Temperature (Soldering, 10        | sec)260°C                              |

### ESD Susceptibility

| HBM (Human Body Mode) | 2kV  |

|-----------------------|------|

| MM (Machine Mode)     | 200V |

### Recommended Operating Conditions <sup>(3)</sup>

| Supply Input Voltage                    | 2.5V to 5.5V   |

|-----------------------------------------|----------------|

| Enable Input Voltage                    | 0V to 5.5V     |

| Operating Junct. Temp (T <sub>J</sub> ) | 40°C to +125°C |

#### **Thermal Resistance** <sup>(4)</sup> $\theta_{JA}$ $\theta_{JC}$ OEN8 (3x3) 50 12 °C/M

| QFN8 (3X3) | 50 | 12 | °C/W |

|------------|----|----|------|

| SOIC8E     | 50 | 10 | °C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub>(MAX), the junction-to-ambient thermal resistance θ<sub>JA</sub>, and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub>(MAX)=(T<sub>J</sub>(MAX)-T<sub>A</sub>)/ θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7 4-layer board.

MP20045 Rev. 1.11 1/19/2020

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2020 MPS. All Rights Reserved.

## **ELECTRICAL CHARACTERISTICS**

V<sub>IN</sub>=V<sub>OUT</sub>+0.5V or V<sub>IN</sub>=2.5V, EN=V<sub>IN</sub>, Typical values are at T<sub>A</sub>=+25°C, unless otherwise specified

| Parameter                      |                    | Condition                                                                                                                           |                                        | Min   | Тур  | Max  | Units             |  |

|--------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------|------|------|-------------------|--|

| Input Voltage                  |                    |                                                                                                                                     |                                        | 2.5   |      | 5.5  | V                 |  |

| Input Under voltage Lockout    |                    | V <sub>IN</sub> rising                                                                                                              |                                        | 2.0   |      | 2.3  | V                 |  |

| Hysteresis of UVL              | Hysteresis of UVLO |                                                                                                                                     | <u> </u>                               |       | 160  |      | mV                |  |

| FB Accuracy                    |                    |                                                                                                                                     |                                        | -2.5  |      | 2.5  |                   |  |

| Output Voltage                 | 1.5V               | I <sub>OUT</sub> =1mA, 2.5V <v<sub>IN</v<sub>                                                                                       | ₄<5.5V                                 | -2.5  |      | 2.5  | %                 |  |

| Accuracy                       | 1.8V               | Iout=1mA, 2.5V <vi< td=""><td>₁&lt;5.5V</td><td>-2.5</td><td></td><td>2.5</td></vi<>                                                | ₁<5.5V                                 | -2.5  |      | 2.5  |                   |  |

| , local doy                    | 2.5V               | IOUT=1mA, 3V <vin<< td=""><td>5.5V</td><td>-2.5</td><td></td><td>2.5</td><td></td></vin<<>                                          | 5.5V                                   | -2.5  |      | 2.5  |                   |  |

| Maximum Output                 | Current            | Continuous, V <sub>IN</sub> >=3V                                                                                                    |                                        | 1     |      |      | A                 |  |

| Short-Circuit Curre            |                    | $V_{OUT}=0, V_{IN}>=3V$                                                                                                             |                                        |       | 1.6  |      | A                 |  |

| In-Regulation Cur              | rent Limit         | V <sub>OUT</sub> within 4% of normal output voltage V <sub>IN</sub> =5.5V                                                           |                                        | 1.4   | 2.2  | 3.0  | А                 |  |

| Ground Current                 |                    | Ιουτ=100μΑ                                                                                                                          |                                        |       | 110  |      | μA                |  |

| Dropout Voltage <sup>(5)</sup> |                    | Iout=1A                                                                                                                             |                                        |       | 140  | 280  | mV                |  |

| Line Regulation <sup>(6)</sup> |                    | $V_{IN}$ from $V_{OUT}$ +0.5V to 5.5V, $I_{OUT}$ =5mA                                                                               |                                        | -0.15 |      | 0.15 | %/V               |  |

| Load Regulation <sup>(7)</sup> |                    | IOUT from 1mA to 1A                                                                                                                 |                                        |       | -0.3 |      | %                 |  |

| Output Voltage Noise           |                    | V <sub>IN</sub> =3.3V, V <sub>OUT</sub> =2.8V, C <sub>OUT</sub> =2.2µF,<br>I <sub>OUT</sub> =100mA, f ranges from 10Hz to<br>100kHz |                                        |       | 13   |      | μV <sub>RMS</sub> |  |

| PSRR                           |                    | At 1kHz, Iout=250mA                                                                                                                 |                                        |       | 56   |      | dB                |  |

| Shutdown Supply Current        |                    | V <sub>IN</sub> =+5.5V                                                                                                              |                                        |       | 5    | 16   | μA                |  |

|                                |                    | EN Logic High                                                                                                                       |                                        | 1.5   |      |      |                   |  |

| EN PIN Threshold               |                    | EN Logic Low                                                                                                                        |                                        |       |      | 0.4  | V                 |  |

| EN pin PULL-UP r               | esistor            |                                                                                                                                     |                                        | 550k  | 1.1M |      | Ω                 |  |

| Thermal Shutdown Temperature   |                    | Typical thermal hysteresis =20°C                                                                                                    |                                        |       | 150  |      | °C                |  |

| Minimum in                     | put voltage        | IOUT(PG)=300µA                                                                                                                      |                                        |       | 1.1  | 1.3  | V                 |  |

| Trip thresho                   |                    |                                                                                                                                     | MP20045                                |       |      |      |                   |  |

| PG                             |                    | Vout decreasing                                                                                                                     | MP20045-15<br>MP20045-18<br>MP20045-25 | 80    |      | 86   | %Vout             |  |

| Hysteresis voltage             |                    | Measured at VOUT                                                                                                                    |                                        |       | 6    |      | %Vout             |  |

| Output low voltage             |                    | I <sub>OUT(PG)</sub> =1mA                                                                                                           |                                        |       | 0.15 | 0.4  | V                 |  |

| Leakage current                |                    | V <sub>(PG)</sub> =5.5V                                                                                                             |                                        |       |      | 1    | μA                |  |

Notes:

5) Dropout Voltage is defined as the input to output differential when the output voltage drops 100mV below its nominal value.

6) Line Regulation=

$$\frac{\left|V_{OUT[V_{IN(MAX)}]} - V_{OUT[V_{IN(MIN)}]}\right|}{\left[V_{IN(MAX)} - V_{IN(MIN)}\right] \times V_{OUT(NOM)}} \times 100(\% / V)$$

7) Load Regulation=

$$\frac{\left|V_{OUT[I_{OUT(MAX)}]} - V_{OUT[I_{OUT(MIN)}]}\right|}{V_{OUT(NOM)}} \times 100(\%)$$

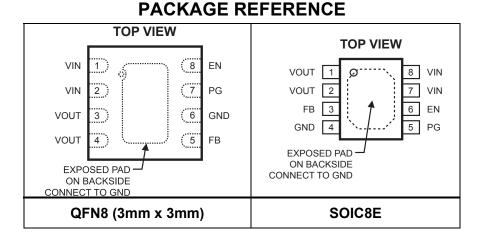

## **PIN DESCRIPTION**

| QFN8 (3X3)<br>Pin # | SOIC8E<br>Pin # | Name                   | Description                                                                                                                                                                                                                        |

|---------------------|-----------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2                | 7, 8            | VIN                    | Regulator Input. Supply voltage ranges from +2.5V to 5.5V. Bypass with $2.2\mu$ F capacitor. These pins must be externally connected for proper operation even if they are internally connected.                                   |

| 3, 4                | 1, 2            | VOUT                   | Regulator output. Bypass with a 2.2 $\mu$ F low-ESR capacitor to GND. Connect all the pin together externally.                                                                                                                     |

| 5                   | 3               | FB                     | Feedback Input.<br>For the adjustable output version, connect FB to the center point of the external resistor divider. The feedback threshold voltage is 1.5V.<br>For the fixed output version, connect FB to the output directly. |

| 6                   | 4               | GND<br>Expose<br>d pad | Ground. Connect exposed pad to GND plane for optimal thermal performance.                                                                                                                                                          |

| 7                   | 5               | PG                     | Open-drain power-good (PG) output.                                                                                                                                                                                                 |

| 8                   | 6               | EN                     | Positive polarity enable (EN) input. Regulator Enable Control Input. Drive EN above 1.5V to turn on the MP20045. Drive EN below 0.4V to turn it off. Do not float the EN pin.                                                      |

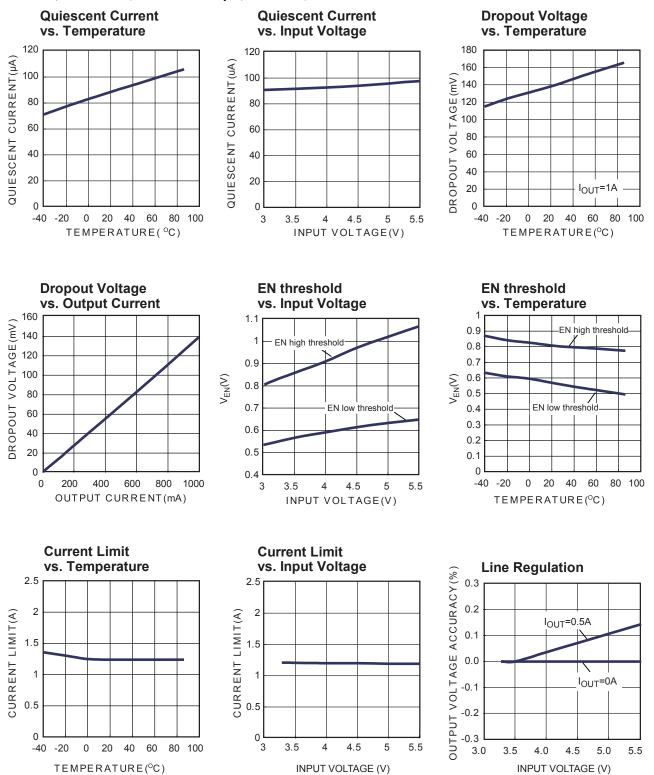

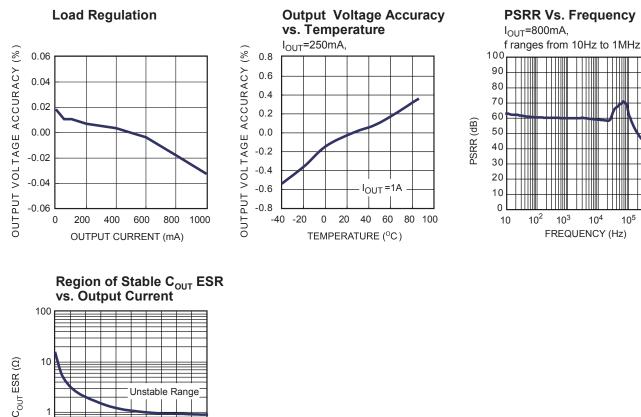

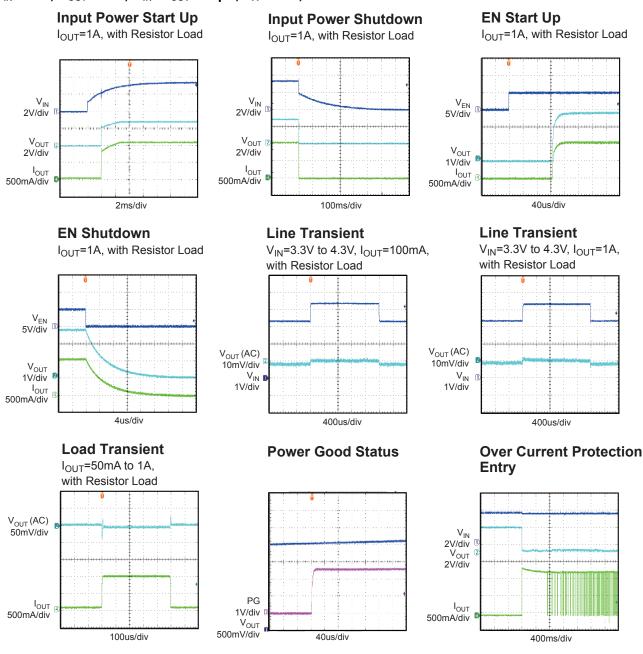

### **TYPICAL PERFORMANCE CHARACTERISTICS**

VIN=3.3V, VOUT=2.8V, CIN=COUT=2.2µF, TA=25°C, unless otherwise noted

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2020 MPS. All Rights Reserved.

Stable Range

400

OUTPUT CURRENT (mA)

600

800

1000

0.1 L

200

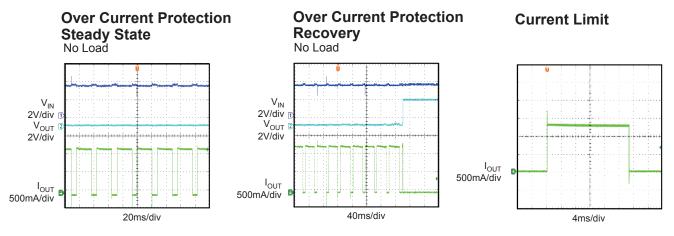

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN}$ =3.3V,  $V_{OUT}$ =2.8V,  $C_{IN}$ = $C_{OUT}$ =2.2 $\mu$ F,  $T_A$ =25°C, unless otherwise noted

10<sup>6</sup>

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN}$ =3.3V,  $V_{OUT}$ =2.8V,  $C_{IN}$ = $C_{OUT}$ =2.2 $\mu$ F,  $T_A$ =25°C, unless otherwise noted

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2020 MPS. All Rights Reserved.

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN}$ =3.3V,  $V_{OUT}$ =2.8V,  $C_{IN}$ = $C_{OUT}$ =2.2 $\mu$ F,  $T_A$ =25°C, unless otherwise noted

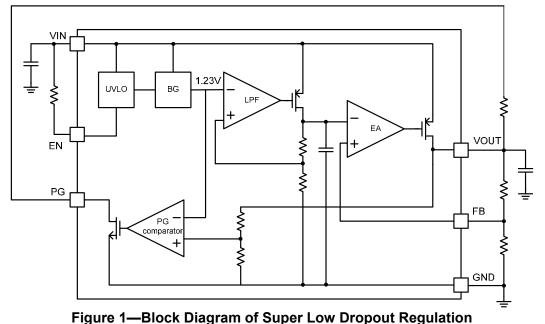

## **BLOCK DIAGRA**

### **OPERATION**

The MP20045 is a low-dropout linear regulator supplies up to 1A current. It is intended for use in devices that require very low voltage, low quiescent, low noise and high PSRR such as wireless LAN, battery powered equipment and hand-held equipment.

The MP20045 uses an internal PMOS as the pass element and features internal thermal shutdown and internal current limit circuit.

#### **Dropout Voltage**

Dropout voltage is the minimum input to output differential voltage required for the regulator to maintain an output voltage within 100mV of its nominal value. Because the PMOS pass element behaves as a low-value resistor, the dropout voltage of MP20045 is very low.

#### Shutdown

The MP20045 can be switched ON or OFF by a logic input at the EN pin. A high voltage at this pin will turn the device on. When the EN pin is low, the regulator output is off. The EN pin should be tied to VIN to keep the regulator output always on if the application does not require the shutdown feature. Do not float the EN pin.

### Current Limit

The MP20045 includes a current limit structures which monitor and control PMOS's gate voltage limiting the guaranteed maximum output current to 1.2A.

#### **Thermal Protection**

Thermal protection turns off the PMOS when the junction temperature exceeds +150°C, allowing the IC to cool. When the IC's junction temperature drops by 20°C, the PMOS will be turned on again. Thermal protection limits total power dissipation in the MP20045. For reliable operation, junction temperature should be limited to 125 °C maximum.

### Load-Transient Considerations

The output response of load-transient consists of a DC shift and transient response. Because of the excellent load regulation of MP20045, the DC shift is very small. The output voltage transient depends on the output capacitor's value and the ESR. Increasing the capacitance and decreasing the ESR will improve the transient response.

MP20045 Rev. 1.11

www.MonolithicPower.com

1/19/2020 MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2020 MPS. All Rights Reserved.

### **APPLICATION INFORMATION**

#### Setting the Output Voltage

The output voltage of MP20045 can be set externally which ranges from 1.5V to 5V by operating from +2.5V to +5.5V input or preset internally at 1.5V, 1.8V, 2.5V, 5V. For the adjustable version, the output voltage is set by using a resistive voltage divider from the output voltage to FB pin. The voltage divider divides the output voltage down to the feedback voltage by the ratio:

$$V_{FB} = V_{OUT} \frac{R2}{R1 + R2}$$

Where  $V_{FB}$  is the feedback threshold voltage  $(V_{FB} = 1.5V)$ , and  $V_{OUT}$  is the output voltage. Thus the output voltage is:

$$V_{OUT} = 1.5 \times \frac{R1 + R2}{R2}$$

R2 can be as high as  $100k\Omega$ , but a typical value is  $10k\Omega$ . Using that value, R1 is determined by:

$$R1 = R2 \times \left(\frac{V_{OUT} - V_{FB}}{V_{FB}}\right)$$

For example, for a 2.8V output voltage, R2 is  $10k\Omega$ , and R1 is  $8.66k\Omega$ . You can select a standard 8.66k $\Omega$  (±1%) resistor for R1.

#### **Power Dissipation**

The power dissipation for any package depends on the thermal resistance of the case and circuit board, the temperature difference between the junction and ambient air, and the rate of air flow. The power dissipation across the device can be represented by the equation:

$$\mathsf{P} = (\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{OUT}}) \times \mathsf{I}_{\mathsf{OUT}}$$

The allowable power dissipation can be calculated using the following equation:

$$P_{(MAX)} = (T_{Junction} - T_{Ambient}) / \theta_{JA}$$

Where  $(T_{Junction} - T_{Ambient})$  is the temperature difference between the junction and the surrounding environment,  $\theta_{JA}$  is the thermal resistance from the junction to the ambient environment. Connecting the GND pin of MP20045 to around using a large pad or ground plane helps to channel heat away.

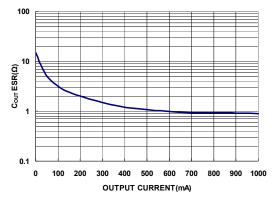

#### **Output Capacitor Selection**

The MP20045 is designed specifically to work with very low ESR ceramic output capacitor in space-saving and performance consideration. A 2.2µF ceramic capacitor with ESR lower than  $0.9\Omega$  is suitable for the MP20045 application circuit. Output capacitor of larger values will help to improve load transient response and reduce noise with the drawback of increased size.

### Figure 2—Relationship between ESR and LDO Stability

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2020 MPS. All Rights Reserved.

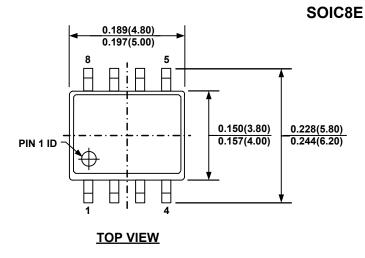

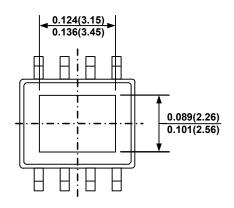

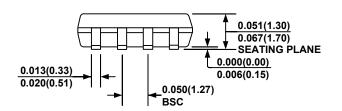

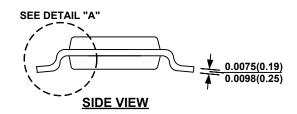

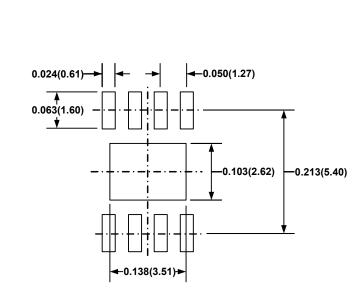

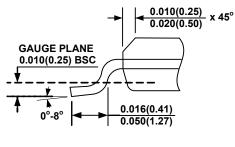

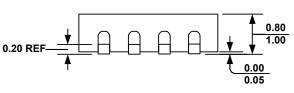

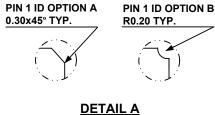

## **PACKAGE INFORMATION**

BOTTOM VIEW

**FRONT VIEW**

#### **RECOMMENDED LAND PATTERN**

DETAIL "A"

### NOTE:

- 1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

- 5) DRAWING CONFORMS TO JEDEC MS-012, VARIATION BA.

- 6) DRAWING IS NOT TO SCALE.

0.2

0.6

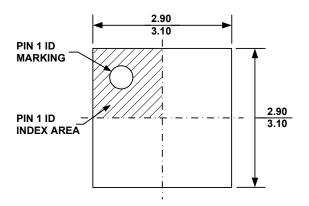

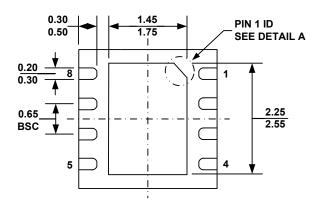

QFN8 (3mm×3mm)

TOP VIEW

**BOTTOM VIEW**

**SIDE VIEW**

2.90 0.7 1 2.50 Т

NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS. 2) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

- 3) LEAD COPLANARITY SHALL BE 0.10 MILLIMETER MAX.

- 4) DRAWING CONFORMS TO JEDEC MO-229, VARIATION VEEC-2. 5) DRAWING IS NOT TO SCALE.

**RECOMMENDED LAND PATTERN**

NOTICE: The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.