# STD150NH02L-1 STD150NH02L

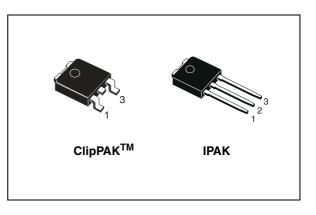

### N-channel 24V - 0.003Ω - 150A - ClipPAK™ - IPAK STripFET™ III Power MOSFET

### **General features**

| Туре          | V <sub>DSSS</sub> | R <sub>DS(on)</sub> | I <sub>D</sub> |

|---------------|-------------------|---------------------|----------------|

| STD150NH02L   | 24V               | <0.0035Ω            | 150A           |

| STD150NH02L-1 | 24V               | <0.0035Ω            | 150A           |

- R<sub>DS(on)</sub> \* Qg industry's benchmark

- Conduction losses reduced

- Switching losses reduced

- Low threshold device

### Description

The STD150NH02L utilizes the latest advanced design rules of ST's proprietary STripFET<sup>™</sup> technology. This novel 0.6µ process utilizes also unique metallization techniques that couple to a "bondless" assembly technique result in outstanding performance with standard DPAK outline. It is therefore ideal in high performance DC-DC converter applications where efficiency it to be achieved at very high out currents.

### Applications

Switching application

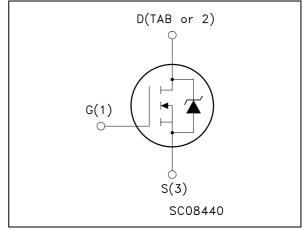

### Internal schematic diagram

#### **Order codes**

| Part number   | Marking   | Package  | Packaging   |

|---------------|-----------|----------|-------------|

| STD150NH02LT4 | D150NH02L | ClipPAK™ | Tape & reel |

| STD150NH02L-1 | D150NH02L | IPAK     | Tube        |

## Contents

| 1 | Electrical ratings                      | 3  |

|---|-----------------------------------------|----|

| 2 | Electrical characteristics              | 4  |

|   | 2.1 Electrical characteristics (curves) | 6  |

| 3 | Test circuit                            | 8  |

| 4 | Package mechanical data                 | 9  |

| 5 | Packaging mechanical data               | 12 |

| 6 | Revision history                        | 15 |

1

# **Electrical ratings**

| Table 1. | Absolute | maximum | ratings |

|----------|----------|---------|---------|

|          |          |         | ·       |

| Symbol                            | Parameter                                         | Value      | Unit |

|-----------------------------------|---------------------------------------------------|------------|------|

| V <sub>spike</sub> <sup>(1)</sup> | Drain-source voltage rating                       | 30         | V    |

| V <sub>DS</sub>                   | Drain-source voltage (V <sub>GS</sub> = 0)        | 24         | V    |

| V <sub>DGR</sub>                  | Drain-gate voltage ( $R_{GS} = 20K\Omega$ )       | 24         | V    |

| V <sub>GS</sub>                   | Drain-source voltage                              | ± 20       | V    |

| I <sub>D</sub>                    | Drain current (continuous) at $T_C = 25^{\circ}C$ | 150        | А    |

| I <sub>D</sub>                    | Drain current (continuous) at $T_C=100^{\circ}C$  | 107        | А    |

| I <sub>DM</sub> <sup>(2)</sup>    | Drain current (pulsed)                            | 600        | А    |

| P <sub>TOT</sub>                  | Total dissipation at $T_{C} = 25^{\circ}C$        | 125        | W    |

|                                   | Derating factor                                   | 0.83       | W/°C |

| E <sub>AS</sub> <sup>(3)</sup>    | Single pulse avalanche energy                     | 500        | mJ   |

| T <sub>stg</sub>                  | Storage temperature                               | -55 to 175 | .0°  |

| TJ                                | Max. operating junction temperature               | -55 10 175 |      |

1. Garanted when external Rg = 4.7  $\Omega$  and  $t_{f}$  <  $t_{fmax}.$

2. Pulse width limited by safe operating area

3. Starting  $T_J = 25 \ ^{o}C$ ,  $I_D = 75A$ ,  $V_{DD} = 10V$

| Table 2. Thermal uata | Table | 2. | Thermal | data |

|-----------------------|-------|----|---------|------|

|-----------------------|-------|----|---------|------|

| Symbol            | Parameter                                         | Value | Unit |

|-------------------|---------------------------------------------------|-------|------|

| R <sub>thJC</sub> | Thermal resistance junction-case Max              | 1.2   | °C/W |

| R <sub>thJA</sub> | Thermal resistance junction-ambient Max           | 100   | °C/W |

| ТI                | Maximum lead temperature for soldering<br>purpose | 275   | °C   |

### 2 Electrical characteristics

(T<sub>CASE</sub>=25°C unless otherwise specified)

| Symbol               | Parameter                                                | Test conditions                                         | Min. | Тур.           | Max.             | Unit     |

|----------------------|----------------------------------------------------------|---------------------------------------------------------|------|----------------|------------------|----------|

| V <sub>(BR)DSS</sub> | Drain-source breakdown<br>voltage                        | I <sub>D</sub> = 25mA, V <sub>GS</sub> = 0              | 24   |                |                  | V        |

| I <sub>DSS</sub>     | Zero gate voltage drain<br>current (V <sub>GS</sub> = 0) | $V_{DS} = 20V$<br>$V_{DS} = 20V$ , $T_C = 125^{\circ}C$ |      |                | 1<br>10          | μA<br>μA |

| I <sub>GSS</sub>     | Gate body leakage current<br>(V <sub>DS</sub> = 0)       | $V_{GS} = \pm 20V$                                      |      |                | ±100             | nA       |

| V <sub>GS(th)</sub>  | Gate threshold voltage                                   | $V_{DS} = V_{GS}, I_D = 250 \mu A$                      | 1    | 1.8            |                  | V        |

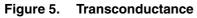

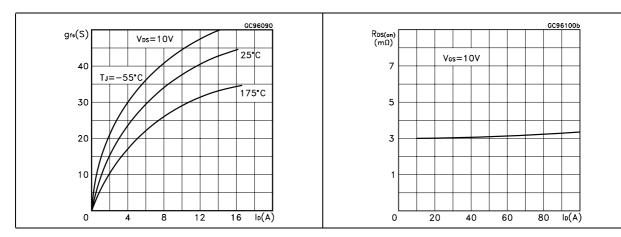

| R <sub>DS(on)</sub>  | Static drain-source on resistance                        | $V_{GS} = 10V, I_D = 75A$<br>$V_{GS} = 5V, I_D = 37.5A$ |      | 0.003<br>0.004 | 0.0035<br>0.0065 | Ω<br>Ω   |

#### Table 3.On<sup>(1)</sup> /off states

1. Pulsed: Pulse duration = 300  $\mu$ s, duty cycle 1.5%

| Symbol                                                   | Parameter                                                                  | Test conditions                                                       | Min. | Тур.                | Max. | Unit           |

|----------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------|------|---------------------|------|----------------|

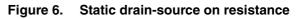

| g <sub>fs</sub> <sup>(1)</sup>                           | Forward transconductance                                                   | $V_{DS} = 10 V_{,} I_{D} = 75A$                                       |      | 60                  |      | S              |

| C <sub>iss</sub><br>C <sub>oss</sub><br>C <sub>rss</sub> | Input capacitance<br>Output capacitance<br>Reverse transfer<br>capacitance | V <sub>DS</sub> = 15V, f = 1 MHz,<br>V <sub>GS</sub> = 0              |      | 4450<br>1126<br>141 |      | pF<br>pF<br>pF |

| Q <sub>g</sub><br>Q <sub>gs</sub><br>Q <sub>gd</sub>     | Total gate charge<br>Gate-source charge<br>Gate-drain charge               | V <sub>DD</sub> = 16V, I <sub>D</sub> = 150A<br>V <sub>GS</sub> = 10V |      | 69<br>13<br>9       | 93   | nC<br>nC<br>nC |

| Q <sub>oss</sub> <sup>(2)</sup>                          | Output charge                                                              | $V_{DS} = 16V, V_{GS} = 0V$                                           |      | 27                  |      | nC             |

| Q <sub>gls</sub> <sup>(3)</sup>                          | Third-quadrant gate charge                                                 | $V_{\rm DS}$ < 0V, $V_{\rm GS}$ = 10V                                 |      | 64                  |      | nC             |

| R <sub>G</sub>                                           | Gate input resistance                                                      | f = 1MHz gate DC Bias = 0<br>Test signal level = 20mV<br>Open drain   |      | 1.6                 |      | Ω              |

1. Pulsed: pulse duration=300 $\mu$ s, duty cycle 1.5%

2.  $Q_{oss} = C_{oss}^{*} \Delta V_{in}, C_{oss} = C_{gd} + C_{ds}$ . See Appendix A

3. Gate charge for synchronous operation

|                                                                               | officining timeo                                                    |                                                                                             |      |                       |      |                      |

|-------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------|-----------------------|------|----------------------|

| Symbol                                                                        | Parameter                                                           | Test conditions                                                                             | Min. | Тур.                  | Max. | Unit                 |

| t <sub>d(on)</sub><br>t <sub>r</sub><br>t <sub>d(off)</sub><br>t <sub>f</sub> | Turn-on delay time<br>Rise time<br>Turn-off delay time<br>Fall time | $V_{DD} = 10V, I_D = 75A,$<br>$R_G = 4.7\Omega, V_{GS} = 10V$<br><i>Figure 13 on page 8</i> |      | 14<br>224<br>69<br>40 | 54   | ns<br>ns<br>ns<br>ns |

Table 5. Switching times

#### Table 6.Source drain diode

| Symbol                                                 | Parameter                                                                    | Test conditions                                                                                          | Min | Тур.            | Max  | Unit          |

|--------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----|-----------------|------|---------------|

| I <sub>SD</sub>                                        | Source-drain current                                                         |                                                                                                          |     |                 | 150  | А             |

| I <sub>SDM</sub>                                       | Source-drain current (pulsed)                                                |                                                                                                          |     |                 | 600  | А             |

| V <sub>SD</sub> <sup>(1)</sup>                         | Forward on voltage                                                           | I <sub>SD</sub> = 75A, V <sub>GS</sub> = 0                                                               |     |                 | 1.15 | V             |

| t <sub>rr</sub><br>Q <sub>rr</sub><br>I <sub>RRM</sub> | Reverse recovery time<br>Reverse recovery charge<br>Reverse recovery current | $I_{SD} = 150A,$<br>di/dt = 100A/µs,<br>$V_{DD} = 15V, T_J = 150^{\circ}C$<br><i>Figure 15 on page 8</i> |     | 47<br>58<br>2.5 |      | ns<br>μC<br>Α |

1. Pulsed: pulse duration=300µs, duty cycle 1.5%

GC94590

$Z_{th} = k R_{thJ-c}$

$10^{-1} t_{P}(s)$

$\delta = t_p / \tau$

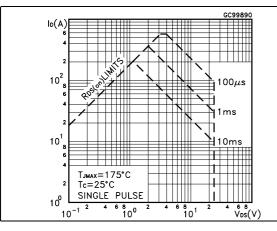

#### 2.1 Electrical characteristics (curves)

#### Figure 1. Safe operating area

Figure 2.

K d=0.5

10

10

Figure 4.

10<sup>-5</sup>

**Thermal impedance**

0.05 0.02

0.01

10<sup>-2</sup>

10<sup>-3</sup>

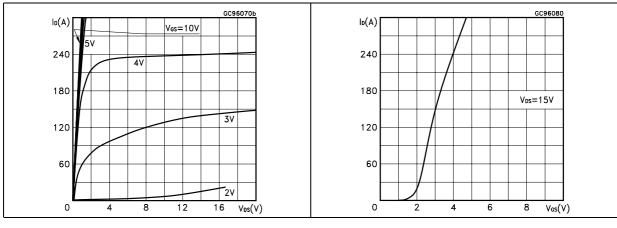

**Transfer characteristics**

SINGLE PULSE

10<sup>-4</sup>

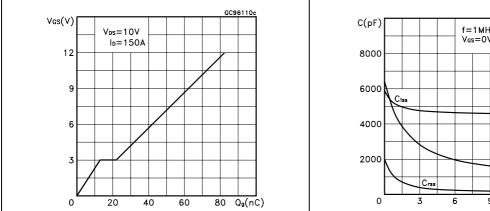

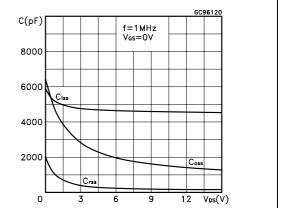

#### Gate charge vs gate-source voltage Figure 8. Capacitance variations Figure 7.

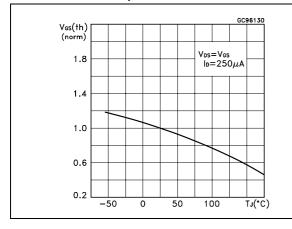

Figure 9. Normalized gate threshold voltage vs temperature

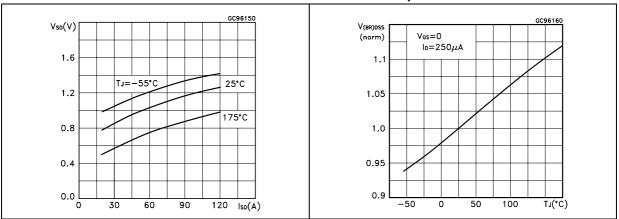

Figure 11. Source-drain diode forward characteristics

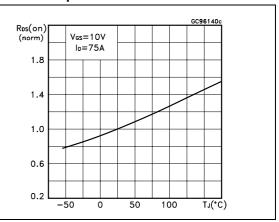

Figure 10. Normalized on resistance vs temperature

Figure 12. Normalized breakdown voltage vs temperature

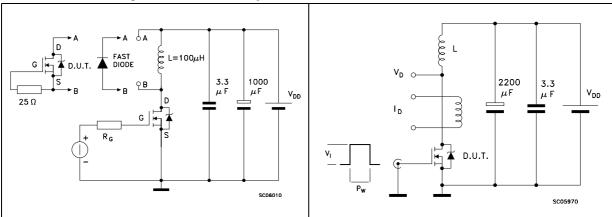

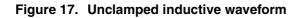

### 3 Test circuit

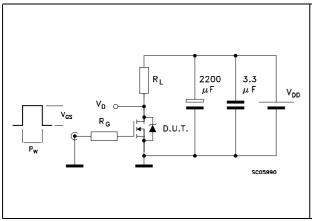

Figure 13. Switching times test circuit for resistive load

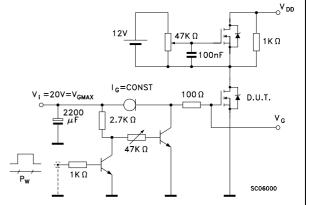

Figure 14. Gate charge test circuit

Figure 15. Test circuit for inductive load switching and diode recovery times

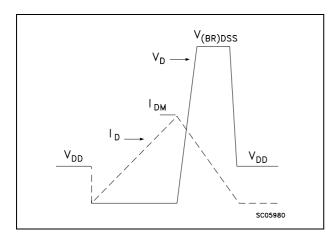

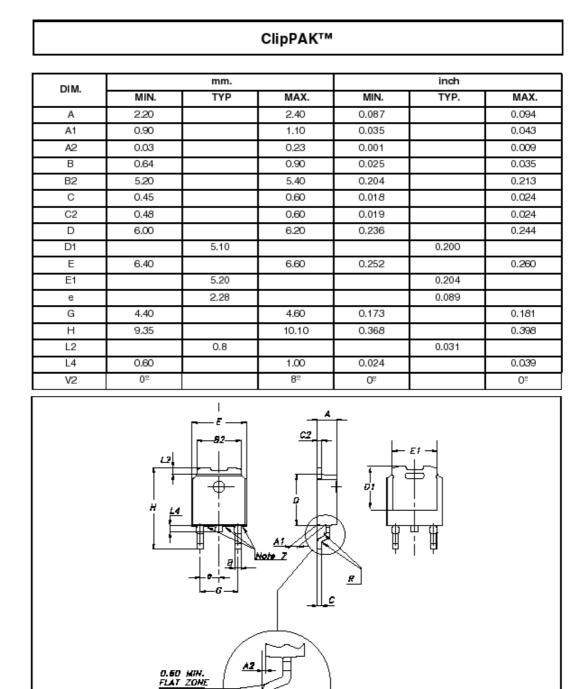

### 4 Package mechanical data

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a Lead-free second level interconnect . The category of second level interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com

STD150NH02L

| DIM. | mm   |      |      | inch  |       |       |

|------|------|------|------|-------|-------|-------|

|      | MIN. | TYP. | MAX. | MIN.  | TYP.  | MAX.  |

| А    | 2.2  |      | 2.4  | 0.086 |       | 0.094 |

| A1   | 0.9  |      | 1.1  | 0.035 |       | 0.043 |

| A3   | 0.7  |      | 1.3  | 0.027 |       | 0.051 |

| В    | 0.64 |      | 0.9  | 0.025 |       | 0.031 |

| B2   | 5.2  |      | 5.4  | 0.204 |       | 0.212 |

| B3   |      |      | 0.85 |       |       | 0.033 |

| B5   |      | 0.3  |      |       | 0.012 |       |

| B6   |      |      | 0.95 |       |       | 0.037 |

| С    | 0.45 |      | 0.6  | 0.017 |       | 0.023 |

| C2   | 0.48 |      | 0.6  | 0.019 |       | 0.023 |

| D    | 6    |      | 6.2  | 0.236 |       | 0.244 |

| E    | 6.4  |      | 6.6  | 0.252 |       | 0.260 |

| G    | 4.4  |      | 4.6  | 0.173 |       | 0.181 |

| Н    | 15.9 |      | 16.3 | 0.626 |       | 0.641 |

| L    | 9    |      | 9.4  | 0.354 |       | 0.370 |

| L1   | 0.8  |      | 1.2  | 0.031 |       | 0.047 |

| L2   |      | 0.8  | 1    |       | 0.031 | 0.039 |

#### TO-251 (IPAK) MECHANICAL DATA

ClipPAK

57

5

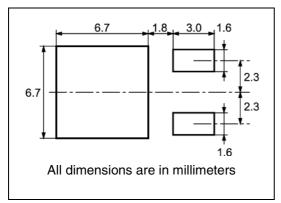

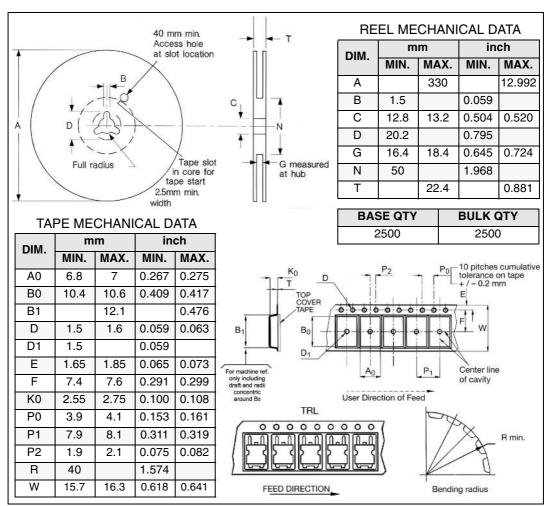

# Packaging mechanical data

**DPAK FOOTPRINT**

#### TAPE AND REEL SHIPMENT

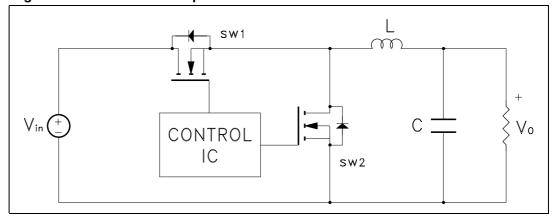

### Appendix A Buck converter - power losses estimation

Figure 18. Buck converter: power losses estimation

The power losses associated with the FETs in a synchronous buck converter can be estimated using the equations shown in the table below. The formulas give a good approximation, for the sake of performance comparison, of how different pairs of devices affect the converter efficiency. However a very important parameter, the working temperature, is not considered. The real device behavior is really dependent on how the heat generated inside the devices is removed to allow for a safer working junction temperature.

- The low side (SW2) device requires:

- Very low R<sub>DS(on)</sub> to reduce conduction losses

- Small QgIs to reduce the gate charge losses

- Small Coss to reduce losses due to output capacitance

- Small Qrr to reduce losses on SW1 during its turn-on

- The Cgd/Cgs ratio lower than Vth/Vgg ratio especially with low drain to source

- voltage to avoid the cross conduction phenomenon;

- The high side (SW1) device requires:

- Small Rg and Ls to allow higher gate current peak and to limit the voltage feedback on the gate

- Small Qg to have a faster commutation and to reduce gate charge losses

- Low R<sub>DS(on)</sub> to reduce the conduction losses.

|                        |                 | High side switching (SW1)                                      | Low side switch (SW2)                  |

|------------------------|-----------------|----------------------------------------------------------------|----------------------------------------|

| Pconduction            |                 | $R_{DS(on)SW1} * I_L^2 * \delta$                               | $R_{DS(on)SW2} * I_L^2 * (1 - \delta)$ |

| Pswitching             |                 | $V_{in} * (Q_{gsth(SW1)} + Q_{gd(SW1)}) * f * \frac{I_L}{I_g}$ | Zero Voltage Switching                 |

| Pdiode                 | Recovery<br>(1) | Not applicable                                                 | $V_{in} * Q_{rr(SW2)} * f$             |

| Paloae                 | Conductio<br>n  | Not applicable                                                 | $V_{f(SW2)} * I_L * t_{deadtime} * f$  |

| Pgate(Q <sub>G</sub> ) |                 | $Q_{g(SW1)} * V_{gg} * f$                                      | $Q_{gls(SW2)} * V_{gg} * f$            |

| P <sub>Qoss</sub>      |                 | $\frac{V_{in} * Q_{oss(SW1)} * f}{2}$                          | $\frac{V_{in} * Q_{oss(SW2)} * f}{2}$  |

Table 7.

Power losses calculation

1. Dissipated by SW1 during turn-on

| Parameter         | Meaning                                      |  |

|-------------------|----------------------------------------------|--|

| d                 | Duty-cycle                                   |  |

| Q <sub>gsth</sub> | Post threshold gate charge                   |  |

| Q <sub>gls</sub>  | Third quadrant gate charge                   |  |

| Pconduction       | On state losses                              |  |

| Pswitching        | On-off transition losses                     |  |

| Pdiode            | Conduction and reverse recovery diode losses |  |

| Pgate             | Gate drive losses                            |  |

| P <sub>Qoss</sub> | Output capacitance losses                    |  |

# 6 Revision history

| Table 9. | Revision | history |

|----------|----------|---------|

|----------|----------|---------|

| Date        | Revision | Changes                           |

|-------------|----------|-----------------------------------|

| 09-Sep-2004 | 6        | Preliminary data                  |

| 21-Jun-2005 | 7        | Complete version with curves      |

| 28-Jul-2006 | 8        | The document has been reformatted |

| 20-Dec-2006 | 9        | Typo mistake on <i>Table 3</i> .  |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2006 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com