## N-Channel Enhancement Mode MOS Transistor

## HCT7000M, HCT70000MTX, HCT7000MTXV

#### Features:

- 200 mA I<sub>D</sub>

- Ultra small surface mount package

- $R_{DS(ON)} < 5\Omega$

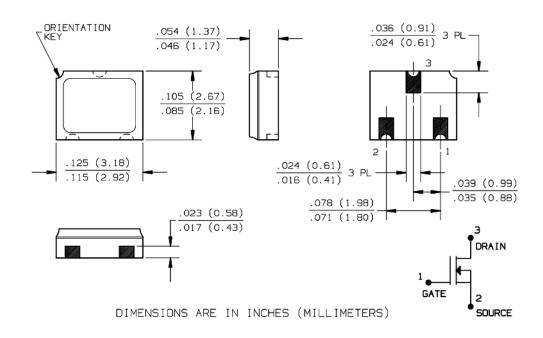

- Pin-out compatible with most SOT23 MOSFETS

### **Description:**

The HCT7000M is a high performance enhancement mode N-channel MOS transistor chip packaged in the ultra small 3 pin ceramic LCC package. Electrical characteristics are similar to those of the JEDEC 2N7000. The pin-out and footprint matches that of most enhancement mode MOS transistors built in SOT23 plastic packages.

TX and TXV devices are processed to OPTEK's military screening program patterned after MIL-PRF-19500. TX products receive a  $V_{GS}$  HTRB at 24 V for 48 hrs. at 150° C and a  $V_{DS}$  HTRB at 48 V for 260 hrs.at 150° C.

#### **Applications:**

- Switching applications: small servo motor control, power MOSFET gate drives

- Relay Drivers

- High Speed Line Drivers

- Power Supplies

| Part<br>Number | Sensor Type | V <sub>DSS</sub><br>Min | V <sub>GS(TH)</sub> Min/<br>Max | I <sub>D(ON)</sub> (mA)<br>Min | G <sub>fs</sub> (ms)<br>Min | t <sub>(ON)</sub> / t <sub>(OFF)</sub> (ns)<br>Max | Package       |

|----------------|-------------|-------------------------|---------------------------------|--------------------------------|-----------------------------|----------------------------------------------------|---------------|

| HCT7000M       | N-Channel   |                         |                                 |                                |                             |                                                    |               |

| HCT7000MTX     | Enhanced    | 60                      | 0.8 / 3.0                       | 75                             | 100                         | 10 / 10                                            | 3-pin Ceramic |

| HCT7000MTXV    | MOSFET      |                         |                                 |                                |                             |                                                    |               |

# N-Channel Enhancement Mode MOS Transistor

# HCT7000M, HCT70000MTX, HCT7000MTXV

### **Performance**

| Absolute Maximum Ratings                                  |                       |  |  |  |

|-----------------------------------------------------------|-----------------------|--|--|--|

| Drain Source Voltage                                      | 60V                   |  |  |  |

| Gate-Source Voltage                                       | ±40 V                 |  |  |  |

| Drain Current                                             | 200 mA                |  |  |  |

| Power Dissipation (T <sub>A</sub> = 25° C)                | 300 mW                |  |  |  |

| Power Dissipation (T <sub>s</sub> <sup>(1)</sup> = 25° C) | 600 mW <sup>(2)</sup> |  |  |  |

| Operating and Storage Temperature                         | -55° C to 150° C      |  |  |  |

| Thermal Resistance R <sub>ØJC</sub>                       | 100° C/W              |  |  |  |

| Thermal Resistance R <sub>ØJA</sub>                       | 583° C/W              |  |  |  |

### Electrical Characteristics (T<sub>A</sub> = 25° C unless otherwise noted)

| SYMBOL              | PARAMETER                       | MIN | MAX | UNITS | TEST CONDITIONS                                                           |  |

|---------------------|---------------------------------|-----|-----|-------|---------------------------------------------------------------------------|--|

| V <sub>DSS</sub>    | Drain Source Voltage            | 60  |     | V     | V <sub>GS</sub> = 0 V, I <sub>D</sub> = 10 μa                             |  |

| V <sub>GS(TH)</sub> | Gate Threshold Voltage          | .8  | 3.0 | V     | $V_{DS} = V_{GS}$ , $I_D = 1$ mA                                          |  |

| I <sub>GSS</sub>    | Gate Leakage                    |     | ±10 | nA    | V <sub>DS</sub> = 0 V, V <sub>GS</sub> = ±15 V                            |  |

| I <sub>DSS</sub>    | Zero Gate Voltage Drain Current |     | 1   | μΑ    | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 48 V                             |  |

| I <sub>D(ON)</sub>  | On-Site Drain Current           | 75  |     | mA    | V <sub>DS</sub> = 10 V, V <sub>GS</sub> = 4.5 V                           |  |

| R <sub>DS(ON)</sub> | Drain Source on-Resistance      |     | 5   | Ω     | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 0.5 A                            |  |

| V <sub>DS(ON)</sub> | Drain Source on-Voltage         |     | 2.5 | V     | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 0.5 A                            |  |

| G <sub>fs</sub>     | Forward Transconductance        |     |     | mS    | V <sub>DS</sub> = 10 V, I <sub>D</sub> = 0.2 A                            |  |

| C <sub>iss</sub>    | Input Capacitance               |     | 60  | pF    |                                                                           |  |

| C <sub>oss</sub>    | Output Capacitance              |     | 25  | pF    | $V_{DS} = 25 \text{ V}, V_{GS} = 0 \text{ V}, f = 1 \text{MHz}$           |  |

| C <sub>rss</sub>    | Reverse Transfer Capacitance    |     | 5   | pF    |                                                                           |  |

| t <sub>(on)</sub>   | Turn-on Time                    |     | 10  | ns    | $V_{DD}$ = 15 V, $I_{D}$ = 0.5 A, $V_{gen}$ = 10 V, $R_{g}$ = 25 $\Omega$ |  |

| t <sub>(off)</sub>  | Turn-off Time                   |     | 10  | ns    |                                                                           |  |

#### Note:

<sup>1)</sup>  $T_S$  = Substrate temperature that the chip carrier is mounted on.

<sup>2)</sup> This rating is provided as an aid to designers. It is dependent upon mounting material and methods and is not measurable as an outgoing test.