| <b>F</b> EE |     | B |

|-------------|-----|---|

| E           | 153 |   |

# 4-BIT PARALLEL-TO-SERIAL CONVERTER

### SY10E446 SY100E446

- On-chip clock ÷4 and ÷8

- Extended 100E VEE range of -4.2V to -5.5V

- 1.6Gb/s typical data rate capability

- Differential clock and serial inputs

- VBB output for single-ended use

- Asynchronous data synchronization

- Mode select to expand to 8 bits

- Internal 75KΩ input pulldown resistors

- Fully compatible with Motorola MC10E/100E446

- Available in 28-pin PLCC package

| Pin             | Function                        |

|-----------------|---------------------------------|

| SIN, <u>SIN</u> | Differential Serial Data Input  |

| D0 – D3         | Parallel Data Input             |

| SOUT, SOUT      | Differential Serial Data Output |

| CLK, CLK        | Differential Clock Input        |

| CL/4, CL/4      | Differential 4 Clock Output     |

| CL/8, CL/8      | Differential 8 Clock Output     |

| MODE            | Conversion Mode, 4-bit/8-bit    |

| SYNC            | Conversion Synchronizing Input  |

| Vcco            | Vcc to Output                   |

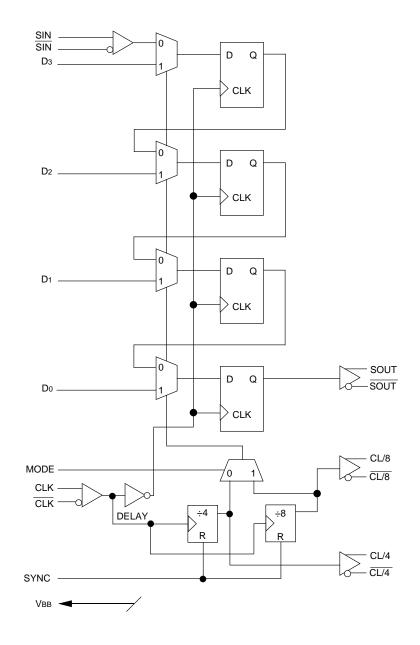

The SY10/100E446 are integrated 4-bit parallel-toserial data converters. These devices are designed to operate for NRZ data rates of up to a minimum of 1.3Gb/ s. The chips generate a divide-by-4 and a divide-by-8 clock for both 4-bit conversion and a two-chip 8-bit conversion function. The conversion sequence was chosen to convert the parallel data into a serial stream from bit D0 to D3. A serial input is provided to cascade two E446 devices for 8-bit conversion applications.

The SYNC input will asynchronously reset the internal clock circuitry. This pin allows the user to reset the internal clock conversion unit and, thus, select the start of the conversion process.

The MODE input is used to select the conversion mode of the device. With the MODE input LOW (or open) the device will function as a 4-bit converter. When the mode input is driven HIGH, the internal load clock will change on every eighth clock cycle, thus allowing for an 8-bit conversion scheme using two E446s. When cascaded in an 8-bit conversion scheme, the devices will not operate at the 1.3Gb/s data rate of a single device. Refer to the applications section of this data sheet for more information on cascading the E446.

For lower data rate applications, a VBB reference voltage is supplied for single-ended inputs. When operating at clock rates above 500MHz, differential input signals are recommended. For single-ended inputs, the VBB pin is tied to the inverting differential input and bypassed via a  $0.01\mu$ F capacitor. The VBB provides the switching reference for the input differential amplifier. The VBB can also be used to AC couple an input signal.

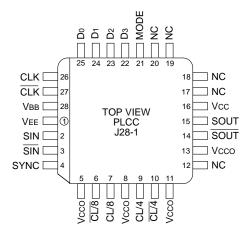

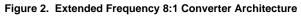

#### 28-Pin PLCC (J28-1)

# Ordering Information<sup>(1)</sup>

| Part Number                     | Package<br>Type | Operating<br>Range | Package<br>Marking                             | Lead<br>Finish      |

|---------------------------------|-----------------|--------------------|------------------------------------------------|---------------------|

| SY10E446JC                      | J28-1           | Commercial         | SY10E446JC                                     | Sn-Pb               |

| SY10E446JCTR <sup>(2)</sup>     | J28-1           | Commercial         | SY10E446JC                                     | Sn-Pb               |

| SY100E446JC                     | J28-1           | Commercial         | SY100E446JC                                    | Sn-Pb               |

| SY100E446JCTR <sup>(2)</sup>    | J28-1           | Commercial         | SY100E446JC                                    | Sn-Pb               |

| SY10E446JZ <sup>(3)</sup>       | J28-1           | Commercial         | SY10E446JZ with<br>Pb-Free bar-line indicator  | Matte-Sn<br>Pb-Free |

| SY10E446JZTR <sup>(2, 3)</sup>  | J28-1           | Commercial         | SY10E446JZ with<br>Pb-Free bar-line indicator  | Matte-Sn<br>Pb-Free |

| SY100E446JZ <sup>(3)</sup>      | J28-1           | Commercial         | SY100E446JZ with Pb-Free bar-line indicator    | Matte-Sn<br>Pb-Free |

| SY100E446JZTR <sup>(2, 3)</sup> | J28-1           | Commercial         | SY100E446JZ with<br>Pb-Free bar-line indicator | Matte-Sn<br>Pb-Free |

Notes:

1. Contact factory for die availability. Dice are guaranteed at  $T_A = 25^{\circ}C$ , DC Electricals only.

2. Tape and Reel.

| Mode | Conversion |

|------|------------|

| L    | 4-Bit      |

| н    | 8-Bit      |

# VEE = VEE (Min.) to VEE (Max.); VCC = VCCO = GND

|        |                                                            | TA = 0°C       |            | TA = +25°C     |                |            | TA = +85°C     |                |            |                |      |           |

|--------|------------------------------------------------------------|----------------|------------|----------------|----------------|------------|----------------|----------------|------------|----------------|------|-----------|

| Symbol | Parameter                                                  | Min.           | Тур.       | Max.           | Min.           | Тур.       | Max.           | Min.           | Тур.       | Max.           | Unit | Condition |

| Іін    | Input HIGH Current                                         |                |            | 150            | _              | _          | 150            | _              | _          | 150            | μΑ   |           |

| Vон    | Output HIGH Voltage<br>(SOUT Only) 10E<br>(SOUT Only) 100E | -1020<br>-1025 |            | 790<br>830     | -980<br>-1025  |            | -760<br>-830   | -910<br>-1025  |            | -670<br>-830   | V    | 1         |

| Vbb    | Output Reference Voltage<br>10E<br>100E                    | -1.38<br>-1.38 | _          | -1.27<br>-1.26 | -1.35<br>-1.38 | _          | -1.25<br>-1.26 | -1.31<br>-1.38 | _          | -1.19<br>-1.26 | V    | _         |

| IEE    | Power Supply Current<br>10E<br>100E                        |                | 110<br>110 | 132<br>132     |                | 110<br>110 | 132<br>132     |                | 110<br>127 | 132<br>152     | mA   | —         |

#### Note:

1. The maximum VoH limit was relaxed from standard ECL due to the high frequency output design. All other outputs are specified with the standard 10E and 100E VoH levels.

#### VEE = VEE (Min.) to VEE (Max.); VCC = VCCO = GND

|          |                                                                                                | TA = 0°C                  |                            |                              | TA = +25°C                |                            |                              | TA                        | = +85°                     | С                            |             |           |

|----------|------------------------------------------------------------------------------------------------|---------------------------|----------------------------|------------------------------|---------------------------|----------------------------|------------------------------|---------------------------|----------------------------|------------------------------|-------------|-----------|

| Symbol   | Parameter                                                                                      | Min.                      | Тур.                       | Max.                         | Min.                      | Тур.                       | Max.                         | Min.                      | Тур.                       | Max.                         | Unit        | Condition |

| fmax     | Max. Conversion Frequency                                                                      | 1.3                       | 1.6                        | —                            | 1.3                       | 1.6                        | —                            | 1.3                       | 1.6                        | _                            | Gb/s<br>NRZ | _         |

| tPD      | Propagation Delay to Output<br>CLK to SOUT<br>CLK to CL/4<br>CLK to CL/8<br>SYNC to CL/4, CL/8 | 1000<br>500<br>800<br>500 | 1400<br>800<br>1100<br>800 | 1700<br>1100<br>1400<br>1100 | 1000<br>500<br>800<br>500 | 1400<br>800<br>1100<br>800 | 1700<br>1100<br>1400<br>1100 | 1000<br>500<br>800<br>500 | 1400<br>800<br>1100<br>800 | 1700<br>1100<br>1400<br>1100 | ps          | _         |

| ts       | Set-up Time<br>SIN<br>Dn<br>Mode                                                               | -200<br>-200<br>0         | -400<br>-400<br>-250       |                              | -200<br>-200<br>0         | -400<br>-400<br>-250       |                              | -200<br>-200<br>0         | -400<br>-400<br>-250       |                              | ps          | _         |

| tΗ       | Hold Time<br>SIN<br>Dn<br>Mode                                                                 | 750<br>800<br>500         | 550<br>600<br>300          |                              | 750<br>800<br>500         | 550<br>600<br>300          |                              | 750<br>800<br>500         | 550<br>600<br>300          |                              | ps          | _         |

| trr      | Reset Recovery Time                                                                            | 500                       | 200                        | _                            | 500                       | 200                        | _                            | 500                       | 200                        | _                            | ps          | _         |

| tPW      | Minimum Pulse Width<br>CLK, MR                                                                 | 400                       | —                          | —                            | 400                       | _                          | —                            | 400                       | _                          | _                            | ps          | _         |

| tr<br>tf | Rise/Fall Time<br>SOUT<br>Other                                                                | 100<br>200                | 225<br>425                 | 350<br>650                   | 100<br>200                | 225<br>425                 | 350<br>650                   | 100<br>200                | 225<br>425                 | 350<br>650                   | ps          | 20–80%    |

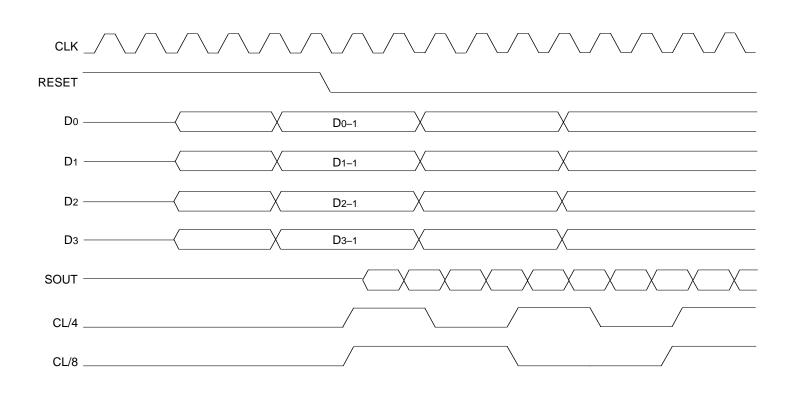

Timing Diagram A. 4:1 Parallel-to-Serial Conversion

| CLK       |   |        |

|-----------|---|--------|

| RESET     |   |        |

| D0 -      | X | D0-1 X |

| D1 -      |   | D1-1   |

| D2 -      | X | D2-1   |

| D3 -      | X | D3–1   |

| D4(D0B) - | X | D4–1   |

| D5(D1B) - | X | D5-1   |

| D6(D2B) - | X | D6–1 X |

| D7(D3B) - | X | D7–1   |

| SOUT -    |   |        |

| -         |   |        |

| -         |   |        |

Timing Diagram B. 8:1 Parallel-to-Serial Conversion

The SY10E/100E446 are integrated 4:1 parallel-to-serial converters. The chips are designed to work with the E445 device to provide both transmission and receiving of a high-speed serial data path. The E446 can convert 4 bits of data into a 1.3Gb/s NRZ data stream. The device features a SYNC input which allows the user to reset the internal clock circuitry and restart the conversion sequence (see Timing Diagram A). Note that SOUT is triggered by negative clock edges.

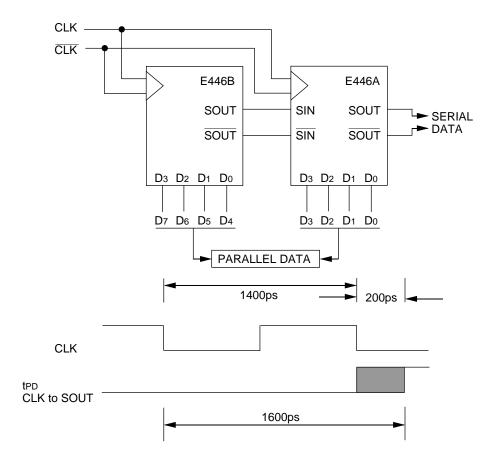

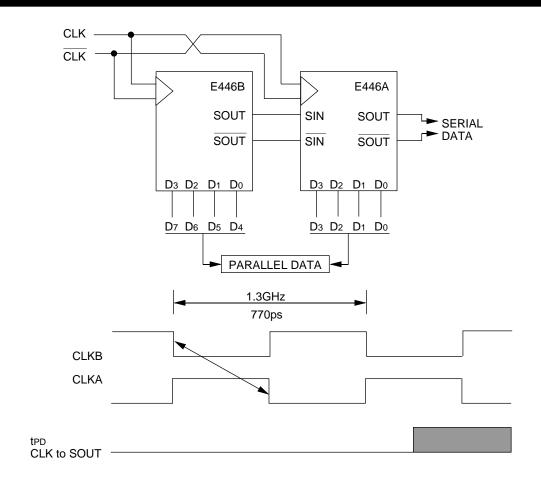

The E446 features a differential serial input and internal divide-by-eight circuitry to facilitate the cascading of two devices to build an 8:1 multiplexer. Figure 1 illustrates the architecture for an 8:1 multiplexer using two E446s (see Timing Diagram B). Notice the serial outputs (SOUT) of the lower order converter feed the serial inputs of the higher order device. This feed through of the serial inputs bounds the upper end of the frequency of operation. The clock-to-serial output propagation delay, plus the set-up time of the

serial input pins, must fit into a single clock period for the cascade architecture to function properly. Using the worst case values for these two parameters from the data sheet, tPD CLK to SOUT = 1600ps and ts for SIN = -200ps, yields a minimum period of 1400ps or a clock frequency of 700MHz.

The clock frequency is somewhat lower than that of a single converter. In order to increase this frequency, it is recommended that the clock edge feeding the E446A be delayed with respect to the E446B, as shown in Figure 2.

Perhaps the easiest way to delay the second clock relative to the first is to take advantage of the differential clock inputs of the E446. By connecting the clock for E446A to the complimentary clock input pin, the device will clock a half a clock period after E446B (Figure 2). Utilizing this simple technique will raise the potential conversion frequency up to the maximum 1.3GHz of a stand-alone E446.

Figure 1. Cascaded 8:1 Converter Architecture

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL + 1 (408) 944-0800 FAX + 1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is at Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2006 Micrel, Incorporated.