36V, 2.2A, Low Quiescent Current

The Future of Analog IC Technology

Synchronous Step-Down Convertor Evaluation Board

### NOT RECOMMENDED FOR NEW DESIGNS, REFER TO EVQ4432-L-00A

### **DESCRIPTION**

The EV4432-L-00A is an evaluation board for the MP/MPQ4432GL.

MP/MPQ4432GL is a frequency programmable (350kHz to 2.5MHz), synchronous, step-down, switching regulator with integrated internal high-side and low-side power MOSFETs. It provides up to 2.2A highly efficient output current with current mode control for fast loop response.

The MP/MPQ4432GL employs AAM (Advanced Asynchronous Modulation) mode which helps to achieve high efficiency at light load condition by scaling down the switching frequency to reduce the switching and gate driving losses.

The EV4432-L-00A is a fully assembled and tested evaluation board, it generates +3.3V output voltage at load current up to 2.2A from a 3.3V to 36V input range.

### **ELECTRICAL SPECIFICATIONS**

| Parameter      | Symbol           | Value    | Units |

|----------------|------------------|----------|-------|

| Input Voltage  | V <sub>IN</sub>  | 3.3 – 36 | V     |

| Output Voltage | V <sub>OUT</sub> | 3.3      | V     |

| Output Current | Іоит             | 2.2      | Α     |

#### **FEATURES**

- Wide 3.3V-to-36V Operating Input Range

- 2.2A Continuous Output Current

- 1µA Low Shutdown Mode Current

- 10µA Sleep Mode Quiescent Current

- Internal  $90m\Omega$  High-Side and  $40m\Omega$  Low-Side MOSFETs

- 350kHz to 2.5MHz Programmable Switching Frequency

- Synchronize to External Clock Selectable In-Phase or 180° Out-of-Phase

- Power Good Indicator

- Programmable Soft-Start Time

- 80ns Minimum On Time

- Selectable Forced CCM and AAM

- Low Dropout Mode

- Over-Current Protection with Valley-Current Detection and Hiccup

- Thermal Shutdown

- Available in Wettable Flank

- Available in AEC-Q100 Grade-1

- Fully Assembled and Tested

### **APPLICATIONS**

- Automotive Systems

- Industrial Power Systems

All MPS parts are lead-free, halogen free, and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

### **EVALUATION BOARD**

(L x W x H) 2.5" x 2.5" x 0.4" (6.4cm x 6.4cm x 1.0cm)

| Board Number | MPS IC Number |  |

|--------------|---------------|--|

| EV4432-L-00A | MP/MPQ4432GL  |  |

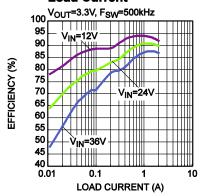

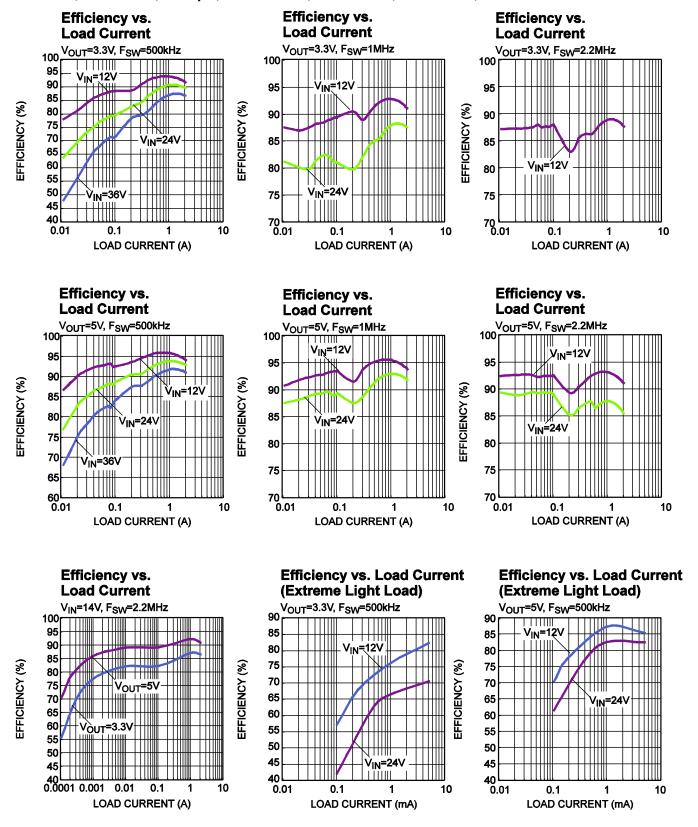

#### Efficiency vs. Load Current

### **QUICK START GUIDE**

- 1. Connect the positive and negative terminals of the load to the VOUT and GND pins, respectively.

- Be aware that electronic loads represent a negative impedance to the regulator and if set to a too high current will trigger Hiccup mode.

- Preset the power supply output to between 3.3V and 36V, and then turn it off.

If longer cables are used between the source and the EVB (>0.5m total), a damping capacitor should be installed at the input terminals. Especially when Vin is ≥ 24V.

- 3. Connect the positive and negative terminals of the power supply output to the VIN and GND pins, respectively.

- 4. Turn the power supply on. The MP/MPQ4432GL will automatically startup.

- 5. To use the Enable function, apply a digital input to the EN pin. Drive EN higher than 1.05V to turn on the regulator, drive EN less than 0.93V to turn it off.

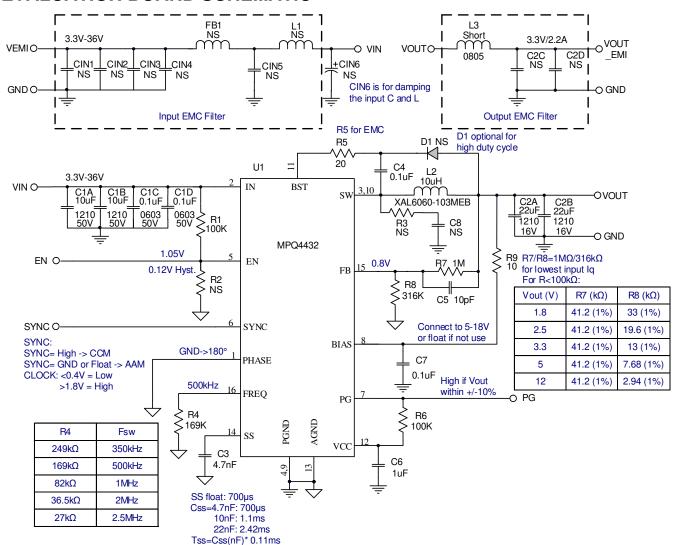

- 6. The oscillating frequency of MP/MPQ4432 can be programmed by an external frequency resistor  $R_{\text{FREQ}}$ . The value of  $R_{\text{FREQ}}$  can be estimated with below equation:

$$R_{FREQ}(k\Omega) = \frac{170000}{f_{SW}^{1.11}(kHz)}$$

- 7. To use the Sync function, apply a 350kHz to 2.5MHz clock to the Sync pin to synchronize the internal oscillator frequency to the external clock. The external clock should be at least 250kHz larger than R<sub>FREQ</sub> set frequency. The SYNC pin can also be used to select forced CCM mode or AAM mode. Drive it high before the chip starts up to choose forced CCM mode, and drive it low or leave it float to choose AAM mode.

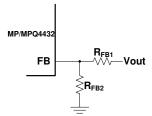

- 8. The output voltage is set by the external resistor divider. Choose  $R_{FB1}$  to be around  $40k\Omega$ . Then  $R_{FB2}$  can be calculated with below equation:

$$R_{FB2} = \frac{R_{FB1}}{\frac{V_{OUT}}{0.8V} - 1}$$

Below table lists the recommended feedback resistor values for common output voltages.

| V <sub>OUT</sub> (V) | $R_{FB1}$ ( $k\Omega$ ) | $R_{FB2}$ ( $k\Omega$ ) |

|----------------------|-------------------------|-------------------------|

| 1.8                  | 41.2 (1%)               | 33 (1%)                 |

| 2.5                  | 41.2 (1%)               | 19.6 (1%)               |

| 3.3                  | 41.2 (1%)               | 13 (1%)                 |

| 5                    | 41.2 (1%)               | 7.68 (1%)               |

| 12                   | 41.2 (1%)               | 2.94 (1%)               |

### **EVALUATION BOARD SCHEMATIC**

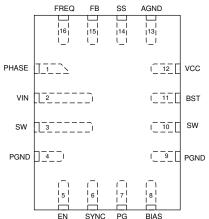

#### Package Reference

## **EV4432-L-00A BILL OF MATERIALS**

| Qty | Ref                                | Value | Description                      | Package             | Manufacturer | Part Number        |

|-----|------------------------------------|-------|----------------------------------|---------------------|--------------|--------------------|

| 2   | C1A, C1B                           | 10μF  | Ceramic Cap;<br>50V;X7R;1210     | 1210                | muRata       | GRM32ER71H106KA12L |

| 2   | C1C, C1D                           | 0.1µF | Ceramic Cap;<br>50V;X7R;0603     | 0603                | muRata       | GRM188R71H104KA93D |

| 2   | C2A, C2B                           | 22µF  | Ceramic Cap;<br>16V;X7R;1210     | 1210                | muRata       | GRM32ER71C226KEA8L |

| 1   | C3                                 | 4.7nF | Ceramic Cap;<br>50V;X7R;0603     | 0603                | muRata       | GRM188R71H472KA01D |

| 2   | C4, C7                             | 0.1µF | Ceramic Cap;<br>16V;X7R;0603     | 0603                | muRata       | GRM188R71C104KA01D |

| 1   | C5                                 | 10pF  | Ceramic Cap;<br>50V;C0G;0603     | 0603                | muRata       | GRM1885C1H100JA01  |

| 1   | C6                                 | 1µF   | Ceramic Cap;<br>16V;X7R;0603     | 0603                | muRata       | GRM188R71C105KA12D |

| 9   | CIN1-CIN6,<br>C2C, C2D,<br>C8      | NS    |                                  |                     |              |                    |

| 1   | FB1                                | NS    |                                  |                     |              |                    |

| 1   | D1                                 | NS    |                                  |                     |              |                    |

| 1   | L1                                 | NS    |                                  |                     |              |                    |

| 1   | L2                                 | 10µH  | Inductor,<br>27mOhm DCR,<br>7.6A | SMD                 | Coilcraft    | XAL6060-103MEB     |

| 1   | L3                                 | Short |                                  |                     |              |                    |

| 2   | R1, R6                             | 100k  | Film Res., 5%                    | 0603                | Yageo        | RC0603JR-07100KL   |

| 1   | R4                                 | 169k  | Film Res., 1%                    | 0603                | Yageo        | RC0603FR-07169KL   |

| 1   | R5                                 | 20    | Film Res., 1%                    | 0603                | Yageo        | RC0603FR-0720RL    |

| 1   | R7                                 | 1M    | Film Res., 1%                    | 0603                | Yageo        | RC0603FR-071ML     |

| 1   | R8                                 | 316k  | Film Res., 1%                    | 0603                | Yageo        | RC0603FR-07316KL   |

| 1   | R9                                 | 10    | Film Res., 5%                    | 0603                | Yageo        | RC0603JR-0710RL    |

| 2   | R2, R3                             | NS    |                                  |                     |              |                    |

| 1   | U1                                 |       | Step-Down<br>Regulator           | QFN-16<br>(3mmX4mm) | MPS          | MPQ4432GL          |

| 5   | VIN, VEMI,<br>GND,<br>VOUT,<br>GND |       | 2.0 Golden Pin                   |                     | HZ           |                    |

| 5   | EN, GND,<br>SYNC,<br>GND, PG       |       | 1.0 Golden Pin                   |                     | HZ           |                    |

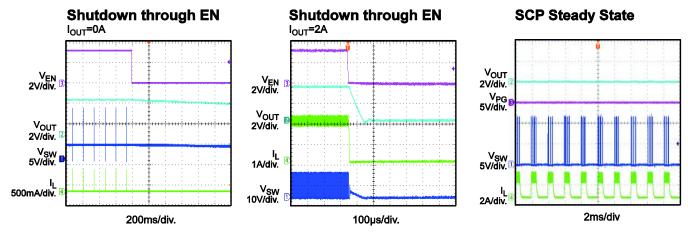

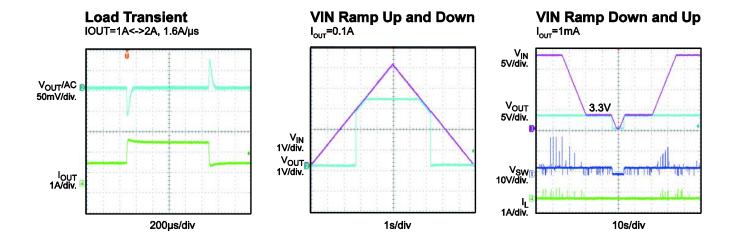

#### **EVB TEST RESULTS**

$V_{IN} = 12V$ ,  $V_{OUT} = 3.3V$ , L=10 $\mu$ H,  $F_{SW} = 500$ kHz, AAM mode,  $T_A = +25$ °C, unless otherwise noted.

### **EVB TEST RESULTS** (continued)

Performance waveforms are tested on the evaluation board.

$V_{IN} = 12V$ ,  $V_{OUT} = 3.3V$ ,  $L = 10\mu H$ ,  $F_{SW} = 500 kHz$ , AAM mode,  $T_A = +25^{\circ}C$ , unless otherwise noted.

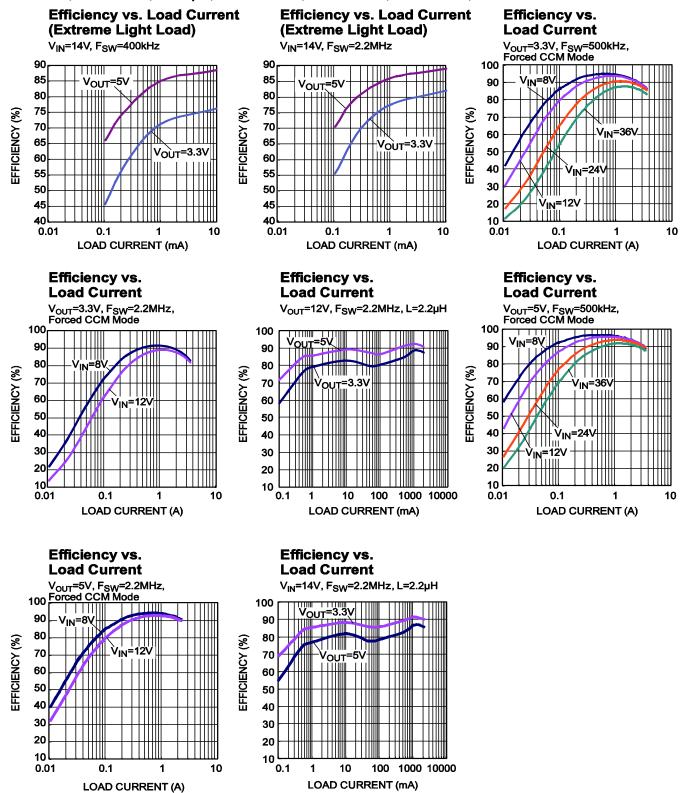

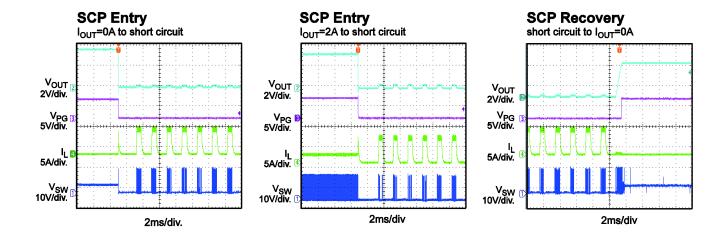

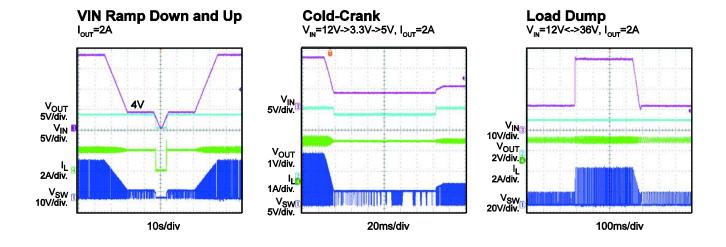

# **EVB TEST RESULTS** (continued)

Performance waveforms are tested on the evaluation board.

$V_{IN} = 12V$ ,  $V_{OUT} = 3.3V$ ,  $L = 10\mu H$ ,  $F_{SW} = 500 kHz$ , AAM mode,  $T_A = +25^{\circ}C$ , unless otherwise noted.

© 2023 MPS. All Rights Reserved.

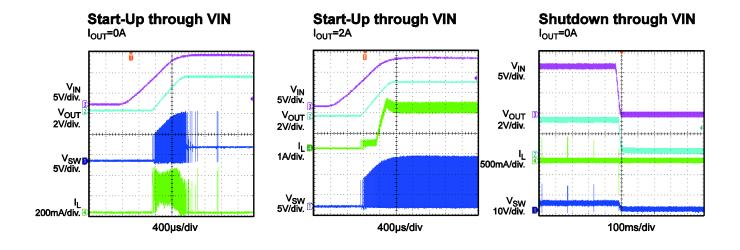

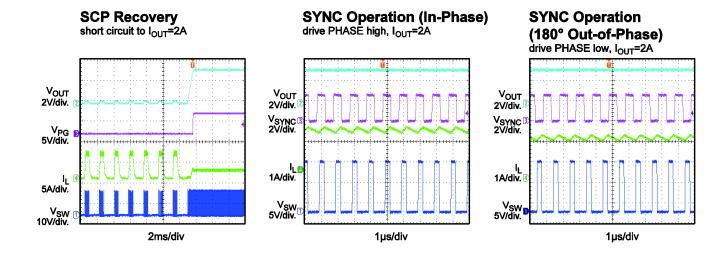

# **EVB TEST RESULTS** (continued)

Performance waveforms are tested on the evaluation board.

$V_{\text{IN}}$  = 12V,  $V_{\text{OUT}}$  =3.3V, L=10 $\mu$ H,  $F_{\text{SW}}$ =500kHz, AAM mode,  $T_{\text{A}}$  = +25°C, unless otherwise noted.

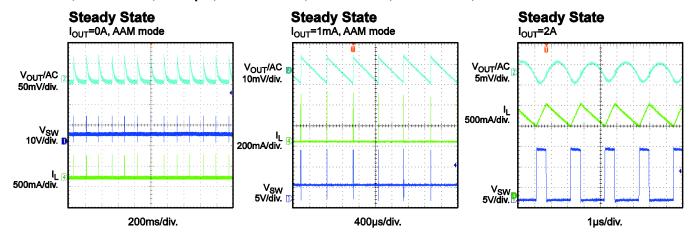

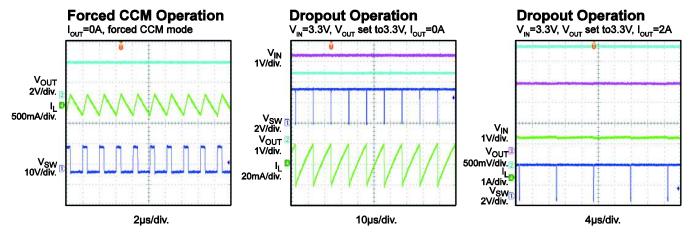

# **EVB TEST RESULTS** (continued)

Performance waveforms are tested on the evaluation board.

$V_{IN} = 12V$ ,  $V_{OUT} = 3.3V$ ,  $L = 10\mu H$ ,  $F_{SW} = 500 kHz$ , AAM mode,  $T_A = +25^{\circ}C$ , unless otherwise noted.

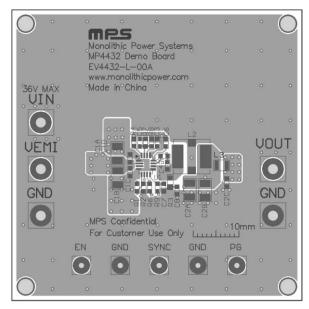

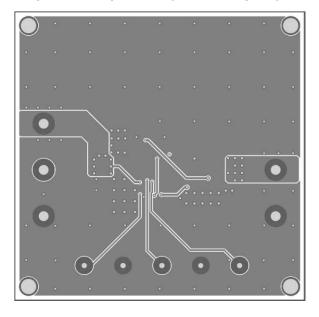

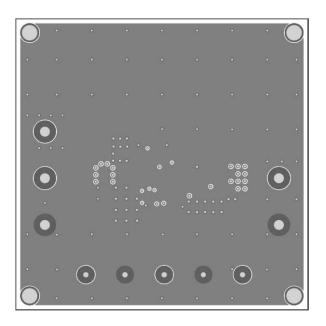

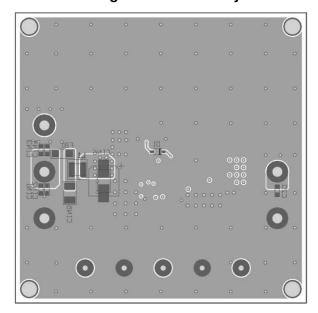

### PRINTED CIRCUIT BOARD LAYOUT

Figure 1—Top Silk Layer and Top Layer

Figure 3—Inner2 Layer

Figure 2—Inner1 Layer

Figure 4—Bottom Silk Layer and Bottom Layer

NOTICE: The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.