# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note: Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

#### 1.1 DESCRIPTION

The 7640 group, an enhanced family of CMOS 8-bit microcontrollers, offers high-speed operation, large internal-memory options, and a wide variety of standard peripherals. The series is code compatible with the 38000, 7200, 7400, and the 7500 series, and provides many performance enhancements to the instruction set.

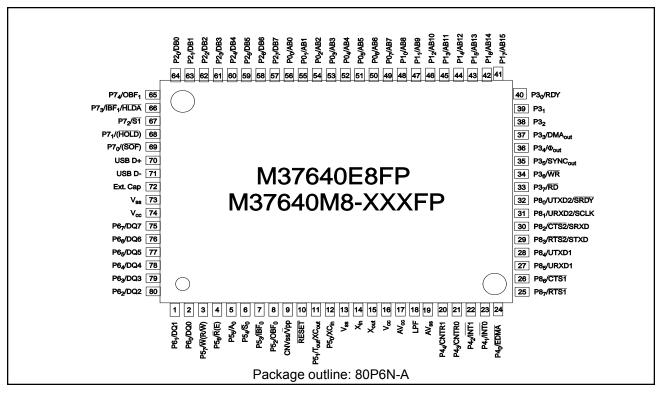

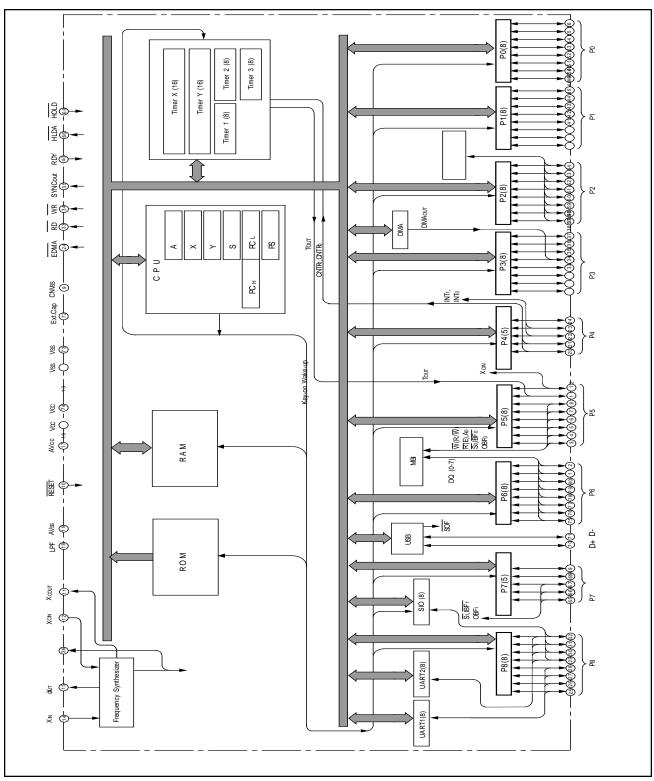

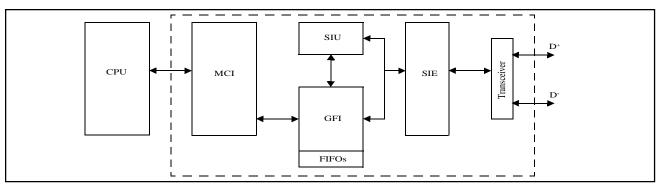

This device is a single chip PC peripheral microcontroller based on the Universal Serial Bus (USB) Version 1.1 specification. This device provides data exchange between a USB-equipped host computer and PC peripherals such as telephones, audio systems and digital cameras. See Figure 1.1 for a pin layout diagram. See Figure 1.2 for the functional block diagram.

# 1.2 MCU FEATURES

| Number of basic instructions         | 71              |

|--------------------------------------|-----------------|

| • Minimum instruction execution time | 83ns            |

| (1-cycle instruction                 | Φ = 12 MHz)     |

| •Clock frequency maximum             | f(Xin) = 24 MHz |

|                                      | f(XCin) = 5 MHz |

|                                      | Φ = 12 MHz      |

| • | METHOLY SIZE                   |                           |

|---|--------------------------------|---------------------------|

|   | ROM                            | 32KB on chip              |

|   | RAM                            |                           |

| • | Programmable I/O ports         |                           |

|   |                                |                           |

| • | Master Bus Interface (MBI)     | •                         |

|   |                                |                           |

| • | Serial I/O                     |                           |

|   | USB Function Control           |                           |

|   | Interrupts                     |                           |

|   |                                | 1 software,1 system       |

| • | DMAC2 cha                      |                           |

|   | (Max. 6M byte/sec. transfer sp | peed in burst mode)       |

| • | Timers                         |                           |

| • | Number of Full duplex UARTs    | available2                |

| • | Supply voltage                 | Vcc = 4.15~5.25V          |

| • | Operating temperature range.   | 20 to 85°C                |

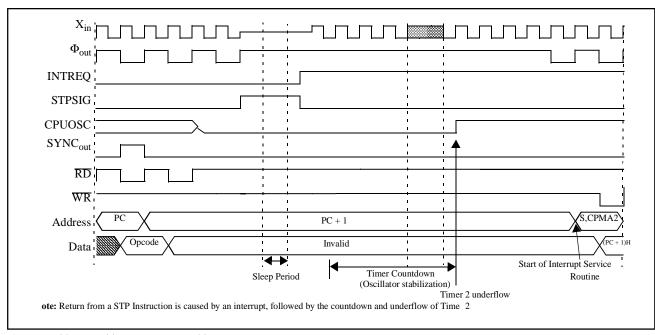

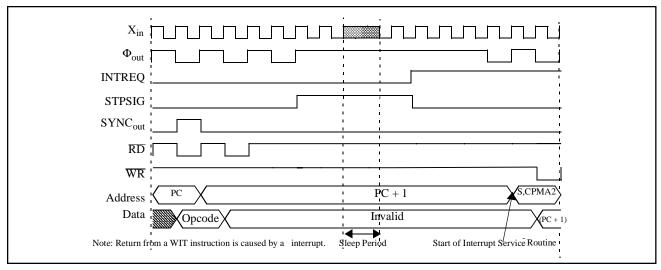

| • | Power-saving modes WIT         | (Idle), STP (Clocks halt) |

|   |                                |                           |

# 1.3 APPLICATIONS

Memory size

Cameras, games, musical instruments, modems scanners, and PC peripherals.

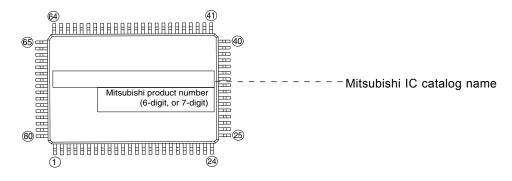

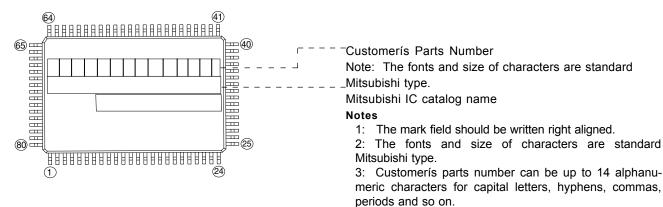

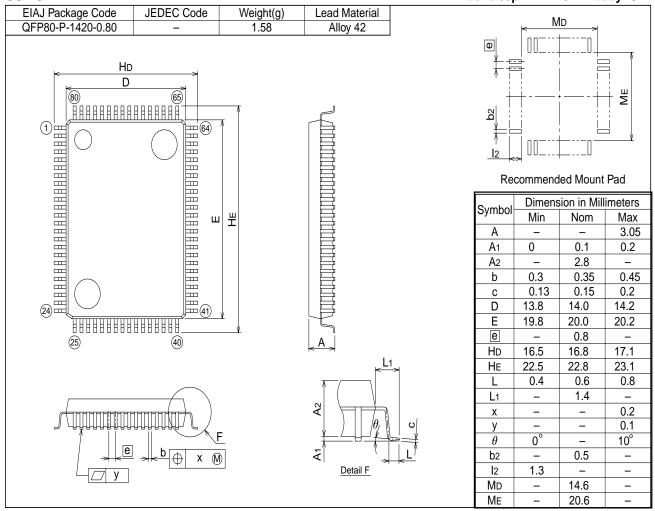

Fig. 1.1. Pin Layout

# 1.4 FUNCTIONAL BLOCK DIAGRAM

Fig. 1.2. Functional Block Diagram

# 1.5 PIN DESCRIPTION AND LAYOUT

Table 1.1. Pin Description and Layout

| NAME                                         | I/O                                                                                                   | DESCRIPTION                                                                                                                                     | PIN#          |  |  |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|--|

| P0 <sub>0</sub> /AB0~ P1 <sub>7</sub> /AB15  | /AB0~ P1 <sub>7</sub> /AB15 I/O CMOS I/O port (address bus). When the MCU is in memory expansion or   |                                                                                                                                                 |               |  |  |

|                                              |                                                                                                       | microprocessor mode, these pins function as the address bus.                                                                                    |               |  |  |

| P2 <sub>0</sub> /DB0 ~ P2 <sub>7</sub> /DB7  | I/O                                                                                                   | CMOS I/O port (data bus). When the MCU is in memory expansion or microprocessor                                                                 |               |  |  |

|                                              |                                                                                                       | mode, these pins function as the data bus. These pins may also be used to implement                                                             | 64-57         |  |  |

|                                              |                                                                                                       | the Key-on Wake up function.                                                                                                                    |               |  |  |

| P3 <sub>0</sub> /RDY                         | I/O                                                                                                   | CMOS I/O port (Ready). When the MCU is in memory expansion or microprocessor                                                                    | 40            |  |  |

|                                              |                                                                                                       | mode, this pin functions as RDY (hardware wait cycle control).                                                                                  |               |  |  |

| P3 <sub>1</sub>                              | I/O                                                                                                   | CMOS I/O port.                                                                                                                                  | 39            |  |  |

| P3 <sub>2</sub>                              | I/O                                                                                                   | CMOS I/O port.                                                                                                                                  | 38            |  |  |

| P3 <sub>3</sub> /DMA <sub>out</sub>          |                                                                                                       | CMOS I/O port (DMA <sub>out</sub> ). When the MCU is in memory expansion or microprocessor                                                      |               |  |  |

| - out                                        | I/O                                                                                                   | mode, this pin is set to a "1" during a DMA transfer.                                                                                           | 37            |  |  |

| $P3_4/\Phi_{Out}$                            | I/O                                                                                                   | CMOS I/O port. When the MCU is in memory expansion or microprocessor mode, this pin becomes $\Phi_{\hbox{\scriptsize Out}}$ pin.                | 36            |  |  |

| P3 <sub>5</sub> /SYNC <sub>out</sub>         | I/O                                                                                                   | CMOS I/O port (SYNC <sub>out</sub> ). When the MCU is in memory expansion or microprocessor mode, this pin becomes the SYNC <sub>out</sub> pin. | 35            |  |  |

|                                              |                                                                                                       | CMOS I/O port. (WR output). When the MCU is in memory expansion or microprocessor                                                               |               |  |  |

| P3 <sub>6</sub> /WR                          | I/O                                                                                                   | mode, this pin becomes WR.                                                                                                                      | 34            |  |  |

|                                              |                                                                                                       | CMOS I/O port. (RD output). When the MCU is in memory expansion or microprocessor                                                               |               |  |  |

| P37/RD                                       | I/O                                                                                                   | mode, this pin becomes RD.                                                                                                                      | 33            |  |  |

| P4 <sub>0</sub> /EDMA                        | 4 <sub>0</sub> /EDMA I/O CMOS I/O port (EDMA: Expanded Data Memory Access). When the MCU is in memory |                                                                                                                                                 |               |  |  |

|                                              |                                                                                                       | expansion or microprocessor mode, this pin can become the EDMA pin.                                                                             |               |  |  |

| P4 <sub>1</sub> /INT0~ P4 <sub>2</sub> /INT1 | I/O                                                                                                   | CMOS I/O port or external interrupt ports INT0 and INT1. These external interrupts can                                                          | 23-22         |  |  |

|                                              |                                                                                                       | be configured to be active high or low.                                                                                                         |               |  |  |

|                                              | I/O                                                                                                   | CMOS I/O port or Timer X input pin for pulse width measurement mode and event                                                                   |               |  |  |

| P4 <sub>3</sub> /CNTR0                       |                                                                                                       | counter mode or Timer X output pin for pulse output mode. This pin can also be used as                                                          | 21            |  |  |

|                                              |                                                                                                       | an external interrupt when Timer X is not in output mode. The interrupt polarity is                                                             |               |  |  |

|                                              |                                                                                                       | selected in the Timer X mode register.                                                                                                          |               |  |  |

|                                              |                                                                                                       | CMOS I/O port or Timer Y input pin for pulse period measurement mode, pulse H-L                                                                 |               |  |  |

| P4₄/CNTR1                                    | I/O                                                                                                   | measurement mode and event counter mode or Timer Y output pin for pulse output                                                                  | 20            |  |  |

|                                              |                                                                                                       | mode. This pin can also be used as an external interrupt when Timer Y is not in output                                                          |               |  |  |

|                                              |                                                                                                       | mode. The interrupt polarity is selected in the Timer Y mode register.                                                                          |               |  |  |

| P5 <sub>0</sub> /XC <sub>in</sub>            | I/O                                                                                                   | CMOS I/O port or XC <sub>in</sub> .                                                                                                             | 12            |  |  |

| P5₁/Tout/XC <sub>out</sub>                   | I/O                                                                                                   | CMOS I/O port or Timer half pulse output pin (can be configured initially high or initially                                                     | 11            |  |  |

|                                              |                                                                                                       | low), or XCout.                                                                                                                                 | _             |  |  |

| P5 <sub>2</sub> /OBF <sub>0</sub>            | I/O                                                                                                   | CMOS I/O port or OBF <sub>0</sub> output to master CPU for data bus buffer 0.                                                                   | 8             |  |  |

| P5 <sub>3</sub> /IBF <sub>0</sub>            | I/O                                                                                                   | CMOS I/O port or $\overline{\text{IBF}}_0$ output to master CPU for data bus buffer 0.                                                          | 7             |  |  |

| P5 <sub>4</sub> /S 0                         | I/O                                                                                                   | CMOS I/O port or $\overline{S}_0$ input from master CPU for data bus buffer 0.                                                                  | 6             |  |  |

| P5 <sub>5</sub> /A <sub>0</sub>              | I/O                                                                                                   | CMOS I/O port or A₀ input from master CPU.                                                                                                      | 5             |  |  |

| P5 <sub>6</sub> /R(E)                        | I/O                                                                                                   | CMOS I/O port or $\overline{R(E)}$ input from master CPU.                                                                                       | 4             |  |  |

| P5 <sub>7</sub> /W(R/W)                      | I/O                                                                                                   | CMOS I/O port or W(R/W) input from master CPU.                                                                                                  | 3             |  |  |

| P6 <sub>0</sub> /DQ0~ P6 <sub>7</sub> /DQ7   | I/O                                                                                                   | CMOS I/O port or master CPU data bus.                                                                                                           | 2-1,<br>80-75 |  |  |

| USB D-                                       | I/O                                                                                                   | USB D- voltage line interface, a series resistor of 33 $\Omega$ should be connected to this pin.                                                | 71            |  |  |

| USB D+                                       | I/O                                                                                                   | ·                                                                                                                                               |               |  |  |

| P7 <sub>0</sub> /SOF                         | I/O                                                                                                   | CMOS I/O port or USB start of frame pulse output, an 80 ns pulse outputs on this pin for every USB frame.                                       |               |  |  |

| P7₁/HOLD                                     | I/O                                                                                                   | CMOS I/O port or HOLD pin.                                                                                                                      | 68            |  |  |

| P7 <sub>2</sub> /S <sub>1</sub>              | I/O                                                                                                   | CMOS I/O port or $\overline{S_1}$ input from master CPU for data bus buffer 1.                                                                  | 67            |  |  |

| 1 12/01                                      | 1/0                                                                                                   | Tomoo ii o port or o <sub>1</sub> input from master or o for data bus buller 1.                                                                 | 07            |  |  |

# SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

| NAME                                | I/O | DESCRIPTION                                                                                               | PIN#  |

|-------------------------------------|-----|-----------------------------------------------------------------------------------------------------------|-------|

|                                     |     | CMOS I/O port or $\overline{IBF}_1$ output to master CPU for data bus buffer 1, or $\overline{HLDA}$ pin. |       |

| P7₃/IBF₁/HLDA                       | I/O | IBF₁ and HLDA are mutually exclusive. IBF₁ has priority over HLDA                                         | 66    |

| P7 <sub>4</sub> /OBF <sub>1</sub>   | I/O | CMOS I/O port or OBF <sub>1</sub> output to master CPU for data bus buffer 1.                             | 65    |

|                                     |     | CMOS I/O port or UART2 pin UTXD2 or SIO pin SRDY. UART2 and SIO are                                       |       |

| P8₀/UTXD2/SRDY                      | I/O | mutually exclusive, UART2 has priority over SIO.                                                          | 32    |

|                                     |     | CMOS I/O port or UART2 pin URXD2 or SIO pin SCLK. UART2 and SIO are                                       |       |

| P8 <sub>1</sub> /URXD2/SCLK         | I/O | mutually exclusive, UART2 has priority over SIO.                                                          | 31    |

|                                     |     | CMOS I/O port or UART2 pin CTS2 or SIO pin SRXD. UART2 and SIO are                                        |       |

| P8₂/CTS2/SRXD                       | I/O | mutually exclusive, UART2 has priority over SIO.                                                          | 30    |

|                                     |     | CMOS I/O port or UART2 pin RTS2 or SIO pin STXD. UART2 and SIO are                                        |       |

| P8₃/RTS2/STXD                       | I/O | mutually exclusive, UART2 has priority over SIO.                                                          | 29    |

| P8₄/UTXD1                           | I/O | CMOS I/O port or UART1 pin UTXD1.                                                                         | 28    |

| P8₅/URXD1                           | I/O | CMOS I/O port or UART1 pin URXD1.                                                                         | 27    |

| P8 <sub>6</sub> /CTS1               | I/O | CMOS I/O port or UART1 pin CTS1.                                                                          | 26    |

| P8 <sub>7</sub> /RTS1               | I/O | CMOS I/O port or UART1 pin RTS1.                                                                          | 25    |

| AV <sub>CC</sub> , AV <sub>SS</sub> | 1   | Power supply inputs for analog circuitry AVcc = 4.15~ 5.25V, AVss = 0V                                    | 17,19 |

|                                     |     | Controls the processor mode of the chip. Normally connected to V <sub>SS</sub> or V <sub>CC</sub> .       |       |

| $CNV_{SS}/\overline{V}_{pp}$        | 1   | When the MCU is in EPROM program mode, this pin supplies the programming                                  | 9     |

|                                     |     | voltage to the EPROM.                                                                                     |       |

| V <sub>CC</sub> ,V <sub>SS</sub>    | 1   | Power supply inputs: $V_{CC} = 4.15 \sim 5.25 \text{V}, V_{SS} = 0 \text{V}$                              |       |

| 00* 00                              |     |                                                                                                           | 13/73 |

|                                     |     | To enter the reset state, this pin must be kept 'L' for more that 2 $\mu$ s (20 $\Phi$ cycles             |       |

| RESET                               | I   | under normal V <sub>CC</sub> conditions). If the crystal or ceramic resonator requires more               | 10    |

|                                     |     | time to stabilize, extend this 'L' level time appropriately.                                              |       |

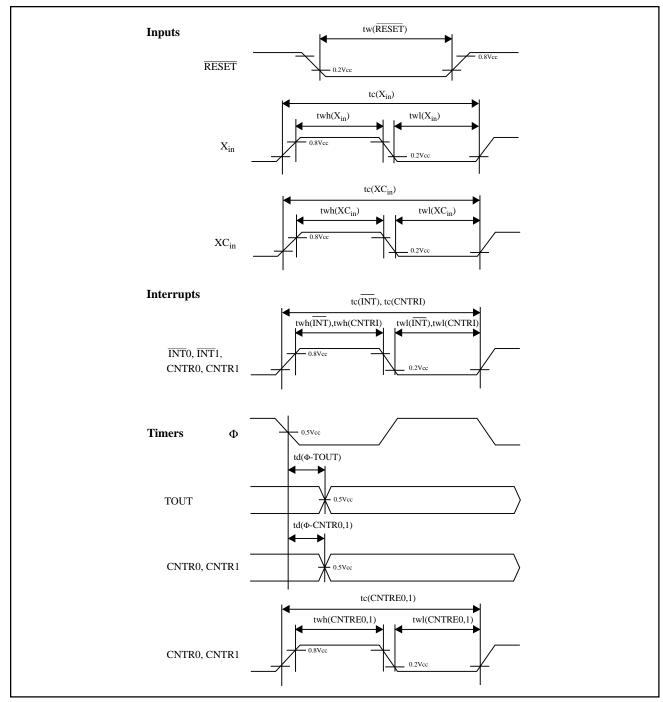

| XC <sub>in</sub>                    | - 1 | An external ceramic or quartz crystal oscillator can be connected between the                             | 12    |

| XC <sub>out</sub>                   | 0   | XC <sub>in</sub> and XC <sub>out</sub> pins. If an external clock source is used, connect the clock       | 11    |

| 7.00ut                              |     | source to the XC <sub>in</sub> pin and leave the XC <sub>out</sub> pin open.                              |       |

|                                     |     | Input and output signals to and from the internal clock generation circuit.                               |       |

| X <sub>in</sub>                     | I   | Connect a ceramic resonator or quartz crystal between X <sub>in</sub> and X <sub>out</sub> pins to set    | 14    |

| X <sub>out</sub>                    | 0   | the oscillation frequency. If an external clock is used, connect the clock source                         | 15    |

|                                     | _   | to the X <sub>in</sub> pin and leave the X <sub>out</sub> pin open.                                       |       |

| LPF                                 | 0   | Loop filter for the frequency synthesizer.                                                                | 18    |

|                                     |     | An external capacitor (Ext. Cap) pin. When the USB transceiver voltage                                    |       |

| Ext. Cap                            | - 1 | converter is used, a 2µf or larger capacitor should connect between this pin and                          | 72    |

|                                     |     | Vss to ensure proper operation of the USB line driver. The voltage converter is                           |       |

|                                     |     | enabled by setting bit 4 of the USB control register (0013 <sub>16</sub> ) to a "1".                      |       |

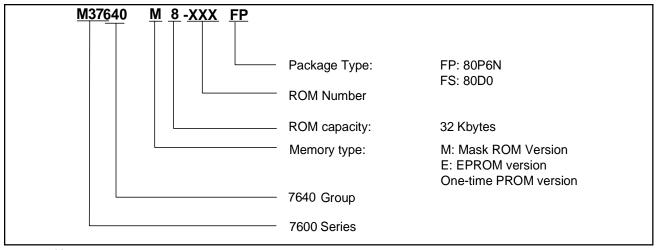

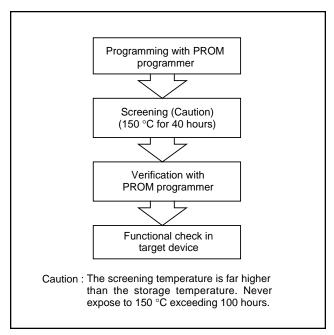

# 1.6 PART NUMBERING

Fig. 1.3. Type no., memory size, and package

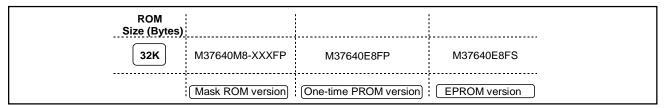

# 1.7 ROM EXPANSION

Table 1.2. ROM Expansion

# 1.8 CURRENTLY SUPPORTED PRODUCTS

Table 1.3. Currently Supported Products

| Type No.       | ROM capacity | RAM capacity | Package<br>type | Remarks               |

|----------------|--------------|--------------|-----------------|-----------------------|

| M37640M8-XXXFP | 32K bytes    | 1 K bytes    | 80P6N-A         | Mask ROM version      |

| M37640E8FP     | 32K bytes    | 1 K bytes    | 80P6N-A         | One-time PROM version |

| M37640E8FS     | 32K bytes    | 1 K bytes    | 80D0            | EPROM version         |

# 1.9 CENTRAL PROCESSING UNIT

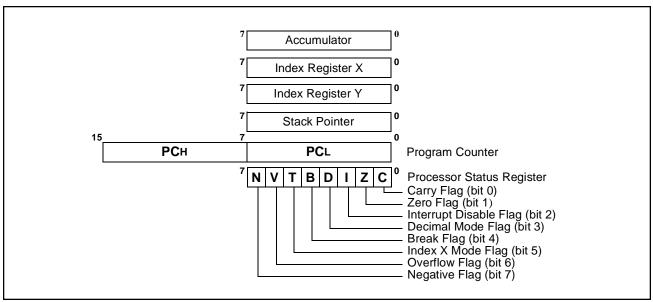

The central processing unit (CPU) has six registers:

- · Accumulator (A)

- Index Register X (X)

- · Index Register Y (Y)

- · Stack Pointer (S)

- Processor Status Register (PS)

- Program Counter (PC)

#### 1.9.1 Register Structure

Five of the CPU registers are 8-bit registers. These are the Accumulator (A), Index register X (X), Index Register Y (Y), Stack pointer (S), and the Processor Status register (PS) as shown in Figure 1.4.

The Program counter (PC) is a 16-bit register consisting of two 8-bit registers (PCH and PCL).

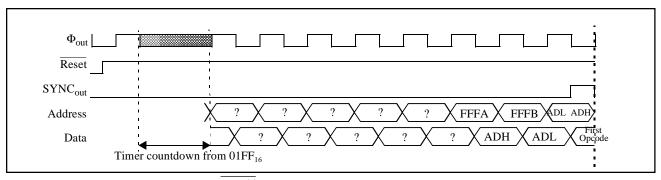

After a hardware reset, bit 2 (I Flag) of the PS is set high and the values at the address FFFA16 and FFFB16 are stored in the PC, but the values of the other bits of the PS and other registers are undefined. Initialization of the undefined registers may be necessary for some programs.

Fig. 1.4. Register Structure

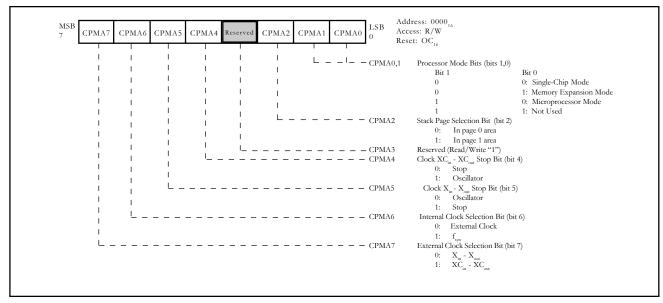

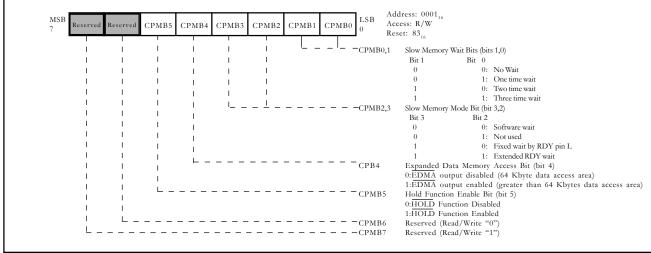

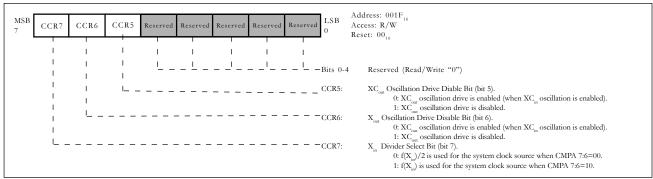

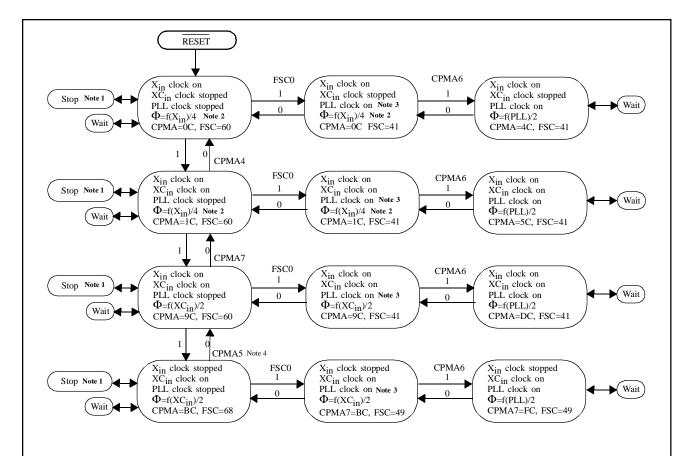

# 1.10 CPU MODE REGISTERS

This device has two CPU mode registers:

- CPU Mode Register A (CPMA)

- CPU Mode Register B (CPMB)

These registers control the processor mode, clock, slow memory wait and other CPU functions. The bit representation of each register is described in Figure 1.5 and Figure 1.6.

Fig. 1.5. CPU Mode Register A (CPMA)

Fig.1.6. CPU Mode Register B (CPMB)

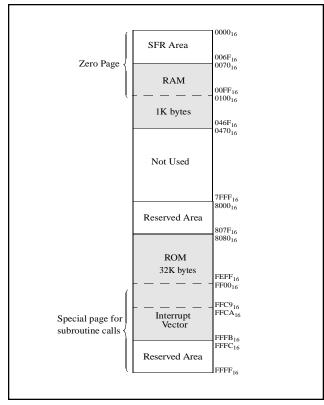

#### 1.11 MEMORY MAP

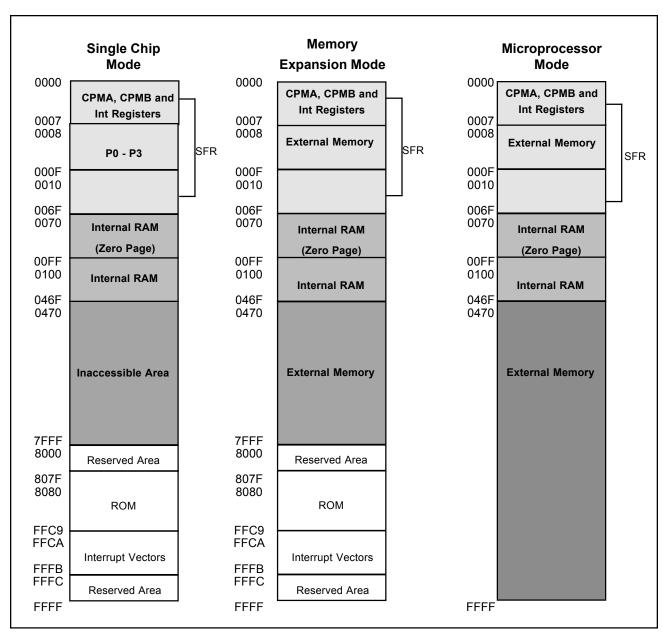

The first 112 bytes of memory from 000016 to 006F16 is the special function register (SFR) area and contains the CPU mode registers, interrupt registers, and other registers to control peripheral functions (see Figure 1.7).

Fig. 1.7. Memory Map

The general purpose RAM resides from 007016 to 046F16. When the MCU is in memory expansion or microprocessor mode and external memory is overlaid on the internal RAM, the CPU reads data from the internal RAM. However, the CPU writes data in both the internal and external memory. The area from 047016 to 7FFF16 is not used in single-chip mode, but can be mapped for an external memory device when the MCU is in memory expansion or microprocessor mode.

The area from 800016 to 807F16 and from FFFC16 to FFFF16 are factory reserved areas. Mitsubishi uses it for test and evaluation purposes. The user can not use this area in single-chip or memory expansion modes.

The user 32K byte ROM resides from 808016 to FFFB16. When the MCU is in microprocessor mode, the CPU accesses an external area rather than accessing the internal ROM.

# 1.11.1 Special page

The 256 bytes from address FF0016 to FFFF16 are called the special page area. In this area special page addressing can be used to specify memory addresses. This dedicated special page addressing mode enables access to this area with fewer instruction cycles. Frequently used subroutines are normally stored in this area.

#### 1.12 PROCESSOR MODES

The operation modes are described below. The memory maps for the first three modes are shown in Figure 1.8. Single chip mode is normally entered after reset. However, if the MCU has a CNVss pin, holding this pin high will cause microprocessor mode to be entered after re-

set. After the reset sequence has completed, the mode can be changed with software by modifying the value of bits 0 and 1 of CPMA. However, while CNVss is high, bit 1 of CPMA is "1" and cannot be changed.

Fig. 1.8. Operation Modes Memory Maps

MITSUBISHI MICROCOMPUTERS

# 1.12.1 Single Chip

In this mode, all ports take on their primary function and all internal memory is accessible. Those areas that are not in internal memory are not accessible. Also, slow memory wait and EDMA are disabled in this mode.

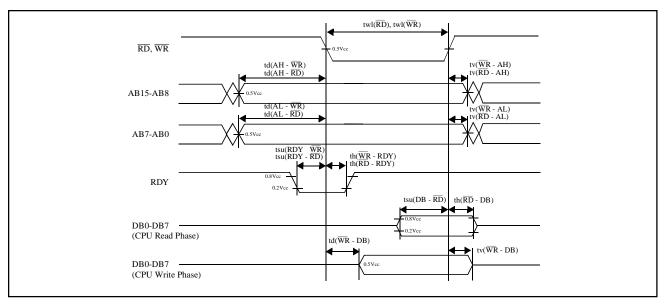

# 1.12.2 Memory Expansion

In this mode, Ports 0 and 1 output the address bus (AB0-AB15), port 2 acts as the data bus input and output, and port 3 bits 7 to 3 output  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$ ,  $\overline{\text{SYNC}}_{\text{out}}$ ,  $\Phi_{\text{out}}$ , and DMA $_{\text{out}}$ , respectively. All memory areas that are not internal memory or SFR area are accessed externally. Because ports 0 to 3 lose their normal function in this mode, the address area for the ports and their direction registers are treated as external memory. In this mode, slow memory wait and EDMA can be enabled.

# 1.12.3 Microprocessor

This mode is primarily the same as memory expansion mode. The difference is that the internal ROM/EPROM area can not be accessed and is instead treated as external memory. Slow memory wait and EDMA can be enabled in this mode.

# 1.12.4 Slow Memory Wait

The wait function is used when interfacing with external memories that are too slow to operate at the normal read/write speed of the MCU. When this is the case, a wait can be used to extend the read/write cycle. Three different wait modes are supported; software wait, RDY wait, and extended RDY wait. The appropriate mode is chosen by the setting of bits 0 to 3 of CPMB. The wait function is disabled for internal memory and is valid only for memory expansion and microprocessor modes.

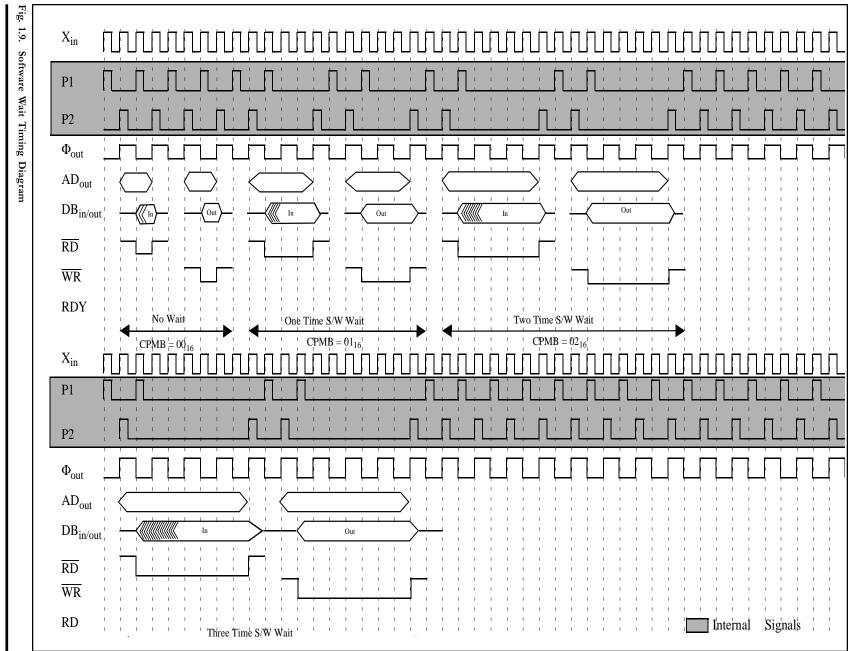

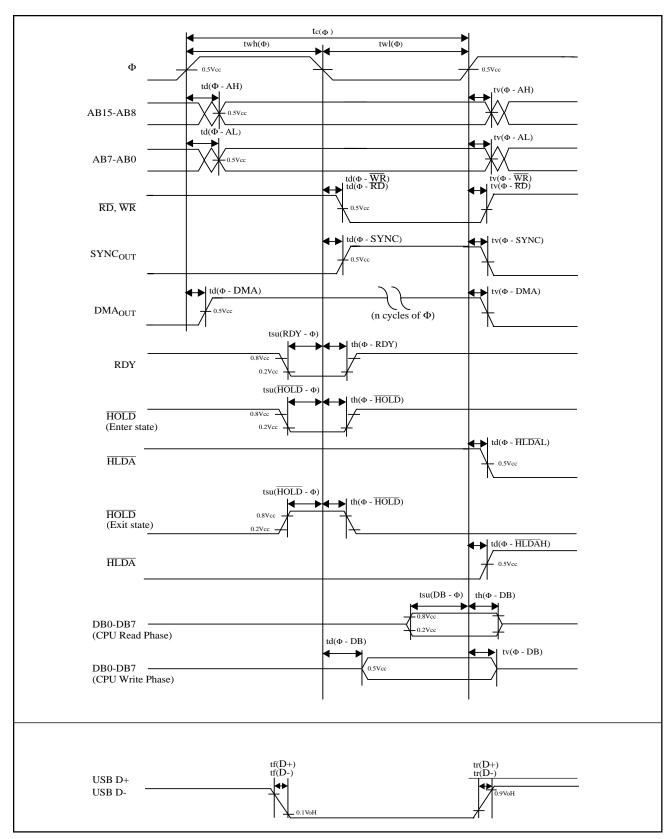

Software wait is used to extend the read/write cycle by one, two, or three cycles of  $\Phi$ . The cycle number is determined by the value of bits 0 and 1 of CPMB. When software wait is selected, the value on the RDY pin is ignored. The timing for software wait is shown in Figure 1.9.

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

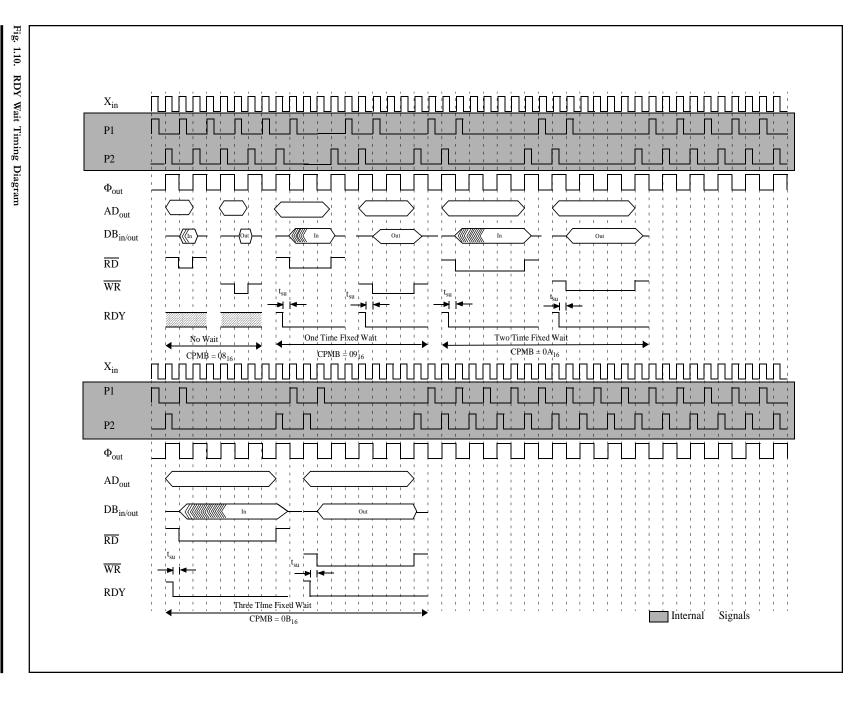

RDY wait is also used to extend the read/write cycle by one, two, or three cycles  $\Phi.$  In this case, the read/write cycle is extended if the RDY pin is low when  $\Phi_{\text{out}}$  goes low (taking into account setup and hold times) at the beginning of the read/write cycle. The extension time is fixed by the value of bits 0 and 1 of CPMB and does not depend on the state of the RDY pin once the read/write cycle has begun. If the RDY pin is high when  $\Phi_{\text{out}}$  goes low at the beginning of the read/write cycle, the read/write cycle is not extended. The timing for RDY wait is shown in Figure 1.10.

The extended RDY wait mode is used to extend the read/write cycle by a variable number of cycles of  $\Phi.$  The exact number is dependent on the state of the RDY pin and the value of bits 0 and 1 of CPMB. In this mode, the read/write cycle is extended if the RDY pin is low when  $\Phi_{\text{out}}$  goes low at the beginning of the read/write cycle. The read/write cycle continues to be extended until the RDY pin is high when  $\Phi_{\text{out}}$  goes low, at which point the read/write cycle completes in one, two, or three cycles of  $\Phi$  (with respect to the previous low to high transition of  $\Phi$ ), dependent on the value in bits 0 and 1 of CPMB. If the RDY pin is high when  $\Phi_{\text{out}}$  goes low at the beginning of the read/write cycle, the read/write cycle is not extended. The timing for this mode is shown in Figure 1.11.

The wait function can only be enabled for external memory access in microprocessor or memory expansion modes. However, the wait function can not be enabled for accesses to addresses  $0008_{16}$  to  $000F_{16}$  (Port 0 through Port 3 registers) in these modes, even though the locations are mapped as external memory.

# SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

#### 1.12.5 Hold Function

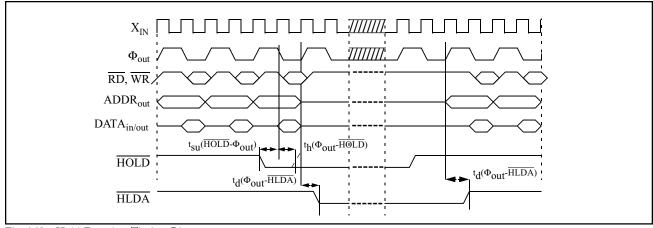

The hold function is used when the MCU is put in a system where more than one device will need control of the external address and data buses. Two signals are used to implement this function, HOLD (P71) and HLDA (P73). HOLD is an input to the MCU and is brought low when an external device wants the MCU to relinquish the address and data buses. HLDA is an output from the MCU that signals when the MCU has relinquished the buses. When this is the case, the MCU tri-state ports 0 and 1 (address bus) and port 2 (data bus), and holds port P37 (RD) and port P36 (WR) high. Ports P37 and P36 are held high to prevent any external device that is enabled by RD or WR from being falsely activated. The clocks to the CPU are stopped, but the peripheral clocks and port P34  $(\Phi out)$  continue to oscillate. HOLD is brought high to allow the MCU to regain the address and data buses. When this occurs, HLDA will go high and ports P1, P2, P37 and P36 will begin to drive the external buses again. The timing for the hold function is shown in Figure 1.12. The hold function is only valid for memory expansion and microprocessor modes. Bit 5 of CPMB is used to enable the hold function. HLDA will loose its function when the IBF1 pin functionality is used.

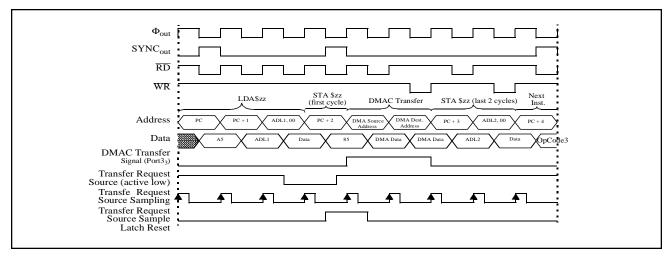

# 1.12.6 Expanded Data Memory Access

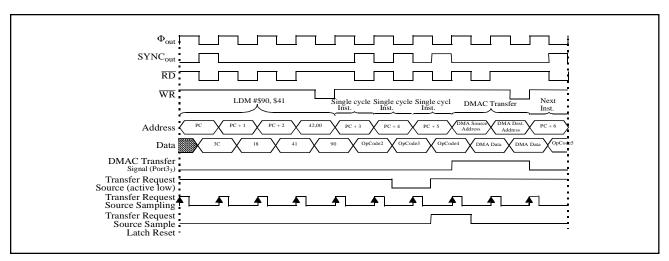

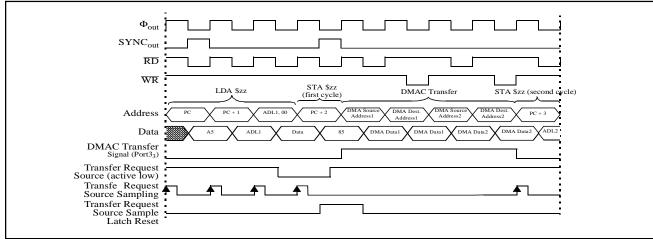

The Expanded Data Memory Access (EDMA) mode feature allows the user to access a greater than 64 Kbyte data area for instructions LDA (IndY) with T="0" and T="1", and STA (IndY). Bit 4 of CPMB is used to enable/disable the EDMA function. If bit 4 of CPMB equals "1", then during the data read/write cycle of instructions LDA (IndY) and STA (IndY) Port 40 (EDMA) is driven low. The EDMA signal output can be used by an external decoder to indicate when the read/write is to a different 64 Kbyte bank. The actual determination of which bank to access can be done by using a few bits of a port to represent the extended addresses above AB15. For example, if four banks are accessed, then two bits are needed to uniquely identify each bank. Two port bits can be used for this, one representing AB16 and the other AB17. The instruction sequences for STA (IndY) and LDA (IndY) are shown in Figure 1.13 and Figure 1.14.

Fig. 1.12. Hold Function Timing Diagram

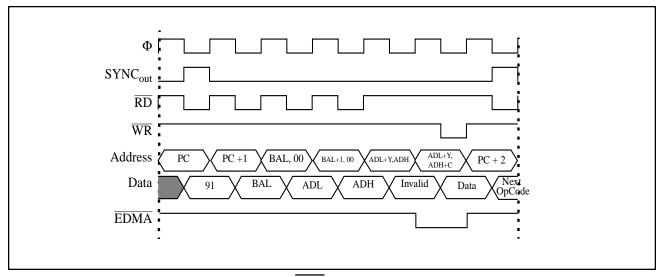

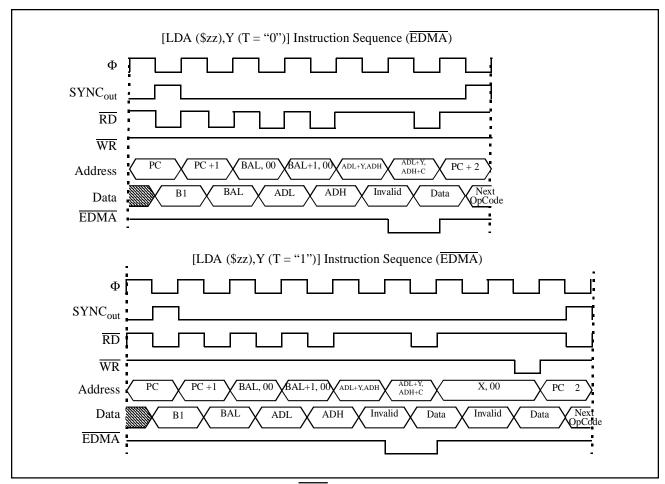

Fig. 1.13. Instruction sequences for STA (\$zz) IndY with EDMA Enable

Fig. 1.14. Instruction sequences for LDA (\$zz) IndY with EDMA Enable

# 1.13 SPECIAL FUNCTION REGISTERS

The special function registers (SFR) are used for controlling the functional blocks, such as I/O ports, Timers, UART, and so forth (see Table 1.4). The reserved addresses should not be read or written to.

Table 1.4. SFR Addresses

| Addr               | Description                           | Acronym and    | Addr               | Description                              | Acronym and                   |

|--------------------|---------------------------------------|----------------|--------------------|------------------------------------------|-------------------------------|

|                    |                                       | Value at Reset |                    |                                          | Value at Reset                |

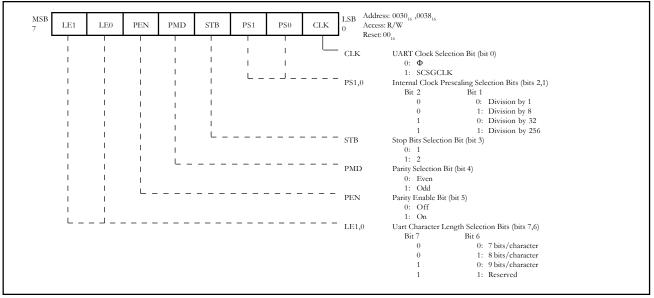

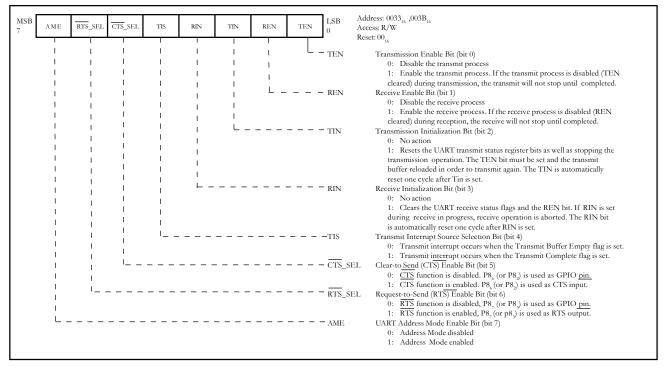

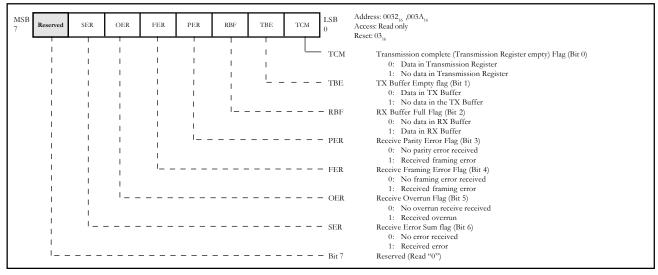

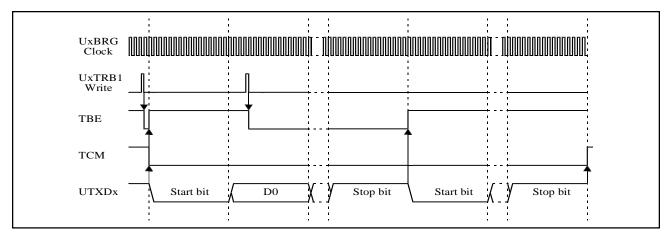

| 000016             | CPU Mode Register A                   | CPMA=0C        | 003816             | UART2 Mode Register                      | U2MOD=00                      |

| 000116             | CPU Mode Register B                   | CPMB=83        | 003916             | UART2 Baud Rate Generator                | U2BRG=XX                      |

| 000216             | Interrupt Request Register A          | IREQA=00       | 003A <sub>16</sub> | UART2 Status Register                    | U2STS=03                      |

| 000316             | Interrupt Request Register B          | IREQB=00       | 003B <sub>16</sub> | UART2 Control Register                   | U2CON=00                      |

| 000416             | Interrupt Request Register C          | IREQC=00       | 003C <sub>16</sub> | UART2 Transmit/Receiver Buffer 1         | U2TRB1=XX                     |

| 000516             | Interrupt Control Register A          | ICONA=00       | 003D <sub>16</sub> | UART2 Transmit/Receiver Buffer 2         | U2TRB2=XX                     |

| 000616             | Interrupt Control Register B          | ICONB=00       | 003E <sub>16</sub> | UART2 RTS Control Register               | U2RTSC=80                     |

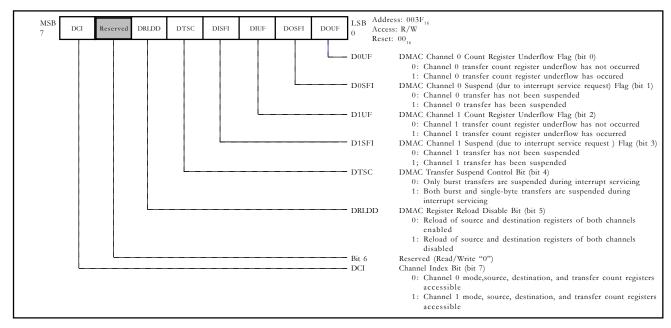

| 0007 <sub>16</sub> | Interrupt Control Register C          | ICONC=00       | 003F <sub>16</sub> | DMAC Index and Status Register           | DMAIS=00                      |

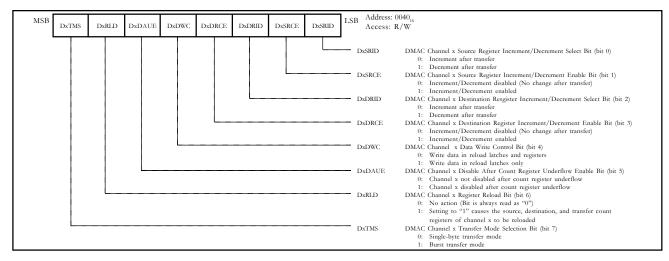

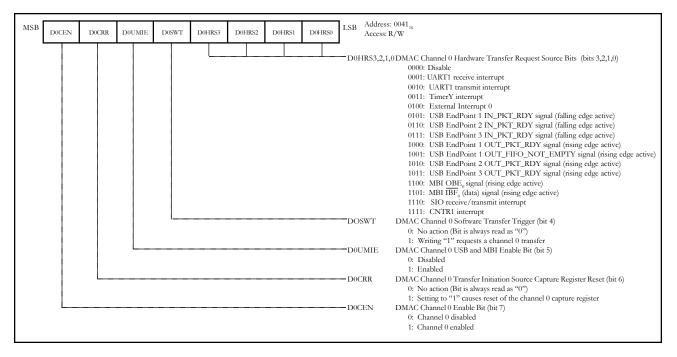

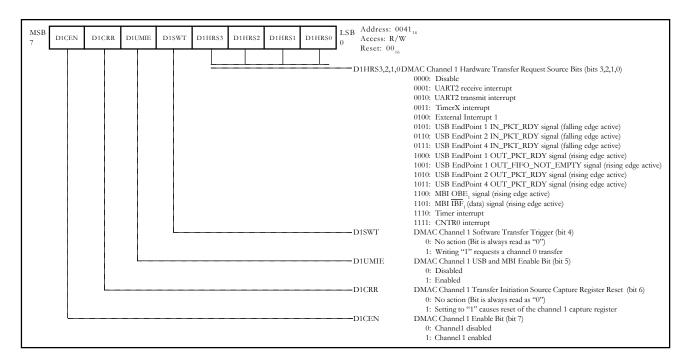

| 000816             | Port P0                               | P0=00          | 004016             | DMAC Channel x Mode Register 1           | DMAxM1=00                     |

| 000916             | Port P0 Direction Register            | P0D=00         | 004116             | DMAC Channel x Mode Register 2           | DMAxM2=00                     |

| 000A <sub>16</sub> | Port P1                               | P1=00          | 004216             | DMAC Channel x Source Register Low       | DMAxSL=00                     |

| 000B <sub>16</sub> | Port P1 Direction Register            | P1D=00         | 004316             | DMAC Channel x Source Register High      | DMAxSH=00                     |

| 000C <sub>16</sub> | Port P2                               | P2=00          | 0044 <sub>16</sub> | DMAC Channel x Destination Register Low  | DMAxDL=00                     |

| 000D <sub>16</sub> | Port P2 Direction Register            | P2D=00         | 004516             | DMAC Channel x Destination Register High | DMAxDH=00                     |

| 000E <sub>16</sub> | Port P3                               | P3=00          | 004616             | DMAC Channel x Count Register Low        | DMAxCL=00                     |

| 000F <sub>16</sub> | Port P3 Direction Register            | P3D=00         | 0047 <sub>16</sub> | DMAC Channel x Count Register High       | DMAxCH=00                     |

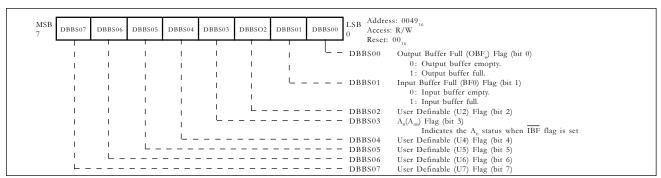

| 001016             | Port Control Register                 | PTC=00         | 004816             | Data Bus Buffer register 0               | DBB0=00                       |

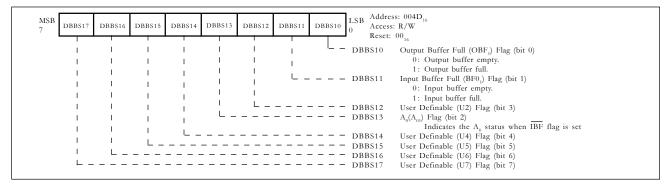

| 001116             | Interrupt Polarity Selection Register | IPOL=00        | 004916             | Data Bus Buffer status register 0        | DBBS0=00                      |

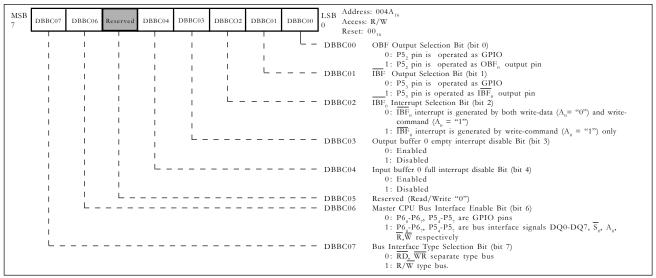

| 001216             | Port P2 pull-up Control Register      | PUP2=00        | 004A <sub>16</sub> | Data Bus Buffer Control Register 0       | DBBC0=00                      |

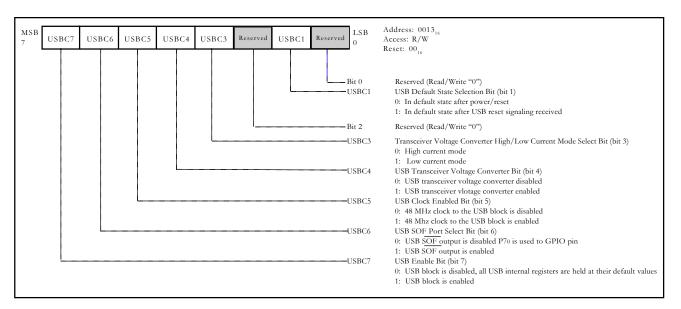

| 0013 <sub>16</sub> | USB Control Register                  | USBC=00        | 004B <sub>16</sub> | Reserved                                 |                               |

| 001416             | Port P6                               | P6=00          | 004C <sub>16</sub> | Data Bus Buffer register 1               | DBB1=00                       |

| 001516             | Port P6 Direction Register            | P6D=00         | 004D <sub>16</sub> | Data Bus Buffer Status Register 1        | DBBS1=00                      |

| 0016 <sub>16</sub> | Port P5                               | P5=00          | 004E <sub>16</sub> | Data Bus Buffer Control Register 1       | DBBC1=00                      |

| 0017 <sub>16</sub> | Port P5 Direction Register            | P5D=00         | 004F <sub>16</sub> | Reserved                                 |                               |

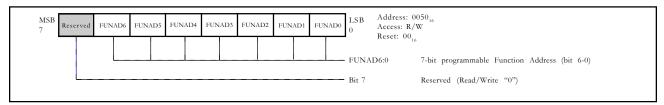

| 0018 <sub>16</sub> | Port P4                               | P4=00          | 005016             | USB Address Register                     | USBA=00                       |

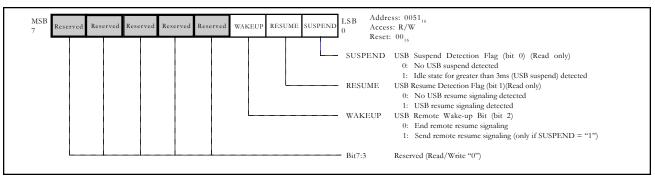

| 0019 <sub>16</sub> | Port P4 Direction Register            | P4D=00         | 005116             | USB Power Management Register            | USBPM=00                      |

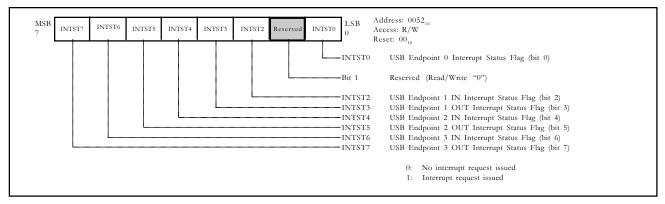

| 001A <sub>16</sub> | Port P7                               | P7=00          | 005216             | USB Interrupt Status Register 1          | USBIS1=00                     |

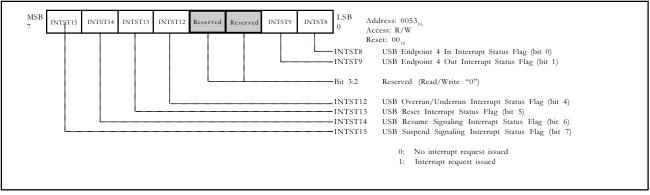

| 001B <sub>16</sub> | Port P7 Direction Register            | P7D=00         | 005316             | USB Interrupt Status Register 2          | USBIS2=00                     |

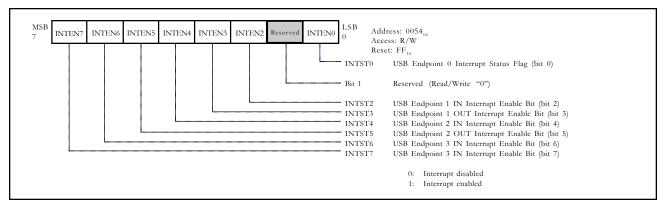

| 001C <sub>16</sub> | Port P8                               | P8=00          | 005416             | USB Interrupt Enable Register 1          | USBIE1=FF                     |

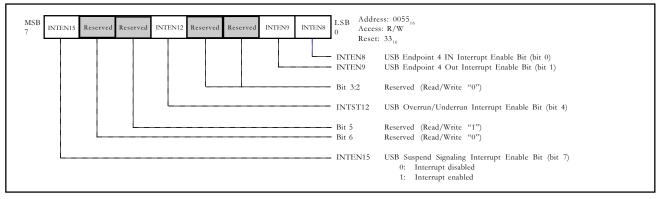

| 001D <sub>16</sub> | Port P8 Direction Register            | P8D=00         | 005516             | USB Interrupt Enable Register 2          | USBIE2=33                     |

| 001E <sub>16</sub> | Reserved                              |                | 005616             | USB Frame Number Register Low            | USBSOFL=00                    |

| 001F <sub>16</sub> | Clock Control Register                | CCR=00         | 005716             | USB Frame Number Register High           | USBSOFH=00                    |

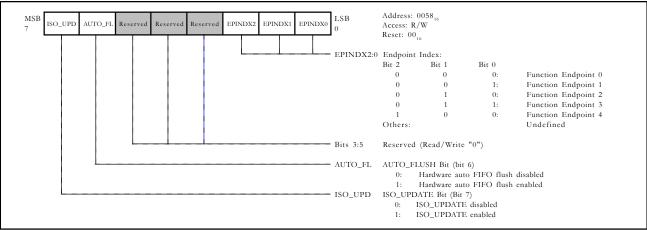

| 002016             | Timer XL                              | TXL=FF         | 005816             | USB Endpoint Index                       | USBINDEX=00                   |

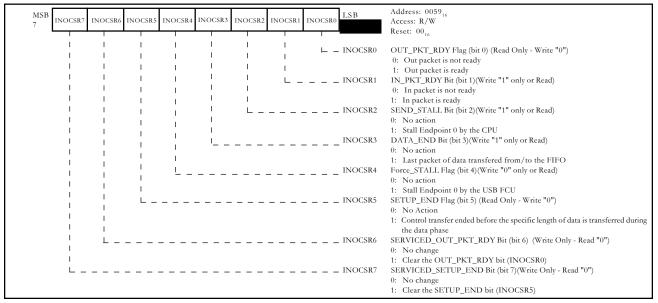

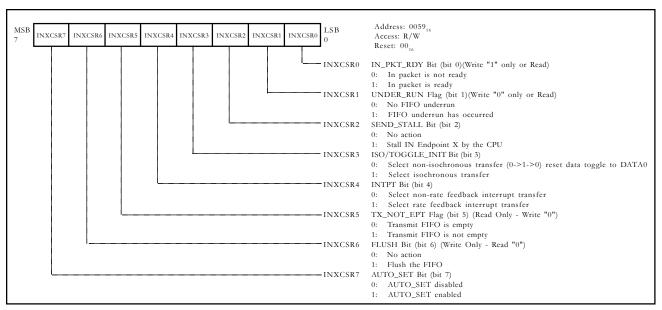

| 002116             | Timer XH                              | TXH=FF         | 005916             | USB Endpoint x IN CSR                    | IN_CSR=00                     |

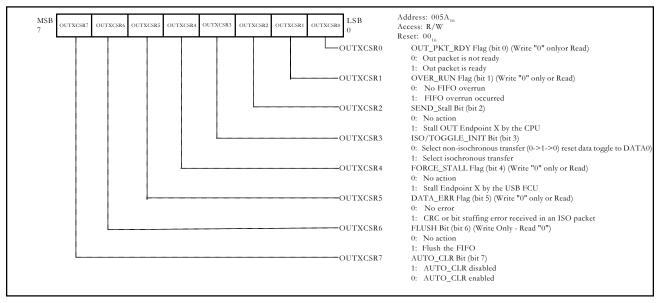

| 002216             | Timer YL                              | TYL=FF         | 005A <sub>16</sub> | USB Endpoint x OUT CSR                   | OUT_CSR=00                    |

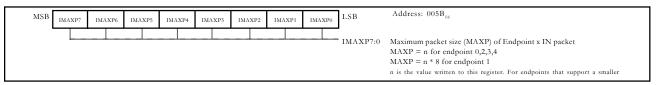

| 002316             | Timer YH                              | TYH=FF         | 005B <sub>16</sub> | USB Endpoint x IN MAXP                   | IN_MAXP (endpoint dependent)  |

| 002416             | Timer 1                               | T1=FF          | 005C <sub>16</sub> | USB Endpoint x OUT MAXP                  | OUT_MAXP (endpoint dependent) |

| 002516             | Timer 2                               | T2=01          | 005D <sub>16</sub> | USB Endpoint x OUT WRT_CNT Low           | WRT_CNTL=00                   |

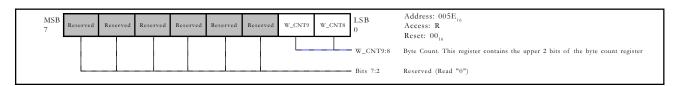

| 002616             | Timer 3                               | T3=FF          | 005E <sub>16</sub> | USB Endpoint x OUT WRT_CNT High          | WRT_CNTH=00                   |

| 002716             | Timer X Mode Register                 | TXM=00         | 005F <sub>16</sub> | Reserved                                 |                               |

| 002816             | Timer Y Mode Register                 | TYM=00         | 0060 <sub>16</sub> | USB Endpoint 0 FIFO                      | USBFIFO0=N/A                  |

| 002916             | Timer 123 Mode Register               | T123M=00       | 0061 <sub>16</sub> | USB Endpoint 1 FIFO                      | USBFIFO1=N/A                  |

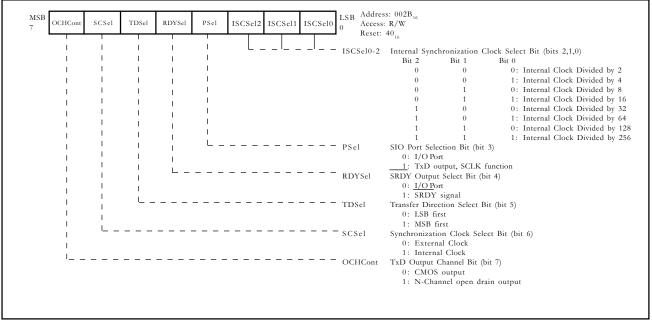

| 002A <sub>16</sub> | SIO Shift Register                    | SIOSHT=XX      | 006216             | USB Endpoint 2 FIFO                      | USBFIFO2=N/A                  |

| 002B <sub>16</sub> | SIO Control Register 1                | SIOCON1=40     | 006316             | USB Endpoint 3 FIFO                      | USBFIFO3=N/A                  |

| 002C <sub>16</sub> | SIO Control Register 2                | SIOCON2=18     | 0064 <sub>16</sub> | USB Endpoint 4 FIFO                      | USBFIFO4=N/A                  |

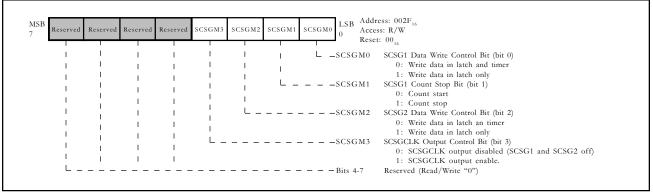

| 002D <sub>16</sub> | Special Count Source Generator1       | SCSG1=FF       | 006516             | Reserved                                 |                               |

| 002E <sub>16</sub> | Special Count Source Generator2       | SCSG2=FF       | 006616             | Reserved                                 |                               |

| 002F <sub>16</sub> | Special Count Source Mode Register    | SCSM=00        | 0067 <sub>16</sub> | Reserved                                 |                               |

| 003016             | UART1 Mode Register                   | U1MOD=00       | 006816             | Reserved                                 |                               |

| 003116             | UART1 Baud Rate Generator             | U1BRG=XX       | 006916             | Reserved                                 |                               |

| 003216             | UART1 Status Register                 | U1STS=03       | 006A <sub>16</sub> | Reserved                                 |                               |

| 003316             | UART1 Control Register                | U1CON=00       | 006B <sub>16</sub> | Reserved                                 |                               |

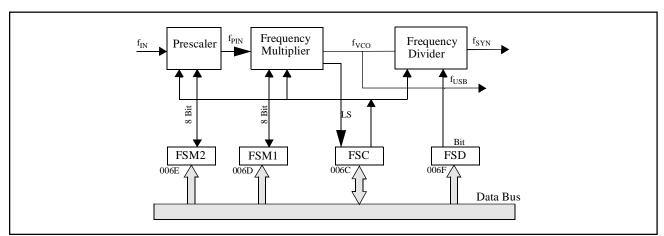

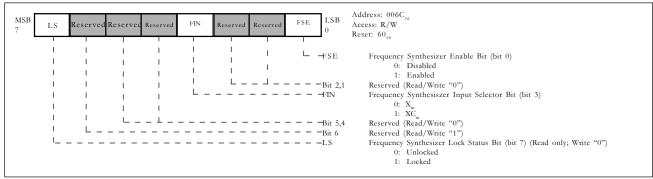

| 003416             | UART1 Transmit/Receiver Buffer 1      | U1TRB1=XX      | 006C <sub>16</sub> | Freq Synthesizer Control                 | FSC=60                        |

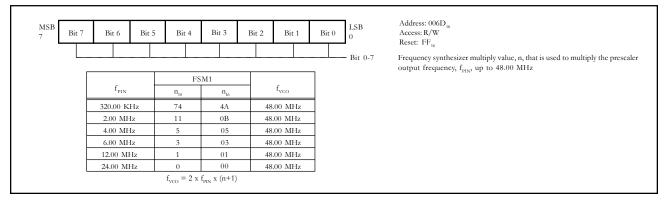

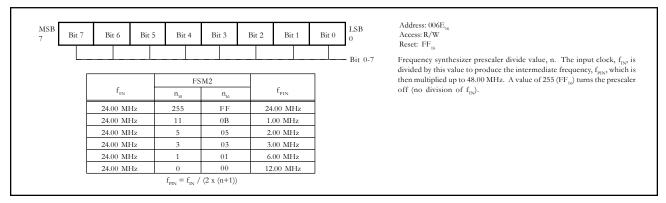

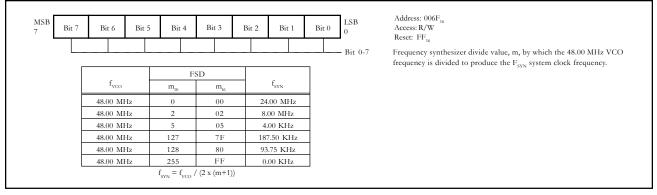

| 003516             | UART1 Transmit/Receiver Buffer 2      | U1TRB2=XX      | 006D <sub>16</sub> | Freq Synthesizer Multiply Register 1     | FSM1=FF                       |

| 003616             | UART1 RTS Control Register            | U1RTSC=80      | 006E <sub>16</sub> | Freq Synthesizer Multiply Register 2     | FSM2=FF                       |

| 003716             | Reserved                              |                | 006F <sub>16</sub> | Freq Synthesizer Divide Register         | FSD=FF                        |

# 1.14 INPUT AND OUTPUT PORTS

Table 1.5. Input and Output Ports

| Pin                               | Name   | Input/<br>Output              | I/O<br>Format    | Non-Port<br>Function                  | Related<br>SFR's                              | Ref. Number |

|-----------------------------------|--------|-------------------------------|------------------|---------------------------------------|-----------------------------------------------|-------------|

| P0 <sub>0</sub> – P0 <sub>7</sub> | Port 0 | Input/output, individual bits | CMOS I/O<br>port | Address Bus                           | CPU Mode Register                             | Fig. 1.15   |

| P1 <sub>0</sub> – P1 <sub>7</sub> | Port 1 | Input/output, individual bits | CMOS I/O<br>port | Address Bus                           | CPU Mode Register                             | Fig. 1.15   |

| P2 <sub>0</sub> – P2 <sub>7</sub> | Port 2 | Input/output, individual bits | CMOS I/O<br>port | Data Bus                              | CPU Mode Register                             | Fig. 1.15   |

| P3 <sub>0</sub> – P3 <sub>7</sub> | Port 3 | Input/output, individual bits | CMOS I/O<br>port | Control signal I/O                    | CPU Mode Register                             | Fig. 1.15   |

| P4 <sub>0</sub>                   |        |                               |                  | Expanded Data Memory<br>Access        | CPU Mode Register                             | Fig. 1.16   |

| P4 <sub>1</sub>                   |        |                               |                  | External Interrupt Input (INT0)       | Interrupt Edge<br>Selection Register          | Fig. 1.16   |

| P4 <sub>2</sub>                   | Port 4 | Input/output, individual bits | CMOS I/O<br>port | External Interrupt Input<br>(INT1)    | Interrupt Edge<br>Selection Register          | Fig. 1.16   |

| P4 <sub>3</sub>                   |        |                               |                  | External Interrupt Input (CNTR0)      | Timer X Mode<br>Register                      | Fig. 1.16   |

| P4 <sub>4</sub>                   |        |                               |                  | External Interrupt Input (CNTR1)      | Timer Y Mode<br>Register                      | Fig. 1.16   |

| P5 <sub>0</sub>                   |        |                               | 1                | X <sub>cin</sub>                      | CPU Mode Register                             | Fig. 1.17   |

| P5 <sub>1</sub>                   |        | Input/output,                 | CMOS I/O         | X <sub>cout</sub> or T <sub>out</sub> | CPU Mode Register<br>or T123 Mode<br>Register | Fig. 1.17   |

| P5 <sub>2</sub>                   | Port 5 | individual bits               | port             | OBF₀ Output                           | MBI Interface                                 | Fig. 1.17   |

| P5 <sub>3</sub>                   |        |                               |                  | IBF₀ Output                           | MBI Interface                                 | Fig. 1.17   |

| P5₄                               | 1      |                               |                  | S <sub>0</sub> Input                  | MBI Interface                                 | Fig. 1.17   |

| P5 <sub>5</sub>                   |        |                               |                  | A <sub>0</sub> Input                  | MBI Interface                                 | Fig. 1.17   |

| P5 <sub>6</sub>                   |        |                               |                  | R(E) Input                            | MBI Interface                                 | Fig. 1.17   |

| P5 <sub>7</sub>                   | 1      |                               |                  | W(R/W) Input                          | MBI Interface                                 | Fig. 1.17   |

| P6 <sub>0</sub> - P6 <sub>7</sub> | Port 6 | Input/output, individual bits | CMOS I/O<br>port | Master CPU data bus                   | MBI Interface                                 | Fig. 1.18   |

| P7₀                               |        |                               |                  | SOF Output                            | USB Interface                                 | Fig. 1.19   |

| P7 <sub>1</sub>                   |        | Input/output,                 | CMOS I/O         | HOLD                                  | CPU Mode Register                             | Fig. 1.19   |

| P7 <sub>2</sub>                   | Port 7 | individual bits               | port             | S₁ Input                              | MBI Interface                                 | Fig. 1.19   |

| P7 <sub>3</sub>                   |        |                               |                  | IBF₁ Output                           | MBI Interface                                 | Fig. 1.19   |

| P7 <sub>4</sub>                   |        |                               |                  | OBF₁ Output                           | MBI Interface                                 | Fig. 1.19   |

| P8 <sub>0</sub>                   |        |                               |                  | UTXD2/SRDY                            | UART Mode<br>Register/SIO Mode<br>Register    | Fig. 1.20   |

| P8 <sub>1</sub>                   |        |                               |                  | URXD2/SCLK                            | UART Mode<br>Register/SIO Mode<br>Register    | Fig. 1.20   |

| P8 <sub>2</sub>                   |        |                               |                  | CTS2/STXD                             | UART Mode<br>Register/SIO Mode<br>Register    | Fig. 1.21   |

| P8 <sub>3</sub>                   | Port 8 | Input/output, individual bits | CMOS I/O<br>port | RTS2/SRXD                             | UART Mode<br>Register/SIO Mode<br>Register    | Fig. 1.21   |

| P8 <sub>4</sub>                   |        |                               |                  | UTXD1                                 | UART Mode<br>Register                         | Fig. 1.21   |

| P8 <sub>5</sub>                   |        |                               |                  | URXD1                                 | UART Mode<br>Register                         | Fig. 1.22   |

| P8 <sub>6</sub>                   |        |                               |                  | CTS1                                  | UART Mode<br>Register                         | Fig. 1.22   |

| P8 <sub>7</sub>                   |        |                               |                  | RTS1                                  | UART Mode<br>Register                         | Fig. 1.22   |

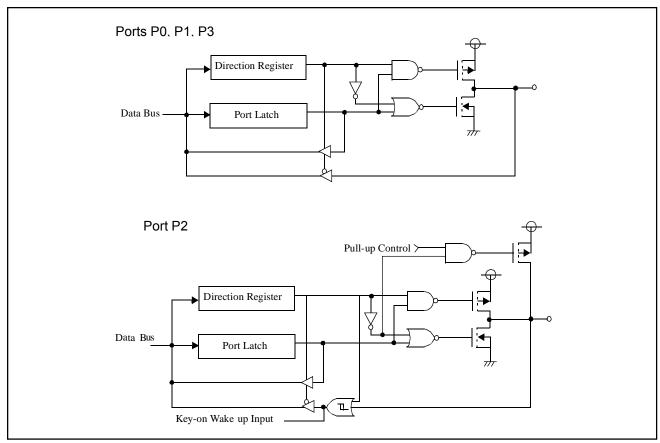

#### 1.14.1 I/O Ports

This device has 66 programmable I/O pins arranged as ports P00 to P87. Each port bit can be configured as input or output. To set the I/O port bit direction, write a "1" to the corresponding direction register bit to select output mode, or write a "0" to the direction register bit to select input mode.

At reset, all of the direction registers are initialized to 0016, setting all of the I/O ports to input mode.

If data is written to a pin and then read from that pin while it is in output mode, the data read is the value of the port latch rather than the value of the pin itself. Therefore, if an external load changes the value of an output pin, the intended output value will still be read correctly. Pins set to input mode are floating (provided that the pull up resistors are not being used) to ensure that the value input to such a pin can be read accurately. In the case when data is written to a pin configured as an input, the data is written only to the port latch; the pin itself remains floating.

Most of the I/O Ports are multiplexed with secondary functions. When a GPI/O is multiplexed with a second function, the control signal from the peripheral overrides the direction register. The multiplexing is briefly described below. The second function signals to and from the I/O ports are described in detail in their respective block's description.

# 1.14.1.1 Ports P0, P1, and P3

Ports P0 and P1 act as the address bus (AB0-AB15) in Microprocessor and Memory Expansion modes. Bits 0 and 3-7 of Port P3 acts as control signals in Microprocessor and Memory Expansion modes.

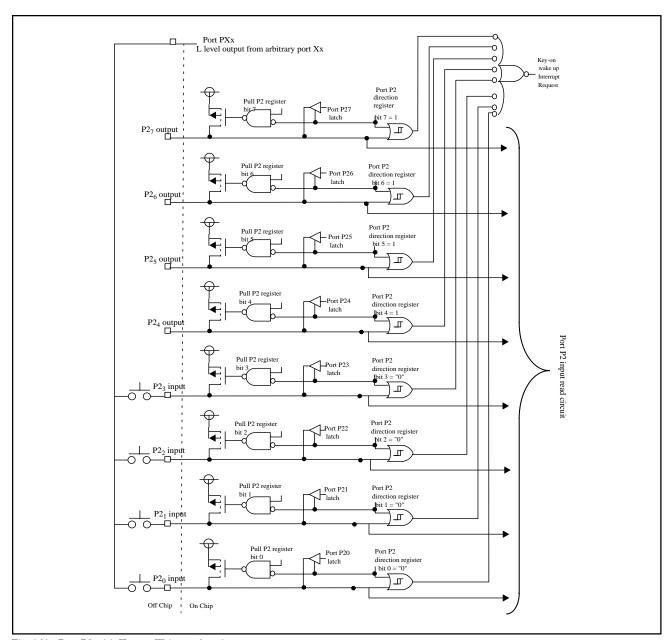

#### 1.14.1.2 Port P2

Port P2 is an 8-bit general purpose I/O port when in single chip mode. In this mode, the port has key-on wake up circuitry which can be used to restart the chip externally from a WIT or STP low power mode. This port also acts as the data bus during microprocessor and memory expansion modes. Port P2 input level can be set to reduced VIHL level or CMOS level by bit 6 of the port control register (PTC).

Fig. 1.15. Ports P0, P1, P2, P3 Block Diagram

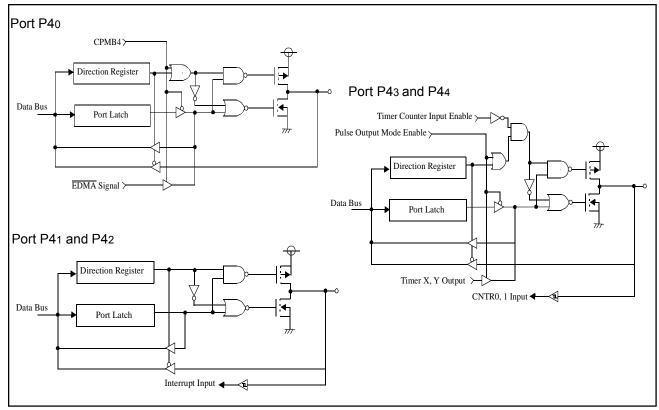

#### 1.14.1.3 Port P4

Port 4 is a 5-bit general purpose I/O port that can be configured to access special second functions. The port can be set up in any configuration in all three processor modes.

#### Port P40

This pin is multiplexed with the EDMA (Extended Data Memory Access) function. When the MCU is in memory expansion or microprocessor mode and CPMB4 is set to "1", this pin operates as the EDMA output as described in section 1.12.6.

#### Port P41- P42

These pins are multiplexed with external interrupts 0 and 1 ( $\overline{\text{INT0}}$  and  $\overline{\text{INT1}}$ ). The external interrupt function is enabled by setting the bits to "1" in the interrupt control register that correspond to  $\overline{\text{INT0}}$  and  $\overline{\text{INT1}}$ . The interrupt polarity register can be configured to define  $\overline{\text{INT0}}$  and  $\overline{\text{INT1}}$  as active high or low interrupts. See section 1.15.1 for more information on configuring interrupts.

#### Port P43- P44

These pins are multiplexed with Timer X and Y functions for P43 and P44 respectively. The timer functions of the pins are independently defined by configuring the timer peripheral. P43 acts as Timer X input pin for pulse width measurement mode and event counter mode or as Timer X output pin for pulse output mode. P43 can also be used as an external interrupt (CNTR0) when Timer X in not in output mode. The polarity is selected in the Timer X mode register. The external interrupt function is enabled by setting the bit to "1" in the interrupt control register that corresponds to CNTR0. See section 1.15.1 for more information on configuring interrupts.

P44 acts as Timer Y input pin for pulse period measurement mode, pulse H-L measurement mode, and event counter mode or as Timer Y output pin for pulse output mode. P43 can also be used as an external interrupt (CNTR1) when Timer Y in not in output mode. The polarity is selected in the Timer Y mode register. The external interrupt function is enabled by setting the bit to "1" in the interrupt control register that corresponds to CNTR1. See section 1.15.1 for more information on configuring interrupts.

Fig. 1.16. Port P4 Block Diagram

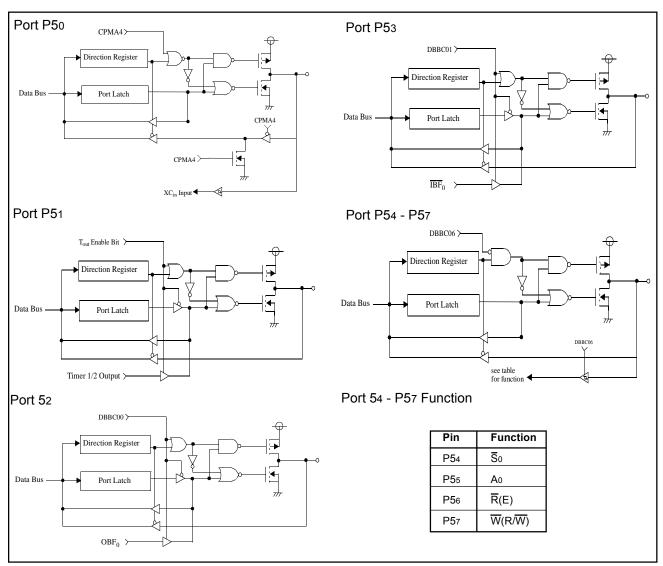

#### 1.14.1.4 Port P5

Port 5 is an 8-bit general purpose I/O port that can be configured to access special second functions. The port can be set up in any configuration in all three processor modes.

#### Port P50

This pin is multiplexed with the XCin clock input. When the XCin clock is activated, the pin's I/O is disabled.

#### Port P51

This pin is multiplexed with the XCout clock output and the Timer 1/2 pulse output. When the XCin clock is activated, the pin's I/O is disabled. If XCin is not be-

ing used as a system clock or XCout oscillation is disabled, the pin can be configured as the Timer 1/2 pulse output pin. This feature is configured in the Timer 123 mode register as described in section 1.17.

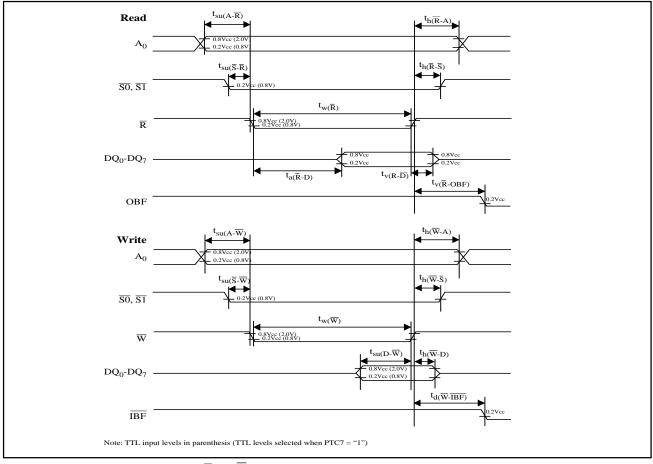

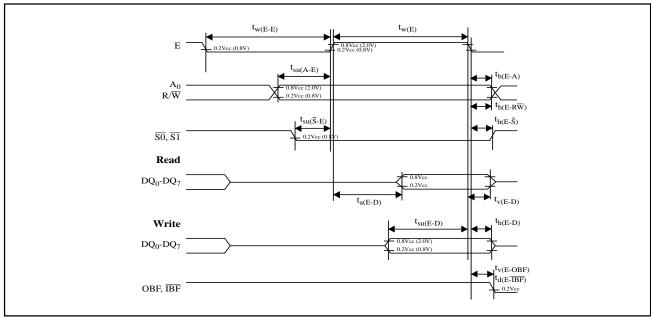

#### Port P52- P57

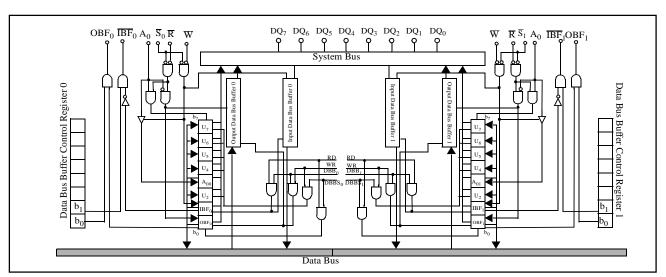

These pins are multiplexed with control pins for the bus interface control block. P52 acts as OBF0 output to a Master CPU when DBBC00 is "1".

P53 acts as IBF0 output to a Master CPU when DBBC01 is "1".

P54-P57 act as input control signals from a Master CPU when DBBC06 is "1". The table featured in Figure 1.17 shows the bus interface control signal that corresponds to each pin.

Fig. 1.17. Port P5 Block Diagram

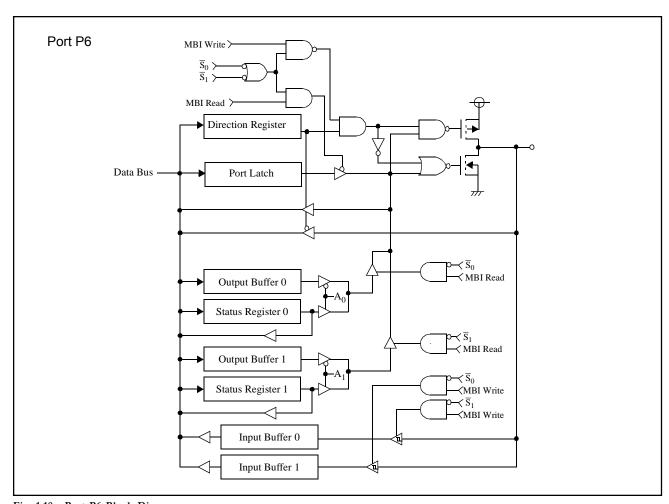

# 1.14.1.5 Port P6

Port P6 is an 8-bit general purpose I/O port that can be configured to access special second functions. The port acts as the data bus interface for the bus interface control block when DBBC06 is "1". The port can be set up in any configuration in all three processor modes.

Fig. 1.18. Port P6 Block Diagram

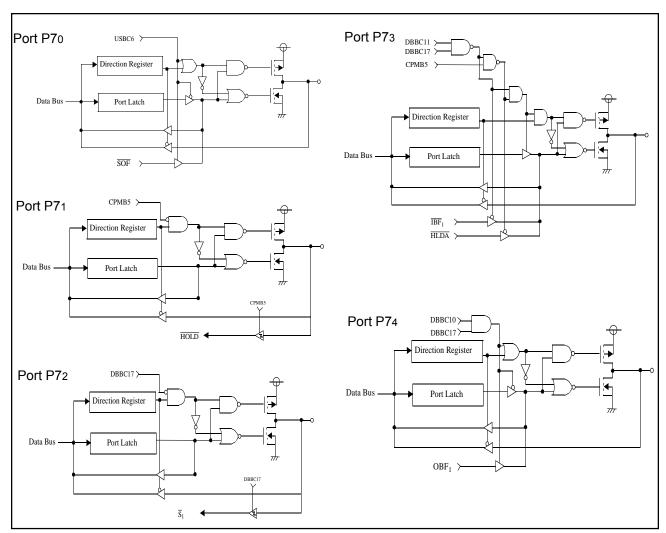

#### 1.14.1.6 Port P7

Port P7 is a 5-bit general purpose I/O port that can be configured to access special second functions.

#### Port P70

This pin is multiplexed with the USB start of frame pulse (SOF) output. When USBC6 is a "1", this pin outputs the USB SOF.

#### Port P71

This pin is multiplexed with the HOLD function. When the MCU is in memory expansion or microprocessor mode and CPMB5 is set to "1".

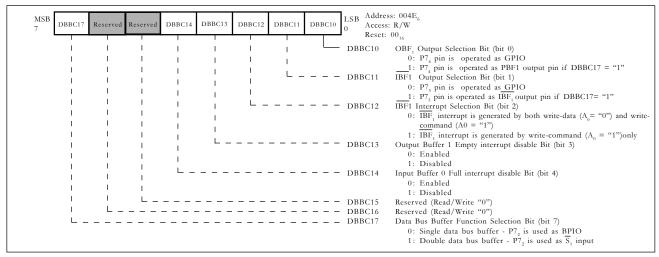

#### Port P72

This pin is multiplexed with the  $\overline{S}_1$  input control signal from a Master CPU. When DBBC17 is "1", the pin takes on the function of the  $\overline{S}_1$  input control signal.

#### Port P73

This pin is multiplexed with the IBF1 output control signal for a Master CPU and the HLDA function. When DBBC11 and DBBC17 are "1", the pin takes on the function of the IBF1 output control signal. When the MCU is in memory expansion or microprocessor mode, CPMB5 is set to "1", and the IBF1 function is not enabled.

#### Port P74

This pin is multiplexed with the OBF1 control pin for the bus interface control block. P74 acts as OBF1 output to a Master CPU when DBBC10 and DBBC17 are "1"

Fig. 1.19. Port P7 Block Diagram

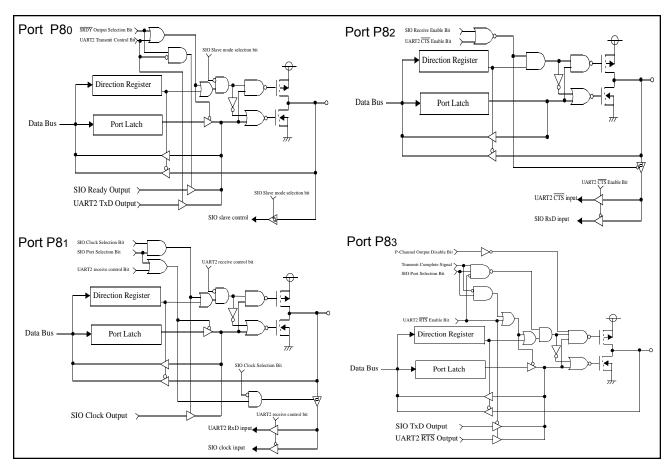

#### 1.14.5.7 Port 8

Port 8 is an 8-bit general purpose I/O port that can be configured to access special second functions. The port can be set up in any configuration in all three processor modes.

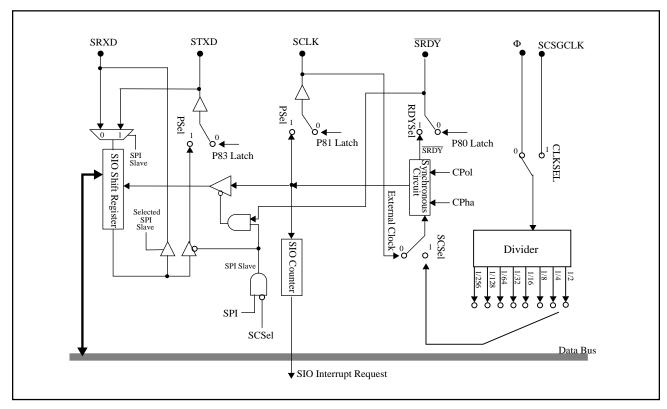

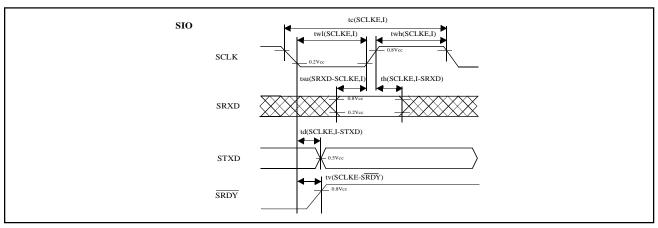

#### Port P80

This pin is multiplexed with the SIO SRDY signal and the UART2 TxD signal. When UART2 is in transmit mode, the pin acts as the TxD output signal. When the pin is not being used as the UART2 TxD output and bit 4 of the SIO control register 1 (SIOCON1) is a "1", the port acts as the SIO SRDY output signal. If during this function, the SIO is configured in slave mode, this pin acts as a slave input from a master. See section 1.18 for more SIO information.

# Port P81

This pin is multiplexed with the SIO SCLK signal and the UART2 RxD signal. When UART2 is in receive mode, the pin acts as the RxD input signal. When the pin is not being used as the UART2 RxD input and bit

2 of the SIO control register 1 (SIOCON1) is a "1", the port acts as the SIO SCLK signal. In this mode a "1" in bit 6 of SIOCON1 configures the pin to output SCLK whereas a "0" configures the pin to input SCLK.

#### Port P82

This pin is multiplexed with the SIO SRxD signal and the UART2 CTS signal. When bit 5 of the UART2 control register (U2CON) is a "1", the port acts as the CTS input signal. When the pin is not being used as the UART2 CTS input and bit 2 of the SIO control register 2 (SIOCON2) is a "1", the port acts as the SIO SRxD input signal.

#### Port P83

This pin is multiplexed with the SIO STxD signal and the UART2 RTS signal. When bit 6 of the UART2 control register (U2CON) is a "1", the port acts as the RTS output signal. When the pin is not being used as the UART2 RTS output and bit 3 of the SIO control register 1 (SIOCON1) is a "1", the port acts as the SIO STxD output signal.

Fig. 1.20. Port P80, P81, P82, P83 Block Diagram

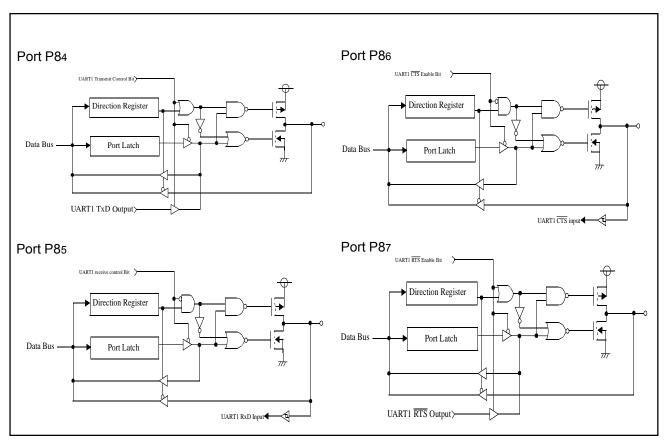

#### Port P84

This pin is multiplexed with the UART1 TxD signal. When UART1 is in transmit mode, the pin acts as the TxD output signal.

#### Port P85

This pin is multiplexed with the UART1 RxD signal. When UART1 is in receive mode, the pin acts as the RxD input signal.

#### Port P86

This pin is multiplexed with the UART1  $\overline{\text{CTS}}$  signal. When bit 5 of the UART1 control register (U1CON) is a "1", the port acts as the  $\overline{\text{CTS}}$  input signal.

#### Port P87

This pin is multiplexed with the UART1 RTS signal. When bit 6 of the UART1 control register (U1CON) is a "1", the port acts as the RTS output signal.

Fig. 1.21. Port P84, P85, P86 and P87 Block Diagram

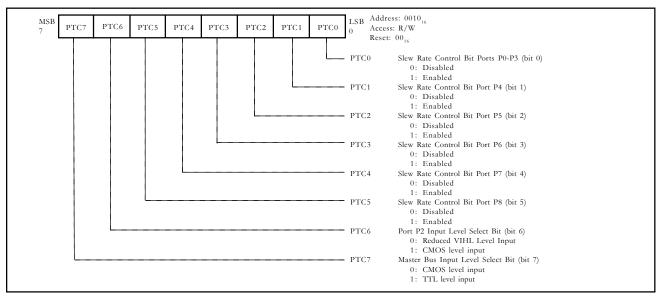

# 1.14.2 Port Control Register (PTC)

This device is equipped with a port control register to turn on and off the slew rate control and to control the input levels for Port P2 and the MBI pins (see Figure 1.22).

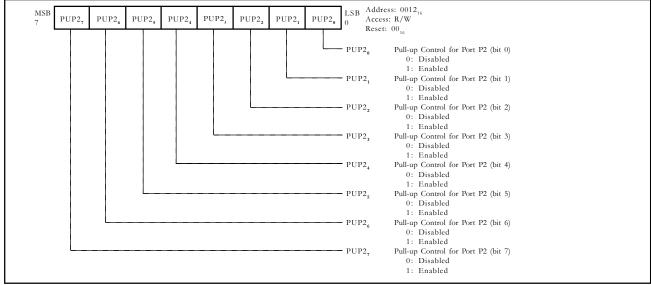

# 1.14.3 Port P2 Pull-up Control Register (PUP2)

This device is equipped with internal pull ups on Port P2 that can be enabled by software. Each bit of the pull-up control register controls a corresponding pin of Port P2. The pull-up control register pulls up the port when the port is in input mode. The value of the pull-up control register has no effect when the port is in output mode (see Figure 1.23).

Fig. 1.22. Port Control Register (PTC)

Fig. 1.23. Pull-up Control Register (PUP2)

# 1.15 INTERRUPT CONTROL UNIT

This section details a specialized peripheral, the interrupt control unit (ICU).

This series supports a maximum of 23 maskable interrupts, one software interrupts, and one reset vector that is treated as a non-maskable interrupt.

Table 1.6 describes the interrupt registers. See Table 1.7 for the interrupt sources, jump destination addresses, interrupt priorities, and section references for the interrupt request sources.

Table 1.6. Interrupt Registers

| Address            | Description                  | Acronym and<br>Value at Reset |

|--------------------|------------------------------|-------------------------------|

| 000216             | Interrupt request register A | IREQA=00                      |

| 0003 <sub>16</sub> | Interrupt request register B | IREQB=00                      |

| 000416             | Interrupt request register C | IREQC=00                      |

| 000516             | Interrupt control register A | ICONA=00                      |

| 000616             | Interrupt control register B | ICONB=00                      |

| 0007 <sub>16</sub> | Interrupt control register C | ICONC=00                      |

| 0011 <sub>16</sub> | Interrupt polarity selection | IPOL=00                       |

|                    | register                     |                               |

Table 1.7. Interrupt Vector

| Priority | Interrupt | -                  | stination<br>Address<br>Address) | Remarks                        |   |     |        |                        |                  |

|----------|-----------|--------------------|----------------------------------|--------------------------------|---|-----|--------|------------------------|------------------|

|          |           | High-order<br>Byte | Low-order<br>Byte                |                                |   |     |        |                        | Reference        |

| 1        | RSRV1     | FFFF               | FFFE                             | Reserved for factory use       |   |     |        |                        |                  |

| 2        | RSRV2     | FFFD               | FFFC                             | Reserved for factory use       |   |     |        |                        |                  |

| 3        | RESET     | FFFB               | FFFA                             | User RESET (Non-Maskable)      |   |     |        |                        |                  |

| 4        | USB       | FFF9               | FFF8                             | USB Function Interrupt         | 0 | LSB |        |                        | Section 1.21.2.1 |

| 5        | SOF       | FFF7               | FFF6                             | USB SOF Interrupt              | 1 |     | ] =    |                        | Section 1.21.2.2 |

| 6        | INT0      | FFF5               | FFF4                             | External Interrupt 0           | 2 |     | IREQA  |                        | Section 1.15.1   |

| 7        | ĪNT1      | FFF3               | FFF2                             | External Interrupt 1           | 3 |     | λ<br>& |                        | Section 1.15.1   |

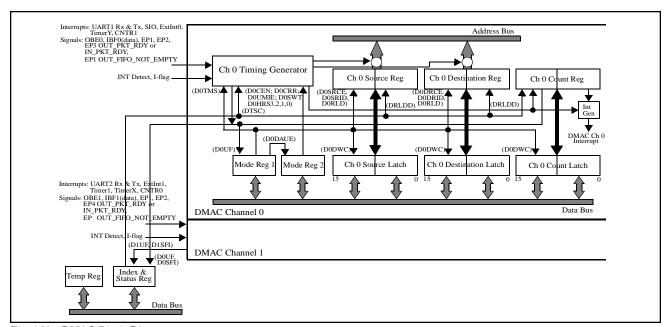

| 8        | DMA1      | FFF1               | FFF0                             | DMAC Channel 0 Interrupt       | 4 |     |        |                        | Section 1.23     |

| 9        | DMA2      | FFEF               | FFEE                             | DMAC Channel 1 Interrupt       | 5 |     | CONA   |                        | Section 1.23     |

| 10       | U1RBF     | FFED               | FFEC                             | UART1 Receiver Buffer Full     | 6 |     | ≻      | ဂ္ဂ                    | Section 1.19.4.2 |

| 11       | U1TX      | FFEB               | FFEA                             | UART1 Transmit Interrupt       | 7 | MSB |        | Corresponding Register | Section 1.19.4.1 |

| 12       | U1ES      | FFE9               | FFE8                             | UART1 Error Sum Interrupt      | 0 | LSB |        | spo                    | Section 1.19.4.2 |

| 13       | U2RBF     | FFE7               | FFE6                             | UART2 Receiver Buffer Full     | 1 |     | =      | ndir                   | Section 1.19.4.2 |

| 14       | U2TX      | FFE5               | FFE4                             | UART2 Transmit Interrupt       | 2 |     | IREQB  | ω<br>R                 | Section 1.19.4.1 |

| 15       | U2ES      | FFE3               | FFE2                             | UART2 Error Sum Interrupt      | 3 |     | 00     | ≀egi                   | Section 1.19.4.2 |

| 16       | TX        | FFE1               | FFE0                             | Timer X Interrupt              | 4 |     | ਨ      | ster                   | Section 1.17     |

| 17       | TY        | FFDF               | FFDE                             | Timer Y Interrupt              | 5 |     | CONB   | AS.                    | Section 1.17     |

| 18       | T1        | FFDD               | FFDC                             | Timer 1 Interrupt              | 6 |     | Φ.     | sigr                   | Section 1.17     |

| 19       | T2        | FFDB               | FFDA                             | Timer 2 Interrupt              | 7 | MSB |        | Assignment             | Section 1.17     |

| 20       | T3        | FFD9               | FFD8                             | Timer 3 Interrupt              | 0 | LSB |        | nt                     | Section 1.17     |

| 21       | CNTR0     | FFD7               | FFD6                             | External CNTR0 Interrupt       | 1 |     | R      |                        | Section 1.17.1.2 |

| 22       | CNTR1     | FFD5               | FFD4                             | External CNTR1 Interrupt       | 2 |     | :QC    |                        | Section 1.17.2   |

| 23       | SIO       | FFD3               | FFD2                             | SIO Interrupt                  | 3 |     | Çο     |                        | Section 1.18     |

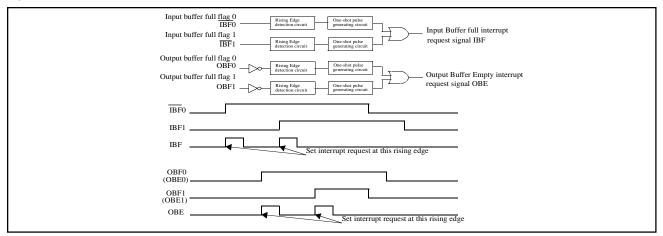

| 24       | ĪBF       | FFD1               | FFD0                             | Input Buffer Full Interrupt    | 4 |     | ICONC  |                        | Section 1.22     |

| 25       | OBE       | FFCF               | FFCE                             | Output Buffer Empty Interrupt  | 5 |     | S      |                        | Section 1.22     |

| 26       | KEY       | FFCD               | FFCC                             | Key-on Wake Up                 | 6 | MSB |        |                        | Section 1.16     |

| 27       | BRK       | FFCB               | FFCA                             | BRK Instruction (Non-Maskable) |   |     |        |                        |                  |

# 1.15.1 Interrupt Control

Each maskable interrupt has associated with it an interrupt request bit and an interrupt enable bit. These bits, along with the I flag, determine whether interrupt events can cause an interrupt service request to be generated. An interrupt request bit is set to "1" when its corresponding interrupt event is activated. The bit is cleared to a "0" when the interrupt is serviced or when a "0" is written to the bit. The bit can not be set high by writing "1" to it. Each interrupt enable bit deter-

mines whether the interrupt request bit it is paired with is seen when the interrupts are polled. When the interrupt enable bit is a "0", the interrupt request bit is not seen; and when the enable bit is a "1", the interrupt request is seen.

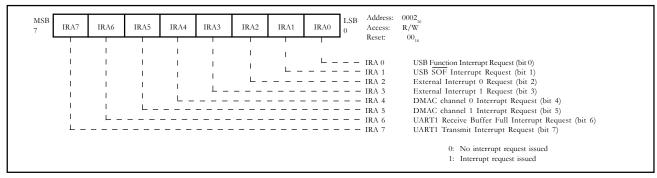

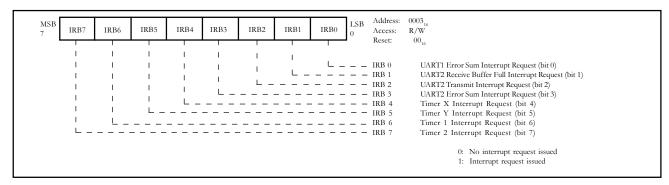

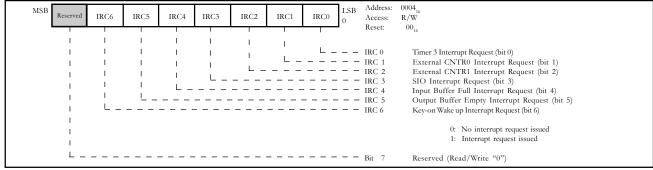

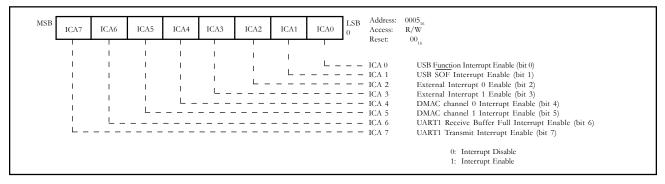

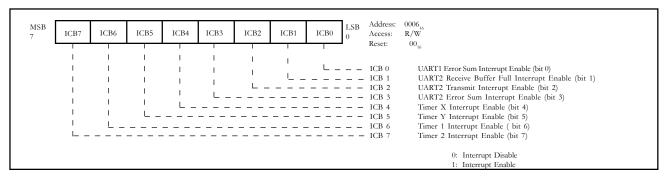

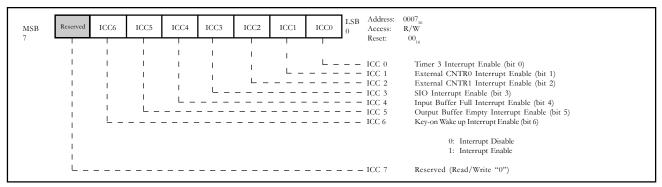

The interrupt request registers (IREQ) for the 23 maskable interrupts are shown in Figure 1.24, Figure 1.25, and Figure 1.26. The interrupt control registers (ICON) for the 23 maskable interrupts are shown in Figure 1.27, Figure 1.28, and Figure 1.29.

Fig. 1.24. Interrupt Request Register A (IREQA)

Fig. 1.25. Interrupt Request Register B (IREQB)

Fig. 1.26. Interrupt Request Register C (IREQC)

Fig. 1.27 Interrupt Control Register A (ICONA)

Fig. 1.28. Interrupt Control Register B (ICONB)

Fig. 1.29. Interrupt Control Register C (ICONC)

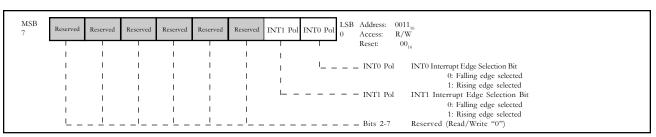

The interrupt polarity register allows the user to select the edge that will trigger an external interrupt

request. The polarity register (IPOL) for the external interrupts is shown in Figure 1.30.

Fig. 1.30. Interrupt Polarity Register (IPOL)

# 1.16 KEY-ON WAKE UP

This device contains a key-on wake up interrupt function. The key-on wake up interrupt function is one way of returning from a power-down state caused by the STP or WIT instructions. This interrupt is generated

by applying low level to any pin of Port P2. If a key matrix is connected as shown in Figure 1.31, the microcomputer can be returned to a normal state by pressing any one of the keys. Key-on wake up is enabled in single-chip mode only.

Fig. 1.31. Port P2 with Key-on Wake up function

# 1.17 TIMERS

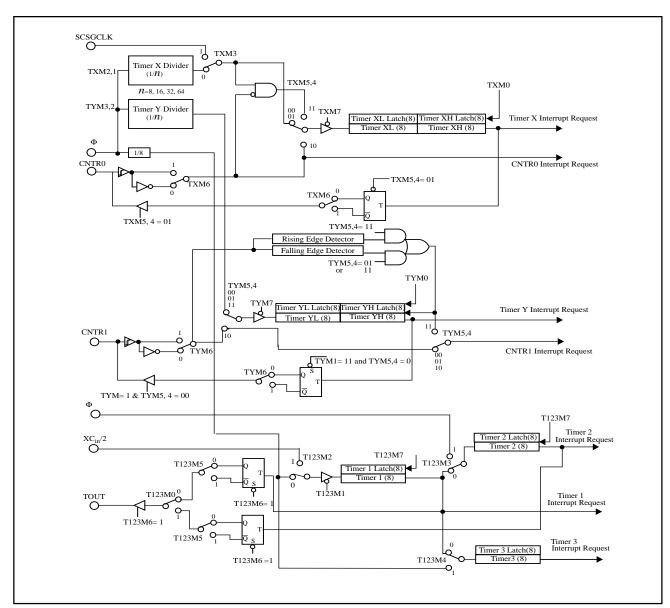

This device has five built-in timers: Timer X, Timer Y, Timer 1, Timer 2, and Timer 3.

The contents of the timer latch, corresponding to each timer, determine the divide ratio. The timers can be read or written at any time. However, the read and write operations on the high and low-order bytes of the 16-bit timers (Timer X and Y) must be performed in a specific order.

The timers are all down count timers; when the count of a timer reaches 0016 (000016 for Timer X and Y),

an underflow occurs at the next count pulse and the contents of the corresponding timer reload latch are reloaded into the timer. When a timer underflows, the interrupt request bit corresponding to that timer is set to a "1".

The divide ratio of a timer is given by 1/(n + 1), where n is the value written to the timer. When the STP instruction is executed or  $\overline{RESET}$  is asserted, 0116 is loaded into Timer 2 and the Timer 2 reload latch, and FF16 is loaded into Timer 1 and the Timer 1 reload latch.

Figure 1.32 is a block diagram of the five timers.

Fig. 1.32. Block diagram of Timers X, Y, 1, 2, and 3

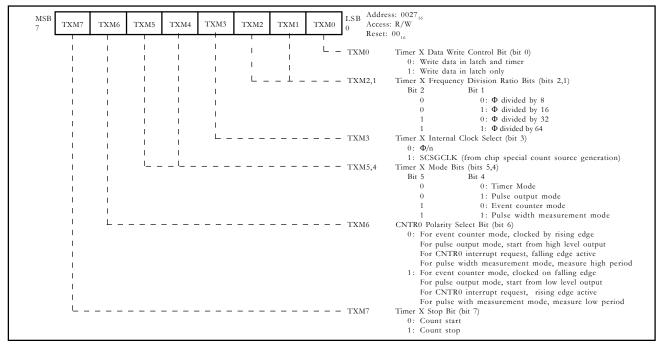

Fig. 1.33. Timer X Mode Register (TXM)

# 1.17.1 Timer X

Timer X is a 16-bit timer that has a 16-bit reload latch, and can be placed in one of four modes by setting bits TXM4 and TXM5 (bits 4 and 5 of the Mode Register, TXM). The bit assignment of the TXM is shown in Figure 1.33.

#### 1.17.1.1 Read and Write Method

Read and write operations on the high and low-order bytes of Timer X must be performed in a specific order.

#### Write Method

When writing to the timer, the lower order byte is written first. This data is placed in a temporary register that is assigned the same address as Timer XL. Next, the higher order byte is written. When this is done, the data is placed in the Timer XH reload latch and the low-order byte is transferred from its temporary register to the Timer XL reload latch. At this point, if the Timer X Data Write Control Bit (TXM0) (bit 0) is "0", the value in the Timer X reload latch is also loaded in Timer X. If TXM0 is "0", the data in the Timer X reload latch is loaded in Timer X after Timer X underflows.

#### Read Method

When reading Timer X, the high-order byte is real first. Reading the high-order byte causes the values of Timer XH and Timer XL to be placed in temporary registers assigned the same addresses as Timer XH and Timer XL. The low-order byte of Timer X is then read from its temporary register. This operation assures the correct reading of Timer X while it is counting.

#### 1.17.1.2 Count Stop Control

If the Timer X Count Stop Bit (TXM7) (bit 7 of the TXM) is set to a "1", Timer X stops counting in all four modes.

#### Timer Mode

Count Source:  $\Phi$ /n (where n is 8, 16, 32, or 64) or SCSGCLK

In this mode, each time the timer underflows, the corresponding timer interrupt request bit is set to a "1", the contents of the timer latch are loaded into the timer, and the count down sequence begins again.

# Pulse Output Mode

Count Source:  $\Phi$ /n (where n is 8, 16, 32, or 64) or SCSGCLK

Each time the timer X underflows, the output of the CNTR0 pin is inverted, and the corresponding Timer X interrupt request bit is set to a "1". The repeated inversion of the CNTR0 pin output produces a rectangular waveform with a duty ratio of 50 percent. The initial level of the output is determined by the CNTR0 polarity select bit (bit 6). When this bit is low, the output starts from a high level. When this bit is high, the output starts from a low level.

#### Event Counter Mode

Count Source: CNTR0

Timer countdown is triggered by inputs to the CNTR0 pin. Each time a timer underflows, the corresponding timer interrupt request bit is set to a "1", the contents of the timer reload latch are loaded into the timer, and the countdown sequence begins again.

The edge used to clock Timer X is determined by the CNTR0 polarity select bit (bit 6).

#### Pulse Width Measurement Mode

Count Source:  $\Phi$ /n (where n is 8, 16, 32, or 64) or SCSGCLK

This mode measures either the high or low-pulse width of the signal on the CNTR0 pin. The pulse width measured is determined by the CNTR0 polarity select bit (bit 6). When this bit is "0", the high pulse is measured. When this bit is "1", the low pulse is measured.

The timer counts down while the level on the CNTR0 pin is the polarity selected by the CNTR0 polarity select bit. When the timer underflows, the Timer X interrupt request bit is set to a "1", the contents of the timer reload latch are reloaded into the timer, and the timer continues counting down. Each time the signal polarity switches to the inactive state, a CNTR0 interrupt occurs indicating that the pulse width has been measured. The width of the measured pulse can be found by reading Timer X during the CNTR0 interrupt service routine.

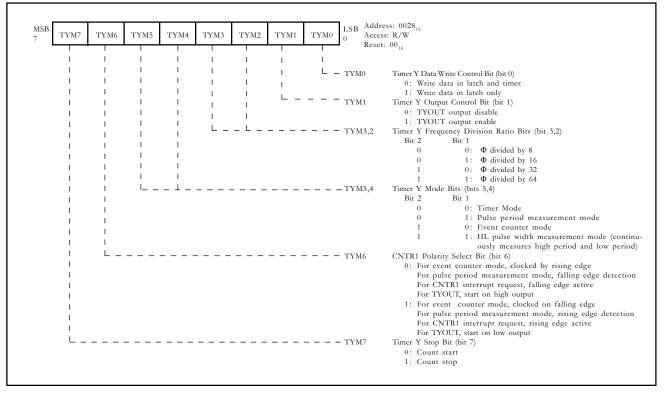

Fig. 1.34. Timer Y Mode Register (TYM)

#### 1.17.2 Timer Y

Timer Y is a 16-bit timer that has a 16-bit reload latch, and can be placed in any of four modes by setting TYM4 and TYM5 (bits 4 and 5) (see Figure 1.34). The desired mode is selected by modifying the values of TYM4 and TYM5.

#### 1.17.2.1 Read and Write Method

Read and write operations on the high and low-order bytes of Timer Y must be performed in a specific order.

#### Write Method

When writing to the timer, the lower order byte is written first. This data is placed in a temporary register that is assigned the same address as Timer YL. Next, the high-order byte is written. Then, the data is placed in the Timer YH reload latch and the low-order byte is transferred from its temporary register to the Timer YL reload latch. At this point, if the Timer Y Data Write Control Bit (TYM0) (bit 0) is low, the value in the Timer Y reload latch is also loaded in Timer Y. If TYM0 is "1", the data in the Timer Y reload latch is loaded in Timer Y after Timer Y underflows.

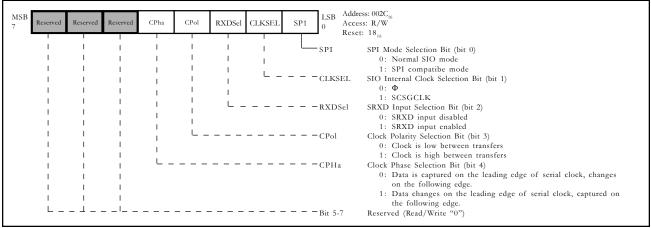

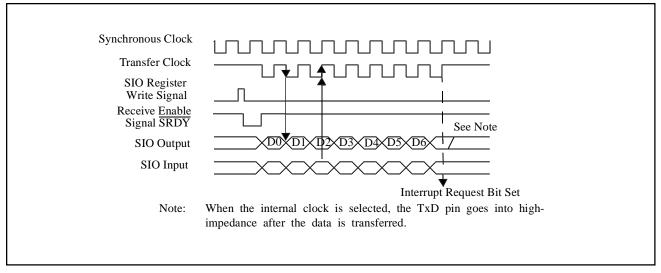

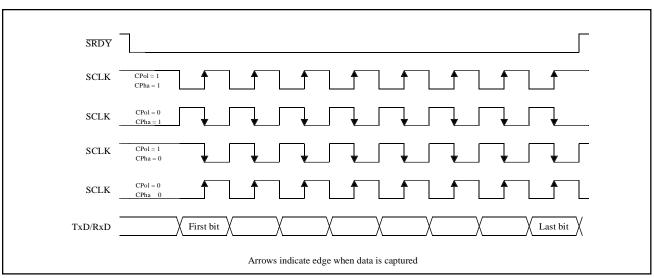

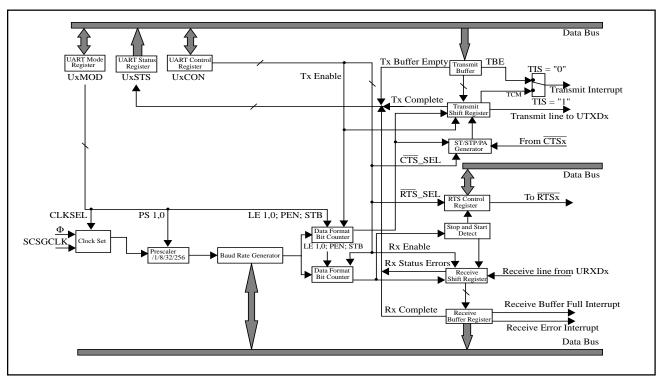

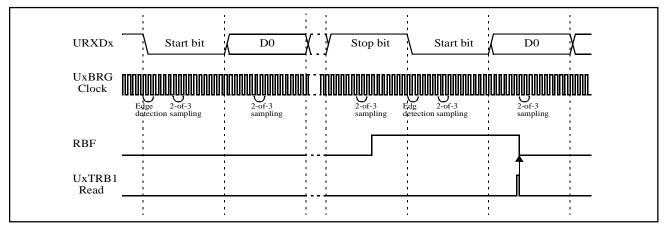

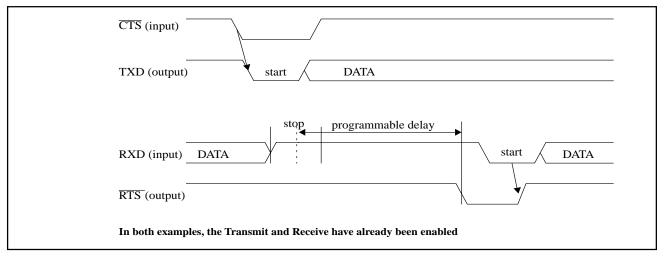

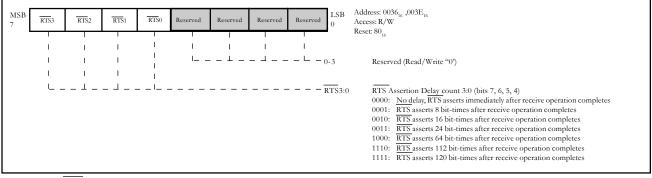

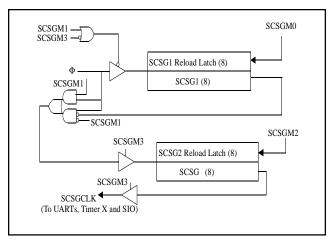

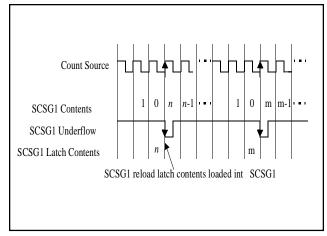

#### •Read Method