### **PD6710/'22** ISA-to-PC-Card (PCMCIA) Controllers

### Datasheet

The PD6710 and PD6722 are single-chip PC Card (PCMCIA) controller solutions capable of controlling one (PD6710) or two (PD6722) PC Card sockets. The chips are compliant with PC Card Standard, PCMCIA 2.1, and JEIDA 4.1 and are optimized for use in embedded applications and notebook/handheld/mobile computer systems where reduced form factor and low power consumption are critical design objectives. With the PD6710, a complete PC Card solution with power-control logic can occupy less than 1.5 square inches (excluding the socket connector). With the PD6722, a complete dual-socket PC Card solution with power-control logic can occupy less than 2 square inches (excluding socket connectors).

The chips employ energy-efficient mixed-voltage technology that can reduce system power consumption by over 50 percent. The chips also provide: a Low-Power Dynamic mode, which automatically stops the internal clock during periods of card inactivity; a software-controlled Suspend mode, which dramatically reduces power by disabling most of the internal circuitry and stopping data transactions to the PC Cards; and a hardware-controlled Super Suspend mode, which reduces current to the  $\mu$ A range.

Personal computer applications typically access PC Cards through a third-party socket/cardservices software interface. To assure full compatibility with industry-standard socket/cardservices software and PC Card applications, the register set in the PD6710 and PD6722 is a superset of the Intel<sup>®</sup> 82365SL register set.

The chips provide fully buffered PC Card interfaces, meaning that no external logic is required for buffering signals to/from the interface, and power consumption can be controlled by limiting signal transitions on the PC Card bus.

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The PD6710 or PD6722 may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, May 2001

\*Third-party brands and names are the property of their respective owners.

# int<sub>el</sub>。 Contents

| 1.0 | Proc                                          | duct Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9                                                                                                              |

|-----|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 2.0 | Gen                                           | eral Conventions                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11                                                                                                             |

|     | 2.1                                           | Numbers and Units                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11                                                                                                             |

| 3.0 | Pin l                                         | Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12                                                                                                             |

|     | 3.1<br>3.2<br>3.3<br>3.4                      | Pin Diagrams<br>Pin Description Conventions<br>Pin Descriptions<br>Power-On Configuration Summary                                                                                                                                                                                                                                                                                                                                                                               | 14<br>16                                                                                                       |

| 4.0 | Intro                                         | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                |

|     | 4.1<br>4.2<br>4.3                             | System Architecture4.1.1PC Card Basics4.1.2PD67XX Windowing Capabilities4.1.3PD67XX Functional Blocks4.1.4Interrupts4.1.5Alternate Functions of Interrupt Pins4.1.6General-Purpose Strobe Feature4.1.7Voltage Sense Pins4.1.8PD67XX Power Management4.1.9Socket Power Management Features4.1.10Write FIFO4.1.11Bus Sizing4.1.2Programmable PC Card Timing4.1.3DMA Mode Operation for the PD67224.1.14Selective Data Drive for I/O WindowsHost Access to RegistersPower-On Setup | 27<br>27<br>30<br>30<br>31<br>32<br>32<br>32<br>32<br>34<br>34<br>35<br>35<br>35<br>36<br>36<br>36<br>36<br>36 |

| 5.0 | Regi                                          | ister Description Conventions                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 39                                                                                                             |

| 6.0 | <b>Ope</b><br>6.1<br>6.2                      | ration Registers<br>Index<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                                               | 41                                                                                                             |

| 7.0 | Chip                                          | o Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 46                                                                                                             |

|     | 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7 | Chip Revision<br>Interface Status<br>Power Control<br>Interrupt and General Control<br>Card Status Change<br>Management Interrupt Configuration<br>Mapping Enable                                                                                                                                                                                                                                                                                                               | 47<br>48<br>51<br>52<br>54                                                                                     |

| 8.0 | I/O V                                         | Vindow Mapping Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 58                                                                                                             |

|     | 8.1<br>8.2                                    | I/O Window Control<br>System I/O Map 0–1 Start Address Low                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                |

|      | 8.3                         | System I/O Map 0–1 Start Address High                                                                         |    |  |  |

|------|-----------------------------|---------------------------------------------------------------------------------------------------------------|----|--|--|

|      | 8.4                         | System I/O Map 0–1 End Address Low                                                                            |    |  |  |

|      | 8.5<br>8.6                  | System I/O Map 0–1 End Address High<br>Card I/O Map 0–1 Offset Address Low                                    |    |  |  |

|      | 8.7                         | Card I/O Map 0–1 Offset Address High                                                                          |    |  |  |

| 9.0  |                             | ory Window Mapping Registers                                                                                  |    |  |  |

|      | 9.1                         | System Memory Map 0–4 Start Address Low                                                                       |    |  |  |

|      | 9.2                         | System Memory Map 0–4 Start Address High                                                                      |    |  |  |

|      | 9.3                         | System Memory Map 0-4 End Address Low                                                                         |    |  |  |

|      | 9.4                         | System Memory Map 0–4 End Address High                                                                        |    |  |  |

|      | 9.5                         | Card Memory Map 0–4 Offset Address Low                                                                        |    |  |  |

|      | 9.6                         | Card Memory Map 0–4 Offset Address High                                                                       |    |  |  |

| 10.0 | Exte                        | nsion Registers                                                                                               |    |  |  |

|      | 10.1                        | Misc Control 1                                                                                                |    |  |  |

|      | 10.2                        | FIFO Control                                                                                                  |    |  |  |

|      | 10.3<br>10.4                | Misc Control 2<br>Chip Information                                                                            |    |  |  |

|      | 10.4                        | ATA Control                                                                                                   |    |  |  |

|      | 10.6                        | Extended Index                                                                                                |    |  |  |

|      | 10.7                        | Extended Data                                                                                                 | 77 |  |  |

|      |                             | 10.7.1 Data Mask 0–1                                                                                          |    |  |  |

|      |                             | 10.7.2 Extension Control 1 (PD6722 only, formerly DMA Control)                                                |    |  |  |

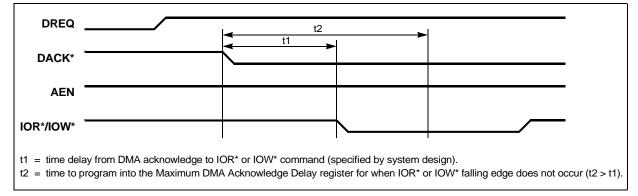

|      |                             | 10.7.3 Maximum DMA Acknowledge Delay (PD6722 only)<br>10.7.4 External Data (PD6722 only, Socket A, Index 2Fh) |    |  |  |

|      |                             | 10.7.5 External Data (PD6722 only, Socket A, Index 2Ph)                                                       |    |  |  |

|      |                             | 10.7.6 Extension Control 2 (PD6722 only)                                                                      |    |  |  |

| 11.0 | Timi                        | ng Registers                                                                                                  |    |  |  |

|      | 11.1                        | Setup Timing 0–1                                                                                              |    |  |  |

|      | 11.2                        | Command Timing 0–1                                                                                            |    |  |  |

|      | 11.3                        | Recovery Timing 0–1                                                                                           |    |  |  |

| 12.0 | ΑΤΑ                         | Mode Operation                                                                                                |    |  |  |

| 13.0 |                             | g GPSTB Pins for External Port Control<br>722 only)91                                                         |    |  |  |

|      | 13.1                        | Control of GPSTB Pins                                                                                         | 91 |  |  |

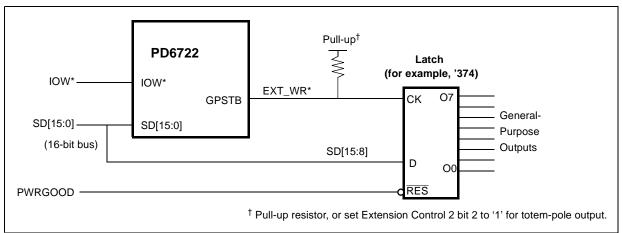

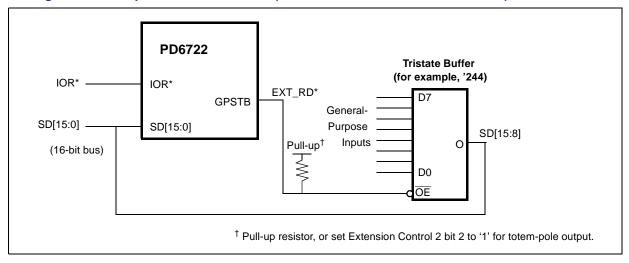

|      | 13.2                        | Example Implementations of GPSTB-Controlled Read and Write Ports                                              | 93 |  |  |

|      | 13.3                        | GPSTB in Suspend Mode                                                                                         | 94 |  |  |

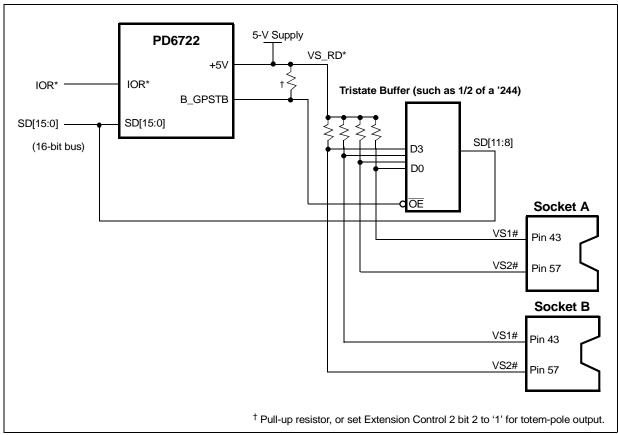

| 14.0 | VS1#                        | # and VS2# Voltage Detection                                                                                  | 95 |  |  |

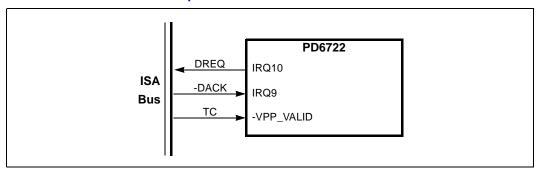

| 15.0 | DMA Operation (PD6722 only) |                                                                                                               |    |  |  |

|      | 15.1                        | DMA Capabilities of the PD6722                                                                                | 97 |  |  |

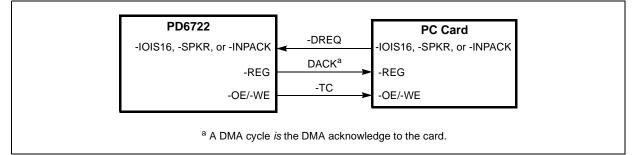

|      | 15.2                        | DMA-Type PC Card Cycles                                                                                       | 97 |  |  |

|      | 15.3                        | ISA Bus DMA Handshake Signal                                                                                  |    |  |  |

|      | 15.4                        | Configuring the PD6722 Registers for a DMA Transfer                                                           |    |  |  |

|      |                             | 15.4.1 Programming the DMA Request Pin from the Card                                                          |    |  |  |

|      |                             | 15.4.2 Configuring the Socket Interface for I/O                                                               |    |  |  |

|       | 15.4.3 Preventing Dual Interpretation of DMA Handshake Signals                                                                     | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 15.4.5 The DMA Transfer Process                                                                                                    | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       | 15.4.6 Terminal Count to Card at Conclusion of Transfer                                                                            | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Elect | trical Specifications                                                                                                              | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16.1  | Absolute Maximum Ratings                                                                                                           | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16.2  | DC Specifications                                                                                                                  | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16.3  | AC Timing Specifications                                                                                                           | 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

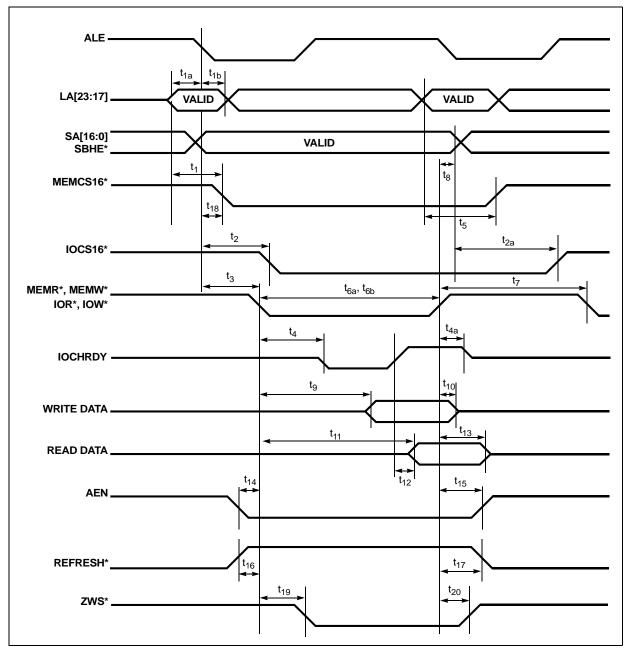

| 16.4  | ISA Bus Timing                                                                                                                     | 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       | 6                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 16.4.2 System Interrupt Timing                                                                                                     | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 16.4.5 PC Card Bus Timing Calculations                                                                                             | 109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Pack  | age Specifications                                                                                                                 | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

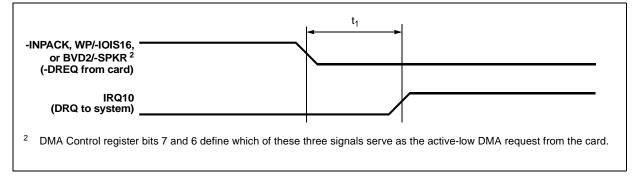

| 17.1  | 144-Pin LQFP Package                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

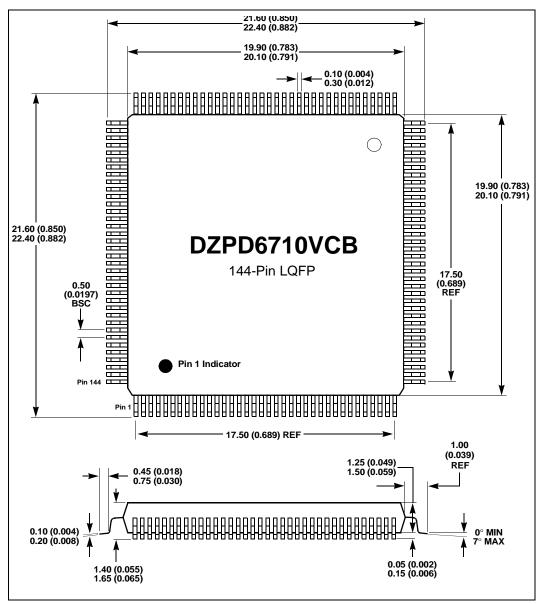

| 17.2  | 208-Pin MQFP Package                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

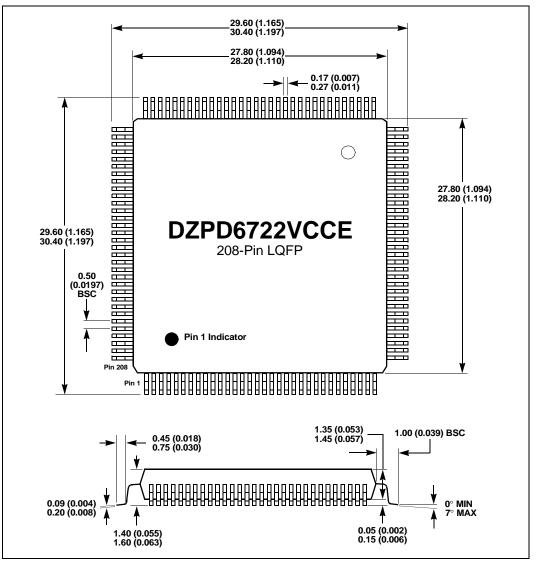

| 17.3  | 208-Pin LQFP Package                                                                                                               | 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

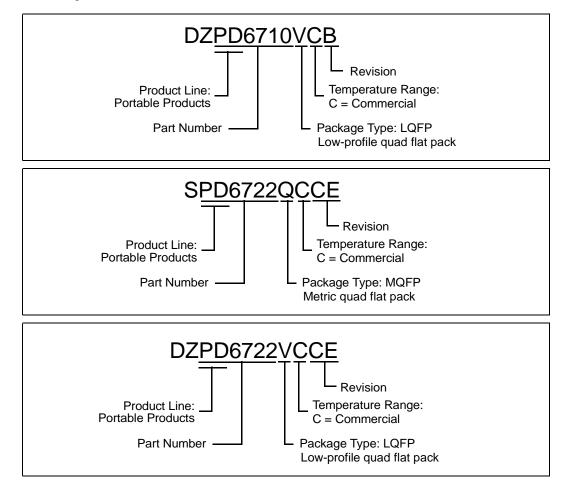

| Orde  | er Numbers Example                                                                                                                 | 124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Appe  | endix A                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 19.1  | Register Summary Tables                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 5 ,                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 19.2  |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 19.3  |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 19.4  |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 19.5  |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 19.6  | 5                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       |                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 16.1<br>16.2<br>16.3<br>16.4<br><b>Pack</b><br>17.1<br>17.2<br>17.3<br><b>Orde</b><br>19.1<br>19.2<br>19.3<br>19.4<br>19.5<br>19.6 | 15.4.5       The DMA Transfer Process.         15.4.6       Terminal Count to Card at Conclusion of Transfer.         Electrical Specifications.         16.1       Absolute Maximum Ratings.         16.2       DC Specifications.         16.3       AC Timing Specifications .         16.4       ISA Bus Timing.         16.4.1       Reset Timing .         16.4.2       System Interrupt Timing .         16.4.3       General-Purpose Strobe Timing (PD6722 only).         16.4.4       Input Clock Specification .         16.4.5       PC Card Bus Timing Calculations.         16.4.5       PC Card Bus Timing Calculations.         16.4.5       PC Card Bus Timing Calculations.         17.1       144-Pin LQFP Package.         17.2       208-Pin MQFP Package.         17.3       208-Pin LQFP Package.         17.3       208-Pin LQFP Package.         17.3       208-Pin LQFP Package.         17.3       208-Pin LQFP Package.         17.4       144-Pin LQFP Package.         17.5       208-Pin LQFP Package.         17.6       208-Pin LQFP Package.         17.7       208-Pin LQFP Package.         19.1       Operation Registers.         19.2 |

### **Figures**

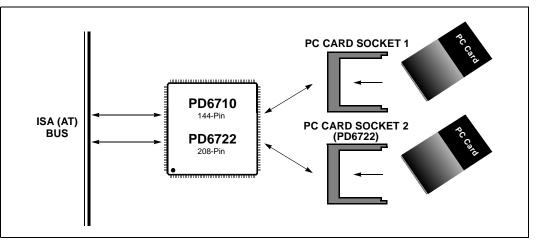

| 1  | System Block Diagram                                             | 10 |

|----|------------------------------------------------------------------|----|

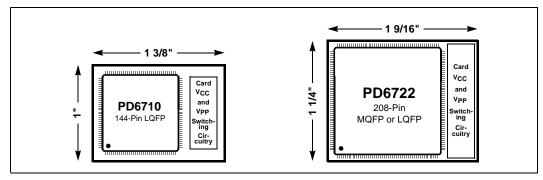

| 2  | PC Card Controller Form Factor                                   | 10 |

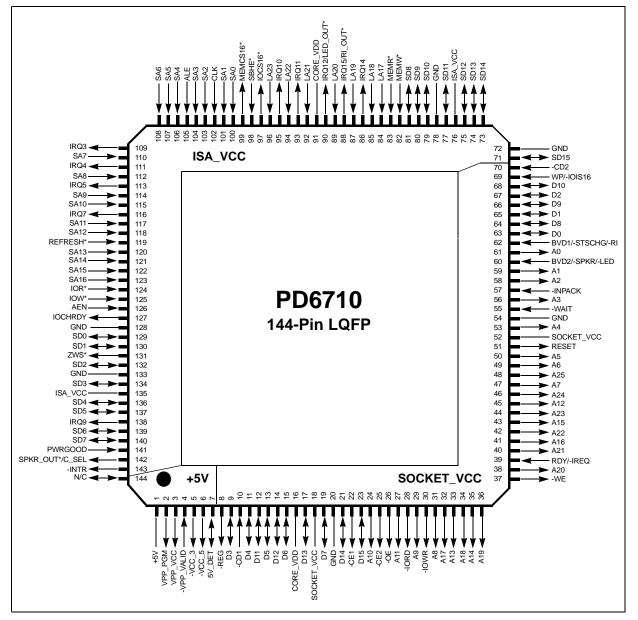

| 3  | PD6710 Pin Diagram                                               | 13 |

| 4  | PD6722 Pin Diagram                                               |    |

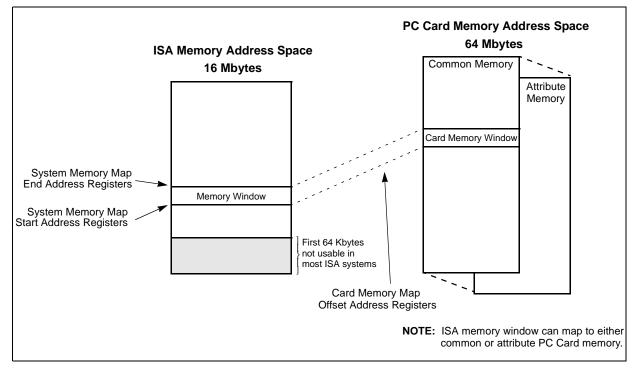

| 5  | Memory Window Organization                                       | 29 |

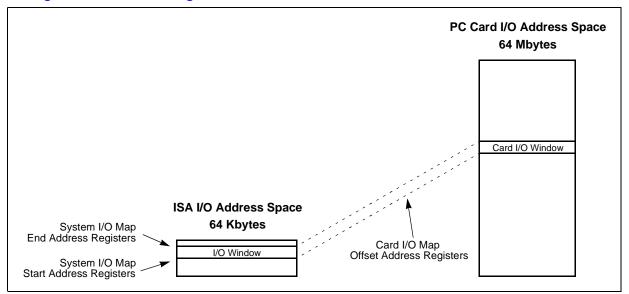

| 6  | I/O Window Organization                                          | 29 |

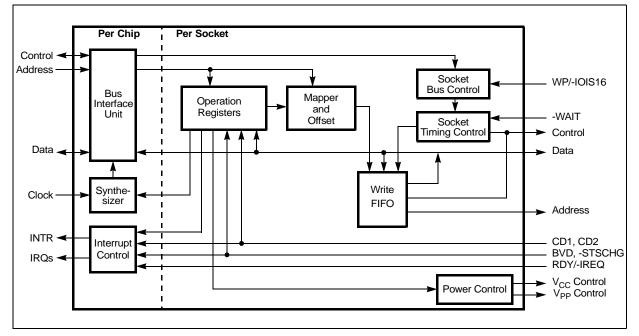

| 7  | Functional Block Diagram                                         | 30 |

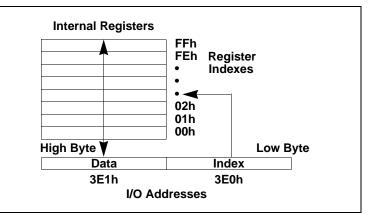

| 8  | Indexed 8-Bit Register Structure                                 | 37 |

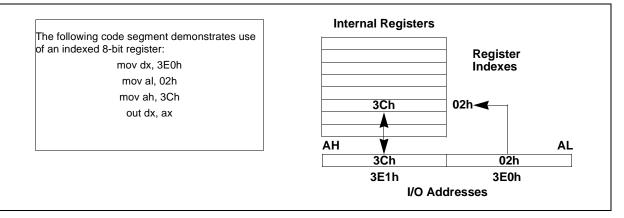

| 9  | Indexed 8-Bit Register Example                                   | 37 |

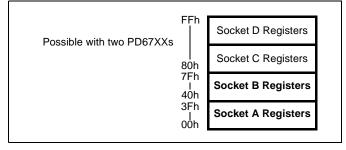

| 10 | Device/Socket/Register Index Space                               | 42 |

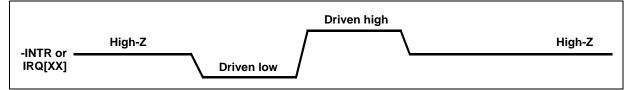

| 11 | Pulse Mode Interrupts                                            |    |

| 12 | Selection of Acknowledge Time-out Interval                       | 80 |

| 13 | Example GPSTB Write Port (Extension Control 2 bits 4:3 are '10') | 93 |

| 14 | Example GPSTB Read Port (Extension Control 2 bits 4:3 are '01')  | 93 |

| 15 | VS1# and VS2# Sensing on a PD6722                                |    |

|    | (Socket B Extension Control 2 bit 3 is '1')                      | 96 |

| 16 | DMA Handshake Connections to the ISA Bus                         |    |

|    | to Make the PD6722 DMA-Capable                                   |    |

| 17 | Card DMA Request and Acknowledge Handshake with Terminal Count   |    |

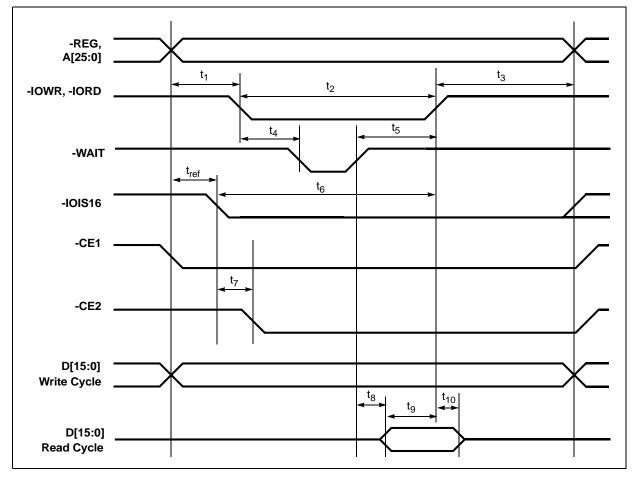

| 18 | Bus Timing — ISA Bus1                                            | 06 |

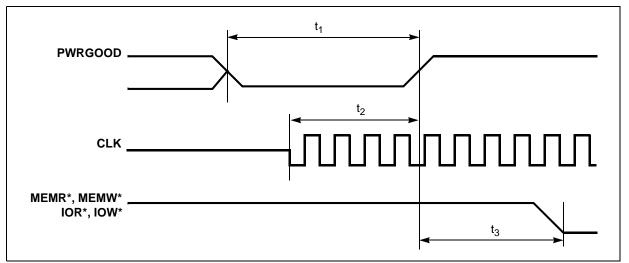

| 19 | Reset Timing 1                                                   |    |

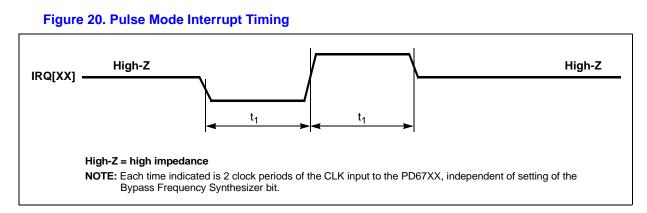

| 20 | Pulse Mode Interrupt Timing1                                     |    |

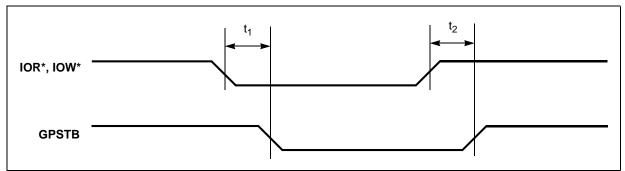

| 21 | General-Purpose Strobe Timing1                                   |    |

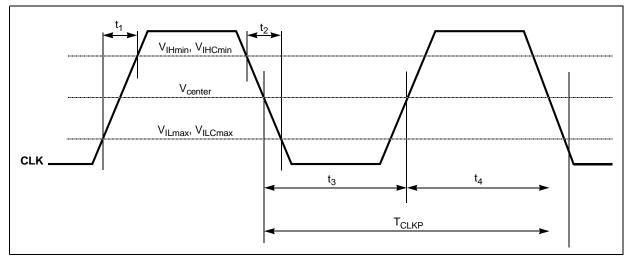

| 22 | Input Clock Specification1                                       |    |

| 23 | Memory Read/Write Timing1                                        | 11 |

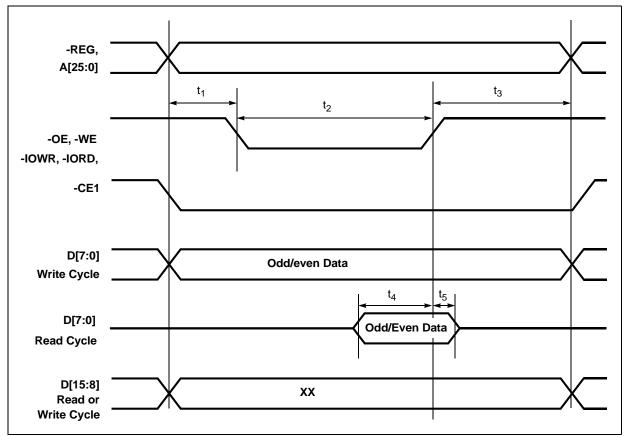

| 24 | Word I/O Read/Write Timing1                                      |    |

| 25 | PC Card Read/Write Timing When System Is 8-Bit (SBHE Tied High)1 | 14 |

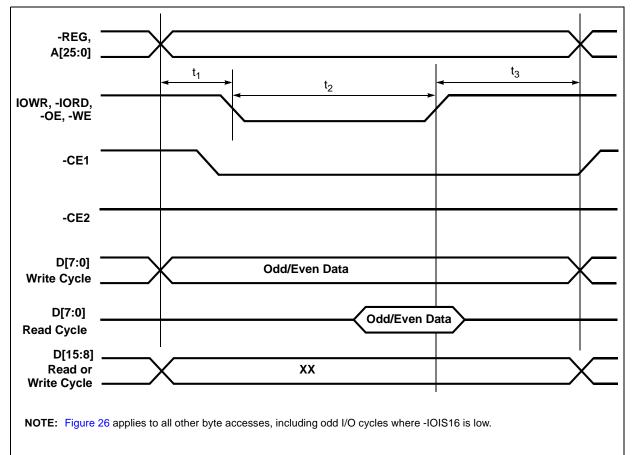

| 26 | Normal Byte Read/Write Timing1                                   |    |

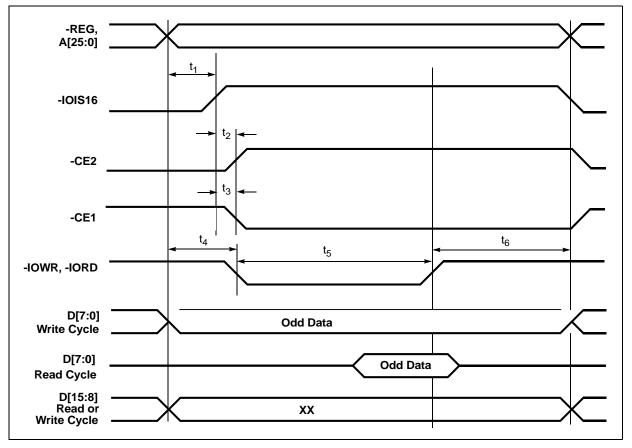

| 27 | 16-Bit System to 8-Bit I/O Card: Odd Byte Timing1                | 16 |

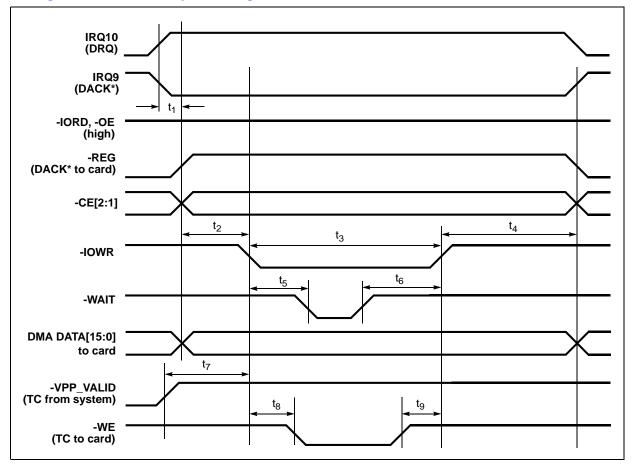

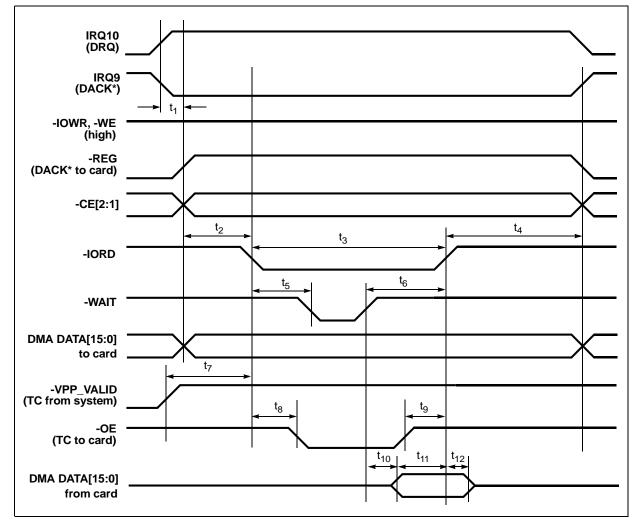

| 28 | DMA Read Cycle Timing1                                           | 17 |

| 29 | DMA Write Cycle Timing1                                          | 19 |

| 30 | DMA Request Timing1                                              | 20 |

|    |                                                                  |    |

### Tables

| 1  | ISA Bus Interface Pins                                     | 16  |

|----|------------------------------------------------------------|-----|

| 2  | Socket Interface Pins                                      | 20  |

| 3  | General-Purpose Strobe / Voltage Sense Pins                | 24  |

| 4  | Power Control Pins                                         | 24  |

| 5  | Power and Ground Pins                                      | 25  |

| 6  | Pin Usage Summary                                          | 25  |

| 7  | Chip Configuration at Power-up for Socket Support          |     |

| 8  | PD67XX Power-Management Modes                              | 34  |

| 9  | 16-Bit Mode Operation                                      | 35  |

| 10 | 8-Bit Mode Operation                                       | 35  |

| 11 | Index Registers                                            |     |

| 12 | Enabling of Socket Power Controls                          |     |

| 13 | Enabling of Outputs to Card Socket                         | 49  |

| 14 | Maximum DMA Acknowledge Delay Register Values              | 80  |

| 15 | Functions of Socket A External Data Register               | 81  |

| 16 | Functions of Socket B External Data Register (PD6722 only) | 82  |

| 17 | ATA Pin Cross-Reference                                    | 88  |

| 18 | Registers for Control and Data of GPSTB Pins               | 91  |

| 19 | Four Card Cycle Types for DMA-Type PC Card Interface       | 97  |

| 20 | General DC Specifications                                  |     |

| 21 | PC Card Bus Interface DC Specifications                    | 101 |

| 22 | ISA Bus Interface DC Specifications                        |     |

| 23 | Power Control Interface (+5V Powered) DC Specifications    |     |

| 24 | Operating Current Specifications                           | 103 |

| 25 | List of AC Timing Specifications                           |     |

| 26 | ISA Bus Timing                                             | 104 |

| 27 | Reset Timing                                               | 107 |

| 28 | Pulse Mode Interrupt Timing                                |     |

| 29 | General-Purpose Strobe Timing                              | 108 |

| 30 | Input Clock Specification                                  | 108 |

| 31 | Memory Read/Write Timing (Word Access)                     | 111 |

| 32 | Word I/O Read/Write Timing                                 | 112 |

| 33 | PC Card Read/Write Timing when System Is 8-Bit             | 113 |

| 34 | Normal Byte Read/Write Timing                              | 114 |

| 35 | 16-Bit System to 8-Bit I/O Card: Odd Byte Timing           | 115 |

| 36 | DMA Read Cycle Timing (PD6722 only)                        |     |

| 37 | DMA Write Cycle Timing (PD6722 only)                       | 118 |

| 38 | DMA Request Timing (PD6722 only)                           |     |

|    |                                                            |     |

### **Revision History**

| Revision | Date     | Description      |

|----------|----------|------------------|

| 1.0      | May 2001 | Initial release. |

### 1.0 **Product Features**

- Single-chip PC Card (PCMCIA) controllers

- Direct connection to ISA (PC AT) bus and one or two PC Card sockets

- Compliant with PC Card Standard, PCMCIA 2.1, and JEIDA 4.1

- 82365SL-compatible register set, ExCA™-compatible

- Automatic Low-Power Dynamic mode for lowest active power consumption

- Programmable Suspend mode

- Hardware-enabled Super Suspend mode

- Five programmable memory windows per socket and two programmable I/O windows per socket

- Programmable card access cycle timing

- 8- or 16-bit system bus interface

- 8- and 16-bit PC Card interface support

- PCMCIA-ATA and ture-IDE disk interface support

- DMA support (PD6722)

- Card-voltage sense support

- PC Card activity indicator

- Mixed-voltage operation (3.3/5.0 V)

- Single-socket interface: 144-pin LQFP for smallest form factor (PD6710)

- Dual-socket interface: 208-pin MQFP or LQFP (PD6722)

| Embedded and Mobile Systems Design Priorities | Supporting Features                                                                                                                                                                             |  |  |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Small Form Factor                             | <ul> <li>Single-chip solutions</li> <li>No external buffers for host or socket</li> <li>Efficient board layout</li> </ul>                                                                       |  |  |

| Minimum Power Consumption                     | <ul> <li>Automatic Low-Power Dynamic mode</li> <li>Hardware- and software-controlled Suspend<br/>modes</li> <li>Mixed-voltage operation</li> </ul>                                              |  |  |

| High Performance                              | <ul> <li>Write cache</li> <li>Programmable timing supports more cards, faster reads and writes</li> <li>Automatic bus sizing for 8- or 16-bit</li> <li>DMA available with the PD6722</li> </ul> |  |  |

| Hardware and Software Compatibility           | <ul> <li>Compliant with PC Card Standard, PCMCIA 2.1,<br/>and JEIDA 4.1</li> <li>82365SL A-step register-compatible,<br/>ExCA<sup>™</sup>-compatible</li> </ul>                                 |  |  |

Figure 1. System Block Diagram

Figure 2. PC Card Controller Form Factor

### 2.0 General Conventions

The following general conventions apply to this document.

Throughout this document, PD67XX means PD6710 and PD6722.

Bits within words and words within various memory spaces are generally numbered with a 0 (zero) as the least-significant bit or word. For example, the least-significant bit of a byte is bit 0, while the most-significant bit is bit 7.

In addition, number ranges for bit fields and words are presented with the most-significant value first. Thus, when discussing a bit field within a register, the bit number of the most-significant bit is written first, followed by a colon (:) and then the bit number of the least-significant bit; as in, bits 7:0.

In this document, the names of the PD67XX internal registers are boldfaced. For example, **Chip Revision** and **Power Control** are register names. The names of bit fields are written with initial uppercase letters. For example, Card Power On and Battery Voltage Detect are bit field names.

### 2.1 Numbers and Units

The unit *Kbyte* designates 1024 bytes (2<sup>10</sup>). The unit *Mbyte* designates 1,048,576 bytes (2<sup>20</sup>). The unit *Gbyte* designates 1,073,741,824 bytes (2<sup>30</sup>). The unit *Hz* designates hertz. The unit *kHz* designates 1000 Hz. The unit *MHz* designates 1,000,000 Hz. The unit *ms* designates millisecond. The unit  $\mu$ s designates microsecond. The unit *ns* designates nanosecond. The unit *mA* designates milliampere. The unit *V* immediately following a number designates volt.

Hexadecimal numbers are presented with all letters in uppercase and a lowercase *h* appended. For example, *14h* and *03CAh* are hexadecimal numbers.

Binary numbers are enclosed in single quotation marks when in text. For example, '11' is a binary number.

Numbers not appended with an *h* nor enclosed by single quotation marks are decimal.

In addition, a capital letter X is used within numbers to indicate digits ignored by the PD67XX within the current context. For example, '*101XX01*' is a binary number with bits 3:2 ignored.

### 3.0 Pin Information

The PD6710 is available in a 144-pin VQFP (very tight-pitch quad flat pack) component package and the PD6722 is available in either a 208-pin PQFP (plastic quad flat pack) component package or a 208-pin VQFP component package. The interface pins can be divided into five groups:

- ISA (or ISA-like) bus interface pins

- PC Card socket interface pins (one or two sets)

- General-purpose strobe / voltage sense pins

- Power control pins

- Power and ground pins

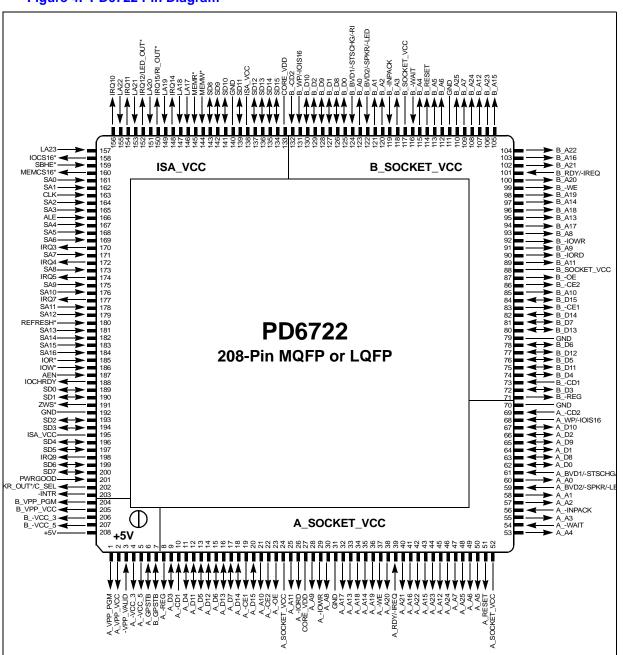

Refer to Figure 3 for the PD6710 and Figure 4 for the PD6722 pin diagrams. The pin assignments for the groups of interface pins are shown in Table 1 through Table 5.

### 3.1 Pin Diagrams

#### Figure 4. PD6722 Pin Diagram

### 3.2 Pin Description Conventions

The following conventions apply to the pin description tables in "Pin Descriptions" on page 16:

• A dash (-) at the beginning of a pin name indicates an active-low signal for the PC Card bus.

- An asterisk (\*) at the end of a pin name indicates an active-low signal for the ISA bus or that is a general interface for the PD67XX.

- Pins marked with a dagger (†) in the pin description tables can be switched between CMOS and TTL input levels when CORE\_VDD is powered at 5 volts. All other pins use CMOS input levels when CORE\_VDD is powered at 5 volts and TTL input levels when powered at 3.3 volts.

- A pin name ending in bracketed digits separated by a colon [n:n] indicates a multi-pin bus.

- The pin number (Pin Number) column indicates the package pin that carries the listed signal. Note that multi-pin buses are listed with the first pin number corresponding to the mostsignificant bit of the bus. For example, pin numbers 123:120, 118, 117, 115, 114, 112, 110, 108:106, 104, 103, 101, and 100 are associated with ISA Bus Address Input and Data Input/ Output pins SA[16:0] and indicate that:

- SA16 is pin 123

- SA15 is pin 122

- SA0 is pin 100

- The quantity (Qty.) column indicates the number of pins used (per socket where applicable).

- The I/O-type code (I/O) column indicates the input and output configurations of the pins on the PD67XX. The possible types are defined below.

- The power-type code (Pwr.) column indicates the output drive power source for an output pin or the pull-up power source for an input pin on the PD67XX. The possible types are defined below.

| I/O Type | Description                             |

|----------|-----------------------------------------|

| I        | Input pin                               |

| 0        | Constant-driven output pin              |

| I/O      | Input/output pin                        |

| O-OD     | Open-drain output pin                   |

| O-TS     | Tristate output pin                     |

| -PU      | An internal pull-up resistor is present |

| GND      | Ground pin                              |

| PWR      | Power pin                               |

| Power Type | Output or Pull-up Power Source                                                                           |

|------------|----------------------------------------------------------------------------------------------------------|

| 1          | +5V: powered from a 5.0-volt power supply<br>in most systems (see description of +5V pin<br>in Table 5)  |

| 2          | A_SOCKET_VCC: powered from the Socket A $V_{CC}$ supply connecting to PC Card pins 17 and 51 of Socket A |

| Power Type | Output or Pull-up Power Source                                                                                                             |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 3          | B_SOCKET_VCC: powered from the Socket B $V_{CC}$ supply connecting to PC Card pins 17 and 51 of Socket B                                   |

| 4          | ISA_VCC: powered from the ISA bus power supply                                                                                             |

| 5          | CORE_VDD: usually powered from the<br>lowest available power supply for lowest<br>power consumption, which in most systems<br>is 3.3 volts |

*Note:* All pin inputs are referenced to CORE\_VDD, independent of their output supply voltage.

The drive-type (Drive) column describes the output drive-type of the pin (see DC specifications in "Electrical Specifications" on page 101 for more information). Note that the drive type listed for an input-only (I) pin is not applicable (–).

### 3.3 Pin Descriptions

| Table 1. | ISA Bus | <b>Interface Pins</b> | (Sheet 1 | of 4) |

|----------|---------|-----------------------|----------|-------|

|----------|---------|-----------------------|----------|-------|

| Pin Name  | Description                                                                                                                                                                                                                  | Pin Number                                                                     |                                                                                | Qty. |     | Durr | Deire |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------|-----|------|-------|

|           | Description                                                                                                                                                                                                                  | PD6710                                                                         | PD6722                                                                         | Qty. | I/O | Pwr. | Drive |

| LA[23:17] | <b>ISA Bus Address Input</b> : Connect to ISA signals LA[23:17] or, for systems limited to 1-Mbyte address space, tie ALE high, ground LA[23:20] and connect LA[19:17] to ISA signals SA[19:17].                             | 96, 94, 92, 89,<br>87, 85, 84                                                  | 157, 155, 153,<br>151, 149, 147,<br>146                                        | 7    | I   | 4    | -     |

| SA[16:0]  | ISA Bus Address Input: Connect to ISA signals SA[16:0].                                                                                                                                                                      | 123:120, 118,<br>117, 115, 114,<br>112, 110,<br>108:106, 104,<br>103, 101, 100 | 184:181, 179,<br>178, 176, 175,<br>173, 171,<br>169:167, 165,<br>164, 162, 161 | 17   | I   | 4    | -     |

| SD[15:0]  | ISA Bus Data Input/Output: These pins are<br>used to transfer data during a memory or I/O<br>cycle. Connect to ISA signals SD[15:0].<br>For 8-bit system buses, leave SD[15:8]<br>unconnected.                               | 71, 73–75, 77,<br>79–81, 140,<br>139, 137, 136,<br>134, 132, 130,<br>129       | 134–137, 139,<br>141–143, 200,<br>199, 197, 196,<br>194, 193, 190,<br>189      | 16   | I/O | 4    | 12 mA |

| SBHE*     | Byte High Enable: This input is used in<br>conjunction with SA[0] to specify the width<br>and alignment of a data transfer. Connect to<br>ISA signal SBHE*.<br>For 8-bit system buses, pull up connect to<br>ISA_VCC supply. | 98                                                                             | 159                                                                            | 1    | I   | 4    | _     |

| IOR*      | <b>I/O Read</b> : This input indicates that a host<br>I/O read cycle is occurring. Connect to ISA<br>signal IOR*.                                                                                                            | 124                                                                            | 185                                                                            | 1    | I   | 4    | -     |

| IOW*      | <b>I/O Write</b> : This input indicates that a host I/O write cycle is occurring. Connect to ISA signal IOW*.                                                                                                                | 125                                                                            | 186                                                                            | 1    | Ι   | 4    | _     |

| Table 1. | <b>ISA Bus</b> | <b>Interface Pins</b> | (Sheet 2 of 4) |

|----------|----------------|-----------------------|----------------|

|          |                |                       |                |

| Dia Mara | Description                                                                                                                                                                                                                                                                                                                                                              | Pin N  | 0      |      | Dura | Duine |       |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|------|------|-------|-------|--|

| Pin Name | Description                                                                                                                                                                                                                                                                                                                                                              | PD6710 | PD6722 | Qty. | I/O  | Pwr.  | Drive |  |

| MEMR*    | <b>Memory Read</b> : This input indicates that a host memory read cycle is occurring. Connect to ISA signal MEMR*.                                                                                                                                                                                                                                                       | 83     | 145    | 1    | I    | 4     | _     |  |