# Am8052

Alphanumeric CRT Controller (CRTC)

#### FINAL

#### DISTINCTIVE CHARACTERISTICS

- On-chip DMA capability, operating via linked-list data structures

- Three on-chip row buffers, each 132 characters by 20 bits support split-screen smooth-scrolling

- General-purpose microprocessor interface. Compatible with 8086, Z8000\*, and 68000 CPUs.

- Smooth-scrolling capability, with minimal CPU overhead

- Multiple vertical and horizontal screen divisions, with optional smooth-scrolling within a window

- Character attributes (12 bits) can be invoked on a character-by-character basis

- Flexible vertical and horizontal sync control

- Flexible blanking for control of front and back-porch positions

- Non-interlace, repeat field interlace, and video interlace options

- High resolution 5-bit character generator row addressing

- 16M-byte system memory addressing capability

- Programmable blink options for cursors and characters

#### **GENERAL DESCRIPTION**

The Am8052 CRT Controller (CRTC) is a general-purpose interface device for raster scan CRT displays. The CRTC provides efficient manipulation of complex character formats and screen structures to allow sophisticated text display without undue CPU overhead.

The CRTC is a register-oriented product that is fully user programmable. The timing definition and operating modes are initialized by the host CPU. Display formats are real-time programmable on a row-by-row basis. Character attributes are specified on a character or field basis, and are interpreted and acted upon during active display of a character row.

Internal DMA capability assures efficient transfer of display information to the three on-chip line buffers. These three line buffers prevent screen flashing in split-screen smooth-scrolling operations. The DMA loads the line buffers via linked list data blocks which facilitate easier editing and text composition.

The Am8052, in conjunction with the Am8152A bipolar Video System Controller (VSC), allows for the flexible assignment of visual attributes. The twelve attribute bits stored in the Am8052 include superscript, subscript, blink, highlight, reverse, underline, strike through and cursor. Both character and cursor can be made to blink at three different rates, and the blink duty cycle is programmable. Further flexibility is achieved by the Am8152A, which allows the video stream to be manipulated by selection of background and foreground as well as background/foreground reversal

The Am8052 and Am8152A combination also supports proportional spacing, text justification, and double-width characters.

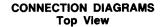

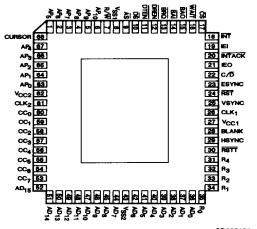

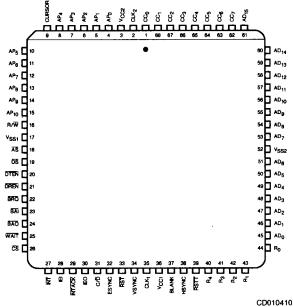

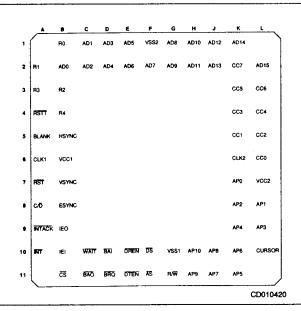

The Am8052 CRTC is assembled in 68-pin plastic leaded chip carrier and ceramic leadless chip carrier packages, while the bipolar Am8152A VSC is assembled in a 48-pin DIP and 68-pin Plastic Leaded Chip Carrier. These interface circuits are available as a chip-set for high performance CRT applications.

#

Publication # Rev. Amendment

03684 D /0

Issue Date: December 1986

Am8052

CD005191

#### 68-Pin PLCC Generic Outline

## LOGIC SYMBOL

#### ORDERING INFORMATION

#### Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: **A. Device Number**

- B. Speed Option (if applicable)

- C. Package Type

- D. Temperature Range

- E. Optional Processing

# Valid Combinations AM8052-4 AM8052-6 JC, LC AM8052-8 JC, LC JC

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

#### **ORDERING INFORMATION** (Cont'd.)

#### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. CPL (Controlled Products List) products are processed in accordance with MIL-STD-883C, but are inherently non-compliant because of package, solderability, or surface treatment exceptions to those specifications. The order number (Valid Combination) for APL products is formed by a combination of: A. Device Number

- B. Speed Option (if applicable)

- C. Device Class

- D. Package Type

- E. Lead Finish

| Valid Combinations  |  |  |  |  |  |

|---------------------|--|--|--|--|--|

| AM8052-6 /BUC, /BZC |  |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

#### **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

#### PIN DESCRIPTION

#### V<sub>SS1</sub>, V<sub>SS2</sub> Ground

V<sub>CC1</sub>, V<sub>CC2</sub> +5-V Power Supply

#### CLK<sub>1</sub> Timing Clock

The Clock 1 signal controls and times the DMA and peripheral portion of the CRTC. In proportional spacing applications, where CLK<sub>2</sub> is variable, CLK<sub>1</sub> must be used to time the horizontal and vertical sync rates. CLK<sub>1</sub> is non-TTL compatible, and is normally driven by the Am8152A VSC.

#### CLK<sub>2</sub> Display Clock

The Clock 2 signal is used to time character accesses from the CRTC line buffers. In applications which do not use proportional spacing,  $CLK_2$  is fixed in frequency and can be used to time horizontal and vertical sync rates, allowing  $CLK_1$ , the system clock, to be unrelated and asynchronous to the display timing.  $CLK_2$  is non-TTL compatible and should be driven by the VSC.

# AD<sub>0</sub>-AD<sub>15</sub> Address/Data Bus (Input/Output, Three-State)

The Address/Data Bus is a multiplexed, bidirectional, hightrue, three-state bus. The presence of addresses is defined by the  $\overline{AS}$  signal, and the presence of data is defined by the  $\overline{DS}$  signal. When the CRTC is in control of the system via its internal DMA capability, it controls the AD Bus; when the CRTC is idle, the CPU or other external devices control the AD Bus and may use it to access the internal registers of the CRTC. The high-order 8-bit memory address is output on the AD $_0$  - AD $_7$  lines. Interrupt vector information is also output in the AD $_0$  - AD $_7$  lines.

# AS Address Strobe (Input/Output; Three State, Active LOW)

Address Strobe is a bidirectional, active-LOW, three-state signal. When the CRTC is in the slave mode and the bus master is accessing the CRTC's internal registers,  $\overline{AS}$  can be used to optionally latch  $\overline{CS}$  and  $C/\overline{D}$  information during the first part of the transaction. During a DMA operation when the CRTC is in control of the system,  $\overline{AS}$  is an output generated by the CRTC to indicate a valid address on the bus. In the slave mode, the  $\overline{AS}$  signal may be asynchronous to CLK1.

# DS Data Strobe (Input/Output; Three State, Active LOW)

Data Strobe is a bidirectional, active-LOW, three-state signal. When the CRTC is in the slave mode and the external system is transferring information to or from it,  $\overline{DS}$  is a timing input used by the CRTC to move data to or from the AD Bus. In the slave mode, the  $\overline{DS}$  signal may be asynchronous to CLK<sub>1</sub>. During a DMA operation when the CRTC is in control of the system,  $\overline{DS}$  is an output generated by the CRTC and used by the system to move data onto the AD Bus.

#### CS Chip Select (Input, Active LOW)

The  $\overline{\text{CS}}$  input is an active-LOW signal used by the host processor to select the CRTC for a slave transfer.

#### WAIT Wait (Input, Active LOW)

The WAIT input is an active-LOW signal used to stretch the  $\overline{DS}$  strobe whenever the CRTC has access to the host's bus for data transfer. The status of the  $\overline{WAIT}$  signal is sampled on the falling edge CLK<sub>1</sub> during t<sub>2</sub> or t<sub>W</sub>.

#### R/W Read/Write (Input/Output, Three State)

Read/Write is a bidirectional, three-state signal indicating the data direction for the bus transaction under way, and remains stable for the length of the bus cycle. When CS input is active, Read (HIGH) indicates that the system is requesting data from the CRTC and Write (LOW) indicates

that the system is presenting data to the CRTC. On the other hand, during a DMA operation when the CRTC is in control of the system,  $R/\overline{W}$  is an output generated by the CRTC, with Read indicating that data is being requested by the CRTC from the addressed memory location and Write indicating that the CRTC is driving a high-order address to an external latch.

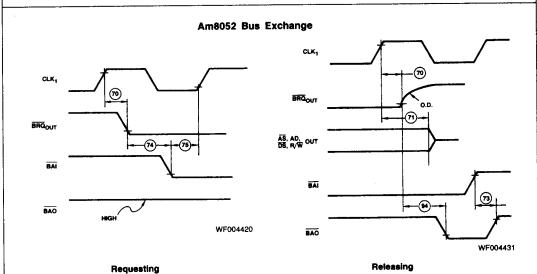

#### BRQ Bus Request (input/Output, Three State)

When the CRTC requires use of the bus for DMA activity, the  $\overline{\text{BRQ}}$  line is driven LOW. It remains LOW until it has ceased using the bus.

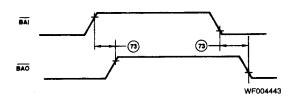

#### BAI Bus Acknowledge In (Input, Active LOW)

Bus Acknowledge In is an active-LOW input. When the CRTC requires host bus access and has successfully pulled its BRQ pin LOW, a BAI-LOW input signifies that the CRTC has obtained bus mastership after having internally synchronized its BAI active-LOW input for two clock periods of CLK<sub>1</sub>. The synchronization is required to alleviate metastable problems. When the CRTC does not require host bus access, the BAI input ripples to the BAO. Forcing BAI HIGH will cause the Am8052 to relinquish the bus.

#### CURSOR Cursor (Output)

This pin is the cursor output indicator.

#### ESYNC External Sync (Input)

This pin is the external synchronization input line. If the ES bit in the mode register is set, the vertical frame scan will commence after the rising edge of ESYNC.

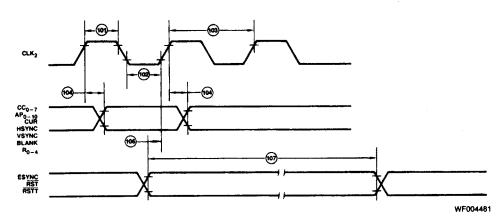

#### HSYNC Horizontal Sync (Output, Active HIGH)

HYSNC is an active-HIGH output used to cause horizontal retrace of the CRT's electron beam. The output is held active LOW while the CRTC is reset to prevent unknown synchronization to the CRT which may cause damage to high bandwidth tubes. Note that this pin can also be initialized as Horizontal Drive.

#### VSYNC Vertical Sync (Output, Active HIGH)

VSYNC is an active-HIGH output used to cause vertical retrace of the CRT's electron beam. VSYNC can be optionally synchronized by the ESYNC input. VSYNC is held LOW while the CRTC is reset to prevent damage to the CRT.

#### BLANK Blank Video (Output, Active HIGH)

BLANK is an active-HIGH output. It serves to blank out inactive display areas of the CRT. The output is held active while the CRTC is reset.

#### R<sub>0</sub>-R<sub>4</sub> Row Control (Output, Active HIGH)

R<sub>0</sub>-R<sub>4</sub> outputs are active HIGH. These outputs represent the binary count of the active scan line being displayed. These outputs address the least significant address portion of an external character generator. The outputs are all held HIGH for those scan lines that do not carry active video during normal character or superscript/subscript display.

#### CCn-CC7 Character Code (Output, Active HIGH)

CC0-CC7 outputs are active HIGH. The 8-bit character port, CC0 - CC7, outputs eight bits of data stored in the character code section of the line buffer currently being displayed.

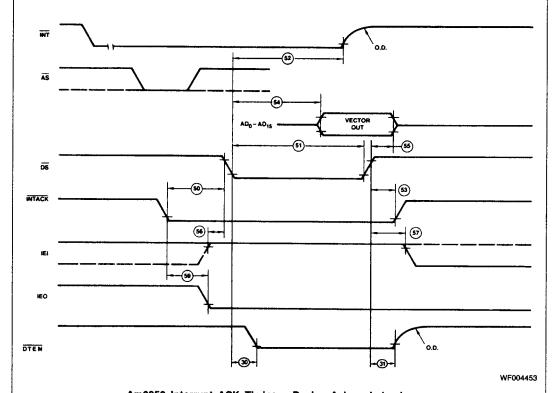

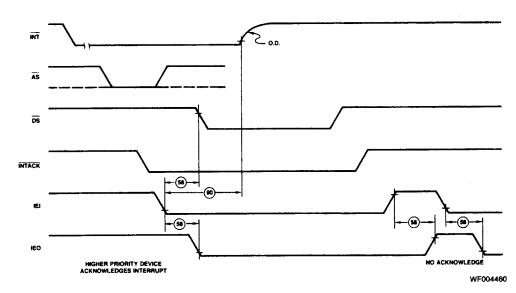

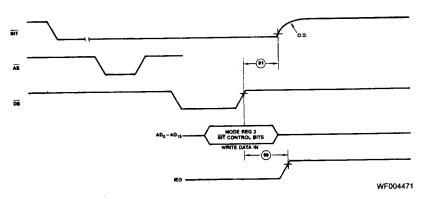

# INT Interrupt Request (Output; Open Drain, Active LOW)

This line is used to indicate an interrupt request to the host processor. It is driven LOW by the CRTC until an interrupt acknowledge is received on the INTACK pin or the relevant IP or IE bits in Mode Register 2 are reset.

#### INTACK Interrupt Acknowledge (Input, Active LOW)

When INTACK is driven LOW, the CRTC examines its IEI line to determine whether it has been granted an acknowledge by the CPU. It also starts priority resolution of the Daisy Chain. When  $\overline{DS}$  is active, the vector is placed on the bus if enabled.

#### IEI Interrupt Enable in (input)

A HIGH on IEI during an Interrupt Acknowledge cycle is regarded as an interrupt acknowledge to the CRTC. A LOW on IEI during Interrupt Acknowledge signifies that a higher priority interrupt on the dasity chain is being acknowledged.

#### IEO Interrupt Enable Out (Output)

IEO follows IEI during Interrupt Acknowledge if the CRTC has not made an interrupt request. IEO LOW disables lower priority devices from making interrrupt requests.

# DTEN, DREN Data Transmit Enable, Data Receive Enable (Outputs; Open-Drain, Active LOW)

Data Transmit Enable and Data Receive Enable are used to control bus transceivers external to the CRTC should they be required. When DTEN is LOW, the transceiver should transmit from the CRTC onto the bus. When DREN is LOW, the transceiver should receive data from the bus. DTEN and DREN are never LOW simultaneously.

#### C/D Command/Data (input)

C/ $\overline{D}$  is used by the CRTC when in the slave mode to determine if an I/O transaction with the host CPU is transferring a command or data. When the CRTC is not involved in an I/O transaction with the host, C/ $\overline{D}$  is disregarded.

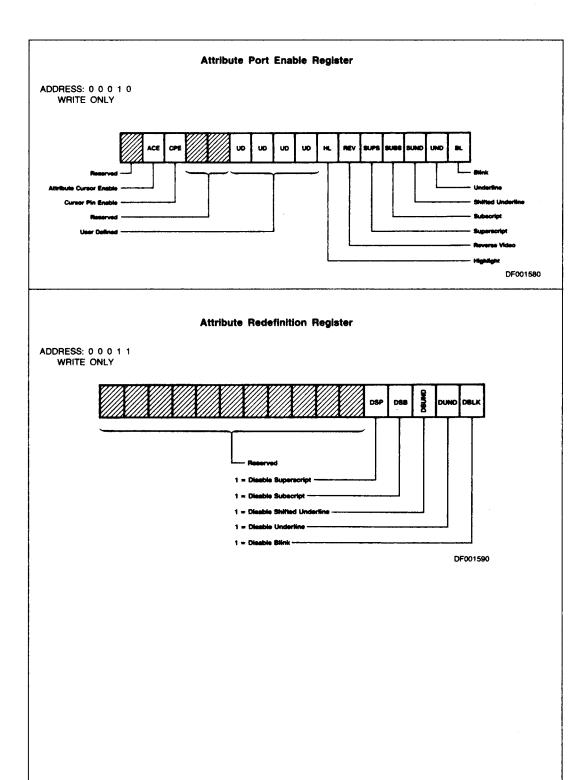

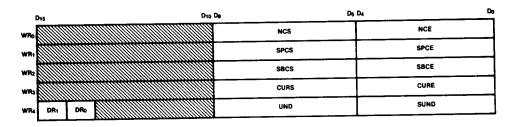

#### AP0-AP10 Attribute Port (Output)

These 11 lines are used to display character attribute information synchronous with each character and CLK<sub>2</sub>. During HSYNC, the row attribute information contained in the Row Redefinition Block is output on AP<sub>0</sub>-AP<sub>10</sub>.

#### BAO Bus Acknowledge Out (Output, Active LOW)

BAO output is forced active HIGH when the CRTC requests bus mastership; otherwise, the BAI input ripples out of the CRTC via the BAO output.

#### RST Reset (Input, Active LOW)

A LOW on this input for at least 5 clock cycles is interpreted as a reset signal. The effect of reset is to drive all CRTC bus signals into the high-impedance state, to clear all mode bits except bits 9 through 15 in MR2, and to force the CRTC into the slave mode.

#### RSTT Test Reset (Input)

For test use only. This pin is a "No Connect."

#### TABLE 1. CHARACTER ATTRIBUTE DESCRIPTION

| Attribute         | Effect                                                                                                                                                                 |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reverse           | - Causes the designated character to be displayed in reverse video.                                                                                                    |

| Highlight         | - Highlights the applicable character.                                                                                                                                 |

| Blink             | - Blinks the designated character at one of four programmed blink rates.                                                                                               |

| Underline         | - Underlines the designated character at a programmable scan line.                                                                                                     |

| Subscript         | - Causes the character to be displayed as a subscript.                                                                                                                 |

| Superscript       | - Causes the character to be displayed as a superscript.                                                                                                               |

| Shifted Underline | - A second underline.                                                                                                                                                  |

| Cursor            | - Causes the attribute or X-Y cursor to be displayed at the designated character position.                                                                             |

| Latched           | - Indicates that the attribute should be latched for all successive characters until changed.                                                                          |

| Ignore            | <ul> <li>Causes the CRTC to skip over the designated characters. Useful for embedded control characters and<br/>protected fields that do not get displayed.</li> </ul> |

| User Definable    | - Four attribute bits reserved for user definition.                                                                                                                    |

#### **FUNCTIONAL DESCRIPTION**

The block diagram of the Am8052 CRTC is shown on front cover. Communication with the external host system takes place over the 16-bit Address/Data Bus, AD<sub>0</sub>-AD<sub>15</sub>. Transfers over the AD Bus are controlled by the  $\overline{\text{CS}}$ , C/ $\overline{\text{D}}$ ,  $\overline{\text{AS}}$ ,  $\overline{\text{DS}}$ , and R/ $\overline{\text{W}}$  lines. When the CRTC is in the slave mode, these four bus control lines are inputs. When the CRTC is in the DMA mode,  $\overline{\text{AS}}$ , R/ $\overline{\text{W}}$  and  $\overline{\text{DS}}$  are outputs and control the external bus.

Following reset, the host system initializes the CRTC's timing and control registers, as well as one address pointer to the start of the display data location in the host memory. Following initialization and upon command from the host, the CRTC takes over bus control from the host and transfers display row control data, character code, and character attribute data. The CRTC requests the host bus by sampling the  $\overline{BRQ}$  line for activity; if the  $\overline{BRQ}$  line is HIGH, the CRTC drives it LOW, and also drives  $\overline{BAO}$  HIGH, to obtain priority over lower priority bus requestors. The on-chip DMA Controller circuit controls the data transfer and performs character data loading into the on-board line buffers.

The CRTC is real-time programmable on a character row-byrow basis through a row control data block fetched either from the host memory or from a dedicated display memory. The Row Control Block (RCB) contains address links to the next row's RCB, a character and attribute data address for the current row and other pertinent control functions for the row. Data from the RCB is transferred into the appropriate set of registers for active control of display and data fetch operations during the subsequent display of character row data. A Top of Page register contains the address of the Main Definition Block for the screen. The Main Definition Block, in turn, points to the first RCB. The character row data, comprised of character code and attribute (if the latter is specified), is fetched starting at the address and for the character length obtained from the RCB. The character code and its attribute consist of a 20-bit wide word which is stored, FIFO style, into one of the three on-board 132-character by 20-bit line buffers. Character attributes are on a character-by-character basis and are interpreted and acted upon by the CRTC during the active display period of the contents of a line buffer. Output lines CC0-CC7 form the transfer path for character code data to an external matrix type character generator, while the character attribute, after selective masking, is interpreted and combined with the resulting video.

Output lines  $R_0$ – $R_4$  exhibit the scan line number for the specific character being displayed, while the character row control logic allows alteration of the scan line number output at the  $R_0$ – $R_4$  lines to enable the display of normal superscript or subscript characters.

The HSYNC, VSYNC and BLANK output lines provide the CRT synchronization signals. The horizontal and vertical control logic blocks contain counters and host programmable registers for deriving the timing signals from either the CLK<sub>1</sub> or the CLK<sub>2</sub> input as well as an ESYNC input line for frame synchronization to an external source, such as the power line frequency. CLK<sub>2</sub> runs at the display character rate. It is a submultiple of the dot clock, whose frequency is determined by the Am8152A oscillator. CLK<sub>2</sub> controls the CRT synchronization lines HSYNC and VSYNC, as well as BLANK, and the rate of character output from the CRTC. CLK<sub>1</sub>, which may be asynchronous to CLK<sub>2</sub>, controls all DMA and related bus activity, associated with the CRTC. In proportional spacing applications, CLK<sub>1</sub> may be also used to time the synchronization signals.

#### **Character Attributes**

AVAC 1 stabs of / I to lot a bod

Character attributes affect various CRTC output signals and other operations on a character-by-character basis. Each attribute word occupies a 16-bit word in memory. Each character, however, need not invoke a new attribute.

Character attributes are stored in parallel with the corresponding character code in each line buffer.

The character attribute information which makes up the character attribute word is shown below:

AM- Hear definable

| AVV 15           | Lateried/ Uniateried | AVV7            | User delinable     |

|------------------|----------------------|-----------------|--------------------|

| AW <sub>14</sub> | Cursor               | AW <sub>6</sub> | Highlight          |

| AW <sub>13</sub> | Ignore               | AW <sub>5</sub> | Reverse            |

| AW <sub>12</sub> | Reserved             | AW <sub>4</sub> | Superscript        |

| AW11             | Reserved             | AW <sub>3</sub> | Subscript          |

| AW <sub>10</sub> | User definable       | AW <sub>2</sub> | Shifted Underline/ |

| AW <sub>9</sub>  | User definable       | _               | Strike Through     |

| AW <sub>8</sub>  | User definable       | AW <sub>1</sub> | Underline          |

| -                |                      | AW <sub>0</sub> | Blink              |

|                  |                      |                 |                    |

#### Latched/Unlatched

When this bit is set to 1 ("latched"), the attribute information applies to all characters following the character that invoked the attribute word. Only the presence of a further latched attribute word cancels the effect of a previous latched attribute word. If the Latched/Unlatched bit is set to 0 ("unlatched"), then the attribute information only applies to the character that invoked the attribute word. All successive characters are modified by the latched attribute information that was valid prior to the unlatched attribute word. The Latched/Unlatched bit is not output to the Attribute Port. The initial state of the latched attribute value is undefined. At the start of any horizontal line, the latched attribute information is the same as at the end of the previous line, unless changed by a further latched attribute.

#### Cursor

If this bit is set, then a cursor is displayed at the affected character position(s), dependent upon the mode of the cursor display logic. See the section on cursor display for further details.

#### Ignore

When the Ignore is set, it inhibits the loading of the associated character into the CRTC line buffer. Such character(s) may be used as control character or software tags, and are not displayed. Whenever the Ignore encoding is detected, both the attribute word and its associated character code are not written into the line buffer, unless the DH (Display Hidden) bit in Mode Register 1 is set. Note that the Ignore bit is not brought out to the Attribute Port.

#### User Definable

The AW<sub>7</sub>–AW<sub>10</sub> attribute bits provide 4 bits of user definable attribute information. These bits are directly output on pins AP<sub>7</sub>–AP<sub>10</sub> of the Attribute Port. (In addition to these four user-definable attribute bits, the Cursor bit can also be user-definable under certain conditions.)

#### Highlight

When this bit is set and AP $_{6}$  is connected to the Foreground Shift (FS) input of the Am8152A, the character is displayed highlighted. The AP $_{6}$  pin of the Attribute Port goes active for each scan line of the relevant character(s).

#### Reverse

When this bit is set and AP $_5$  is connected to the REV input of the Am8152A, the character is displayed reversed. The AP $_5$  pin of the Attribute Port goes active for each scan line of the relevant character(s).

3-10 Am8052

#### Superscript

When this bit is set to 1, the affected character is displayed as a superscript. Its position on the character row  $(R_0-R_4)$  is determined by the superscript control field in the Row Redefinition Block for that particular row.

#### Subscript

When this bit is set, the affected character is displayed as a subscript. Its position on the character row ( $R_0$ – $R_4$ ) is determined by the subscript control fields in the Row Redefinition Block.

#### Underline/Shifted Underline

Attribute bits AW<sub>1</sub> and AW<sub>2</sub> provide underline and shifted underline display. The underline/shifted underline display information is output on the AP<sub>1</sub> and AP<sub>2</sub> Attribute Port pins, during applicable scan lines of the character. (The applicable scan lines have been programmed within the Row Redefinition Blocks.)

#### Blink

When this attribute is invoked, the Attribute Port pin APo is

gated with the character blink rate generator, during the time that the relevant character is output on  $\text{CC}_0\text{--}\text{CC}_7$ .

The character blink rate and character blink duty cycle are derived from the blink field of the Main Definition Block.

#### Attribute Fetches

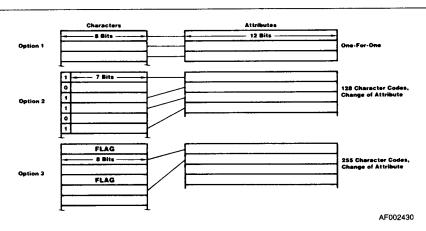

Attributes can be fetched in three different ways to suit most design philosophies (see Figure 2). In Option 1, one attribute is fetched per character. This option, although straightforward, imposes heavy bus overhead since the DMA has to access the attribute list from memory for every character displayed on the screen. Bus overhead can be reduced considerably by fetching attributes on a demand basis. Options 2 and 3 accomplish this in two different ways. In Option 2 one character bit is set to 1 when an attribute is required. When this bit is set to 0, the attribute will not be fetched. This option allows 7 bits of character code or a 128-character set for display with no overhead for attribute incorporation.

Option 3 makes use of an 8-bit flag which precedes the character invoking the attribute. This option allows for a 255-character set with an 8-bit overhead (the flag) per attribute.

Figure 1. Am8052 Attribute Word

Figure 2. Attribute Fetch

#### **Cursor Generation**

The CRTC can generate three different cursor formats: block, underline, and reverse, at variable blink rates and blink duty cycles.

Cursor information for the CRTC comes from two different sources, and each source can be independently steered to one of three different destinations. The two cursor sources are:

The XY cursor field which is held in the Main Definition Block for the screen. 2. Attribute word bit 14 of the character attribute word. A cursor designated by an attribute will follow its row and character position whenever text is scrolled. The cursor controlled by positioning X and Y coordinates within the cursor X and Y register will be displayed on a fixed X, Y character position on the screen. The X, Y cursor should be disabled by resetting the CUE bit in Mode Register 2 during smooth-scroll.

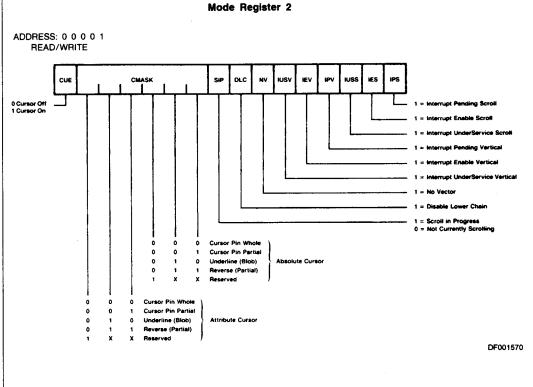

The steering of the cursor sources is under software control of the cursor mask field within Mode Register 2. The field is divided into two three-bit segments, one for the XY cursor and one for the attribute cursor. Three destinations are selectable for each cursor source:

- (a) The cursor pin

- (b) The underline pin

- (c) The reverse video pin.

If (a) is selected, then either the whole character cell or partial character cell is selectable. If whole is selected, the cursor pin will be active for every scan line of the character cell. If part is selected, then the cursor pin will only be active for those scan lines within the limits of CURSOR START and CURSOR END, as specified in the Row Redefinition Block (RRB).

If (b) is selected, then either an underline will be active, if CURSOR START and END have the same values, or a block, if CURSOR START and END are not coincident.

If (c) is selected, then either all or part of the character will be reversed, dependent upon the CURSOR START and CURSOR END setting as explained in (b).

In addition to these choices, either cursor can be made to blink (at the cursor blink rate) and duty cycle (as programmed into the Main Definition Block blink field).

#### **Row Buffers**

The on-chip DMA controller accesses the display memory and loads data from linked-list data blocks in memory into one of three row buffers. Each line buffer is 132 characters in length and 20 bits wide. Each 20-bit wide location accommodates an 8-bit character code and 12-bit attribute words. The row buffers operate in a rotating fill-display mode whereby one buffer is being loaded while another is being displayed.

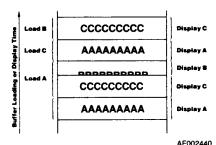

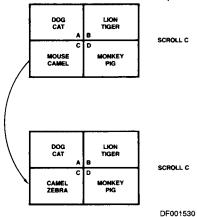

The presence of three row buffers on-chip is of significant advantage in split screen smooth-scrolling operations where a character row may only be displayed for a single scan line. With two row buffers, this would not leave enough time for the reloading of the alternate line buffer. A partially filled buffer results in screen flashing. This can only be prevented by incorporating three line buffers. Figure 3 highlights this advantage.

Figure 3. Triple Row Buffers

In the rotating fill-display mode, Row Buffer C is displayed when Row Buffer B is being loaded. Likewise, the next Row Buffer C is loaded while Row Buffer A is being displayed.

Because of the split-screen, Row Buffer B is displayed for one scan line only, while Row Buffer A is being loaded. By virtue of the third row buffer, the loading of Buffer A can spill over into the next buffer display, thus eliminating screen flashing.

#### **Smooth-Scrolling**

A smooth-scroll is defined as the gradual displacement of a character row on a scan line-by-scan line basis. Smooth-scrolling is achieved by a gradual offsetting of the scan line counter, on a frame-by-frame basis. At the start of the scroll, the offset counter is set to zero or equal to the number of scan lines per character row, depending on whether the scroll is up or down. As the counter is incremented or decremented, the text travels up or down until the offset is equal to the number of scan lines or zero. The start of the screen pointer pointing to the character row is adjusted and the offset counter reset simultaneously to scroll the next successive character row. Smooth-scrolling of the entire screen is thus a simple task.

A number of applications require screen overlays, such as menu or status areas which must remain static while the major portion of the screen is scrolling or vice versa. The Am8052 can support multiple windows, each capable of being scrolled. (Only one window can be scrolled at a time.)

#### Linked-List Data Structures

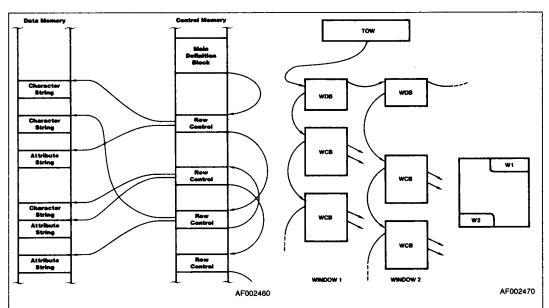

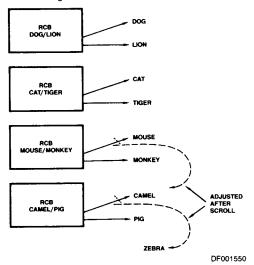

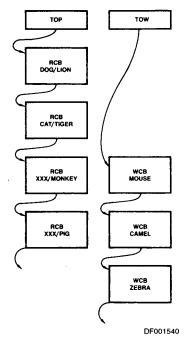

The DMA channel on the Am8052 operates via linked-list data structures that allow for the overlaying and independent smooth-scrolling of windows. The linked-list data structures are particularly suited to the manipulation of data strings where insertions and deletions are common. A typical CRTC linked-list structure is shown in Figure 4.

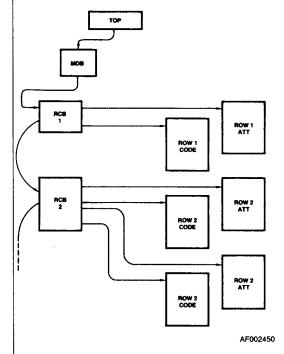

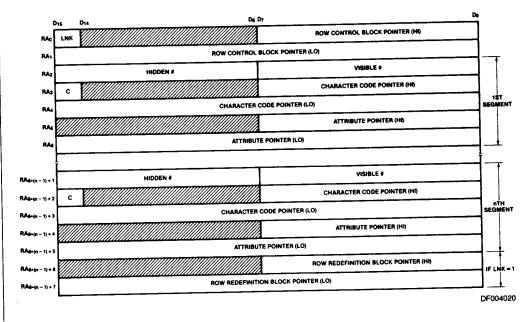

The linked list consists of Row Control Blocks (RCBs) for each character row on the screen. The RCB does not contain any displayable data, but contains the address which points to the character information. Each RCB is linked to the next block via an address link word (RCB ADR). The structure of the RCB linkage is shown in Figure 5. The Top of Page register on-chip points to the Main Definition Block, which in turn points to a linked list of RCBs.

The Am8052 allows for the separation of attribute and character lists. By extending the RCB, split-screen segments can be constructed as in the case of RCB2 in Figure 5. In parallel with the screen or background data structure, there exists a window structure which contains Window Control Blocks (WCBs) for each row of each window. Windows can exist in any position on the screen and are overlayed on top of the screen or background information. For example, the structure shown in Figure 6 could be used to implement a menu overlay at the top of the screen together with a status overlay.

#### Main Definition Block

The Main Definition Block is a set of control data and addresses, located in the system memory, which allow the user to specify screen oriented features. The Top of Page register points to the first word of the Main Definition Block. Cursor position, fill code and scroll rate are set by the appropriate fields within the block. The Main Definition Block also points to the first RCB.

Figure 4. Am8052 Linked-List Structure

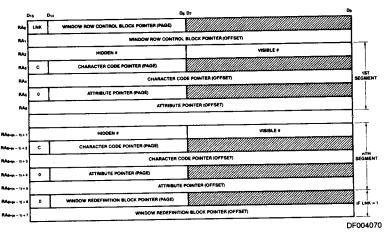

Figure 5. Background Data Structure

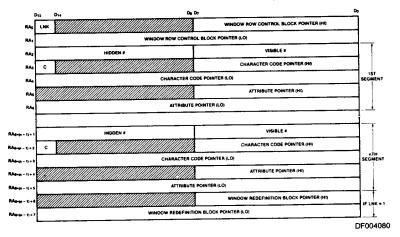

Figure 6. Window Data Structure

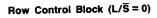

#### **Row Control Blocks**

The RCB Pointer in the Main Definition Block points to the first word of the first Row Control Block (RCB) of the list. Each RCB in the main chain is linked to the next via the RCB Pointer. Changing the RCB Pointer within the chain allows quick insertion or deletion of character rows.

Attributes associated with characters exist in their own separate lists. A character row may be composed of one or more segments of data. Each segment is a block of words with consecutive addresses. An RCB has a character code pointer (2 words) and an attribute pointer (2 words) for each segment. A fifth word, HIDDEN # and VISIBLE #, defines the number of characters (byte count) contained in the segment as well as the number of displayed characters in the segment. Character attributes are in word format, and there can be as many character attributes as character codes.

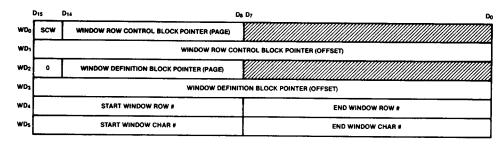

#### Window Definition Block

The Window Definition Block (WDB) defines the size and location of the window. It is the header block for a list of Window Row Control Blocks (WRCB) and can also point to another WDB if more than one window is displayed on the screen. The Top of Window (TOW) register points to the first word of the first WDB. Within the first WDB, the WRCB Pointer points to the current window's first WRCB, while the next WDB Pointer points to the next window's WDB. Window size is specified by two words in the WDB. START WINDOW ROW # and END WINDOW ROW # are byte values which position the window vertically on the screen. The window display becomes active in the character row number specified by START WINDOW ROW # and will become inactive in the character row following END WINDOW ROW #.

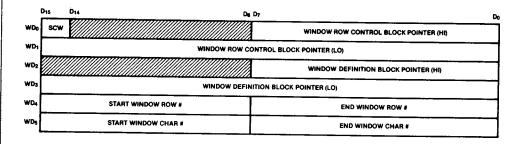

#### Window Row Control Blocks

The Window Row Control Blocks (WRCBs) have the same format as the RCBs.

The WCB Pointer is the address link to the next row's WRCB. A window can also be described with segments, and the WRCB contains five words for each segment.

To hard-scroll a window, it is only necessary to change the WRCB Pointer in the WDB to an adjacent WRCB.

#### Window Display Mechanism

A window is any bounded area on the screen which is linked in by a WDB. The window has the following size characteristics:

Width:

Defined by the number of character code positions occupied within a character row. Maximum width is the length of the line buffer (132 characters), and minimum width is one character.

Height: Defined by the number of displayable character rows contained within the window. The maximum height is the total number of displayed character rows on the face of the screen. The height limit is specified by the number of WRCB in the window linked list. The minimum height of a window is one row.

#### Window Positioning

The window is originally positioned to occupy any portion of the displayable character rows. It can be as large as the full screen or as small as one row high and one character wide. The window is always unscrolled when first displayed. (The counter holding the value of the first scan line of the uppermost character row of the window is reset.)

The window must be positioned horizontally such that its leftand right-hand sides begin and end at a background character row segment boundary. Any unfilled character positions within the window segment, and following the end of the window segment to the end of the line buffer (character position 131), are filled with the fill character code obtained from the Main Definition Block (MDB).

#### **Multiple Windows**

Multiple windows can be displayed simultaneously. Windows cannot be horizontally aligned to each other, and hence must be specified on non-overlapping character row boundaries (see section on virtual windows). Each window is defined by a WDB, and the scrolling windows are designated by a control bit within the WDB.

#### Window Positioning

The window position is defined in the WDB. The coordinate units are background character rows and background character columns. When the background is scrolling, the window (or windows) remain stationary on the display.

#### Example of Window Overlavs

The example (Figure 7) explains how windows are constructed using the linked-list feature that the Am8052 provides.

Figure 7. Example of Vertical Split Screen Smooth Scroll

#### Step 1

The first step toward constructing windows on a CRT screen is to split the screen horizontally and vertically using RCBs with multiple data pointers. The data pointers in each RCB point to the first characters within each subscreen area defined by the horizontal/vertical splits. In this example, the RCB that controls the first character row (DOG/LION) contains two data pointers. The first points to subscreen DOG and the second to subscreen LION. The segment length information in the RCB indicates to the DMA when to switch from data field DOG to data field LION. The linked-list structure for this example is shown in Figure 8. Note that in most applications, this split screen will have been set up prior to the invocation of the window.

#### Step 2

A window can now be overlayed on to the background by the creation of a window linked-list as shown in Figure 9. The scrollable window has a linked list structure pointed to by the Top of Window (TOW) Pointer which functions similarly to Top of Page (TOP). The other information required for window definition is the START WINDOW CHAR # and END WIN-DOW CHAR # which define the start/end coordinates of the window. To effect a window scroll, just one change to the toW value is required, which significantly relieves CPU overhead.

#### Virtual Windows

Although the rules of multiple windows do not permit overlapping windows, the background and window structures can be used to implement virtual horizontally aligned windows. This can be best described by using the illustration in Figure 7. The screen is divided into 4 subscreens: A, B, C and D; each can be independently defined as a window using a linked-list structures similar to Figure 9.

If subscreen C is defined as a window, subscreens A, B, and D are configured to be the background. Window C can be scrolled independently of the background by TOW Pointer manipulation. Similarly, subscreen D can be defined as a window with A, B and C configured as background. Thus, two aligned subscreens can be independently defined as windows

by intelligent use of linked-list structures, giving the user the illusion of aligned windows.

Figure 8. Split Screen Control Blocks

Figure 9. Window Overlay Structure

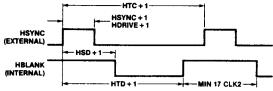

#### Horizontal Screen Format

The horizontal format defines the general timing of a single raster scan line. The scan line consists of two basic periods: visible raster line scan from left-to-right across the CRT screen and the right-to-left beam retrace period (or horizontal sync). The beam is always blanked during the retrace period. The front and back porch periods on either side of the horizontal

sync are also blanked because no active video is desired during that time.

Horizontal scan frequencies range from a minimum of 15 kHz for small screen, low bandwidth CRTs up to about 60 kHz for 100 MHz bandwidth large screen CRTs. The horizontal format versatility must accommodate this wide range of scan frequencies. The horizontal circuit generates two basic timing signals: horizontal sync and blanking. The horizontal blanking signal is "ORed" with the vertical blanking signal prior to output at the BLANK pin.

#### **Horizontal Timing Control**

Horizontal timing is controlled by the RST signal and the DE (Display Enable) bit in the mode register.

The HSYNC output is disabled (inactive) and the BLANK output active whenever the CRTC is reset by RST input (active LOW) or whenever the DE bit is reset (display disabled). RST active LOW is a hardware reset to the CRTC (this action also resets DE bit), and the DE bit is a software reset of the CRTC.

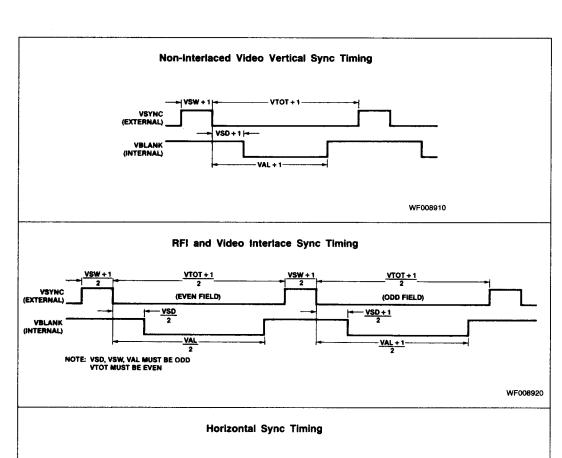

#### Am8052 Vertical Screen Format

The vertical format defines the number of horizontal scan lines to be displayed in each frame. The front and rear porches, as well as the vertical retrace time, are also defined.

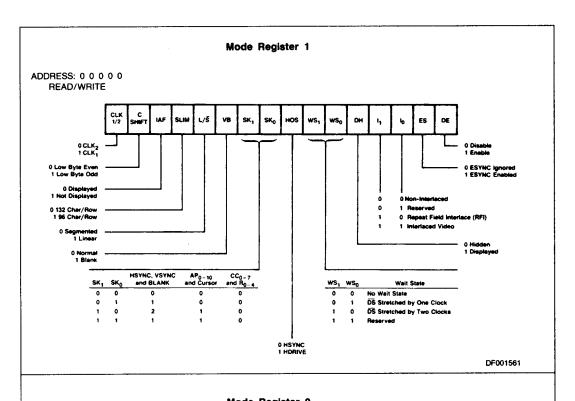

The CRTC operates in either an interlace or non-interlace mode. The  $I_1$  bit, in Mode Register 1, determines if the CRTC will operate in the interlace or non-interlace mode. See below for each of the interlace options.

The Vertical Line Counter is clocked by either the horizontal sync rate in the non-interlaced or twice the horizontal sync rate in the interlaced mode. In non-interlaced mode all vertical frames (period between two vertical sync pulses) are even. In interlaced mode, the first vertical frame following a Display Enable (setting of DE bit in the mode register) is always even and alternates between odd and even from there on.

#### External SYNC (ES) Operation

The ESYNC input allows synchronization of the CRT display vertical frame rate to the power line frequency to eliminate interference effects. The ES bit in Mode Register 1 specifies whether the ESYNC input is used to control the vertical syncrete.

The ESYNC input is recognized by the CRTC during every frame. It causes the VSYNC signal to become active at the occurrence of HSYNC. In non-interlaced mode, VSYNC becomes active at the rising edge of HSYNC active. In interlaced mode, VSYNC either becomes active at the next HSYNC, active when in the even frame, or active at the next half point between HSYNCs (2x HSYNC) in the odd frame.

#### Interlace

There are two types of interlace, Repeat Field Interlace (RFI) and Interlaced Video (IV). The effect of both schemes is to offset the vertical position of the scan lines of the odd numbered fields so that they will be physically interleaved with the scan lines of the even fields. For RFI, the same video information is displayed on both odd and even fields, the slight offset of the odd field tending to eliminate the horizontal stripes that sometimes occur between scan lines of non-interlaced displays.

Interlaced Video (IV) is used to increase the amount of information displayed on a monitor without increasing the horizontal or vertical scan rates. IV takes advantage of the odd field scan line offset by displaying half the video in the even field (alternating lines) and half in the odd field. The effect is to essentially double the vertical character density with respect to RFI or non-interlace.

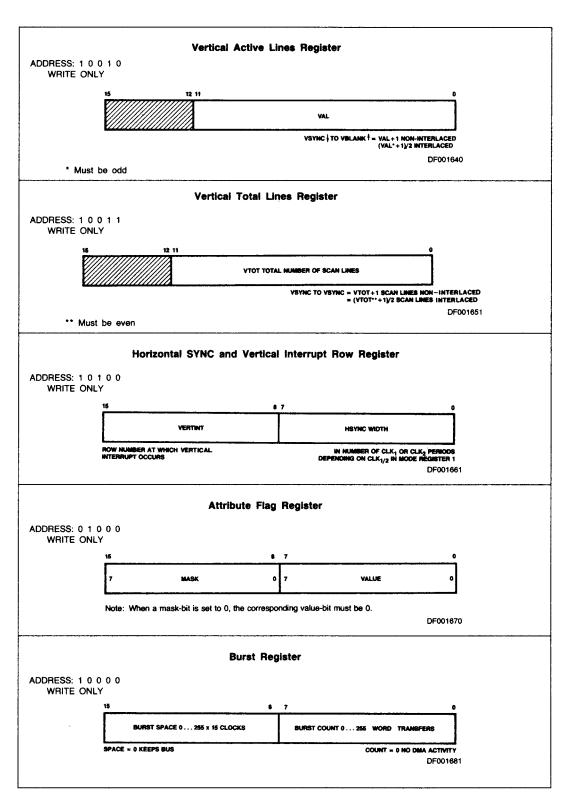

#### REGISTER SUMMARY

ADDRESS (AD4 - AD0)

| BINARY | HEX | TYPE | ACTIVE BITS | REGISTER MODE                 |

|--------|-----|------|-------------|-------------------------------|

| 00000  | 00  | R/W  | 16          | MODE 1                        |

| 00001  | 01  | R/W  | 16          | MODE 2                        |

| 00010  | 02  | W    | 12          | ATTRIBUTE ENABLE              |

| 00011  | 03  | W    | 5<br>8      | ATTRIBUTE REDEFINITION        |

| 00100  | 04  | R/W  | 8           | TOP OF PAGE SOFT (HI-ORDER)   |

| 00101  | 05  | R/W  | 16          | TOP OF PAGE SOFT (LO-ORDER)   |

| 00110  | 06  | R/W  | 8           | TOP OF WINDOW SOFT (HI-ORDER) |

| 00111  | 07  | R/W  | 16          | TOP OF WINDOW SOFT (LO-ORDER) |

| 01000  | 08  | W    | 16          | ATTRIBUTE FLAG                |

| 01001  | 09  | R/W  | 8           | TOP OF PAGE HARD (HI)         |

| 01010  | 0A  | R/W  | 16          | TOP OF PAGE HARD (LO)         |

| 01011  | 08  | R/W  | 8           | TOP OF WINDOW HARD (HI)       |

| 01100  | OC. | R/W  | 16          | TOP OF WINDOW HARD (LO)       |

| 10000  | 10  | W    | 16          | DMA BURST                     |

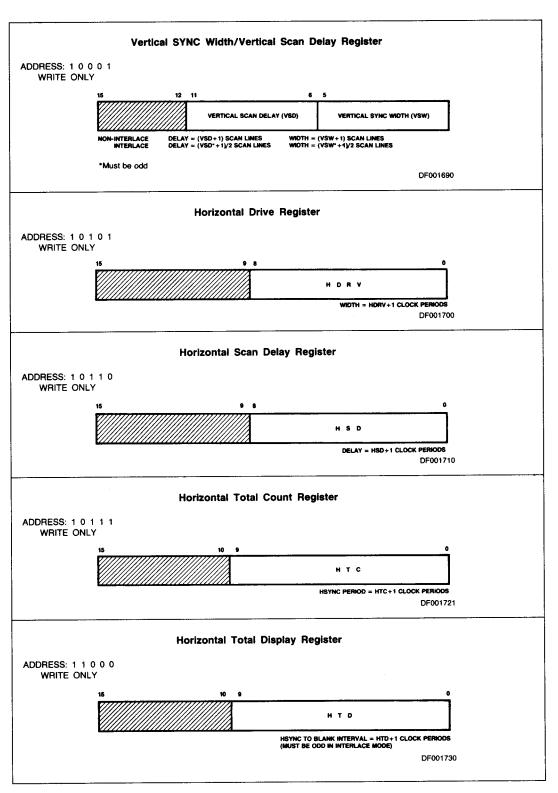

| 10001  | 11  | W    | 12          | *VSYNC WIDTH/SCAN DELAY       |

| 10010  | 12  | W    | 12          | *VERTICAL ACTIVE LINES        |

| 10011  | 13  | W    | 12          | *VERTICAL TOTAL LINES         |

| 10100  | 14  | W    | 16          | *H\$YNC/VERTINT               |

| 10101  | 15  | W    | 9<br>9      | *HDRIVE                       |

| 10110  | 16  | W    | 9           | *H \$CAN DELAY                |

| 10111  | 17  | W    | 10          | *H TOTAL COUNT                |

| 11000  | 18  | W    | 10          | *H TOTAL DISPLAY              |

<sup>\*</sup>These registers should only be accessed when Display Enable ("'DE" bit in Mode Register 1) is reset, since they control the video timing signals.

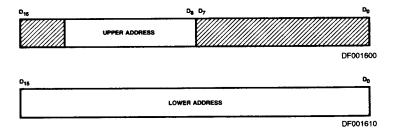

## Top of Page/Top of Window Registers $L/\overline{S} = 0$

| READ/WRITE |                         |             |

|------------|-------------------------|-------------|

| ADDRESS    | REGISTER                | ACTIVE BITS |

| 00100      | Top of Page Soft (HI)   | 14 8        |

| 00101      | Top of Page Soft (LO)   | 15 0        |

| 00110      | Top of Window Soft (HI) | 14 8        |

| 00111      | Top of Window Soft (LO) | 15 0        |

| 01001      | Top of Page Hard (HI)   | 14 8        |

| 01010      | Top of Page Hard (LO)   | 15 0        |

| 01011      | Top of Window Hard (HI) | 14 8        |

| 01100      | Top of Window Hard (LO) | 15 0        |

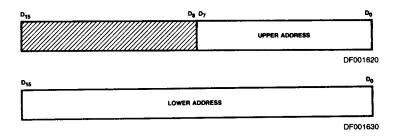

## Top of Page/Top of Window Registers $L/\overline{S} = 1$

#### READ/WRITE

| ADDRESS | REGISTER                | ACTIVE BITS |

|---------|-------------------------|-------------|

| 00100   | Top of Page Soft (HI)   | 7 0         |

| 00101   | Top of Page Soft (LO)   | 15 0        |

| 00110   | Top of Window Soft (HI) | 7 0         |

| 00111   | Top of Window Soft (LO) | 15 0        |

| 01001   | Top of Page Hard (HI)   | 7 0         |

| 01010   | Top of Page Hard (LO)   | 15 0        |

| 01011   | Top of Window Hard (HI) | 7 0         |

| 01100   | Top of Window Hard (LO) | 15 0        |

WF008930

Note: HSD ≥ 6

Interlaced Video: HTC must be even.

#### (

VAL ODD

VSD ODD

#### FRAME TIMING SIGNALS SUMMARY:

#### Non-Interlaced Mode

| VERTICAL SYNC WIDTH FRONT PORCH (VBLANK R.E. TO VSYNC R.E.) BACK PORCH (VSYNC F.E. TO VBLANK F.E.) VSYNC F.E. TO NEXT VBLANK R.E. TOTAL SCAN LINES/FRAME-VSYNC WIDTH HORIZONTAL SYNC WIDTH HORIZONTAL SYNC PERIOD HSYNC R.E. TO NEXT HBLANK R.E. HSYNC R.E. TO HBLANK F.E. | VSW + 1<br>VTOT-VAL<br>VSD + 1<br>VAL + 1<br>VTOT + 1<br>HSYNC + 1<br>HTC + 1<br>HTD + 1<br>HSD + 1 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| HSYNC R.E. TO HBLANK F.E.<br>HDRIVE R.E. TO HDRIVE F.E.                                                                                                                                                                                                                    | HSD + 1<br>HDRV + 1                                                                                 |

|                                                                                                                                                                                                                                                                            |                                                                                                     |

#### **Interlaced Mode**

| <b>VERTICAL</b> | SYNC | WIDTH |

|-----------------|------|-------|

| BACK POF        | RCH  |       |

VSYNC F.E. TO NEXT VBLANK R.E.

TOTAL SCAN LINES/FRAME-VSYNC WIDTH HORIZONTAL SYNC WIDTH HORIZONTAL SYNC PERIOD HSYNC R.E. TO NEXT HBLANK R.E. HSYNC E. TO HBLANK F.E. HDRIVE R.E. TO HDRIVE F.E. FRONT PORCH (VBLANK R.E. TO VSYNC R.E.)

(VSW + 1)/2, VSW ODD VSD/2, EVEN FIELDV (VSD + 1)/2, ODD FIELD (VAL + 1)/2, ODD FIELD VAL/2, EVEN FIELD (VtoT + 1)/2, VTOT EVEN HSYNC + 1 HTC + 1 HTD + 1, HTD ODD HSD + 1 HDRV + 1 (VTOT-VAL)/2, EVEN FIELD

(VTOT + 1-VAL)/2, ODD FIELD VAL ODD, VTOT EVEN

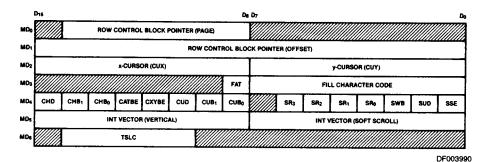

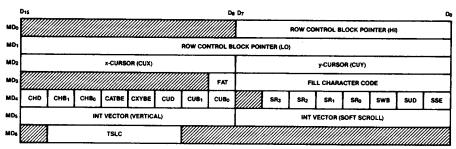

#### Main Definition Block (L/ $\overline{S} = 0$ )

#### Main Definition Block (L/ $\overline{S} = 1$ )

DF004000

## Row Control Block (L/ $\overline{S} = 1$ )

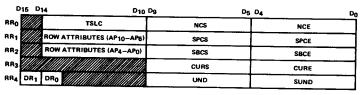

## **Row Redefinition Block**

DF004030

## Window Definition Block (L/ $\overline{S} = 0$ )

DF004040

#### Window Definition Block $(L/\overline{S} = 1)$

DF004050

## Window Row Control Block (L/ $\overline{S} = 1$ )

## Window Redefinition Block

DF004090

#### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature65 to +150°C     | , |

|-------------------------------------|---|

| Supply Voltage (TTL)                |   |

| with Respect to Ground0.5 to +7.0 V | , |

| Voltage on Any Input Pin            |   |

| with Respect to Ground0.5 to +7.0 V | , |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

| Commercial (C) Devices            |              |

|-----------------------------------|--------------|

| Temperature (T <sub>A</sub> )     | 0 to +70°C   |

| Supply Voltage (V <sub>CC</sub> ) |              |

| Military (M) Devices              |              |

| Temperature (T <sub>C</sub> )     | 55 to +125°C |

| Supply Voltage (Vcc)              |              |

Operating ranges define those limits between which the functionality of the device is guaranteed.

# **DC CHARACTERISTICS** over operating ranges unless otherwise specified; Included in Group A, Subgroup 1, 2, 3, 7, 8 tests unless otherwise noted.

| Parameter Symbol   | Parameter Description                                                                 | Min.   | Max.                    | Units |

|--------------------|---------------------------------------------------------------------------------------|--------|-------------------------|-------|

| Voн                | Output HIGH Voltage (I <sub>OH</sub> = 400 μA)                                        | 2.4    |                         | V     |

| V <sub>OL</sub>    | Output LOW Voltage (IOL = 3.2 mA)                                                     |        | 0.4                     | V     |

| V <sub>IH</sub>    | Input HIGH Voltage (except CLK <sub>1</sub> and CLK <sub>2</sub> )                    | 2.0    | V <sub>CC</sub> + 0.5 † | V     |

| VCIH               | CLK <sub>1</sub> /CLK <sub>2</sub> Input HIGH Voltage                                 | 4.0    | V <sub>CC</sub> + 0.5 † | ٧     |

| V <sub>IL</sub>    | Input LOW Voltage (except CLK <sub>1</sub> and CLK <sub>2</sub> )                     | -0.5 † | 0.8                     | v     |

| V <sub>CIL</sub>   | CLK <sub>1</sub> /CLK <sub>2</sub> Input LOW Voltage                                  | -0.5 † | 0.3                     | v     |

| l <sub>IX</sub>    | Input Load Current (except RSTT), 0 ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>               |        | ± 10                    | Aμ    |

| İIXR               | Input Load Current (RSTT), 0 ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>                      |        | ± 100                   | μА    |

| lo                 | Output Leakage Current, 0.45 V ≤ V <sub>OUT</sub> ≤ V <sub>CC</sub>                   |        | ±10                     | μА    |

| lcc                | Supply Current                                                                        |        | 500                     | mA    |

| C <sub>IN</sub> †  | Input Capacitance (all pins except CLK <sub>1</sub> and CLK <sub>2</sub> ), f = 1 MHz |        | 15                      | pF    |

| C <sub>CIN</sub> † | Input Capacitance, CLK <sub>1</sub> and CLK <sub>2</sub> , f = 1 MHz                  |        | 80                      | pF    |

| C <sub>OUT</sub> † | Output Capacitance, f = 1 MHz                                                         |        | 15                      | pF    |

| C <sub>1/O</sub> † | Bidirectional Pin Capacitance, f = 1 MHz                                              |        | 20                      | pF    |

† Not included in Group A tests.

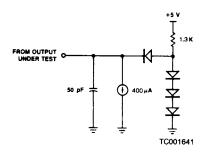

## **SWITCHING TEST CIRCUITS**

#### Standard Test Load

#### Open-Drain Test Load

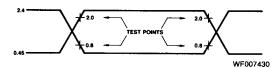

#### SWITCHING TEST WAVEFORM

#### Input Waveform

## SWITCHING CHARACTERISTICS over operating ranges unless otherwise specified; Included in Group A, Subgroup 9, 10, 11 tests unless otherwise noted.

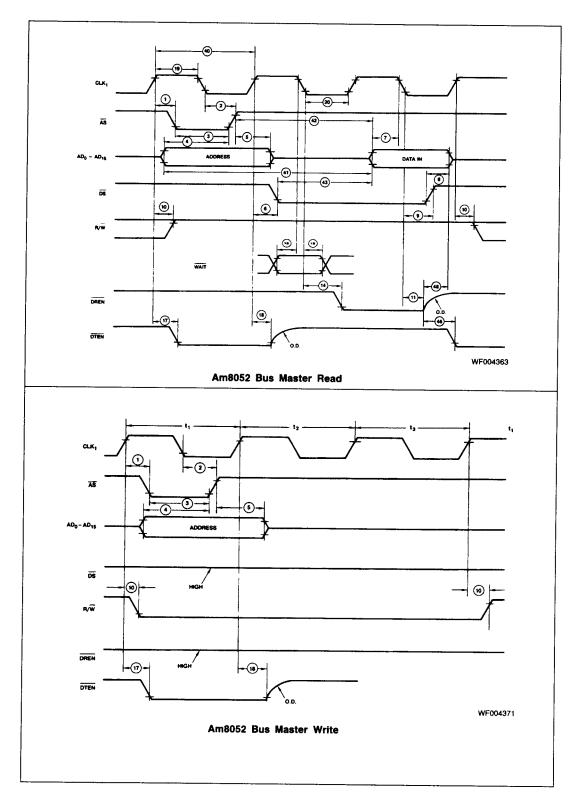

#### Am8052 Bus Master Read/Write

|     | Parameter<br>Symbol |                                       | 4 MHz          |          | 6 N            | lHz      | 8 MHz*         |      |       |

|-----|---------------------|---------------------------------------|----------------|----------|----------------|----------|----------------|------|-------|

| No. |                     | Parameter<br>Description              | Min.           | Max.     | Min.           | Max.     | Min.           | Max. | Unite |

| 1   | t <sub>PHL</sub>    | CLK <sub>1</sub> to AS L              |                | 65       |                | 55       |                | 45   | ns    |

| 2   | t <sub>PLH</sub>    | CLK 1 to AS 1                         |                | 65       |                | 55       |                | 45   | ns    |

| 3   | tpw                 | AS Pulse Width                        | <b>19 - 30</b> |          | 19 10          |          | <b>19 - 10</b> |      | ns    |

| 4   | ts                  | Address Valid to AS ↑                 | <b>(9</b> – 50 |          | <b>19 - 35</b> |          | 19 - 35        |      | ns    |

| 5   | t <sub>H</sub>      | Address from AS 1                     | 20             |          | 20             |          | 20             |      | ns    |

| 6   | tpHL                | CLK <sub>1</sub> † to DS ↓            |                | 80       |                | 65       |                | 45   | ns    |

| 7   | ts                  | Data in to CLK <sub>1</sub> i         | 20             |          | 15             | L        | 10             |      | ns    |

| 8   | t <sub>H</sub>      | Data In from DS t                     | 0              |          | 0              |          | 0              |      | ns    |

| 9   | tpLH                | CLK <sub>1</sub> i to DS †            |                | 80       |                | 65       |                | 45   | ns    |

| 10  | t <sub>PLH</sub>    | CLK <sub>1</sub> 1 to B/W             | 0 †            | 65       | 0 †            | 55       | 0              | 45   | ns    |

| 11  | tH                  | CLK <sub>1</sub> i to DREN † (Note 2) |                | 70       |                | 45       | <u> </u>       | 40   | ns    |

| 12  | ts                  | WAIT Valid to CLK <sub>1</sub> ↓      | 20             |          | 15             | <u> </u> | 10             |      | ns    |

| 13  | t <sub>H</sub>      | WAIT from CLK <sub>1</sub> i          | 30             |          | 20             |          | 20             |      | ns    |

| 14  | tpHL                | CLK <sub>1</sub> ↓ to DREN ↓          |                | 65       |                | 55       | <u>l</u>       | 45   | ns    |

| -17 | THE                 |                                       |                |          |                |          | -              |      |       |

| 17  | tehn                | CLK <sub>1</sub> † to DTEN ;          |                | 65       |                | 55       |                | 45   | ns    |

| 18  | tPLH                | CLK <sub>1</sub> t to DTEN t          |                | 65       |                | 55       |                | 45   | ns    |

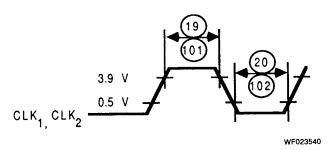

| 19  | tpw                 | CLK <sub>1</sub> HIGH Pulse Width     | 100            | 500      | 70             | 500      | 50             | 500  | ns    |

| 20  | tpw                 | CLK1 LOW Pulse Width                  | 100            | 500      | 70             | 500      | 50             | 500  | ns    |

| 40  | tcyc                | CLK <sub>1</sub> Period               | 250            | 1000     | 165            | 1000     | 125            | 1000 | ns    |

| 41  | tayby f             | Address Valid to Data In (Note 1)     |                | 1        |                |          |                |      | ns    |

| 42  | taspy †             | AS to Data Valid (Note 1)             |                |          |                |          |                |      | ns    |

| 42  |                     | DS to Data Valid (Note 1)             |                | 1        |                |          |                |      | ns    |

| 46  | tosov t             | DBEN : to DTEN 1                      | 20             |          | 20             |          | 20             |      | ns    |

| 48  | tort<br>th          | Data In from DREN 1                   | 0              | <b>†</b> | 0              |          | 0              |      | ns    |

Notes: 1. ①, ②, and ③ can be computed with the following equations, but are not tested:

$$(4) = 2 \cdot (4) + (9) - (1) - (3) + (4) - (7)$$

$$@ = 2 \cdot @ - ? - (CLK_1 \text{ Fall time})$$

2. This parameter specifies when the Am8052 stops driving DREN (open drain) LOW.

3. In the following diagrams (Switching Waveforms), O.D. designates an open-drain output which has turned off and is being pulled up by an external load.

† Not included in Group A tests.

\* Commercial products only.

Clock

3-29

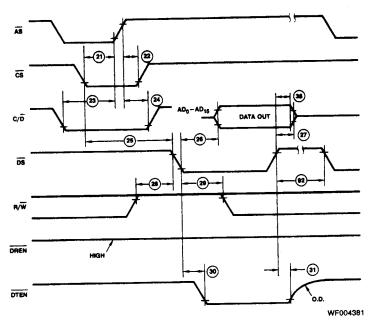

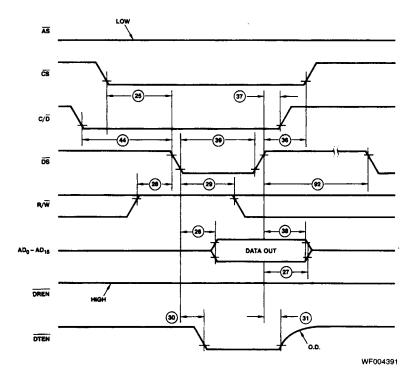

# SWITCHING CHARACTERISTICS (Cont'd.) Am8052 Bus Slave Read Latched

|     |                     | _                                | 4 1  | WHz  | 6 N  | AHZ  | 8 MHz* |          | 1     |

|-----|---------------------|----------------------------------|------|------|------|------|--------|----------|-------|

| No. | Parameter<br>Symbol | Parameter Description            | Min. | Max. | Min. | Max. | Min.   | Max.     | Units |

| 21  | ts                  | CS ⊥ to AS ↑                     | 0    |      | 0    |      | 0      |          | ns    |

| 22  | tH                  | CS LOW from AS t                 | 30   |      | 25   |      | 20     |          | ns    |

| 23  | ts                  | C/D to AS r                      | 0    |      | 0    |      | 0      |          | ns    |

| 24  | t <sub>H</sub>      | C/D from AS 1                    | 30   |      | 25   |      | 20     |          | ns    |

| 25  | ten                 | CS i to DS i                     | 50   |      | 40   |      | 30     |          | ns    |

| 26  | tpspv               | DS i to Data Valid               |      | 180  |      | 180  |        | 150      | ns    |

| 27  | tH                  | Data Valid from DS 1             | 15   |      | 15   |      | 10     |          | ns    |

| 28  | ts                  | R/W to DS i                      | 10   |      | 10   |      | 10     | L        | ns    |

| 29  | 14                  | R/W Valid from DS 1              | 50   |      | 40   |      | 40     | <u> </u> | ns    |

| 30  | tPD                 | Delay from DS ; to DTEN ;        |      | 65   |      | 55   | L      | 45       | กร    |

| 31  | tPD tPD             | Delay from DS 1 to DTEN 1        |      | 65   |      | 55   |        | 45       | ns    |

|     |                     |                                  |      |      |      |      |        | -        |       |

|     |                     |                                  |      |      |      |      |        |          |       |

| 38  | tz                  | DS 1 to AD0 - AD15 HI-Z (Note 4) | 10   | 70   | 10   | 60   | 10     | 50       | กร    |

- Notes: 1. R/W latched internally by DS 1.

2. CS latched internally by AS 1.

3. C/D latched internally by AS 1.

4. This parameter specifies when the Am8052 stops driving AD<sub>0</sub>-AD<sub>15</sub>.

- \* Commercial products only.

Am8052 Bus Slave Read Latched

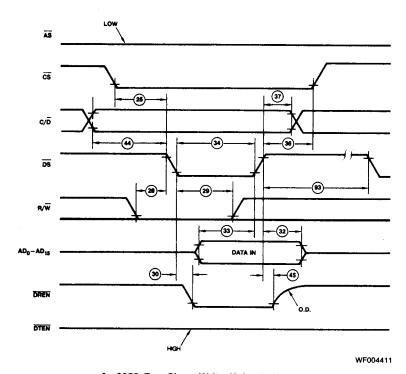

# SWITCHING CHARACTERISTICS (Cont'd.) Am8052 Bus Slave Read Unlatched

|     | Parameter<br>Symbol | Parameter<br>Description | 4 1  | 4 MHz |      | 6 MHz |      | 8 MHz* |       |

|-----|---------------------|--------------------------|------|-------|------|-------|------|--------|-------|

| No. |                     |                          | Min. | Max.  | Min. | Max.  | Min. | Max.   | Units |

| 36  | ŧн                  | CS LOW from DS 1         | 10   | ·     | 7    |       | 5    |        | ns    |

| 37  | ч                   | C/D LOW from DS :        | 10   |       | 7    |       | 5    |        | ns    |

| 39  | tpw                 | DS ; to DS † Read        | 250  |       | 200  |       | 150  |        | ns    |

| 44  | ts                  | C/D to DS ↓              | 50   |       | 40   |       | 30   |        | ns    |

|     |                     |                          |      |       |      |       |      |        |       |

| 92  | tsrt -              | Slave Recovery Time      | 500  |       | 300  |       | 225  |        | ns    |

<sup>\*</sup> Commercial products only.

Am8052 Bus Slave Read Unlatched

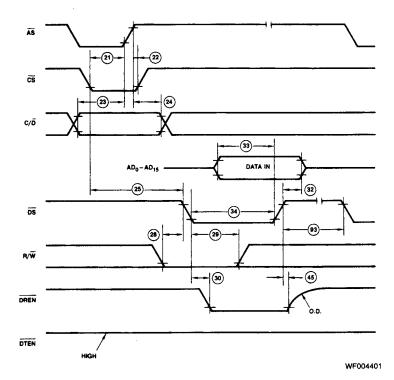

## SWITCHING CHARACTERISTICS (Cont'd.) Am8052 Bus Slave Write Latched

| Parameter<br>Symbol | Parameter<br>Description  | 4 1                                                                                                                                                                 | 4 MHz                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                | 6 MHz                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                            | 8 MHz*                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |                           | Min.                                                                                                                                                                | Max.                                                                                                                                                                                                                              | Min.                                                                                                                                                                                                                                           | Max.                                                                                                                                                                                                                                                                                                                                         | Min.                                                                                                                                                                                                                                                                                                       | Max.                                                                                                                                                                                                                                                                                                                                                | Units                                                                                                                                                                                                                                                                                                                                                                                                    |

| tu                  | Data In Valid from DS 1   | 20                                                                                                                                                                  |                                                                                                                                                                                                                                   | 20                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                              | 20                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                                                                                                                                                                       |

|                     | Data In Valid to DS ↑     | 100                                                                                                                                                                 |                                                                                                                                                                                                                                   | 90                                                                                                                                                                                                                                             | T                                                                                                                                                                                                                                                                                                                                            | 80                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                                                                                                                                                                       |

|                     | DS Pulse Width            | 160                                                                                                                                                                 |                                                                                                                                                                                                                                   | 135                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                              | 125                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                                                                                                                                                                       |

| tн                  | Delay from DS 1 to DREN 1 | 20                                                                                                                                                                  | 80                                                                                                                                                                                                                                | 20                                                                                                                                                                                                                                             | 70                                                                                                                                                                                                                                                                                                                                           | 20                                                                                                                                                                                                                                                                                                         | 70                                                                                                                                                                                                                                                                                                                                                  | ns                                                                                                                                                                                                                                                                                                                                                                                                       |