# **Uni-directional Ultra Low Capacitance ESD Protection Diode**

#### **DESCRIPTIONS**

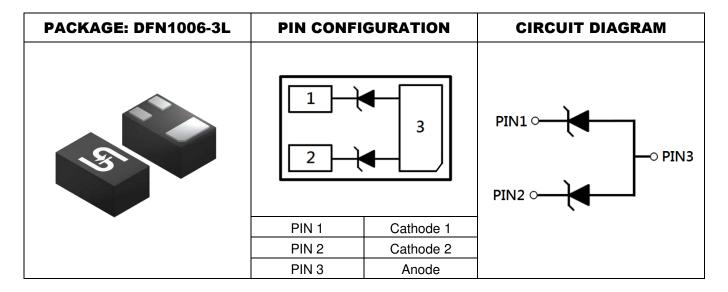

The TESDH5V0U04P2Q1 is an ultra-low capacitance ESD protection diode which includes two unidirectional ESD rated clamping cells to protect high speed data interfaces. It has been specifically designed to protect sensitive electronic components which are connected to data and transmission lines from over-stress caused by ESD (Electrostatic Discharge).

TESDH5V0U04P2Q1 is a unique design which includes proprietary clamping cells in a small package. During transient conditions, the proprietary clamping cells prevent over-voltage on the control/data/power lines, protecting any downstream components.

The TESDH5V0U04P2Q1 may be used to provide ESD protection up to  $\pm 20 \text{kV}$  (contact and air discharge) according to IEC61000-4-2, and withstand peak pulse current up to 4A (8/20 $\mu$ s) according to IEC61000-4-5.

#### **FEATURES**

- ESD Protect for 2 high-speed I/O channels

- Provide ESD protection for each channel to IEC 61000-4-2 (ESD) ±20kV (air), ±20kV (contact) IEC 61000-4-5 (Lightning) 4A (8/20us)

- Low clamping voltage: Vcl = 22.2V @ ITLP = 16A

- Ultra-low capacitance: 0.65pF

- Ultra-small DFN1006-3L package

- Fast turn-on and Low clamping voltage

- Moisture sensitivity level: level 1, per J-STD-020

- RoHS Compliant

- Halogen-Free according to IEC 61249-2-21

#### **APPLICATION**

- IEEE 1394

- PCI Express

- USB 2.0 and 3.0

- SATA and eSATA

- HDMI 1.3, 1.4 and 2.0 version

- Portable Electronics and Notebooks

1

| ABSOLUTE MAXIMUM RATINGS (T <sub>A</sub> = 25°C unless otherwise noted) |                    |             |      |  |

|-------------------------------------------------------------------------|--------------------|-------------|------|--|

| PARAMETER                                                               | SYMBOL             | VALUE       | UNIT |  |

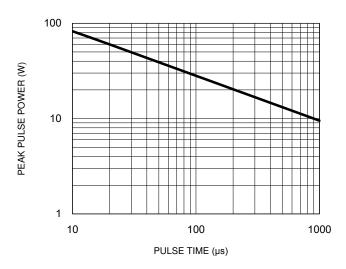

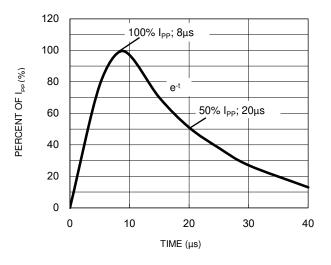

| Peak pulse power (tp = 8/20us)                                          | P <sub>PK</sub>    | 60          | W    |  |

| Peak pulse current (tp = 8/20us)                                        | I <sub>PP</sub>    | 4           | Α    |  |

| ESD according to IEC61000-4-2 air discharge                             | V                  | ±20         | kV   |  |

| ESD according to IEC61000-4-2 contact discharge                         | - V <sub>ESD</sub> | ±20         | kV   |  |

| Operating junction temperature range                                    | T <sub>J</sub>     | -55 to +125 | °C   |  |

| Storage temperature range                                               | T <sub>STG</sub>   | -55 to +150 | °C   |  |

| ELECTRICAL SPECIFICATIONS (T <sub>A</sub> = 25°C unless otherwise noted) |                                                    |                 |     |      |      |      |

|--------------------------------------------------------------------------|----------------------------------------------------|-----------------|-----|------|------|------|

| PARAMETER                                                                | CONDITIONS                                         | SYMBOL          | MIN | TYP  | MAX  | UNIT |

| Reverse working voltage                                                  |                                                    | $V_{RWM}$       | -   | -    | 5    | V    |

| Reverse breakdown voltage                                                | $I_R = 1 \text{mA}, T_J = 25^{\circ}\text{C}$      | $V_{BR}$        | 7   | -    | 9    | V    |

| Forward voltage                                                          | I <sub>F</sub> = 10mA, T <sub>J</sub> = 25°C       | $V_{F}$         | 0.6 | -    | 1.2  | V    |

| Reverse leakage current                                                  | $V_{RWM} = 5V$                                     | I <sub>R</sub>  | -   | -    | 100  | nA   |

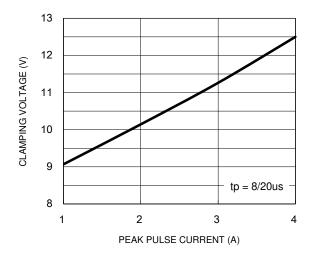

| Clamping voltage <sup>(1)</sup>                                          | $I_{PP} = 1A$ , $tp = 8/20us$                      | V <sub>C</sub>  | -   | -    | 11   | V    |

|                                                                          | $I_{PP} = 4A$ , $tp = 8/20us$                      |                 | -   | -    | 15   | V    |

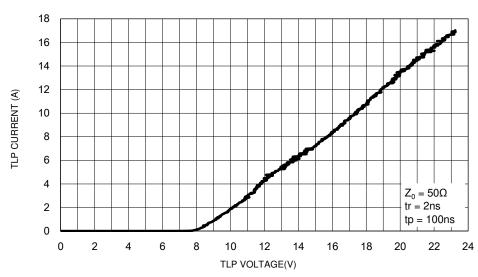

| Clamping voltage <sup>(2)</sup>                                          | $I_{TLP} = 16A, tp = 100ns$                        | V <sub>CL</sub> | -   | 22.2 | -    | V    |

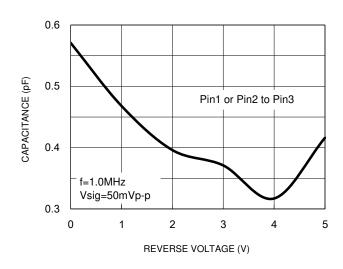

| Junction capacitance                                                     | 1MHz, $V_R = 0V$<br>Pin1 or 2 to Pin3              | CJ              | -   | 0.57 | 0.65 | pF   |

|                                                                          | 1MHz, V <sub>R</sub> = 0V<br>Between Pin1 and Pin2 |                 | -   | 0.25 | 0.40 | pF   |

| Dynamic resistance <sup>(2)</sup>                                        |                                                    | $R_{DYN}$       | -   | 0.85 | -    | Ω    |

# Notes:

- 1. Non-repetitive current pulse, according to IEC61000-4-5.

- 2. TLP parameter:  $Z_0$  = 50  $\Omega$ , tp = 100ns, tr = 2ns, averaging window from 60ns to 80ns. RDYN is calculated from 4A to 16A.

| ORDERING INFORMATION |            |                  |  |

|----------------------|------------|------------------|--|

| ORDERING CODE        | PACKAGE    | PACKING          |  |

| TESDH5V0U04P2Q1 RNG  | DFN1006-3L | 10,000 / 7" Reel |  |

### **CHARACTERISTICS CURVES**

$(T_A = 25^{\circ}C \text{ unless otherwise noted})$

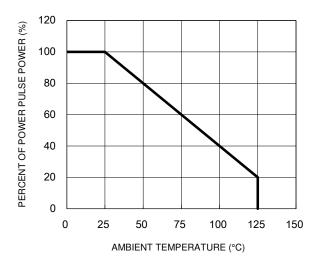

Fig.1 Peak Pulse Power vs. Junction Temperature Fig.2 Non-Repetitive Peak Pulse Power vs. Pulse Time

Fig.3 Clamping Voltage vs. Peak Pulse Current

Fig.4 Capacitance vs. Reverse Voltage

Fig.5 TLP Curve

## **CHARACTERISTICS CURVES**

$(T_A = 25^{\circ}C \text{ unless otherwise noted})$

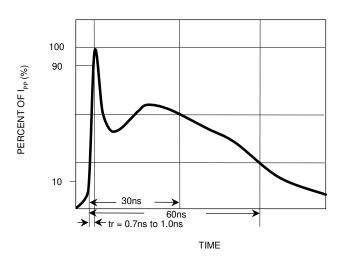

Fig.6 8/20µs pulse waveform per IEC61000-4-5

Fig.7 ESD pulse waveform per IEC61000-4-2

### **APPLICATION INFORMATION**

#### **Device Connection**

The TESDH5V0U04P2Q1 is designed to protect two data lines from transient over-voltage (such as ESD stress pulse). The device connection of TESDH5V0U04P2Q1 is shown in the Fig. 1. In Fig. 1, the two protected data lines are connected to the ESD protection pins (pin1, pin2) of TESDH5V0U04P2Q1. The ground pin (pin3) of TESDH5V0U04P2Q1 is a negative reference pin. This pin should be directly connected to the GND rail of PCB (Printed Circuit Board). To get minimum parasitic inductance, the path length should keep as shortas possible.

TESDH5V0U04P2Q1 can provide protection for 2 I/O signal lines simultaneously. If the number of I/O signal lines is less than 2, the unused I/O pin canbe simply left as NC pin.

The TESDH5V0U04P2Q1 is designed to protect two high speed line against ESD. The Fig.1 below shown the onnection for USB interface ESD protection

VBUS

D+

DGND

TO

Protected

IC

Fig.1 Data lines connection of TESDH5V0U04P2Q1

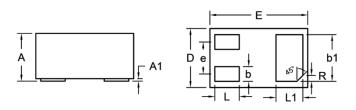

### **PACKAGE OUTLINE DIMENSIONS**

### **DFN1006-3L**

| DIM. Unit (n |              | (mm) | m) Unit (inch) |        |

|--------------|--------------|------|----------------|--------|

| Dilvi.       | Min.         | Max. | Min.           | Max.   |

| Α            | 0.46         | 0.51 | 0.018          | 0.020  |

| A1           | 0.00         | 0.05 | 0.000          | 0.002  |

| b            | 0.10         | 0.20 | 0.004          | 0.008  |

| b1           | 0.40         | 0.55 | 0.016          | 0.022  |

| D            | 0.55         | 0.65 | 0.022          | 0.026  |

| E            | 0.95         | 1.05 | 0.037          | 0.041  |

| е            | 0.325 (TYP.) |      | 0.013          | (TYP.) |

| L            | 0.20         | 0.30 | 0.008          | 0.012  |

| L1           | 0.20         | 0.35 | 0.008          | 0.014  |

| R            | 0.06 (TYP.)  |      | 0.002          | (TYP.) |

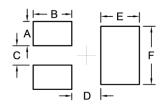

# **SUGGESTED PAD LAYOUT**

| Symbol | Unit (mm) | Unit (inch) |

|--------|-----------|-------------|

| Α      | 0.25      | 0.010       |

| В      | 0.40      | 0.016       |

| С      | 0.20      | 0.008       |

| D      | 0.30      | 0.012       |

| E      | 0.40      | 0.016       |

| F      | 0.60      | 0.024       |

### Notes:

This recommended land pattern is for reference purposes only. Please consult your manufacturing group to ensure your PCB design guidelines are met.

### **MARKING DIAGRAM**

6

Taiwan Semiconductor

# **Notice**

Specifications of the products displayed herein are subject to change without notice. TSC or anyone on its behalf, assumes no responsibility or liability for any errors or inaccuracies.

Purchasers are solely responsible for the choice, selection, and use of TSC products and TSC assumes no liability for application assistance or the design of Purchasers' products.

Information contained herein is intended to provide a product description only. No license, express or implied, to any intellectual property rights is granted by this document. Except as provided in TSC's terms and conditions of sale for such products, TSC assumes no liability whatsoever, and disclaims any express or implied warranty, relating to sale and/or use of TSC products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright, or other intellectual property right.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications. Customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify TSC for any damages resulting from such improper use or sale.