MT3170B/71B, MT3270B/71B, MT3370B/71B Wide Dynamic Range DTMF Receiver

#### Data Sheet

February 2007

#### **Features**

- Wide dynamic range (50 dB) DTMF Receiver

- Call progress (CP) detection via cadence indication

- · 4-bit synchronous serial data output

- Software controlled guard time for MT3x70B

- Internal guard time circuitry for MT3x71B

- Powerdown option (MT317xB & MT337xB)

- 4.194304 MHz crystal or ceramic resonator (MT337xB and MT327xB)

- External clock input (MT317xB)

- · Guarantees non-detection of spurious tones

# **Applications**

- · Integrated telephone answering machine

- End-to-end signalling

- Fax Machines

| Ordering Information |                                                                                                                                                                                                                                 |                                                                                                                               |  |  |  |  |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                      | 8 Pin PDIP<br>8 Pin PDIP<br>18 Pin SOIC<br>20 Pin SSOP<br>18 Pin SOIC<br>20 Pin SSOP<br>8 Pin PDIP*<br>8 Pin PDIP*<br>8 Pin PDIP*<br>20 Pin SSOP*<br>18 Pin SOIC*<br>18 Pin SOIC*<br>Pb Free Matte Tin<br>Free Tin/Silver/Coppe | Tubes<br>Tubes<br>Tubes<br>Tape & Reel<br>Tape & Reel<br>Tubes<br>Tubes<br>Tubes<br>Tubes<br>Tubes<br>Tubes<br>Tubes<br>Tubes |  |  |  |  |  |  |  |

|                      | -40°C to 85°C                                                                                                                                                                                                                   |                                                                                                                               |  |  |  |  |  |  |  |

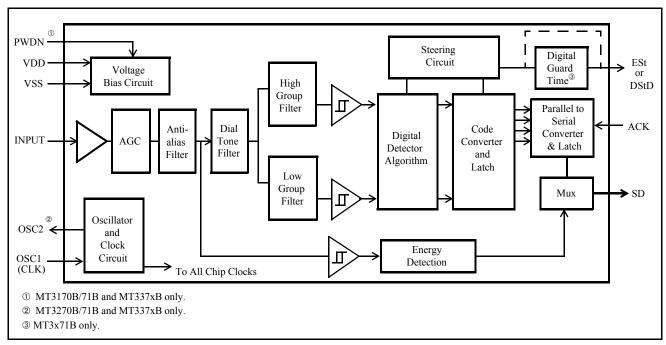

#### Figure 1 - Functional Block Diagram

Zarlink Semiconductor Inc. Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc. Copyright 1995-2007, Zarlink Semiconductor Inc. All Rights Reserved.

# Description

The MT3x7xB is a family of high performance DTMF receivers which decode all 16 tone pairs into a 4-bit binary code. These devices incorporate an AGC for wide dynamic range and are suitable for end-to-end signalling. The MT3x70B provides an early steering (ESt) logic output to indicate the detection of a DTMF signal and requires external software guard time to validate the DTMF digit. The MT3x71B, with preset internal guard times, uses a delay steering (DStD) logic output to indicate the detection of a valid DTMF digit. The 4-bit DTMF binary digit can be clocked out synchronously at the serial data (SD) output. The SD pin is multiplexed with call progress detector output. In the presence of supervisory tones, the call progress detector circuit indicates the cadence (i.e., envelope) of the tone burst. The cadence information can then be processed by an external microcontroller to identify specific call progress signals. The MT327xB and MT337xB can be used with a crystal or a ceramic resonator without additional components. A power-down option is provided for the MT317xB and MT337xB.

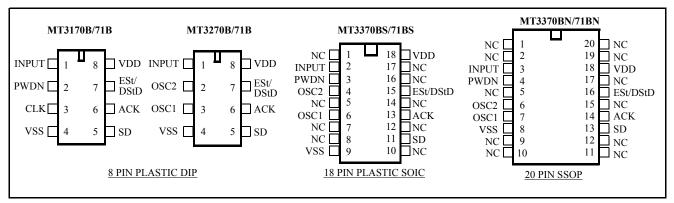

Figure 2 - Pin Connections

#### **Pin Description**

|        |        | Pin # |       | Name            | Description                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|--------|--------|-------|-------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 337xBN | 337xBS | 327xB | 317xB | Name            | Description                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 3      | 2      | 1     | 1     | INPUT           | <b>DTMF/CP Input.</b> Input signal must be AC coupled via capacitor.                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 6      | 4      | 2     | -     | OSC2            | Oscillator Output.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 7      | 6      | 3     | 3     | OSC1<br>(CLK)   | <ul> <li>Oscillator/Clock Input. This pin can either be driven by:</li> <li>an external digital clock with defined input logic levels.<br/>OSC2 should be left open.</li> <li>connecting a crystal or ceramic resonator between<br/>OSC1 and OSC2 pins.</li> </ul>                                                                                                                   |  |  |  |

| 8      | 9      | 4     | 4     | V <sub>SS</sub> | Ground. (0V)                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 13     | 11     | 5     | 5     | SD              | Serial Data/Call Progress Output. This pin serves the dual function of being the serial data output when clock pulses are applied after validation of DTMF signal, and also indicates the cadence of call progress input. As DTMF signal lies in the same frequency band as call progress signal, this pin may toggle for DTMF input. The SD pin is at logic low in powerdown state. |  |  |  |

#### **Pin Description**

|                                      |                                     | Pin # |       | Name                                  | Description                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------|-------------------------------------|-------|-------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 337xBN                               | 337xBS                              | 327xB | 317xB | Name                                  | Description                                                                                                                                                                                                                                                                                                                                                                    |

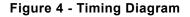

| 14                                   | 13                                  | 6     | 6     | ACK                                   | Acknowledge Pulse Input. After ESt or DStD is high,<br>applying a sequence of four pulses on this pin will then shift<br>out four bits on the SD pin, representing the decoded DTMF<br>digit. The rising edge of the first clock is used to latch the 4-<br>bit data prior to shifting. This pin is pulled down internally.<br>The idle state of the ACK signal should be low. |

| 16                                   | 15                                  | 7     | 7     | ESt<br>(MT3x70B)<br>DStD<br>(MT3x71B) | <ul> <li>Early Steering Output. A logic high on ESt indicates that a DTMF signal is present. ESt is at logic low in powerdown state.</li> <li>Delayed Steering Output. A logic high on DStD indicates that a valid DTMF digit has been detected. DStD is at logic low in powerdown state.</li> </ul>                                                                           |

| 18                                   | 18                                  | 8     | 8     | V <sub>DD</sub>                       | <b>Positive Power Supply (5 V Typ.)</b> Performance of the device can be optimized by minimizing noise on the supply rails. Decoupling capacitors across $V_{DD}$ and $V_{SS}$ are therefore recommended.                                                                                                                                                                      |

| 1,2,5,9,<br>10,11,12,<br>15,17,19,20 | 1,5,7,8,<br>10, 12,<br>14,16,<br>17 | -     | -     | NC                                    | No Connection. Pin is unconnected internally.                                                                                                                                                                                                                                                                                                                                  |

| 4                                    | 3                                   | -     | 2     | PWDN                                  | <b>Power Down Input.</b> A logic high on this pin will power down the device to reduce power consumption. This pin is pulled down internally and can be left open if not used. ACK pin should be at logic '0' to power down device.                                                                                                                                            |

#### Summary of MT3x70/71B Product Family

| Device<br>Type | 8 Pin        | 18 Pin       | 20 Pin       | PWDN         | 2 Pin<br>OSC | Ext<br>CLK   | ESt          | DStD         |

|----------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| MT3170B        | $\checkmark$ |              |              | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |              |

| MT3171B        | $\checkmark$ |              |              | $\checkmark$ |              | $\checkmark$ |              | $\checkmark$ |

| MT3270B        | $\checkmark$ |              |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |

| MT3271B        | $\checkmark$ |              |              |              | $\checkmark$ | $\checkmark$ |              | $\checkmark$ |

| MT3370B        |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |

| MT3371B        |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              | $\checkmark$ |

# **Change Summary**

The following table summarizes the changes from the August 2006 issue.

| Page Item Description |                   | Description                                     |

|-----------------------|-------------------|-------------------------------------------------|

| 2                     | Figure 2          | Added ordering codes to Pin Connection diagram. |

| 2                     | "Pin Description" | Added 20 pin description to the table.          |

# Functional Description

The MT3x7xBs are high performance and low power consumption DTMF receivers. These devices provide wide dynamic range DTMF detection and a serial decoded data output. These devices also incorporate an energy detection circuit. An input voiceband signal is applied to the devices via a series decoupling capacitor. Following the unity gain buffering, the signal enters the AGC circuit followed by an anti-aliasing filter. The bandlimited output is routed to a dial tone filter stage and to the input of the energy detection circuit. A bandsplit filter is then used to separate the input DTMF signal into high and low group tones. The high group and low group tones are then verified and decoded by the internal frequency counting and DTMF detection circuitry. Following the detection stage, the valid DTMF digit is translated to a 4-bit binary code (via an internal look-up ROM). Data bits can then be shifted out serially by applying external clock pulses.

#### Automatic Gain Control (AGC) Circuit

As the device operates on a single power supply, the input signal is biased internally at approximately VDD/2. With large input signal amplitude (between 0 and approximately -30 dBm for each tone of the composite signal), the AGC is activated to prevent the input signal from being clipped. At low input level, the AGC remains inactive and the input signal is passed directly to the hardware DTMF detection algorithm and to the energy detection circuit.

#### Filter and Decoder Section

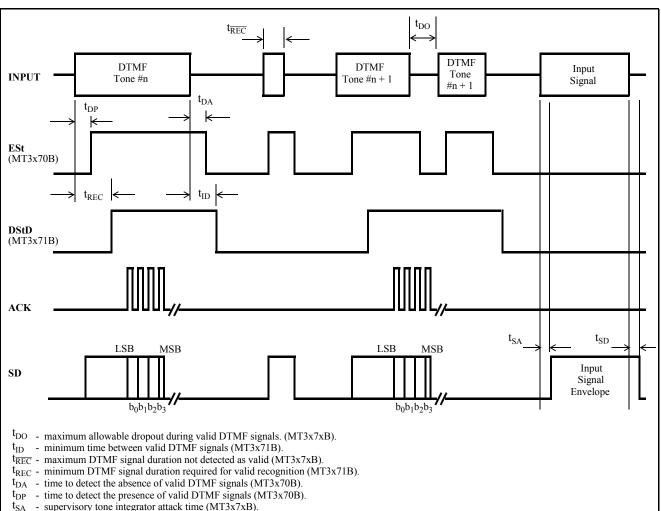

The signal entering the DTMF detection circuitry is filtered by a notch filter at 350 and 440 Hz for dial tone rejection. The composite dual-tone signal is further split into its individual high and low frequency components by two 6<sup>th</sup> order switched capacitor bandpass filters. The high group and low group tones are then smoothed by separate output filters and squared by high gain limiting comparators. The resulting squarewave signals are applied to a digital detection circuit where an averaging algorithm is employed to determine the valid DTMF signal. For MT3x70B, upon recognition of a valid frequency from each tone group, the early steering (ESt) output will go high, indicating that a DTMF tone has been detected. Any subsequent loss of DTMF signal condition will cause the ESt pin to go low. For MT3x71B, an internal delayed steering counter validates the early steering signal after a predetermined guard time which requires no external components. The delayed steering (DStD) will go high only when the validation period has elapsed. Once the DStD output is high, the subsequent loss of early steering signal due to DTMF signal dropout will activate the internal counter for a validation of tone absent guard time. The DStD output will go low only after this validation period.

#### **Energy Detection**

The output signal from the AGC circuit is also applied to the energy detection circuit. The detection circuit consists of a threshold comparator and an active integrator. When the signal level is above the threshold of the internal comparator (-35 dBm), the energy detector produces an energy present indication on the SD output. The integrator ensures the SD output will remain at high even though the input signal is changing. When the input signal is removed, the SD output will go low following the integrator decay time. Short decay time enables the signal envelope (or cadence) to be generated at the SD output. An external microcontroller can monitor this output for specific call progress signals. Since presence of speech and DTMF signals (above the threshold limit) can cause the SD output to toggle, both ESt (DStD) and SD outputs should be monitored to ensure correct signal identification. As the energy detector is multiplexed with the digital serial data output at the SD pin, the detector output is selected at all times except during the time between the rising edge of the first pulse and the falling edge of the fourth pulse applied at the ACK pin.

#### Serial Data (SD) Output

When a valid DTMF signal burst is present, ESt or DStD will go high. The application of four clock pulses on the ACK pin will provide a 4-bit serial binary code representing the decoded DTMF digit on the SD pin output. The rising edge of the first pulse applied on the ACK pin latches and shifts the least significant bit of the decoded digit on the SD pin. The next three pulses on ACK pin will shift the remaining latched bits in a serial format (see Figure 5). If less than four pulses are applied to the ACK pin, new data cannot be latched even though ESt/DStD can be valid. Clock pulses should be applied to clock out any remaining data bits to resume normal operation. Any transitions in excess

of four pulses will be ignored until the next rising edge of the ESt/DStD. ACK should idle at logic low. The 4-bit binary representing all 16 standard DTMF digits are shown in Table 1.

| F <sub>LOW</sub> | F <sub>HIGH</sub>           | DIGIT | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> | b <sub>0</sub> |  |  |  |  |

|------------------|-----------------------------|-------|----------------|----------------|----------------|----------------|--|--|--|--|

| 697              | 1209                        | 1     | 0              | 0              | 0              | 1              |  |  |  |  |

| 697              | 1336                        | 2     | 0              | 0              | 1              | 0              |  |  |  |  |

| 697              | 1477                        | 3     | 0              | 0              | 1              | 1              |  |  |  |  |

| 770              | 1209                        | 4     | 0              | 1              | 0              | 0              |  |  |  |  |

| 770              | 1336                        | 5     | 0              | 1              | 0              | 1              |  |  |  |  |

| 770              | 1477                        | 6     | 0              | 1              | 1              | 0              |  |  |  |  |

| 852              | 1209                        | 7     | 0              | 1              | 1              | 1              |  |  |  |  |

| 852              | 1336                        | 8     | 1              | 0              | 0              | 0              |  |  |  |  |

| 852              | 1477                        | 9     | 1              | 0              | 0              | 1              |  |  |  |  |

| 941              | 1336                        | 0     | 1              | 0              | 1              | 0              |  |  |  |  |

| 941              | 1209                        | *     | 1              | 0              | 1              | 1              |  |  |  |  |

| 941              | 1477                        | #     | 1              | 1              | 0              | 0              |  |  |  |  |

| 697              | 1633                        | А     | 1              | 1              | 0              | 1              |  |  |  |  |

| 770              | 1633                        | В     | 1              | 1              | 1              | 0              |  |  |  |  |

| 852              | 1633                        | С     | 1              | 1              | 1              | 1              |  |  |  |  |

| 941              | 1633                        | D     | 0              | 0              | 0              | 0              |  |  |  |  |

|                  | 0= LOGIC LOW, 1= LOGIC HIGH |       |                |                |                |                |  |  |  |  |

Table 1 - Serial Decode Bit Table

Note: b0=LSB of decoded DTMF digit and shifted out first.

#### Powerdown Mode (MT317xB/337xB)

The MT317xB/337xB devices offer a powerdown function to preserve power consumption when the device is not in use. A logic high can be applied at the PWDN pin to place the device in powerdown mode. The ACK pin should be kept at logic low to avoid undefined ESt/DStD and SD outputs (see Table 2).

| ACK (input) | PWDN (input)      | ESt/DStD (output)                    | SD (output)                             | MT317xB/337xB<br>status |

|-------------|-------------------|--------------------------------------|-----------------------------------------|-------------------------|

| low         | low               | Refer to Fig. 4 for timing waveforms | Refer to Fig. 4 for<br>timing waveforms | normal operation        |

| low         | high <sup>+</sup> | low                                  | low                                     | powerdown mode          |

| high        | low               | low                                  | undefined                               | undefined               |

| high        | high              | undefined                            | undefined                               | undefined               |

Table 2 - Powerdown Mode

<sup>+</sup> =enters powerdown mode on the rising edge.

| Frequency 1 (Hz) | quency 1 (Hz) Frequency 2 (Hz) On/Off |             | Description                    |

|------------------|---------------------------------------|-------------|--------------------------------|

| 350              | 440                                   | continuous  | North American Dial Tones      |

| 425              |                                       | continuous  | European Dial Tones            |

| 400              |                                       | continuous  | Far East Dial Tones            |

| 480              | 620                                   | 0.5s/0.5s   | North American Line Busy       |

| 440              |                                       | 0.5s/0.5s   | Japanese Line Busy             |

| 480              | 620                                   | 0.25s/0.25s | North American Reorder Tones   |

| 440              | 480                                   | 2.0s/4.0s   | North American Audible Ringing |

| 480              | 620                                   | 0.25s/0.25s | North American Reorder Tones   |

Table 3 - Call Progress Tones

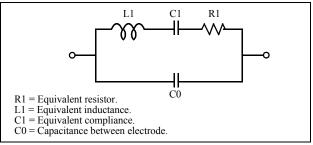

| Parameter | Unit | Resonator | Crystal    |

|-----------|------|-----------|------------|

| R1        | Ohms | 6.580     | 150        |

| L1        | mH   | 0.359     | 95.355     |

| C1        | pF   | 4.441     | 15.1E-03   |

| C0        | pF   | 34.890    | 12.0       |

| Qm        | -    | 1.299E+03 | 101.2E+ 03 |

| Δf        | %    | ±0.2%     | ±0.01%     |

Table 4 - Recommended Resonator and Crystal Specifications

Note: Qm=quality factor of RLC model, i.e., 1/2P¶R1C1.

**Resonator and Crystal Electric Equivalent Circuit**

#### Oscillator

The MT327xB/337xB can be used in both external clock or two pin oscillator mode. In two pin oscillator mode, the oscillator circuit is completed by connecting either a 4.194304 MHz crystal or ceramic resonator across OSC1 and OSC2 pins. Specifications of the ceramic resonator and crystal are tabulated in Table 4. It is also possible to configure a number of these devices employing only a single oscillator crystal. The OSC2 output of the first device in the chain is connected to the OSC1 input of the next device. Subsequent devices are connected similarly. The oscillator circuit can also be driven by an 4.194304 MHz external clock applied on pin OSC 1. The OSC2 pin should be left open.

For MT317xB devices, the CLK input is driven directly by an 4.194304 MHz external digital clock.

# Applications

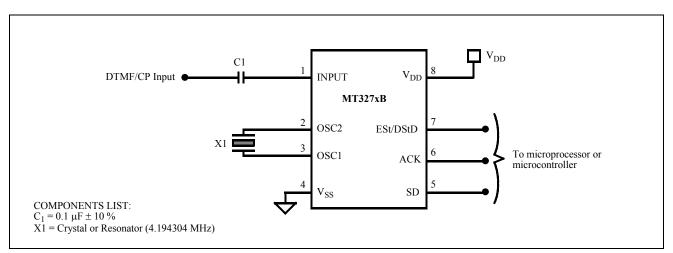

The circuit shown in Figure 3 illustrates the use of a MT327xB in a typical receiver application. It requires only a coupling capacitor (C1) and a crystal or ceramic resonator (X1) to complete the circuit.

The MT3x70B is designed for user who wishes to tailor the guard time for specific applications. When a DTMF signal is present, the ESt pin will go high. An external microcontroller monitors ESt in real time for a period of time set by the user. A guard time algorithm must be implemented such that DTMF signals not meeting the timing requirements are rejected. The MT3x71B uses an internal counter to provide a preset DTMF validation period. It requires no external components. The DStD output high indicates that a valid DTMF digit has been detected.

The 4.194304 MHz frequency has a secondary advantage in some applications where a real time clock is required. A 22-bit counter will count 4,194,304 cycles to provide a one second time base.

Figure 3 - Application Circuit for MT327xB

|   | Parameter                              | Symbol              | Min. | Max. | Units |

|---|----------------------------------------|---------------------|------|------|-------|

| 1 | DC Power Supply Voltage                | $V_{DD}$ - $V_{SS}$ |      | 6    | V     |

| 2 | Voltage on any pin (other than supply) | V <sub>I/O</sub>    | -0.3 | 6.3  | V     |

| 3 | Current at any pin (other than supply) | I <sub>I/O</sub>    |      | 10   | mA    |

| 4 | Storage temperature                    | Τ <sub>S</sub>      | -65  | 150  | °C    |

| 5 | Package power dissipation              | P <sub>D</sub>      |      | 500  | mW    |

### Absolute Maximum Ratings<sup>†</sup> - Voltages are with respect to V<sub>SS</sub>=0V unless otherwise stated.

† Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

#### Recommended Operating Conditions - Voltages are with respect to $V_{SS}$ =0V unless otherwise stated

|   | Parameter                      | Sym.             | Min. | Typ.‡    | Max. | Units | Test Conditions |

|---|--------------------------------|------------------|------|----------|------|-------|-----------------|

| 1 | Positive Power Supply          | $V_{DD}$         | 4.75 | 5.0      | 5.25 | V     |                 |

| 2 | Oscillator Clock Frequency     | f <sub>OSC</sub> |      | 4.194304 |      | MHz   |                 |

| 3 | Oscillator Frequency Tolerance | $\Delta f_{OSC}$ |      |          | ±0.1 | %     |                 |

| 4 | Operating Temperature          | Τ <sub>d</sub>   | -40  | 25       | 85   | °C    |                 |

‡ Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

# **DC Electrical Characteristics** - Voltages are with respect to $V_{DD}$ =5V $\pm$ 5%, $V_{SS}$ =0V, and temperature -40 to 85°C, unless otherwise stated.

|    | Characteristics                        | Sym.             | Min. | Typ.‡ | Max. | Units | Test Conditions                                                         |

|----|----------------------------------------|------------------|------|-------|------|-------|-------------------------------------------------------------------------|

| 1  | Operating supply current               | I <sub>DD</sub>  |      | 3     | 8    | mA    |                                                                         |

| 2  | Standby supply current                 | I <sub>DDQ</sub> |      | 30    | 100  | μA    | PWDN=5V, ACK=0V<br>ESt/DStD = SD = 0V                                   |

| 3a | Input logic 1                          | V <sub>IH</sub>  | 4.0  |       |      | V     |                                                                         |

| 3b | Input logic 1<br>(for OSC1 input only) | V <sub>IH</sub>  | 3.5  |       |      | V     | MT327xB/MT337xB                                                         |

| 4a | Input logic 0                          | V <sub>IL</sub>  |      |       | 1.0  | V     |                                                                         |

| 4b | Input logic 0<br>(for OSC1 input only) | V <sub>IL</sub>  |      |       | 1.5  | V     | MT327xB/MT337xB                                                         |

| 5  | Input impedance (pin 1)                | R <sub>IN</sub>  | 50   |       |      | kW    |                                                                         |

| 6  | Pull-down Current<br>(PWDN, ACK pins)  | I <sub>PD</sub>  |      | 25    |      | mA    | with internal pull-down<br>resistor of approx. 200 kΩ.<br>PWDN/ACK = 5V |

| 7  | Output high (source) current           | I <sub>OH</sub>  | 0.4  | 4.0   |      | mA    | V <sub>OUT</sub> =V <sub>DD</sub> -0.4V                                 |

| 8  | Output low (sink) current              | I <sub>OL</sub>  | 1.0  | 9.0   |      | mA    | V <sub>OUT</sub> =V <sub>SS</sub> +0.4V                                 |

‡ Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

|            | Characteristics                                             | Sym.             | Min.        | Typ.‡ | Max.           | Units                    | Test Conditions*                                          |

|------------|-------------------------------------------------------------|------------------|-------------|-------|----------------|--------------------------|-----------------------------------------------------------|

| 1          | Valid input signal level<br>(each tone of composite signal) |                  | -50<br>2.45 |       | 0<br>775       | dBm<br>mV <sub>RMS</sub> | 1,2,3,5,6,12                                              |

| 2          | Positive twist accept                                       |                  |             |       | 8              | dB                       | 1,2,3,4,11,12,15                                          |

| 3          | Negative twist accept                                       |                  |             |       | 8              | dB                       | 1,2,3,4,11,12,15                                          |

| 4          | Frequency deviation accept                                  |                  | ±1.5%± 2Hz  |       |                |                          | 1,2,3,5,12                                                |

| 5          | Frequency deviation reject                                  |                  | ±3.5%       |       |                |                          | 1,2,3,5,12,15                                             |

| 6          | Third tone tolerance                                        |                  |             | -16   |                | dB                       | 1,2,3,4,5,12                                              |

| 7          | Noise tolerance                                             |                  |             | -12   |                | dB                       | 7,9,12                                                    |

| 8          | Dial tone tolerance                                         |                  |             | +15   |                | dB                       | 8,10,12                                                   |

| 9          | Supervisory tones detect level (Total power)                |                  | -35         |       |                | dBm                      | 16                                                        |

| 10         | Supervisory tones reject level                              |                  |             |       | -50            | dBm                      | 16                                                        |

| 11         | Energy detector attack time                                 | t <sub>SA</sub>  |             | 1.0   | 6.5            | ms                       | 16                                                        |

| 12         | Energy detector decay time                                  | t <sub>SD</sub>  | 3           |       | 25             | ms                       | 16                                                        |

| 13a<br>13b | Powerdown time<br>Powerup time                              |                  |             |       | 10<br>30<br>50 | ms<br>ms<br>ms           | IDDQ ≤ 100µA<br>MT3170B/3370B<br>MT3171B/3371B<br>Note 14 |

| 14         | Tone present detect time (ESt logic output)                 | t <sub>DP</sub>  | 3           | 13    | 20             | ms                       | MT3x70B                                                   |

| 15         | Tone absent detect time (ESt logic output)                  | t <sub>DA</sub>  |             | 3     | 15             | ms                       | MT3x70B                                                   |

| 16         | Tone duration accept<br>(DStD logic output)                 | t <sub>REC</sub> |             |       | 40             | ms                       | MT3x71B                                                   |

| 17         | Tone duration reject<br>(DStD logic output)                 | t <sub>REC</sub> | 20          |       |                | ms                       | MT3x71B                                                   |

AC Electrical Characteristics - voltages are with respect to  $V_{DD}$ =5V±5%,  $V_{SS}$ =0V and temperature -40 to +85°C unless otherwise stated.

|    | Characteristics                                | Sym.             | Min. | Typ.‡ | Max. | Units | Test Conditions*                |

|----|------------------------------------------------|------------------|------|-------|------|-------|---------------------------------|

| 18 | Interdigit pause accept (DStD logic output)    | t <sub>ID</sub>  |      |       | 40   | ms    | MT3x71B                         |

| 19 | Interdigit pause reject (DStD<br>logic output) | t <sub>DO</sub>  | 20   |       |      | ms    | MT3x71B                         |

| 20 | Data shift rate 40-60% duty cycle              | f <sub>ACK</sub> |      | 1.0   | 3.0  | MHz   | 13,15                           |

| 21 | Propagation delay<br>(ACK to Data Bit)         | t <sub>PAD</sub> |      | 100   | 140  | ns    | 1MHz f <sub>ACK,</sub><br>13,15 |

| 22 | Data hold time (ACK to SD)                     | t <sub>DH</sub>  | 30   | 50    |      | ns    | 13,15                           |

AC Electrical Characteristics - voltages are with respect to  $V_{DD}$ =5V±5%,  $V_{SS}$ =0V and temperature -40 to +85°C unless otherwise stated.

‡ Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing

dBm refers to a reference power of 1 mW delivered into a 600 ohms load.

Data sequence consists of all DTMF digits.

Tone on = 40 ms, tone off = 40 ms.

Signal condition consists of nominal DTMF frequencies.

Both topos in composite signal have a parallelement. **Test Conditions**

Both tones in composite signal have an equal amplitude.

Tone pair is deviated by ±1.5%± 2 Hz.

Bandwidth limited (0-3 kHz) Gaussian noise.

8. Precise dial tone frequencies are 350 Hz and 440 Hz (± 2%).

9. Referenced to lowest level frequency component in DTMF signal.

10. Referenced to the minimum valid accept level.

Referenced to the minimum valid accept level.

Both tones must be within valid input signal range.

External guard time for MT3x70B = 20 ms.

Timing parameters are measured with 70pF load at SD output.

Time duration between PWDN pin changes from '1' to '0' and ESt/DStD becomes active.

Guaranteed by design and characterization. Not subject to production testing.

Value measured with an applied tone of 450 Hz.

$t_{SD}$  - supervisory tone integrator decay time (MT3x7xB).

#### Figure 5 - ACK to SD Timing

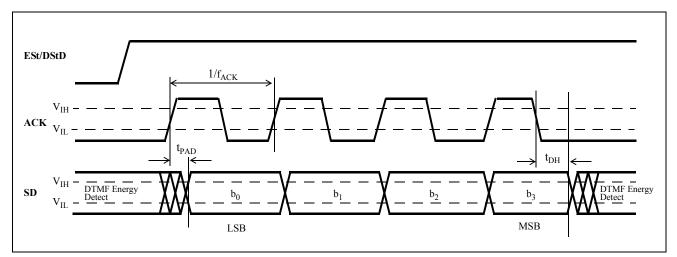

|                                   |              | ol Dime  |       |  | Altern. Dimensions<br>in inches |         |       |  |

|-----------------------------------|--------------|----------|-------|--|---------------------------------|---------|-------|--|

| Symbol                            | in ı         | millimet | res   |  |                                 |         |       |  |

|                                   | MIN          | Nominal  | MAX   |  | MIN                             | Nominal | MAX   |  |

| Α                                 | 2.35         |          | 2.65  |  | 0.093                           |         | 0.104 |  |

| A1                                | 0.10         |          | 0.30  |  | 0.004                           |         | 0.012 |  |

| A2                                | 2.25         |          | 2.35  |  | 0.089                           |         | 0.092 |  |

| D                                 | 11.35        |          | 11.75 |  | 0.447                           |         | 0.463 |  |

| Н                                 | 10.00        |          | 10.65 |  | 0.394                           |         | 0.419 |  |

| Ε                                 | 7.40         |          | 7.60  |  | 0.291                           |         | 0.299 |  |

| L                                 | 0.40         |          | 1.27  |  | 0.016                           |         | 0.050 |  |

| е                                 | 1.1          | 27 BS    | C.    |  | 0.050 BSC.                      |         |       |  |

| b                                 | 0.33         |          | 0.51  |  | 0.013                           |         | 0.020 |  |

| С                                 | 0.23         |          | 0.32  |  | 0.009                           |         | 0.013 |  |

| θ                                 | 0°           |          | 8°    |  | 0°                              |         | 8°    |  |

| h                                 | 0.25         |          | 0.75  |  | 0.010                           |         | 0.029 |  |

|                                   | Pin features |          |       |  |                                 |         |       |  |

| Ν                                 | 18           |          |       |  |                                 |         |       |  |

| Conforms to JEDEC MS-013AB Iss. C |              |          |       |  |                                 |         |       |  |

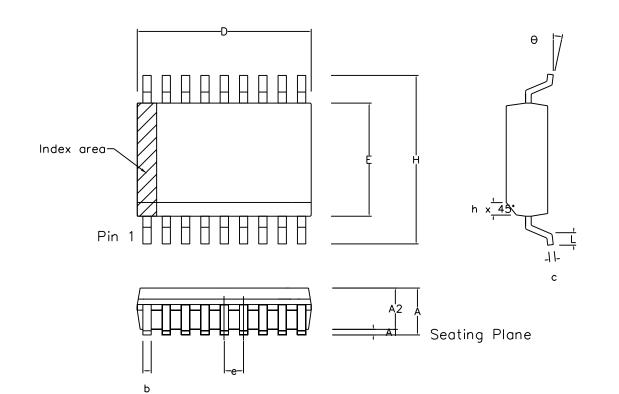

#### Notes:

- 1. The chamfer on the body is optional. If not present, a visual index feature, e.g. a dot, must be located within the cross-hatched area.

- 2. Controlling dimensions are in millimeters

- 3. Dimension D do not include mould flash, protusion or gate burrs. These shall not exceed 0.006" per side.

- 4. Dimension E1 do not include inter-lead flash or protusion. These shall not exceed 0.010" per side.

- 5. Dimension b does not include dambar protusion / intrusion. Allowable dambar protusion shall be 0.004" total in excess of b dimension.

| © Zarlink Semiconductor 2002 All rights reserved. |        |         |         |  |               |                        | Package Code                        |

|---------------------------------------------------|--------|---------|---------|--|---------------|------------------------|-------------------------------------|

| ISSUE                                             | 1      | 2       | 3       |  |               | Previous package codes | Package Outline for                 |

| ACN                                               | 6746   | 201940  | 212432  |  | SEMICONDUCTOR | MP/S                   | 18 lead SOIC<br>(0.300" Body Width) |

| DATE                                              | 7Apr95 | 27Feb97 | 25Mar02 |  | SEMICONDUCTOR | ,                      |                                     |

| APPRD.                                            |        |         |         |  |               |                        | GPD00014                            |

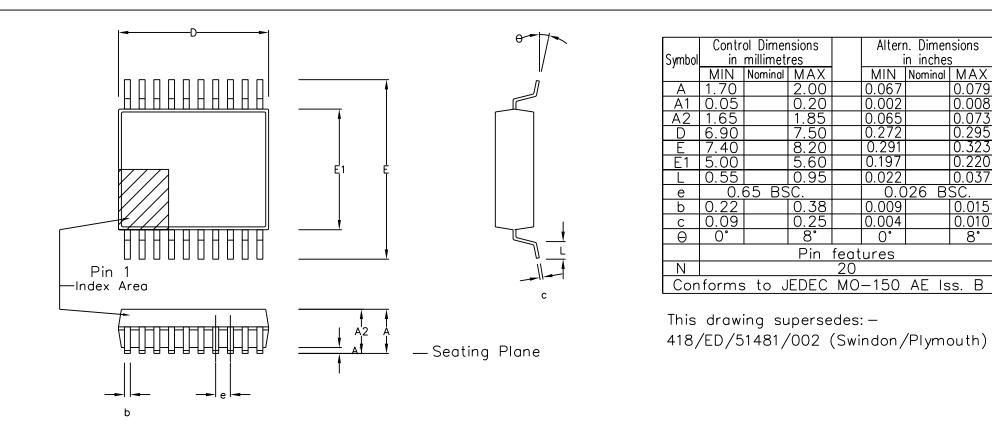

#### Notes:

- 1. A visual index feature, e.g. a dot, must be located within the cross-hatched area.

- 2. Controlling dimension are in millimeters.

- 3. Dimensions D and E1 do not include mould flash or protusion. Mould flash or protusion shall not exceed

- 0.20 mm per side. D and E1 are maximum plastic body size dimensions including mould mismatch.

4. Dimension b does not include dambar protusion/intrusion. Allowable dambar protusion shall be 0.13 mm total in excess of b dimension. Dambar intrusion shall not reduce dimension b by more than 0.07 mm.

| © Zarlink Semiconductor 2002 All rights reserved. |         |         |        |  |               |                        | Package Code                |

|---------------------------------------------------|---------|---------|--------|--|---------------|------------------------|-----------------------------|

| ISSUE                                             | 1       | 2       | 3      |  |               | Previous package codes | Package Outline for 20 lead |

| ACN                                               | 201933  | 205234  | 212477 |  | SEMICONDUCTOR |                        | SSOP (5.3mm Body Width)     |

| DATE                                              | 27Feb97 | 25Sep98 | 3Apr02 |  |               |                        |                             |

| APPRD.                                            |         |         |        |  |               |                        | GPD00294                    |

# For more information about all Zarlink products visit our Web Site at

# www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sub>2</sub>C components conveys a licence under the Philips I<sub>2</sub>C Patent rights to use these components in and I<sub>2</sub>C System, provided that the system conforms to the I<sub>2</sub>C Standard Specification as defined by Philips.

Zarlink, ZL, the Zarlink Semiconductor logo and the Legerity logo and combinations thereof, VoiceEdge, VoicePort, SLAC, ISLIC, ISLAC and VoicePath are trademarks of Zarlink Semiconductor Inc.

**TECHNICAL DOCUMENTATION - NOT FOR RESALE**