Click here to ask an associate for production status of specific part numbers.

## **DS28C16**

# I<sup>2</sup>C Low-Voltage SHA-3 Authenticator

## **General Description**

The DS28C16 secure authenticator combines FIPS202-compliant Secure Hash Algorithm (SHA-3) challenge and response authentication with secured EEP-ROM.

The device provides a core set of cryptographic tools derived from integrated blocks including a SHA-3 engine, 256 bits of secured user EEPROM, a decrement-only counter, and a unique 64-bit ROM identification number (ROM ID). The unique ROM ID is used as a fundamental input parameter for cryptographic operations and serves as an electronic serial number within the application.

## **Applications**

- Medical Tools/Accessories Authentication and Calibration

- Accessory and Peripheral Secure Authentication

- Battery Authentication and Charge Cycle Tracking

Request DS28C16

Security User Guide

### **Benefits and Features**

- Robust Countermeasures Protect Against Security Attacks

- All Stored Data Cryptographically Protected from Discovery

- Efficient Secure Hash Algorithm to Authenticate Peripherals

- FIPS 202-Compliant SHA-3 Algorithm for Challenge/Response Authentication

- FIPS 198-Compliant Keyed-Hash Message Authentication Code (HMAC)

- Supplemental Features Enable Easy Integration into End Applications

- 17-Bit, One-Time Settable, Nonvolatile Decrement-Only Counter with Authenticated Read

- Secure Storage for Secrets

- · 256 Bits of Secure EEPROM for User Data

- Unique and Unalterable Factory Programmed 64-Bit Identification Number (ROM ID)

- I<sup>2</sup>C Communications up to 1MHz

- Operating Range: 1.62V to 3.63V, -40°C to +85°C

- 8-Pin, 2mm x 2mm TDFN-EP Package

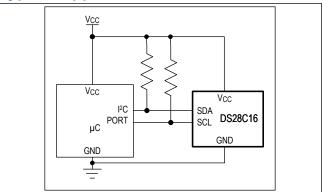

# **Typical Application Circuit**

# **Absolute Maximum Ratings**

| Voltage Range on Any Pin Relative to GND0.5V to 4.0V | Storage Temperature Range40°C to +125°C |

|------------------------------------------------------|-----------------------------------------|

| Maximum Current into Any Pin20mA to 20mA             | Lead Temperature (soldering, 10s)+300°C |

| Operating Temperature Range40°C to +85°C             | Soldering Temperature (reflow)+260°C    |

| Junction Temperature+150°C                           |                                         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **Package Information**

#### 8 TDFN-EP

| Package Code                            | T822+3C        |  |  |  |

|-----------------------------------------|----------------|--|--|--|

| Outline Number                          | <u>21-0168</u> |  |  |  |

| Land Pattern Number                     | <u>90-0065</u> |  |  |  |

| Thermal Resistance, Single-Layer Board: |                |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> )  | _              |  |  |  |

| Junction to Case (θ <sub>JC</sub> )     | _              |  |  |  |

| Thermal Resistance, Four-Layer Board:   |                |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> )  | 85.1°C/W       |  |  |  |

| Junction to Case (θ <sub>JC</sub> )     | 20.8°C/W       |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

### **Electrical Characteristics**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                                          | SYMBOL            | CONDITIONS              | MIN                      | TYP                       | MAX                      | UNITS |

|----------------------------------------------------|-------------------|-------------------------|--------------------------|---------------------------|--------------------------|-------|

| Supply Voltage                                     | V <sub>CC</sub>   | ( <u>Note 1</u> )       | 1.62                     | 3.3                       | 3.63                     | V     |

| Supply Current                                     | Icc               | Standby                 |                          | 3.5                       | 12                       | μΑ    |

|                                                    |                   | Communicating (Note 2)  |                          |                           | 60                       |       |

| I <sup>2</sup> C SCL AND SDA PINS                  | ( <u>Note 3</u> ) |                         | ·                        |                           |                          |       |

| Low-Level Input Voltage                            | V <sub>IL</sub>   |                         | -0.3                     |                           | 0.3 ×<br>V <sub>CC</sub> | V     |

| High-Level Input Voltage                           | V <sub>IH</sub>   | V <sub>CC</sub> > 1.98V | 0.7 ×<br>V <sub>CC</sub> |                           | V <sub>CC</sub> + 0.3    | - V   |

|                                                    |                   | V <sub>CC</sub> ≤ 1.98V | 0.8 ×<br>V <sub>CC</sub> |                           | V <sub>CC</sub> + 0.3    |       |

| Hysteresis of Schmitt<br>Trigger Inputs            | V <sub>HYS</sub>  | ( <u>Note 4</u> )       |                          | 0.05 ×<br>V <sub>CC</sub> |                          | V     |

| Low-Level Output<br>Voltage at 4mA Sink<br>Current | V <sub>OL</sub>   | ( <u>Note 5</u> )       |                          |                           | 0.4                      | >     |

# **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                                                                                                    | SYMBOL              | CONDITIONS                                | MIN  | TYP | MAX  | UNITS |

|--------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------------------|------|-----|------|-------|

| Output Fall Time from V <sub>IH(MIN)</sub> to V <sub>IL(MAX)</sub> with a Bus Capacitance from 10pF to 400pF | t <sub>OF</sub>     | ( <u>Note 4</u> )                         |      | 30  |      | ns    |

| Pulse Width of Spikes<br>that are Suppressed by<br>the Input Filter                                          | t <sub>SP</sub>     |                                           |      |     | 50   | ns    |

| Input Current with an Input Voltage Between 0.1V <sub>CC(MAX)</sub> and 0.9V <sub>CC(MAX)</sub>              | lį                  | ( <u>Note 4, Note 6</u> )                 | -1   |     | +1   | μА    |

| Input Capacitance                                                                                            | C <sub>I</sub>      | ( <u>Note 4</u> )                         |      | 10  |      | pF    |

| SCL Clock Frequency                                                                                          | f <sub>SCL</sub>    | ( <u>Note 1</u> )                         |      |     | 1    | MHz   |

| Hold Time (Repeated)<br>START Condition                                                                      | t <sub>HD:STA</sub> |                                           | 0.45 |     |      | μs    |

| Low Period of the SCL<br>Clock                                                                               | t <sub>LOW</sub>    | ( <u>Note 7</u> )                         | 0.65 |     |      | μs    |

| High Period of the SCL<br>Clock                                                                              | tHIGH               |                                           | 0.35 |     |      | μs    |

| Setup Time for a<br>Repeated START<br>Condition                                                              | <sup>t</sup> su:sta |                                           | 0.35 |     |      | μs    |

| Data Hold Time                                                                                               | t <sub>HD:DAT</sub> | (Note 4, Note 7, Note 8)                  |      |     | 0.35 | μs    |

| Data Setup Time                                                                                              | t <sub>SU:DAT</sub> | ( <u>Note 7</u> , <u>Note 9</u> )         | 100  |     |      | ns    |

| Setup Time for STOP<br>Condition                                                                             | tsu:sto             |                                           | 0.35 |     |      | μs    |

| Bus Free Time Between<br>a STOP and START<br>Condition                                                       | t <sub>BUF</sub>    |                                           | 0.6  |     |      | μs    |

| Capacitive Load for<br>Each Bus Line                                                                         | $C_{B}$             | ( <u>Note 1</u> , <u>Note 10</u> )        |      |     | 400  | pF    |

| Warm-Up Time                                                                                                 | toscwup             | ( <u>Note 1</u> , <u>Note 11</u> )        |      |     | 1    | ms    |

| CRYPTO FUNCTIONS                                                                                             |                     |                                           | •    |     |      |       |

| Computation Current                                                                                          | I <sub>CMP</sub>    |                                           |      |     | 3    | mA    |

| Read Memory Time                                                                                             | t <sub>RM</sub>     |                                           |      |     | 5    | ms    |

| Write Memory Time                                                                                            | t <sub>WM</sub>     |                                           |      |     | 60   | ms    |

| Short Write Memory<br>Time                                                                                   | t <sub>WMS</sub>    |                                           |      |     | 15   | ms    |

| Computation Time                                                                                             | t <sub>CMP</sub>    |                                           |      |     | 15   | ms    |

| EEPROM                                                                                                       |                     |                                           |      |     |      |       |

| Write/Erase Cycles (Endurance)                                                                               | N <sub>CY</sub>     | ( <u>Note 12</u> )                        | 100k |     |      |       |

| Data Retention                                                                                               | t <sub>DR</sub>     | T <sub>A</sub> = +85°C ( <u>Note 13</u> ) | 10   |     |      | years |

## DS28C16

# I<sup>2</sup>C Low-Voltage SHA-3 Authenticator

- Note 1: System requirement.

- Note 2: Operating current during I<sup>2</sup>C communication at 1MHz with < 25ns rise and fall times on SDA and SCL.

- **Note 3:** All I<sup>2</sup>C timing values are referred to V<sub>IH(MIN)</sub> and V<sub>IL(MAX)</sub> levels.

- Note 4: Guaranteed by design and/or characterization only. Not production tested.

- Note 5: The I-V characteristic is linear for voltages less than 1V.

- Note 6: I/O pins of the DS28C16 do not obstruct the SDA and SCL lines if V<sub>CC</sub> is switched off.

- Note 7:  $t_{LOW}$  min =  $t_{HD:DAT}$  max + 200ns for rise or fall time +  $t_{SU:DAT}$  min. Values greater than these can be accommodated by extending  $t_{LOW}$  accordingly.

- Note 8: The DS28C16 provides a hold time of at least 100ns for the SDA signal (referenced to the V<sub>IH(MIN)</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- Note 9: The DS28C16 can be used in a standard-mode  $I^2C$ -bus system, but the requirement  $t_{SU:DAT} \ge 250$ ns must then be met. Also, the acknowledge timing must meet this setup time ( $I^2C$  bus specification Rev. 03, 19 June 2007).

- Note 10:  $C_B$  = Total capacitance of one bus line in pF. The maximum bus capacitance allowable may vary from this value depending on the actual operating voltage and frequency of the application (I<sup>2</sup>C bus specification Rev. 03, 19 June 2007).

- Note 11: I<sup>2</sup>C communication should not take place for at least t<sub>OSCWUP</sub> after V<sub>CC</sub> reaches V<sub>CC(MIN)</sub>.

- Note 12: Write-cycle endurance is tested in compliance with JESD47H.

- Note 13: Data retention is tested in compliance with JESD47H.

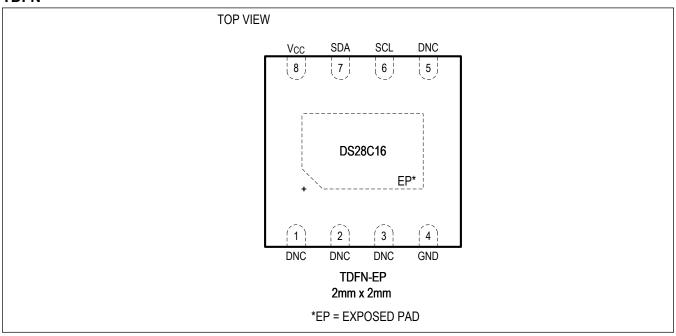

# **Pin Configuration**

## **TDFN**

# **Pin Description**

| PIN    | NAME            | FUNCTION                                                                                                                                                                                       |

|--------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1–3, 5 | DNC             | Do Not Connect                                                                                                                                                                                 |

| 4      | GND             | Ground Reference. Connect all contacts to GND.                                                                                                                                                 |

| 6      | SCL             | I <sup>2</sup> C Clock. Connect to V <sub>CC</sub> with pullup resistor.                                                                                                                       |

| 7      | SDA             | I <sup>2</sup> C Data. Connect to V <sub>CC</sub> with pullup resistor.                                                                                                                        |

| 8      | V <sub>CC</sub> | Supply Voltage                                                                                                                                                                                 |

| _      | EP              | Exposed Pad (TDFN Only). Solder evenly to the board's ground plane for proper operation. Refer to <u>Application Note 3273: Exposed Pads: A Brief Introduction</u> for additional information. |

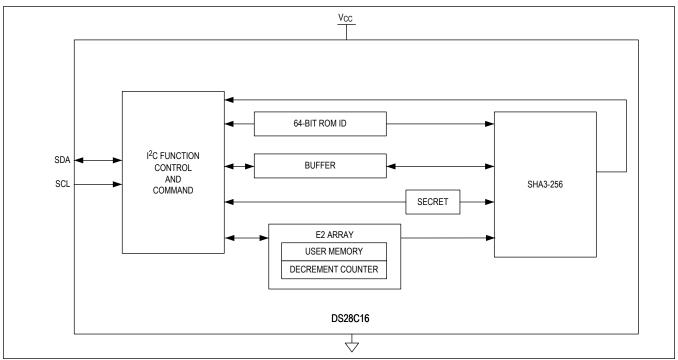

## **Detailed Description**

The DS28C16 integrates the Maxim DeepCover® capability to protect all device stored data from invasive discovery. In addition to the SHA-3 engine for signatures, 256-bit EEPROM for user memory, SHA-3 secret storage, 17-bit decrement counter, and control registers. The device operates from an I<sup>2</sup>C interface.

Figure 1. Block Diagram

### **Design Resource Overview**

Operation of the DS28C16 involves use of device EEPROM and execution of device function commands. The following section provides an overview including the decrement counter. Refer to the <u>DS28C16 Security User Guide</u> for details.

## Memory

A secured EEPROM array provides SHA-3 secret storage, along with a decrement counter, and/or general-purpose, user-programmable memory. Depending on the memory space, there are either default or user-programmable options to set protection modes.

### **Decrement Counter**

The optional 17-bit decrement counter can be written one time on a page of memory. A dedicated device function command is used to decrement the count value by one with each call. Once the count value reaches a value of 0, no additional decrements are possible.

## I<sup>2</sup>C

#### **General Characteristics**

The  $I^2C$  bus uses a data line (SDA) plus a clock signal (SCL) for communication. Both SDA and SCL are bidirectional lines, connected to a positive supply voltage through a pullup resistor. When there is no communication, both lines are high. The output stages of devices connected to the bus must have an open drain or open collector to perform the wired-AND function. Data on the  $I^2C$  bus can be transferred at rates up to 100kbps in standard mode and up to 400kbps in

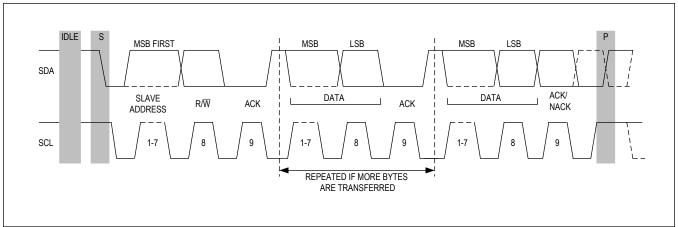

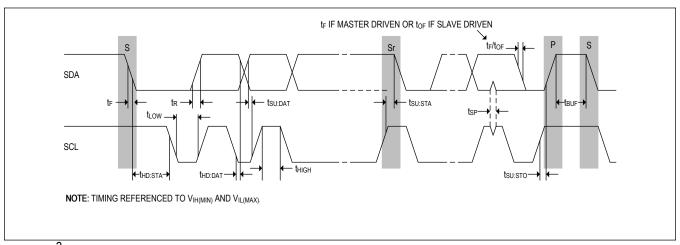

fast mode. The DS28C16 works in both modes or up to a clock rate of 1MHz. A device that sends data on the bus is defined as a transmitter, and a device receiving data is defined as a receiver. The device that controls communication is called a master. Devices controlled by the master are slaves. To be individually accessed, each device must have a slave address that does not conflict with other devices on the bus. Data transfers can be initiated only when the bus is not busy. The master generates the serial clock (SCL), controls the bus access, generates the START and STOP conditions, and determines the number of data bytes transferred between START and STOP (Figure 2). Data is transferred in bytes with the most significant bit being transmitted first. An acknowledge bit follows each byte to allow synchronization between master and slave.

#### **Slave Address**

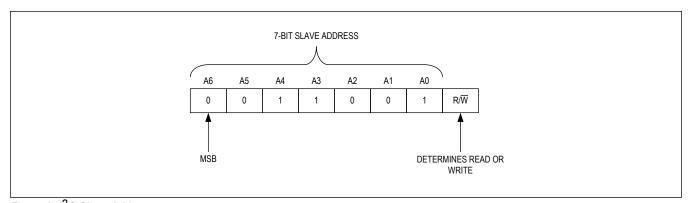

The slave address to which the DS28C16 responds is shown in <u>Figure 3</u>. The slave address is part of the slave address/control byte. The last bit of the slave address/control byte (R/W) defines the data direction. When set to 0, subsequent data flows from master to slave (write access); when set to 1, data flows from slave to master (read access).

Figure 2. I<sup>2</sup>C Protocol Overview

Figure 3. I<sup>2</sup>C Slave Address

### I<sup>2</sup>C Definitions

The following terminology is commonly used to describe I<sup>2</sup>C data transfers. The timing references are defined in <u>Figure</u> 4.

#### **Bus Idle or Not Busy**

Both SDA and SCL are inactive and in their logic-high states.

#### **START Condition**

To initiate communication with a slave, the master must generate a START condition. A START condition is defined as a change in state of SDA from high to low while SCL remains high.

#### **STOP Condition**

To end communication with a slave, the master must generate a STOP condition. A STOP condition is defined as a change in state of SDA from low to high while SCL remains high.

#### **Repeated START Condition**

Repeated STARTs are commonly used for read accesses after having specified a memory address to read from in a preceding write access. The master can use a repeated START condition at the end of a data transfer to immediately initiate a new data transfer following the current one. A repeated START condition is generated the same way as a normal START condition, but without leaving the bus idle after a STOP condition.

#### **Data Valid**

With the exception of the START and STOP condition, transitions of SDA can occur only during the low state of SCL. The data on SDA must remain valid and unchanged during the entire high pulse of SCL plus the required setup and hold time (t<sub>HD:DAT</sub> after the falling edge of SCL and t<sub>SU:DAT</sub> before the rising edge of SCL; see <u>Figure 4</u>). There is one clock pulse per bit of data. Data is shifted into the receiving device during the rising edge of the SCL pulse.

When finished with writing, the master must release the SDA line for a sufficient amount of setup time (minimum  $t_{SU:DAT}$ , +  $t_R$  in Figure 4) before the next rising edge of SCL to start reading. The slave shifts out each data bit on SDA at the falling edge of the previous SCL pulse and the data bit is valid at the rising edge of the current SCL pulse. The master generates all SCL clock pulses, including those needed to read from a slave.

Figure 4. I<sup>2</sup>C Timing Diagram

# **Ordering Information**

| PART NUMBER | TEMP RANGE     | PIN-PACKAGE           |

|-------------|----------------|-----------------------|

| DS28C16Q+T  | -40°C to +85°C | 8 TDFN-EP* (2.5k pcs) |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

<sup>\*</sup>EP = Exposed pad.

## **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                            | PAGES<br>CHANGED |

|--------------------|---------------|----------------------------------------|------------------|

| 0                  | 2/20          | Initial release                        | _                |

| 1                  | 7/20          | Added user guide link                  | 1                |

| 2                  | 10/20         | Updated data sheet title               | All              |

| 3                  | 1/22          | Updated I <sup>2</sup> C Slave Address | 7                |