## Features

- Monolithic Field Programmable System Level Integrated Circuit (FPSLIC<sup>™</sup>)

- AT40K SRAM-based FPGA with Embedded High-performance RISC AVR<sup>®</sup> Core, Extensive Data and Instruction SRAM and JTAG ICE

- 5,000 to 40,000 Gates of Patented SRAM-based AT40K FPGA with FreeRAM<sup>™</sup>

- 2 18.4 Kbits of Distributed Single/Dual Port FPGA User SRAM

- High-performance DSP Optimized FPGA Core Cell

- Dynamically Reconfigurable In-System FPGA Configuration Access Available On-chip from AVR Microcontroller Core to Support Cache Logic<sup>®</sup> Designs

- Very Low Static and Dynamic Power Consumption Ideal for Portable and Handheld Applications

- Patented AVR Enhanced RISC Architecture

- 120+ Powerful Instructions Most Single Clock Cycle Execution

- High-performance Hardware Multiplier for DSP-based Systems

- Approaching 1 MIPS per MHz Performance

- C Code Optimized Architecture with 32 x 8 General-purpose Internal Registers

- Low-power Idle, Power-save and Power-down Modes

- 100 µA Standby and Typical 2-3 mA per MHz Active

- Up to 36 Kbytes of Dynamically Allocated Instruction and Data SRAM

Up to 16 Kbytes x 16 Internal 15 ns Instructions SRAM

- Up to 16 Kbytes x 8 Internal 15 ns Data SRAM

- JTAG (IEEE std. 1149.1 Compliant) Interface

Extensive On abin Debug Support

- Extensive On-chip Debug Support

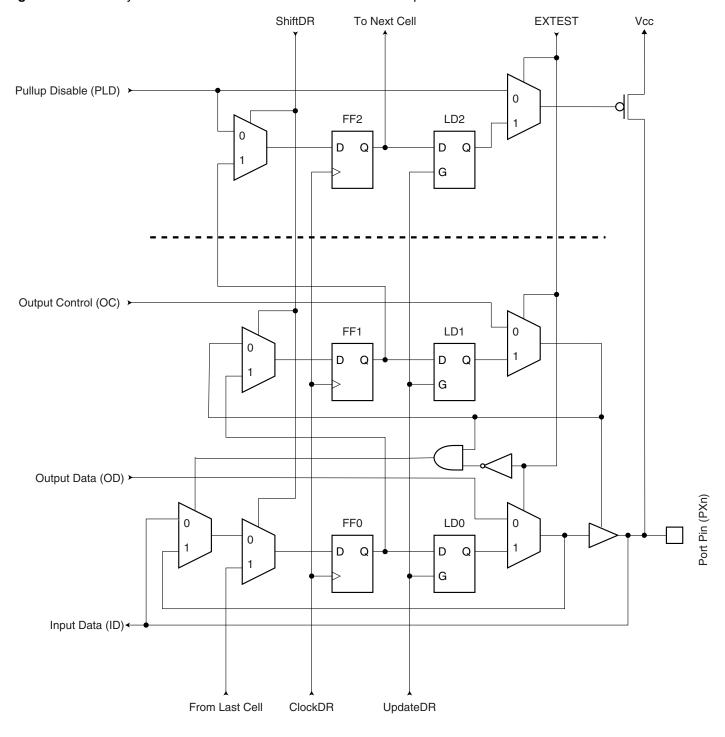

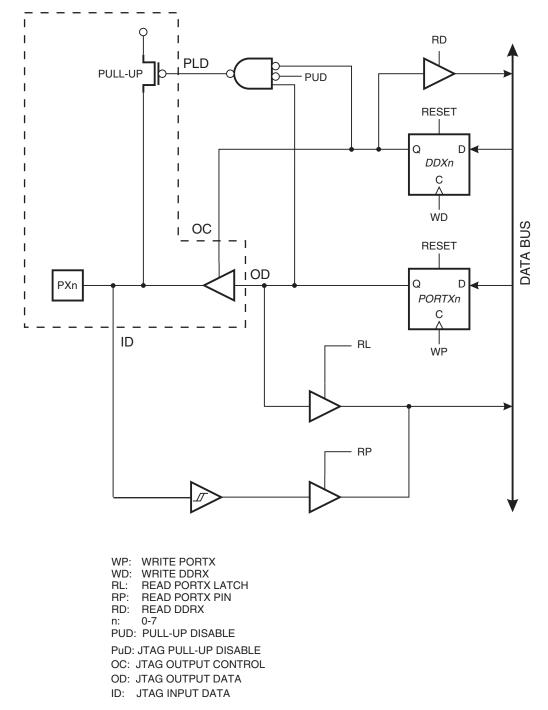

Limited Boundary-scan Capabilities According to the JTAG Standard (AVR Ports)

- AVR Fixed Peripherals

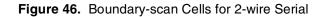

- Industry-standard 2-wire Serial Interface

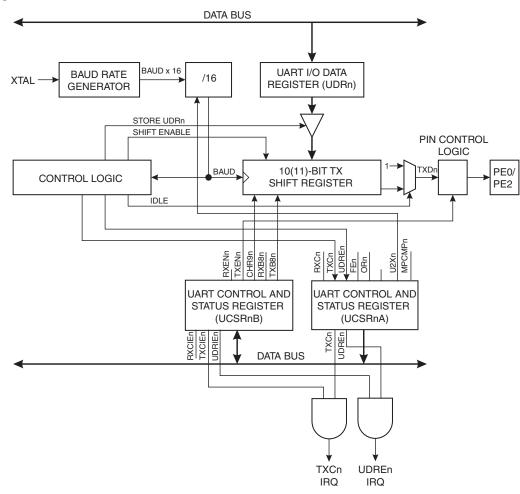

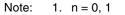

- Two Programmable Serial UARTs

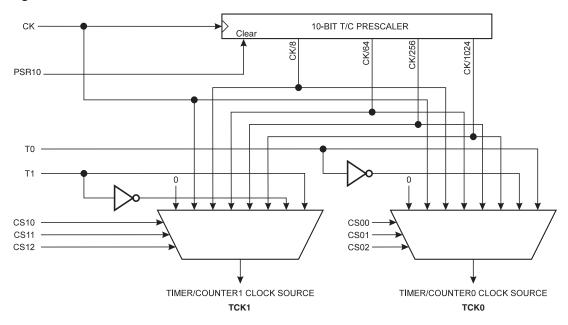

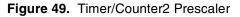

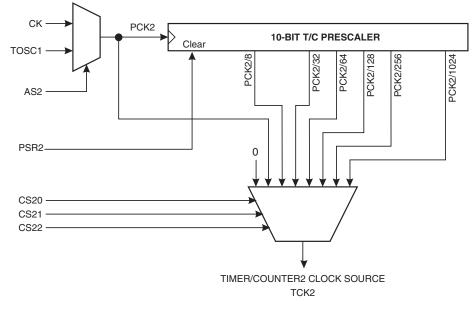

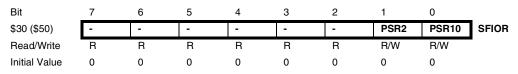

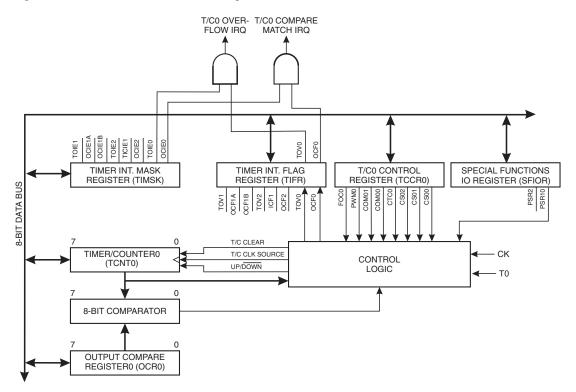

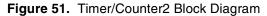

- Two 8-bit Timer/Counters with Separate Prescaler and PWM

- One 16-bit Timer/Counter with Separate Prescaler, Compare, Capture Modes and Dual 8-, 9- or 10-bit PWM

- Support for FPGA Custom Peripherals

- AVR Peripheral Control 16 Decoded AVR Address Lines Directly Accessible to FPGA

- FPGA Macro Library of Custom Peripherals

- 16 FPGA Supplied Internal Interrupts to AVR

- Up to Four External Interrupts to AVR

- 8 Global FPGA Clocks

- Two FPGA Clocks Driven from AVR Logic

- FPGA Global Clock Access Available from FPGA Core

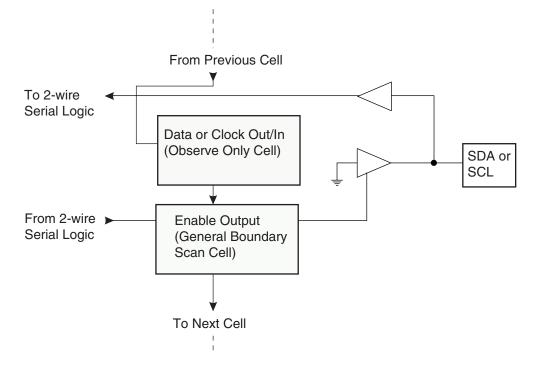

- Multiple Oscillator Circuits

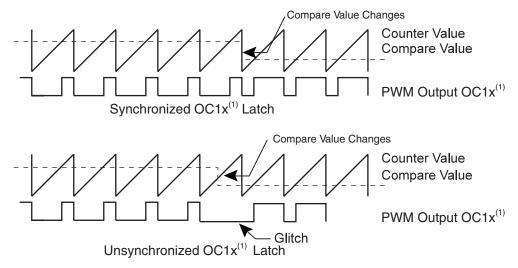

- Programmable Watchdog Timer with On-chip Oscillator

- Oscillator to AVR Internal Clock Circuit

- Software-selectable Clock Frequency

- Oscillator to Timer/Counter for Real-time Clock

- V<sub>cc</sub>: 3.0V 3.6V

- 3.3V 33 MHz PCI-compliant FPGA I/O

- 20 mA Sink/Source High-performance I/O Structures

- All FPGA I/O Individually Programmable

- High-performance, Low-power 0.35µ CMOS Five-layer Metal Process

- State-of-the-art Integrated PC-based Software Suite including Co-verification

- 5V I/O Tolerant

5K - 40K Gates of AT40K FPGA with 8-bit **AVR**<sup>®</sup> Microcontroller, up to 36K Bytes of SRAM and On-chip JTAG ICE

AT94KAL Series Field Programmable System Level Integrated Circuit

## Description

The AT94KAL Series FPSLIC family shown in Table 1 is a combination of the popular Atmel AT40K Series SRAM FPGAs and the high-performance Atmel AVR 8-bit RISC microcontroller with standard peripherals. Extensive data and instruction SRAM as well as device control and management logic are included on this monolithic device, fabricated on Atmel's 0.35µ five-layer metal CMOS process.

The AT40K FPGA core is a fully 3.3V PCI-compliant, SRAM-based FPGA with distributed 10 ns programmable synchronous/asynchronous, dual-port/single-port SRAM, 8 global clocks, Cache Logic ability (partially or fully reconfigurable without loss of data) and 5,000 to 40,000 usable gates.

| Device                              |             | AT94K05AL                 | AT94K10AL                 | AT94K40AL                 |

|-------------------------------------|-------------|---------------------------|---------------------------|---------------------------|

| FPGA Gates                          |             | 5K 10K                    |                           | 40K                       |

| FPGA Core Cells                     |             | 256                       | 576                       | 2304                      |

| FPGA SRAM Bits                      |             | 2048                      | 4096                      | 18432                     |

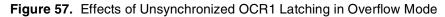

| FPGA Registers (T                   | otal)       | 436                       | 846                       | 2862                      |

| Maximum FPGA U                      | ser I/O     | 96                        | 144                       | 288                       |

| AVR Programmable                    | e I/O Lines | 8                         | 16                        | 16                        |

| Program SRAM                        |             | 4 Kbytes - 16 Kbytes      | 20 Kbytes - 32 Kbytes     | 20 Kbytes - 32 Kbytes     |

| Data SRAM                           |             | 4 Kbytes - 16 Kbytes      | 4 Kbytes- 16 Kbytes       | 4 Kbytes - 16 Kbytes      |

| Hardware Multiplier (8-bit)         |             | Yes                       | Yes                       | Yes                       |

| 2-wire Serial Interface             |             | Yes                       | Yes                       | Yes                       |

| UARTs                               |             | 2                         | 2                         | 2                         |

| Watchdog Timer                      |             | Yes                       | Yes                       | Yes                       |

| Timer/Counters                      |             | 3                         | 3                         | 3                         |

| Real-time Clock                     |             | Yes                       | Yes                       | Yes                       |

| JTAG ICE                            |             | Yes <sup>(1)</sup>        | Yes <sup>(1)</sup>        | Yes <sup>(1)</sup>        |

| Typical AVR<br>throughput           | @ 25 MHz    | 19 MIPS                   | 19 MIPS                   | 19 MIPS                   |

| Operating<br>Voltage <sup>(2)</sup> | AL          | 3.0 - 3.6V <sup>(2)</sup> | 3.0 - 3.6V <sup>(2)</sup> | 3.0 - 3.6V <sup>(2)</sup> |

Table 1. The AT94K Series Characteristics

Notes: 1. FPSLIC parts with JTAG ICE support can be identified by the letter "J" after the device date code, e.g., 4201 (no ICE support) and 4201J (with ICE support), see Figure 1.

FPSLIC devices should be laid out during PCB design to support a split power supply. Please refer to the "Designing in Split Power Supply Support for AT94KAL and AT94SAL Devices" application note, available on the Atmel web site at http://www.atmel.com/atmel/acrobat/doc2308.pdf.

Figure 1. FPSLIC Device Date Code with JTAG ICE Support

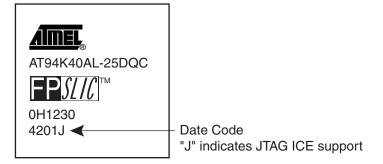

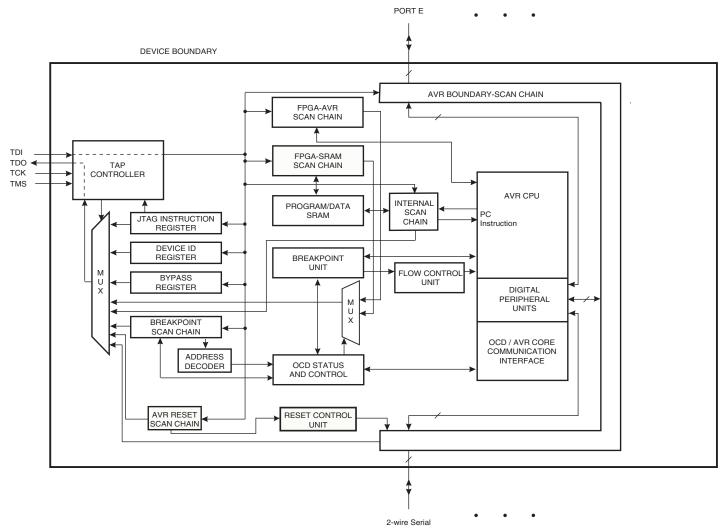

The AT94K series architecture is shown in Figure 2.

Figure 2. AT94K Series Architecture

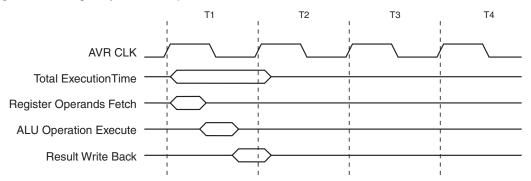

The embedded AVR core achieves throughputs approaching 1 MIPS per MHz by executing powerful instructions in a single-clock cycle, and allows system designers to optimize power consumption versus processing speed. The AVR core is based on an enhanced RISC architecture that combines a rich instruction set with 32 general-purpose working registers. All 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code-efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers at the same clock frequency. The AVR executes out of on-chip SRAM. Both the FPGA configuration SRAM and the AVR instruction code SRAM can be automatically loaded at system power-up using Atmel's In-System Programmable (ISP) AT17 Series EEPROM Configuration Memories or ATFS FPSLIC Support Devices.

State-of-the-art FPSLIC design tools, System Designer<sup>™</sup>, were developed in conjunction with the FPSLIC architecture to help reduce overall time-to-market by integrating microcontroller development and debug, FPGA development and Place and Route, and complete system co-verification in one easy-to-use software tool.

| FPSLIC Device | FPSLIC Support Device | Configuration Data | Spare Memory |

|---------------|-----------------------|--------------------|--------------|

| AT94K05       | ATFS05                | 226520 Bits        | 35624 Bits   |

| AT94K10       | ATFS10                | 430488 Bits        | 93800 Bits   |

| AT94K40       | ATFS40                | 815382 Bits        | 233194 Bits  |

Table 2. ATFS FPSLIC Support Devices

4

| FPGA Core                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                    | The AT40K core can be used for high-performance designs, by implementing a variety of com-<br>pute-intensive arithmetic functions. These include adaptive finite impulse response (FIR) filters, fast Fourier transforms (FFT), convolvers, interpolators, and discrete-cosine transforms (DCT) that are required for video compression and decompression, encryption, convolution and other multimedia applications.                                                                                                        |

| Fast, Flexible and Efficient SRAM                  | The AT40K core offers a patented distributed 10 ns SRAM capability where the RAM can be used without losing logic resources. Multiple independent, synchronous or asynchronous, dual-port or single-port RAM functions (FIFO, scratch pad, etc.) can be created using Atmel's macro generator tool.                                                                                                                                                                                                                          |

| Fast, Efficient<br>Array and Vector<br>Multipliers | The AT40K cores patented 8-sided core cell with direct horizontal, vertical and diagonal cell-<br>to-cell connections implements ultra-fast array multipliers without using any busing resources.<br>The AT40K core's Cache Logic capability enables a large number of design coefficients and<br>variables to be implemented in a very small amount of silicon, enabling vast improvement in<br>system speed.                                                                                                               |

| Cache Logic<br>Design                              | The AT40K FPGA core is capable of implementing Cache Logic (dynamic full/partial logic reconfiguration, without loss of data, on-the-fly) for building adaptive logic and systems. As new logic functions are required, they can be loaded into the logic cache without losing the data already there or disrupting the operation of the rest of the chip; replacing or complementing the active logic. The AT40K FPGA core can act as a reconfigurable resource within the FPSLIC environment.                              |

| Automatic<br>Component<br>Generators               | The AT40K is capable of implementing user-defined, automatically generated, macros; speed<br>and functionality are unaffected by the macro orientation or density of the target device. This<br>enables the fastest, most predictable and efficient FPGA design approach and minimizes<br>design risk by reusing already proven functions. The Automatic Component Generators work<br>seamlessly with industry-standard schematic and synthesis tools to create fast, efficient<br>designs.                                  |

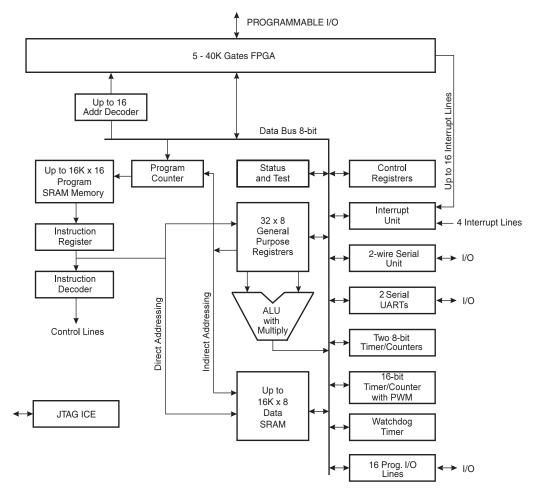

|                                                    | The patented AT40K architecture employs a symmetrical grid of small yet powerful cells con-<br>nected to a flexible busing network. Independently controlled clocks and resets govern every<br>column of four cells. The FPSLIC device is surrounded on three sides by programmable I/Os.                                                                                                                                                                                                                                    |

|                                                    | Core usable gate counts range from 5,000 to 40,000 gates and 436 to 2,864 registers. Pin locations are consistent throughout the FPSLIC family for easy design migration in the same package footprint.                                                                                                                                                                                                                                                                                                                      |

|                                                    | The Atmel AT40K FPGA core architecture was developed to provide the highest levels of per-<br>formance, functional density and design flexibility. The cells in the FPGA core array are small,<br>efficient and can implement any pair of Boolean functions of (the same) three inputs or any<br>single Boolean function of four inputs. The cell's small size leads to arrays with large numbers<br>of cells. A simple, high-speed busing network provides fast, efficient communication over<br>medium and long distances. |

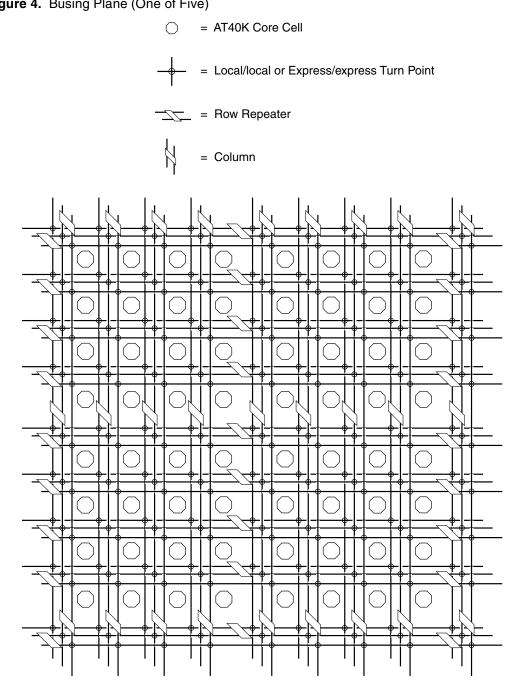

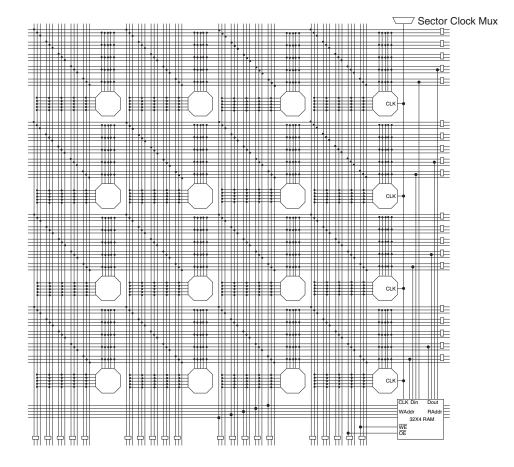

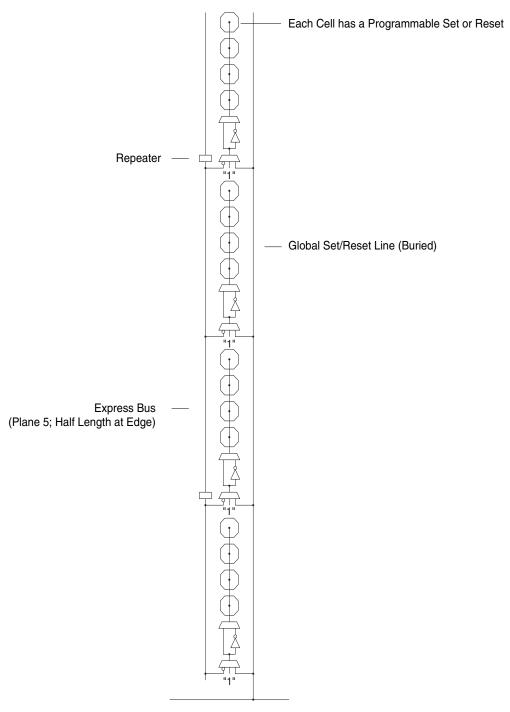

| The Symmetrical<br>Array                           | At the heart of the Atmel FPSLIC architecture is a symmetrical array of identical cells. The array is continuous from one edge to the other, except for bus repeaters spaced every four cells, see Figure 3. At the intersection of each repeater row and column is a 32 x 4 RAM block accessible by adjacent buses. The RAM can be configured as either a single-ported or dual-ported RAM, with either synchronous or asynchronous operation.                                                                              |

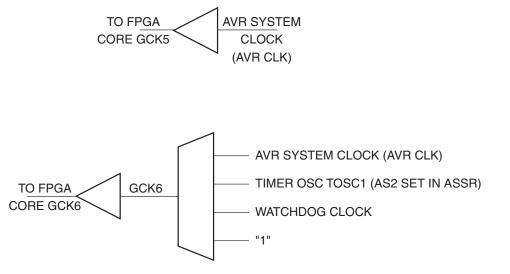

Figure 4 depicts one of five identical FPGA busing planes. Each plane has three bus resources: a local-bus resource (the middle bus) and two express-bus resources. Bus resources are connected via repeaters. Each repeater has connections to two adjacent local-bus segments and two express-bus segments. Each local-bus segment spans four cells and connects to consecutive repeaters. Each express-bus segment spans eight cells and bypasses a repeater. Repeaters regenerate signals and can connect any bus to any other bus (all pathways are legal) on the same plane. Although not shown, a local bus can bypass a repeater via a programmable pass gate, allowing long on-chip tri-state buses to be created. Local/local turns are implemented through pass gates in the cell-bus interface. Express/express turns are implemented through separate pass gates distributed throughout the array.

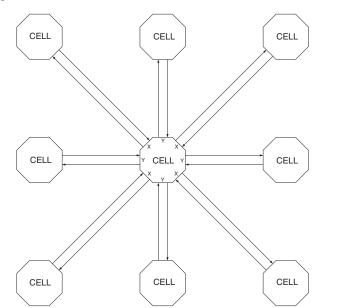

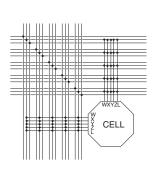

## **Cell Connections** Figure 5(a) depicts direct connections between an FPGA cell and its eight nearest neighbors. Figure 5(b) shows the connections between a cell five horizontal local buses (one per busing plane) and five vertical local buses (one per busing plane).

Figure 5. Cell Connections

(a) Cell-to-Cell Connections

(b) Cell-to-Bus Connections

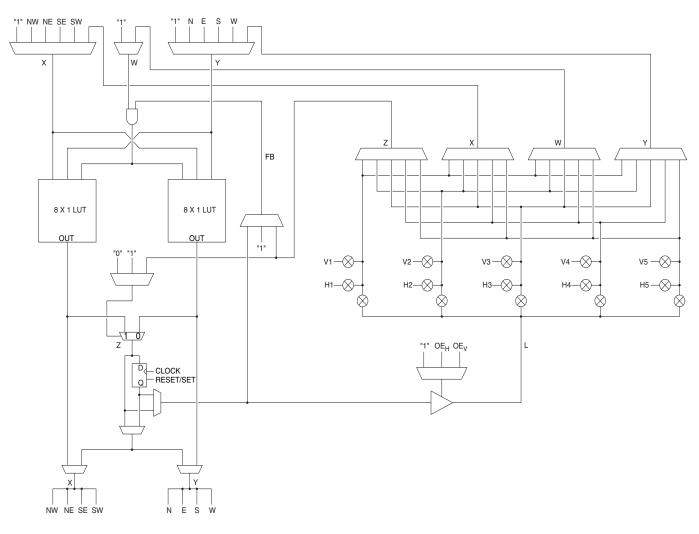

The CellFigure 6 depicts the AT40K FPGA embedded core logic cell. Configuration bits for separate<br/>muxes and pass gates are independent. All permutations of programmable muxes and pass<br/>gates are legal. Vn is connected to the vertical local bus in plane n. Hn is connected to the hor-<br/>izontal local bus in plane n. A local/local turn in plane n is achieved by turning on the two pass<br/>gates connected to Vn and Hn. Up to five simultaneous local/local turns are possible.

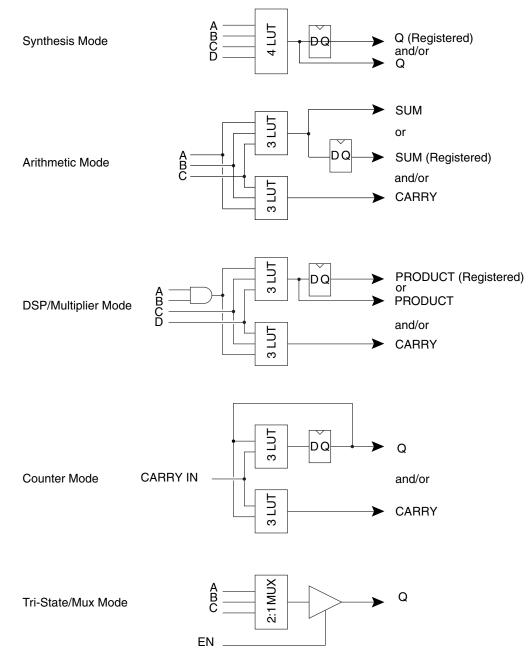

The logic cell can be configured in several "modes". The logic cell flexibility makes the FPGA architecture well suited to all digital design application areas, see Figure 7. The IDS layout tool automatically optimizes designs to utilize the cell flexibility.

### Figure 6. The Cell

- X = Diagonal Direct Connect or Bus

- Y = Orthogonal Direct Connect or Bus

- W = Bus Connection

- Z = Bus Connection

- FB = Internal Feedback

Figure 7. Some Single Cell Modes

RAM

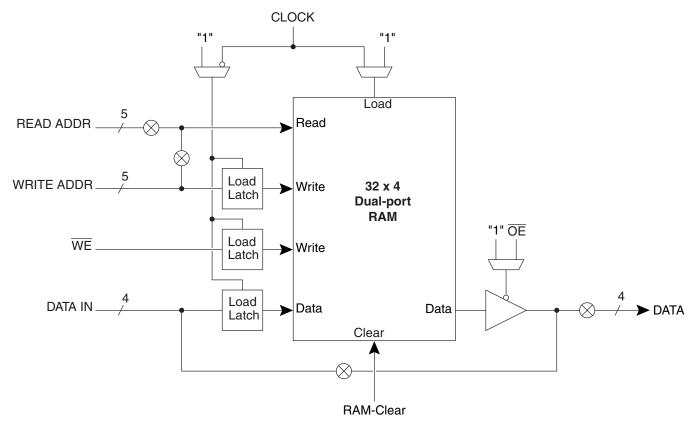

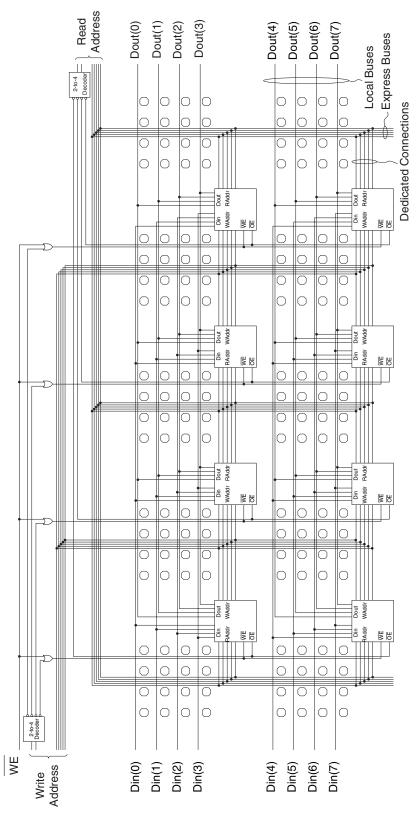

There are two types of RAM in the FPSLIC device: the FreeRAM distributed through the FPGA Core and the SRAM shared by the AVR and FPGA. The SRAM is described in "FPGA/AVR Interface and System Control" on page 21. The 32 x 4 dual-ported FPGA FreeRAM blocks are dispersed throughout the array and are connected in each sector as shown in Figure 8. A four-bit Input Data bus connects to four horizontal local buses (Plane 1) distributed over four sector rows. A four-bit Output Data bus connects to four horizontal local buses (Plane 2) distributed over four sector rows. A five-bit Input-address bus connects to five vertical express buses in the same sector column (column 3). A five-bit Output-address bus connects to five vertical express buses in the same column. WAddr (Write Address) and RAddr (Read Address) alternate positions in horizontally aligned RAM blocks. For the left-

most RAM blocks, RAddr is on the left and WAddr is on the right. For the right-most RAM blocks, WAddr is on the left and RAddr is tied off. For single-ported RAM, WAddr is the READ/WRITE address port and Din is the (bi-directional) data port. The right-most RAM blocks can be used only for single-ported memories. WE and  $\overline{OE}$  connect to the vertical express buses in the same column on Plane V<sub>1</sub> and V<sub>2</sub>, respectively. WAddr, RAddr, WE and  $\overline{OE}$  connect to express buses that are full length at array edge.

Reading and writing the 32 x 4 dual-port RAM are independent of each other. Reading the 32 x 4 dual-port RAM is completely asynchronous. Latches are transparent; when Load is logic 1, data flows through; when Load is logic 0, data is latched. Each bit in the 32 x 4 dual-port RAM is also a transparent latch. The front-end latch and the memory latch together and form an edge-triggered flip-flop. When a bit nibble is (Write) addressed and LOAD is logic 1 and  $\overline{WE}$  is logic 0, DATA flows through the bit. When a nibble is not (Write) addressed or LOAD is logic 0 or  $\overline{WE}$  is logic 1, DATA is latched in the nibble. The two CLOCK muxes are controlled together; they both select CLOCK or they both select "1". CLOCK is obtained from the clock for the sector-column immediately to the left and immediately above the RAM block. Writing any value to the RAM Clear Byte during configuration clears the RAM, see Figure 5 and Figure 6.

Figure 8. FPGA RAM Connections (One RAM Block)

## Figure 9. FreeRAM Logic<sup>(1)</sup>

Note: 1. For dual port, the switches on READ ADDR and DATA OUT would be on. The other two would be off. The reverse is true for single port.

**AT94KAL Series FPSLIC**

Figure 10. FreeRAM Example: 128 x 8 Dual-ported RAM (Asynchronous)<sup>(1)</sup>

Note: 1. These layouts can be generated automatically using the Macro Generators.

## Clocking and Set/Reset

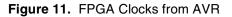

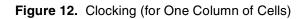

Six of the eight dedicated Global Clock buses (1, 2, 3, 4, 7 and 8) are connected to a dual-use Global Clock pin. In addition, two Global Clock buses (5 and 6) are driven from clock signals generated within the AVR microcontroller core, see Figure 11.

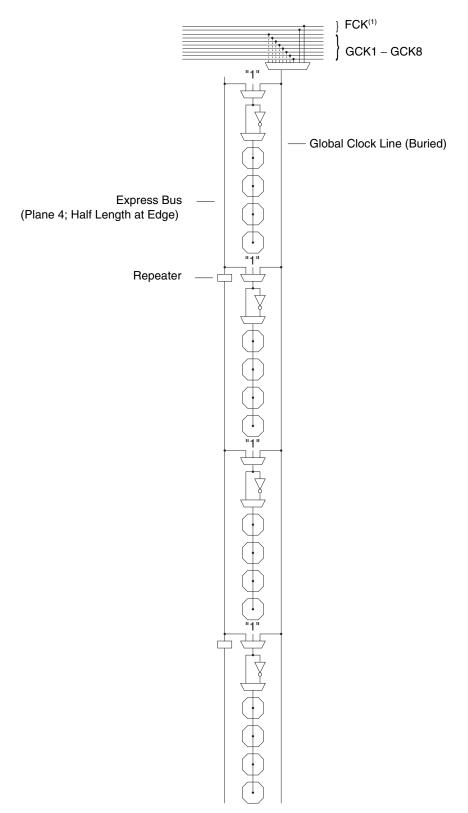

An FPGA core internal signal can be placed on any Global Clock bus by routing that signal to a Global Clock access point in the corners of the embedded core. Each column of the array has a Column Clock selected from one of the eight Global Clock buses. The left edge Column Clock mux has two additional inputs from dual-use pins FCK1, see Figure 8, and FCK2 to provide fast clocking to left-side I/O. Each sector column of four cells can be clocked from a (Plane 4) express bus or from the Column Clock. Clocking to the 4 cells of a sector can be disabled. The Plane 4 express bus used for clocking is half length at the array edge. The clock provided to each sector column of four cells can be either inverted or not inverted. The register in each cell is triggered on a rising clock edge. On power-up, constant "0" is provided to each register's clock pins. A dedicated Global Set/Reset bus, see Figure 9, can be driven by any USER I/O pad, except those used for clocking, Global or Fast. An internal signal can be placed on the Global Set/Reset bus by routing that signal to the pad programmed as the Global Set/Reset input. Global Set/Reset is distributed to each column of the array. Each sector column of four cells can be Set/Reset by a (Plane 5) express bus or by the Global Set/Reset. The Plane 5 express bus used for Set/Reset is half length at array edge. The Set/Reset provided to each sector column of four cells can be either inverted or not inverted. The function of the Set/Reset input of a register (either Set or Reset) is determined by a configuration bit for each cell. The Set/Reset input of a register is Active Low (logic 0). Setting or resetting of a register is asynchronous. On power-up, a logic 1 (High) is provided by each register, i.e., all registers are set at power-up.

The FPGA clocks from the AVR are effected differently in the various sleep modes of the AVR, see Table 3.

The source clock into the FPGA GCK5 and GCK6 will determine what happens during the various power-down modes of the AVR.

If the XTAL clock input is used as an FPGA clock (GCK5 or GCK6) in Idle mode, it will still be running. In Power-down/save mode the XTAL clock input will be off.

If the TOSC clock input is used as an FPGA clock (GCK6) in Idle mode, it will still be running in Power-save mode but will be off in Power-down mode.

If the Watchdog Timer is used as an FPGA clock (GCK6) and was enabled in the AVR, it will be running in all sleep modes.

| Mode       | Clock Source | GCK5          | GCK6     |

|------------|--------------|---------------|----------|

|            | XTAL         | Active        | Active   |

| Idle       | TOSC         | Not Available | Active   |

|            | WDT          | Not Available | Active   |

|            | XTAL         | Inactive      | Inactive |

| Power-save | TOSC         | Not Available | Active   |

|            | WDT          | Not Available | Active   |

|            | XTAL         | Inactive      | Inactive |

| Power-down | TOSC         | Not Available | Inactive |

|            | WDT          | Not Available | Active   |

Table 3. Clock Activity in Various Modes

Note: 1. Two on left edge column of the embedded FPGA array only.

Figure 13. Set/Reset (for One Column of Cells)

Any User I/O can Drive Global Set/Reset Line

Some of the bus resources on the embedded FPGA core are used as dual-function resources. Table 4 shows which buses are used in a dual-function mode and which bus plane is used. The FPGA software tools are designed to automatically accommodate dual-function buses in an efficient manner.

#### Table 4. Dual-function Buses

| Function                 | Туре    | Plane(s) | Direction                     | Comments                                                                          |

|--------------------------|---------|----------|-------------------------------|-----------------------------------------------------------------------------------|

| Cell Output Enable       | Local   | 5        | Horizontal<br>and<br>Vertical |                                                                                   |

| FreeRAM Output<br>Enable | Express | 2        | Vertical                      | Bus full length at array edge bus in first column to left of RAM block            |

| FreeRAM Write<br>Enable  | Express | 1        | Vertical                      | Bus full length at array edge bus in first column to left of RAM block            |

| FreeRAM Address          | Express | 1 - 5    | Vertical                      | Buses full length at array edge<br>buses in second column to left of<br>RAM block |

| FreeRAM<br>Data In       | Local   | 1        | Horizontal                    |                                                                                   |

| FreeRAM<br>Data Out      | Local   | 2        | Horizontal                    |                                                                                   |

| Clocking                 | Express | 4        | Vertical                      | Bus full length at array edge                                                     |

| Set/Reset                | Express | 5        | Vertical                      | Bus full length at array edge                                                     |

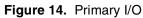

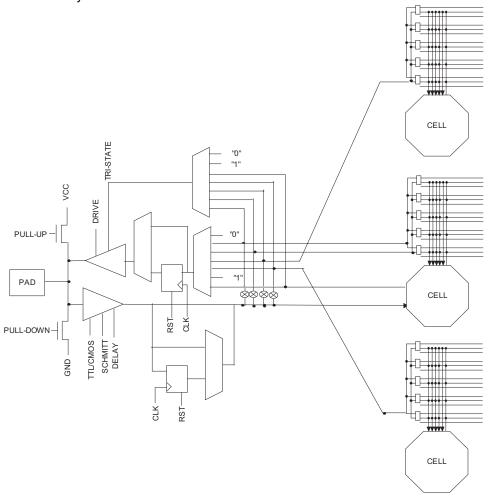

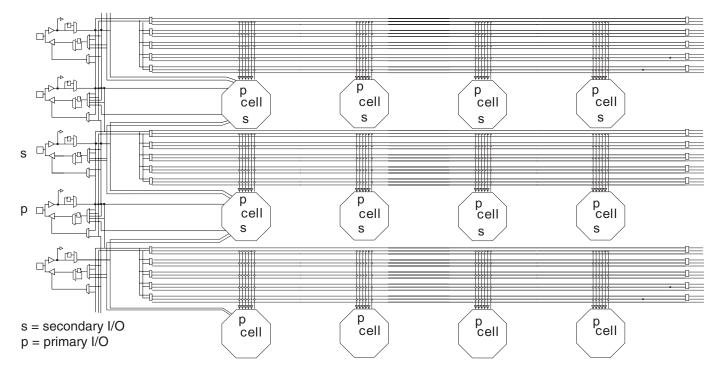

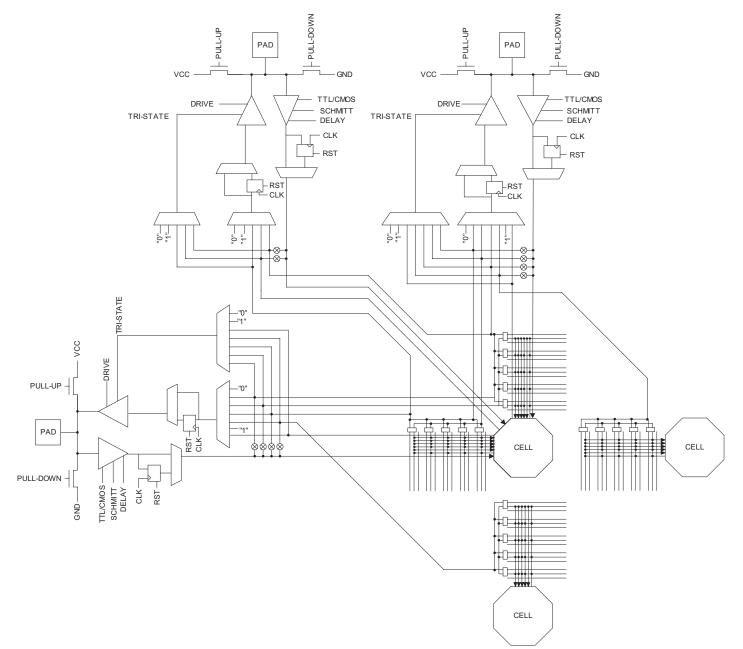

Figure 15. Secondary I/O

Figure 16. Primary and Secondary I/Os

#### Figure 17. Corner I/Os

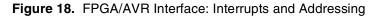

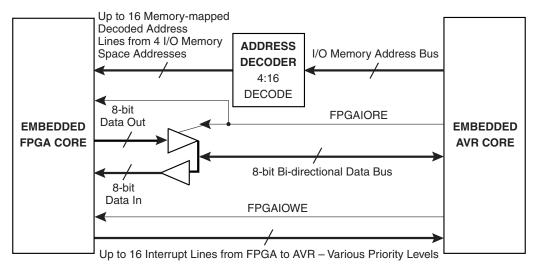

## **FPGA/AVR Interface and System Control**

The FPGA and AVR share a flexible interface which allows for many methods of system integration.

- Both FPGA and AVR share access to the 15 ns dual-port SRAM.

- The AVR data bus interfaces directly into the FPGA busing resources, effectively treating the FPGA as a large I/O device. Users have complete flexibility on the types of additional peripherals which are placed and routed inside the FPGA user logic.

- Up to 16 decoded address lines are provided into the FPGA.

- Up to 16 interrupts are available from the FPGA to the AVR.

- The AVR can reprogram the FPGA during operation to create a dynamic reconfigurable system (Cache Logic).

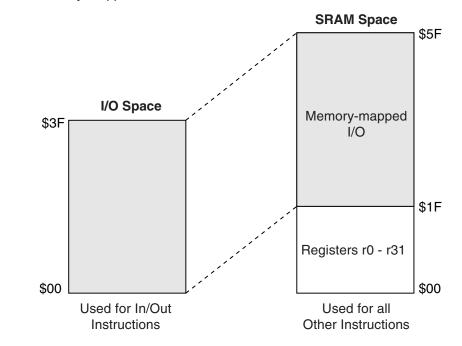

FPGA/AVR Interface– Memory-mapped Peripherals

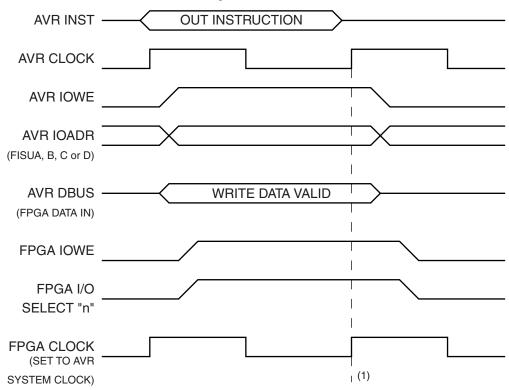

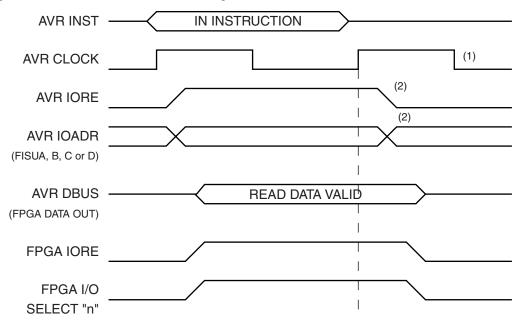

The FPGA core can be directly accessed by the AVR core, see Figure 18. Four memory locations in the AVR memory map are decoded into 16 select lines (8 for AT94K05) and are presented to the FPGA along with the AVR 8-bit data bus. The FPGA can be used to create additional custom peripherals for the AVR microcontroller through this interface. In addition there are 16 interrupt lines (8 for AT94K05) from the FPGA back into the AVR interrupt controller. Programmable peripherals or regular logic can use these interrupt lines. Full support for programmable peripherals is available within the System Designer tool suite.

The FPGA I/O selection is controlled by the AVR. This is described in detail beginning on page 53. The FPGA I/O interrupts are described beginning on page 57.

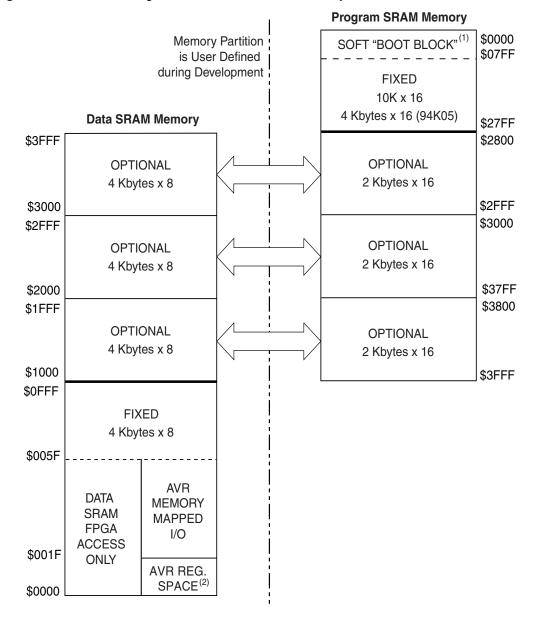

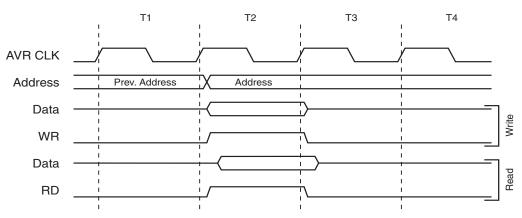

## Program and Data SRAM

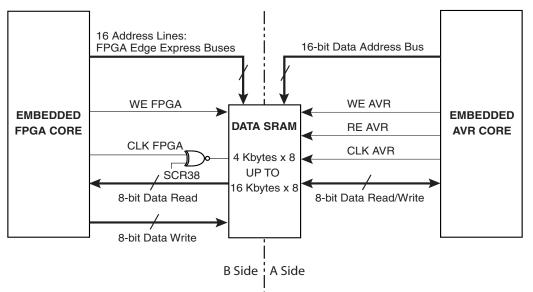

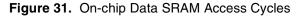

Up to 36 Kbytes of 15 ns dual-port SRAM reside between the FPGA and the AVR. This SRAM is used by the AVR for program instruction and general-purpose data storage. The AVR is connected to one side of this SRAM; the FPGA is connected to the other side. The port connected to the FPGA is used to store data without using up bandwidth on the AVR system data bus.

The FPGA core communicates directly with the data SRAM<sup>(1)</sup> block, viewing all SRAM memory space as 8-bit memory.

Note: 1. The unused bits for the FPGA-SRAM address must tie to '0' because there is no pull-down circuitry.

For the AT94K10 and AT94K40, the internal program and data SRAM is divided into three blocks: 10 Kbytes x 16 dedicated program SRAM, 4 Kbytes x 8 dedicated data SRAM and 6 Kbytes x 16 or 12 Kbytes x 8 configurable SRAM, which may be swapped between program and data memory spaces in 2 Kbytes x 16 or 4 Kbytes x 8 partitions.

For the AT94K05, the internal program and data SRAM is divided into three blocks: 4 Kbytes 16 dedicated program SRAM, 4 Kbytes x 8 dedicated data SRAM and 6 Kbytes x 16 or 12 Kbytes x 8 configurable SRAM, which may be swapped between program and data memory spaces in 2 Kbytes x 16 or 4 Kbytes x 8 partitions.

The addressing scheme for the configurable SRAM partitions prevents program instructions from overwriting data words and vice versa. Once configured (SCR41:40 – See "System Control Register – FPGA/AVR" on page 30.), the program memory space remains isolated from the data memory space. SCR41:40 controls internal muxes. Write enable signals allow the memory to be safely segmented. Figure 19 shows the FPSLIC configurable allocation SRAM memory.

Figure 19. FPSLIC Configurable Allocation SRAM Memory<sup>(1)(2)</sup>

- Notes: 1. The Soft "BOOT BLOCK" is an area of memory that is first loaded when the part is powered up and configured. The remainder of the memory can be reprogrammed while the device is in operation for switching functions in and out of memory. The Soft "BOOT BLOCK" can only be programmed by a full device configuration on power-up.

- 2. The lower portion of the Data memory is not shared between the AVR and FPGA. The AVR uses addresses \$0000 \$001F for the AVR CPU general working registers. \$001F \$005F are the addresses used for Memory Mapped I/O and store the information in dedicated registers. Therefore, on the FPGA side \$0000 \$005F are available for data that is only needed by the FPGA.

## Data SRAM Access by FPGA – FPGAFrame Mode

The FPGA user logic has access to the data SRAM directly through the FPGA side of the dual-port memory, see Figure 20. A single bit in the configuration control register (SCR63 – see "System Control Register – FPGA/AVR" on page 30) enables this interface. The interface is disabled during configuration downloads. Express buses on the East edge of the array are used to interface the memory. Full read and write access is available. To allow easy implementation, the interface itself is dedicated in routing resources, and is controlled in the System Designer software suite using the AVR FPGA interface dialog.

Once the SCR63 bit is set there is no additional read enable from the FPGA side. This means that the read is always enabled. You can also perform a read or write from the AVR at the same time as an FPGA read or write. If there is a possibility of a write address being accessed by both devices at the same time, the designer should add arbitration to the FPGA Logic to control who has priority. In most cases the AVR would be used to restrict access by the FPGA using the FMXOR bit, see "Software Control Register – SFTCR" on page 51. You can read from the same location from both sides simultaneously.

SCR bit 38 controls the polarity of the clock to the SRAM from the AT40K FPGA.

This option is used to allow for code (Program Memory) changes.

The FPSLIC SRAM is up to 36 x 8 Kbytes of dual port, see Figure 19):

- The A side (port) is accessed by the AVR.

- The B side (port) is accessed by the FPGA/Configuration Logic.

- The B side (port) can be accessed by the AVR with ST and LD instructions in DBG mode for code self-modify.

Structurally, the [ $(n \cdot 2)$  Kbytes 8] memory is built from (n)2 Kbytes 8 blocks, numbered SRAM0 through SRAM(n).

### SRAM Access by FPGA/AVR

Accessing and Modifying the Program Memory from the AVR

#### A Side

The A side is partitioned into Program memory and Data memory:

- Program memory is 16-bit words.

- Program memory address \$0000 always starts in the highest two SRAMs (n 1, n) [SRAMn - 1 (low byte) and SRAMn (high byte)] (SRAM labels are for layout, the addressing scheme is transparent to the AVR PC).

- System configuration determines the higher addresses for program memory:

- SCR bits 41 = 0 : 40 = 0, program memory extended from \$2800 \$3FFF

- SCR bits 41 = 0 : 40 = 1, program memory extended from \$2800 \$37FF

- SCR bits 41 = 1 : 40 = 0, program memory extended from \$2800 \$2FFF

- SCR bits 41 = 1 : 40 = 1, no extra program memory

- Extended program memory is always lost to extended data memory from SRAM2/3 down to SRAM6/7, see Table 5.

| Address Range                                                                                                                                                           | SRAM                                               | Comments                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$3FFF - \$3800<br>\$3FFF - \$3800                                                                                                                                      | 02<br>03                                           | CR41:40 = 00                                                                                                                                                                                                                  |

| \$37FF - \$3000<br>\$37FF - \$3000                                                                                                                                      | 04<br>05                                           | CR41:40 = 00,01                                                                                                                                                                                                               |

| \$2FFF - \$2800<br>\$2FFF - \$2800                                                                                                                                      | 06<br>07                                           | CR41:40 = 00,01,10                                                                                                                                                                                                            |

| \$27FF - \$2000<br>\$27FF - \$2000<br>\$1FFF - \$1800<br>\$1FFF - \$1800<br>\$17FF - \$1000<br>\$17FF - \$1000<br>\$0FFF - \$0800<br>\$0FFF - \$0800<br>\$07FF - \$0000 | 08<br>09<br>10<br>11<br>12<br>13<br>14<br>15<br>16 | AVR Program Read-only<br>AVR Program Read-only |

| \$07FF - \$0000                                                                                                                                                         | n = 17                                             | AVR Program Read-only                                                                                                                                                                                                         |

Table 5.

AVR Program Decode for SRAM 2:7 (16K16)

- Data memory is 8-bit words.

- Data memory address \$0000 always starts in SRAM0 (SRAM labels are for layout, the addressing scheme is transparent to AVR data read/write).

- System configuration determines the higher address for data memory:

- SCR bits 41 = 0: 40 = 0, no extra data memory

- SCR bits 41 = 0 : 40 = 1, data memory extended from \$1000 \$1FFF

- SCR bits 41 = 1 : 40 = 0, data memory extended from \$1000 \$2FFF

- SCR bits 41 = 1 : 40 = 1, data memory extended from \$1000 \$3FFF

- Extended data memory is always lost to extended program memory from SRAM7 up to SRAM2 in 2 x SRAM blocks, see Table 6.

| Address Range                      | SRAM     | Comments                                   |

|------------------------------------|----------|--------------------------------------------|

| \$07FF – \$0000<br>\$0FFF – \$0800 | 00<br>01 | AVR Data Read/Write<br>AVR Data Read/Write |

| \$17FF – \$1000<br>\$1FFF – \$1800 | 02<br>03 | CR41:40 = 11,10,01                         |

| \$27FF – \$2000<br>\$2FFF – \$2800 | 04<br>05 | CR41:40 = 11,10                            |

| \$37FF – \$3000<br>\$3FFF – \$3800 | 06<br>07 | CR41:40 = 11                               |

#### Table 6. AVR Data Decode for SRAM 0:17 (16K8)

B Side

The B side is not partitioned; the FPGA (and AVR debug mode) views the memory space as 36 x 8 Kbytes.

- The B side is accessed by the FPGA/Configuration Logic.

- The B side is accessed by the AVR with ST and LD instructions in DBG mode for code self-modify.

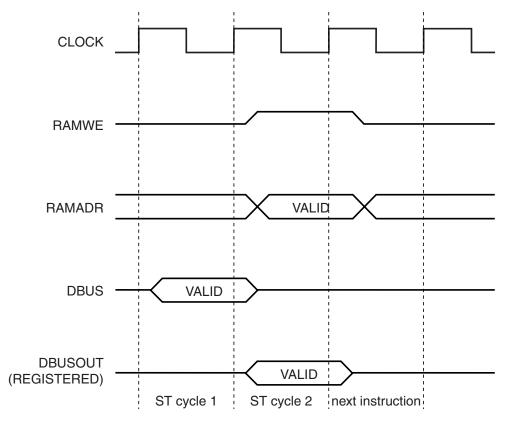

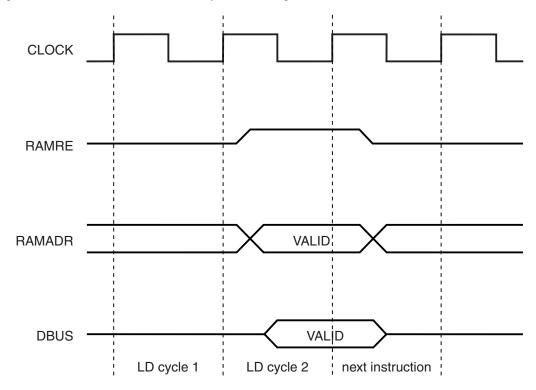

To activate the debug mode and allow the AVR to access the program code space (with ST - see Figure 21 – and LD – see Figure 22 – instructions), the DBG bit (bit 1) of the SFTCR \$3A (\$5A) register has to be set. When this bit is set, SCR36 and SCR37 are ignored – you can overwrite anything in the AVR program memory.

The FPGA memory access interface should be disabled while in debug mode. This is to ensure that there is no contention between the FPGA address and data signals and the AVR-generated address and data signals. To ensure the AVR has control over the "B side" memory interface, the FMXOR bit (bit 3) of the SFTCR \$3A (\$5A) register should be used in conjunction with the SCR63 system control register bit.

The FMXOR bit is XORed with the System Control Register's Enable FPGA SRAM Interface bit (SCR63). The behavior when this bit is set to 1 is dependent on how the SCR was initialized. If the Enable FPGA SRAM Interface bit (SCR63) in the SCR is 0, the FMXOR bit enables the FPGA SRAM Interface when set to 1. If the Enable FPGA SRAM Interface bit in the SCR is 1, the FMXOR bit disables the FPGA SRAM Interface when set to 1. During AVR reset, the FMXOR bit is cleared by the hardware.

Even though the FPGA (and AVR debug mode) views the memory space as 36 x 8 Kbytes, an awareness of the 2K x 8 partitions (or SRAM labels) is required if Frame (and AVR debug mode) read/writes are to be meaningful to the AVR.

- AVR data to FPGA addressing is 1:1 mapping.

- AVR program to FPGA addressing requires 16-bit to 8-bit mapping and an understanding of the partitions in Table 7.

| SRAM              | FPGA and AVR DBG<br>Address Range | AVR Data<br>Address Range | AVR PC Address Range      |

|-------------------|-----------------------------------|---------------------------|---------------------------|

| 00                | \$0000 - \$07FF                   | \$0000 - \$07FF           |                           |

| 01                | \$0800 - \$0FFF                   | \$0800 - \$0FFF           |                           |

| 02 <sup>(1)</sup> | \$1000 - \$17FF                   | \$1000 - \$17FF           | \$3800 - \$3FFF (LS Byte) |

| 03 <sup>(1)</sup> | \$1800 - \$1FFF                   | \$1800 - \$1FFF           | \$3800 - \$3FFF (MS Byte) |

| 04 <sup>(1)</sup> | \$2000 - \$27FF                   | \$2000 - \$27FF           | \$3000 - \$37FF (LS Byte) |

#### **Table 7.** Summary Table for AVR and FPGA SRAM Addressing

## <sup>26</sup> AT94KAL Series FPSLIC

| SRAM              | FPGA and AVR DBG<br>Address Range | AVR Data<br>Address Range | AVR PC Address Range      |

|-------------------|-----------------------------------|---------------------------|---------------------------|

| 05 <sup>(1)</sup> | \$2800 - \$2FFF                   | \$2800 - \$2FFF           | \$3000 - \$37FF (MS Byte) |

| 06 <sup>(1)</sup> | \$3000 - \$37FF                   | \$3000 - \$37FF           | \$2800 - \$2FFF (LS Byte) |

| 07 <sup>(1)</sup> | \$3800 - \$3FFF                   | \$3800 - \$3FFF           | \$2800 - \$2FFF (MS Byte) |

| 08                | \$4000 - \$47FF                   |                           | \$2000 - \$27FF (LS Byte) |

| 09                | \$4800 - \$4FFF                   |                           | \$2000 - \$27FF (MS Byte) |

| 10                | \$5000 - \$57FF                   |                           | \$1800 - \$1FFF (LS Byte) |

| 11                | \$5800 - \$5FFF                   |                           | \$1800 - \$1FFF (MS Byte) |

| 12                | \$6000 - \$67FF                   |                           | \$1000 - \$17FF (LS Byte) |

| 13                | \$6800 - \$6FFF                   |                           | \$1000 - \$17FF (MS Byte) |

| 14                | \$7000 - \$77FF                   |                           | \$0800 - \$0FFF (LS Byte) |

| 15                | \$7800 - \$7FFF                   |                           | \$0800 - \$0FFF (MS Byte) |

| 16                | \$8000 - \$87FF                   |                           | \$0000 - \$07FF (LS Byte) |

| 17 = n            | \$8800 - \$8FFF                   |                           | \$0000 - \$07FF (MS Byte) |

Table 7.

Summary Table for AVR and FPGA SRAM Addressing (Continued)

Note: 1. Whether these SRAMs are "Data" or "Program" depends on the SCR40 and SCR41 values.

Example: Frame (and AVR debug mode) write of instructions to associated AVR PC addresses, see Table 8 and Table 9.

| Table 8. AVR PC Ad | dresses |

|--------------------|---------|

|--------------------|---------|

| AVR PC | Instruction |

|--------|-------------|

| OFFE   | 9B28        |

| 0FFF   | CFFE        |

| 1000   | B300        |

| 1001   | 9A39        |

#### Table 9. Frame Addresses

| Frame Address | Frame Data |

|---------------|------------|

| 77FE          | 28         |

| 77FF          | FE         |

| 6000          | 00         |

| 6001          | 39         |

| 7FFE          | 9B         |

| 7FFF          | CF         |

| 6800          | В3         |

| 6801          | 9A         |

Figure 21. AVR SRAM Data Memory Write Using "ST" Instruction

Figure 22. AVR SRAM Data Memory Read Using "LD" Instruction

### AVR Cache Mode

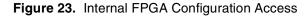

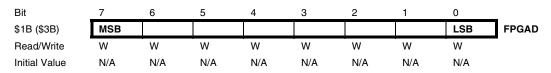

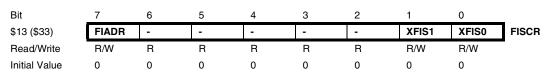

The AVR has the ability to cache download the FPGA memory. The AVR has direct access to the data buses of the FPGA's configuration SRAM and is able to download bitstreams. AVR Cache access of configuration SRAM is not available during normal configuration downloads. The Cache Logic port in the AVR is located in the I/O memory map. Three registers, FPGAX, FPGAY FPGAZ, control the address written to inside the FPGA; and FPGAD in the AVR memory map controls the Data. Registers FPGAX, FPGAY and FPGAZ are write only, see Figure 23.

Configuration Clock – Each tick is generated when the Memorymapped I/O location FPGAD is written to inside the AVR.

The AVR Cache Logic access mode is write only. Transfers may be aborted at any time due to AVR program wishes or external interrupts.

The FPGA CHECK function is not supported by the AVR Cache mode.

A typical application for this mode is for the AVR to accept serial data through a UART for example, and port it as configuration data to the FPGA, thereby affecting a download, or allowing reconfigurable systems where the FPGA is updated algorithmically by the AVR. For more information, refer to the "AT94K Series Configuration" application note available on the Atmel web site, at: http://www.atmel.com/atmel/acrobat/doc2313.pdf.

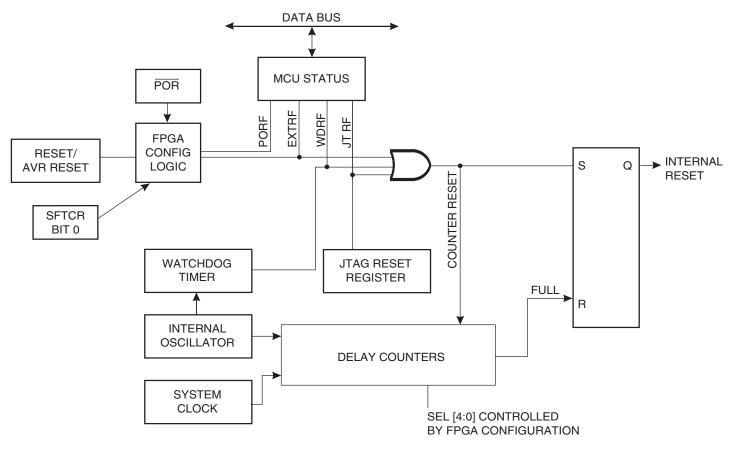

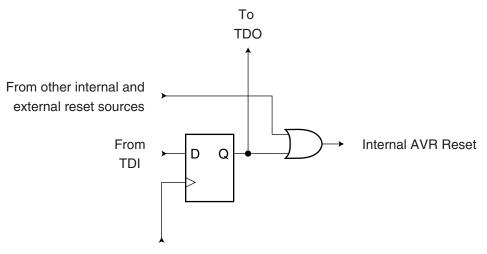

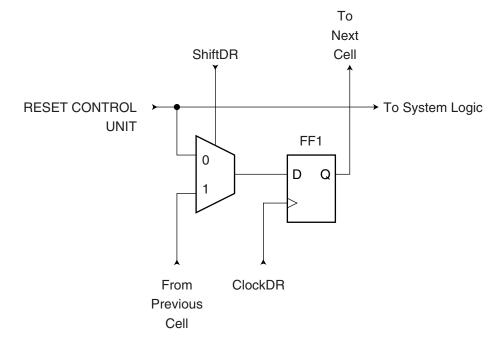

Resets

The user must have the flexibility to issue resets and reconfiguration commands to separate portions of the device. There are two Reset pins on the FPSLIC device. The first, RESET, results in a clearing of all FPGA configuration SRAM and the System Control Register, and initiates a download if in mode 0. The AVR will stop and be reset.

A second reset pin, AVRReset, is implemented to reset the AVR portion of the FPSLIC functional blocks. This is described in the "Reset Sources" on page 61.

## System Control

**Configuration Modes**

The AT94K family has four configuration modes controlled by mode pins M0 and M2, see Table 10.

#### Table 10. Configuration Modes

| M2 | МО | Name                          |

|----|----|-------------------------------|

| 0  | 0  | Mode 0 - Master Serial        |

| 0  | 1  | Mode 1 - Slave Serial Cascade |

| 1  | 0  | Mode 2 - Reserved             |

| 1  | 1  | Mode 3 - Reserved             |

Modes 2 and 3 are reserved and are used for factory test.

Modes 0 and 1 are pin-compatible with the appropriate AT40K counterpart. AVR I/O will be taken over by the configuration logic for the CHECK pin during both modes.

Refer to the "AT94K Series Configuration" application note for details on downloading bitstreams.

#### System Control Register – FPGA/AVR

The configuration control register in the FPSLIC consists of 8 bytes of data, which are loaded with the FPGA/Prog. Code at power-up from external nonvolatile memory. FPSLIC System Control Register values, see Table 11, can be set in the System Designer software. Recommended defaults are included in the software.

| Table 11. | FPSLIC System | Control Register |

|-----------|---------------|------------------|

|-----------|---------------|------------------|

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCR0 - SCR1 | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SCR2        | 0 = Enable Cascading<br>1 = Disable Cascading<br>SCR2 controls the operation of the dual-function I/O CSOUT. When SCR2 is set,<br>the CSOUT pin is not used by the configuration during downloads, set this bit for<br>configurations where two or more devices are cascaded together. This applies for<br>configuration to another FPSLIC device or to an FPGA.                                                                                                                                                                                                                                                                                                    |

| SCR3        | 0 = Check Function Enabled<br>1 = Check Function Disabled<br>SCR3 controls the operation of the CHECK pin and enables the Check Function.<br>When SCR3 is set, the dual use AVR I/O/CHECK pin is not used by the<br>configuration during downloads, and can be used as AVR I/O.                                                                                                                                                                                                                                                                                                                                                                                     |

| SCR4        | 0 = Memory Lockout Disabled<br>1 = Memory Lockout Enabled<br>SCR4 is the Security Flag and controls the writing and checking of configuration<br>memory during any subsequent configuration download. When SCR4 is set, any<br>subsequent configuration download initiated by the user, whether a normal<br>download or a CHECK function download, causes the INIT pin to immediately<br>activate. CON is released, and no further configuration activity takes place. The<br>download sequence during which SCR4 is set is NOT affected. The Control<br>Register write is also prohibited, so bit SCR4 may only be cleared by a power-on<br>reset or manual reset. |

| SCR5        | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Bit           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCR6          | 0 = OTS Disabled<br>1 = OTS Enabled<br>Setting SCR6 makes the OTS (output tri-state) pin an input which controls the<br>global tri-state control for all user I/O. This junction allows the user at any time to<br>tristate all user I/O and isolate the chip.                                                                                                                                                                                                                                                     |

| SCR7 - SCR12  | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SCR13         | 0 = CCLK Normal Operation<br>1 = CCLK Continues After Configuration.<br>Setting bit SCR13 allows the CCLK pin to continue to run after configuration<br>download is completed. This bit is valid for Master mode, mode 0 only. The CCLK<br>is not available internally on the device. If it is required in the design, it must be<br>connected to another device I/O.                                                                                                                                              |

| SCR14 - SCR15 | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SCR16 - SCR23 | 0 = GCK 0:7 Always Enabled<br>1 = GCK 0:7 Disabled During Internal and External Configuration Download.<br>Setting SCR16:SCR23 allows the user to disable the input buffers driving the<br>global clocks. The clock buffers are enabled and disabled synchronously with the<br>rising edge of the respective GCK signal, and stop in a High "1" state. Setting one<br>of these bits disables the appropriate GCK input buffer only and has no effect on<br>the connection from the input buffer to the FPGA array. |

| SCR24 - SCR25 | 0 = FCK 0:1 Always Enabled<br>1 = FCK 0:1 Disabled During Internal and External Configuration Download.<br>Setting SCR24:SCR25 allows the user to disable the input buffers driving the fast<br>clocks. The clock buffers are enabled and disabled synchronously with the rising<br>edge of the respective FCK signal, and stop in a High "1" state. Setting one of<br>these bits disables the appropriate FCK input buffer only and has no effect on the<br>connection from the input buffer to the FPGA array.   |

| SCR26         | 0 = Disable On-chip Debugger<br>1 = Enable On-chip Debugger.<br>JTAG Enable, SCR27, must also be set (one) and the configuration memory<br>lockout, SCR4, must be clear (zero) for the user to have access to internal scan<br>chains.                                                                                                                                                                                                                                                                             |

| SCR27         | 0 = Disable TAP at user FPGA I/O Ports<br>1 = Enable TAP at user FPGA I/O Ports.<br>Device ID scan chain and AVR I/O boundary scan chain are available. The user<br>must set (one) the On-chip Debug Enable, SCR26, and must keep the<br>configuration memory lockout, SCR4, clear (zero) for the user to have access to<br>internal scan chains.                                                                                                                                                                  |

| SCR28 - SCR29 | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SCR30         | <ul> <li>0 = Global Set/Reset Normal</li> <li>1 = Global Set/Reset Active (Low) During Internal and External Configuration<br/>Download.</li> <li>SCR30 allows the Global set/reset to hold the core DFFs in reset during any<br/>configuration download. The Global set/reset net is released at the end of<br/>configuration download on the rising edge of CON, if set.</li> </ul>                                                                                                                              |

| SCR31         | 0 = Disable I/O Tri-state<br>1 = I/O Tri-state During (Internal and External) Configuration Download.<br>SCR31 forces all user defined I/O pins to go tri-state during configuration<br>download. Tri-state is released at the end of configuration download on the rising<br>edge of CON, if set.                                                                                                                                                                                                                 |

| Table 11. | <b>FPSLIC Sv</b> | stem Control | Register       |

|-----------|------------------|--------------|----------------|

|           |                  |              | i i i o giotoi |

## Table 11. FPSLIC System Control Register

| Bit               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCR32 - SCR34     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SCR35             | 0 = AVR Reset Pin Disabled<br>1 = AVR Reset Pin Enabled (active Low Reset)<br>SCR35 allows the AVR Reset pin to reset the AVR only.                                                                                                                                                                                                                                                                                                                                                 |

| SCR36             | 0 = Protect AVR Program SRAM<br>1 = Allow Writes to AVR Program SRAM (Excluding Boot Block)<br>SCR36 protects AVR program code from writes by the FPGA.                                                                                                                                                                                                                                                                                                                             |

| SCR37             | 0 = AVR Program SRAM Boot Block Protect<br>1 = AVR Program SRAM Boot Block Allows Overwrite                                                                                                                                                                                                                                                                                                                                                                                         |

| SCR38             | 0 = (default) Frame Clock Inverted to AVR Data/Program SRAM<br>1 = Non-inverting Clock Into AVR Data/Program SRAM                                                                                                                                                                                                                                                                                                                                                                   |

| SCR39             | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SCR40 - SCR41     | SCR41 = 0, SCR40 = 0 16 Kbytes x 16 Program/4 Kbytes x 8 Data<br>SCR41 = 0, SCR40 = 1 14 Kbytes x 16 Program/8 Kbytes x 8 Data<br>SCR41 = 1, SCR40 = 0 12 Kbytes x 16 Program/12 Kbytes x 8 Data<br>SCR41 = 1, SCR40 = 1 10 Kbytes x 16 Program/16 Kbytes x 8 Data<br>SCR40 : SCR41 AVR program/data SRAM partitioning (set by using the AT94K<br>Device Options in System Designer).                                                                                               |

| SCR 42 -<br>SCR47 | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

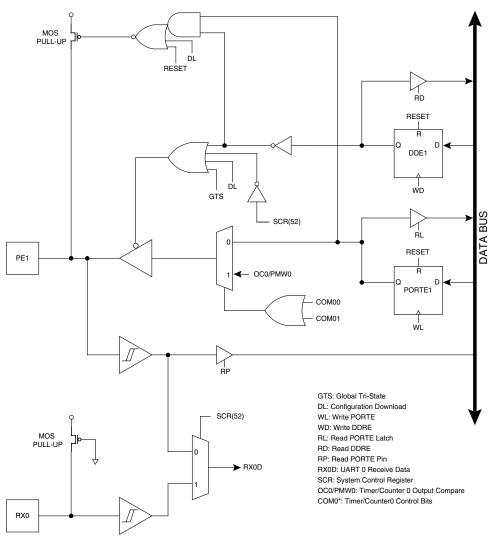

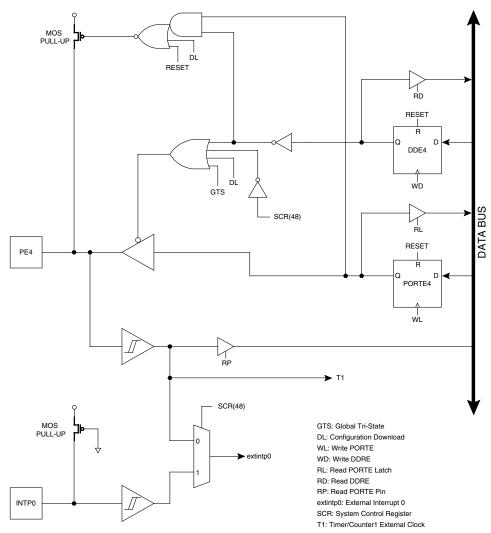

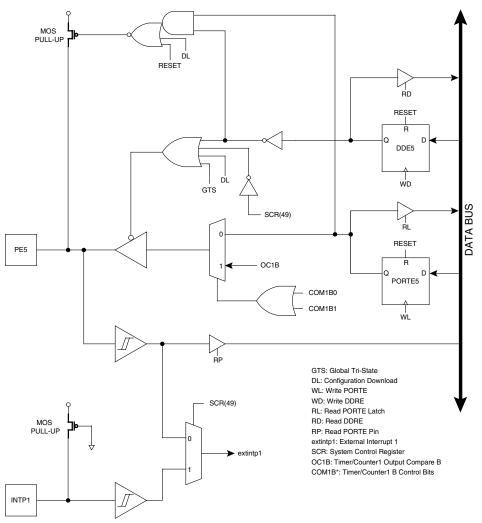

| SCR48             | 0 = EXT-INT0 Driven By Port E<4><br>1 = EXT-INT0 Driven By INTP0 pad<br>SCR48 : SCR53 Defaults dependent on package selected.                                                                                                                                                                                                                                                                                                                                                       |

| SCR49             | 0 = EXT-INT1 Driven By Port E<5><br>1 = EXT-INT1 Driven By INTP1 pad<br>SCR48 : SCR53 Defaults dependent on package selected.                                                                                                                                                                                                                                                                                                                                                       |

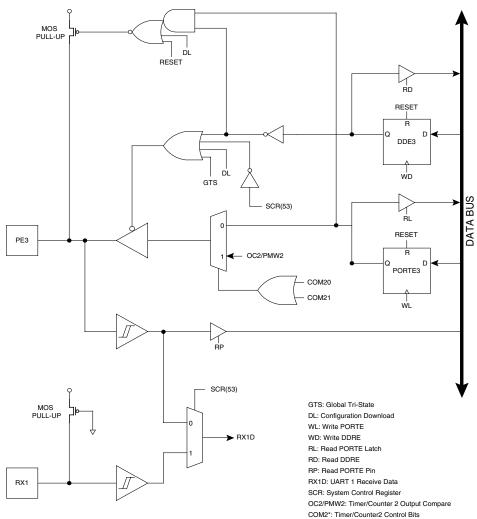

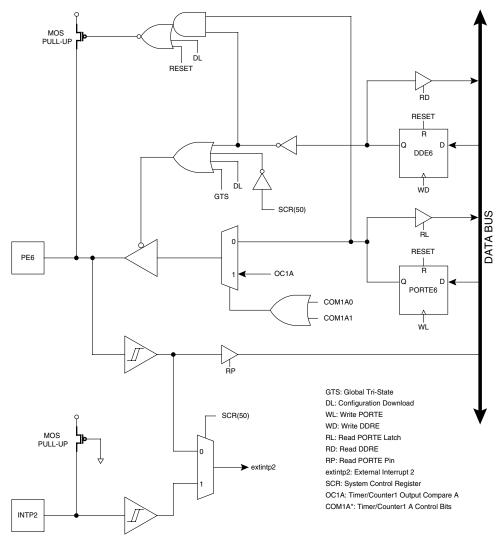

| SCR50             | 0 = EXT-INT2 Driven By Port E<6><br>1 = EXT-INT2 Driven By INTP2 pad<br>SCR48 : SCR53 Defaults dependent on package selected.                                                                                                                                                                                                                                                                                                                                                       |

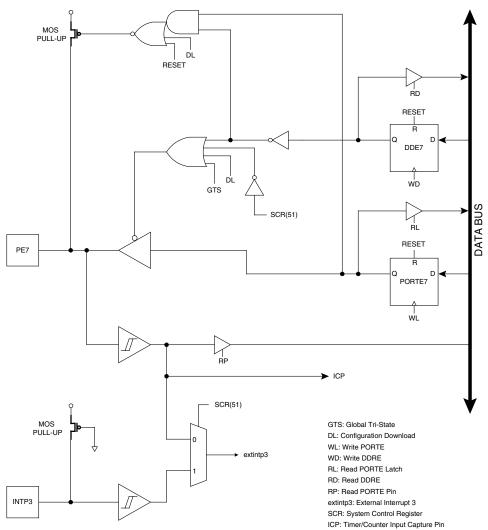

| SCR51             | 0 = EXT-INT3 Driven By Port E<7><br>1 = EXT-INT3 Driven By INTP3 pad<br>SCR48 : SCR53 Defaults dependent on package selected.                                                                                                                                                                                                                                                                                                                                                       |

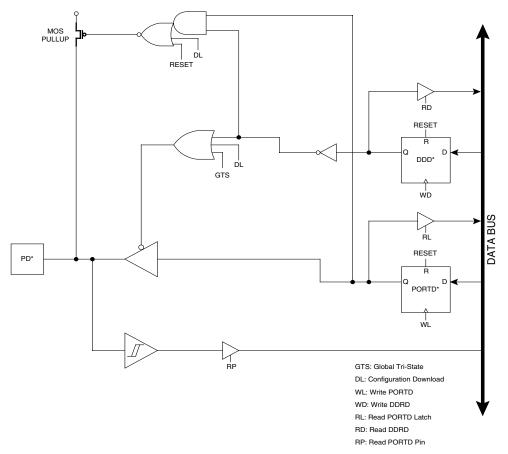

| SCR52             | 0 = UART0 Pins Assigned to Port E<1:0><br>1 = UART0 Pins Assigned to UART0 pads<br>SCR48 : SCR53 Defaults dependent on package selected.                                                                                                                                                                                                                                                                                                                                            |

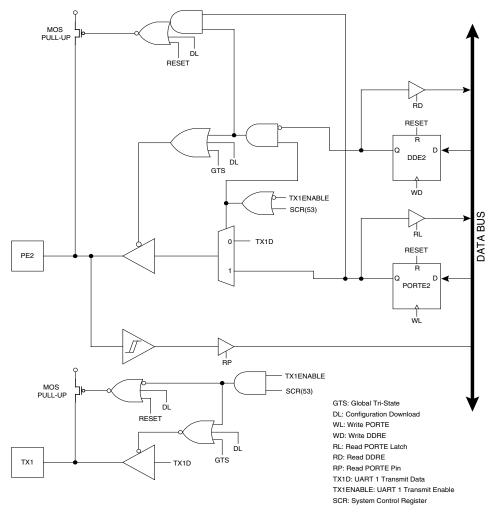

| SCR53             | 0 = UART1 Pins Assigned to Port E<3:2><br>1 = UART1 Pins Assigned to UART1 pads<br>SCR48 : SCR53 Defaults dependent on package selected.<br>On packages less than 144-pins, there is reduced access to AVR ports. Port D is<br>not available externally in the smallest package and Port E becomes dual-purpose<br>I/O to maintain access to the UARTs and external interrupt pins. The Pin List (East<br>Side) on page 177 shows exactly which pins are available in each package. |

| SCR54             | 0 = AVR Port D I/O With 6 mA Drive<br>1 = AVR Port D I/O With 20 mA Drive                                                                                                                                                                                                                                                                                                                                                                                                           |

| SCR55             | 0 = AVR Port E I/O With 6 mA Drive<br>1 = AVR Port E I/O With 20 mA Drive                                                                                                                                                                                                                                                                                                                                                                                                           |

| Bit           | Description                                                                                                                                                                                                                                                                                                                          |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

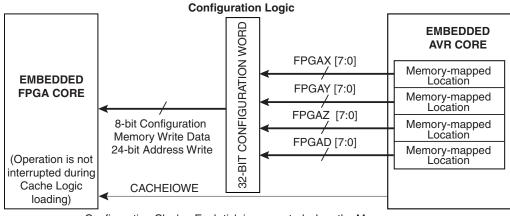

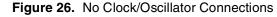

| SCR56         | 0 = Disable XTAL Pin (R <sub>feedback</sub> )<br>1 = Enable XTAL Pin (R <sub>feedback</sub> )                                                                                                                                                                                                                                        |

| SCR57         | 0 = Disable TOSC2 Pin (R <sub>feedback</sub> )<br>1 = Enable TOSC2 Pin (R <sub>feedback</sub> )                                                                                                                                                                                                                                      |

| SCR58 - SCR59 | Reserved                                                                                                                                                                                                                                                                                                                             |

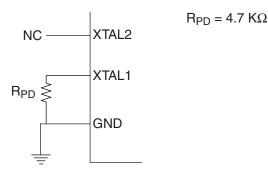

| SCR60 - SCR61 | SCR61 = 0, SCR60 = 0 "1"<br>SCR61 = 0, SCR60 = 1 AVR System Clock<br>SCR61 = 1, SCR60 = 0 Timer Oscillator Clock (TOSC1) <sup>(1)</sup><br>SCR61 = 1, SCR60 = 1 Watchdog Clock<br>Global Clock 6 mux select (set by using the AT94K Device Options in System<br>Designer).<br>Note: 1. The AS2 bit must be set in the ASSR register. |

| SCR62         | 0 = Disable CacheLogic Writes to FPGA by AVR<br>1 = Enable CacheLogic Writes to FPGA by AVR                                                                                                                                                                                                                                          |

| SCR63         | 0 = Disable Access (Read and Write) to SRAM by FPGA<br>1 = Enable Access (Read and Write) to SRAM by FPGA                                                                                                                                                                                                                            |

Table 11. FPSLIC System Control Register

## **AVR Core and Peripherals**

- AVR Core

- Watchdog Timer/On-chip Oscillator

- Oscillator-to-Internal Clock Circuit

- Oscillator-to-Timer/Counter for Real-time Clock

- 16-bit Timer/Counter and Two 8-bit Timer/Counters

- Interrupt Unit

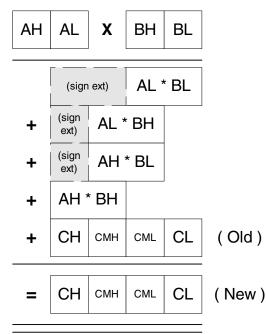

- Multiplier

- UART (0)

- UART (1)

- I/O Port D (full 8 bits available on 144-pin or higher devices)

- I/O Port E

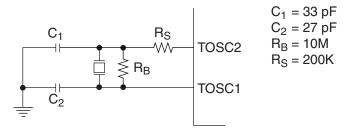

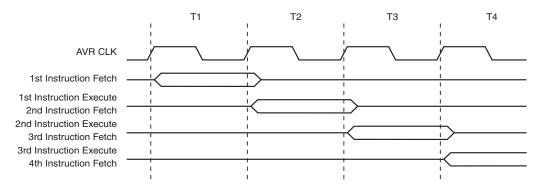

The embedded AVR core is a low-power CMOS 8-bit microcontroller based on the AVR RISC architecture. The embedded AVR core achieves throughputs approaching 1 MIPS per MHz by executing powerful instructions in a single-clock-cycle, and allows the system architect to optimize power consumption versus processing speed.

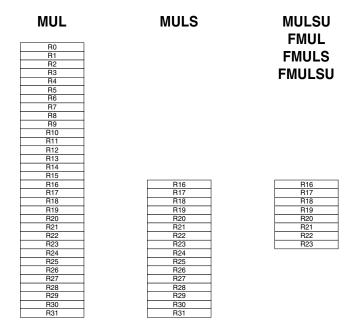

The AVR core is based on an enhanced RISC architecture that combines a rich instruction set with 32 x 8 general-purpose working registers. All the 32 x 8 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent register bytes to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The embedded AVR core provides the following features: 16 general-purpose I/O lines, 32 x 8 general-purpose working registers, Real-time Counter (RTC), 3 flexible timer/counters with compare modes and PWM, 2 UARTs, programmable Watchdog Timer with internal oscillator, 2-wire serial port, and three software-selectable Power-saving modes. The Idle mode stops the CPU while allowing the SRAM, timer/counters, two-wire serial port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the oscillator, disabling all other chip functions until the next interrupt or hardware reset. In Power-save mode, the timer oscillator continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping.

The embedded AVR core is supported with a full suite of program and system development tools, including C compilers, macro assemblers, program debugger/simulators and evaluation kits.

### Instruction Set Nomenclature (Summary)

The complete "AVR Instruction Set" document is available on the Atmel web site, at http://www.atmel.com/atmel/acrobat/doc0856.pdf.

| Status Register<br>(SREG) | SREG:      | Status register                                                                                            |

|---------------------------|------------|------------------------------------------------------------------------------------------------------------|

| (oned)                    | C:         | Carry flag in status register                                                                              |

|                           | Z:         | Zero flag in status register                                                                               |

|                           | N:         | Negative flag in status register                                                                           |

|                           | V:         | Two's complement overflow indicator                                                                        |

|                           | S:         | $N \oplus V$ , For signed tests                                                                            |

|                           | H:         | Half-carry flag in the status register                                                                     |

|                           | T:         | Transfer bit used by BLD and BST instructions                                                              |

|                           | l:         | Global interrupt enable/disable flag                                                                       |

| Registers and             | Rd:        | Destination (and source) register in the register file                                                     |

| Operands                  | Rr:        | Source register in the register file                                                                       |

|                           | R:         | Result after instruction is executed                                                                       |

|                           | K:         | Constant data                                                                                              |

|                           | k:         | Constant address                                                                                           |

|                           | b:         | Bit in the register file or I/O register ( $0 \le b \le 7$ )                                               |

|                           | s:         | Bit in the status register ( $0 \le s \le 2$ )                                                             |

|                           | X,Y,Z:     | Indirect address register (X = R27:R26, Y = R29:R28 and Z = R31:R30)                                       |

|                           | A:         | I/O location address                                                                                       |

|                           | q:         | Displacement for direct addressing (0 $\leq$ q $\leq$ 63)                                                  |

| I/O Registers             |            |                                                                                                            |

| Stack                     | STACK:     | Stack for return address and pushed registers                                                              |

|                           | SP:        | Stack Pointer to STACK                                                                                     |

| Flags                     | ⇔:         | Flag affected by instruction                                                                               |

|                           | <b>O</b> : | Flag cleared by instruction                                                                                |

|                           | 1:         | Flag set by instruction                                                                                    |

|                           | -:         | Flag not affected by instruction                                                                           |

|                           |            | ructions EIJMP, EICALL, ELPM, GPM, ESPM (from the megaAVR Instruction Set) are orted in the FPSLIC device. |

#### **Conditional Branch Summary**

| Test        | Boolean       | Mnemonic  | Complementary | Boolean                      | Mnemonic  | Comment  |

|-------------|---------------|-----------|---------------|------------------------------|-----------|----------|

| Rd > Rr     | Z•(N ⊕ V) = 0 | BRLT      | Rd ≤ Rr       | Z+(N ⊕ V) = 1                | BRGE      | Signed   |

| $Rd \ge Rr$ | (N ⊕ V) = 0   | BRGE      | Rd < Rr       | (N ⊕ V) = 1                  | BRLT      | Signed   |

| Rd = Rr     | Z = 1         | BREQ      | Rd ≠ Rr       | Z = 0                        | BRNE      | Signed   |

| Rd ≤ Rr     | Z+(N ⊕ V) = 1 | BRGE      | Rd > Rr       | $Z \bullet (N \oplus V) = 0$ | BRLT      | Signed   |

| Rd < Rr     | (N ⊕ V) = 1   | BRLT      | Rd ≥ Rr       | (N ⊕ V) = 0                  | BRGE      | Signed   |

| Rd > Rr     | C + Z = 0     | BRLO      | Rd ≤ Rr       | C + Z = 1                    | BRSH      | Unsigned |

| $Rd \ge Rr$ | C = 0         | BRSH/BRCC | Rd < Rr       | C = 1                        | BRLO/BRCS | Unsigned |

| Rd = Rr     | Z = 1         | BREQ      | Rd ≠ Rr       | Z = 0                        | BRNE      | Unsigned |

| Rd ≤ Rr     | C + Z = 1     | BRSH      | Rd > Rr       | C + Z = 0                    | BRLO      | Unsigned |

| Rd < Rr     | C = 1         | BRLO/BRCS | Rd ≥ Rr       | C = 0                        | BRSH/BRCC | Unsigned |

| Carry       | C = 1         | BRCS      | No Carry      | C = 0                        | BRCC      | Simple   |

| Negative    | N = 1         | BRMI      | Positive      | N = 0                        | BRPL      | Simple   |

| Overflow    | V = 1         | BRVS      | No Overflow   | V = 0                        | BRVC      | Simple   |

| Zero        | Z = 1         | BREQ      | Not Zero      | Z = 0                        | BRNE      | Simple   |

## **Complete Instruction Set Summary**

### Instruction Set Summary

| Mnemonics | Operands | Description                   | Operation                                           | Flags       | #Clock |

|-----------|----------|-------------------------------|-----------------------------------------------------|-------------|--------|

|           |          | Arithmetic and                | Logic Instructions                                  |             |        |

| ADD       | Rd, Rr   | Add without Carry             | $Rd \leftarrow Rd + Rr$                             | Z,C,N,V,S,H | 1      |

| ADC       | Rd, Rr   | Add with Carry                | $Rd \gets Rd + Rr + C$                              | Z,C,N,V,S,H | 1      |

| ADIW      | Rd, K    | Add Immediate to Word         | $Rd\text{+1:}Rd \leftarrow Rd\text{+1:}Rd\text{+}K$ | Z,C,N,V,S   | 2      |

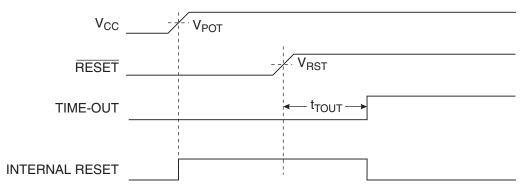

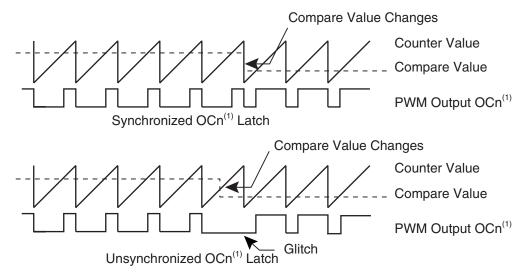

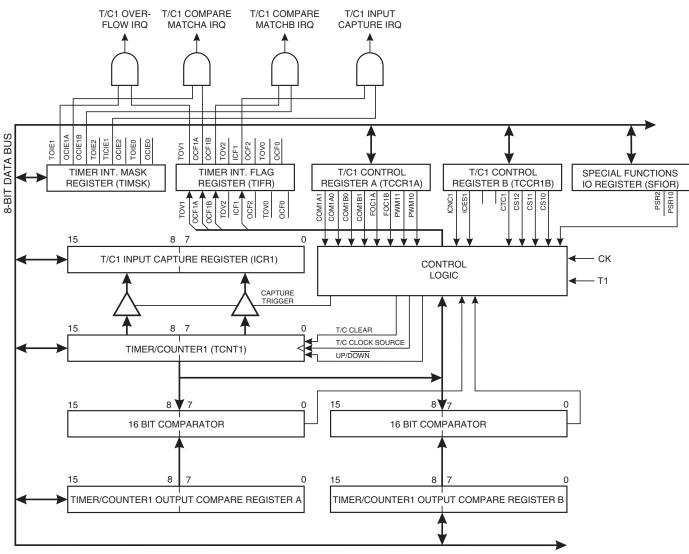

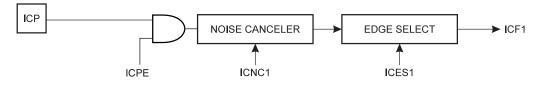

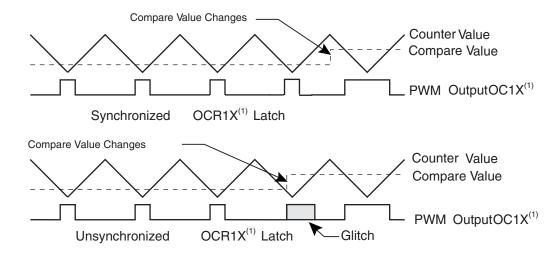

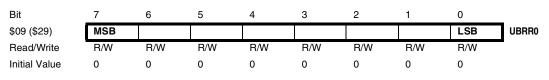

| SUB       | Rd, Rr   | Subtract without Carry        | $Rd \leftarrow Rd - Rr$                             | Z,C,N,V,S,H | 1      |