#### FEATURES AND BENEFITS

- Automotive-grade AEC-Q100 qualified

- Input voltage from 3 to 10 V

- Four individual output supplies

- · Independent control of each output voltage

- Boost switching frequency: 350 kHz to 2.25 MHz

- External synchronization capability is available

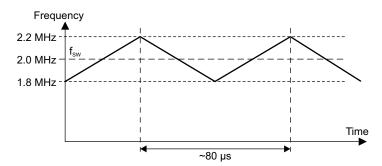

- Frequency dithering to reduce EMI

- Less than 10 μA shutdown current

- Protection features: overcurrent, overvoltage, short circuit, and thermal overload protection

- Fully programmable outputs through I<sup>2</sup>C

- □ Regulator voltage

- ☐ Startup/shutdown sequences

- □ Fault retry counter

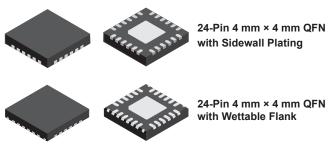

## **PACKAGES:**

## Not to scale

### **DESCRIPTION**

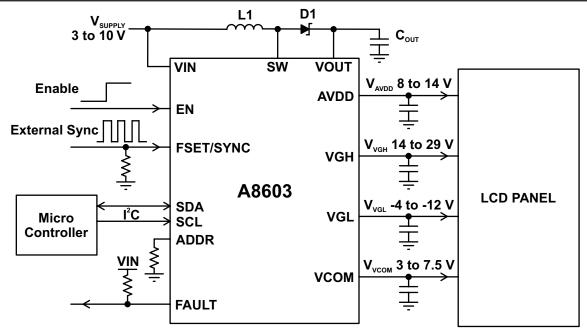

The A8603 is a fixed-frequency, multiple-output supply for LCD bias. Its switching frequency can be either programmed or synchronized with an external clock signal between 350 kHz and 2.25 MHz. This will minimize interference with AM and FM radio bands.

An I<sup>2</sup>C-compliant serial interface allows a system microcontroller to configure the A8603 by writing into its internal registers. A system controller can also access the A8603 status registers in case of fault conditions.

The A8603 incorporates a boost stage followed by two linear regulators and two charge-pump regulators. Each output voltage can be programmed independently through serial interface. During power-up and shutdown, the outputs are turned on and off in preprogrammed sequences with adjustable delay. This will meet the sequencing requirements for specific LCD panels.

Short-circuit protection is provided for all outputs. The boost switch is protected against overcurrent and overvoltage.

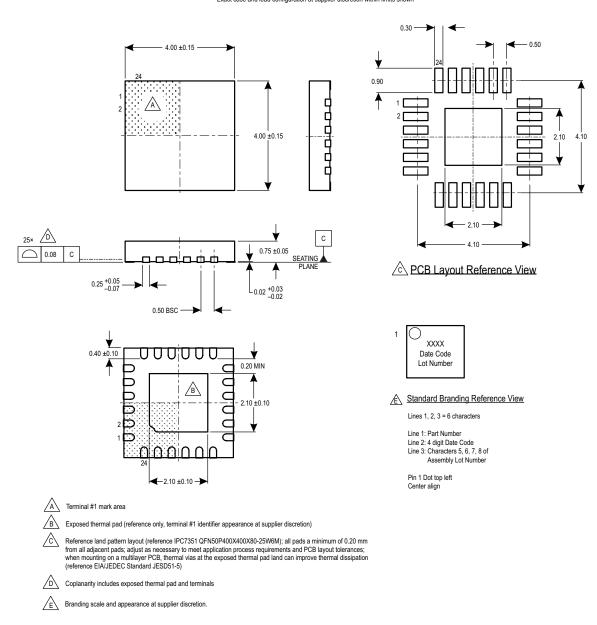

The A8603 is provided in a 24-pin 4 mm  $\times$  4 mm QFN package, with exposed thermal pad to allow operation at high ambient temperatures. It is lead (Pb) free with 100% matte-tin leadframe plating.

## **APPLICATIONS**

- GPS

- Infotainment

- Medium LCDs

System Block Diagram Showing Typical Regulator Voltages

**Table 1: Selection Guide**

| Part Number  | Package                                 | Packing*                    | Pin Soldering    |

|--------------|-----------------------------------------|-----------------------------|------------------|

| A8603KESTR-R | 24-pin 4×4 QFN with exposed thermal pad | 1500 pieces per 13-in. reel | Sidewall Plating |

| A8603KESTR-J | 24-pin 4×4 QFN with exposed thermal pad | Contact Factory             | Wettable Flank   |

<sup>\*</sup>Contact Allegro<sup>™</sup> for additional packing options.

#### **Table of Contents**

| Specifications                          | 3   | VGL/VGH Charge Pumps                 | 18 |

|-----------------------------------------|-----|--------------------------------------|----|

| Absolute Maximum Ratings                | 3   | Boost Controller                     | 20 |

| Thermal Characteristics                 | 3   | Boost Switching Frequency            | 22 |

| Pinout Diagrams and Terminal List Table | 4   | Boost Frequency Dithering            | 23 |

| Functional Block Diagram                | 5   | Fault Conditions                     | 24 |

| Electrical Characteristics              | 6   | Over- and Undervoltage Protections   | 24 |

| Characteristic Performance              | 10  | Overcurrent Protection               | 24 |

| Functional Description                  | 12  | Examples of Various Fault Conditions | 25 |

| Program Diagnostics                     | 12  | Pre-Output Fault Detection           | 29 |

| Programmable Registers                  | 13  | General Fault Detection              | 29 |

| I <sup>2</sup> C Register Map           | 14  | Fault Monitoring                     | 31 |

| Diagnostic Registers                    | 15  | Fault1 (Group1)                      | 31 |

| Real-Time Status Registers              | 15  | Fault2 (Group2)                      | 31 |

| Latched Status Registers                | 16  | Fault3 (Group3)                      | 31 |

| Description of Regulators               | 17  | Thermal Analysis                     | 33 |

| AVDD Regulator                          | 17  | Boost Stage Power Loss               | 33 |

| VCOM Regulator                          | 17  | Output Regulator Power Loss          | 33 |

| · ··· · - g-··-··                       | * * | Package Outline Drawing              | 35 |

#### **SPECIFICATIONS**

#### ABSOLUTE MAXIMUM RATINGS [1][2][5]

| Characteristic                        | Symbol                                                          | Notes                                     | Rating                                             | Unit |

|---------------------------------------|-----------------------------------------------------------------|-------------------------------------------|----------------------------------------------------|------|

| VIN Pin Voltage                       | V <sub>IN</sub>                                                 | All voltages measured with respect to GND | -0.3 to 11                                         | V    |

| CM/ Din Malka na [2][4]               |                                                                 | Continuous                                | -0.6 to 22                                         | V    |

| SW Pin Voltage <sup>[3][4]</sup>      | $V_{SW}$                                                        | Voltage spikes (pulse width < 100 ns)     | -1 to 40                                           | V    |

| OUT Pin Voltage                       | V <sub>OUT</sub>                                                |                                           | -0.3 to 22                                         | V    |

| AVDD Pin Voltage                      | V <sub>AVDD</sub>                                               |                                           | -0.3 to lower of 16 or<br>V <sub>OUT</sub> + 0.3   | V    |

| CP11 Pin Voltage                      | V <sub>CP11</sub>                                               | Positive charge pump                      | -0.3 to 31                                         | V    |

| CP12 Pin Voltage                      | V <sub>CP12</sub>                                               | Positive charge pump                      | -0.3 to V <sub>CP11</sub> + 0.3                    | V    |

| VGH and VGH3 Pin Voltage              | V <sub>VGH</sub> , V <sub>VGH3</sub>                            | Positive charge pump                      | -0.3 to 31                                         | V    |

| CP21 Pin Voltage                      | V <sub>CP21</sub>                                               | Negative charge pump                      | -0.3 to 14                                         | V    |

| CP22 and VGL Pin Voltage              | V <sub>CP22</sub> , V <sub>VGL</sub>                            | Negative charge pump                      | -14 to 0.3                                         | V    |

| FAULT Pin Voltage                     | V <sub>FAULT</sub>                                              |                                           | -0.3 to lower of 10 or<br>V <sub>VIN</sub> + 0.3   | V    |

| BIAS, COMP, FSET Pin Voltage          | V <sub>BIAS</sub> , V <sub>COMP</sub> ,<br>V <sub>FSET</sub>    |                                           | -0.3 to 3.3                                        | V    |

| VCOM Pin Voltage                      | V <sub>VCOM</sub>                                               |                                           | -0.3 to lower of 8.5 or<br>V <sub>AVDD</sub> + 0.3 | V    |

| AGND, PGND and GNDVCOM Pin<br>Voltage | V <sub>AGND</sub> , V <sub>PGND</sub> ,<br>V <sub>GNDVCOM</sub> |                                           | -0.3 to 0.3                                        | V    |

| Logic Pins (EN, SCL, SDA, ADDR, NC)   | _                                                               |                                           | -0.3 to 5.5                                        | V    |

| Operating Ambient Temperature         | T <sub>A</sub>                                                  | K temperature range                       | -40 to 125                                         | °C   |

| Maximum Junction Temperature          | T <sub>J(max)</sub>                                             |                                           | 150                                                | °C   |

| Storage Temperature                   | T <sub>stg</sub>                                                |                                           | -55 to 150                                         | °C   |

<sup>[1]</sup> Stresses beyond those listed in this table may cause permanent damage to the device. The Absolute Maximum ratings are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics table is not implied. Exposure to Absolute Maximum-rated conditions for extended periods may affect device reliability.

## THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic             | Symbol        | Test Conditions <sup>[6]</sup>                    |    | Unit |

|----------------------------|---------------|---------------------------------------------------|----|------|

| Package Thermal Resistance | $R_{	hetaJA}$ | Package ES on 4-layer PCB based on JEDEC standard | 37 | °C/W |

<sup>[6]</sup> Additional thermal information available on the Allegro website.

<sup>[2]</sup> All voltages referenced to AGND.

<sup>[3]</sup> The SW pin has internal clamp diodes to GND. Applications that forward bias this diode should take care not to exceed the IC package power dissipation limits. Note: Exact energy specification to be determined.

<sup>[4]</sup> The switch DMOS is self-protected. If voltage spikes exceeding 40 V are applied, the device would conduct and absorb the energy safely.

$<sup>^{[5]}</sup>$  When  $V_{IN}$  = 0 (no power), all inputs are limited by -0.3 to 5.5 V.

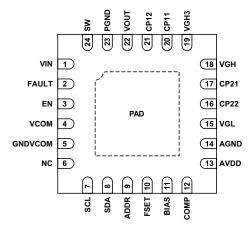

## PINOUT DIAGRAMS AND TERMINAL LIST TABLE

Package ES, 24-Pin QFN Pinouts

## **Terminal List Table**

| Number | Name    | Function                                                                                                                                                                                      |

|--------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | VIN     | Input supply voltage (3 to 10 V) for the IC                                                                                                                                                   |

| 2      | FAULT   | Open-drain output, pulls low in case of error condition                                                                                                                                       |

| 3      | EN      | Enable pin for enabling the IC; system can only be enabled after V <sub>IN</sub> is above UVLO level (refer to Startup Timing Diagram)                                                        |

| 4      | VCOM    | Output from internal low-dropout (LDO) regulator (item 2 in Functional Block Diagram) powered by AVDD                                                                                         |

| 5      | GNDVCOM | Ground reference for VCOM; connect to ground plane                                                                                                                                            |

| 6      | NC      | No Connect (reserved for Test Mode); connect to GND in actual PCB                                                                                                                             |

| 7      | SCL     | I <sup>2</sup> C clock signal                                                                                                                                                                 |

| 8      | SDA     | I <sup>2</sup> C data signal                                                                                                                                                                  |

| 9      | ADDR    | I <sup>2</sup> C address selection (up to 4 physical IC addresses based on voltage level)                                                                                                     |

| 10     | FSET    | Input for synchronizing boost and charge pump signals switching frequency to external clock signal; alternatively, it can be connected to an external resistor to set the switching frequency |

| 11     | BIAS    | Output from internal 2.8 V bias regulator; connect to GND via 1 µF ceramic capacitor for decoupling                                                                                           |

| 12     | COMP    | Compensation pin, connect to external COMP components (R <sub>Z</sub> and C <sub>Z</sub> )                                                                                                    |

| 13     | AVDD    | Output from internal LDO (item 1 in Functional Block Diagram) powered by V <sub>OUT</sub>                                                                                                     |

| 14     | AGND    | Analog GND reference for signals; connect to ground plane                                                                                                                                     |

| 15     | VGL     | Inverted charge pump output (item 3 in Functional Block Diagram)                                                                                                                              |

| 16     | CP22    | Capacitor terminals for inverted charge pump (item 3 in Functional Block Diagram)                                                                                                             |

| 17     | CP21    | Capacitor terminals for inverted charge pump (item 3 in Functional block blagram)                                                                                                             |

| 18     | VGH     | 2× charge pump output (item 4 in Functional Block Diagram)                                                                                                                                    |

| 19     | VGH3    | 3× charge pump output (item 4 in Functional Block Diagram)                                                                                                                                    |

| 20     | CP11    | Consider terminals for shares numn (item 4 in Functional Black Diagram)                                                                                                                       |

| 21     | CP12    | Capacitor terminals for charge pump (item 4 in Functional Block Diagram)                                                                                                                      |

| 22     | VOUT    | Connect to boost output for internal LDO and charge pump regulators                                                                                                                           |

| 23     | PGND    | Power ground for internal boost switch; connect this pin to ground terminal of output ceramic capacitor(s)                                                                                    |

| 24     | SW      | Internal boost converter switch node                                                                                                                                                          |

| _      | PAD     |                                                                                                                                                                                               |

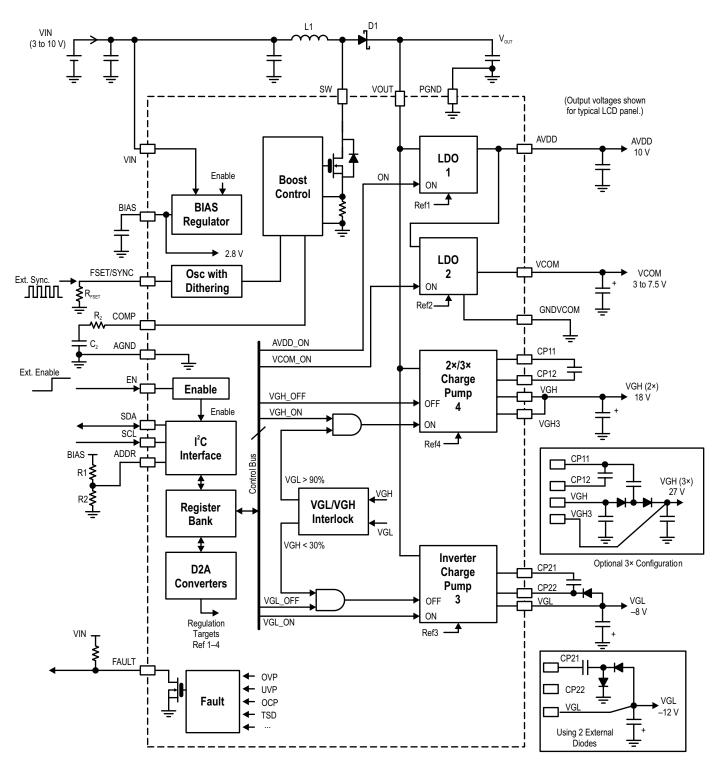

**Functional Block Diagram**

ELECTRICAL CHARACTERISTICS [1]: Valid at  $V_{IN}$  = 5 V, EN = high,  $f_{SW}$  = 2 MHz,  $V_{AVDD}$  = 10 V,  $V_{VGH1}$  = 20 V,  $V_{VGL}$  = -8 V,  $T_J$  =  $T_A$  = 25°C, except • indicates specifications guaranteed for  $T_J$  =  $T_A$  = -40°C to 125°C, unless otherwise specified

| Characteristics                                  | Characteristics Symbol Test Conditions |                                                                                                  |   | Min. | Тур. | Max. | Unit |  |

|--------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------|---|------|------|------|------|--|

| INPUT VOLTAGE AND CURRENT                        |                                        |                                                                                                  |   |      |      |      |      |  |

| Input Voltage                                    | V <sub>IN</sub>                        |                                                                                                  | • | 3    | _    | 10   | V    |  |

| VIN Pin Undervoltage Lockout<br>(UVLO) Threshold | V <sub>UVLO</sub>                      | V <sub>IN</sub> rising                                                                           |   | _    | 2.8  | 2.9  | V    |  |

| VIN Pin UVLO Hysteresis                          | V <sub>UVLO(HYS)</sub>                 |                                                                                                  |   | _    | 0.15 | 0.25 | V    |  |

| BIAS Voltage                                     | V <sub>BIAS</sub>                      | Internal BIAS regulator, EN = high                                                               |   | _    | 2.8  | _    | V    |  |

| Shutdown BIAS Current [1]                        | I <sub>VINBIAS(SD)</sub>               | Current into VIN pin, EN = low                                                                   | • | -    | 1    | 10   | μA   |  |

| Standby BIAS Current                             | I <sub>VINBIAS(STB)</sub>              | EN = high, output disabled                                                                       |   | _    | 3    | _    | mA   |  |

| Operating BIAS Current                           | I <sub>VINBIAS(OP)</sub>               | EN = high, output enabled                                                                        |   | _    | 6    | _    | mA   |  |

| BOOST SWITCH                                     |                                        |                                                                                                  |   |      |      |      | •    |  |

| Switch Peak Current Limit                        | I <sub>SWILIM</sub>                    | Cycle-by-cycle current limit                                                                     | • | 2.2  | 2.6  | 3    | А    |  |

| Switch Secondary Current Limit                   | I <sub>SWILIM2</sub>                   | Trips SW_OCP fault if exceeded                                                                   |   | _    | 3.7  | _    | Α    |  |

| Switch On-Resistance                             | R <sub>DS(on)</sub>                    | I <sub>SW</sub> = 0.4 A                                                                          |   | _    | 0.4  | 0.7  | Ω    |  |

| Switch Minimum On-Time                           | t <sub>ON(MIN)</sub>                   |                                                                                                  | • | _    | 65   | 120  | ns   |  |

| Switch Minimum Off-Time                          | t <sub>OFF(MIN)</sub>                  |                                                                                                  | • | _    | 60   | 100  | ns   |  |

| SW Pin Leakage Current                           | I <sub>SW(LKG)</sub>                   | V <sub>SW</sub> = 5 V, EN = low                                                                  |   | _    | 0.1  | _    | μΑ   |  |

| VOLT DI L. C.                                    |                                        | V <sub>OUT</sub> = 5 V, EN = low                                                                 |   | _    | 0.1  | _    | μΑ   |  |

| VOUT Pin Leakage Current                         | I <sub>OUT(LKG)</sub>                  | V <sub>OUT</sub> = 10 V, EN = low                                                                |   | _    | 25   | 37   | μΑ   |  |

| SW Pin Overvoltage Protection<br>Threshold       | V <sub>SW(OVP)</sub>                   | Measured from SW to GND                                                                          |   | 18.6 | 21   | 23   | V    |  |

| SW OVP Detection Time [2]                        | t <sub>SW(OVP)</sub>                   | Minimum pulse width required for V <sub>SW</sub> ≥ V <sub>SW(OVP)</sub> to be detected as SW OVP |   | _    | 40   | _    | ns   |  |

| SW OVP to Shutdown Delay [2]                     | t <sub>FAULT(OVP)</sub>                | Delay from SW OVP to FAULT = L                                                                   |   | _    | 1    | 2.5  | μs   |  |

| SWITCHING FREQUENCY/SYNCH                        |                                        |                                                                                                  |   |      |      |      | *    |  |

| FSET_SYNC Pin Voltage                            | V <sub>FSETSYNC</sub>                  | Without using outernal aunahranization signal                                                    |   | _    | 0.64 | _    | V    |  |

| FSET_SYNC Pin Current                            | I <sub>FSETSYNC</sub>                  | Without using external synchronization signal                                                    |   | 22   | _    | 140  | μA   |  |

| Switching Frequency                              | f <sub>SW</sub>                        | $R_{FSET\_SYNC} = 5.1 \text{ k}\Omega$                                                           | • | 1.8  | 2    | 2.2  | MHz  |  |

| Synchronization Frequency                        | f <sub>SYNC</sub>                      | External logic sugnal connected to FSET_<br>SYNC pin                                             |   | 0.35 | _    | 2.25 | MHz  |  |

| Synchronization Minimum On-Time                  | t <sub>SYNC(ON)</sub>                  |                                                                                                  | • | 150  | _    | _    | ns   |  |

| Synchronization Minimum Off-Time                 | t <sub>SYNC(OFF)</sub>                 |                                                                                                  | • | 150  | _    | _    | ns   |  |

|                                                  |                                        | No external synch, REG0x10 = '00b'                                                               |   | _    | 0    | _    | %    |  |

| Switching Frequency Dithering                    | ٨٤                                     | No external synch, REG0x10 = '01b'                                                               |   | _    | 5    | _    | %    |  |

| Range                                            | $\Delta f_{SW0}$                       | No external synch, REG0x10 = '10b'                                                               |   | _    | 10   | _    | %    |  |

|                                                  |                                        | No external synch, REG0x10 = '11b'                                                               |   | _    | 15   | _    | %    |  |

Continued on the next page...

ELECTRICAL CHARACTERISTICS [1] (continued): Valid at  $V_{IN} = 5$  V, EN = high,  $f_{SW} = 2$  MHz,  $V_{AVDD} = 10$  V,  $V_{VGH1} = 20$  V,  $V_{VGL} = -8$  V,  $V_{IN} = -8$  V,  $V_{$

| Characteristics                                              | Symbol                | Test Conditions                                                                                |   | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------|---|------|------|------|------|

| ERROR AMPLIFIER                                              |                       |                                                                                                |   |      |      | l.   |      |

| Open-Loop Voltage Gain [2]                                   | A <sub>VOL</sub>      |                                                                                                |   | _    | 43   | _    | dB   |

| Transconductance [2]                                         | g <sub>m</sub>        | I <sub>COMP</sub> = between –100 μA and 100 μA                                                 |   | _    | 550  | _    | μA/V |

| EA Source Current                                            | I <sub>EA_SRC</sub>   | V <sub>COMP</sub> = 0.7 V, V <sub>OUT</sub> below regulation target                            |   | _    | 200  | _    | μA   |

| EA Sink Current                                              | I <sub>EA SINK</sub>  | V <sub>COMP</sub> = 0.7 V, V <sub>OUT</sub> over regulation target                             |   | _    | 200  | _    | μA   |

| COMP Pull Prove Projects                                     | R <sub>COMP1</sub>    | Active pull-down when EN = H, Boost disabled                                                   |   | _    | 2.5  | _    | kΩ   |

| COMP Pull-Down Resistor                                      | R <sub>COMP2</sub>    | Passive pull-down when EN = L                                                                  |   | _    | 450  | _    | kΩ   |

| LOGIC INPUTS                                                 |                       |                                                                                                |   |      |      |      |      |

| EN Pin Logic High                                            | V <sub>IH_EN</sub>    |                                                                                                | • | 1.8  | _    | _    | V    |

| EN Pin Logic Low                                             | V <sub>IL EN</sub>    |                                                                                                | • | _    | _    | 0.8  | V    |

| Internal Pull-Down Resistance to AGND                        | R <sub>EN(PD)</sub>   |                                                                                                |   | -    | 100  | _    | kΩ   |

| Hard-Reset Duration [2]                                      | t <sub>RESET</sub>    | EN = L duration in order to initiate a hardware reset during normal operation                  |   | 2    | _    | _    | μs   |

| FSET Pin Input Logic High                                    | V <sub>IH FSE</sub>   | When used in external sync mode                                                                | • | 1.5  | _    | _    | V    |

| FSET Pin Input Logic Low                                     | V <sub>IL_FSE</sub>   | When used in external sync mode                                                                | • | _    | _    | 0.4  | V    |

| OVER- AND UNDERVOLTAGE PRO                                   | TECTION FO            | R OUTPUT REGULATORS                                                                            |   |      |      |      |      |

| Output Overvoltage Fault Threshold                           | V <sub>OUTx(OV)</sub> | Output rising; measured as % of target voltage                                                 |   | _    | 120  | _    | %    |

| Output Undervoltage Fault Threshold                          | V <sub>OUTx(UV)</sub> | Output falling; measured as % of target voltage                                                |   | -    | 80   | _    | %    |

| OUTPUT REGULATORS                                            |                       |                                                                                                |   |      |      |      |      |

| AVDD Output Voltage                                          | V <sub>AVDD</sub>     |                                                                                                | • | 5    | _    | 15   | V    |

| VCOM Output Voltage                                          | V <sub>VCOM</sub>     | V <sub>AVDD</sub> > V <sub>VCOM</sub> + 1.5 V                                                  | • | 2.5  | _    | 7.5  | V    |

| VGH Output Voltage                                           | $V_{VGH}$             | VGH & VGH3 shorted                                                                             | • | 10   | _    | 30   | V    |

| VGL Output Voltage                                           | $V_{VGL}$             |                                                                                                | • | -12  | _    | -4   | V    |

| Boost Minimum Headroom for AVDD Regulator                    | V <sub>AVDD(DO)</sub> | Defined as $V_{OUT} - V_{AVDD}$ ; when AVDD = 15 V, $I_{OUT}$ = 100 mA                         |   | -    | 2.1  | _    | V    |

| Boost Minimum Headroom for VGH Regulator                     | V <sub>VGH(DO)</sub>  | Defined as $V_{OUT} - V_{VGH} / 2$ ; when $V_{VGH} = 24 \text{ V}$ , $I_{OUT} = 8 \text{ mA}$  |   | -    | 2.9  | _    | V    |

| Boost Minimum Headroom for VGL Regulator                     | V <sub>VGL(DO)</sub>  | Defined as $V_{OUT} - (-V_{VGL})$ ; when $V_{VGL} = -12 \text{ V}$ , $I_{OUT} = -8 \text{ mA}$ |   | -    | 3.5  | _    | V    |

| Ouptut Pull-Down Resistor During<br>Shutdown (AVDD, VCOM)    | R <sub>OUTPD1</sub>   | EN = high, output disabled                                                                     |   | -    | 250  | -    | Ω    |

| Ouptut Pull-Down Resistor During<br>Shutdown (VGH, VGL)      | R <sub>OUTPD2</sub>   | EN = high, output disabled                                                                     |   | -    | 500  | _    | Ω    |

| Ouptut Pull-Down Resistor in Sleep<br>Mode (AVDD, VCOM, VGH) | R <sub>OUTPD3</sub>   | EN = low, V <sub>IN</sub> > V <sub>UVLO</sub>                                                  |   | -    | 1    | _    | kΩ   |

| Ouptut Pull-Down Resistor in Sleep<br>Mode (VGL only)        | R <sub>OUTPD4</sub>   | EN = low                                                                                       |   | _    | 10   |      | kΩ   |

Continued on the next page...

ELECTRICAL CHARACTERISTICS [1] (continued): Valid at  $V_{IN} = 5$  V, EN = high,  $f_{SW} = 2$  MHz,  $V_{AVDD} = 10$  V,  $V_{VGH1} = 20$  V,  $V_{VGL} = -8$  V,  $T_J = T_A = 25$ °C, except • indicates specifications guaranteed for  $T_J = T_A = -40$ °C to 125°C, unless otherwise specified

| Characteristics                                                                     | Symbol                                                             | Test Conditions                                                                                                                         |   | Min.       | Тур.  | Max. | Unit  |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---|------------|-------|------|-------|

| OUTPUT CURRENT CAPACITY                                                             |                                                                    |                                                                                                                                         |   |            |       |      |       |

| AVDD OCP Trip Level                                                                 | I <sub>AVDD(OCP)</sub>                                             | Includes I <sub>VCOM</sub>                                                                                                              |   | 200        | 275   | 350  | mA    |

| VCOM OCP Trip Level                                                                 | I <sub>VCOM(OCP)</sub>                                             |                                                                                                                                         |   | 36         | 45    | 54   | mA    |

| VGH OCP Trip Level                                                                  | I <sub>VGH(OCP)</sub>                                              |                                                                                                                                         |   | 11         | 20    | 26   | mA    |

| VGL OCP Trip Level                                                                  | I <sub>VGL(OCP)</sub>                                              | Current into VGL pin                                                                                                                    |   | 11         | 20    | 26   | mA    |

| OUTPUT VOLTAGE ACCURACY                                                             | , ,                                                                |                                                                                                                                         |   |            |       | ,    |       |

| AVDD, VGH, and VGL Load<br>Regulation                                               | V <sub>AVDDreg</sub><br>V <sub>VGHreg</sub><br>V <sub>VGLreg</sub> | $V_{AVDD}$ =10 V, $I_{AVDD}$ = 10 to 100 mA<br>$V_{VGH}$ = 20 V, $I_{VGH}$ = 0.4 to 4 mA<br>$V_{VGL}$ = -8 V, $I_{VGL}$ = -0.8 to -8 mA | • | -0.1       | _     | 0.1  | V     |

| AVDD Accuracy                                                                       | Err <sub>AVDD</sub>                                                | Reg00 = 0x40 (V <sub>AVDD</sub> = 10.04 V), I <sub>AVDD</sub> = 50 mA                                                                   | • | -2.1       | _     | 2.1  | %     |

| VCOM Accuracy                                                                       | Err <sub>VCOM</sub>                                                | Reg01,02 = 0x100 ( $V_{VCOM}$ = 5.005 V),<br>$I_{VCOM}$ = 10 mA                                                                         | • | -2.1       | _     | 2.1  | %     |

| VGH Accuracy                                                                        | err <sub>VGH</sub>                                                 | Reg04 = 0x40 (V <sub>VGH</sub> = 20.65 V), I <sub>VGH</sub> = 2 mA                                                                      | • | -2.5       | _     | 2.5  | %     |

| VGL Accuracy                                                                        | err <sub>VGL</sub>                                                 | Reg03 = 0x20 ( $V_{VGL}$ = -8.39 V), $I_{VGL}$ = -4 mA                                                                                  | • | -2.5       | _     | 2.5  | %     |

| VCOM Step Size                                                                      |                                                                    |                                                                                                                                         |   |            | 10    |      | mV    |

| VCOM Load Regulation <sup>[2]</sup>                                                 | V <sub>VCOMreg</sub>                                               | I <sub>LOAD</sub> = 2 to 20 mA, V <sub>VCOM</sub> = 5.0 V                                                                               | • | <b>-</b> 5 | _     | 5    | mV    |

| VCOM Temperature Coefficient <sup>[2]</sup>                                         | TC <sub>VCOM</sub>                                                 | V <sub>VCOM</sub> = 5 V, -30°C < T <sub>A</sub> < 85°C,<br>I <sub>LOAD</sub> = 10 mA                                                    | • | -100       | _     | 150  | μV/°C |

| Minimum Dropout for VCOM from AVDD                                                  | V <sub>VCOM(DO)</sub>                                              | V <sub>AVDD</sub> = 7 V, I <sub>VCOM</sub> = 20 mA                                                                                      |   | -          | _     | 1.5  | V     |

| FAULT PIN                                                                           |                                                                    |                                                                                                                                         |   |            | *     |      |       |

| FAULT Pull-Down Voltage                                                             | V <sub>FAULT(PD)</sub>                                             | Fault condition asserted, pull-up current = 1 mA                                                                                        |   | _          | _     | 0.4  | V     |

| FAULT Pin Leakage Current                                                           | V <sub>FAULT(LKG)</sub>                                            | Fault condition cleared, pull-up to 5 V                                                                                                 |   | _          | _     | 1    | μA    |

| PROGRAMMABLE DELAYS AND                                                             | TIMERS                                                             |                                                                                                                                         |   |            |       |      |       |

| Startup Timeout/Watchdog Timer                                                      | t <sub>SU_TO_min</sub>                                             | Minimum timeout when Reg0x9 = 0x03 or lower                                                                                             |   | _          | 9.6   | _    | ms    |

| (Time limit for all outputs to reach<br>90% target, starting from internal<br>EN=H) | t <sub>SU_TO_max</sub>                                             | Maximum timeout when Reg0x9 = 0x1F                                                                                                      |   | -          | 99.2  | _    | ms    |

| Startup Delay Timer#1-4                                                             | t <sub>SU_DLY_min</sub>                                            | Minimum delay when Reg_X = 0x00, X = 58 [3]                                                                                             |   | _          | 0     | _    | ms    |

| (One each for AVDD/VCOM/VGL/<br>VGH)                                                | t <sub>SU_DLY_max</sub>                                            | Maximum delay when Reg_X = 0xFF, X = 58 [3]                                                                                             |   | _          | 25.5  | -    | ms    |

| Shutdown Timeout<br>(starting from internal EN = L)                                 | t <sub>SD_TO</sub>                                                 | All outputs discharged to below 10% target (30% for VGL and VGH)                                                                        |   | 40         | 50    | 65   | ms    |

| Shutdown Delay Timer#5-8                                                            | t <sub>SD_DLY_min</sub>                                            | Minimum delay when Reg_X = 0x00,<br>X = C,D,E,F [3]                                                                                     |   | -          | 0     |      | ms    |

| (One each for AVDD/VCOM/VGL/<br>VGH)                                                | t <sub>SD_DLY_max</sub>                                            | Maximum delay when Reg_X = 0xFF,<br>X = C,D,E,F [3]                                                                                     |   | -          | 25.5  | _    | ms    |

| Overcurrent Protection (OCP) Timeout                                                | t <sub>OCP_TO</sub>                                                | Maximum time for any output to stay in OCP fault condition before shutdown.                                                             |   | 40         | 50    | 60   | ms    |

| Fault Retry Counter                                                                 | N <sub>RESTART</sub>                                               | Maximum number of fault retries. Programmable through Reg0x0A                                                                           |   | 0          | _     | 15   |       |

| Fault Cool-Down Timer                                                               | t <sub>RESTART_min</sub>                                           | Cooldown time between fault shutdown and next retry. Reg0x0B = 0x03 or lower                                                            |   | _          | 9.6   | _    | ms    |

| rauit Cool-Down Timer                                                               | t <sub>RESTART_max</sub>                                           | Cooldown time between fault shutdown and next retry. Reg0x0B = 0x3F                                                                     |   | -          | 201.6 | _    | ms    |

Continued on the next page...

ELECTRICAL CHARACTERISTICS [1] (continued): Valid at  $V_{IN} = 5$  V, EN = high,  $f_{SW} = 2$  MHz,  $V_{AVDD} = 10$  V,  $V_{VGH1} = 20$  V,  $V_{VGL} = -8$  V,  $T_J = T_A = 25$ °C, except • indicates specifications guaranteed for  $T_J = T_A = -40$ °C to 125°C, unless otherwise specified

| Characteristics                       | Symbol                 | Test Conditions                     |     | Min. | Тур. | Max. | Unit |

|---------------------------------------|------------------------|-------------------------------------|-----|------|------|------|------|

| THERMAL SHUTDOWN (TSD) PROTECTION     |                        |                                     |     |      |      |      |      |

| TSD Threshold [2]                     | T <sub>TSD</sub>       | Temperature rising                  |     | 155  | 165  | _    | °C   |

| TSD Hysteresis <sup>[2]</sup>         | T <sub>TSD(HYS)</sub>  |                                     |     | _    | 20   | _    | °C   |

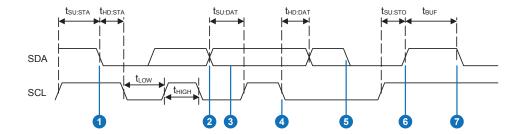

| I <sup>2</sup> C INTERFACE            |                        |                                     | · · |      |      |      | `    |

| Logic Input Low (SDA, SCL)            | V <sub>SCL(L)</sub>    |                                     |     | _    | _    | 8.0  | V    |

| Logic Input High (SDA, SCL)           | V <sub>SCL(H)</sub>    |                                     |     | 2.3  | _    | _    | V    |

| Logic Input Hysteresis <sup>[2]</sup> | V <sub>I2CIHYS</sub>   |                                     |     | _    | 150  | -    | mV   |

| Logic Input Current                   | I <sub>I2CI</sub>      |                                     |     | -1   | _    | 1    | μA   |

| SDA Output Voltage Low                | V <sub>I2COut(L)</sub> | SDA = Low, pull-up current = 2.5 mA |     | _    | _    | 0.4  | V    |

| SDA Output Leakage                    | I <sub>I2CLKG</sub>    | EN = Low, pull-up to 5.5 V          |     | _    | _    | 1    | μA   |

| SCL Clock Frequency                   | f <sub>CLK</sub>       |                                     |     | _    | _    | 400  | KHz  |

| ADDR PIN COMPARATOR THRES             | HOLD                   |                                     |     |      |      |      |      |

| Voltage Level for Address 101,0000    | V <sub>ADDLEVEL1</sub> | ADDR connected to GND               |     | 0    | _    | 0.3  | V    |

| Voltage Level for Address 101,0001    | V <sub>ADDLEVEL2</sub> |                                     |     | 0.6  | _    | 0.9  | V    |

| Voltage Level for Address 101,0010    | V <sub>ADDLEVEL3</sub> |                                     |     | 1.5  | _    | 1.8  | V    |

| Voltage Level for Address 101,0011    | V <sub>ADDLEVEL4</sub> | ADDR connected to BIAS pin          |     | 2.4  | _    | 3    | V    |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Ensured by design and characterization, not production tested.

<sup>[3]</sup> Refer to Table 5 for Register Map.

## CHARACTERISTIC PERFORMANCE

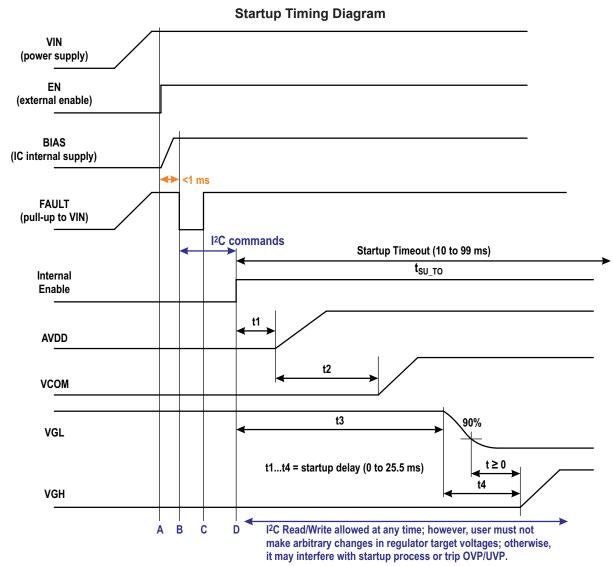

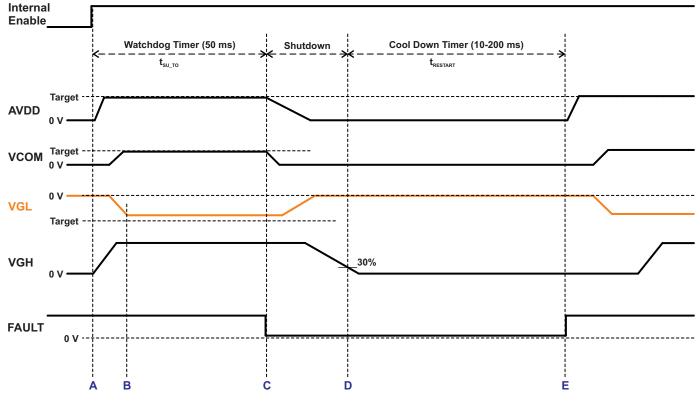

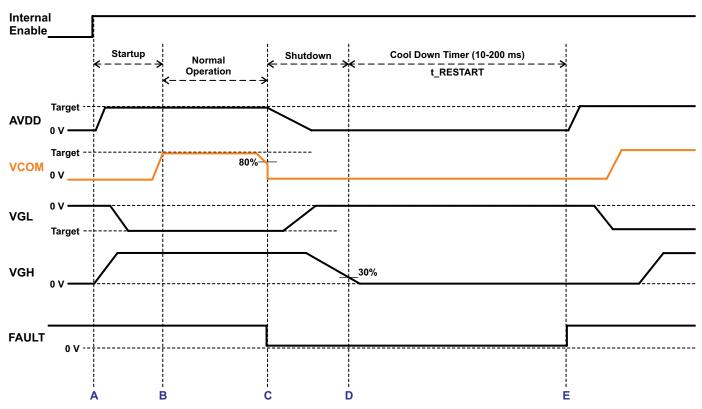

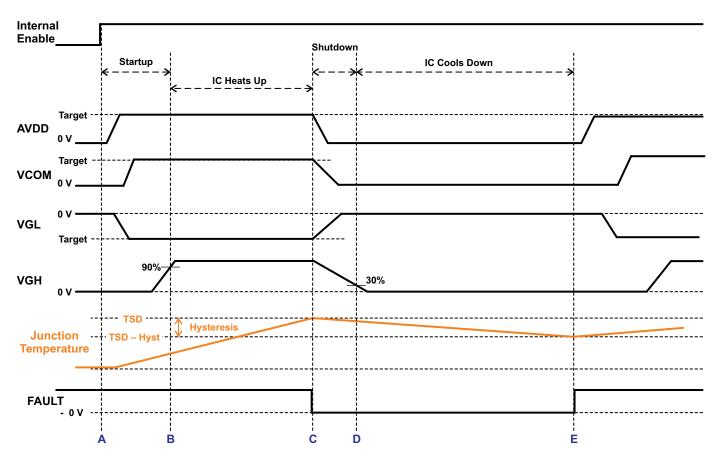

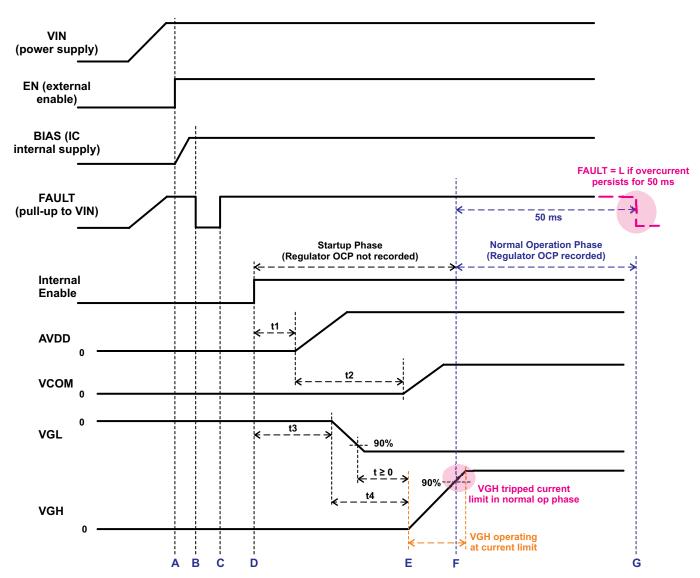

#### Sequence of events:

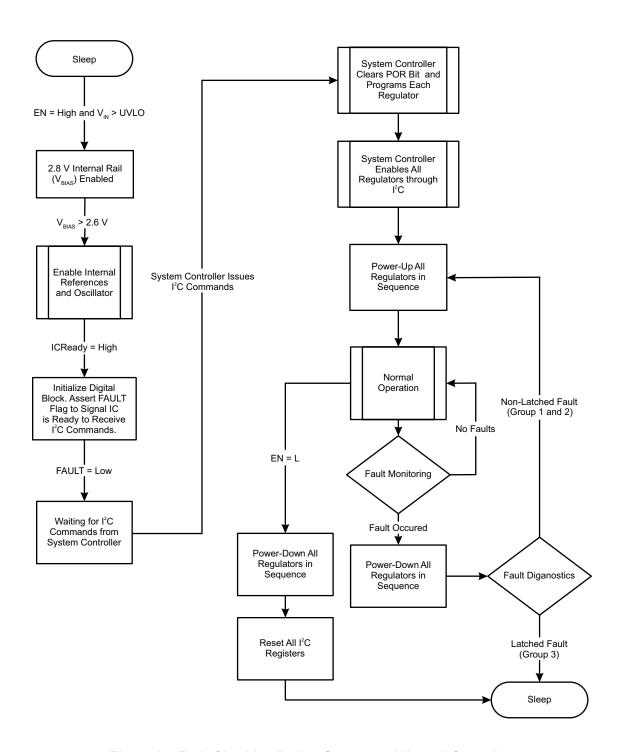

- A: System controller brings EN = H to enable the A8603, provided that  $V_{IN}$  is above UVLO level.

- B:After A8603 performs a Power-On Reset (POR), it pulls down FAULT flag to signal that it is ready for I2C commands. (\*)

- C:System controller detected FAULT = L and sends in I<sup>2</sup>C command to clear POR status bit. This resets FAULT to H (unless there were other faults detected).

- D:After Programming the A8603 registers, system controller sets the regulator\_internal\_enable bit to 1 to turn on all output regulators.

#### **Notes on Startup Timing Diagram**

- · Each regulator has a programmable Startup Delay timer. Each timer has a resolution of 0.1 ms and a maximum duration of 25.5 ms.

- VCOM cannot start before AVDD (because internally the VCOM regulator takes its power from AVDD output)

- · VGH cannot start before VGL has reached 90% of its target voltage

- There is no dependency between {t1, t2} and {t3, t4}. That means VGL/VGH can start before or after AVDD/VCOM

- If any regulator output failed to reach 90% target after the Startup Timeout period (default 50 ms, starting from Internal Enable = H), the FAULT pin will be pulled low and all outputs are shut down in an orderly manner. The IC will then retry after a Cool Down period.

- (\*) The delay time between EN = H and FAULT = L depends mainly on how fast the external BIAS capacitor can be charged up. For example, charging 1 μF at 5 mA from 0 to 2.8 V takes ~0.6 ms. Therefore, a 1 ms delay time is sufficient.

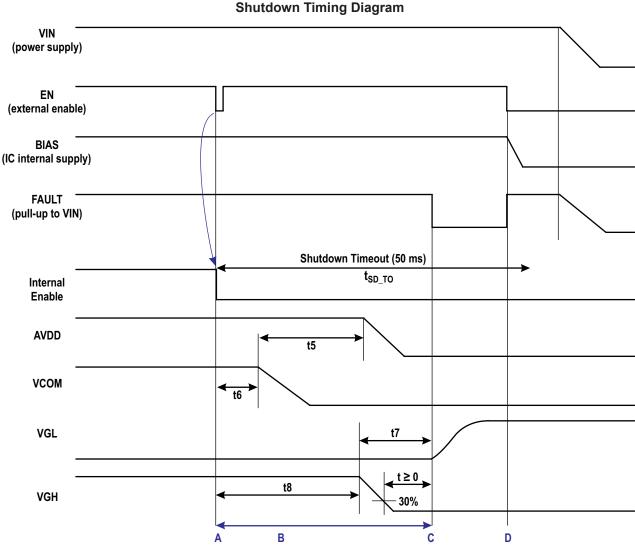

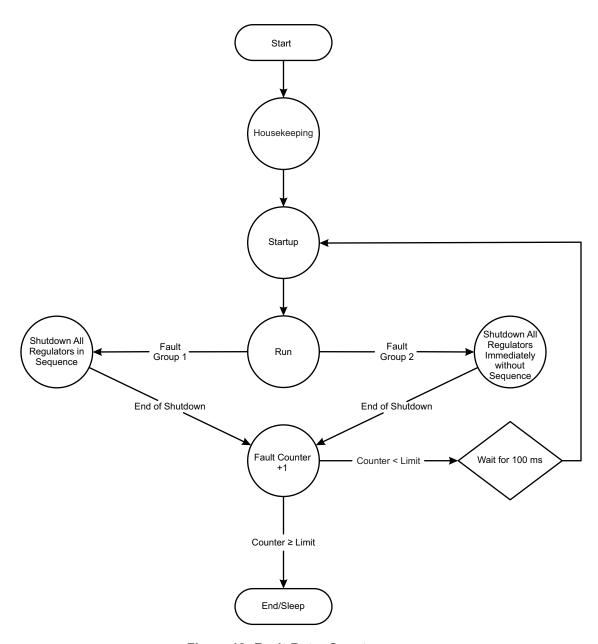

#### Sequence of events:

- A: System controller brings EN pin to Low for >2 µs to initiate a "Hardware Shutdown." The IC responds by pulling Internal Enable to Low.

- B: The A8603 shuts down all output regulators in sequence, according to their shutdown delay times. All registers will be restored to power-up defaults at the end of a Hardware Shutdown. This does not apply to a Software Shutdown when user programs INT EN = L.

- C:After the last regulator has shut down, the A8603 resets all internal registers to their power-on defaults, sets the HARD\_RESET status bit to 1, and pulls FAULT pin to Low. The A8603 is now ready to accept new I<sup>2</sup>C commands.

- D: The A8603 is powered down only if EN = L after shutdown has completed.

#### **Notes on Shutdown Timing Diagram**

- Each regulator has a programmable Shutdown Delay timer. Each timer has a resolution of 0.1 ms and a maximum duration of 25.5 ms.

- AVDD can only be turned off after VCOM is turned off (t5 = 0 is allowed)

- VGL can only be turned off after VGH drops below 30%, even through t7 = 0 is allowed.

- There is no dependency between {t5, t6} and {t7, t8}

- Once a shutdown is in progress, both external Enable and Internal EN are ignored until shutdown is completed.

- All output discharge times are based on external capacitance and internal pull-down resistance (250 Ω for AVDD and VCOM, 500 Ω for VGH and VGL). The external DC load is assumed to be negligible.

- If any of the regulator output does not decay to below 10% (30% for VGL and VGH) of target voltage after 50 ms time-out period, starting from beginning of shutdown, it is ignored and then the IC is allowed to power down.

## **FUNCTIONAL DESCRIPTION**

The A8603 is a flexible multivoltage regulator designed for LCD panel bias applications. It utilizes a high-efficiency boost converter, together with space-saving low-dropout (LDO) regulator and charge pump circuits to provide four independently adjustable voltage outputs:

- AVDD: Typically between 5 and 15 V. Nominal output current 100 mA. This output is from a LDO powered by VOUT.

- VCOM: Typically between 3 and 7.5 V at 20 mA. The power supply of this regulator is internally connected to AVDD.

Therefore AVDD must be at least 1.5 V higher than the upper limit of VCOM.

- VGL: Typically between -12 and -4 V at 4 mA. This voltage is generated by an inverted charge pump, which is powered by VOUT.

- VGH: Typically between 10 and 24 V at 4 mA. This voltage is generated by a 2× charge pump, which is powered by VOUT.

If necessary, an external 3× charge pump can generate a higher VGH between 20 and 30 V at 4 mA.

## **Program Diagnostics**

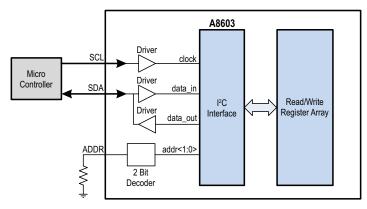

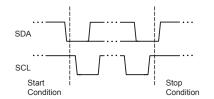

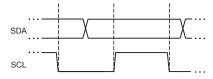

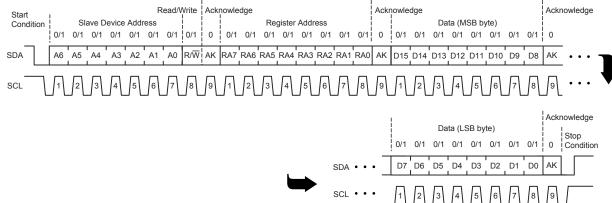

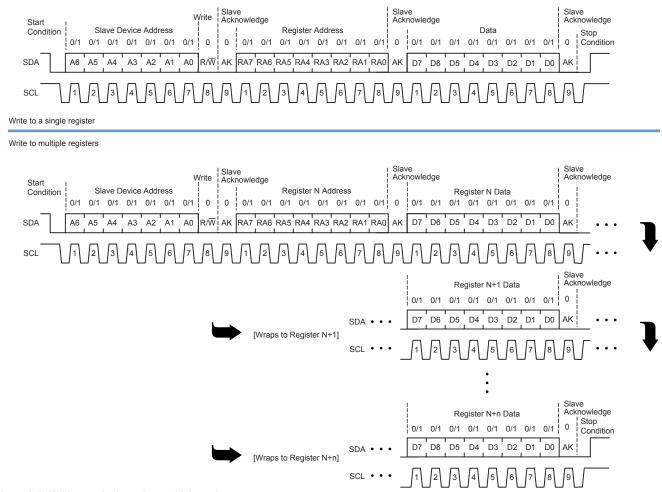

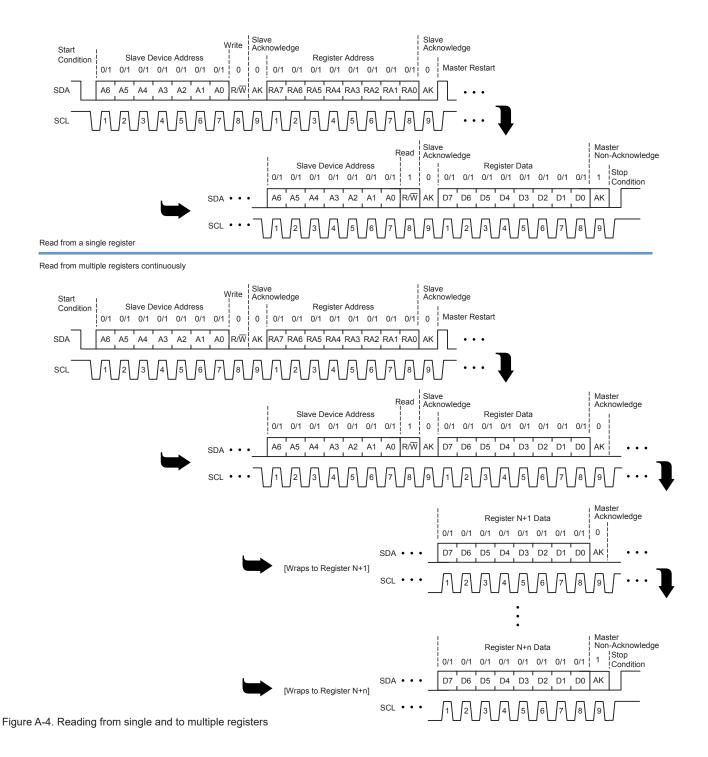

A8603 features the I<sup>2</sup>C (Inter-Integrated Circuit, alternatively spelled as I2C) serial interface and programmable memory array.

The I<sup>2</sup>C serial interface allows external microcontroller or some type of master device to communicate with A8603 as its slave

Figure 1: I<sup>2</sup>C Serial Interface and Programmable Memory Array

device. Two bus lines, SCL and SDA, provide access to the internal control registers. The clock input on the SCL pin is generated by the master, while the SDA line functions as either an input or an open-drain output for the A8603, depending on the direction of the data flow.

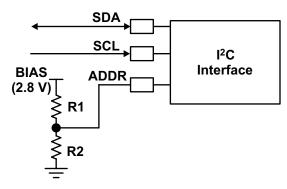

In case there are two or more slave devices in an I<sup>2</sup>C network, each device must present a unique physical address for the master to select. To avoid conflict, the A8603 uses a 4-level ADDR pin to set its physical address. Depending on the voltage level at ADDR, the physical address is set as '101,00xx', where  $xx = \{00 \mid 01 \mid 10 \mid 11\}$ . This is illustrated by the figure below.

Figure 2: Select I<sup>2</sup>C Address by Using Resistor Divider at ADDR Pin

Table 1: I<sup>2</sup>C Address Selection Using Resistor Divider

| R1 (k) | R2 (k) | V <sub>ADDR</sub> (V) | I <sup>2</sup> C Address |

|--------|--------|-----------------------|--------------------------|

| open   | 0      | 0                     | 101,0000                 |

| 27.4   | 10     | 0.75                  | 101,0001                 |

| 6.98   | 10     | 1.65                  | 101,0010                 |

| 0      | open   | 2.8                   | 101,0011                 |

## A8603

# Multiple-Output Regulator for Automotive LCD Displays

## **Programmable Regulators**

The A8603 has four voltage regulators: AVDD, VCOM, VGL, and VGH.

Target voltages of all four regulators are programmable by internal registers. In addition, other features (such as startup and shutdown sequences, Fault retry counter, etc.) can also be programmed.

The target voltage for each output regulator is programmed by writing to a register, according to the following equation:

Target  $Voltage = Min\ voltage + \#steps \times step\ size$

For example, to set AVDD to 12 V, the user should write '0x59' to Reg0x00. This is because:

$$\#steps = (Target\_Voltage - Min\_Voltage) / step\_size$$

=  $(12 - 5) / 0.07874 = 88.9$

So the content of Reg0x00 is 89 in decimal, or '0x59' in hexadecimal.

**Table 2: Target Voltages**

| Output Regulator | Register | Min. Voltage (V) | Max. Voltage (V) | DAC # of Bits | DAC # of Steps | Step Size (mV) |

|------------------|----------|------------------|------------------|---------------|----------------|----------------|

| AVDD             | 00       | 5 (Reg=0x00)     | 15 (0x7F)        | 7             | 127            | 78.74          |

| VCOM             | 01, 02   | 2.5 (0x0000)     | 7.5 (0x01FF)     | 9             | 511            | 9.785          |

| VGL              | 03       | -3.6 (0x00)      | -13.03 (0x3F)    | 6             | 63             | -149.7         |

| VGH              | 04       | 9.9 (0x00)       | 31.236 (0x7F)    | 7             | 127            | 168            |

<sup>\*</sup>Note: AVDD must be at least 1.5V higher than VCOM, so not all combinations of VCOM and AVDD are possible.

**Table 3: Startup Time Delay**

Refer to Startup Timing Diagram on how those time delays are defined.

| Timer     | Min. Delay (ms) | Max. Delay (ms) | Step Size (ms) | Number of Bits |

|-----------|-----------------|-----------------|----------------|----------------|

| t1 = AVDD | 0 (0x00)        | 25.5 (0xFF)     | 0.1            | 8              |

| t2 = VCOM | 0               | 25.5            | 0.1            | 8              |

| t3 = VGL  | 0               | 25.5            | 0.1            | 8              |

| t4 = VGH  | 0               | 25.5            | 0.1            | 8              |

**Table 4: Shutdown Time Delay**

Refer to Shutdown Timing Diagram on how those time delays are defined.

| Timer     | Min. Delay (ms) | Max. Delay (ms) | Step Size (ms) | Number of Bits |

|-----------|-----------------|-----------------|----------------|----------------|

| t5 = AVDD | 0 (0x00)        | 25.5 (0xFF)     | 0.1            | 8              |

| t6 = VCOM | 0               | 25.5            | 0.1            | 8              |

| t7 = VGL  | 0               | 25.5            | 0.1            | 8              |

| t8 = VGH  | 0               | 25.5            | 0.1            | 8              |

| Name                | Register | Default         | Min.          | Max.            | Step Size | Number of Bits |

|---------------------|----------|-----------------|---------------|-----------------|-----------|----------------|

| Watchdog Timer      | 0x09     | 51.2 (0x10) ms  | 9.6 (0x03) ms | 99.2 (0x1F) ms  | 3.2 ms    | 5              |

| Cooldown Timer      | 0x0B     | 102.4 (0x20) ms | 9.6 (0x03) ms | 201.6 (0x3F) ms | 3.2 ms    | 6              |

| Fault Retry Counter | 0x0A     | 8 (0x08)        | 0 (0x00)      | 15 (0x0F)       | 1         | 4              |

### **Dithering:**

Reg0x10 bit[0,1]: controls Dithering off,  $\pm 5\%$ , 10% or 15%.

#### **Power Sequence:**

Reg0x10 bit4: By default VGL is enabled before VGH during power-up. But if this bit is set to '1', then VGH is enabled first.

Table 5: I<sup>2</sup>C Register Map

| Registers                 | Default     | Address      | Comments                                                                                                                                                                           |

|---------------------------|-------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | Delault     | 0x00-0x13    | Confinents                                                                                                                                                                         |

| Regulator Programming     | 0v40        |              | 7 hite adjust AVDD regulator output from 5 V to 15 V in 79 74 mV aton                                                                                                              |

| AVDD_voltage              | 0x40        | 0x00         | 7 bits adjust AVDD regulator output from 5 V to 15 V in 78.74 mV step.                                                                                                             |

| VCOM_voltage_msb          | 0x1<br>0x0  | 0x01<br>0x02 | 9 bits adjust VCOM regulator output from 2.5 V to 7.5 V in 9.785 mV step.  Must be programmed in the order of MSB followed by LSB.                                                 |

| VCI_voltage_lsb           | 0x0<br>0x20 | 0x02         | 6 bits adjust VGL regulator output from –3.6 V to –13.03 V in –150 mV step.                                                                                                        |

| VGL_voltage               | 1 1         | 0x03<br>0x04 |                                                                                                                                                                                    |

| VGH_voltage               | 0x40        |              | 7 bits adjust VGH regulator output from 9.9 V to 31.236 V in 168 mV step.                                                                                                          |

| delay_startup_AVDD        | 0x0         | 0x05         | Program the turn-on delay for AVDD. 100 µs step size. 0 ms to 25.5 ms.                                                                                                             |

| delay_startup_VCOM        | 0x20        | 0x06         | Program the turn-on delay for VCOM (after AVDD). 100 µs step size. 0 ms to 25.5 ms. See Startup Timing diagram.                                                                    |

| delay_startup_VGL         | 0x40        | 0x07         | Program the turn-on delay for VGL. 100 µs step size. 0 ms to 25.5 ms.                                                                                                              |

| delay_startup_VGH         | 0x40        | 0x08         | Program the turn-on delay for VGH (after VGL). 100 $\mu s$ step size. 0 ms to 25.5 ms.                                                                                             |

| watchdog_timer            | 0x10        | 0x09         | Maximum time allowing regulator to reach its target value. 3.2 ms step. 9.6 ms to 99.2 ms. Same value is used for all regulators.                                                  |

| fault_counter             | 0x8         | 0x0A         | Programmable counter allowing system to reattempt 0 to 15 times at the event of fault.                                                                                             |

| cooldown_timer            | 0x20        | 0x0B         | Prevent immediate reattempt after the fault. System will wait for timer to expire before possible reattempt to turn on the regulators. Step size 3.2 ms. Range 9.6 ms to 201.6 ms. |

| delay_shutdown_AVDD       | 0x0         | 0x0C         | Program the turn-off delay for AVDD (after VCOM). 100 µs step size. 0 ms to 25.5 ms. See Shutdown Timing diagram.                                                                  |

| delay_shutdown_VCOM       | 0x0         | 0x0D         | Program the turn-off delay for VCOM. 100 μs step size. 0 ms to 25.5 ms.                                                                                                            |

| delay_shutdown_VGL        | 0x0         | 0x0E         | Program the turn-off delay for VGL (after VGH). 100 µs step size. 0 ms to 25.5 ms.                                                                                                 |

| delay_shutdown_VGH        | 0x0         | 0x0F         | Program the turn-off delay for VGH. 100 μs step size. 0 ms to 25.5 ms.                                                                                                             |

| dither                    | 0x0         | 0x10         | Bit[1,0] for dither programming (off/5%/10%/15%); Bit4 for VGL/VGH power sequence option.                                                                                          |

| regulator_internal_enable | 0x0         | 0x11         | '1' = Turn all regulators on. '0' = OFF                                                                                                                                            |

| spare1                    | 0x0         | 0x12         | Spare                                                                                                                                                                              |

| spare2                    | 0x0         | 0x13         | Spare                                                                                                                                                                              |

| Fault Status              |             | 0x14-0x1B    |                                                                                                                                                                                    |

| output_status_now         | 0x0         | 0x14         | Present output voltage status of regulators (over 10%, 30%, or 90%)                                                                                                                |

| ilimt_status_now          | 0x0         | 0x15         | Present output current status of regulators (OCP)                                                                                                                                  |

| fault_status_now          | 0x0         | 0x16         | Present fault status (TSD, FSET_short, SW_OVP, SW_OCP, etc.)                                                                                                                       |

| output_status_hold        | 0x0         | 0x17         | Latched output voltage status (over 120% or under 80%)                                                                                                                             |

| ilimt_status_hold         | 0x0         | 0x18         | Latched output current status                                                                                                                                                      |

| fault_status_hold         | 0x0         | 0x19         | Latched fault status                                                                                                                                                               |

| rstatus_hold              | 0x01        | 0x1A         | Retry counter status [bit 4:7], Diagnostic [2,3], Hard_Reset [1], and POR [0].                                                                                                     |

| sstatus_hold              | 0x0         | 0x1B         | OVP/UVP status of regulators during startup                                                                                                                                        |

### DIAGNOSTIC REGISTERS

All faults and critical signals are recorded into log registers. External devices can read these log registers for diagnostic or maintenance purposes.

The A8603 provides two types of diagnostic status registers:

- Registers 0x14-16 (#20-22 in decimal) store the real-time status bits for regulator voltage, current, and fault conditions.

- Registers 0x17-1B (#23-27 in decimal) store the 'latched' status bits for voltage, current, and fault conditions. In case of a fault shutdown, the real-time status bits may be cleared, but the user can read the latched status bits and determine the cause for the shutdown.

## **Real-Time Status Registers**

Registers 0x14 to 0x16 are read-only (refer to Tables 6 - 8).

Table 6: Register 0x14 - Output Voltage Status During Startup/Shutdown

| bit7      | bit6      | bit5       | bit4       | bit3      | bit2      | bit1       | bit0       |

|-----------|-----------|------------|------------|-----------|-----------|------------|------------|

| VGH > 90% | VGL > 90% | VCOM > 90% | AVDD > 90% | VGH > 30% | VGL > 30% | VCOM > 10% | AVDD > 10% |

Each bit is set to '1' when its corresponding regulator voltage is above threshold. They are only useful during startup and shutdown.

#### Table 7: Register 0x15 – Output Current Status During Operation

| bit7 | bit6 | bit5 | bit4 | bit3       | bit2       | bit1        | bit0        |

|------|------|------|------|------------|------------|-------------|-------------|

| -    | -    | -    | -    | VGH ILimit | VGL ILimit | VCOM ILimit | AVDD ILimit |

Each bit is set to '1' when its corresponding regulator is operating at current limit. Note that those bits are ignored during startup phase (where all regulators must work at current limit to charge up output capacitors quickly). During normal operation mode, it is acceptable for any regulator to reach its current limit momentarily. Only if the overcurrent condition persists for 50 ms, then the FAULT pin is pulled down and a RailFault (Reg0x16 bit2) is recorded.

### Table 8: Register 0x16 - Fault Status

| bit7  | bit6     | bit5     | bit4       | bit3   | bit2       | bit1       | bit0 |

|-------|----------|----------|------------|--------|------------|------------|------|

| FAULT | MaxRetry | WatchDog | SW ILimit2 | SW OVP | Rail Fault | FSET fault | TSD  |

Explanation of each bit:

Bit7 = 1 if any Fault has occurred (it is *not* set in case of a POR or Hard-Reset).

Bit6 = 1 if the number of fault retries has reached MaxRetry limit.

Bit5 = 1 if the startup watchdog timer (Reg0x09) has expired before all output regulators can reach 90% target.

Bit4 = 1 if the boost switch current has exceeded its secondary OCP limit (150% of cycle-by-cycle current limit).

Bit3 = 1 if the boost switch voltage has exceeded its OVP threshold.

Bit2 = 1 if any output regulator reached its OCP limit for 50 ms.

Bit1 = 1 if the FSET pin is either open or shorted to GND.

Bit0 = 1 if a thermal shutdown has occurred.

## **Latched Status Registers**

Registers 0x17 to 0x1B hold the status bits after a fault has occurred. Each bit is read-only and can be only cleared by writing a '1' to it. In case of a fault shutdown, the user can read those registers to determine the cause of the shutdown, and then clear them by writing '0xFF' to each register.

#### Table 9: Register 0x17 - Latched Output Over- and Undervoltage Protection Fault

| bit7       | bit6       | bit5        | bit4        | bit3      | bit2      | bit1       | bit0       |

|------------|------------|-------------|-------------|-----------|-----------|------------|------------|

| VGH > 120% | VGL > 120% | VCOM > 120% | AVDD > 120% | VGH < 80% | VGL < 80% | VCOM < 80% | AVDD < 80% |

Each bit is set to '1' when its corresponding regulator has tripped OVP/UVP fault. Note that those bits can only be set after all regulators have finished startup stage and the IC is in normal operation mode.

### Table 10: Register 0x18 - Latched Output Overcurrent Protection Fault

| bit7     | bit6 | bit5 | bit4 | bit3       | bit2       | bit1        | bit0        |

|----------|------|------|------|------------|------------|-------------|-------------|

| Reserved | -    | -    | -    | VGH ILimit | VGL ILimit | VCOM ILimit | AVDD ILimit |

Each bit is set to '1' when its corresponding regulator is operating at current limit during normal operation.

#### Table 11: Register 0x19 - Latched Fault Status

| bit7  | bit6     | bit5     | bit4       | bit3   | bit2       | bit1       | bit0 |

|-------|----------|----------|------------|--------|------------|------------|------|

| FAULT | MaxRetry | Watchdog | SW ILimit2 | SW OVP | Rail Fault | FSET fault | TSD  |

See Register 0x16 for explanation of each bit.

## Table 12: Register 0x1A - Latched Non-Fault Status

| bit7                              | bit6 | bit5 | bit4       | bit3          | bit2       | bit1           | bit0 |

|-----------------------------------|------|------|------------|---------------|------------|----------------|------|

| Current Retry Counter (Read-Only) |      |      | SW ILimit1 | Slow Shutdown | Hard Reset | Power-On Reset |      |

Bit[4..7] = Current Retry Counter (0 to 15)

Bit3 = 1 if boost switch cycle-by-cycle current limit has be reached. This is not a fault condition and IC does not shutdown.

Bit2 = 1 if during shutdown, any regulator failed to decay below 10% (AVDD/VCOM) or 30% (VGL/VGH) before watchdog timer expires. This is not a fault since the IC still shuts down afterward.

Bit1 = 1 if the IC has finished a hardware-initiated shutdown (by EN = L briefly) and all registers are restored to default values.

Bit0 = 1 if the IC has finished a power-on reset and all registers are initialized to their default values.

Note that after a Power-On Reset (or a Hard Reset), the output regulator cannot be enabled until bit0 (or bit1) is cleared. This can be done by writing a '0x03' to Register0x1A.

#### Table 13: Register 0x1B – Latched Over- and Undervoltage Status During Startup

| bit7       | bit6       | bit5        | bit4        | bit3      | bit2      | bit1       | bit0       |

|------------|------------|-------------|-------------|-----------|-----------|------------|------------|

| VGH > 120% | VGL > 120% | VCOM > 120% | AVDD > 120% | VGH < 80% | VGL < 80% | VCOM < 80% | AVDD < 80% |

This is similar to Register 0x17, except it only records OVP/UVP during startup phase. Suppose, under certain unlikely situations, a regulator output rises above 120% or drops below 80% after it reached 90% but before the IC enters normal operation mode, then it will be recorded.

### **DESCRIPTION OF REGULATORS**

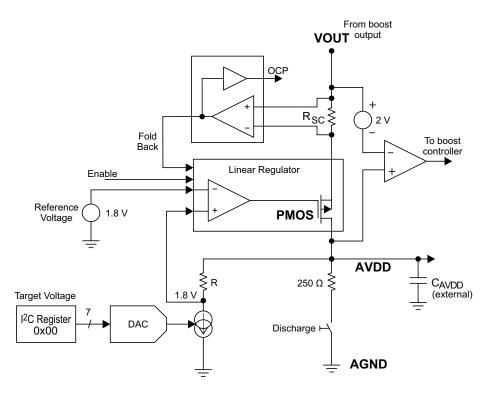

## **AVDD Regulator**

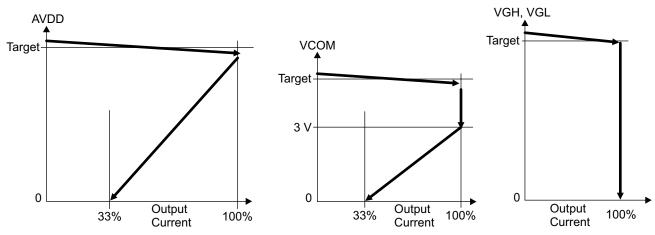

The AVDD output is driven by a linear regulator, which takes its input power from the boost output voltage. The target voltage of AVDD is programmable through Register 0x00 (7 bits). Its range is between 5 V (Register = 0x00) and 15 V (Register = 0x7F) in 127 steps, with step resolution = 78.74 mV. A representative block diagram is shown in Figure 3.

The AVDD circuit monitors the voltage drop across its linear regulator. If this voltage drop is less than the headroom required (approximately 2 V between OUT and AVDD), the monitor circuit sends a control signal to cause the boost voltage to increase. This ensures there is always enough headroom for regulation.

## VCOM Regulator

The VCOM output is also driven by a linear regulator similar to the case of AVDD, except that it takes its input power from the regulated AVDD output voltage. This arrangement gives VCOM exceptional stability over full operating temperature range. The target voltage of VCOM is programmable through Register 0x01-02 (9 bits total). Its range is between 2.5 V (Register=0x0000) and 7.5 V (Register=0x01FF) in 511 steps, with step resolution = 9.785 mV.

In order to ensure there is enough headroom, AVDD must be at least 1.5 V higher than VCOM.

If VCOM is not required, the VCOM pin can be left open, but a small output capacitor (approximately  $0.1~\mu F$ ) must be present to prevent oscillation.

Figure 3: Representative Block Diagram of the AVDD Regulator

## **VGL/VGH Charge Pumps**

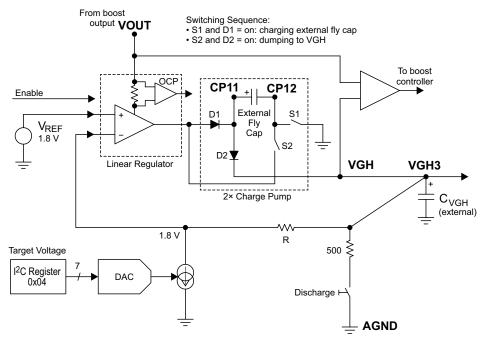

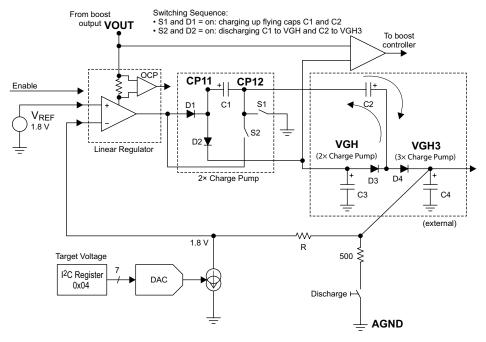

The A8603 uses a 2× charge pump to generate VGH from boost voltage. If necessary, a 3× charge pump can be implemented at the VGH3 pin using external components. See Representative Block Diagrams as shown in Figures 4 and 5. Depending on the

magnitude of VGH, using a 3× charge pump may lower the boost output voltage and hence improve the system efficiency. See Boost Controller section for details.

Figure 4: Representative Block Diagram of the VGH Regulator in 2× Charge Pump Mode

Figure 5: Representative Block Diagram of the VGH Regulator in 3× Charge Pump Mode

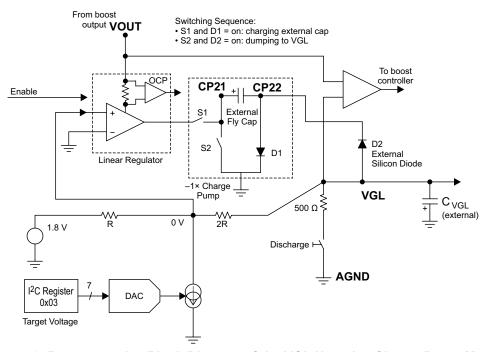

An inverting charge pump is used to generate the negative voltage for VGL. A representative block diagram is shown in Figure 6.

Figure 6: Representative Block Diagram of the VGL Negative Charge Pump Mode

The frequency of the charge pumps is the same as the boost switching frequency (or external SYNC frequency). When an external SYNC signal is used, it is internally converted into a clock signal with the same frequency, but at 50% duty cycle.

Recommended values of the external flying capacitor,  $C_{FLYx}$ , on the  $C_{Pxx}$  pins depends on the switching frequency as shown in the following table; a voltage rating of 25 V is sufficient.

**Table 14: Recommended Flying Capacitor Values**

| Switching Frequency (MHz) | C <sub>FLYx</sub> (μF) |

|---------------------------|------------------------|

| 2                         | 0.1                    |

| 1                         | 0.22                   |

| 0.35                      | 0.47                   |

The value of the flying capacitor can be calculates as follows:

1. The equivalent series resistance of the flying capacitor is:

$$ESR_{FLY2} = 1 / (f_{SW} \times C_{FLY2})$$

(2)

2. Assuming a flying capacitor ripple voltage of 100 mV, and a maximum output current of 20 mA, the series resistance is:

$$R_{FLY2} \le 0.1 \ (V) / 0.02 \ (A) = 5 \ \Omega$$

3. Therefore at an  $f_{SW}$  of 2 MHz, the required capacitance,  $C_{FLY2},$  is 0.1  $\mu F.$

## **Boost Controller**

The A8603 contains an integrated DMOS switch and PWM controller to drive a boost converter. The input voltage,  $V_{\text{IN}}$ , (3.3 V nominal) is boosted to an intermediate voltage,  $V_{\text{OUT}}$ , which is the lowest voltage required to keep all outputs within regula-

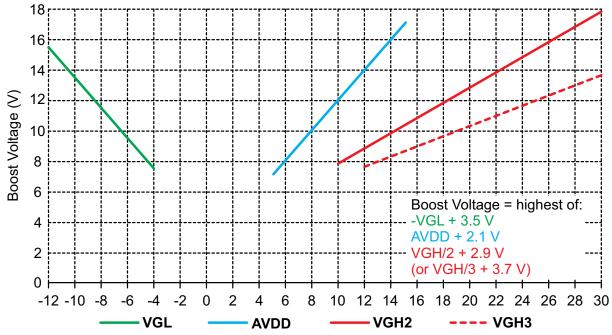

tion. The final output voltage is decided by the regulator, which requires the highest boost voltage. This is illustrated in Figure 7.

Figure 7: Boost Voltage Requirement with Respect to VGL, AVDD and VGH

For example: assume the output requirements for a certain LCD panel are:  $V_{AVDD} = 10 \text{ V}$ ,  $V_{VGH} = 18 \text{ V}$  and  $V_{VGL} = -7 \text{ V}$ , then:

• AVDD (LDO):

$$V_{OUT} \ge V_{AVDD} + 2.1 \ (V) = 12.1 \ V$$

• VGH (2× Charge Pump):

$$V_{OUT} \ge V_{VGH} / 2 + 2.9 (V) = 11.9 V$$

• VGL (Inverted Charge Pump):

$$V_{OUT} \ge -V_{VGL} + 3.5 (V) = 10.5 V$$

In this example, AVDD has the highest requirement, so the boost output voltage will be regulated at a  $V_{OUT} = 12.1~V$  approximately. However, if  $V_{VGH}$  were increased to 24 V, it would require higher voltage, and then the boost converter would increase the boost output voltage to 14.9 V to satisfy the  $2\times$  charge pump. This leads to higher voltage drop across the linear regulator for AVDD, and hence higher power loss. In such case, it

is worthwhile to consider the option of 3× charge pump for VGH.

• VGH (2× Charge Pump):

$$V_{OUT} \ge V_{VGH} / 2 + 2.9 (V) = 14.9 V$$

• VGH (3× Charge Pump):

$$V_{OUT} \ge V_{VGH} / 3 + 3.7 (V) = 11.7 V$$

So by using 3× charge pump for VGH, the boost voltage is reduced to 12.1 V (as dominated by AVDD). This results in lower power loss and hence better system efficiency.

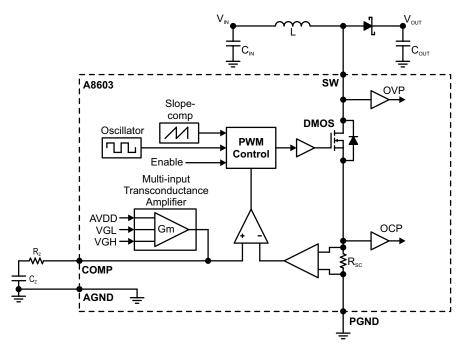

A block diagram of the A8603 boost controller circuit is shown in Figure 8. Typical values for external COMP components are  $R_Z=511~\Omega$  and  $C_Z=0.22~\mu F.$  Note that the boost stage simply provides an intermediate voltage. The actual output voltages (AVDD, VGL, VGH) are controlled by linear regulators and charge pumps, which contain their own internal compensation.

**Figure 8: Boost Controller Circuit**

The boost controller is protected against overvoltage and overcurrent fault conditions.

- The Switch OVP threshold, V<sub>SW(OVP)</sub>, is internally set at approximately 21 V typical. Under normal operating conditions, the boost output voltage should always be lower than 18 V, so only in the event of a fault will SW\_OVP be tripped (for example: boost diode open or VOUT pin open during startup).

- The switch current is protected by a cycle-by-cycle current limit (I<sub>SWILIM</sub>, 2.6 A typical). In the event of a heavy load or during a transient, the SW peak current may reach

- SWILIM level momentarily. In this case, the present on-time is truncated immediately, but no signal is generated on the FAULT pin. The switching will continue with the same period.

- In the event of a catastrophic failure (such as shorted inductor), the SW current may exceed SWILIM2, which is 150% of the SWILIM threshold. In this case, the IC is shut down immediately.

It is important to note that the A8603 cannot protect the input current in case there is a short from boost output to GND. To do so requires the use of an input disconnect switch.

## **Boost Switching Frequency**

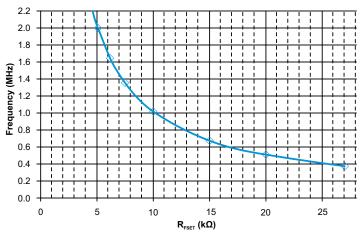

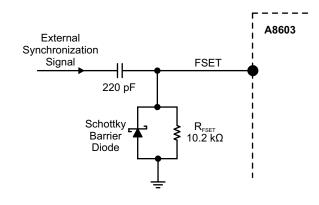

The boost stage switching frequency,  $f_{SW}$ , of the A8603 can be programmed by using an external resistor between the FSET pin to GND, or it can be synchronized to an external clock frequency between 350 kHz and 2.25 MHz.

During startup, the A8603 senses the FSET pin for any external SYNC signal. If periodic logic transitions are detected (Low < 0.4 V or High > 1.5 V), this is evaluated as an external clock signal, and the boost switching frequency is synchronized to it. If no periodic signal is detected, the bias current flowing through FSET\_SYNC pin is used to determine the switching frequency. The bias current is set by an external resistor,  $R_{FSET}$ , on the FSET\_SYNC pin. The relation between  $R_{FSET}$  and switching frequency is given as:

$$R_{FSET} = 10.21 / (f_{SW} - 0.0025)$$

(3)

where  $R_{ESET}$  is in  $k\Omega$  and  $f_{SW}$  is in MHz.

This relationship is charted in Figure 9. For example, to get a switching frequency of 2 MHz requires an  $R_{ESET}$  of 5.11 k $\Omega$ .

Figure 9: Boost Switching Frequency as a Function of FSET Resistance

Suppose the A8603 is started up with a valid external SYNC signal, but the SYNC signal is lost during normal operation. In that case, one of the following happens