SGUS039 - AUGUST 2002

- Controlled Baseline

One Assembly/Test Site, One Fabrication Site

- Enhanced Diminishing Manufacturing Sources (DMS) Support

- Enhanced Product Change Notification

- Qualification Pedigree<sup>†</sup>

- Operating Temperature Ranges:

Military (M) –55°C to 125°C

- High-Performance Floating-Point Digital Signal Processor (DSP):

- SM320LC31-40EP (3.3 V)

50-ns Instruction Cycle Time

220 MOPS, 40 MFLOPS, 20 MIPS

- 32-Bit High-Performance CPU

- 16-/32-Bit Integer and 32-/40-Bit Floating-Point Operations

- 32-Bit Instruction and Data Words, 24-Bit Addresses

- Two 1K Word × 32-Bit Single-Cycle Dual-Access On-Chip RAM Blocks

- Boot-Program Loader

- 64-Word × 32-Bit Instruction Cache

- Eight Extended-Precision Registers

- Two Address Generators With Eight Auxiliary Registers and Two Auxiliary Register Arithmetic Units (ARAUs)

- Two Low-Power Modes

- On-Chip Memory-Mapped Peripherals:

One Serial Port Supporting

- 8-/16-/24-/32-Bit Transfers

- Two 32-Bit Timers

- One-Channel Direct Memory Access (DMA) Coprocessor for Concurrent I/O and CPU Operation

- Fabricated Using Enhanced Performance Implanted CMOS (EPIC<sup>™</sup>) Technology by Texas Instruments (TI)

- Two- and Three-Operand Instructions

- 40/32-Bit Floating-Point/Integer Multiplier and Arithmetic Logic Unit (ALU)

- Parallel ALU and Multiplier Execution in a Single Cycle

- Block-Repeat Capability

- Zero-Overhead Loops With Single-Cycle Branches

- Conditional Calls and Returns

- Interlocked Instructions for Multiprocessing Support

- Bus-Control Registers Configure Strobe-Control Wait-State Generation

- Validated Ada Compiler

- Integer, Floating-Point, and Logical Operations

- 32-Bit Barrel Shifter

- One 32-Bit Data Bus (24-Bit Address)

- Packaging

- 132-Lead Plastic Quad Flatpack (PQ Suffix)

#### description

The SM320LC31-EP digital signal processor (DSP) is a 32-bit, floating-point processor manufactured in 0.6-µm triple-level-metal CMOS technology. The device is part of the SMJ320C3x generation of DSPs from Texas Instruments.

The SM320LC31-EP internal busing and special digital-signal-processing instruction set have the speed and flexibility to execute up to 60 MFLOPS. The SM320LC31-EP optimizes speed by implementing functions in hardware that other processors implement through software or microcode. This hardware-intensive approach provides performance previously unavailable on a single chip.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

<sup>†</sup> Component qualification in accordance with JEDEC and industry standards to ensure reliable operation over an extended temperature range. This includes, but is not limited to, Highly Accelerated Stress Test (HAST) or biased 85/85, temperature cycle, autoclave or unbiased HAST, electromigration, bond intermetallic life, and mold compound life. Such qualification testing should not be viewed as justifying use of this component beyond specified performance and environmental limits.

EPIC is a trademark of Texas Instruments Incorporated. All trademarks are the property of their respective owners

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

1

SGUS039 - AUGUST 2002

#### description (continued)

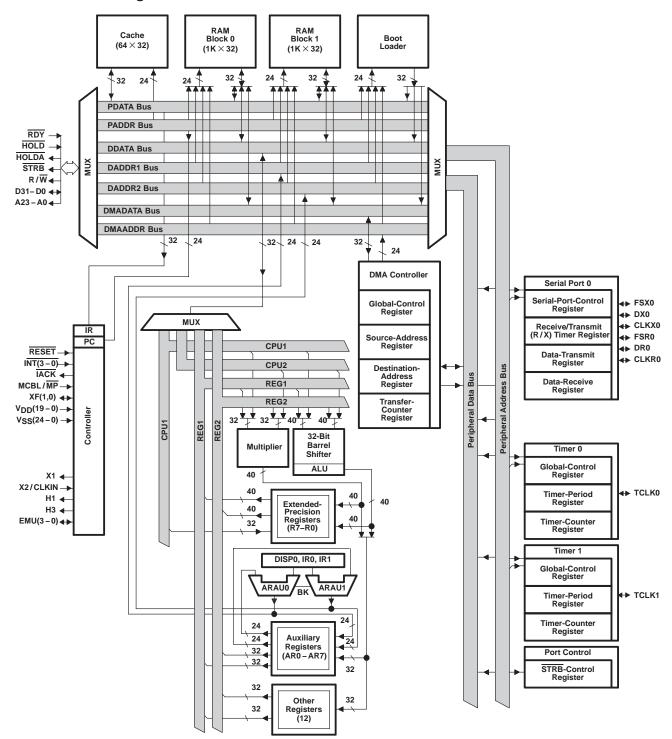

The SM320LC31-EP can perform parallel multiply and ALU operations on integer or floating-point data in a single cycle. Each processor also possesses a general-purpose register file, a program cache, dedicated ARAUs, internal dual-access memories, one DMA channel supporting concurrent I/O, and a short machine-cycle time. High performance and ease of use are results of these features.

General-purpose applications are greatly enhanced by the large address space, multiprocessor interface, internally and externally generated wait states, one external interface port, two timers, one serial port, and multiple-interrupt structure. The SM320LC31-EP supports a wide variety of system applications from host processor to dedicated coprocessor.

High-level-language support is easily implemented through a register-based architecture, large address space, powerful addressing modes, flexible instruction set, and well-supported floating-point arithmetic.

For additional information when designing for cold temperature operation, please see Texas Instruments application report 320C3x, 320C4x and 320MCM42x Power-up Sensitivity at Cold Temperature, literature number SGUA001.

SGUS039 - AUGUST 2002

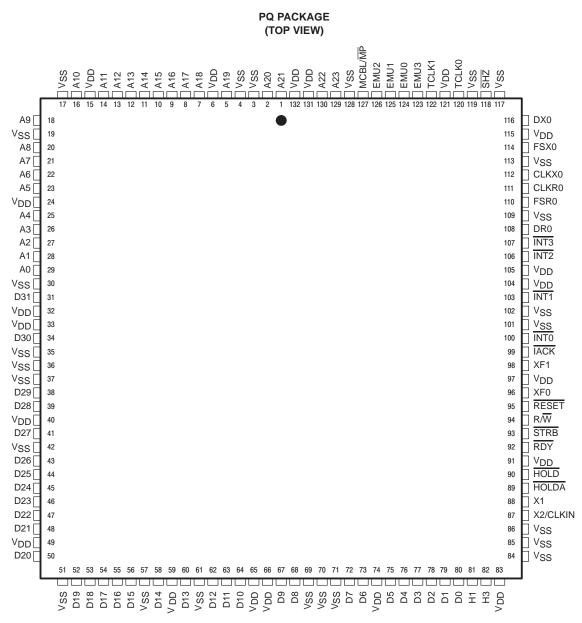

#### SM320LC31-EP pinout (top view)

The SM320LC31-EP device is packaged in a132-pin plastic quad flatpack (PQ Suffix). The full part number is SM320LC31PQM40EP.

SGUS039 - AUGUST 2002

#### Terminal Assignments (PQ Package)

| PI     | N     | PI     | N           | Р      | IN                 | Р      | PIN                 |

|--------|-------|--------|-------------|--------|--------------------|--------|---------------------|

| NUMBER | NAME  | NUMBER | NAME        | NUMBER | NAME               | NUMBER | NAME                |

| 29     | A0    | 64     | D10         | 103    | INT1               | 30     | V <sub>SSL</sub> †  |

| 28     | A1    | 63     | D11         | 106    | INT2               | 35     | V <sub>SSL</sub> †  |

| 27     | A2    | 62     | D12         | 107    | INT3               | 36     | DVSS                |

| 26     | A3    | 60     | D13         | 127    | MCBL/MP            | 37     | IVSS†               |

| 25     | A4    | 58     | D14         | 92     | R/W                | 42     | DVSS                |

| 23     | A5    | 56     | D15         | 95     | RDY                | 51     | CV <sub>SS</sub> †  |

| 22     | A6    | 55     | D16         | 94     | RESET              | 57     | IV <sub>SS</sub> †  |

| 21     | A7    | 54     | D17         | 118    | SHZ                | 61     | DVSS                |

| 20     | A8    | 53     | D18         | 93     | STRB               | 69     | $v_{SSL}^{\dagger}$ |

| 18     | A9    | 52     | D19         | 120    | TCLK0              | 70     | $v_{SSL}^{\dagger}$ |

| 16     | A10   | 50     | D20         |        |                    | 71     | DVSS                |

| 14     | A11   | 48     | D21         |        |                    | 84     | CV <sub>SS</sub> †  |

| 13     | A12   | 47     | D22         | 6      | AV <sub>DD</sub> ‡ | 85     | IV <sub>SS</sub> †  |

| 12     | A13   | 46     | D23         | 15     | AV <sub>DD</sub> ‡ | 86     | DVSS                |

| 11     | A14   | 45     | D24         | 24     | V <sub>DDL</sub>   | 101    | V <sub>SSL</sub> †  |

| 10     | A15   | 44     | D25         | 32     | V <sub>DDL</sub>   | 102    | cv <sub>ss</sub> †  |

| 9      | A16   | 43     | D26         | 33     | dv <sub>dd</sub> ‡ | 109    | IV <sub>SS</sub> †  |

| 8      | A17   | 41     | D27         | 40     | dv <sub>dd</sub> ‡ | 113    | VSUBS <sup>§</sup>  |

| 7      | A18   | 39     | D28         | 49     | dv <sub>dd</sub> ‡ | 117    | DVSS                |

| 5      | A19   | 38     | D29         | 59     | V <sub>DDL</sub>   | 119    | CV <sub>SS</sub> †  |

| 2      | A20   | 34     | D30         | 65     | VDDL               | 128    | X1                  |

| 1      | A21   | 31     | D31         | 66     | dv <sub>dd</sub> ‡ | 88     | X2/CLKIN            |

| 130    | A22   | 108    | DR0         | 74     | dv <sub>dd</sub> ‡ | 87     | XF0                 |

| 129    | A23   | 116    | DX0         | 83     | CV <sub>DD</sub> ‡ | 96     | XF1                 |

| 111    | CLKR0 | 124    | EMU0        | 91     | cv <sub>DD</sub> ‡ | 98     | No Connec           |

| 112    | CLKX0 | 125    | EMU1        | 97     | V <sub>DDL</sub>   |        |                     |

| 80     | D0    | 126    | EMU2        | 104    | V <sub>DDL</sub>   |        |                     |

| 79     | D1    | 123    | EMU3        | 105    | PV <sub>DD</sub> ‡ |        |                     |

| 78     | D2    | 110    | FSR0        | 115    | PV <sub>DD</sub> ‡ |        |                     |

| 77     | D3    | 114    | FSX0        | 121    | V <sub>DDL</sub>   |        |                     |

| 76     | D4    | 81     | HOLD        | 131    | V <sub>DDL</sub>   |        |                     |

| 75     | D5    | 82     | HOLDA       | 132    | V <sub>SSL</sub> † |        |                     |

| 73     | D6    | 90     | H1          | 3      | DVSS               |        |                     |

| 72     | D7    | 89     | H3          | 4      | cvss†              |        |                     |

| 68     | D8    | 99     | IACK        | 17     | DVSS               |        |                     |

| 67     | D9    | 100    | <b>INTO</b> | 19     | cv <sub>ss</sub> † |        |                     |

<sup>†</sup> CV<sub>SS</sub>, V<sub>SSL</sub>, and IV<sub>SS</sub> are on the same plane. <sup>‡</sup> AV<sub>DD</sub>, DV<sub>DD</sub>, CV<sub>DD</sub>, and PV<sub>DD</sub> are on the same plane. § V<sub>SUBS</sub> connects to die metallization. Tie this pin to clean ground.

SGUS039 - AUGUST 2002

#### **Terminal Functions**

| TERMINAL  |                                                                       | TYPET | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                         | со |   | - |

|-----------|-----------------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---|---|

| NAME      | QTY     PRIMARY-BUS INTERFACE       32     I/O/Z     32-bit data port | SIGN/ | AL IS Z                                                                                                                                                                                                                                                                                                                                                                                                             |    |   |   |

|           |                                                                       |       | PRIMARY-BUS INTERFACE                                                                                                                                                                                                                                                                                                                                                                                               |    |   |   |

| D31-D0    | 32                                                                    | I/O/Z | 32-bit data port                                                                                                                                                                                                                                                                                                                                                                                                    | S  | Н | R |

| A23-A0    | 24                                                                    | O/Z   | 24-bit address port                                                                                                                                                                                                                                                                                                                                                                                                 | S  | Н | R |

| R/W       | 1                                                                     | O/Z   | Read/write. $R/\overline{W}$ is high when a read is performed and low when a write is performed over the parallel interface.                                                                                                                                                                                                                                                                                        | S  | Н | R |

| STRB      | 1                                                                     | O/Z   | External-access strobe                                                                                                                                                                                                                                                                                                                                                                                              | S  | Н |   |

| RDY       | 1                                                                     | I     | Ready. RDY indicates that the external device is prepared for a transaction completion.                                                                                                                                                                                                                                                                                                                             |    |   |   |

| HOLD      | 1                                                                     | I     | Hold. When $\overline{\text{HOLD}}$ is a logic low, any ongoing transaction is completed. A23–A0, D31–D0, $\overline{\text{STRB}}$ , and R/W are placed in the high-impedance state and all transactions over the primary-bus interface are held until HOLD becomes a logic high or until the NOHOLD bit of the primary-bus-control register is set.                                                                |    |   |   |

| HOLDA     | 1                                                                     | O/Z   | Hold acknowledge. HOLDA is generated in response to a logic low on HOLD. HOLDA indicates that $A23 - A0$ , $D31 - D0$ , STRB, and $R/W$ are in the high-impedance state and that all transactions over the bus are held. HOLDA is high in response to a logic high of HOLD or the NOHOLD bit of the primary-bus-control register is set.                                                                            | S  |   |   |

|           |                                                                       | -     | CONTROL SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                     |    |   |   |

| RESET     | 1                                                                     | I     | Reset. When RESET is a logic low, the device is in the reset condition. When RESET becomes a logic high, execution begins from the location specified by the reset vector.                                                                                                                                                                                                                                          |    |   |   |

| INT3-INT0 | 4                                                                     | I     | External interrupts                                                                                                                                                                                                                                                                                                                                                                                                 |    |   |   |

| IACK      | 1                                                                     | O/Z   | Interrupt acknowledge. IACK is generated by the IACK instruction. IACK can be used to indicate the beginning or the end of an interrupt-service routine.                                                                                                                                                                                                                                                            | S  |   |   |

| MCBL/MP   | 1                                                                     | I     | Microcomputer boot-loader/microprocessor mode-select                                                                                                                                                                                                                                                                                                                                                                |    |   |   |

| SHZ       | 1                                                                     | I     | Shutdown high impedance. When active, $\overline{SHZ}$ shuts down the device and places all pins in the high-impedance state. $\overline{SHZ}$ is used for board-level testing to ensure that no dual-drive conditions occur. <b>CAUTION:</b> A low on $\overline{SHZ}$ corrupts the device memory and register contents. Reset the device with $\overline{SHZ}$ high to restore it to a known operating condition. |    |   |   |

| XF1, XF0  | 2                                                                     | I/O/Z | External flags. XF1 and XF0 are used as general-purpose I/Os or to support interlocked processor instruction.                                                                                                                                                                                                                                                                                                       | S  |   | R |

|           |                                                                       |       | SERIAL PORT 0 SIGNALS                                                                                                                                                                                                                                                                                                                                                                                               |    |   |   |

| CLKR0     | 1                                                                     | I/O/Z | Serial port 0 receive clock. CLKR0 is the serial shift clock for the serial port 0 receiver.                                                                                                                                                                                                                                                                                                                        | S  |   | R |

| CLKX0     | 1                                                                     | I/O/Z | Serial port 0 transmit clock. CLKX0 is the serial shift clock for the serial port 0 transmitter.                                                                                                                                                                                                                                                                                                                    | S  |   | R |

| DR0       | 1                                                                     | I/O/Z | Data-receive. Serial port 0 receives serial data on DR0.                                                                                                                                                                                                                                                                                                                                                            | S  |   | R |

| DX0       | 1                                                                     | I/O/Z | Data-transmit output. Serial port 0 transmits serial data on DX0.                                                                                                                                                                                                                                                                                                                                                   | S  |   | R |

| FSR0      | 1                                                                     | I/O/Z | Frame-synchronization pulse for receive. The FSR0 pulse initiates the data-receive process using DR0.                                                                                                                                                                                                                                                                                                               | S  |   | R |

| FSX0      | 1                                                                     | I/O/Z | Frame-synchronization pulse for transmit. The FSX0 pulse initiates the data-transmit process using DX0.                                                                                                                                                                                                                                                                                                             | S  |   | R |

|           |                                                                       |       | TIMER SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                       |    |   |   |

| TCLK0     | 1                                                                     | I/O/Z | Timer clock 0. As an input, TCLK0 is used by timer 0 to count external pulses. As an output, TCLK0 outputs pulses generated by timer 0.                                                                                                                                                                                                                                                                             | S  |   |   |

| TCLK1     | 1                                                                     | I/O/Z | Timer clock 1. As an input, TCLK0 is used by timer 1 to count external pulses. As an output, TCLK1 outputs pulses generated by timer 1.                                                                                                                                                                                                                                                                             | S  |   |   |

$^{\dagger}$ I = input, O = output, Z = high-impedance state  $^{\ddagger}$ S = SHZ active, H = HOLD active, R = RESET active

SGUS039 - AUGUST 2002

## **Terminal Functions (Continued)**

| TERMINAL<br>NAME QTY |    | TYPET | DESCRIPTION                                                                                                    | CONDITIONS<br>WHEN |

|----------------------|----|-------|----------------------------------------------------------------------------------------------------------------|--------------------|

|                      |    | ITFE  | DESCRIPTION                                                                                                    | SIGNAL IS Z TYPE   |

|                      |    | •     | SUPPLY AND OSCILLATOR SIGNALS                                                                                  |                    |

| H1                   | 1  | O/Z   | External H1 clock. H1 has a period equal to twice CLKIN.                                                       | S                  |

| H3                   | 1  | O/Z   | External H3 clock. H3 has a period equal to twice CLKIN.                                                       | S                  |

| V <sub>DD</sub>      | 20 | I     | 5-V supply for C31 devices and 3.3-V supply for LC31 devices. All must be connected to a common supply plane.§ |                    |

| V <sub>SS</sub>      | 25 | I     | Ground. All grounds must be connected to a common ground plane.                                                |                    |

| X1                   | 1  | 0     | Output from the internal-crystal oscillator. If a crystal is not used, X1 should be left unconnected.          |                    |

| X2/CLKIN             | 1  | I     | Internal-oscillator input from a crystal or a clock                                                            |                    |

|                      |    | -     | RESERVED                                                                                                       |                    |

| EMU2-EMU0            | 3  | I     | Reserved for emulation. Use pullup resistors to V <sub>DD</sub>                                                |                    |

| EMU3                 | 1  | O/Z   | Reserved for emulation                                                                                         | S                  |

<sup>†</sup>I = input, O = output, Z = high-impedance state <sup>‡</sup>S = SHZ active, H = HOLD active, R = RESET active

$\$  Recommended decoupling capacitor value is 0.1  $\mu F.$

$\P$  Follow the connections specified for the reserved pins. Use 18-k $\Omega$ -22-k $\Omega$  pullup resistors for best results. All V<sub>DD</sub> supply pins must be connected to a common supply plane, and all ground pins must be connected to a common ground plane.

SGUS039 - AUGUST 2002

#### functional block diagram

SGUS039 - AUGUST 2002

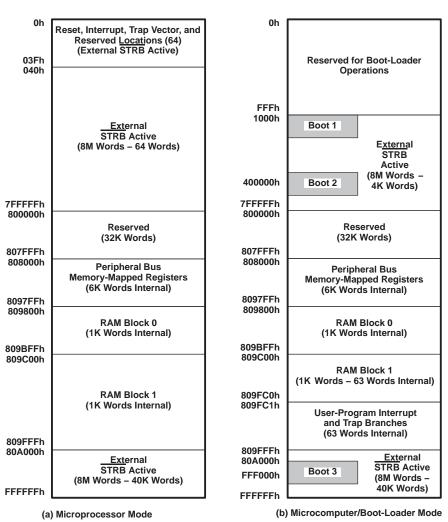

#### memory map<sup>†</sup>

<sup>†</sup> Figure 1 depicts the memory map for the SMJ320C31. See the *TMS320C3x Users Guide* (literature number SPRU031) for a detailed description of this memory mapping.

Figure 1. SM320C31-EP Memory Map

SGUS039 - AUGUST 2002

#### 00h 809FC1h Reset INT0 01h INT0 809FC2h INT1 INT1 02h 809FC3h INT2 INT2 03h 809FC4h INT3 04h INT3 809FC5h XINT0 05h **XINTO** 809FC6h **RINT0** 06h **RINT0** 07h 809FC7h Reserved Reserved 08h 809FC8h 09h TINT0 809FC9h TINT0 0Ah 809FCAh TINT1 TINT1 0Bh 809FCBh DINT DINT 0Ch 809FCCh Reserved Reserved 1Fh 809FDFh 809FE0h 20h TRAP 0 TRAP 0 • ۲ 3Bh TRAP 27 809FFBh TRAP 27 3Ch 809FFCh Reserved Reserved 3Fh 809FFFh (a) Microprocessor Mode (b) Microcomputer/Boot-Loader Mode

memory map (continued)

Figure 2. Reset, Interrupt, and Trap Vector/Branches Memory-Map Locations

SGUS039 - AUGUST 2002

#### memory map (continued)

| 808000h | DMA Global Control               |

|---------|----------------------------------|

| 808004h | DMA Source Address               |

| 808006h | DMA Destination Address          |

| 808008h | DMA Transfer Counter             |

| 808020h | Timer 0 Global Control           |

| 808024h | Timer 0 Counter                  |

| 808028h | Timer 0 Period Register          |

| 808030h | Timer 1 Global Control           |

| 808034h | Timer 1 Counter                  |

| 808038h | Timer 1 Period Register          |

| 808040h | Serial Global Control            |

| 808042h | FSX/DX/CLKX Serial Port Control  |

| 808043h | FSR/DR/CLKR Serial Port Control  |

| 808044h | Serial R/X Timer Control         |

| 808045h | Serial R/X Timer Counter         |

| 808046h | Serial R/X Timer Period Register |

| 808048h | Data-Transmit                    |

| 80804Ch | Data-Receive                     |

| 808064h | Primary-Bus Control              |

|         |                                  |

<sup>†</sup>Shading denotes reserved address locations

Figure 3. Peripheral Bus Memory-Mapped Registers<sup>†</sup>

SGUS039 - AUGUST 2002

#### absolute maximum ratings over specified temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage, V <sub>DD</sub> (see Note 1)                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input voltage, V <sub>I</sub>                                                                                                                              |

| Output voltage, V_O $\ldots \ldots \ldots$ |

| Continuous power dissipation (worst case) (see Note 2) 850 mW                                                                                              |

| Operating case temperature, T <sub>C</sub>                                                                                                                 |

| Storage temperature, T <sub>stg</sub>                                                                                                                      |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values are with respect to V<sub>SS</sub>.

Actual operating power is less. This value was obtained under specially produced worst-case test conditions for the TMS320C31-33 and the TMS320LC31-40, which are not sustained during normal device operation. These conditions consist of continuous parallel writes of a checkerboard pattern to both primary and extension buses at the maximum rate possible. See normal (I<sub>CC</sub>) current specification in the electrical characteristics table and also read *Calculation of TMS320C30 Power Dissipation Application Report* (literature number SPRA020).

#### recommended operating conditions (see Note 3)

|                 |                                          | MIN    | NOM | MAX                    | UNIT |

|-----------------|------------------------------------------|--------|-----|------------------------|------|

| V <sub>DD</sub> | Supply voltage (DV <sub>DD</sub> , etc.) | 3.13   | 3.3 | 3.47                   | V    |

| VSS             | Supply voltage (CV <sub>SS</sub> , etc.) |        | 0   |                        | V    |

|                 | High-level input voltage (except RESET)  | 1.8    |     | V <sub>DD</sub> + 0.3* | V    |

| VIH             | High-level input voltage (RESET)         | 2.2    |     | V <sub>DD</sub> + 0.3* | V    |

| VIL             | Low-level input voltage                  | - 0.3* |     | 0.6                    | V    |

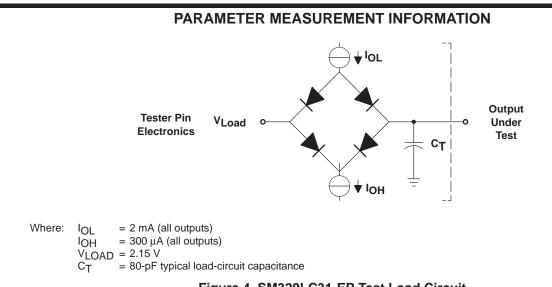

| IOH             | High-level output current                |        |     | - 300                  | μΑ   |

| IOL             | Low-level output current                 |        |     | 2                      | mA   |

| ТС              | Operating case temperature               | -55    |     | 125                    | °C   |

| VTH             | High-level input voltage for CLKIN       | 2.5    |     | V <sub>DD</sub> + 0.3* | V    |

\* This parameter is not production tested.

NOTE 3: All voltage values are with respect to V<sub>SS</sub>. All input and output voltage levels are TTL-compatible. CLKIN can be driven by a CMOS clock.

SGUS039 - AUGUST 2002

#### electrical characteristics over recommended ranges of supply voltage (unless otherwise noted) (see Note 3)<sup>†</sup>

|                 | PARAMETER                            | TEST CONDITIONS                                                                                                | MIN     | TYP‡ | MAX  | UNIT |

|-----------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------|---------|------|------|------|

| Vон             | High-level output voltage            | $V_{DD} = MIN, I_{OH} = MAX$                                                                                   | 2       |      |      | V    |

| VOL             | Low-level output voltage             | $V_{DD} = MIN, I_{OH} = MAX$                                                                                   |         |      | 0.4  | V    |

| ΙZ              | High-impedance current               | V <sub>DD</sub> = MAX                                                                                          | - 20    |      | + 20 | μA   |

| II .            | Input current                        | $V_{I} = V_{SS}$ to $V_{DD}$                                                                                   | - 10    |      | + 10 | μA   |

| I <sub>IP</sub> | Input current (with internal pullup) | Inputs with internal pullups§                                                                                  | - 600   |      | 10   | μΑ   |

| ICC             | Supply current¶#                     | $\begin{array}{l} T_{A}=25^{\circ}C,\\ V_{DD}=MAX \end{array} \hspace{1.5cm} f_{X}=40 \text{ MHz} \end{array}$ |         | 150  | 300  | mA   |

| IDD             | Supply current                       | Standby, IDLE2, Clocks sł                                                                                      | hut off | 20   |      | μA   |

| ~               |                                      | All inputs except CLKIN                                                                                        |         |      | 15*  | _    |

| Ci              | Input capacitance                    | CLKIN                                                                                                          |         |      | 25   | pF   |

| Co              | Output capacitance                   |                                                                                                                |         |      | 20*  | рF   |

<sup>†</sup> All input and output voltage levels are TTL compatible.

<sup>‡</sup> For LC31, all typical values are at  $V_{DD} = 3.3 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ . § Pins with internal pullup devices: INT3–INT0, MCBL/MP.

I Actual operating current is less than this maximum value. This value was obtained under specially produced worst-case test conditions, which are not sustained during normal device operation. These conditions consist of continuous parallel writes of a checkerboard pattern to both primary and expansion buses at the maximum rate possible. See Calculation of TMS320C30 Power Dissipation Application Report (literature number SPRA020).

$^{\#}$  f<sub>x</sub> is the input clock frequency.

\* This parameter is not production tested.

NOTE 3: All voltage values are with respect to VSS. All input and output voltage levels are TTL-compatible. CLKIN can be driven by a CMOS clock.

Figure 4. SM320LC31-EP Test Load Circuit

SGUS039 - AUGUST 2002

### PARAMETER MEASUREMENT INFORMATION

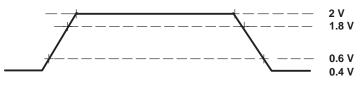

#### signal transition levels for LC31 (see Figure 5 and Figure 6)

Outputs are driven to a minimum logic-high level of 2 V and to a maximum logic-low level of 0.4 V. Output transition times are specified as follows:

- For a high-to-low transition on an output signal, the level at which the output is said to be no longer high is 2 V and the level at which the output is said to be low is 1 V.

- For a low-to-high transition, the level at which the output is said to be no longer low is 1 V and the level at which the output is said to be high is 2 V.

Figure 5. LC31 Output Levels

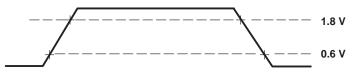

Transition times for inputs are specified as follows:

- For a high-to-low transition on an input signal, the level at which the input is said to be no longer high is 1.8 V and the level at which the input is said to be low is 0.6 V.

- For a low-to-high transition on an input signal, the level at which the input is said to be no longer low is 0.6 V and the level at which the input is said to be high is 1.8 V.

Figure 6. LC31 Input Levels

SGUS039 - AUGUST 2002

### PARAMETER MEASUREMENT INFORMATION

#### timing parameter symbology

Timing parameter symbols used herein were created in accordance with JEDEC Standard 100-A. In order to shorten the symbols, some of the pin names and other related terminology have been abbreviated as follows, unless otherwise noted:

| А       | A23-A0                                       | Н     | H1 and H3                          |

|---------|----------------------------------------------|-------|------------------------------------|

| ASYNCH  | Asynchronous reset signals                   | HOLD  | HOLD                               |

| С       | CLKX0                                        | HOLDA | HOLDA                              |

| CI      | CLKIN                                        | IACK  | IACK                               |

| CLKR    | CLKR0                                        | INT   | INT3-INT0                          |

| CONTROL | Control signals                              | RDY   | RDY                                |

| D       | D31-D0                                       | RW    | R/W                                |

| DR      | DR                                           | RESET | RESET                              |

| DX      | DX                                           | S     | STRB                               |

| FS      | FSX/R                                        | SCK   | CLKX/R                             |

| FSX     | FSX0                                         | SHZ   | SHZ                                |

| FSR     | FSR0                                         | TCLK  | TCLK0, TCLK1, or TCLKx             |

| GPI     | General-purpose input                        | XF    | XF0, XF1, or XFx                   |

| GPIO    | General-purpose input/output; peripheral pin | XFIO  | XFx switching from input to output |

| GPO     | General-purpose output                       |       |                                    |

|         |                                              |       |                                    |

## timing

Timing specifications apply to the SM320LC31-EP.

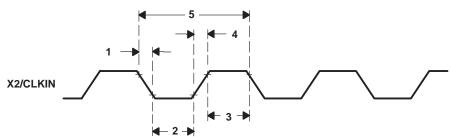

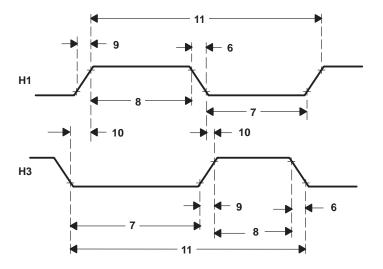

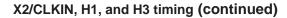

#### X2/CLKIN, H1, and H3 timing

The following table defines the timing parameters for the X2/CLKIN, H1, and H3 interface signals.

#### timing parameters for X2/CLKIN, H1, H3 (see Figure 7, Figure 8, and Figure 9)

| NO. |                       |                                                              | MIN              | MAX | UNIT |

|-----|-----------------------|--------------------------------------------------------------|------------------|-----|------|

| 1   | <sup>t</sup> f(CI)    | Fall time, CLKIN                                             |                  | 5*  | ns   |

| 2   | <sup>t</sup> w(CIL)   | Pulse duration, CLKIN low t <sub>c(CI)</sub> = min           | 9                |     | ns   |

| 3   | <sup>t</sup> w(CIH)   | Pulse duration, CLKIN high t <sub>C(CI)</sub> = min          | 9                |     | ns   |

| 4   | <sup>t</sup> r(CI)    | Rise time, CLKIN                                             |                  | 5*  | ns   |

| 5   | <sup>t</sup> c(CI)    | Cycle time, CLKIN                                            | 25               | 303 | ns   |

| 6   | <sup>t</sup> f(H)     | Fall time, H1 and H3                                         |                  | 3   | ns   |

| 7   | <sup>t</sup> w(HL)    | Pulse duration, H1 and H3 low                                | P-5†             |     | ns   |

| 8   | <sup>t</sup> w(HH)    | Pulse duration, H1 and H3 high                               | P-6 <sup>†</sup> |     | ns   |

| 9   | <sup>t</sup> r(H)     | Rise time, H1 and H3                                         |                  | 3   | ns   |

| 10  | <sup>t</sup> d(HL-HH) | Delay time. from H1 low to H3 high or from H3 low to H1 high | 0                | 4   | ns   |

| 11  | <sup>t</sup> c(H)     | Cycle time, H1 and H3                                        | 50               | 606 | ns   |

<sup>†</sup>  $P = t_{C(CI)}$ \* This parameter is not production tested.

#### Figure 7. Timing for X2/CLKIN

Figure 8. Timing for H1 and H3

SGUS039 - AUGUST 2002

Figure 9. SM320LC31-EP CLKIN to H1/H3 as a Function of Temperature (Typical)

SGUS039 - AUGUST 2002

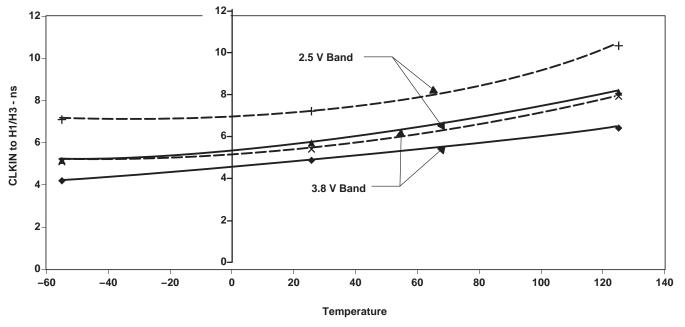

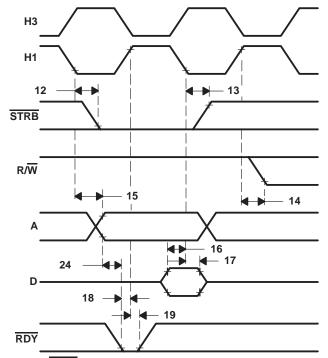

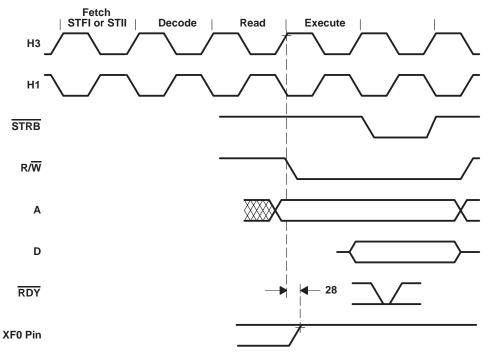

#### memory read/write timing

The following table defines memory read/write timing parameters for STRB.

#### timing parameters for memory (STRB = 0) read/write (see Figure 10 and Figure 11)<sup>†</sup> NO. MIN MAX UNIT 12 Delay time, H1 low to STRB low 0\* 6 ns td(H1L-SL) Delay time, H1 low to STRB high 13 <sup>t</sup>d(H1L-SH) 0\* 6 ns Delay time, H1 high to R/W low (read) 14 0\* 9 td(H1H-RWL)R ns 15 Delay time, H1 low to A valid 0\* 10 ns <sup>t</sup>d(H1L-A) 14 16 tsu(D-H1L)R Setup time, D before H1 low (read) ns 17 Hold time, D after H1 low (read) 0 <sup>t</sup>h(H1L-D)R ns Setup time, RDY before H1 high 8 18 tsu(RDY-H1H) ns 19 Hold time, RDY after H1 high 0 ns <sup>t</sup>h(H1H-RDY) Delay time, H1 high to R/W high (write) 20 9 td(H1H-RWH)W ns 21 Valid time, D after H1 low (write) 17 tv(H1L-D)W ns Hold time, D after H1 high (write) 22 0 <sup>t</sup>h(H1H-D)W ns Delay time, H1 high to A valid on back-to-back write cycles (write) 23 15 td(H1H-A)W ns Delay time, RDY from A valid 24 7\* ns td(A-RDY)

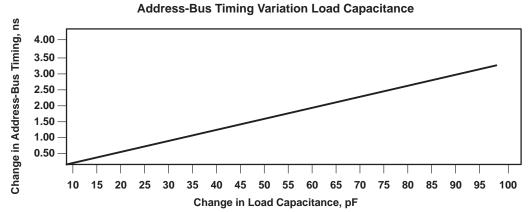

<sup>†</sup> See Figure 12 for address bus timing variation with load capacitance greater than typical load-circuit capacitance (C<sub>T</sub> = 80 pF).

\* This parameter is not production tested.

NOTE A: STRB remains low during back-to-back read operations.

SGUS039 - AUGUST 2002

#### memory read/write timing (continued)

NOTE A: 30 pF/ns slope

SGUS039 - AUGUST 2002

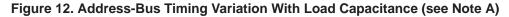

#### XF0 and XF1 timing when executing LDFI or LDII

The following table defines the timing parameters for XF0 and XF1 during execution of LDFI or LDII.

#### timing for XF0 and XF1 when executing LDFI or LDII (see Figure 13)

| NO. |                                                        | MIN | MAX | UNIT |

|-----|--------------------------------------------------------|-----|-----|------|

| 25  | td(H3H-XF0L) Delay time, H3 high to XF0 low            |     | 13  | ns   |

| 26  | t <sub>su(XF1-H1L)</sub> Setup time, XF1 before H1 low | 10  |     | ns   |

| 27  | th(H1L-XF1) Hold time, XF1 after H1 low                | 0   |     | ns   |

SGUS039 - AUGUST 2002

#### XF0 timing when executing STFI and STII<sup>†</sup>

The following table defines the timing parameters for the XF0 pin during execution of STFI or STII.

#### timing for XF0 when executing STFI or STII (see Figure 14)

| NO. |                                              | MIN | MAX | UNIT |

|-----|----------------------------------------------|-----|-----|------|

| 28  | td(H3H-XF0H) Delay time, H3 high to XF0 high |     | 13  | ns   |

<sup>†</sup> XF0 is always set high at the beginning of the execute phase of the interlock-store instruction. When no pipeline conflicts occur, the address of the store is also driven at the beginning of the execute phase of the interlock-store instruction. However, if a pipeline conflict prevents the store from executing, the address of the store will not be driven until the store can execute.

Figure 14. Timing for XF0 When Executing an STFI or STII

SGUS039 - AUGUST 2002

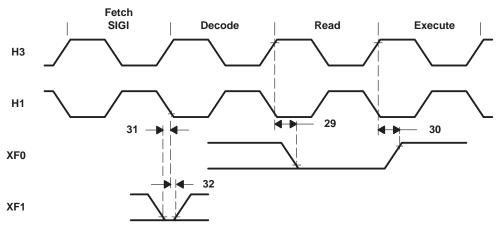

#### XF0 and XF1 timing when executing SIGI

The following table defines the timing parameters for the XF0 and XF1 pins during execution of SIGI.

## timing for XF0 and XF1 when executing SIGI (see Figure 15)

| NO. |                                                          | MIN MAX | UNIT |

|-----|----------------------------------------------------------|---------|------|

| 29  | t <sub>d</sub> (H3H-XF0L) Delay time, H3 high to XF0 low | 13      | ns   |

| 30  | td(H3H-XF0H) Delay time, H3 high to XF0 high             | 13      | ns   |

| 31  | t <sub>su(XF1-H1L)</sub> Setup time, XF1 before H1 low   | 10      | ns   |

| 32  | t <sub>h(H1L-XF1)</sub> Hold time, XF1 after H1 low      | 0       | ns   |

Figure 15. Timing for XF0 and XF1 When Executing SIGI

SGUS039 - AUGUST 2002

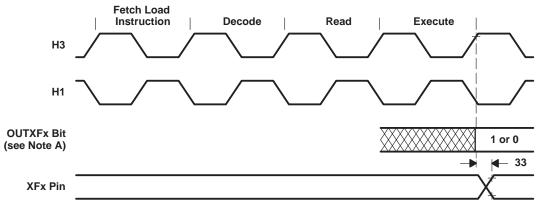

#### loading when XF is configured as an output

The following table defines the timing parameter for loading the XF register when the XFx pin is configured as an output.

#### timing for loading the XF register when configured as an output pin (see Figure 16)

| NO. |                        |                            | MIN | MAX | UNIT |

|-----|------------------------|----------------------------|-----|-----|------|

| 33  | t <sub>v(H3H-XF)</sub> | Valid time, H3 high to XFx |     | 13  | ns   |

NOTE A: OUTXFx represents either bit 2 or 6 of the IOF register.

#### Figure 16. Timing for Loading XF Register When Configured as an Output Pin

SGUS039 - AUGUST 2002

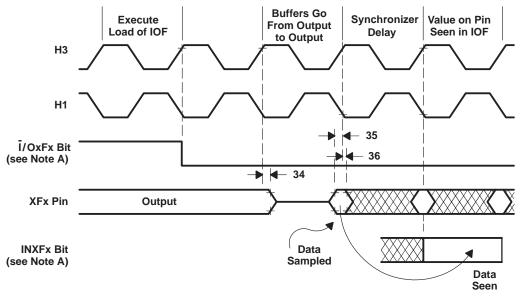

#### changing XFx from an output to an input

The following table defines the timing parameters for changing the XFx pin from an output pin to an input pin.

#### timing of XFx changing from output to input mode (see Figure 17)

| NO. |                                                       | MIN | MAX | UNIT |

|-----|-------------------------------------------------------|-----|-----|------|

| 34  | th(H3H-XF) Hold time, XFx after H3 high               |     | 13* | ns   |

| 35  | t <sub>su(XF-H1L)</sub> Setup time, XFx before H1 low | 10  |     | ns   |

| 36  | t <sub>h(H1L-XF)</sub> Hold time, XFx after H1 low    | 0   |     | ns   |

\* This parameter is not production tested.

NOTE A: I/OxFx represents either bit 1 or bit 5 of the IOF register, and INXFx represents either bit 3 or bit 7 of the IOF register.

Figure 17. Timing for Change of XFx From Output to Input Mode

SGUS039 - AUGUST 2002

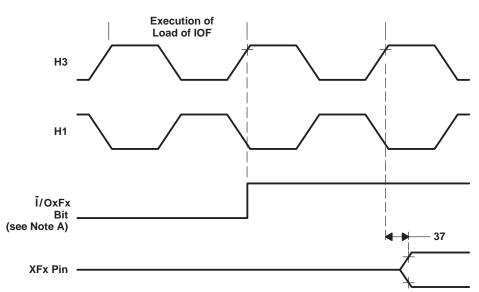

#### changing XFx from an input to an output

The following table defines the timing parameter for changing the XFx pin from an input pin to an output pin.

#### timing for XFx changing from input to output mode (see Figure 18)

| NO. |                          |                                                           | MIN | MAX | UNIT |

|-----|--------------------------|-----------------------------------------------------------|-----|-----|------|

| 37  | <sup>t</sup> d(H3H-XFIO) | Delay time, H3 high to XFx switching from input to output |     | 17  | ns   |

NOTE A: I/OxFx represents either bit 1 or bit 5 of the IOF register.

#### Figure 18. Timing for Change of XFx From Input to Output Mode

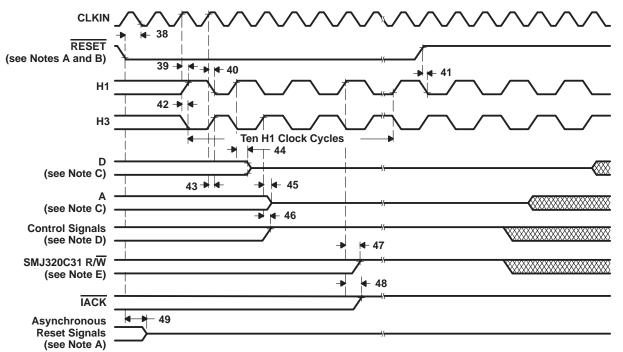

#### reset timing

RESET is an asynchronous input that can be asserted at any time during a clock cycle. If the specified timings are met, the exact sequence shown in Figure 19 occurs; otherwise, an additional delay of one clock cycle is possible.

The asynchronous reset signals include XF0/1, CLKX0, DX0, FSX0, CLKR0, DR0, FSR0, and TCLK0/1.

Resetting the device initializes the primary- and expansion-bus control registers to seven software wait states and therefore results in slow external accesses until these registers are initialized.

HOLD is an asynchronous input and can be asserted during reset.

SGUS039 - AUGUST 2002

| NO. |                                 |                                                                                 | MIN | MAX | UNIT |

|-----|---------------------------------|---------------------------------------------------------------------------------|-----|-----|------|

| 38  | <sup>t</sup> su(RESET-CIL)      | Setup time, RESET before CLKIN low                                              | 10  | P†* | ns   |

| 39  | <sup>t</sup> d(CLKINH-H1H)      | Delay time, CLKIN high to H1 high (see Note 4)                                  | 2   | 14  | ns   |

| 40  | <sup>t</sup> d(CLKINH-H1L)      | Delay time, CLKIN high to H1 low (see Note 4)                                   | 2   | 14  | ns   |

| 41  | <sup>t</sup> su(RESETH-H1L)     | Setup time, RESET high before H1 low and after ten H1 clock cycles              | 9   |     | ns   |

| 42  | td(CLKINH-H3L)                  | Delay time, CLKIN high to H3 low (see Note 4)                                   | 2   | 14  | ns   |

| 43  | <sup>t</sup> d(CLKINH-H3H)      | Delay time, CLKIN high to H3 high (see Note 4)                                  | 2   | 14  | ns   |

| 44  | <sup>t</sup> dis(H1H-DZ)        | Disable time, H1 high to D (high impedance)                                     |     | 13* | ns   |

| 45  | <sup>t</sup> dis(H3H-AZ)        | Disable time, H3 high to A (high impedance)                                     |     | 9*  | ns   |

| 46  | td(H3H-CONTROLH)                | Delay time, H3 high to control signals high                                     |     | 9*  | ns   |

| 47  | <sup>t</sup> d(H1H-RWH)         | Delay time, H1 high to $R/\overline{W}$ high                                    |     | 9*  | ns   |

| 48  | <sup>t</sup> d(H1H-IACKH)       | Delay time, H1 high to IACK high                                                |     | 9*  | ns   |

| 49  | <sup>t</sup> dis(RESETL-ASYNCH) | Disable time, RESET low to asynchronous reset signals disabled (high impedance) |     | 21* | ns   |

### **RESET** timing (see Figure 19)

$\overline{\dagger} P = t_{C(CI)}$

\* This parameter is not production tested.

NOTE 4: See Figure 9 for typical temperature dependence.

- NOTES: A. Asynchronous reset signals include XF0/1, CLKX0, DX0, FSX0, CLKR0, DR0, FSR0, and TCLK0/1.

- B. RESET is an asynchronous input and can be asserted at any point during a clock cycle. If the specified timings are met, the exact sequence shown occurs; otherwise, an additional delay of one clock cycle is possible.

- C. In microprocessor mode, the reset vector is fetched twice, with seven software wait states each time. In microcomputer mode, the reset vector is fetched twice, with no software wait states.

D. Control signals include STRB.

E. The R/ $\overline{W}$  outputs are placed in a high-impedance state during reset and can be provided with a resistive pullup, nominally 18–22 k $\Omega$ , if undesirable spurious writes are caused when these outputs go low.

Figure 19. Timing for RESET

SGUS039 - AUGUST 2002

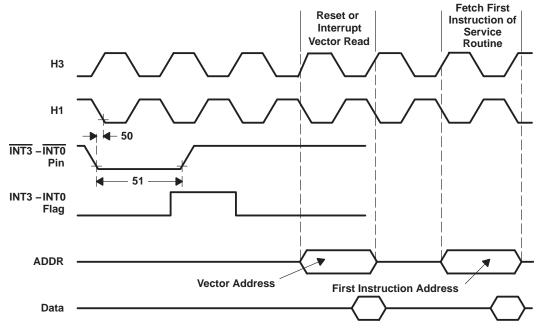

#### interrupt response timing

The following table defines the timing parameters for the INT signals.

### timing for INT3-INT0 response (see Figure 20)

| NO. |                          |                                                        | MIN | MAX  | UNIT |

|-----|--------------------------|--------------------------------------------------------|-----|------|------|

| 50  | <sup>t</sup> su(INT-H1L) | Setup time, INT3-INT0 before H1 low                    | 15  |      | ns   |

| 51  | <sup>t</sup> w(INT)      | Pulse duration, interrupt to ensure only one interrupt | Р   | 2P†* | ns   |

$^{\dagger}P = t_{C(H)}$

\* This parameter is not production tested.

The interrupt (INT) pins are asynchronous inputs that can be asserted at any time during a clock cycle. The SM320LC31-EP interrupts are level-sensitive, not edge-sensitive. Interrupts are detected on the falling edge of H1. Therefore, interrupts must be set up and held to the falling edge of H1 for proper detection. The CPU and DMA respond to detected interrupts on instruction-fetch boundaries only.

For the processor to recognize only one interrupt on a given input, an interrupt pulse must be set up and held to:

- A minimum of one H1 falling edge

- No more than two H1 falling edges

The SM320LC31-EP can accept an interrupt from the same source every two H1 clock cycles.

If the specified timings are met, the exact sequence shown in Figure 20 occurs; otherwise, an additional delay of one clock cycle is possible.

Figure 20. Timing for INT3–INT0 Response

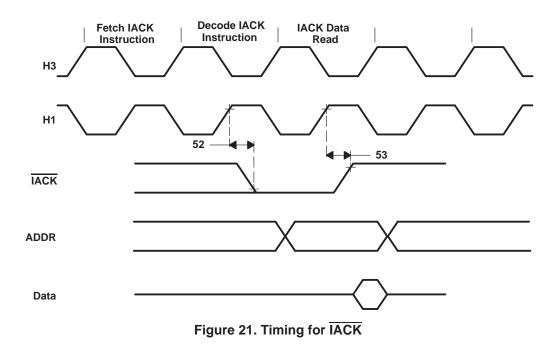

#### interrupt-acknowledge timing

The IACK output goes active on the first half-cycle (HI rising) of the decode phase of the IACK instruction and goes inactive at the first half-cycle (HI rising) of the read phase of the IACK instruction.

timing for IACK (see Note 5 and Figure 21)

| NO. |                                                            | MIN | MAX | UNIT |

|-----|------------------------------------------------------------|-----|-----|------|

| 52  | t <sub>d</sub> (H1H-IACKL) Delay time, H1 high to IACK low |     | 9   | ns   |

| 53  | td(H1H-IACKH) Delay time, H1 high to IACK high             |     | 9   | ns   |

NOTE 5: IACK goes active on the first half-cycle (H1 rising) of the decode phase of the IACK instruction and goes inactive at the first half-cycle (H1 rising) of the read phase of the IACK instruction. Because of pipeline conflicts, IACK remains low for one cycle even if the decode phase of the IACK instruction is extended.

SGUS039 - AUGUST 2002

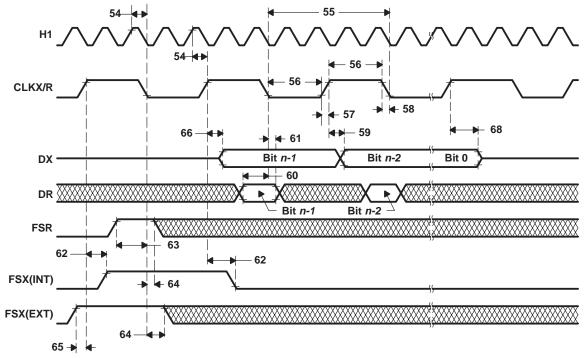

### serial-port timing (see Figure 22 and Figure 23)

| NO. |                            |                                                  |            | MIN                        | MAX                               | UNIT |

|-----|----------------------------|--------------------------------------------------|------------|----------------------------|-----------------------------------|------|

| 54  | <sup>t</sup> d(H1H-SCK)    | Delay time, H1 high to internal CLKX/R           |            |                            | 13                                | ns   |

|     |                            |                                                  |            | t <sub>c(H)</sub> x2.6     |                                   |      |

| 55  | <sup>t</sup> c(SCK)        | Cycle time, CLKX/R                               | CLKX/R int | t <sub>c(H)</sub> x2       | <sup>t</sup> c(H) <sup>x232</sup> | ns   |

| 50  |                            | Pulse duration OU/C//D bish // au                | CLKX/R ext | <sup>t</sup> c(H)+10       |                                   |      |

| 56  | <sup>t</sup> w(SCK)        | Pulse duration, CLKX/R high/low                  | CLKX/R int | [t <sub>c(SCK)</sub> /2]-5 | [t <sub>C(SCK)</sub> /2]+5        | ns   |

| 57  | <sup>t</sup> r(SCK)        | Rise time, CLKX/R                                |            |                            | 7                                 | ns   |

| 58  | <sup>t</sup> f(SCK)        | Fall time, CLKX/R                                |            |                            | 7                                 | ns   |

| 50  |                            | Deleviting OLKY to DY callel                     | CLKX ext   |                            | 30                                |      |

| 59  | <sup>t</sup> d(C-DX)       | Delay time, CLKX to DX valid                     | CLKX int   |                            | 17                                | ns   |

|     |                            |                                                  | CLKR ext   | 9                          |                                   |      |

| 60  | <sup>t</sup> su(DR-CLKRL)  | Setup time, DR before CLKR low                   | CLKR int   | 21                         |                                   | ns   |

|     |                            |                                                  | CLKR ext   | 9                          |                                   |      |

| 61  | <sup>t</sup> h(CLKRL-DR)   | Hold time, DR from CLKR low                      | CLKR int   | 0                          |                                   | ns   |

| 00  |                            | Deleviting OLICY is interest FOX bish for        | CLKX ext   |                            | 27                                |      |

| 62  | <sup>t</sup> d(C-FSX)      | Delay time, CLKX to internal FSX high/low        | CLKX int   |                            | 15                                | ns   |

|     |                            |                                                  | CLKR ext   | 9                          |                                   |      |

| 63  | <sup>t</sup> su(FSR-CLKRL) | Setup time, FSR before CLKR low                  | CLKR int   | 9                          |                                   | ns   |

| ~ 1 |                            |                                                  | CLKX/R ext | 9                          |                                   |      |

| 64  | <sup>t</sup> h(SCKL-FS)    | Hold time, FSX/R input from CLKX/R low           | CLKX/R int | 0                          |                                   | ns   |

|     |                            |                                                  | CLKX ext   | -[t <sub>c(H)</sub> -8]*   | [t <sub>c(SCK)</sub> /2]-10*      |      |

| 65  | <sup>t</sup> su(FSX-C)     | Setup time, external FSX before CLKX             | CLKX int   | [t <sub>c(H)</sub> -21]*   | tc(SCK)/2*                        | ns   |

| 00  |                            | Delay time, CLKX to first DX bit, FSX            | CLKX ext   |                            | 30*                               |      |

| 66  | <sup>t</sup> d(CH-DX)V     | precedes CLKX high                               | CLKX int   |                            | 18*                               | ns   |

| 67  | <sup>t</sup> d(FSX-DX)V    | Delay time, FSX to first DX bit, CLKX preced     | es FSX     |                            | 30*                               | ns   |

| 68  | <sup>t</sup> d(CH-DXZ)     | Delay time, CLKX high to DX high impedanc<br>bit |            | 17*                        | ns                                |      |

\* This parameter is not production tested.

SGUS039 - AUGUST 2002

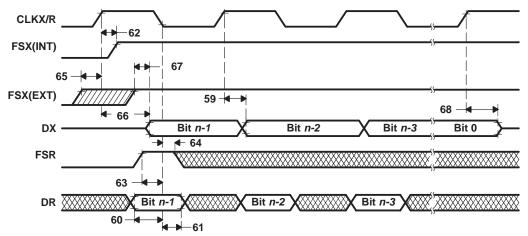

#### data-rate timing modes

Unless otherwise indicated, the data-rate timings shown in Figure 22 and Figure 23 are valid for all serial-port modes, including handshake. For a functional description of serial-port operation, see the *TMS320C3x User's Guide* (literature number SPRU031).

NOTES: A. Timing diagrams show operations with CLKXP = CLKRP = FSXP = FSRP = 0.

B. Timing diagrams depend on the length of the serial-port word, where n = 8, 16, 24, or 32 bits, respectively.

Figure 22. Timing for Fixed Data-Rate Mode

SGUS039 - AUGUST 2002

#### data-rate timing modes (continued)

- NOTES: A. Timing diagrams show operation with CLKXP = CLKRP = FSXP = FSRP = 0.

- B. Timing diagrams depend on the length of the serial-port word, where n = 8, 16, 24, or 32 bits, respectively.

- C. The timings that are not specified expressly for the variable data-rate mode are the same as those that are specified for the fixed data-rate mode.

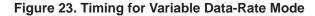

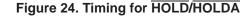

#### HOLD timing

HOLD is an asynchronous input that can be asserted at any time during a clock cycle. If the specified timings are met, the exact sequence shown in Figure 27 occurs; otherwise, an additional delay of one clock cycle is possible.

The NOHOLD bit of the primary-bus control register overrides the HOLD signal. When this bit is set, the device comes out of hold and prevents future hold cycles.

Asserting HOLD prevents the processor from accessing the primary bus. Program execution continues until a read from or a write to the primary bus is requested. In certain circumstances, the first write is pending, thus allowing the processor to continue until a second write is encountered.

| NO. |                                   |                                                                     | MIN                 | MAX | UNIT |

|-----|-----------------------------------|---------------------------------------------------------------------|---------------------|-----|------|

| 69  | <sup>t</sup> su(HOLD-H1L)         | Setup time, HOLD before H1 low                                      | 13                  |     | ns   |

| 70  | <sup>t</sup> v(H1L-HOLDA)         | Valid time, HOLDA after H1 low                                      | 0*                  | 9   | ns   |

| 71  | <sup>t</sup> w(HOLD) <sup>†</sup> | Pulse duration, HOLD low                                            | 2t <sub>c(H)</sub>  |     | ns   |

| 72  | <sup>t</sup> w(HOLDA)             | Pulse duration, HOLDA low                                           | t <sub>cH</sub> −5* |     | ns   |

| 73  | <sup>t</sup> d(H1L-SH)H           | Delay time, H1 low to STRB high for a HOLD                          | 0*                  | 9   | ns   |

| 74  | <sup>t</sup> dis(H1L-S)           | Disable time, H1 low to STRB to the high-impedance state            | 0*                  | 9*  | ns   |

| 75  | <sup>t</sup> en(H1L-S)            | Enable time, H1 low to STRB enabled (active)                        | 0*                  | 9   | ns   |

| 76  | <sup>t</sup> dis(H1L-RW)          | Disable time, H1 low to $R\overline{W}$ to the high-impedance state | 0*                  | 9*  | ns   |

| 77  | <sup>t</sup> en(H1L-RW)           | Enable time, H1 low to $R/\overline{W}$ enabled (active)            | 0*                  | 9   | ns   |

| 78  | <sup>t</sup> dis(H1L-A)           | Disable time, H1 low to address to the high-impedance state         | 0*                  | 10* | ns   |

| 79  | <sup>t</sup> en(H1L-A)            | Enable time, H1 low to address enabled (valid)                      | 0*                  | 13  | ns   |

| 80  | <sup>t</sup> dis(H1H-D)           | Disable time, H1 high to data to the high-impedance state           | 0*                  | 9*  | ns   |

#### timing for HOLD/HOLDA (see Figure 24)

<sup>†</sup> HOLD is an asynchronous input and can be asserted at any point during a clock cycle. If the specified timings are met, the exact sequence shown in Figure 24 occurs; otherwise, an additional delay of one clock cycle is possible.

\* This parameter is not production tested.

NOTE A: HOLDA goes low in response to HOLD going low and continues to remain low until one H1 cycle after HOLD goes back high.

#### SUS039 - AUGUST 2002

#### general-purpose I/O timing

Peripheral pins include CLKX0, CLKR0, DX0, DR0, FSX0, FSR0, and TCLK0/1. The contents of the internal control registers associated with each peripheral define the modes for these pins.

#### peripheral pin I/O timing

The table, timing parameters for peripheral pin general-purpose I/O, defines peripheral pin general-purpose I/O timing parameters.

#### timing requirements for peripheral pin general-purpose I/O (see Note 6 and Figure 25)

| NO. |                                                                           | MIN | MAX | UNIT |

|-----|---------------------------------------------------------------------------|-----|-----|------|

| 81  | tsu(GPIO-H1L) Setup time, general-purpose input before H1 low             | 10  |     | ns   |

| 82  | th(H1L-GPIO) Hold time, general-purpose input after H1 low                | 0   |     | ns   |

| 83  | t <sub>d(H1H-GPIO)</sub> Delay time, general-purpose output after H1 high |     | 13  | ns   |

NOTE 6: Peripheral pins include CLKX0, CLKR0, DX0, DR0, FSX0, FSR0, and TCLK0/1. The modes of these pins are defined by the contents of internal-control registers associated with each peripheral.

(see Note A)

NOTE A: Peripheral pins include CLKX0, CLKR0, DX0, DR0, FSX0, FSR0, and TCLK0/1.

#### Figure 25. Timing for Peripheral Pin General-Purpose I/O

SUS039 - AUGUST 2002

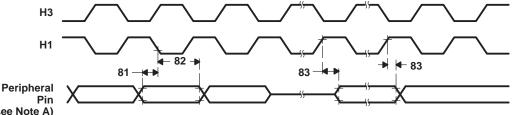

#### changing the peripheral pin I/O modes

The following tables show the timing parameters for changing the peripheral pin from a general-purpose output pin to a general-purpose input pin and vice versa.

# timing requirements for peripheral pin changing from general-purpose output to input mode (see Note 6 and Figure 26)

| NO. |                                                                    | MIN MAX | UNIT |

|-----|--------------------------------------------------------------------|---------|------|

| 84  | th(H1H) Hold time, peripheral pin after H1 high                    | 13      | ns   |

| 85  | t <sub>su(GPIO-H1L)</sub> Setup time, peripheral pin before H1 low | 9       | ns   |

| 86  | th(H1L-GPIO) Hold time, peripheral pin after H1 low                | 0       | ns   |

NOTE 6: Peripheral pins include CLKX0, CLKR0, DX0, DR0, FSX0, FSR0, and TCLK0/1. The modes of these pins are defined by the contents of internal-control registers associated with each peripheral.

NOTE A: Peripheral pins include CLKX0, CLKR0, DX0, DR0, FSX0, FSR0, and TCLK0/1.

Figure 26. Timing for Change of Peripheral Pin From General-Purpose Output to Input Mode

SUS039 - AUGUST 2002

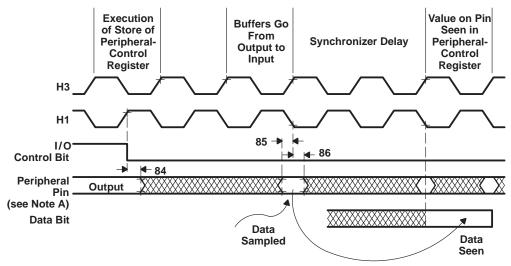

# timing for peripheral pin changing from general-purpose input to output mode (see Note 6 and Figure 27)

| NO. |                                                                                                                                      | MIN | MAX | UNIT |  |  |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|--|--|--|

| 87  | t <sub>d</sub> (H1H-GPIO) Delay time, H1 high to peripheral pin switching from input to output                                       |     | 13  | ns   |  |  |  |

|     | NOTE 6. Derinherel pine include CLKX0, CLKP0, DX0, DP0, ESX0, ESP0, and TCLK0/1. The medee of these pine are defined by the contents |     |     |      |  |  |  |

NOTE 6: Peripheral pins include CLKX0, CLKR0, DX0, DR0, FSX0, FSR0, and TCLK0/1. The modes of these pins are defined by the contents of internal-control registers associated with each peripheral.

NOTE A: Peripheral pins include CLKX0, CLKR0, DX0, DR0, FSX0, FSR0, and TCLK0/1.

Figure 27. Timing for Change of Peripheral Pin From General-Purpose Input to Output Mode

SUS039 - AUGUST 2002

#### timer pin timing

Valid logic-level periods and polarity are specified by the contents of the internal control registers.

The following tables define the timing requirements for the timer pin.

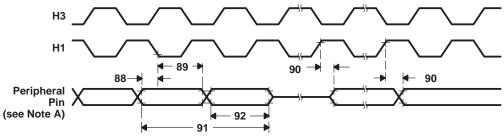

#### timing for timer pin (see Note 7 and Figure 28)

| NO. |                                        |                                            |          | MIN                         | MAX                                 | UNIT |

|-----|----------------------------------------|--------------------------------------------|----------|-----------------------------|-------------------------------------|------|

| 88  | tsu(TCLK-H1L)                          | Setup time, TCLK external before H1 low    |          | 10                          |                                     | ns   |

| 89  | <sup>t</sup> h(H1L-TCLK)               | Hold time, TCLK external after H1 low      |          | 0                           |                                     | ns   |

| 90  | <sup>t</sup> d(H1H-TCLK)               | Delay time, H1 high to TCLK internal valid |          |                             | 9                                   | ns   |

| 04  | t <sub>c(TCLK)</sub> Cycle time, TCLK  |                                            | TCLK ext | t <sub>c(H)</sub> ×2.6      |                                     |      |

| 91  |                                        | - Cycle time, TCLK                         | TCLK int | t <sub>c(H)</sub> ×2        | t <sub>c(H)</sub> ×2 <sup>32*</sup> | ns   |

| 92  | t (70) (0)                             |                                            | TCLK ext | <sup>t</sup> c(H)+10        |                                     | 20   |

| 92  | tw(TCLK) Pulse duration, TCLK high/low |                                            | TCLK int | [t <sub>c(TCLK)</sub> /2]-5 | [t <sub>c(TCLK)</sub> /2]+5         | ns   |

\* This parameter is not production tested.

NOTE 7: Numbers 88 and 89 are applicable for a synchronous input clock. Timing parameters 91 and 92 are applicable for an asynchronous input clock.

NOTE A: HOLDA goes low in response to HOLD going low and continues to remain low until one H1 cycle after HOLD goes back high.

Figure 28. Timing for Timer Pin

SUS039 - AUGUST 2002

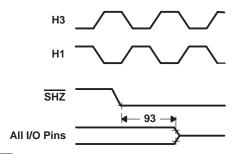

#### SHZ pin timing

The following table defines the timing parameter for the  $\overline{SHZ}$  pin.

## timing parameters for SHZ (see Figure 29)

| NO. |                                                                              | MIN | MAX  | UNIT |

|-----|------------------------------------------------------------------------------|-----|------|------|

| 93  | tdis(SHZ) Disable time, SHZ low to all O, I/O pins disabled (high impedance) | 0*  | 2P†* | ns   |

| + - |                                                                              |     | -    |      |

<sup>†</sup>  $P = t_{C(CI)}$ \* This parameter is not production tested.

NOTE A: Enabling SHZ destroys SM320LC31-EP register and memory contents. Assert SHZ = 1 and reset the SM320LC31-EP to restore it to a known condition.

SGUS039 - AUGUST 2002

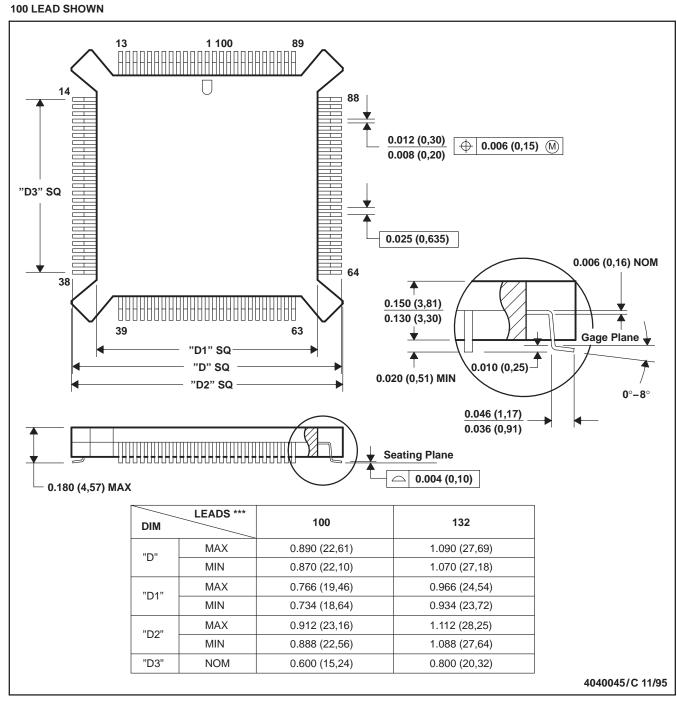

#### PROCESSING POWER OPERATING TECHNOLOGY DEVICE PACKAGE TYPE SUPPLY FREQUENCY LEVEL SM320LC31PQM40EP EΡ 0.72-µm CMOS $3.3 V \pm 5\%$ 40 MHz Plastic 132-lead good flatpack SM PQ 320 (L) C 31 Μ 40 EP - ENHANCED PLASTIC PREFIX -SMJ = MIL-PRF-38535 (QML) SM = Standard Processing SMQ = Plastic (QML) SPEED RANGE 40 = 40 MHz 50 = 50 MHz **DEVICE FAMILY** 60 = 60 MHz320 = SMJ320 Family **TEMPERATURE RANGE** TECHNOLOGY $M = -55^{\circ}C \text{ to } 125^{\circ}C$ $S = -55^{\circ}C \text{ to } 105^{\circ}C$ $L = 0^{\circ}C \text{ to } 70^{\circ}C$ L = Low Voltage (3.3-V option) PACKAGE TYPE TECHNOLOGY GFA = 141-Pin Ceramic Staggered Pin Grid C = CMOSArray Ceramic Package HFG = 132-Pin Ceramic Quad Flatpack with a nonconductive tie bar DEVICE -PQ 132-lead Plastic Quad Flatpack 31 = 320C31 or 320LC31 = = 132-lead TAB frame with TA polyimide encapsulant ТΒ 132-lead TAB frame, bare-die = option KGD = Known Good Die

part order information

Note: Not all speed, package, process, or temperature combinations are available.

Figure 30. Device Nomenclature

SGUS039 - AUGUST 2002

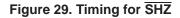

**MECHANICAL DATA**

PQ (S-PQFP-G\*\*\*)

PLASTIC QUAD FLATPACK

- NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MO-069

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications       |                           |

|-----------------------------|------------------------|--------------------|---------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters             | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                         | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Clocks and Timers           | www.ti.com/clocks      | Digital Control    | www.ti.com/digitalcontrol |

| Interface                   | interface.ti.com       | Medical            | www.ti.com/medical        |

| Logic                       | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt                  | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers            | microcontroller.ti.com | Security           | www.ti.com/security       |

| RFID                        | www.ti-rfid.com        | Telephony          | www.ti.com/telephony      |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Video & Imaging    | www.ti.com/video          |

|                             |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated