#### Dear customer

LAPIS Semiconductor Co., Ltd. ("LAPIS Semiconductor"), on the 1<sup>st</sup> day of October, 2020, implemented the incorporation-type company split (shinsetsu-bunkatsu) in which LAPIS established a new company, LAPIS Technology Co., Ltd. ("LAPIS Technology") and LAPIS Technology succeeded LAPIS Semiconductor's LSI business.

Therefore, all references to "LAPIS Semiconductor Co., Ltd.", "LAPIS Semiconductor" and/or "LAPIS" in this document shall be replaced with "LAPIS Technology Co., Ltd."

Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

LAPIS Technology Co., Ltd. October 1, 2020

FEUL620Q504H-02

## ML620Q503H/Q504H User's Manual

Issue Date: May.20, 2020

<u>Notes</u>

- 1) The information contained herein is subject to change without notice.

- 2) Although LAPIS Semiconductor is continuously working to improve product reliability and quality, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury or fire arising from failure, please take safety measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures. LAPIS Semiconductor shall have no responsibility for any damages arising out of the use of our Products beyond the rating specified by LAPIS Semiconductor.

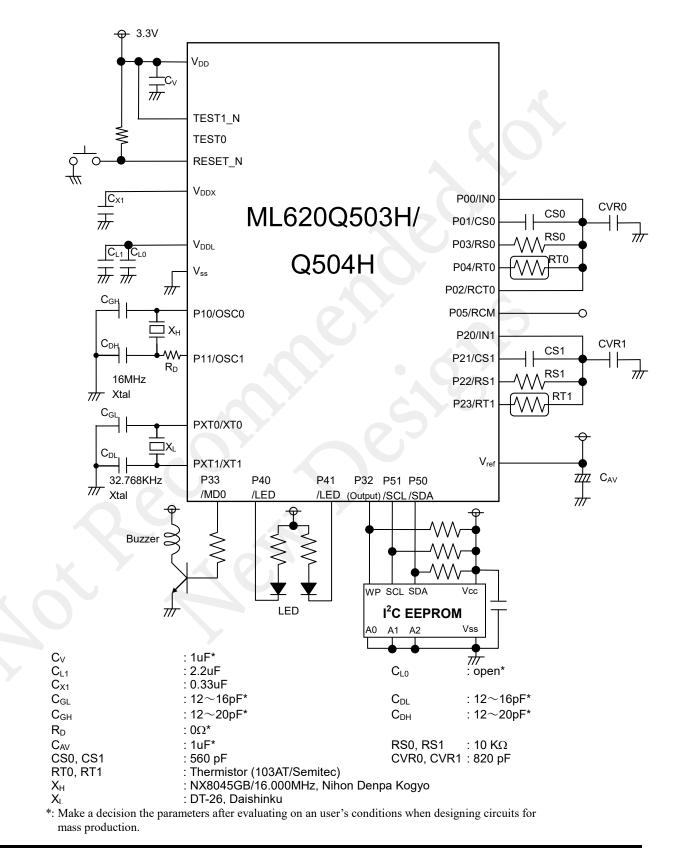

- 3) Examples of application circuits, circuit constants and any other information contained herein are provided only to illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

- 4) The technical information specified herein is intended only to show the typical functions of the Products and examples of application circuits for the Products. No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of LAPIS Semiconductor or any third party with respect to the information contained in this document; therefore LAPIS Semiconductor shall have no responsibility whatsoever for any dispute, concerning such rights owned by third parties, arising out of the use of such technical information.

- 5) The Products are intended for use in general electronic equipment (i.e. AV/OA devices, communication, consumer systems, gaming/entertainment sets) as well as the applications indicated in this document.

- 6) The Products specified in this document are not designed to be radiation tolerant.

- 7) For use of our Products in applications requiring a high degree of reliability (as exemplified below), please contact and consult with a LAPIS Semiconductor representative: transportation equipment (i.e. cars, ships, trains), primary communication equipment, traffic lights, fire/crime prevention, safety equipment, medical systems, servers, solar cells, and power transmission systems.

- 8) Do not use our Products in applications requiring extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters.

- 9) LAPIS Semiconductor shall have no responsibility for any damages or injury arising from non-compliance with the recommended usage conditions and specifications contained herein.

- 10)LAPIS Semiconductor has used reasonable care to ensure the accuracy of the information contained in this document. However, LAPIS Semiconductor does not warrant that such information is error-free and LAPIS Semiconductor shall have no responsibility for any damages arising from any inaccuracy or misprint of such information.

- 11)Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS Directive. For more details, including RoHS compatibility, please contact a ROHM sales office. LAPIS Semiconductor shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 12) When providing our Products and technologies contained in this document to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act.

- 13) This document, in part or in whole, may not be reprinted or reproduced without prior consent of LAPIS Semiconductor.

Copyright 2015-2020 LAPIS Semiconductor Co., Ltd.

#### LAPIS Semiconductor Co., Ltd.

2-4-8 Shinyokohama, Kouhoku-ku, Yokohama 222-8575, Japan http://www.lapis-semi.com/en/

## Preface

This manual describes the operation of the hardware of the 16-bit microcontroller ML620Q503H/Q504H.

See the relevant manuals listed in supplementary volume; "MCU Relevant Documents list" as necessary.

| Classification  | Notation                                                                                                                            | Description                                                                                                                                                                                                             |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ◆ Numeric value | xxh, xxH<br>xxb                                                                                                                     | Indicates a hexadecimal number. x: Any value in the range of 0 to F<br>Indicates a binary number; "b" may be omitted. x: A value 0 or 1                                                                                 |

| ♦ Unit          | word, W<br>byte, B<br>nibble, N<br>mega-, M<br>kilo-, K<br>kilo-, k<br>milli-, m<br>micro-, μ<br>nano-, n<br>second, s (lower case) | 1 word = 16 bits<br>1 byte = 8 bits<br>1 nibble = 4 bits<br>$10^{6}$<br>$2^{10} = 1024$<br>$10^{3} = 1000$<br>$10^{-3}$<br>$10^{-6}$<br>$10^{-9}$<br>second                                                             |

| ♦ Terminology   | "H" level, "1" level<br>"L" level, "0" level                                                                                        | Indicates high voltage signal levels $V_{IH}$ and $V_{OH}$ as specified by the electrical characteristics.<br>Indicates low voltage signal levels $V_{IL}$ and $V_{OL}$ as specified by the electrical characteristics. |

#### Notation

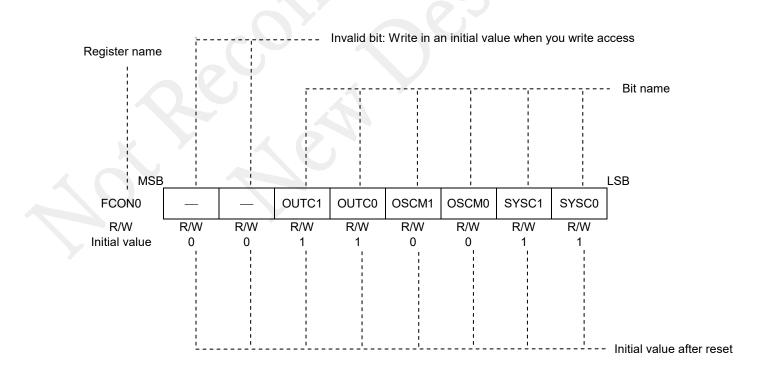

◆ Register description

R/W: Indicates that Read/Write attribute. "R" indicates that data can be read and "W" indicates that data can be written. "R/W" indicates that data can be read or written.

#### Table of Contents

| Cł | napte | er 1                                                  |     |

|----|-------|-------------------------------------------------------|-----|

|    | Over  | view                                                  |     |

|    | 1.1   | Features                                              | 1-1 |

|    | 1.2   | Configuration of Functional Blocks                    | 1-5 |

|    |       | 1.2.1 Block Diagram of ML620Q503H/Q504H               |     |

|    | 1.3   | Pins                                                  |     |

|    |       | 1.3.1 Pin Layout                                      |     |

|    |       | 1.3.1.1 Pin Layout of ML620Q503H/Q504H TQFP Package   |     |

|    |       | 1.3.2 List of Pins                                    |     |

|    |       | 1.3.2.1 List of Pins of ML620Q503H/Q504H TQFP Package |     |

|    |       | 1.3.3 Description of Pins                             |     |

|    |       | 1.3.4 Termination of Unused Pins                      |     |

|    |       |                                                       |     |

#### Chapter 2

| 2.        | CPU   | and Memory Space                              |  |

|-----------|-------|-----------------------------------------------|--|

|           | 2.1   | General Description                           |  |

|           |       | 2.1.1 Features                                |  |

|           |       | 2.1.2 Notes When Executing SB/RB Instruction  |  |

|           | 2.2   | 5                                             |  |

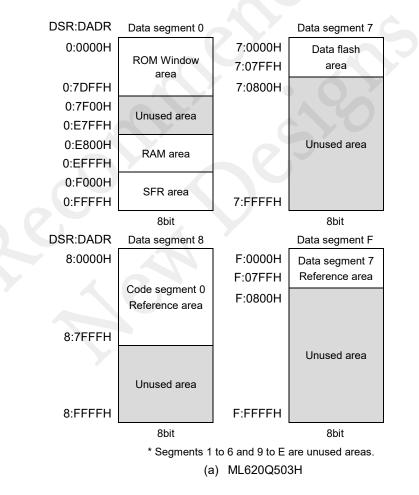

|           | 2.3   | Data Memory Space                             |  |

|           | 2.4   | Instruction Length                            |  |

|           | 2.5   |                                               |  |

|           | 2.6   |                                               |  |

|           |       | 2.6.1 List of Registers                       |  |

|           |       | 2.6.2 Data Segment Register (DSR)             |  |

|           | 2.7   | Multiplication/Division Coprocessor           |  |

|           |       | 2.7.1 General Description                     |  |

|           |       | 2.7.2 List of Registers                       |  |

|           |       | 2.7.2.1 Registers A, B, C, and D (CR0 to CR7) |  |

|           |       | 2.7.2.2 Operation Mode Register (CR8)         |  |

|           |       | 2.7.2.3 Operation Status Register (CR9)       |  |

|           |       | 2.7.2.4 Coprocessor ID Register (CR15)        |  |

|           |       | 2.7.3 Description of Operation                |  |

| _         |       |                                               |  |

| <u>Cł</u> | napte | er 3                                          |  |

| -         | -     |                                               |  |

## Chapter 3

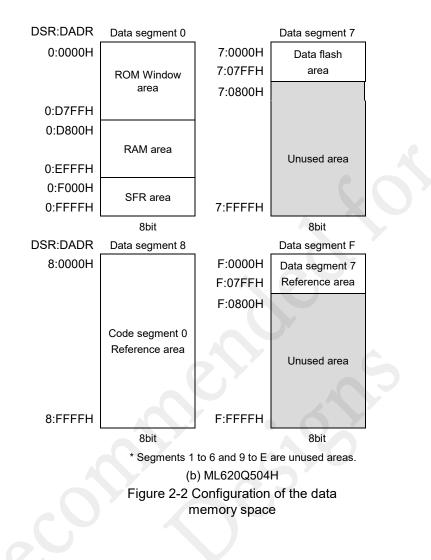

| 3. | Rese | et Function                          | 3-1 |

|----|------|--------------------------------------|-----|

|    |      | Overview                             |     |

|    |      | 3.1.1 Features                       | 3-1 |

|    |      | 3.1.2 Configuration                  | 3-1 |

|    |      | 3.1.3 List of Pin                    | 3-1 |

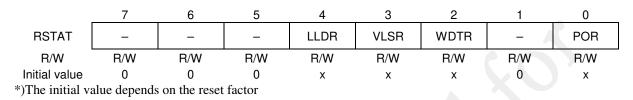

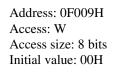

|    | 3.2  | Description of Registers             | 3-2 |

|    |      | 3.2.1 List of Registers              | 3-2 |

|    |      | 3.2.2 Reset Status Register (RSTAT)  | 3-3 |

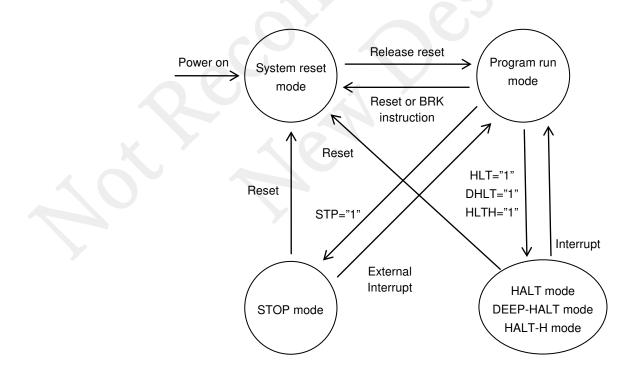

|    | 3.3  | Description of Operation             | 3-4 |

|    |      | 3.3.1 Cause of Reset                 | 3-4 |

|    |      | 3.3.2 Operation of System Reset Mode | 3-4 |

|    |      |                                      |     |

| 4. | Powe | r Management        | 4- <sup>-</sup> | 1 |

|----|------|---------------------|-----------------|---|

|    | 4.1  | General Description | 4- <sup>-</sup> | 1 |

|     | 4.1.1 Features                                                        |      |

|-----|-----------------------------------------------------------------------|------|

|     | 4.1.2 Configuration                                                   |      |

| 4.2 | Description of Registers                                              | 4-2  |

|     | 4.2.1 Register Configuration List                                     |      |

|     | 4.2.2 Stop Code Acceptor (STPACP)                                     |      |

|     | 4.2.3 Standby Control Register (SBYCON)                               |      |

|     | 4.2.4 Block Control Register 01 (BLKCON01)                            |      |

|     | 4.2.5 Block Control Register 23 (BLKCON23)                            |      |

|     | 4.2.6 Block Control Register 45 (BLKCON45)                            |      |

| 4.3 | Description of Operation                                              | 4-11 |

|     | 4.3.1 HALT Mode                                                       |      |

|     | 4.3.1.1 HALT Mode                                                     |      |

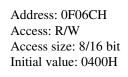

|     | 4.3.1.2 DEEP-HALT Mode                                                |      |

|     | 4.3.1.3 HALT-H Mode                                                   |      |

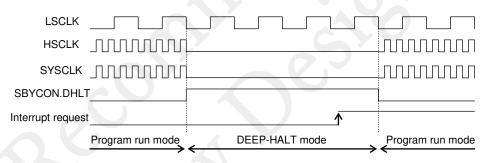

|     | 4.3.2 STOP Mode                                                       |      |

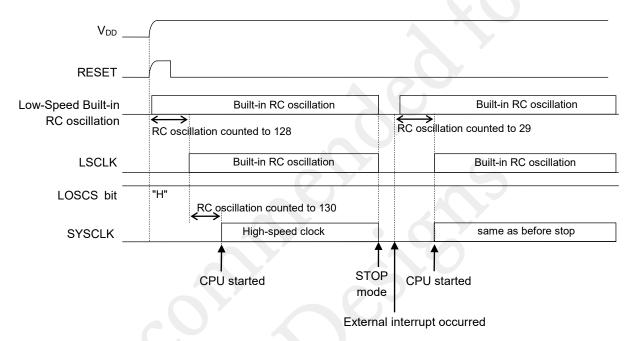

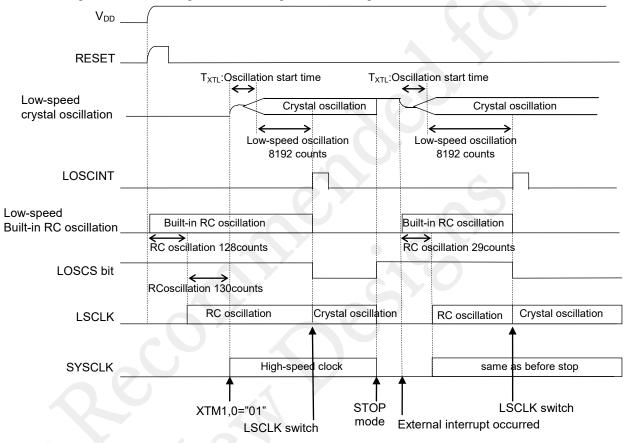

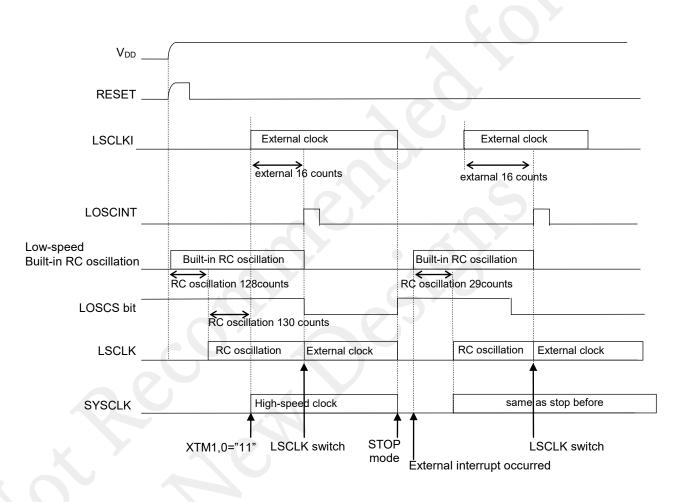

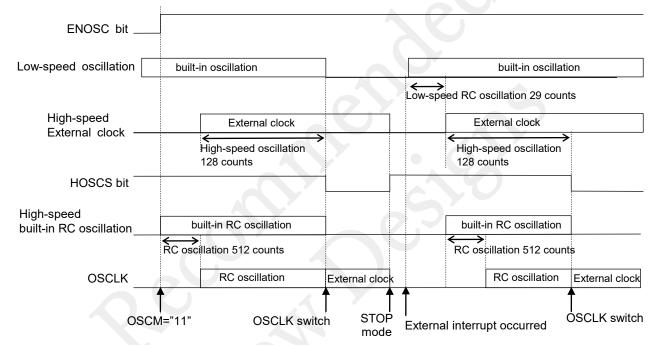

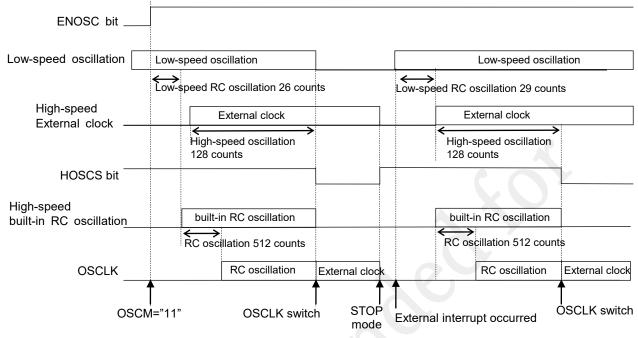

|     | 4.3.2.1 Oscillation Stop and Restart Timing of Low-Speed Clock        | 4-14 |

|     | 4.3.2.2 Oscillation Stop and Restart Timing of High-Speed Clock       |      |

|     | 4.3.2.3 Note on Return Operation from STOP/HALT/DEEP-HALT/HALT-H Mode |      |

|     | 4.3.3 Operation of Functions in STOP/HALT/DEEP-HALT/HALT-H Mode       |      |

|     | 4.3.4 Block Control Function                                          |      |

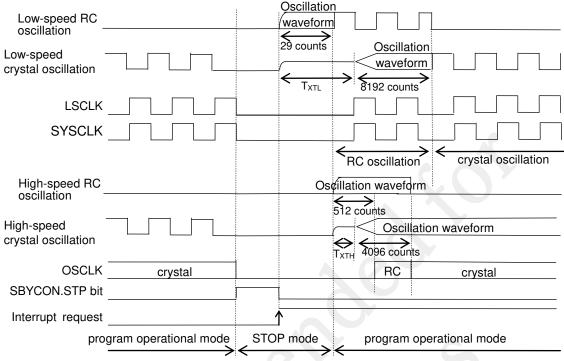

| 5. | Interr | upts                                                        | 5-1    |

|----|--------|-------------------------------------------------------------|--------|

|    | 5.1    |                                                             |        |

|    |        | 5.1.1 Features                                              | 5-1    |

|    |        | 5.1.2 Configuration                                         |        |

|    | 5.2    | Description of Registers                                    | 5-3    |

|    |        | 5.2.1 List of Registers                                     | 5-3    |

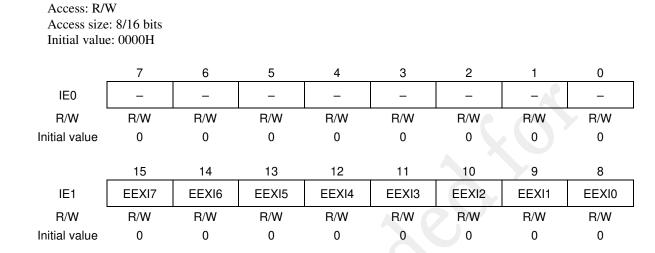

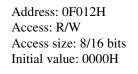

|    |        | 5.2.2 Interrupt Enable Register 01 (IE01)                   | 5-5    |

|    |        | 5.2.3 Interrupt Enable Register 23 (IE23)                   | 5-7    |

|    |        | 5.2.4 Interrupt Enable Register 45 (IE45)                   | 5-9    |

|    |        | 5.2.5 Interrupt Enable Register 67 (IE67)                   | . 5-11 |

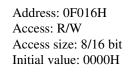

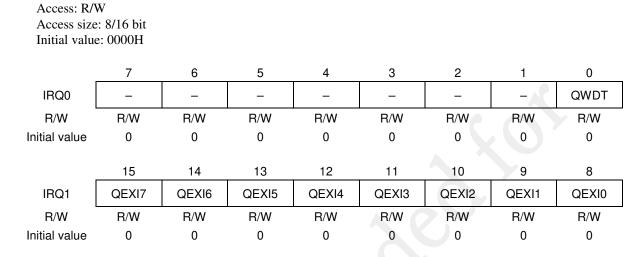

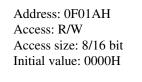

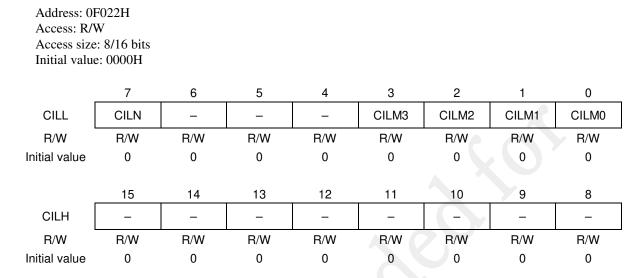

|    |        | 5.2.6 Interrupt Request Register 01 (IRQ01)                 | . 5-13 |

|    |        | 5.2.7 Interrupt Request Register 23 (IRQ23)                 | . 5-16 |

|    |        | 5.2.8 Interrupt Request Register 45 (IRQ45)                 |        |

|    |        | 5.2.9 Interrupt Request Register 67 (IRQ67)                 |        |

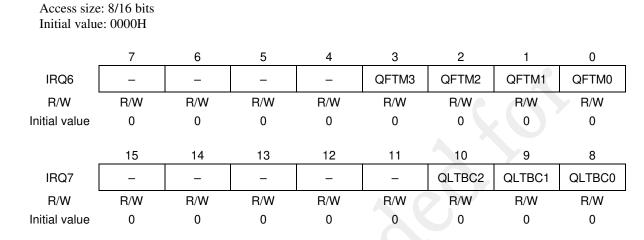

|    |        | 5.2.10 Interrupt Level Control Enable Register (ILEN)       | . 5-24 |

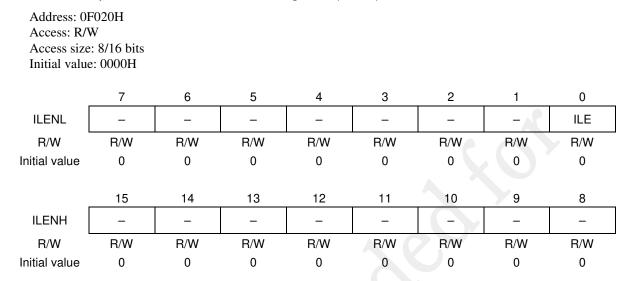

|    |        | 5.2.11 Current Interrupt Request Level Register (CIL)       |        |

|    |        | 5.2.12 Interrupt Level Control Register 1 (ILC1)            |        |

|    |        | 5.2.13 Interrupt Level Control Register 2 (ILC2)            |        |

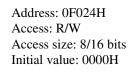

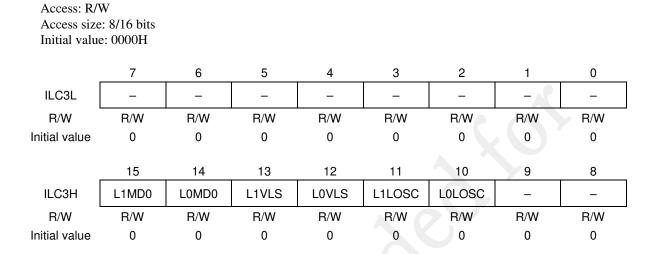

|    |        | 5.2.14 Interrupt Level Control Register 3 (ILC3)            | . 5-31 |

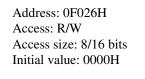

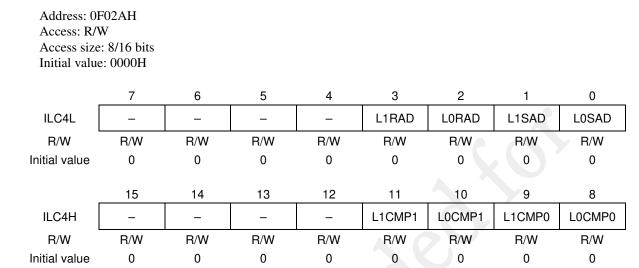

|    |        | 5.2.15 Interrupt Level Control Register 4 (ILC4)            | . 5-33 |

|    |        | 5.2.16 Interrupt Level Control Register 5 (ILC5)            |        |

|    |        | 5.2.17 Interrupt Level Control Register 6 (ILC6)            |        |

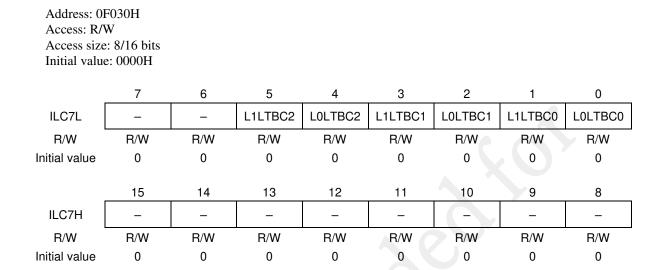

|    |        | 5.2.18 Interrupt Level Control Register 7 (ILC7)            |        |

|    |        | 5.2.19 External Interrupt Control Registers 01 (EXICON01)   | . 5-41 |

|    |        | 5.2.20 External Interrupt Control Registers 23 (EXICON23)   | . 5-42 |

|    |        | 5.2.21 External Interrupt 0/1 Selection Register (EXI01SEL) | . 5-43 |

|    |        | 5.2.22 External Interrupt 2/3 Selection Register (EXI23SEL) |        |

|    |        | 5.2.23 External Interrupt 4/5 Selection Register (EXI45SEL) |        |

|    |        | 5.2.24 External Interrupt 6/7 Selection Register (EXI67SEL) | . 5-49 |

|    | 5.3    | Description of Operation                                    |        |

|    |        | 5.3.1 Interrupt Source                                      |        |

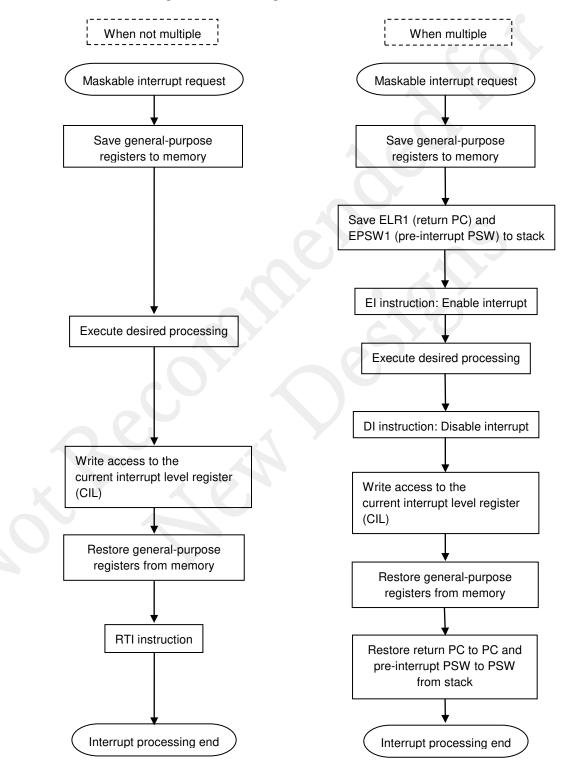

|    |        | 5.3.2 Maskable Interrupt Processing                         | . 5-53 |

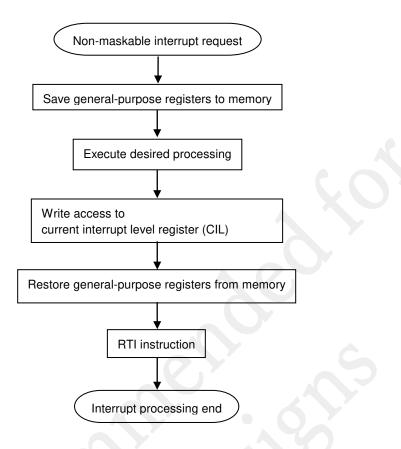

| 5.3.3 | Non-Maskable Interrupt Processing                         |  |

|-------|-----------------------------------------------------------|--|

|       | Software Interrupt Processing                             |  |

|       | Notes on Interrupt Routine                                |  |

| 5.3.6 | Interrupt Processing When Interrupt Level Control Enabled |  |

| 5.3.7 | Flow Chart (When Interrupt Level Control Enabled)         |  |

| 5.3.8 | Interrupt Disable State                                   |  |

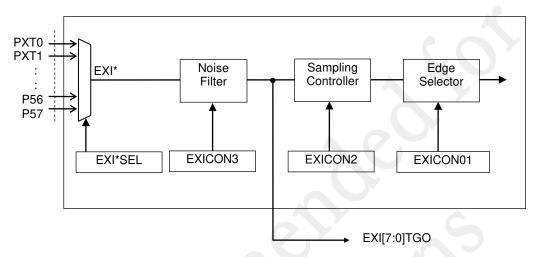

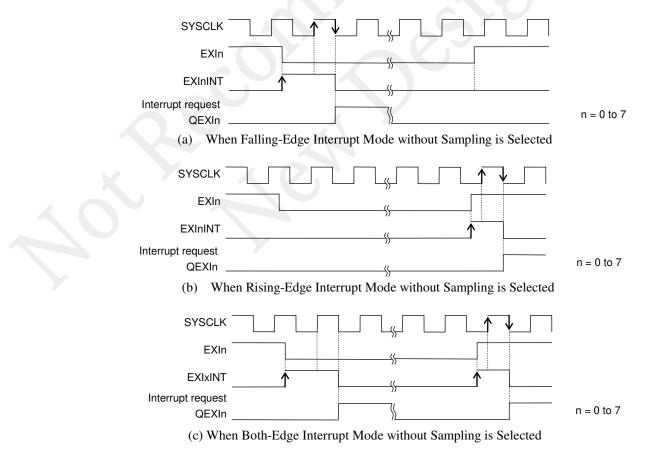

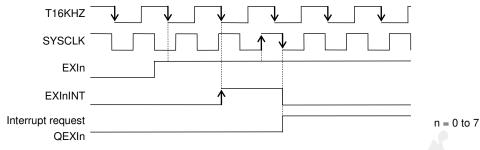

|       | External Interrupt                                        |  |

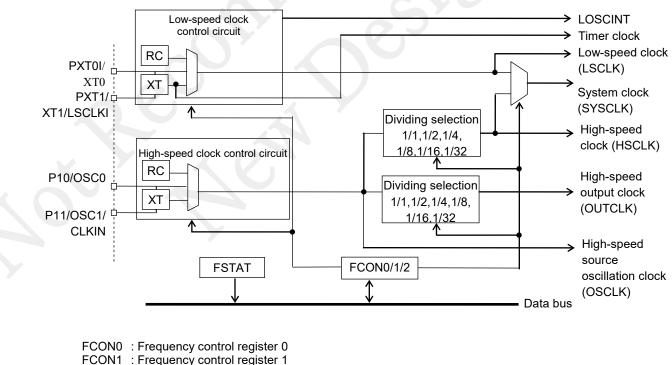

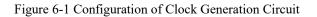

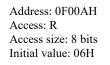

| 6. | Clock | Generation  | Circuit                                               | 6-1  |

|----|-------|-------------|-------------------------------------------------------|------|

|    | 6.1   | General De  | escription                                            |      |

|    |       | 6.1.1 Feat  | tures                                                 | 6-1  |

|    |       | 6.1.2 Con   | figuration                                            | 6-1  |

|    |       | 6.1.3 List  | of Pins                                               | 6-3  |

|    |       | 6.1.4 Cloc  | k Configuration Diagram                               | 6-4  |

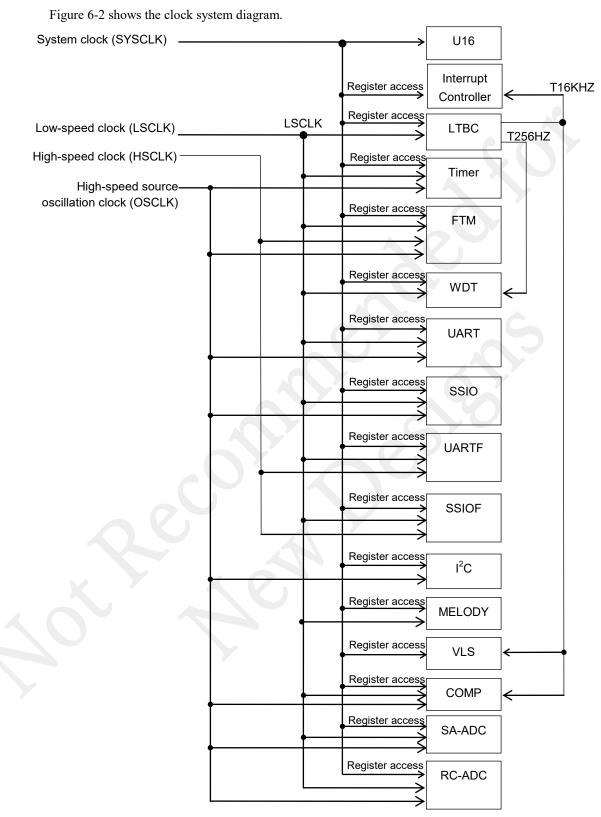

|    | 6.2   | Description | of Registers                                          | 6-5  |

|    |       |             | of Registers                                          |      |

|    |       | 6.2.2 Freq  | uency Control Register 01 (FCON01)                    | 6-6  |

|    |       | 6.2.3 Freq  | uency Control Register 23 (FCON23)                    | 6-9  |

|    |       | 6.2.4 Freq  | uency Status Register (FSTAT)                         | 6-11 |

|    | 6.3   | Description | of Operation                                          | 6-12 |

|    |       |             | -Speed Clock                                          |      |

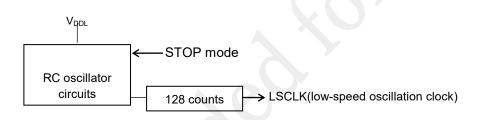

|    |       |             | Low-Speed Built-in RC Oscillation Mode                |      |

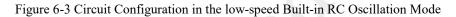

|    |       |             | Low-Speed Crystal Oscillation Mode                    |      |

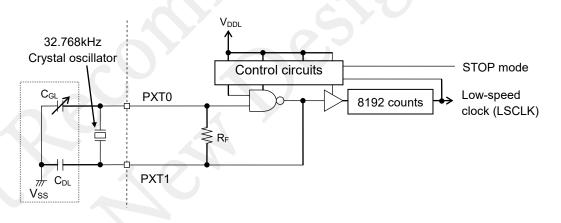

|    |       |             | Low-Speed External Clock Input Mode                   |      |

|    |       |             | Low-Speed Built-In RC Oscillation Mode Operation      |      |

|    |       |             | Low-Speed Crystal Oscillation Mode Operation          |      |

|    |       |             | Low-Speed External Clock Mode Operation               |      |

|    |       |             | n-Speed Clock                                         |      |

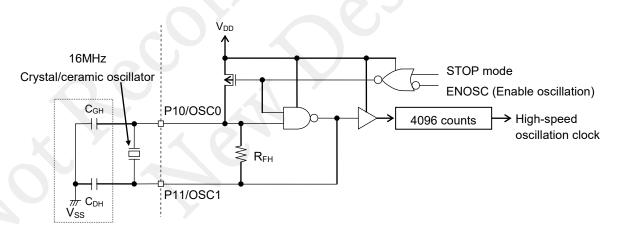

|    |       | 6.3.2.1     | 5 1                                                   |      |

|    |       | 6.3.2.2     |                                                       |      |

|    |       | 6.3.2.3     | High-Speed External Clock Input Mode                  |      |

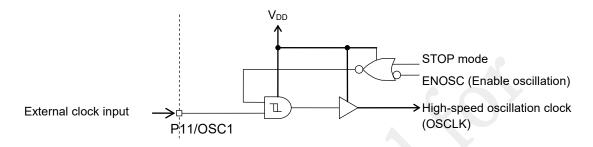

|    |       | 6.3.2.4     | High-Speed Built-In RC Oscillation Mode Operation     |      |

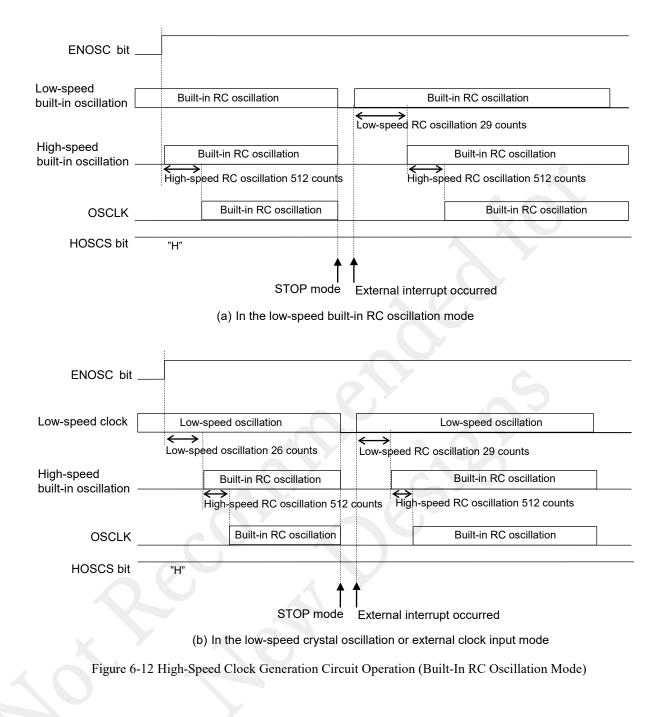

|    |       | 6.3.2.5     | High-Speed Crystal/Ceramic Oscillation Mode Operation |      |

|    |       | 6.3.2.6     | 5 1 1                                                 |      |

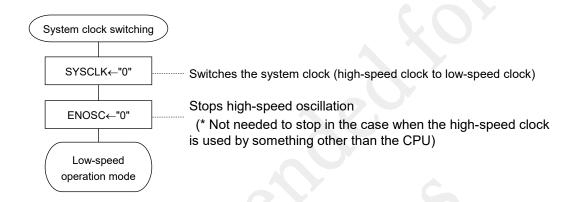

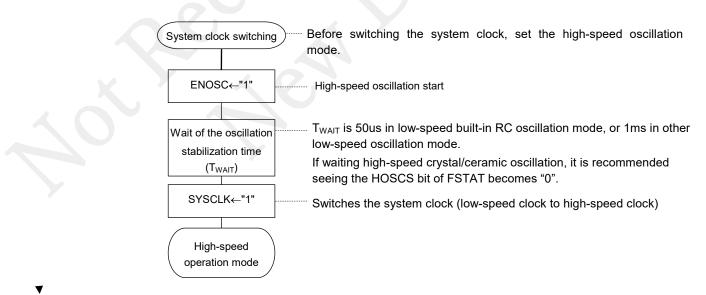

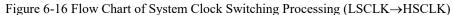

|    |       |             | ching of System Clock                                 |      |

|    |       | 6.3.4 Low   | -speed oscillation clock switch interrupt             | 6-26 |

|    |      | 6.3.4  | Low-speed oscillation clock switch interrupt                        | 6-26 |

|----|------|--------|---------------------------------------------------------------------|------|

|    |      |        |                                                                     |      |

|    |      | Chapt  |                                                                     |      |

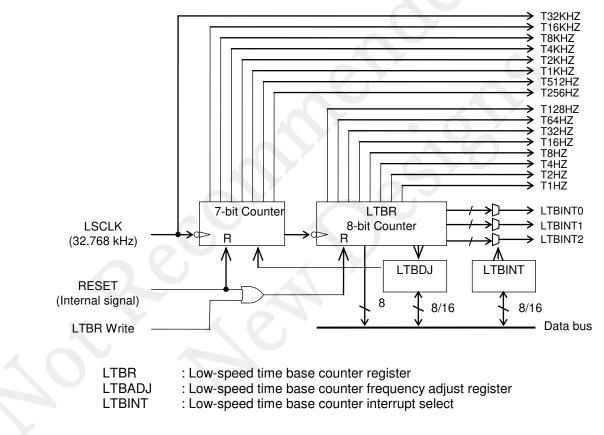

| 7. | Time | Base C | Counter                                                             | 7-1  |

|    | 7.1  | Overv  | riew                                                                | 7-1  |

|    |      | 7.1.1  | Features                                                            | 7-1  |

|    |      |        | Configuration                                                       |      |

|    | 7.2  | Descr  | iption of Registers                                                 | 7-2  |

|    |      | 7.2.1  | List of Registers                                                   | 7-2  |

|    |      |        | Low-Speed Time Base Counter (LTBR)                                  |      |

|    |      | 7.2.3  | Low-Speed Time Base Counter Frequency Adjustment Registers (LTBADJ) | 7-4  |

|    |      | 7.2.4  | Low-Speed Time Base Counter Interrupt select Registers (LTBINT)     | 7-6  |

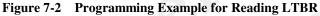

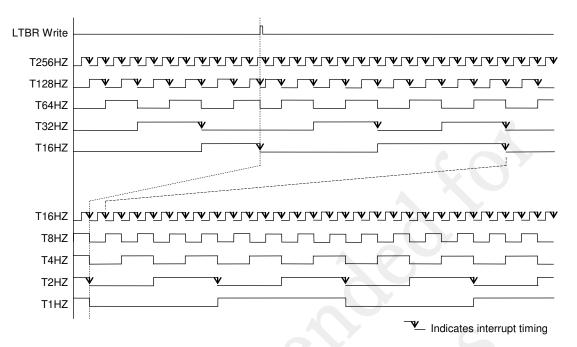

|    | 7.3  | Descr  | iption of Operation                                                 | 7-7  |

|    |      |        | Low-Speed Time Base Counter                                         |      |

|    |      |        | •                                                                   |      |

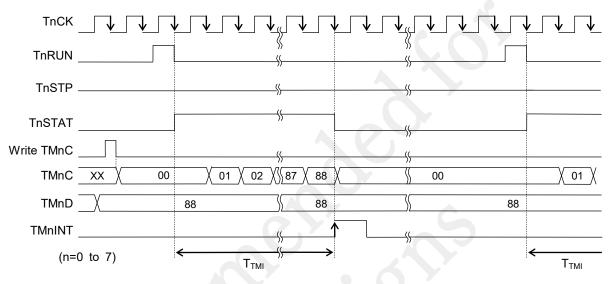

| 8. | Timer | rs8      | -1 |

|----|-------|----------|----|

|    | 8.1   | Overview | -1 |

|     | 8.1.1 | Features                                                              |  |

|-----|-------|-----------------------------------------------------------------------|--|

|     | 8.1.2 | Configuration                                                         |  |

| 8.2 |       | iption of Registers                                                   |  |

|     |       | List of Registers                                                     |  |

|     |       | Timer n Data Register (TMnmD : {n,m}={0,1}, {2,3}, {4,5}, {6,7})      |  |

|     |       | Timer n Counter Register (TMnmC : {n,m}={0,1}, {2,3}, {4,5}, {6,7})   |  |

|     |       | Timer n Control Register (TMnmCON : {n,m}={0,1}, {2,3}, {4,5}, {6,7}) |  |

|     |       | Timer Start Register 0 (TMSTR0)                                       |  |

|     |       | Timer Stop Register 0 (TMSTP0)                                        |  |

|     |       | Timer Status Register 0 (TMSTAT0)                                     |  |

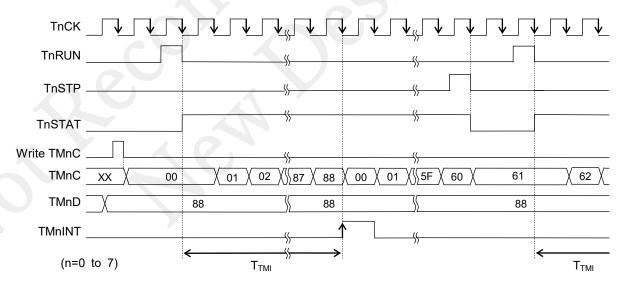

| 8.3 |       | iption of operation                                                   |  |

|     |       | Normal timer mode operation                                           |  |

|     | 8.3.2 | One shot timer mode operation                                         |  |

|     |       | 16bit timer mode                                                      |  |

|     | 8.3.4 | Restriction                                                           |  |

|    |      |                                                                             | 0-10 |

|----|------|-----------------------------------------------------------------------------|------|

| Ch | apte | ar Q                                                                        |      |

|    | Eupo | tion Timer (FTM)                                                            | 0.1  |

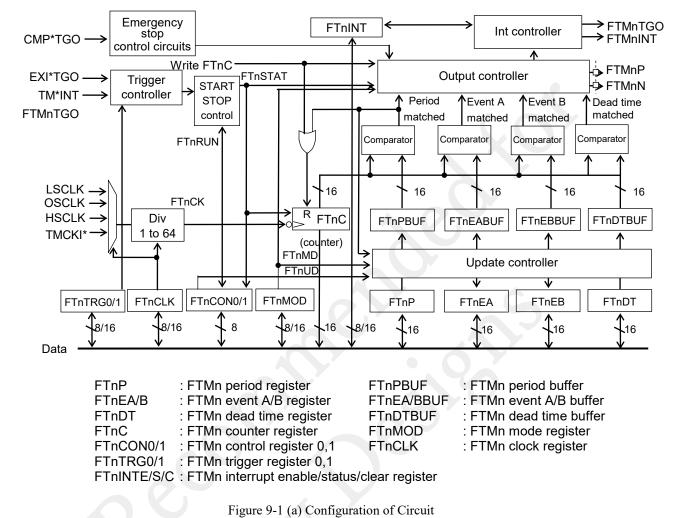

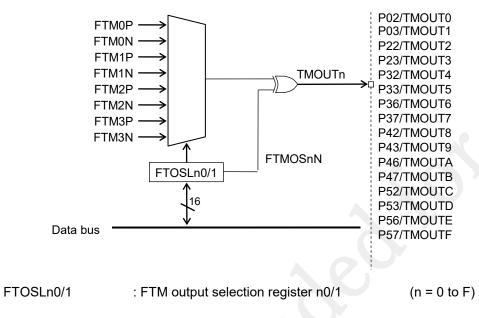

| 9. | 9.1  | General Description                                                         | 9-1  |

|    | 9.1  | 9.1.1 Features                                                              | 0.1  |

|    |      | 9.1.2 Configuration                                                         |      |

|    |      | 9.1.2 Configuration                                                         |      |

|    | 9.2  | Description of Registers                                                    |      |

|    | 0.2  | 9.2.1 List of Registers                                                     |      |

|    |      | 9.2.2 FTMn Period Register (FTnP : n=0,1,2,3)                               | 0 4  |

|    |      | 9.2.3 FTMn Event Register A (FTnEA : n=0,1,2,3)                             |      |

|    |      | 9.2.4 FTMn Event Register B (FTnEB : n=0,1,2,3)                             |      |

|    |      | 9.2.5 FTMn DeadTime Register (FTnDT : n=0,1,2,3)                            |      |

|    |      | 9.2.6 FTMn Counter Register (FTnC : n=0,1,2,3)                              |      |

|    |      | 9.2.7 FTMn Control Register 0 (FTnCON0 : n=0,1,2,3)                         |      |

|    |      | 9.2.8 FTMn Control Register 1 (FTnCON1 : n=0,1,2,3)                         | 9-13 |

|    |      | 9.2.9 FTMn Mode Register (FTnMOD : n=0,1,2,3)                               | 9-15 |

|    |      | 9.2.10 FTMn Clock Register (FTnCLK : n=0,1,2,3)                             |      |

|    |      | 9.2.11 FTMn Trigger Register 0 (FTnTRG0 : n=0,1,2,3)                        |      |

|    |      | 9.2.12 FTMn Trigger Register 1 (FTnTRG1 : n=0,1,2,3)                        | 9-21 |

|    |      | 9.2.13 FTMn Interrupt Enable Register (FTnINTE: n = 0,1,2,3)                | 9-22 |

|    |      | 9.2.14 FTMn Interrupt Status Register (FTnINTS : n=0,1,2,3)                 | 9-24 |

|    |      | 9.2.15 FTMn Interrupt Clear Register (FTnINTC : n=0,1,2,3)                  | 9-26 |

|    |      | 9.2.16 FTM Output nm Select Register (FTOnmSL : n = 0,2,4,6,8,A,C,E, m=n+1) |      |

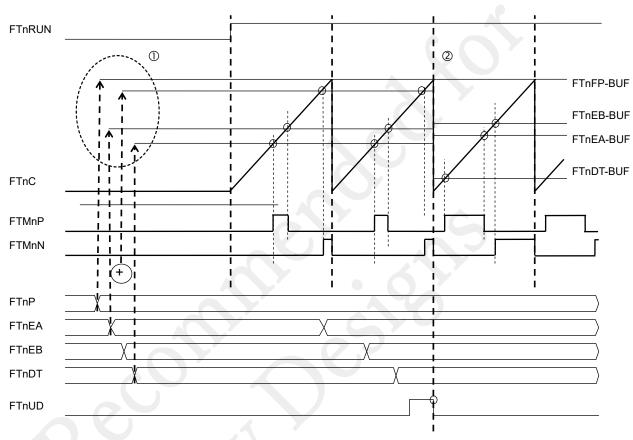

|    | 9.3  | Description of Operation                                                    |      |

|    |      | 9.3.1 Common Sequence                                                       |      |

|    |      | 9.3.2 Counter Operation                                                     |      |

|    |      | 9.3.2.1 Starting/Stopping Counting by Software                              |      |

|    |      | 9.3.2.2 Starting/Stopping Counting by Trigger Event                         | 9-31 |

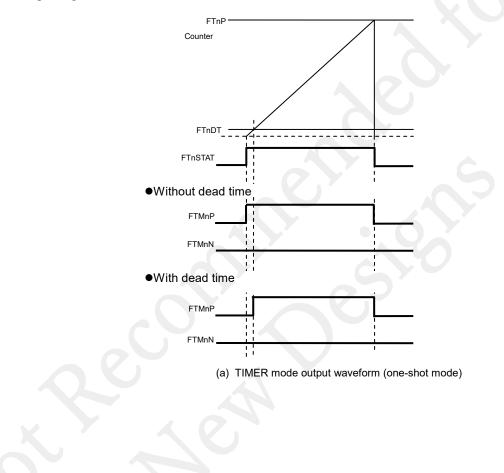

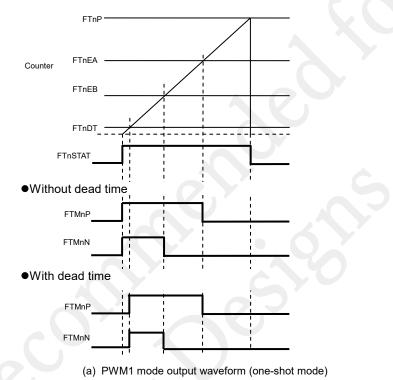

|    |      | 9.3.3 TIMER Mode Operation                                                  |      |

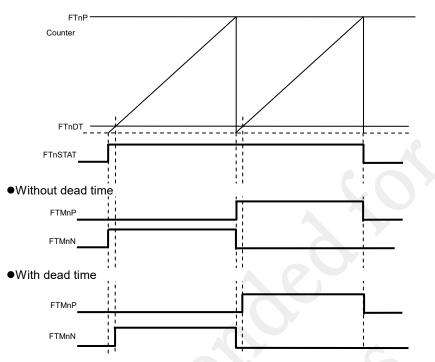

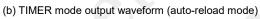

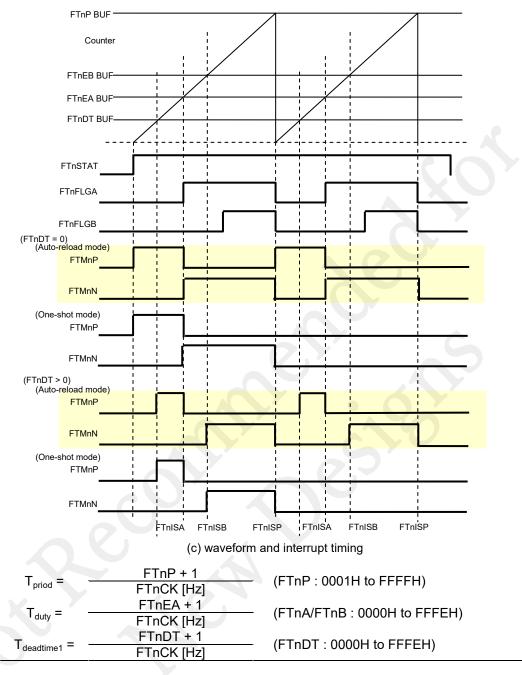

|    |      | 9.3.3.1 Output Waveform in TIMER Mode                                       |      |

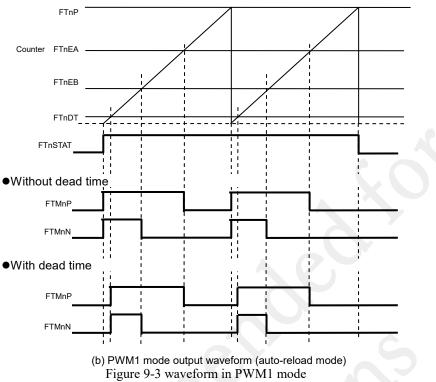

|    |      | 9.3.4 PWM1 Mode Operation                                                   |      |

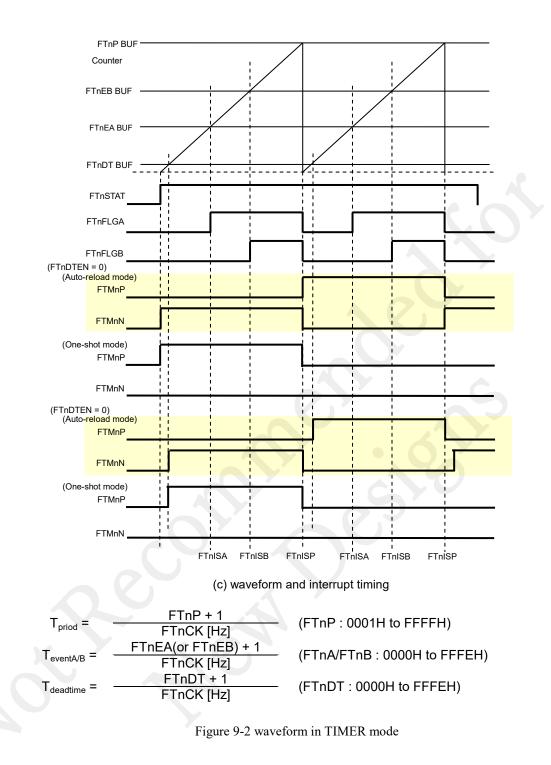

|    |      | 9.3.4.1 Output Waveform in PWM1 Mode                                        |      |

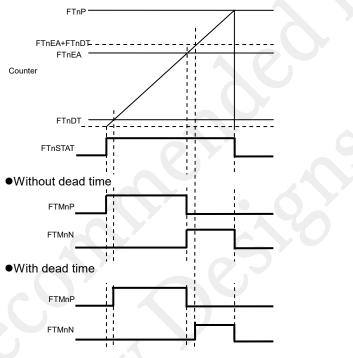

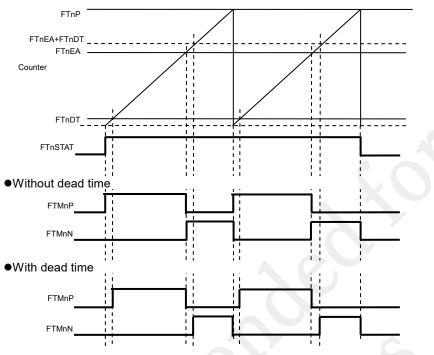

|    |      | 9.3.5 PWM2 Mode Operation                                                   | 9-37 |

|    |      | 9.3.5.1 Output Waveform in PWM2 Mode                                        |      |

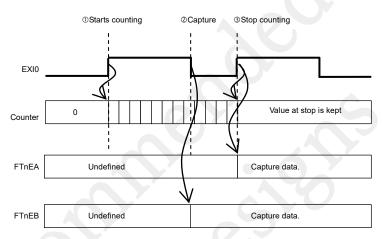

|    |      | 9.3.6 CAPTURE Mode Operation                                                | 9-40 |

|    |      | 9.3.6.1 Measurement Example in the CAPTURE Mode                             |      |

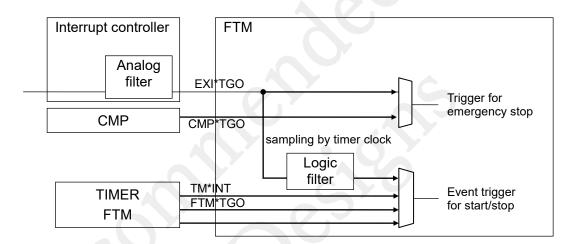

|    |      | 9.3.7 Event/Emergency Stop Trigger Control                                  |      |

|    |      | 9.3.7.1 Trigger Signal                                                      |      |

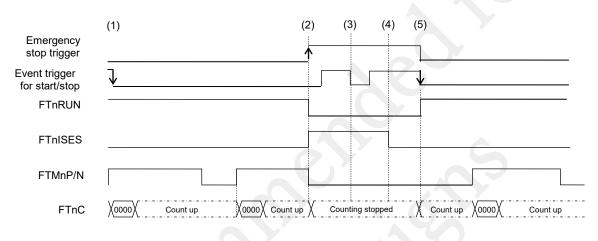

|    |      | 9.3.7.2 Start/Stop Operations by Event Trigger                              | 9-43 |

| 9.3.7.3 Emergency Stop Operation                                 |  |

|------------------------------------------------------------------|--|

| 9.3.8 Output at Counter Stop                                     |  |

| 9.3.9 Changing Period, Event A/B, and Dead Time during Operation |  |

| 9.3.10 Interrupt Source                                          |  |

#### Chapter 10

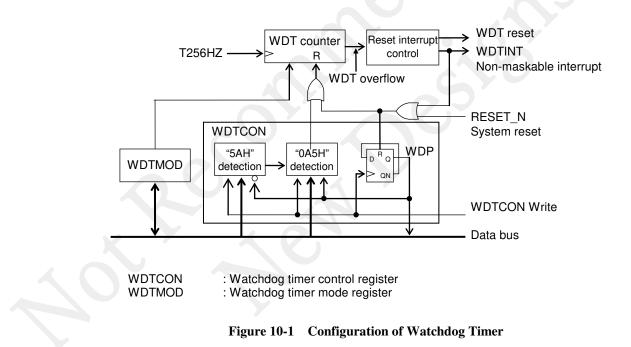

| 10. |                 | imer                                              |  |

|-----|-----------------|---------------------------------------------------|--|

|     | 10.1 Overv      | iew                                               |  |

|     | 10.1.1          | Features                                          |  |

|     | 10.1.2          | Configuration                                     |  |

|     |                 | iption of Registers                               |  |

|     |                 | List of Registers                                 |  |

|     |                 | Watchdog Timer Control Register (WDTCON)          |  |

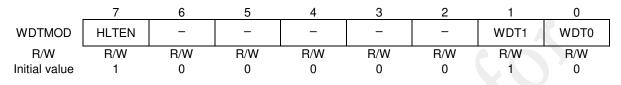

|     |                 | Watchdog Timer Mode Register (WDTMOD)             |  |

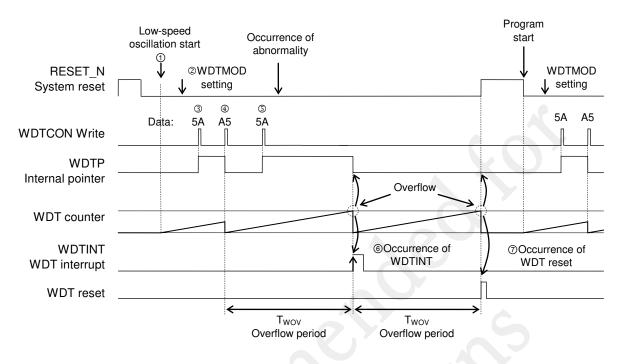

|     |                 | iption of Operation                               |  |

|     | 10.3.1          | The process example when not using Watchdog Timer |  |

|     |                 |                                                   |  |

| Cha | <u>apter 11</u> |                                                   |  |

|     |                 |                                                   |  |

#### Chapter 11

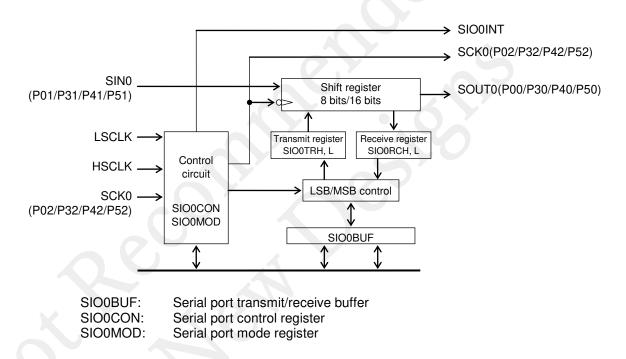

| 11. | Synchronous | s Serial Port                                    |      |

|-----|-------------|--------------------------------------------------|------|

|     | 11.1 Overv  | /iew                                             | 11-1 |

|     | 11.1.1      | Features                                         |      |

|     |             | Configuration                                    |      |

|     | 11.1.3      | List of Pins                                     |      |

|     | 11.2 Descr  | ription of Registers                             | 11-2 |

|     | 11.2.1      | List of Registers                                |      |

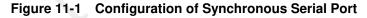

|     | 11.2.2      | Serial Port 0 Transmit/Receive Buffers (SIO0BUF) |      |

|     |             | Serial Port Control Register (SIO0CON)           |      |

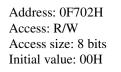

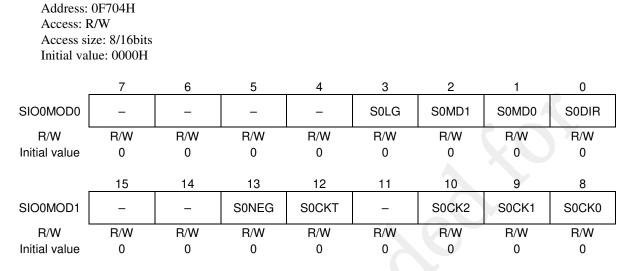

|     |             | Serial Port Mode Register (SIO0MOD)              |      |

|     |             | iption of Operation                              |      |

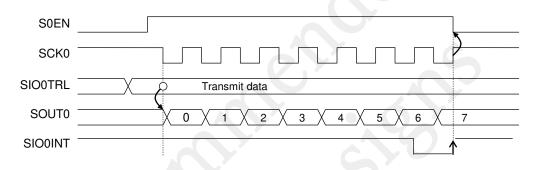

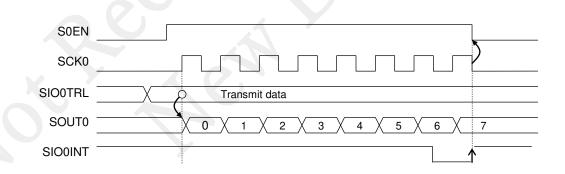

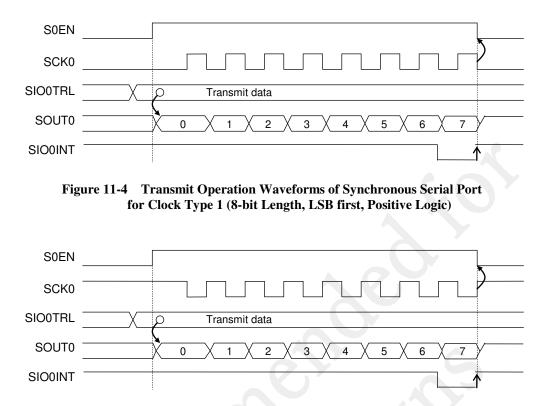

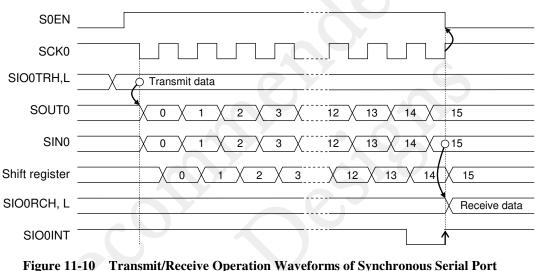

|     | 11.3.1      | Transmit Operation                               |      |

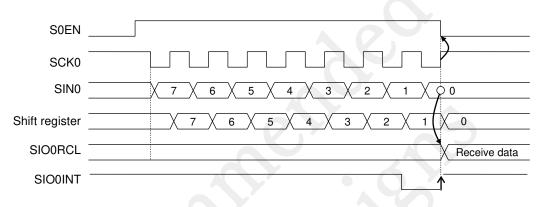

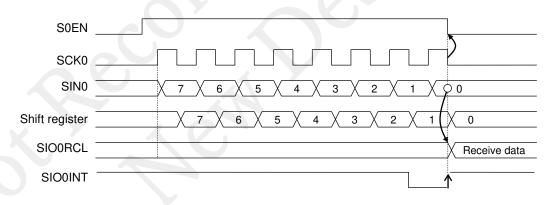

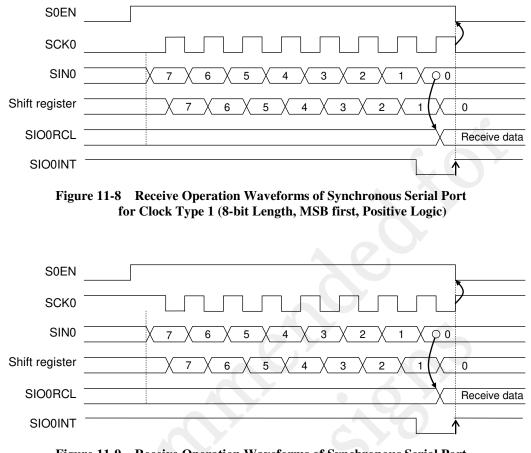

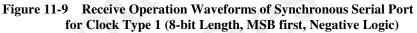

|     | 11.3.2      | Receive Operation                                |      |

|     | 11.3.3      | Transmit/Receive Operation                       |      |

|     |             | Pin Settings                                     |      |

|     |             |                                                  |      |

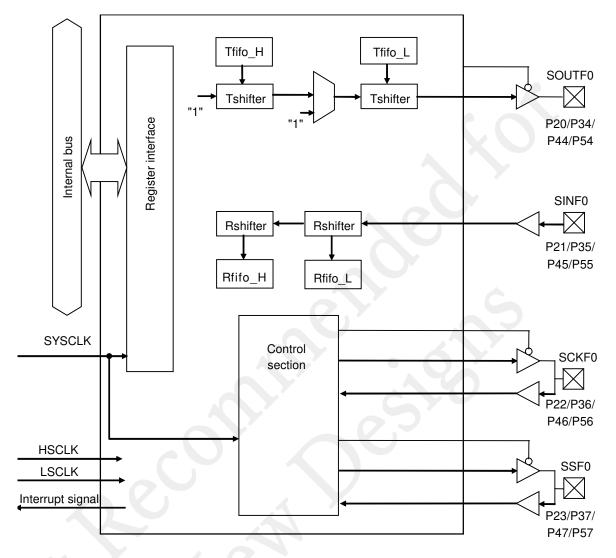

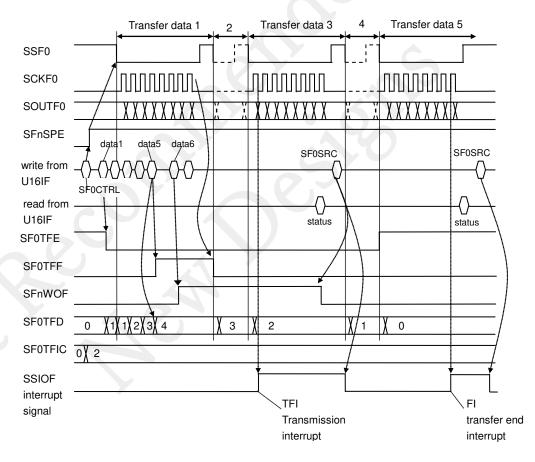

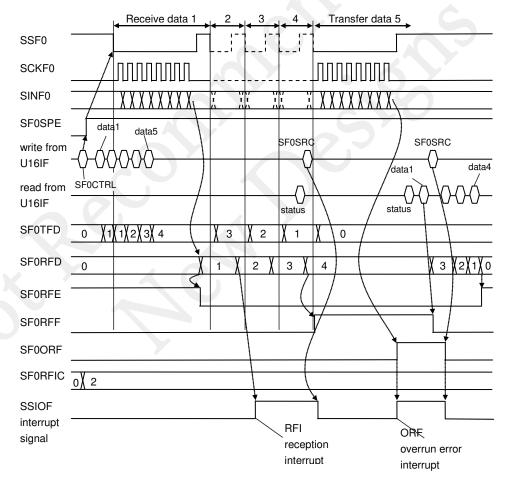

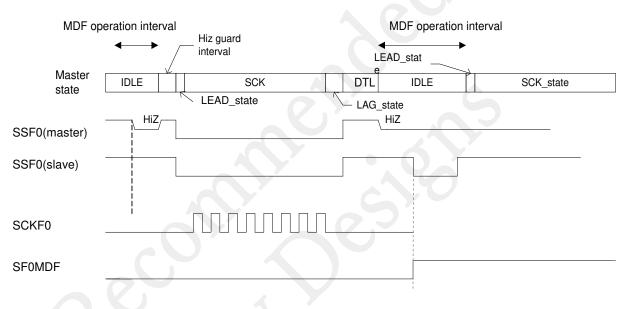

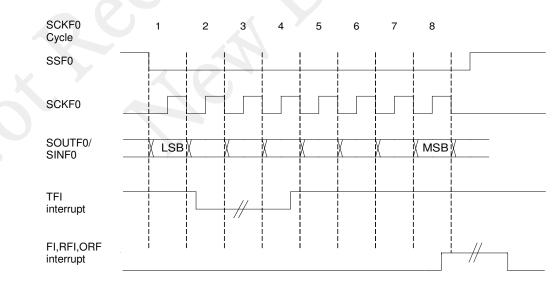

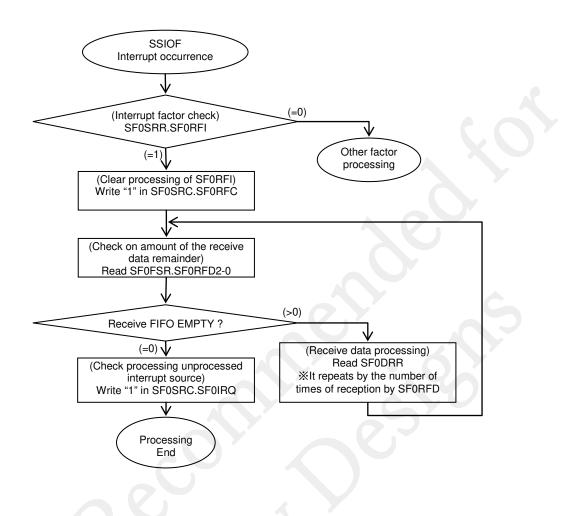

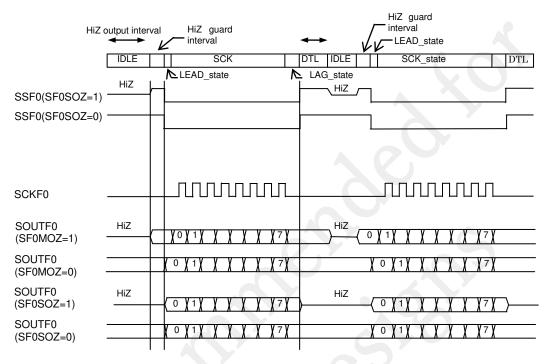

| 12. | Synchronous | s Serial Port with FIFO (SSIOF)                    |       |

|-----|-------------|----------------------------------------------------|-------|

|     | 12.1 Gener  | al Description                                     |       |

|     | 12.1.1      | Features                                           |       |

|     | 12.1.2      | Configuration                                      |       |

|     | 12.1.3      | List of Pins                                       |       |

|     | 12.2 Descr  | iption of Registers                                |       |

|     | 12.2.1      | List of Registers                                  |       |

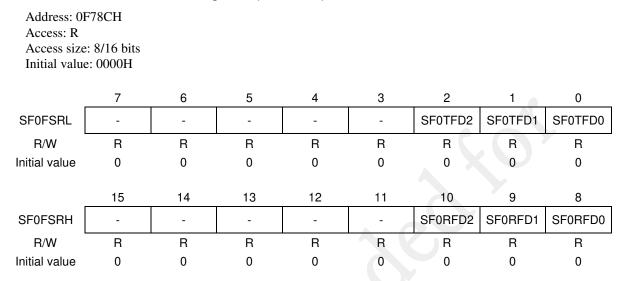

|     | 12.2.2      | SIOF0 Control Register (SF0CTRL)                   |       |

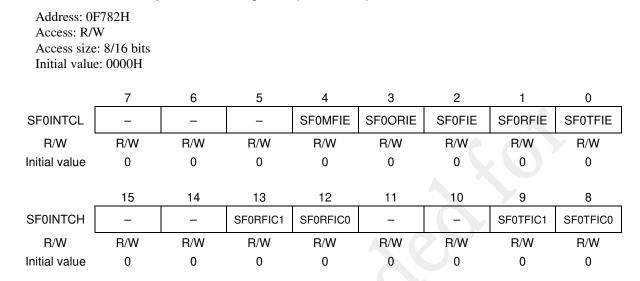

|     | 12.2.3      | SIOF0 Interrupt Control Register (SF0INTC)         |       |

|     | 12.2.4      | SIOF0 Transfer Interval Control Register (SF0TRAC) |       |

|     | 12.2.5      | SIOF0 Baud Rate Register (SF0BRR)                  |       |

|     | 12.2.6      | SIOF0 Status Register (SF0SRR)                     |       |

|     | 12.2.7      | SIOF0 Status Clear Register (SF0SRC)               |       |

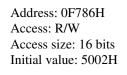

|     | 12.2.8      | SIOF0 FIFO Status Register (SF0FSR)                |       |

|     | 12.2.9      | SIOF0 Write Data Register (SF0DWR)                 |       |

|     | 12.2.10     | SIOF0 Read Data Register (SF0DRR)                  |       |

|     | 12.3 Descr  | iption of Operation                                |       |

|     |             | Master Mode and Slave Mode                         |       |

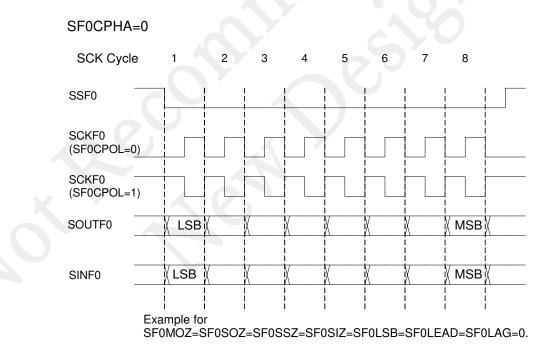

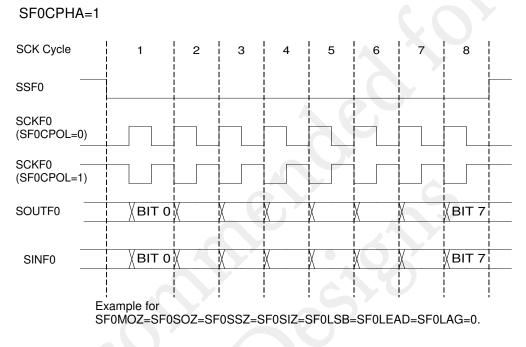

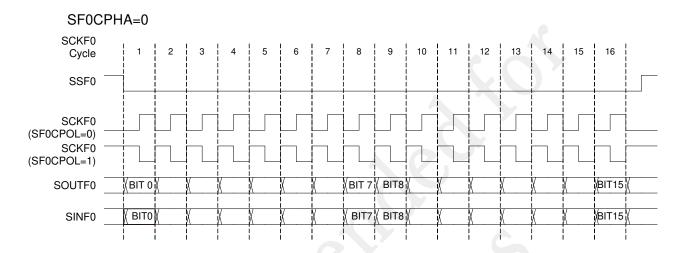

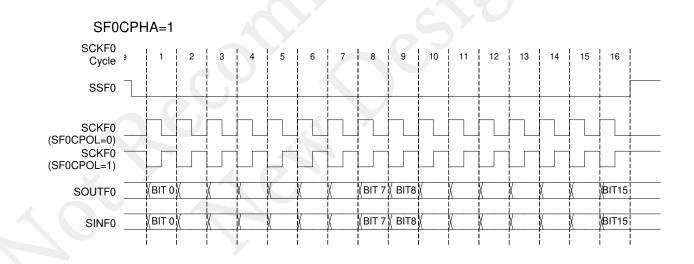

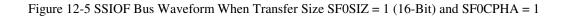

|     | 12.3.2      | Control of Polarity and Phase of Serial Clock      | 12-19 |

|     |             |                                                    |       |

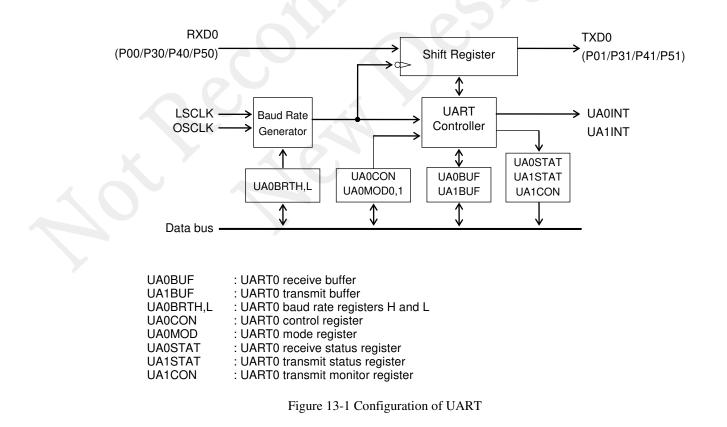

| 13. |            |                                          |  |

|-----|------------|------------------------------------------|--|

|     | 13.1 Gener | ral Description                          |  |

|     | 13.1.1     | Features                                 |  |

|     | 13.1.2     | Configuration                            |  |

|     |            | List of Pins                             |  |

|     | 13.2 Descr | iption of Registers                      |  |

|     | 13.2.1     | List of Registers                        |  |

|     | 13.2.2     | UART0 Receive Buffer (UA0BUF)            |  |

|     | 13.2.3     | UART0 Transmit Buffer (UA1BUF)           |  |

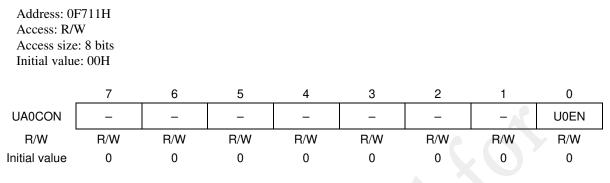

|     | 13.2.4     | UART0 Control Register (UA0CON)          |  |

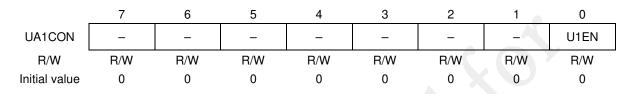

|     | 13.2.5     | UART0 Transmit Monitor Register (UA1CON) |  |

|     | 13.2.6     | UART0 Mode Register (UA0MOD)             |  |

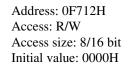

|     | 13.2.7     | UART0 Baud Rate Registers (UA0BRT)       |  |

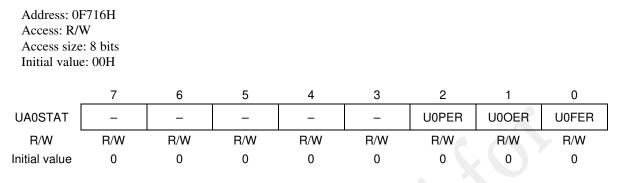

|     | 13.2.8     | UART0 Receive Status Register (UA0STAT)  |  |

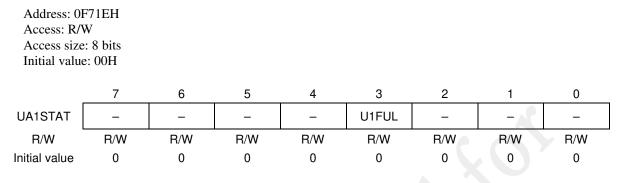

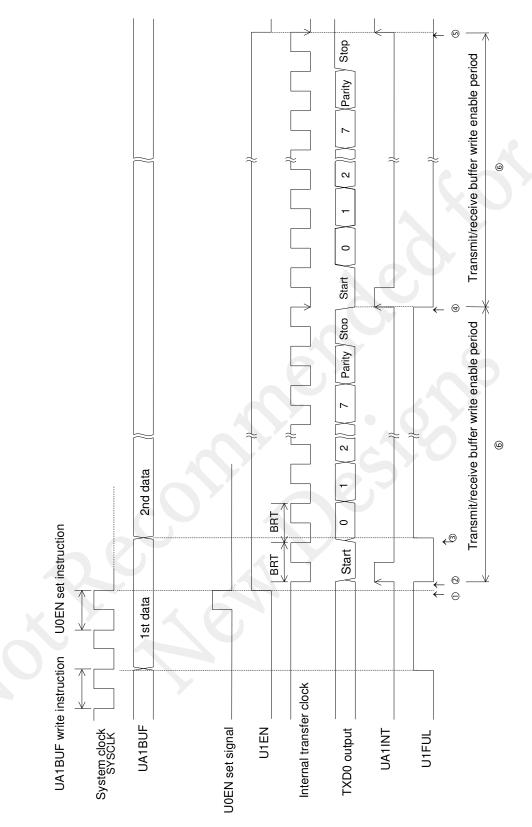

|     | 13.2.9     | UART0 Transmit Status Register (UA1STAT) |  |

|     |            | iption of Operation                      |  |

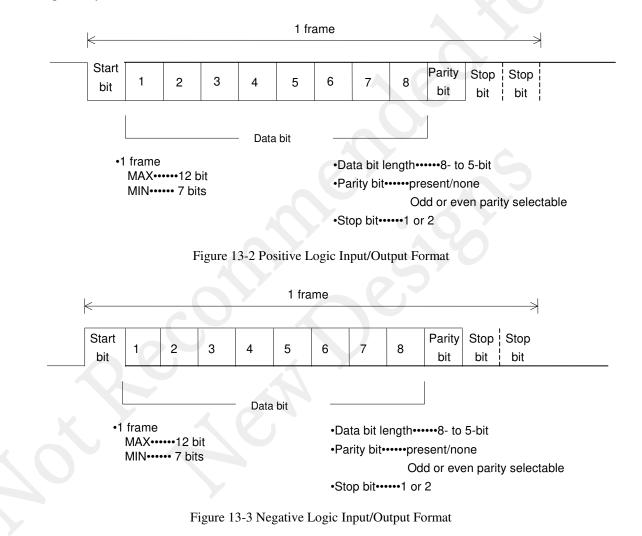

|     | 13.3.1     | Transfer Data Format                     |  |

|     | 13.3.2     | Baud Rate                                |  |

|     | 13.3.3     | Transmitted Data Direction               |  |

|     | 13.3.4     | Transmit Operation                       |  |

|     |            | Receive Operation                        |  |

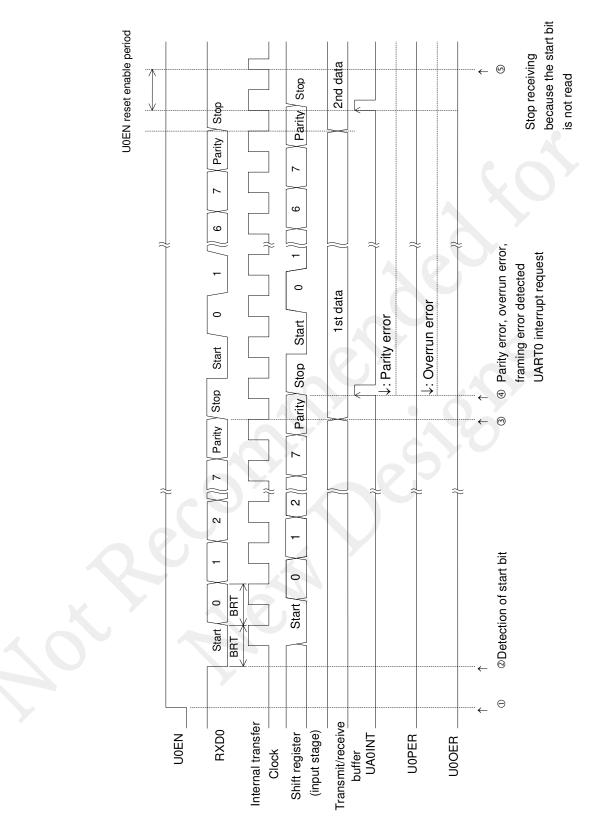

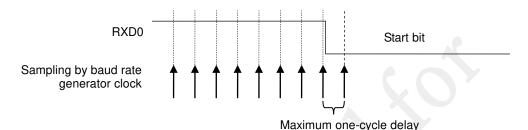

|     |            | 3.3.5.1 Detection of Start Bit           |  |

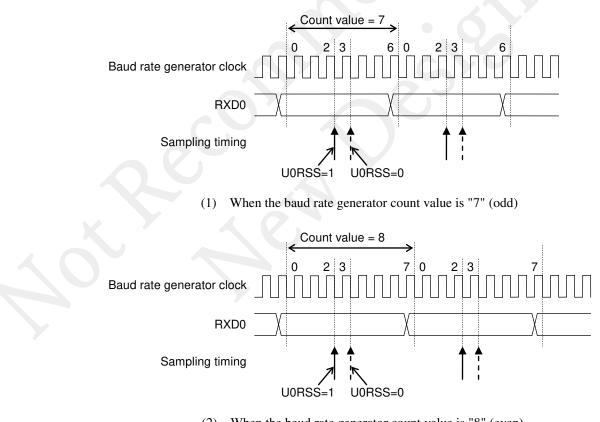

|     |            | 3.3.5.2 Sampling Timing                  |  |

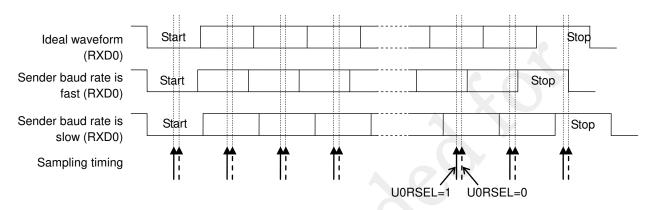

|     | 13         | 3.3.5.3 Receive Margin                   |  |

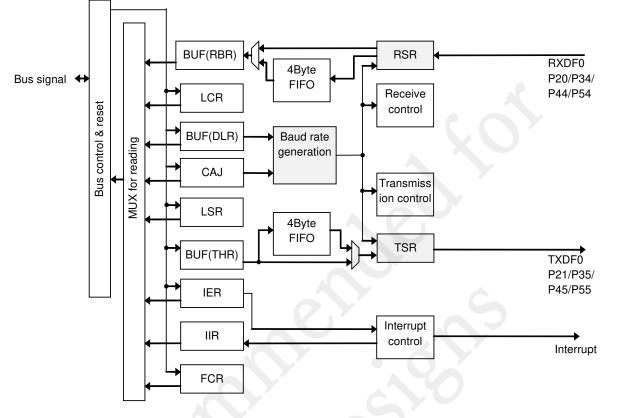

| 14. | UART with FIFO (UARTF)        |  |

|-----|-------------------------------|--|

|     | 14.1 General Description      |  |

|     | 14.1.1 Features               |  |

|     | 14.1.2 Configuration          |  |

|     | 14.1.3 List of Pins           |  |

|     | 14.2 Description of Registers |  |

| 14.2.1          | List of Registers                           |  |

|-----------------|---------------------------------------------|--|

| 14.2.2          | UARTF0 Transmit/Receive Buffer (UAF0BUF)    |  |

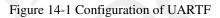

| 14.2.3          | UARTF0 Interrupt Enable Register (UAF0IER)  |  |

| 14.2.4          | UARTF0 Interrupt Status Register (UAF0IIR)  |  |

| 14.2.5          | UARTF0 Mode Register (UAF0MOD)              |  |

| 14.2.6          | UARTF0 Line Status Register (UAF0LSR)       |  |

|                 | UARTF0 Clock Adjustment Register (UAF0CAJ)  |  |

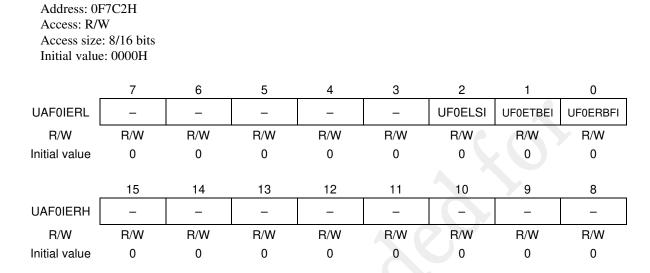

| 14.2.8          | UARTF0 Interrupt Request Register (UAF0IRQ) |  |

|                 | iption of Operation                         |  |

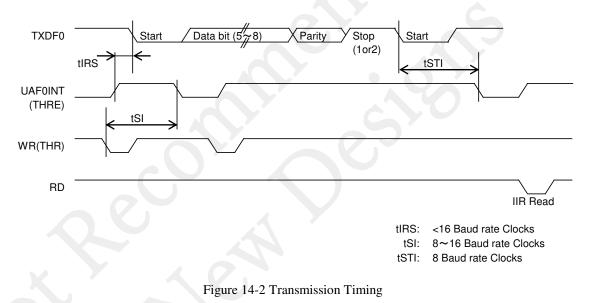

|                 | Data Transmission                           |  |

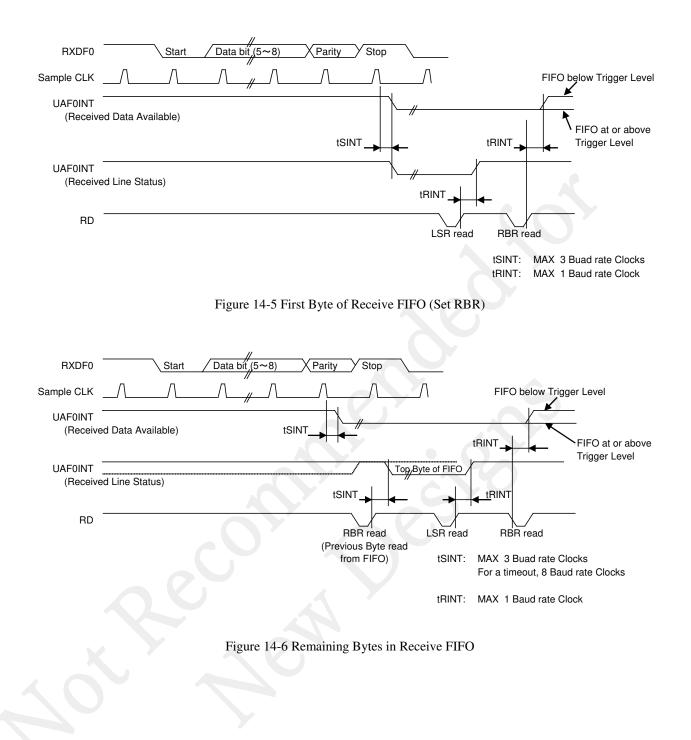

| 14.3.2          | Data Reception                              |  |

|                 | Baud Rate Clock Generation                  |  |

|                 | FIFO Mode                                   |  |

| 14.3.5          | FIFO Polled Mode                            |  |

| 14.3.6          | Error Status                                |  |

| 14.3.7          | Reset By Block Control Register             |  |

|                 |                                             |  |

| <u>apter 15</u> |                                             |  |

| 120 Due lete    |                                             |  |

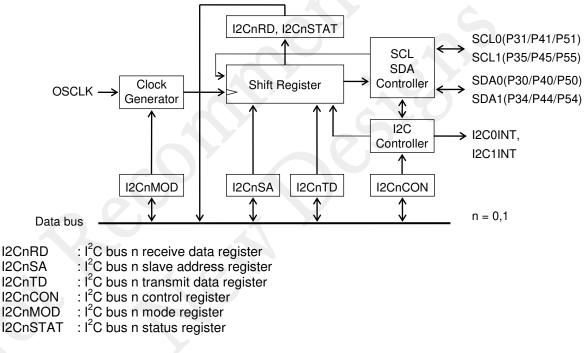

| 15.1 General Description                     |                                         |

|----------------------------------------------|-----------------------------------------|

|                                              |                                         |

|                                              |                                         |

|                                              |                                         |

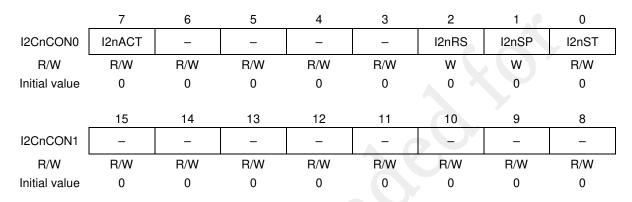

| 15.2 Description of Registers                |                                         |

| 15.2.1 List of Registers                     | 15-2                                    |

|                                              |                                         |

|                                              |                                         |

|                                              |                                         |

|                                              |                                         |

|                                              |                                         |

|                                              |                                         |

|                                              |                                         |

|                                              |                                         |

|                                              |                                         |

|                                              |                                         |

|                                              |                                         |

|                                              |                                         |

|                                              |                                         |

| 15.3.1.6 Control Register Setting Wait State |                                         |

|                                              |                                         |

|                                              |                                         |

|                                              |                                         |

| 15.3.4 Pin Settings                          | 15-16                                   |

|                                              | <ul> <li>15.1.2 Configuration</li></ul> |

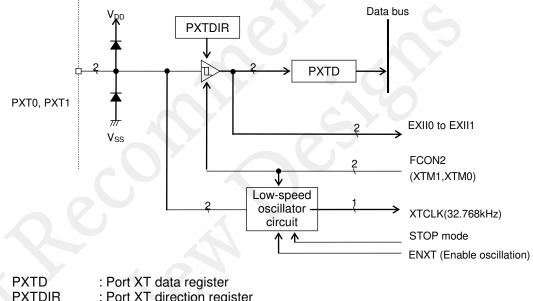

| 16. | Port XT    |                                     |  |

|-----|------------|-------------------------------------|--|

|     | 16.1 Gener | ral Description                     |  |

|     | 16.1.1     | Features                            |  |

|     | 16.1.2     | Configuration                       |  |

|     | 16.1.3     | List of Pins                        |  |

|     | 16.2 Descr | ription of Registers                |  |

|     | 16.2.1     | List of Registers                   |  |

|     | 16.2.2     | Port XT Data Register (PXTD)        |  |

|     | 16.2.3     | Port XT Direction Register (PXTDIR) |  |

#### ML620Q503H/Q504H User's Manual Contents

| 16.3 | Descri | ption of Operation                     | 16-5 |

|------|--------|----------------------------------------|------|

|      | 16.3.1 | Input Port Function                    | 16-5 |

|      | 16.3.2 | Primary Function Other Than Input Port | 16-5 |

#### Chapter 17

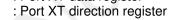

| 17. | Port0      |                                               |       |

|-----|------------|-----------------------------------------------|-------|

|     | 17.1 Overv | iew                                           |       |

|     | 17.1.1     | Features                                      | 17-1  |

|     | 17.1.2     | Configuration                                 |       |

|     | 17.1.3     | List of Pins                                  |       |

|     | 17.2 Descr | iption of Registers                           |       |

|     |            | List of Registers                             |       |

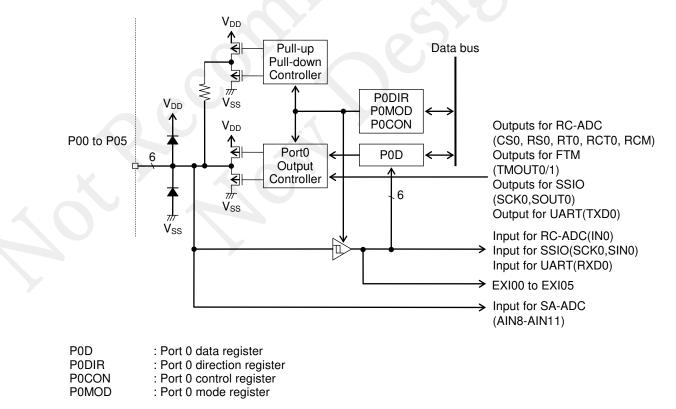

|     | 17.2.2     | Port 0 Data Register (P0D)                    |       |

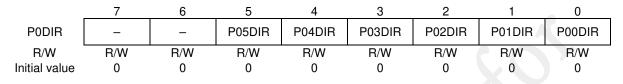

|     | 17.2.3     | Port 0 Direction Register (P0DIR)             | 17-5  |

|     | 17.2.4     | Port 0 Control Registers (P0CON)              | 17-6  |

|     | 17.2.5     | Port 0 Mode Registers (P0MOD).                |       |

|     | 17.3 Descr | iption of Operation                           |       |

|     |            | Input/Output Port Functions                   |       |

|     | 17.3.2     | Primary Function except for Input/Output Port | 17-10 |

|     |            | Secondary ,Tertiary and Fourthly Functions    |       |

|     |            |                                               |       |

#### Chapter 18

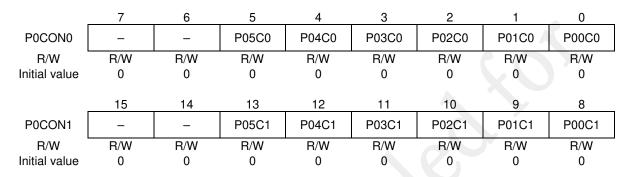

| 18. | Port1      |                                   |      |

|-----|------------|-----------------------------------|------|

|     |            | /iew                              |      |

|     | 18.1.1     | Features                          |      |

|     | 18.1.2     | Configuration                     |      |

|     | 18.1.3     | List of Pins                      |      |

|     | 18.2 Descr | iption of Registers               |      |

|     | 18.2.1     | List of Registers                 |      |

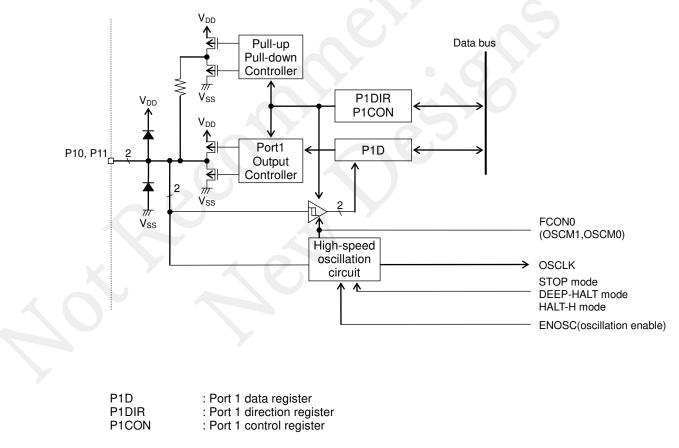

|     | 18.2.2     | Port 1 Data Register (P1D)        |      |

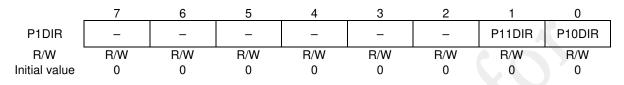

|     |            | Port 1 Direction Register (P1DIR) |      |

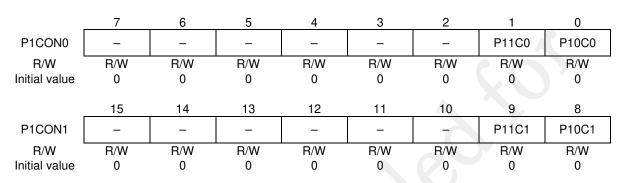

|     |            | Port 1 Control Registers (P1CON)  |      |

|     | 18.3 Descr | iption of Operation               |      |

|     |            | Input/Output Port Function        |      |

|     |            | Other Function                    |      |

|     |            |                                   |      |

| Cha | apter 19   |                                   |      |

|     | Dort2      |                                   | 10.1 |

| Port2      |                                                                                                                                                      |                          |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 19.1 Overv | <i>r</i> iew                                                                                                                                         |                          |

| 19.1.1     | Features                                                                                                                                             |                          |

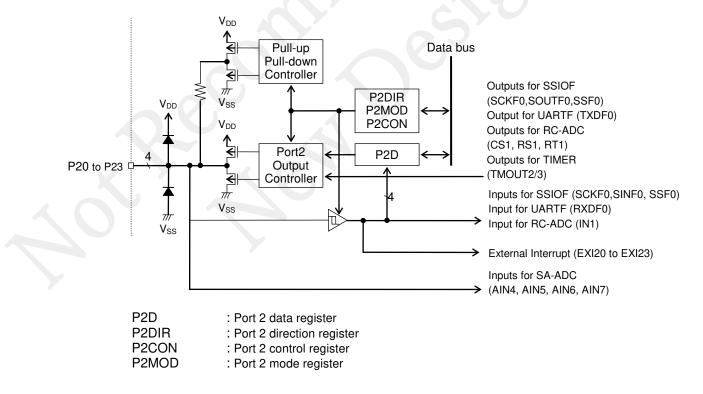

| 19.1.2     | Configuration                                                                                                                                        |                          |

| 19.1.3     | List of Pins                                                                                                                                         |                          |

|            |                                                                                                                                                      |                          |

| 19.2.1     | List of Registers                                                                                                                                    |                          |

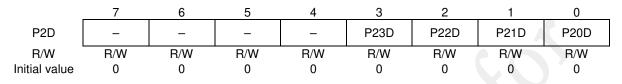

| 19.2.2     | Port 2 Data Register (P2D)                                                                                                                           |                          |

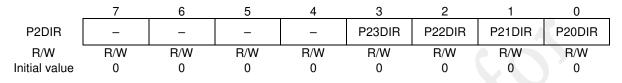

| 19.2.3     | Port 2 Direction Register (P2DIR)                                                                                                                    |                          |

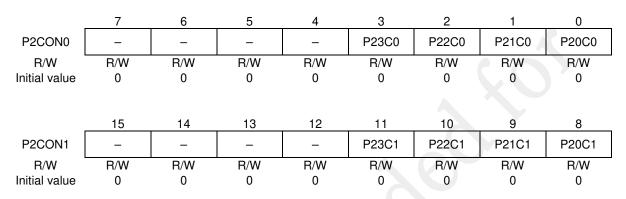

| 19.2.4     | Port 2 Control Registers (P2CON)                                                                                                                     |                          |

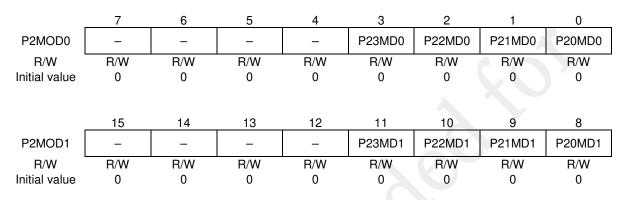

| 19.2.5     | Port 2 Mode Registers (P2MOD)                                                                                                                        |                          |

| 19.3 Descr | iption of Operation                                                                                                                                  |                          |

| 19.3.1     | Input/Output Port Functions                                                                                                                          |                          |

|            |                                                                                                                                                      |                          |

|            |                                                                                                                                                      |                          |

|            | 19.1 Overv<br>19.1.1<br>19.1.2<br>19.1.3<br>19.2 Descr<br>19.2.1<br>19.2.2<br>19.2.3<br>19.2.4<br>19.2.5<br>19.3 Descr<br>19.3.1<br>19.3.1<br>19.3.2 | <ul> <li>Port2</li></ul> |

#### Chapter 20 20. Port 2

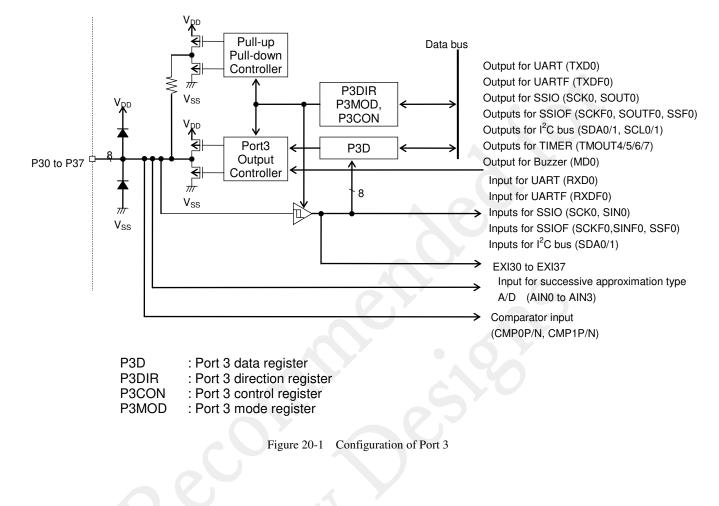

| 20. | Port 3     |                                               |  |

|-----|------------|-----------------------------------------------|--|

|     | 20.1 Gener | ral Description                               |  |

|     | 20.1.1     | Features                                      |  |

|     | 20.1.2     | Configuration                                 |  |

|     | 20.1.3     | List of Pins                                  |  |

|     | 20.2 Descr | iption of Registers                           |  |

|     | 20.2.1     | List of Registers                             |  |

|     | 20.2.2     | Port 3 Data Register (P3D)                    |  |

|     | 20.2.3     | Port 3 Direction Register (P3DIR)             |  |

|     | 20.2.4     | Port 3 Control Register (P3CON)               |  |

|     |            | Port 3 Mode Register (P3MOD)                  |  |

|     | 20.3 Descr | iption of Operation                           |  |

|     | 20.3.1     | Input/Output Port Functions                   |  |

|     |            | Primary Function Other Than Input/Output Port |  |

|     |            | Secondary to Quartic Functions                |  |

## Chapter 21

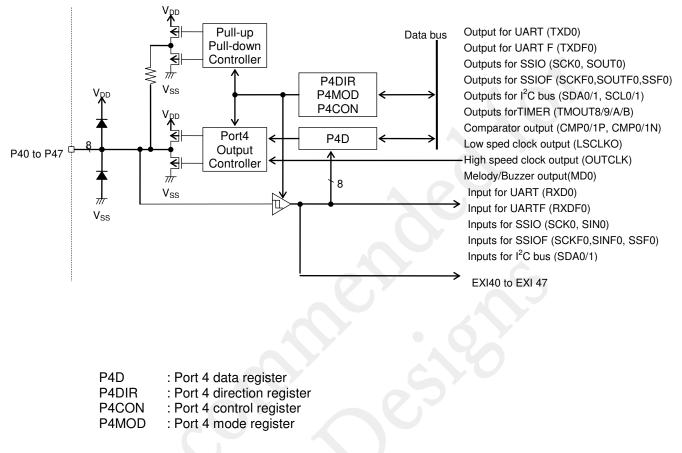

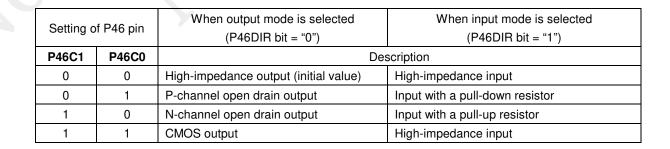

| 21. | Port 4     |                                               |  |

|-----|------------|-----------------------------------------------|--|

|     | 21.1 Gener | ral Description                               |  |

|     | 21.1.1     | Features                                      |  |

|     | 21.1.2     | Configuration                                 |  |

|     | 21.1.3     | List of Pins                                  |  |

|     | 21.2 Descr | iption of Registers                           |  |

|     | 21.2.1     | List of Registers                             |  |

|     | 21.2.2     | Port 4 Data Register (P4D)                    |  |

|     | 21.2.3     | Port 4 Direction Register (P4DIR)             |  |

|     | 21.2.4     | Port 4 Control Register (P4CON)               |  |

|     | 21.2.5     | Port 4 Mode Register (P4MOD)                  |  |

|     | 21.3 Descr | iption of Operation                           |  |

|     | 21.3.1     | Input/Output Port Functions                   |  |

|     | 21.3.2     | Primary Function Other Than Input/Output Port |  |

|     | 21.3.3     | Secondary to Quartic Functions                |  |

|     |            |                                               |  |

## Chapter 22

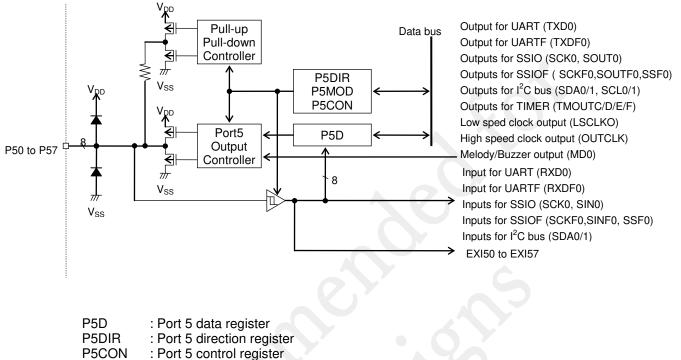

| 22. | Port 5     |                                               |  |

|-----|------------|-----------------------------------------------|--|

|     | 22.1 Gener | ral Description                               |  |

|     | 22.1.1     | Features                                      |  |

|     |            | Configuration                                 |  |

|     | 22.1.3     | List of Pins                                  |  |

|     | 22.2 Descr | iption of Registers                           |  |

|     | 22.2.1     | List of Registers                             |  |

|     | 22.2.2     | Port 5 Data Register (P5D)                    |  |

|     | 22.2.3     | Port 5 Direction Register (P5DIR)             |  |

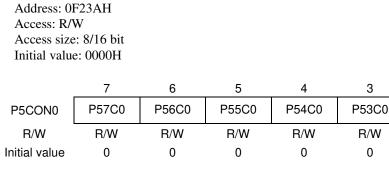

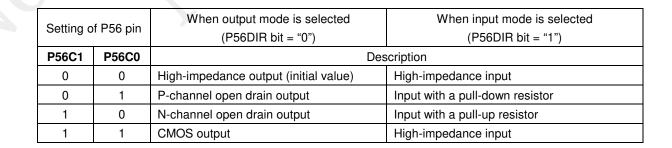

|     | 22.2.4     | Port 5 Control Register (P5CON)               |  |

|     | 22.2.5     | Port 5 Mode Register (P5MOD)                  |  |

|     | 22.3 Descr | iption of Operation                           |  |

|     | 22.3.1     | Input/Output Port Functions                   |  |

|     | 22.3.2     | Primary Function Other Than Input/Output Port |  |

|     | 22.3.3     | Secondary to Quartic Functions                |  |

|     |            |                                               |  |

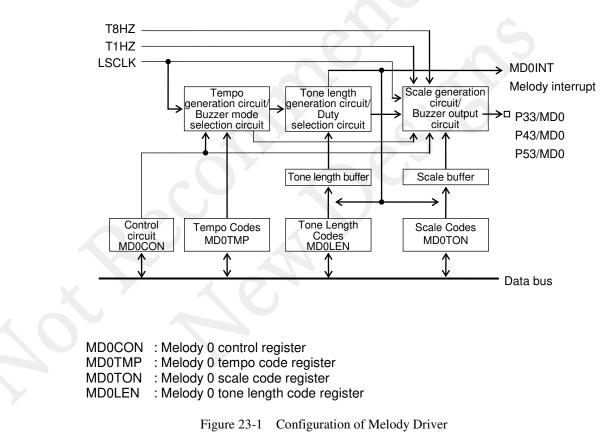

| 23.1 Ove | erview                                             |      |

|----------|----------------------------------------------------|------|

| 23.1.    | 1 Features                                         |      |

| 23.1.    | 2 Configuration                                    |      |

|          | 3 List of Pins                                     |      |

| 23.2 Des | scription of Registers                             |      |

| 23.2.    | 1 List of Registers                                |      |

| 23.2.    | 2 Melody 0 Control Register (MD0CON)               |      |

| 23.2.    |                                                    |      |

| 23.2.    | 4 Melody 0 Scale/Tone Length Code Register (MD0TL) |      |

| 23.3 Des | scription of Operation                             |      |

| 23.3.    |                                                    |      |

| 23.3.    | 2 Example of Using Melody Circuit                  |      |

| 23.3.    | 3 Tempo Codes                                      |      |

| 23.3.    |                                                    |      |

| 23.3.    |                                                    |      |

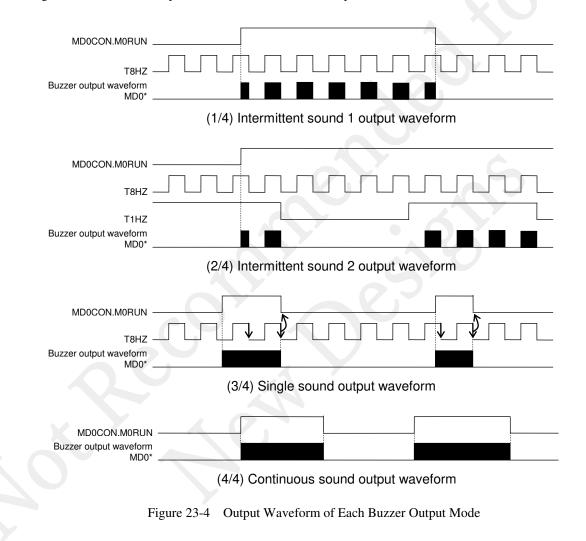

| 23.3.    | 6 Operations of Buzzer Output                      |      |

|          |                                                    |      |

| apter 24 |                                                    |      |

|          |                                                    | 04.4 |

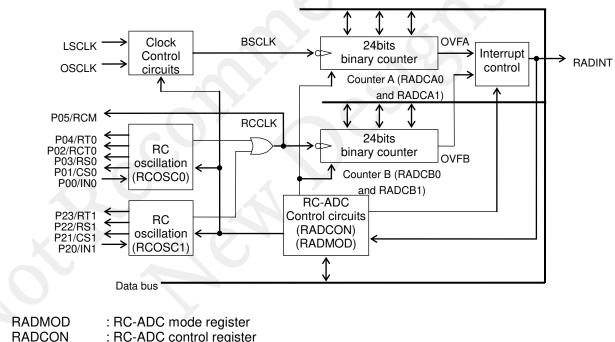

| 24. | RC Oscillation | on Type A/D Converter (RC-ADC)                      |  |

|-----|----------------|-----------------------------------------------------|--|

|     |                | ral Description                                     |  |

|     |                | Features                                            |  |

|     | 24.1.2         | Configuration                                       |  |

|     |                | List of Pins                                        |  |

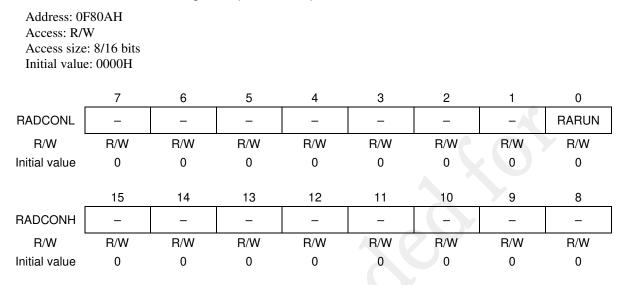

|     | 24.2 Descr     | iption of Registers                                 |  |

|     | 24.2.1         | List of Registers                                   |  |

|     | 24.2.2         | RC-ADC Counter A Register 0 (RADCA0)                |  |

|     | 24.2.3         | RC-ADC Counter A Register 1 (RADCA1)                |  |

|     | 24.2.4         | RC-ADC Counter B Register 0 (RADCB0)                |  |

|     | 24.2.5         | RC-ADC Counter B Register 1 (RADCB1)                |  |

|     | 24.2.6         | RC-ADC Mode Register (RADMOD)                       |  |

|     | 24.2.7         | RC-ADC Control Register (RADCON)                    |  |

|     | 24.3 Descr     | iption of Operation                                 |  |

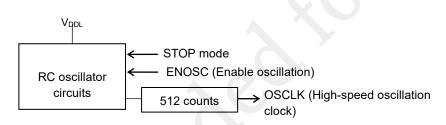

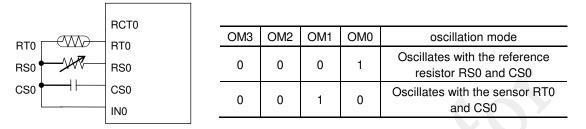

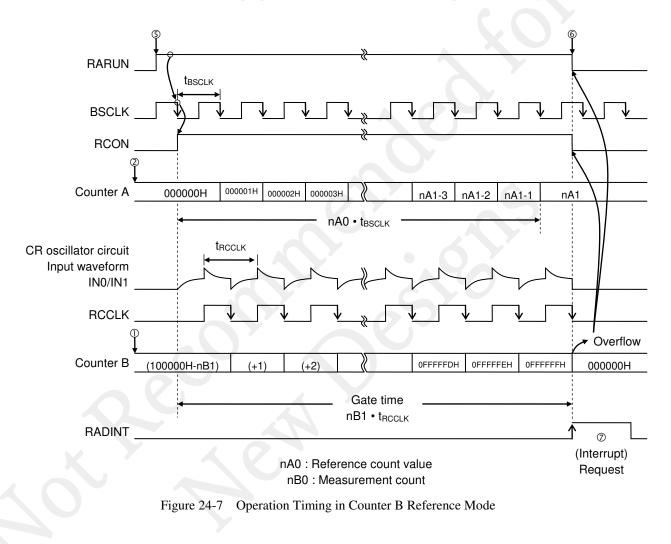

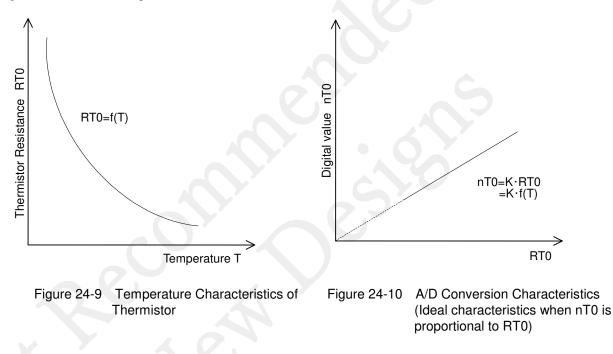

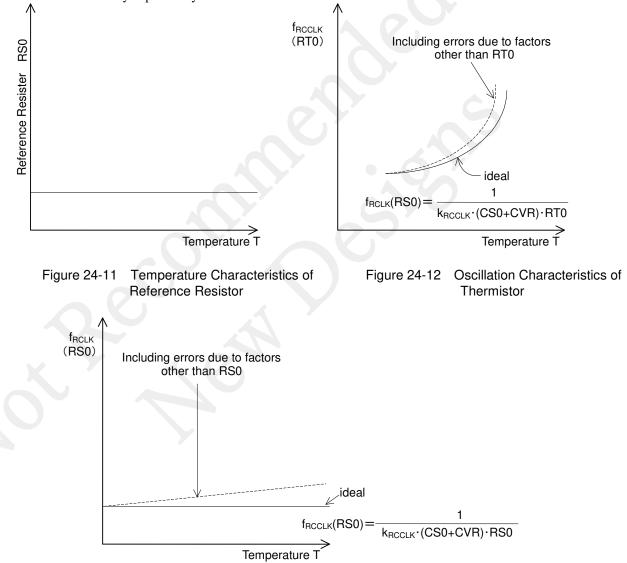

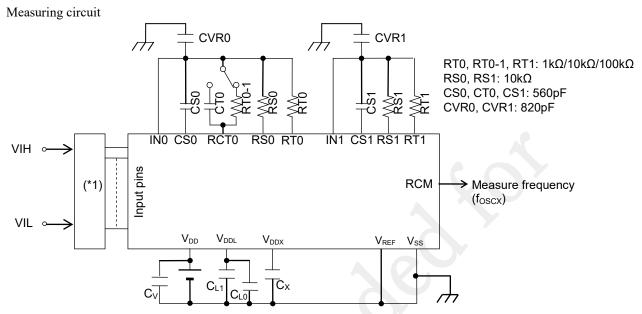

|     | 24.3.1         | RC Oscillator Circuits                              |  |

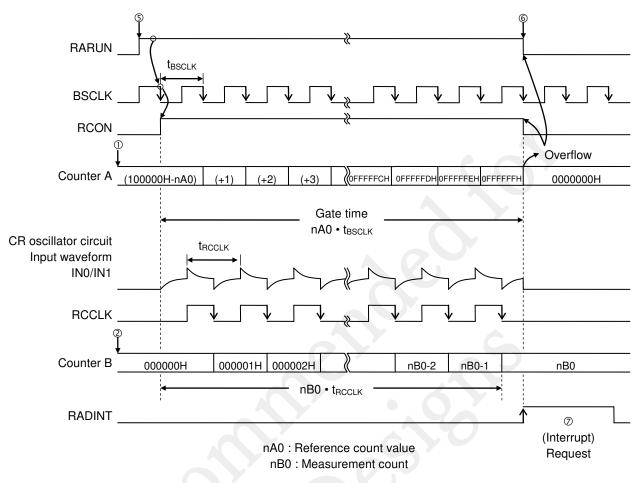

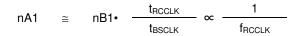

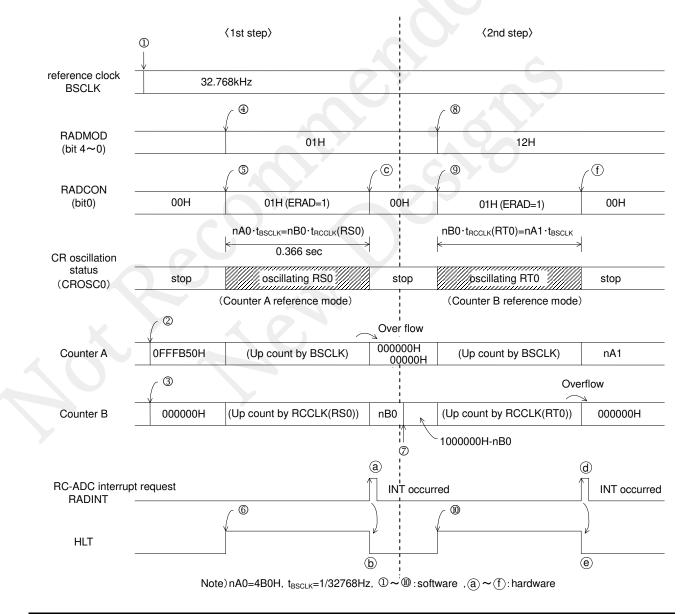

|     | 24.3.2         | Counter A/B Reference Modes                         |  |

|     | 24.3.3         | Example of Use of RC Oscillation Type A/D Converter |  |

|     | 24.3.4         | Monitoring RC Oscillation                           |  |

|     |                |                                                     |  |

| Ch  | apter 25   |                                                 |  |

|-----|------------|-------------------------------------------------|--|

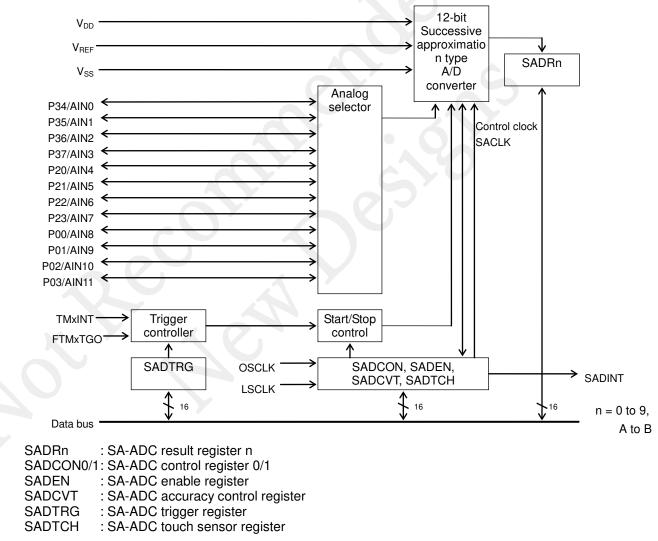

| 25. |            | Approximation Type A/D Converter (SA-ADC)       |  |

|     |            | ral Description                                 |  |

|     | 25.1.1     |                                                 |  |

|     | 25.1.2     | Configuration                                   |  |

|     | 25.1.3     | List of Pins                                    |  |

|     | 25.2 Descr | iption of Registers                             |  |

|     |            | List of Registers                               |  |

|     | 25.2.2     | SA-ADC Result Register n (SADRn) n=0 to 9, A, B |  |

|     | 25.2.3     | SA-ADC Control Register 0(SADCON0)              |  |

|     | 25.2.4     | SA-ADC Control Register1 (SADCON1)              |  |

|     | 25.2.5     | SA-ADC Enable Register (SADEN)                  |  |

|     | 25.2.6     | SA-ADC Touch Sensor Register (SADTCH)           |  |

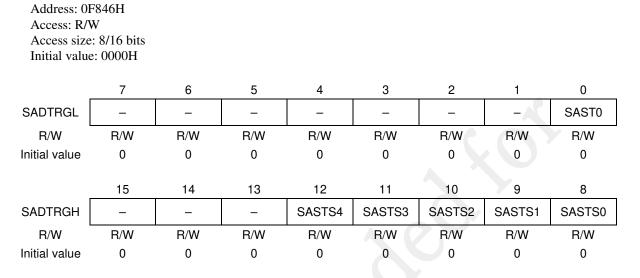

|     | 25.2.7     | SA-ADC Trigger Register (SADTRG)                |  |

|     | 25.2.8     | SA-ADC Accuracy Control Register (SADCVT)       |  |

|     | 25.3 Descr | iption of Operation                             |  |

|     | 25.3.1     | Setting of A/D Conversion Channels              |  |

|     |            |                                                 |  |

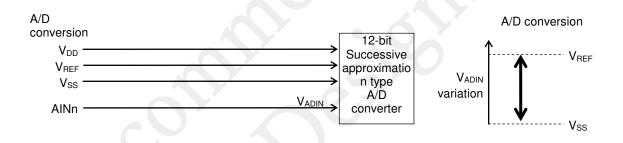

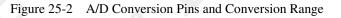

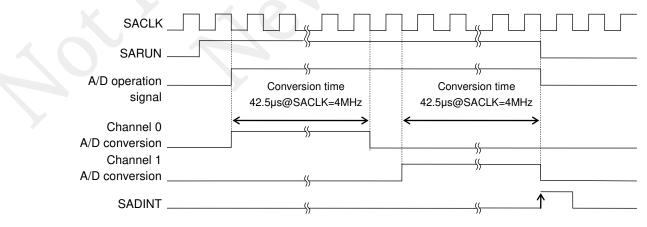

| 25.3.2 | Operation of the Successive Approximation Type A/D Converter | 25-14 |

|--------|--------------------------------------------------------------|-------|

| 25.3.3 | Capacitive Touch sensor mode operation                       | 25-15 |

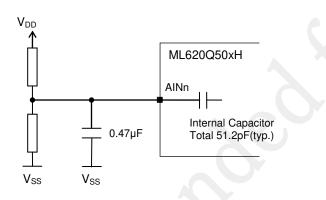

| 25.3.4 | Notes on Use of SA-ADC                                       | 25-16 |

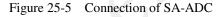

| 26.       | Analog Com      | parator                                         |   |

|-----------|-----------------|-------------------------------------------------|---|

|           | 26.1 Overv      | iew                                             |   |

|           | 26.1.1          | Features                                        |   |

|           | 26.1.2          | Configuration                                   |   |

|           |                 | List of Pins                                    |   |

|           | 26.2 Descr      | iption of Registers                             |   |

|           | 26.2.1          | List of Registers                               |   |

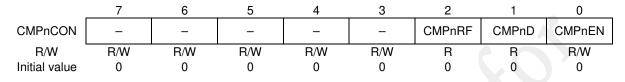

|           | 26.2.2          | Comparator n Control Register (CMPnCON : n=0,1) |   |

|           |                 | Comparator n mode Registers (CMPnMOD : n=0,1)   |   |

|           | 26.3 Functi     | ion description                                 |   |

|           | 26.3.1          | Comparator function                             |   |

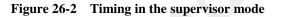

|           | 26.3.2          | Supervisor mode                                 |   |

|           | 26.3.3          | Single mode                                     |   |

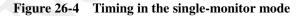

|           | 26.3.4          | Single monitor mode                             |   |

|           |                 | C C C C C C C C C C C C C C C C C C C           |   |

| <u>Ch</u> | <u>apter 27</u> |                                                 |   |

|           |                 |                                                 | · |

#### Chapter 27

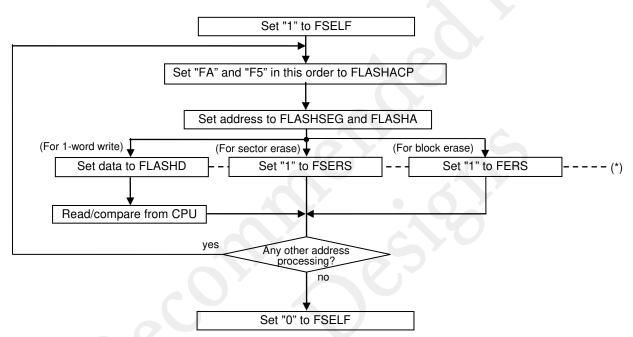

| 27. | Flash Memo | ry Control                           |  |

|-----|------------|--------------------------------------|--|

|     | 27.1 Gener | ral Description                      |  |

|     | 27.1.1     |                                      |  |

|     | 27.2 Descr | iption of Registers                  |  |

|     | 27.2.1     |                                      |  |

|     | 27.2.2     | Flash Address Register (FLASHA)      |  |

|     | 27.2.3     | Flash Data Register (FLASHD)         |  |

|     | 27.2.4     |                                      |  |

|     | 27.2.5     |                                      |  |

|     | 27.2.6     | Flash Segment Register (FLASHSEG)    |  |

|     | 27.2.7     | Flash Self Register (FLASHSLF)       |  |

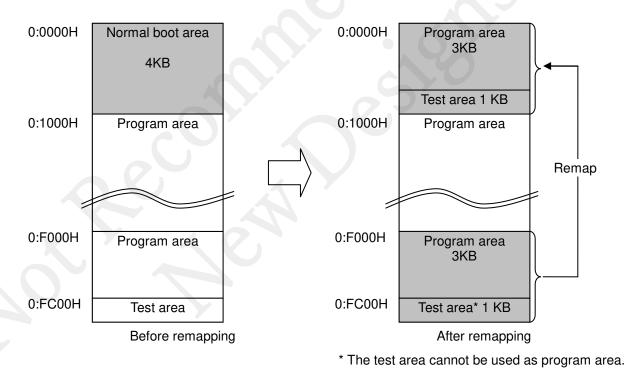

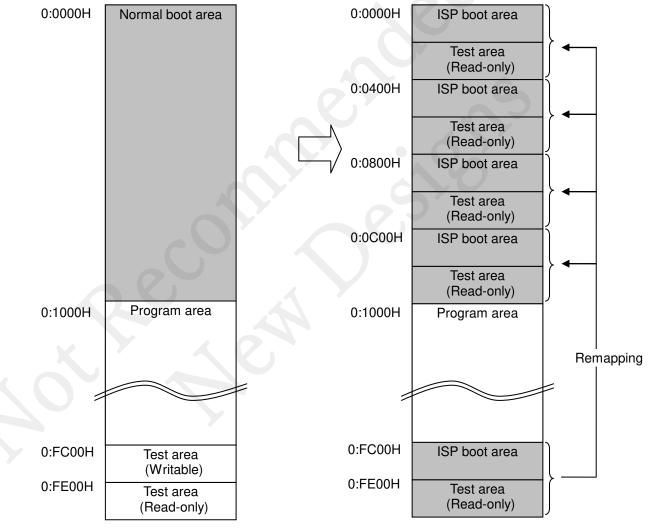

|     | 27.2.8     | Remap Address Register (REMAPADD)    |  |

|     | 27.3 Descr | iption of Operation                  |  |

|     | 27.3.1     |                                      |  |

|     | 27.3.2     |                                      |  |

|     | 27.3.3     | -                                    |  |

|     | 27.3.4     |                                      |  |

|     | 27.3.5     |                                      |  |

|     | 27.3.6     | Notes of the program after remapping |  |

|     | 27.3.7     |                                      |  |

|     |            |                                      |  |

## Chapter 29

| 29. | LLD circuit                   | 29-1 |

|-----|-------------------------------|------|

|     | 29.1 General Description      |      |

|     | 29.1.1 Features               |      |

|     | 29.2 Description of resister  |      |

|     | 29.3 Description of operation |      |

|     |                               | -• . |

#### Chapter 30 30. On –Chip

| _ |      |                                                |        |

|---|------|------------------------------------------------|--------|

|   |      | Chip Debug Function                            | . 30-1 |

|   |      | Overview                                       |        |

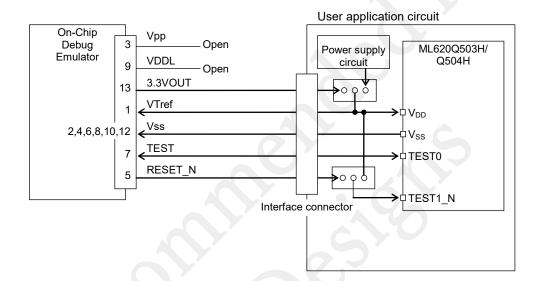

|   | 30.2 | Method of Connecting to On-Chip Debug Emulator | . 30-1 |

|   |      | Flash Memory Rewrite Function                  |        |

|   |      | ,                                              |        |

## **Appendixes**

| Appendix A | Registers                               | <br>A1 |

|------------|-----------------------------------------|--------|

|            |                                         |        |

|            | 0                                       |        |

|            |                                         |        |

|            | · + + · · · · · · · · · · · · · · · · · |        |

#### **Revision History**

| Revision HistoryR1 | ł |

|--------------------|---|

|--------------------|---|

## Overview

#### 1. Overview

#### 1.1 Features

This LSI family is a high-performance 16-bit CMOS microcontroller into which rich peripheral circuits, such as synchronous serial port, UART, I<sup>2</sup>C bus interface (master), supply voltage level detect circuit, RC oscillation type A/D converter, and successive approximation type A/D converter are incorporated around 16-bit CPU nX-U16/100. The CPU nX-U16/100 is capable of efficient instruction execution in 1-instruction 1-clock mode by 3-stage pipe line architecture parallel processing. The Flash ROM\* that is installed as program memory achieves low-voltage low-power consumption operation (read operation) is most suitable for battery-driven applications. And, this LSI has a data flash-memory\* fill area by a software which can be written in.

The on-chip debug function that is installed enables program debugging and programming.

- \*: This product uses SuperFlash® technology licensed from Silicon Storage Technology, Inc. SuperFlash® is a registered trademark of Silicon Storage Technology, Inc.

- CPU

- 16-bit RISC CPU (CPU name: nX-U16/100)

- Instruction system: 16-bit instructions

- Instruction set: Transfer, arithmetic operations, comparison, logic operations, multiplication/division, bit manipulations, bit logic operations, jump, conditional jump, call return stack manipulations, arithmetic shift, and so on

- Build-in On-Chip debug function

- Minimum instruction execution time 30.5 μs (@32.768 kHz system clock) 62.5ns (@16 MHz system clock)

- Built-in coprocessor for multiplication, division, and multiply-accumulate operations

- Signed or unsigned operation setting

- Multiplication: 16bit × 16bit (operation time 4 cycles)

- Division: 32bit / 16bit (operation time 8 cycles)

- Division: 32bit / 32bit (operation time 16 cycles)

- Multiply-accumulate (non-saturating): 16bit × 16bit + 32bit (operation time 4 cycles)

- Multiply-accumulate (saturating): 16bit × 16bit + 32bit (operation time 4 cycles)

- Internal memory

- Supports ISP function (re-writing the program memory area by software)

- Number of segments

| Product name | Flash me         | SRAM          |               |

|--------------|------------------|---------------|---------------|

| Flouuct name | Program area     | Data area     | - SRAIM       |

| ML620Q503H   | 32KB (16K×16bit) | 2KB(1K×16bit) | 2KB(1K×16bit) |

| ML620Q504H   | 64KB (32K×16bit) | 2KB(1K×16bit) | 6KB(3K×16bit) |

\*\*: including 1KB of unusable test area

- Interrupt controller (INTC)

- 1 non-maskable interrupt sources (Internal source: 1)

- 37 maskable interrupt sources (Internal sources: 29, External sources: 8)

- Software interrupt (SWI): maximum 64 sources

- External interrupts and comparator allow edge selection and sampling selection

- Priority level (4-level) can be set for each interrupt

- Time base counter (TBC)

- Low-speed time base counter × 1 channel

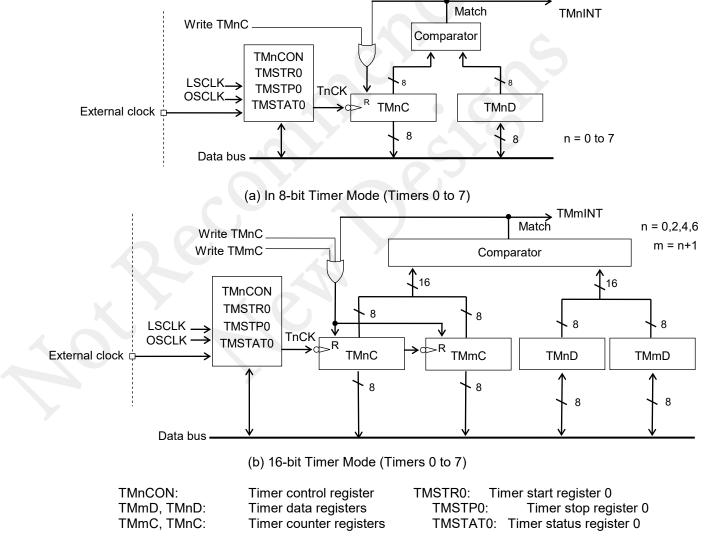

- Timers (TMR)

- -8 bits  $\times 8$  channels

- (Timer0-7: 16-bit × 4 configuration available by using Timer0-1 or Timer2-3, Timer4-5, Timer6-7)

- Selection of one shot timer mode is possible

- External clock can be selected as timer clock.

- Function Timers (FTM)

- -16-bit  $\times 4$  channels

- Equipped with the timer/capture/PWM functions using a 16-bit counter

- Timer start/stop function by software/event trigger(external pin or other timer)

- External pin can be selected as counter clock

- Capture function (the measurement such as the pulse width is possible using external trigger input)

- Two types of PWM with the same period and different duties and complementary PWM with the dead time set can be output.

- Watchdog timer (WDT)

- Non-maskable interrupt and reset

- Free running

- Overflow period: 4 types selectable (125ms, 500ms, 2s, and 8s when LSCLK = 32.768 kHz)

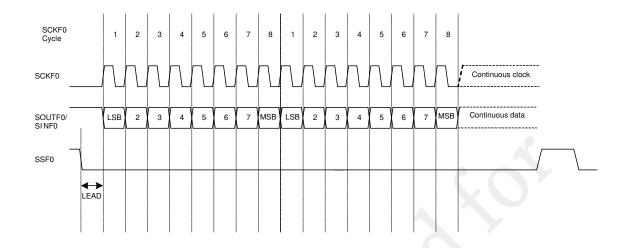

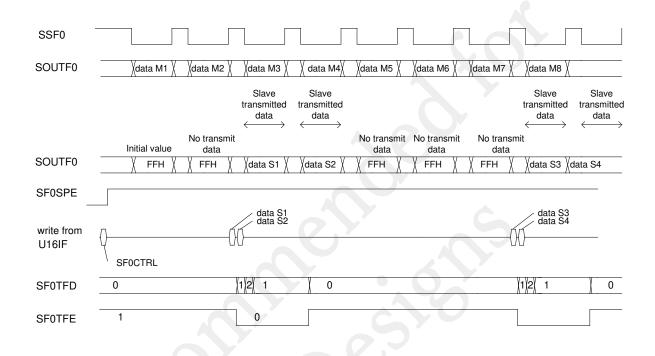

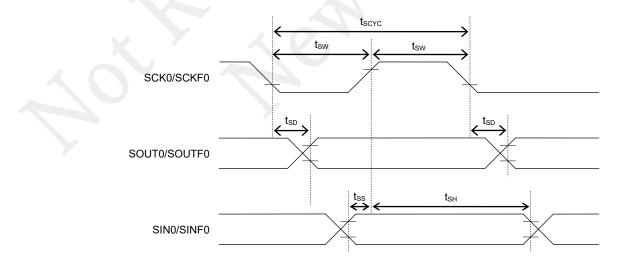

- Synchronous serial port (SSIOF/ SSIO)

- without FIFOs (SSIO) : 1 channel

- with 4-byte transmits and receives FIFOs (SSIOF) : 1 channel

- Master/slave are selectable

- LSB first/MSB first are selectable

- 8-bit length/16-bit length are selectable

- Phase/Polarity of clock are selectable

- supports slave-select signal (only SSIOF)

- UART (UARTF/ UART)

- without FIFOs (UART) : 1ch

- with 4-byte transmits and receives FIFOs (UARTF) : 1ch

- Full duplex buffer system

- Communication speed: Settable within the range of 2400bps to 115200bps.

- Programmable interface (data length, parity, stop bits are selectable)

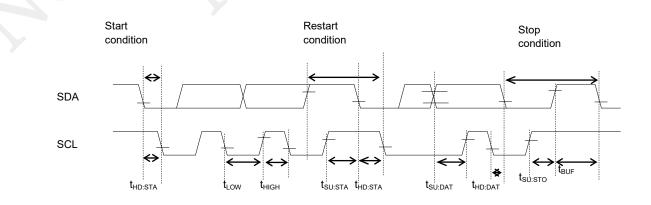

- I<sup>2</sup>C bus interface (I<sup>2</sup>C)

- Master function × 2 channel

- Fast mode (400 kbps), standard mode (100 kbps)

- General-purpose ports (PORT)

Input port x 2, Input/output port × 36 channels

- Melody driver (MELODY)

- Tempo: 15 types

- Scale: 29 types (Melody sound frequency: 508 Hz to 10.922 kHz)

- Tone length: 63 types

- Buzzer output mode (4 output modes, 8 buzzer frequencies, 7duty levels at 4.096kHz/15 duty levels at other buzzer frequencies)

- RC oscillation type A/D converter (RC-ADC)

- Time division  $\times$  2 channels

- 24-bit counter

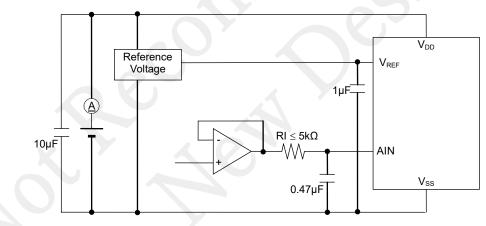

- Successive approximation type A/D converter (SA-ADC)

- Input  $\times$  12 channels

- 12-bit A/D converter

- Starting by trigger of Timer/FTM function.

- Capacitive touch sense function

- Analog Comparator (CMP)

- Input  $\times$  2 ch

- Common mode input voltage: 0.2V to  $V_{DD}$  0.2V

- Input offset voltage: 30mV(max)

- Interrupt allow edge selection and sampling selection are selectable

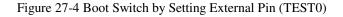

- Voltage Level Supervisor (VLS)

- Threshold voltages: selectable from 13 levels

- interrupt or reset generate are selectable

- Low Level Detector(LLD)

- Judgment Voltage: 1.8V±0.2V

- Usable as low level detection reset

- Reset

- Reset by the RESET\_N pin

- Reset by power-on detection

- Reset by overflow of watchdog timer (WDT)

- Reset by Voltage Level Supervisor(VLS)

- Reset by Low Level Detector(LLD)

- Clock

- Low-speed clock: (This LSI can not guarantee the operation without low-speed clock)

- Crystal oscillation (32.768 kHz)

- External clock input (30kHz to 36kHz)

- Built-in RC oscillation (32.768kHz)

- High-speed clock:

- Crystal/Ceramic oscillation (16 MHz)

- External clock input (2MHz to 16 MHz)

- Built-in RC oscillation (16MHz)

- Power management

- HALT mode: Instruction execution by CPU is suspended. All peripheral circuits can keep in operating states.

- HALT-H mode: Instruction execution by CPU is suspended. Stop of high-speed oscillation automatically. All peripheral circuits can keep in operating states.

- DEEP-HALT mode: Instruction execution by CPU is suspended. Some peripheral circuits(Timer, LTBC etc.) can keep in operating states.

- STOP mode: Stop of low-speed oscillation and high-speed oscillation (Operations of CPU and peripheral circuits are stopped.)

- Clock gear: The frequency of high-speed system clock can be changed by software (1/1, 1/2, 1/4, 1/8,1/16,1/32 of the oscillation clock)

- Block Control Function: Power down (reset registers and stop clock supply) the circuits of unused peripherals.

- Shipment

- Die \*Please contact our responsible sales person for the pad layout information.

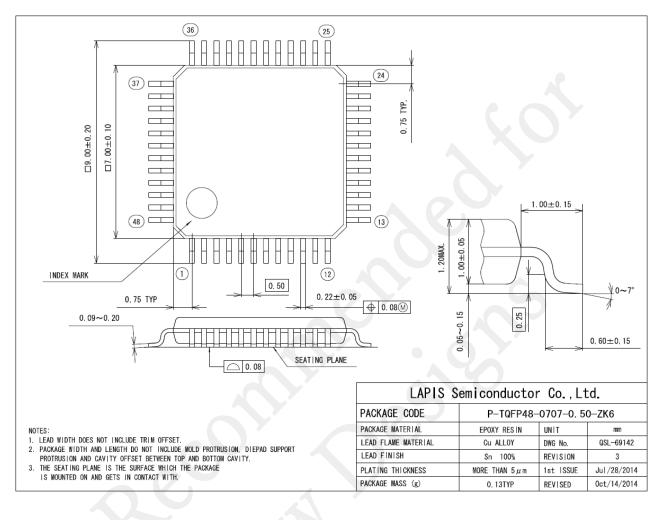

- 48-pin plastic TQFP Tray/Tape and Reel

- ML620Q503H-xxxTB ML620Q504H-xxxTB

- Guaranteed operating range

- Operating temperature (ambient) :  $-40^{\circ}$ C to  $+85^{\circ}$ C

- Operating voltage:  $V_{DD} = 1.8V$  to 5.5V

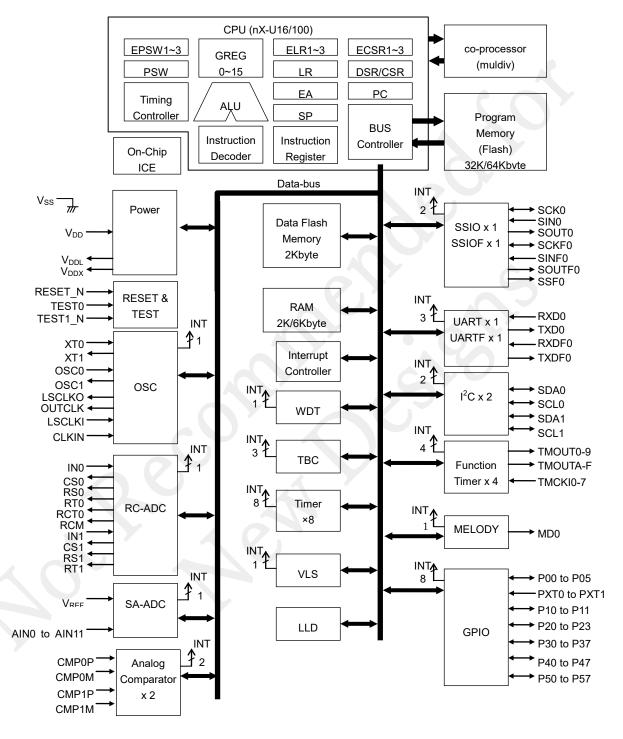

#### 1.2 Configuration of Functional Blocks

#### 1.2.1 Block Diagram of ML620Q503H/Q504H

- 1.3 Pins

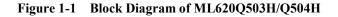

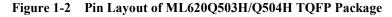

- 1.3.1 Pin Layout

#### 1.3.1.1 Pin Layout of ML620Q503H/Q504H TQFP Package

#### 1.3.2 List of Pins

#### 1.3.2.1 List of Pins of ML620Q503H/Q504H TQFP Package

| PK<br>G    |                                      |     | 1st F              | unction                                                                                                      |             |     |                                                            | 2nd/3rd                | /4th Fu | nction                          |          |     |                          |

|------------|--------------------------------------|-----|--------------------|--------------------------------------------------------------------------------------------------------------|-------------|-----|------------------------------------------------------------|------------------------|---------|---------------------------------|----------|-----|--------------------------|

| Pin<br>No. | Pin<br>name                          | I/O | Reset<br>State     | Function                                                                                                     | pin<br>name | I/O | function                                                   | pin name               | I/O     | function                        | pin name | I/O | functio<br>n             |

| 14,<br>45  | V <sub>SS</sub>                      | _   | -                  | Negative power supply pin                                                                                    | -           | -   | -                                                          | -                      | -       | -                               | -        | -   | -                        |

| 13,<br>44  | V <sub>DD</sub>                      | _   | _                  | Positive power supply pin                                                                                    | -           | -   | -                                                          | _                      | -       | -                               | -        | -   | -                        |

| 44         | V <sub>DDL</sub>                     | _   | _                  | Power supply pin for internal                                                                                | -           | -   | -                                                          | _                      | -       | -                               | -        | -   | -                        |

| 46         |                                      |     |                    | circuit (internally generated)<br>Power supply pin for internal                                              |             | _   |                                                            |                        |         |                                 |          |     |                          |

| 46         | V <sub>DDX</sub>                     | -   | -                  | circuit (internally generated)                                                                               | -           |     | -                                                          | _                      | -       |                                 | _        | -   | -                        |

| 12         | V <sub>REF</sub>                     | -   | -                  | Reference power supply pin of<br>SA-ADC                                                                      | -           | -   | -                                                          | -                      | -       | -                               | -        | -   | -                        |

| 1          | RESE<br>T_N                          | I   | Pull-up<br>Input   | Reset input pin                                                                                              | -           | -   | -                                                          |                        | -       |                                 | -        | -   | -                        |

| 42         | TEST1<br>_N                          | I   | Pull-up<br>Input   | Input pin for testing                                                                                        | -           | -   | -                                                          | -                      |         | -                               | -        | -   | -                        |

| 41         | TEST0                                | I/O | Pull-down<br>Input | Input/output pin for testing                                                                                 | -           | -   | -                                                          | $\mathbf{\mathcal{O}}$ |         | -                               | -        | -   | -                        |

| 48         | PXT0/<br>EXII0/<br>XT0               | Ι   | Input<br>disable   | Input port/<br>External interrupt/<br>Low-speed oscillation port                                             | Ι           | -   | -                                                          | I                      | -       | -                               | -        | -   | -                        |

| 47         | PXT1/<br>EXI1/<br>XT1/<br>LSCLK<br>I | I/O | Hi-Z<br>output     | Input-Output port/<br>External interrupt/<br>Low-speed oscillation port<br>Low-speed external clock<br>input | -           | -   | -                                                          | -                      | _       | Ċ                               | -        | _   | _                        |

| 19         | P00/<br>EXI00/<br>AIN8               | I/O | Hi-Z<br>output     | Input-Output port/<br>External interrupt/<br>SA-ADC input                                                    | IN0         | -   | RC-ADC<br>oscillation<br>input                             | SOUTO                  | 0       | SSIO data<br>output             | RXD0     | I   | UART<br>data<br>input    |

| 20         | P01/<br>EXI01/<br>AIN9               | I/O | Hi-Z<br>output     | Input-Output port/<br>External interrupt/<br>SA-ADC input                                                    | CS0         | 0   | RC-ADC<br>reference<br>capacitance<br>connection pin       | SINO                   |         | SSIO data<br>input              | TXD0     | 0   | UART<br>data<br>output   |

| 21         | P02/<br>EXI02/<br>AIN10              | I/O | Hi-Z<br>output     | Input-Output port/<br>External interrupt/<br>SA-ADC input                                                    | RCT0        | ο   | RCADC<br>resistor/capaci<br>tor sensor<br>connection pin   | SCK0                   | I/O     | SSIO clock<br>input/output      | TMOUT0   | 0   | FTM<br>output            |

| 22         | P03/<br>EXI03/<br>AIN11              | I/O | Hi-Z<br>output     | Input-Output port/<br>External interrupt/<br>SA-ADC input                                                    | RS0         | 0   | RC-ADC<br>reference<br>resistor<br>connection pin          | ) -                    | -       | -                               | TMOUT1   | 0   | FTM<br>output            |

| 23         | P04/<br>EXI04                        | I/O | Hi-Z<br>output     | Input-Output port/<br>External interrupt                                                                     | RT0         | 0   | RC-ADC<br>measurement<br>resistor sensor<br>connection pin | -                      | -       | -                               | -        | -   | -                        |

| 24         | P05/<br>EXI05                        | 1/0 | Hi-Z<br>output     | Input-Output port/<br>External interrupt                                                                     | RCM         | ο   | RC-ADC<br>oscillation<br>monitor                           | -                      | -       | -                               | -        | -   | -                        |

| 2          | P10/<br>OSC0                         | 1/0 | Hi-Z<br>output     | Input-Output port/<br>High-speed oscillation port                                                            |             | -   | -                                                          | -                      | -       | -                               | -        | -   | -                        |

| 3          | P11/<br>OSC1/<br>CLKIN               | I/O | Hi-Z<br>output     | Input-Output port/<br>High-speed oscillation port<br>High-speed external clock<br>input                      | -           | -   | -                                                          | -                      | -       | -                               | -        | -   | -                        |

| 15         | P20/<br>EXI20/<br>AIN4               | I/O | Hi-Z<br>output     | Input-Output port/<br>External interrupt/<br>SA-ADC input                                                    | IN1         | I   | RC-ADC<br>oscillation<br>input                             | SOUTF0                 | 0       | SSIOF data output               | RXDF0    | I   | UART<br>F data<br>input  |

| 16         | P21/<br>EXI21/<br>AIN5               | I/O | Hi-Z<br>output     | Input-Output port/<br>External interrupt/<br>SA-ADC input                                                    | CS1         | ο   | RC-ADC<br>reference<br>capacitance<br>connection pin       | SINF0                  | I       | SSIOF data<br>input             | TXDF0    | 0   | UART<br>F data<br>output |

| 17         | P22/<br>EXI22/<br>AIN6               | I/O | Hi-Z<br>output     | Input-Output port/<br>External interrupt/<br>SA-ADC input                                                    | RS1         | 0   | RC-ADC<br>reference<br>resistor<br>connection pin          | SCKF0                  | I/O     | SSIOF<br>clock<br>input/output  | TMOUT2   | 0   | FTM<br>output            |

| 18         | P23/<br>EXI23/<br>AIN7               | I/O | Hi-Z<br>output     | Input-Output port/<br>External interrupt/<br>SA-ADC input                                                    | RT1         | 0   | RC-ADC<br>measurement<br>resistor sensor<br>connection pin | SSF0                   | I/O     | SSIOF<br>select<br>input/output | TMOUT3   | 0   | FTM<br>output            |

| 4          | P30/<br>EXI30/<br>CMP0<br>P          | I/O | Hi-Z<br>output     | Input-Output port/<br>External interrupt/<br>Comparator plus input                                           | SDA0        | I/O | l <sup>2</sup> C data<br>input/output                      | SOUT0                  | 0       | SSIO data<br>output             | RXD0     | I   | UART<br>data<br>input    |

#### ML620Q503H/Q504H User's Manual Chapter 1 Overview

| PK<br>G         |                                      |     | 1st F                   | unction                                                                       |              |     |                                       | 2nd/3rd  | /4th Fur | nction                          |            |     |                             |

|-----------------|--------------------------------------|-----|-------------------------|-------------------------------------------------------------------------------|--------------|-----|---------------------------------------|----------|----------|---------------------------------|------------|-----|-----------------------------|

| Pin             | Pin                                  | I/O | Reset                   | Function                                                                      | pin          | I/O | function                              | pin name | I/O      | function                        | pin name   | I/O | functio                     |

| <u>No.</u><br>5 | name<br>P31/<br>EXI31/<br>CMP0<br>M  | I/O | State<br>Hi-Z<br>output | Input-Output port/<br>External interrupt/<br>Comparator minus input           | name<br>SCL0 | 0   | l <sup>2</sup> C clock<br>output      | SINO     |          | SSIO data<br>input              | TXD0       | 0   | n<br>UART<br>data<br>output |