# Octal Low-Side Relay Driver

The NCV7240 is an automotive eight channel low-side driver providing drive capability up to 600 mA per channel. Output control is via a SPI port and offers convenient reporting of faults for open load (or short to ground), over load, and over temperature conditions. Additionally, parallel control of the outputs is addressable (in pairs) via the INx pins.

A dedicated limp-home mode pin (LHI) enables OUT1-OUT4 while disabling OUT5-OUT8.

Each output driver is protected for over load current and includes an output clamp for inductive loads.

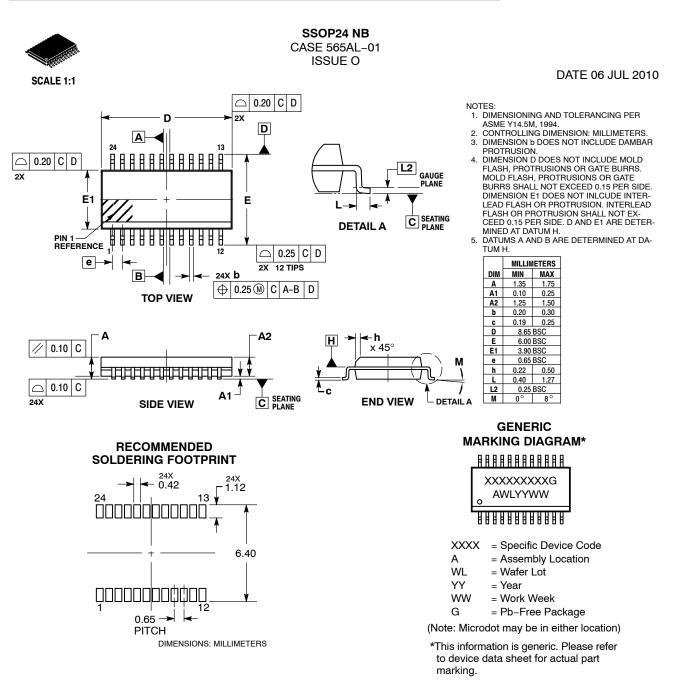

The NCV7240 is available in a SSOP-24 fused lead package.

#### Features

- 8 Channels

- 600 mA Low-Side Drivers

- R<sub>DS(on)</sub> 1.5 Ω (Typ), 3 Ω (Max)

- 16-bit SPI Control

- Frame Error Detection (8-bit)

- Daisy Chain Capable

- Parallel Input Pins for PWM operation

- Power Up Without Open Circuit Detection Active (for LED applications)

- Low Quiescent Current in Sleep and Standby Modes

- Limp Home Functionality

- 3.3 V and 5 V compatible Digital Input Supply Range

- Fault Reporting

- Open Load Detection (selectable)

- Over Load

- Over Temperature

- Power-on Reset (VDD, VDDA)

- SSOP-24 Package (internally fused leads)

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- These are Pb–Free Devices

#### Applications

- Automotive Body Control Unit

- Automotive Engine Control Unit

- Relay Drive

- LED Drive

- Stepper Motor Driver

## **ON Semiconductor®**

www.onsemi.com

| NCV72 | 240x = Specific Device Code |

|-------|-----------------------------|

|       | (x = blank, A or B)         |

| А     | = Assembly Location         |

| WL    | = Wafer Lot                 |

| Y     | = Year                      |

| WW    | = Work Week                 |

| G     | = Pb-Free Package           |

|       |                             |

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 27 of this data sheet.

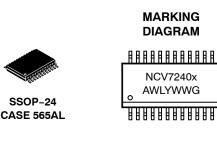

Figure 1. Basic Block Diagram

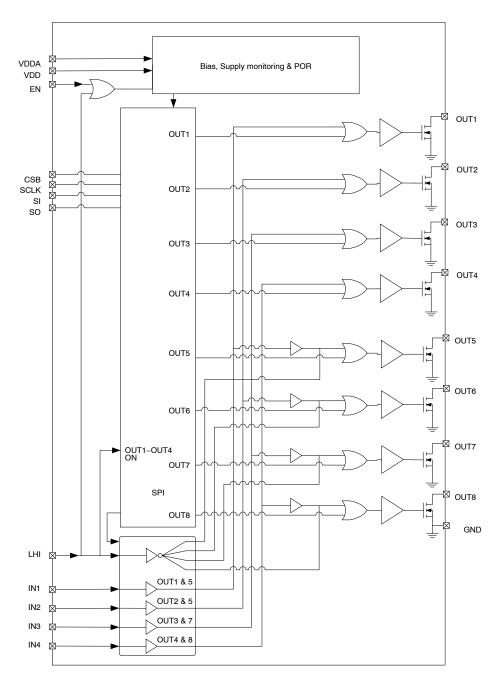

#### Figure 2. Application Diagram (relay loads)

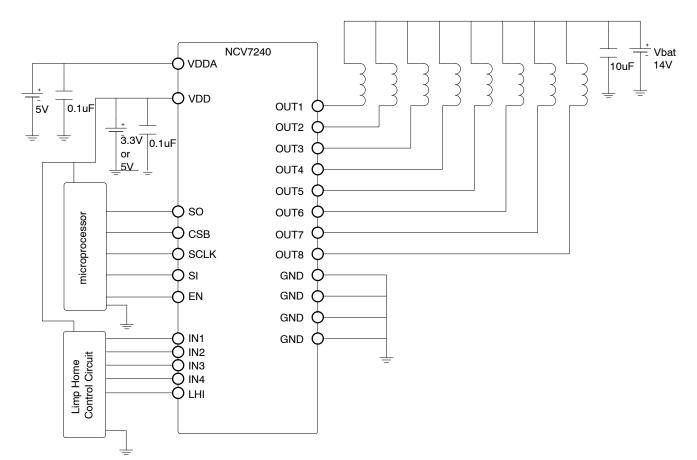

Figure 3. Pinout

#### PACKAGE PIN DESCRIPTION

| SSOP-24 | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GND    | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2       | GND    | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3       | OUT1   | Channel 1 low-side drive output. Requires an external pull-up device for operation.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4       | OUT2   | Channel 2 low-side drive output. Requires an external pull-up device for operation.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5       | OUT3   | Channel 3 low-side drive output. Requires an external pull-up device for operation.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6       | OUT4   | Channel 4 low-side drive output. Requires an external pull-up device for operation.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7       | OUT5   | Channel 5 low-side drive output. Requires an external pull-up device for operation.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8       | OUT6   | Channel 6 low-side drive output. Requires an external pull-up device for operation.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9       | OUT7   | Channel 7 low-side drive output. Requires an external pull-up device for operation.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10      | OUT8   | Channel 8 low-side drive output. Requires an external pull-up device for operation.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11      | GND    | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 12      | GND    | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 13      | VDD    | Digital Power Supply for SO output (3.3 V or 5 V).                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 14      | IN4    | Parallel control of OUT4 and OUT8<br>Ground if not used for best EMI performance.<br>Alternatively keep open and internal pull-down will hold the input low.<br>(120 k $\Omega$ pull down resistor).                                                                                                                                                                                                                                                                                               |

| 15      | IN3    | Parallel control of OUT3 and OUT7<br>Ground if not used for best EMI performance.<br>Alternatively keep open and internal pull-down will hold the input low.<br>(120 k $\Omega$ pull down resistor).                                                                                                                                                                                                                                                                                               |

| 16      | IN2    | Parallel control of OUT2 and OUT6.<br>Ground if not used for best EMI performance.<br>Alternatively keep open and internal pull-down will hold the input low.<br>(120 k $\Omega$ pull down resistor).                                                                                                                                                                                                                                                                                              |

| 17      | IN1    | Parallel control of OUT1 and OUT5.<br>Ground if not used for best EMI performance.<br>Alternatively keep open and internal pull-down will hold the input low.<br>(120 k $\Omega$ pull down resistor).                                                                                                                                                                                                                                                                                              |

| 18      | LHI    | Limp Home Input. Active High.<br>A high on this pin powers up the device and activates the respective output drive INx designator while<br>disabling outputs OUT5–OUT8.<br>Input SPI commands are ignored, but the output register reports faults.<br>(Read capability only. No write capability.)<br>All registers are reset coming out of LHI mode.<br>Ground if not used for best EMI performance.<br>Alternatively keep open and internal pull-down resistor (120 kΩ) will hold the input low. |

| 19      | SO     | SPI serial data output. Output high voltage level referenced to pin VDD.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 20      | SCLK   | SPI clock (120 kΩ pull down resistor).                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 21      | EN     | Global Enable (active high). (120 k $\Omega$ pull down resistor).                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 22      | SI     | SPI serial data input (120 k $\Omega$ pull down resistor).                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23      | CSB    | SPI Chip Select "Bar" (120 k $\Omega$ pull up resistor to VDD).                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 24      | VDDA   | Analog Power Supply Input voltage (5 V).                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

#### MAXIMUM RATINGS

| Parameter                                                                                                              | Min            | Max                          | Unit |

|------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------|------|

| Supply Input Voltage (VDDA, VDD)<br>DC                                                                                 | -0.3           | 5.5                          | V    |

| Digital I/O pin voltage<br>(EN, LHI, Inx, CSB, SCLK, SI)<br>(SO)                                                       | -0.3<br>-0.3   | 5.5<br>V <sub>DD</sub> + 0.3 | V    |

| High Voltage Pins (OUTx)<br>DC<br>Peak Transient                                                                       | -0.3           | 36<br>44 (Note 1)            | V    |

| Output Current (OUTx)                                                                                                  | -1             | 1.3                          | А    |

| Clamping Energy<br>Maximum (single pulse)<br>Repetitive (multiple pulse) (Note 2)                                      |                | 75<br>-                      | mJ   |

| Operating Junction Temperature Range                                                                                   | -40            | 150                          | °C   |

| Storage Temperature Range                                                                                              | -55            | 150                          | °C   |

| ESD Capability,<br>Human body model (100 pF, 1.5 kΩ) (OUTx pins)<br>Human body model (100 pF, 1.5 kΩ) (all other pins) | -4000<br>-2000 | 4000<br>2000                 | V    |

| ESD Capability<br>Machine Model (200 pF)                                                                               | -200           | 200                          | V    |

| AECQ10x-12-RevA<br>Short Circuit Reliability Characterization                                                          | Grade A        | -                            |      |

#### PACKAGE

| Moisture Sensitivity Level                                                                                                                                 | MSL2 |                | -    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------|------|

| Lead Temperature Soldering: SMD style only, Reflow (Note 3)<br>Pb-Free Part 60 – 150 sec above 217°C, 40 sec max at peak                                   |      | 265 peak       | °C   |

| Package Thermal Resistance (per JESD51)                                                                                                                    |      |                | °C/W |

| SSOP-24                                                                                                                                                    |      |                |      |

| Junction-to-Ambient (1s0p + 600 mm <sup>2</sup> Cu) (Note 4)<br>Junction-to-Ambient (2s2p) (Notes 4 and 5)<br>Junction-to-Pin (pins 1, 2, 11, 12) (Note 6) |      | 68<br>62<br>30 |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Internally limited. Specification applies to unpowered and powered modes. (0 V to VDDA, 0 V to VDD)

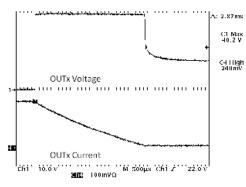

2. Testing particulars, 2M pulses,  $V_{bat}$  = 15 V, 63  $\Omega$ , 390 mH, T<sub>A</sub> = 25°C. (See Figure 4)

- 3. For additional information, see or download ON Semiconductor's Soldering and Mounting Techniques Reference Manual, SOLDERRM/D and Application Note AND8083/D.

- 4. 76 mm x 76 mm x 1.5 mm FR4 PCB with additional heat spreading copper (2 oz) of 600 mm<sup>2</sup>, LS1 to LS8 dissipating 100 mW each. No vias.

- 5. Include 2 inner 1 oz copper layers. No vias.

- 6. One output dissipating 100 mW.

Figure 4. Repetitive Clamping Energy Test

$\textbf{ELECTRICAL CHARACTERISTICS} (3.0 \text{ V} < \text{VDD} < \text{VDDA}, 4.5 \text{ V} < \text{VDDA} (\text{Note 7}) < 5.5 \text{ V}, -40^{\circ}\text{C} \leq \text{T}_{\text{J}} \leq 150^{\circ}\text{C}, \text{ EN} = \text{VDD}, \text{C} \leq 150^{\circ}\text{C}, \text{C} = 100^{\circ}\text{C}, \text{C} = 100^{\circ}\text{C},$ LHI = 0 V unless otherwise specified).

| Symbol                                                                            | Characteristic                                                        | Conditions                                                                                                                                                                                                                  | Min         | Тур         | Max            | Unit |

|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|----------------|------|

| GENERAL                                                                           | -                                                                     | •                                                                                                                                                                                                                           | -           | -           | -              | -    |

| I <sub>VDDA_ON</sub>                                                              | Operating Current (VDDA)<br>ON Mode<br>(All Channels On)              |                                                                                                                                                                                                                             | _           | 3           | 5              | mA   |

| I <sub>VDDA_</sub> GS_25<br>I <sub>VDDA_</sub> GS_85<br>I <sub>VDDA_</sub> GS_150 | Quiescent Current (VDDA)<br>Global Standby Mode<br>(All Channels Off) | $\begin{array}{l} \text{SI} = \text{SCLK} = 0 \text{ V, CSB} = \text{VDD} \\ \text{T}_{\text{J}} = 25^{\circ}\text{C} \\ \text{T}_{\text{J}} = 85^{\circ}\text{C} \\ \text{T}_{\text{J}} = 150^{\circ}\text{C} \end{array}$ |             |             | 32<br>35<br>40 | μΑ   |

| I <sub>VDDA_LO_25</sub><br>I <sub>VDDA_LO_85</sub><br>I <sub>VDDA_LO_150</sub>    | Quiescent Current (VDDA)<br>Low lq Mode                               | $\label{eq:SI} \begin{array}{l} SI = SCLK = EN = 0 \ V, \ CSB = VDD \\ T_J = 25^\circC \\ T_J = 85^\circC \\ T_J = 150^\circC \end{array}$                                                                                  | -<br>-<br>- | -<br>-<br>- | 10<br>10<br>20 | μΑ   |

| IVDD_ON                                                                           | Operating Current (VDD)<br>ON Mode<br>(All Channels On)               | EN=high, SCLK = Inx = 0 V,<br>CSB = VDD = VDDA                                                                                                                                                                              | -           | 0.3         | 0.5            | mA   |

| IVDD_GS_25<br>IVDD_GS_85<br>IVDD_GS_150                                           | Quiescent Current (VDD)<br>Global Standby Mode<br>(All Channels Off)  | $\label{eq:CSB} \begin{array}{l} \text{CSB} = \text{VDD} = \text{VDDA}, \ f_{\text{SCLK}} = 0 \ \text{Hz} \\ T_J = 25^\circ\text{C} \\ T_J = 85^\circ\text{C} \\ T_J = 150^\circ\text{C} \end{array}$                       | _<br>_<br>_ | _<br>_<br>_ | 20<br>20<br>40 | μΑ   |

| IVDD_LO_25<br>IVDD_LO_85<br>IVDD_LO_150                                           | Quiescent Current (VDD)<br>Low Iq Mode                                | $ \begin{array}{l} EN = 0 \ V \\ T_{J} = 25^\circC \\ T_{J} = 85^\circC \\ T_{J} = 150^\circC \end{array} $                                                                                                                 |             |             | 5<br>5<br>20   | μΑ   |

| POR_VDDA_rise                                                                     | NCV7240 / NCV7240A<br>Power–on Reset threshold (VDDA)                 | VDDA rising                                                                                                                                                                                                                 | -           | 3.80        | 4.15           | V    |

| POR_VDDA_hys                                                                      | NCV7240 / NCV7240A<br>Power–on Reset hysteresis (VD-<br>DA)           |                                                                                                                                                                                                                             | 150         | 200         | 350            | mV   |

| POR_VDDA_riseB                                                                    | NCV7240B<br>Power-on Reset threshold (VDDA)                           | VDDA rising                                                                                                                                                                                                                 | -           | 3.60        | 3.85           | V    |

| POR_VDDA_fallB                                                                    | NCV7240B<br>Power-on Reset threshold (VDDA)                           | VDDA falling                                                                                                                                                                                                                | 3.00        | 3.30        | 3.50           | V    |

| POR_VDDA_hysB                                                                     | NCV7240B<br>Power–on Reset hysteresis (VD-<br>DA)                     |                                                                                                                                                                                                                             | 150         | 200         | 350            | mV   |

| POR_VDD_rise                                                                      | Power-on Reset threshold (VDD)                                        | VDD rising                                                                                                                                                                                                                  | -           | 2.4         | 2.7            | V    |

| POR_VDD_hys                                                                       | Power-on Reset Hysteresis (VDD)                                       |                                                                                                                                                                                                                             | 75          | 100         | 240            | mV   |

| TSD                                                                               | Thermal Shutdown (Note 8)                                             | Not ATE tested.                                                                                                                                                                                                             | 150         | 175         | 200            | °C   |

| TSDhys                                                                            | Thermal Hysteresis                                                    | Not ATE tested.                                                                                                                                                                                                             | 10          | 25          | -              | °C   |

| OUTPUT DRIVE                                                                      | R                                                                     |                                                                                                                                                                                                                             |             |             |                |      |

| R <sub>DS(on)</sub>                                                               | Output Transistor R <sub>DS(on)</sub>                                 | IOUTx = 180 mA                                                                                                                                                                                                              | -           | 1.5         | 3.0            | Ω    |

| I <sub>OL</sub>                                                                   | Overload Detection Current                                            |                                                                                                                                                                                                                             | 0.6         | 0.95        | 1.3            | А    |

| l <sub>leak_typ</sub><br>l <sub>leak_temp</sub><br>l <sub>leak_HV</sub>           | Output Leakage                                                        | OUTx = 13.5 V, 25°C<br>OUTx = 13.5 V<br>OUTx = 35 V                                                                                                                                                                         | -<br>-<br>- | -<br>-<br>- | 1<br>5<br>10   | μΑ   |

| CLAMP                                                                             | Output Clamp Voltage                                                  | VDD = 0 V to 5.5 V<br>VDDA = 0 V to 5.5 V<br>IOUTx = 50 mA                                                                                                                                                                  | 36          | 40          | 44             | V    |

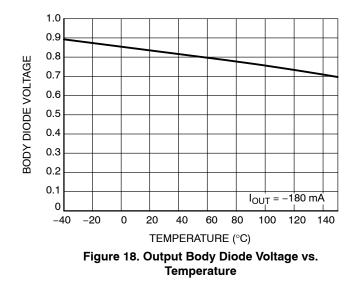

| BODY                                                                              | Output Body Diode Voltage                                             | IOUTx = -180mA                                                                                                                                                                                                              | -           | -           | 1.5            | V    |

| OPEN_V                                                                            | Open Load Detection Threshold<br>Voltage (Vol)                        |                                                                                                                                                                                                                             | 1.0         | 1.75        | 2.5            | V    |

| OPEN_I                                                                            | Open Load Diagnostic Sink Cur-<br>rent (lol)                          | 1 V < OUTx < 13.5 V, Output<br>Disabled                                                                                                                                                                                     | 20          | 60          | 100            | μΑ   |

|                                                                                   |                                                                       |                                                                                                                                                                                                                             |             |             |                |      |

7. Reduced performance down to 4 V provided VDDA Power-On Reset threshold has not been breached.

8. Each output driver is protected by its' own individual thermal sensor.

9. Input signals H→L→H greater than 50usec are guaranteed to be detected.

$\textbf{ELECTRICAL CHARACTERISTICS} (3.0 \text{ V} < \text{VDD} < \text{VDDA}, 4.5 \text{ V} < \text{VDDA} (\text{Note 7}) < 5.5 \text{ V}, -40^{\circ}\text{C} \leq \text{T}_{\text{J}} \leq 150^{\circ}\text{C}, \text{ EN} = \text{VDD}, \text{C} \leq 150^{\circ}\text{C}, \text{C} = 100^{\circ}\text{C}, \text{C} = 100^{\circ}\text{C},$ LHI = 0 V unless otherwise specified).

| Symbol                  | Characteristic                                           | Conditions                                                                                                                            | Min | Тур | Max | Unit |  |

|-------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|--|

| OUTPUT TIMIN            | OUTPUT TIMING SPECIFICATIONS                             |                                                                                                                                       |     |     |     |      |  |

| t <sub>WU</sub>         | Enable (EN) wake-up time                                 | CSB = 0 V, EN going high 80% to SO active                                                                                             | -   | _   | 200 | μs   |  |

| t <sub>Sig</sub>        | Enable (EN) and LHI (Note 9) Sig-<br>nal Duration        |                                                                                                                                       | 50  | -   | -   | μs   |  |

| tSPI_ON                 | Serial Control<br>Output turn-on time<br>All Channels    | CSB going high 80% to OUTx going low 20% $V_{bat}$ , $V_{bat} = 13.5$ V, $I_{DS} = 180$ mA resistive load                             | -   | 30  | 50  | μs   |  |

| tspi_off                | Serial Control<br>Output turn–off time<br>All Channels   | CSB going high 80% to OUTx going<br>high 80% V <sub>bat</sub> , V <sub>bat</sub> = 13.5 V,<br>I <sub>DS</sub> = 180 mA resistive load | -   | 30  | 50  | μs   |  |

| t <sub>Logic_</sub> ON  | Parallel Control<br>Output turn–on time<br>All Channels  | INx going high 80% to OUTx going<br>low 20% V <sub>bat</sub> , V <sub>bat</sub> = 13.5 V,<br>I <sub>DS</sub> = 180 mA resistive load  | -   | 30  | 50  | μs   |  |

| t <sub>Logic_</sub> OFF | Parallel Control<br>Output turn-off time<br>All Channels | Inx going low 20% to OUTx going high 80% V <sub>bat</sub> , V <sub>bat</sub> = 13.5 V, $I_{DS}$ = 180 mA resistive load               | -   | 30  | 50  | μs   |  |

| t <sub>OVER</sub>       | Over Load Shut-Down Delay Time                           |                                                                                                                                       | 3   | 15  | 50  | μs   |  |

| t <sub>OPEN</sub>       | Open Load Detection Time                                 |                                                                                                                                       | 30  | 115 | 200 | μs   |  |

| DIGITAL INTER           | IGITAL INTERFACE CHARACTERISTICS                         |                                                                                                                                       |     |     |     |      |  |

#### **INPUT CHARACTERISTICS**

| LOGIC_V       | Digital Input Threshold<br>(CSB, SI, SCLK, LHI, EN,INx) |                                  | 0.8 | 1.4 | 2.0 | V  |

|---------------|---------------------------------------------------------|----------------------------------|-----|-----|-----|----|

| LOGIC_H1      | Digital Input Hysteresis<br>(CSB, SI, SCLK, INx)        |                                  | 50  | 175 | 300 | mV |

| LOGIC_H2      | Digital Input Hysteresis<br>(LHI, EN)                   |                                  | 150 | 400 | 800 | mV |

| RI_PD         | Input Pulldown Resistance<br>(SI, SCLK, LHI, EN,INx)    | Inx = SI = SCLK = LHI = EN = VDD | 50  | 120 | 190 | kΩ |

| RI_PU         | Input Pullup Resistance (CSB)                           | CSB = 0 V                        | 50  | 120 | 190 | kΩ |

| CSB_leak_VDD  | CSB Leakage to VDD                                      | CSB = 5 V, VDD = 0 V             | -   | _   | 100 | uA |

| CSB leak VDDA | CSB Leakage to VDDA                                     | CSB = 5 V, VDDA = 0 V            | -   | -   | 100 | uA |

#### **OUTPUT CHARACTERISTICS**

| SO_HI      | SO – Output High     | l(out) = −1.5 mA | V <sub>DD</sub> -<br>0.4 | - | -   | V  |

|------------|----------------------|------------------|--------------------------|---|-----|----|

| SO_LO      | SO – Output Low      | I(out) = 2.0 mA  | -                        | - | 0.6 | V  |

| SO_TS_leak | SO Tri-state Leakage | CSB = VDD        | -3                       | 0 | 3   | μΑ |

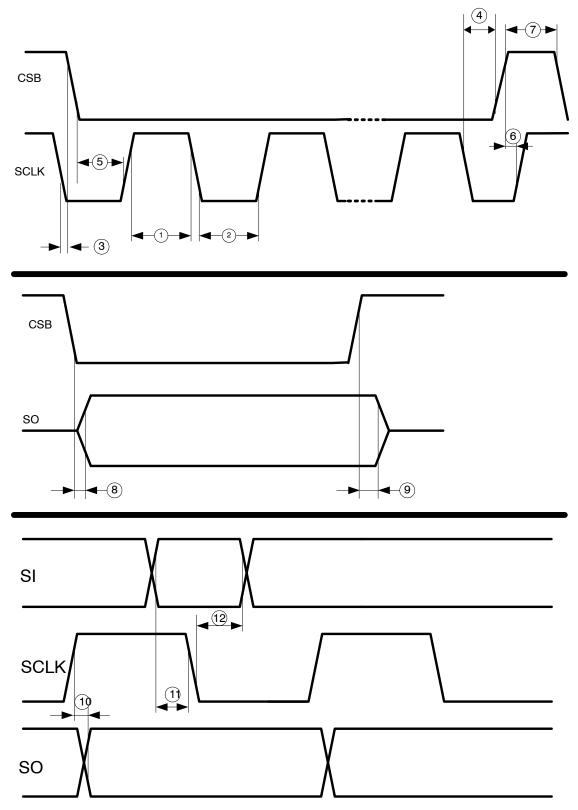

SPI TIMING (all timing specifications measured at 20% and 80% voltage levels)

|                       |                                                    |                                                           |     | ī |     |     |

|-----------------------|----------------------------------------------------|-----------------------------------------------------------|-----|---|-----|-----|

| freq                  | SCLK Frequency                                     |                                                           | -   | - | 5   | MHz |

| l/f                   | SCLK Clock Period                                  |                                                           | 200 | - | I   | ns  |

| t <sub>SCLK_</sub> HI | SCLK High Time                                     | Figure 5, #1                                              | 85  | - | -   | ns  |

| t <sub>SCLK_LO</sub>  | SCLK Low Time                                      | Figure 5, #2                                              | 85  | - | I   | ns  |

| tsi_s∪                | SI Setup Time                                      | Figure 5, #11                                             | 50  | - | I   | ns  |

| t <sub>SI_hold</sub>  | SI Hold Time                                       | Figure 5, #12                                             | 50  | - | -   | ns  |

| tcsb_su               | CSB Setup Time                                     | Figure 5, #5, 6                                           | 100 | - | -   | ns  |

| t <sub>CSB_</sub> ні  | CSB High Time                                      | Figure 5, #7                                              | 1.5 | - | -   | μs  |

| t <sub>SCLK</sub> _SU | SCLK Setup Time                                    | Figure 5, #3, 4                                           | 85  | - | -   | ns  |

| t <sub>SO_EN</sub>    | SO Output Enable Time<br>(CSB falling to SO valid) | Figure 5, #8, C <sub>load</sub> = 50 pF<br>Not ATE tested | -   | - | 200 | ns  |

Reduced performance down to 4 V provided VDDA Power–On Reset threshold has not been breached.

Each output driver is protected by its' own individual thermal sensor.

Input signals H→L→H greater than 50usec are guaranteed to be detected.

$\textbf{ELECTRICAL CHARACTERISTICS} (3.0 \text{ V} < \text{VDD} < \text{VDDA}, 4.5 \text{ V} < \text{VDDA} (\text{Note 7}) < 5.5 \text{ V}, -40^{\circ}\text{C} \leq \text{T}_{\text{J}} \leq 150^{\circ}\text{C}, \text{ EN} = \text{VDD}, \text{C} \leq 150^{\circ}\text{C}, \text{C} = 100^{\circ}\text{C}, \text{C} = 100^{\circ}\text{C},$ LHI = 0 V unless otherwise specified).

| Symbol                                                                        | Characteristic                                         | Conditions                                                 | Min | Тур | Max | Unit |

|-------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------|-----|-----|-----|------|

| SPI TIMING (all timing specifications measured at 20% and 80% voltage levels) |                                                        |                                                            |     |     |     |      |

| t <sub>SO_DIS</sub>                                                           | SO Output Disable Time<br>(CSB rising to SO tri-state) | Figure 5, #9<br>Not ATE tested                             | -   | -   | 200 | ns   |

| t <sub>SO_valid</sub>                                                         | SO Output Data Valid Time with<br>capacitive load      | Figure 5, #10, C <sub>load</sub> = 50 pF<br>Not ATE tested | -   | -   | 100 | ns   |

Reduced performance down to 4 V provided VDDA Power–On Reset threshold has not been breached.

Each output driver is protected by its' own individual thermal sensor.

9. Input signals  $H \rightarrow L \rightarrow H$  greater than 50usec are guaranteed to be detected.

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

Figure 5. Detailed SPI Timing (measured at 20% and 80% voltage levels)

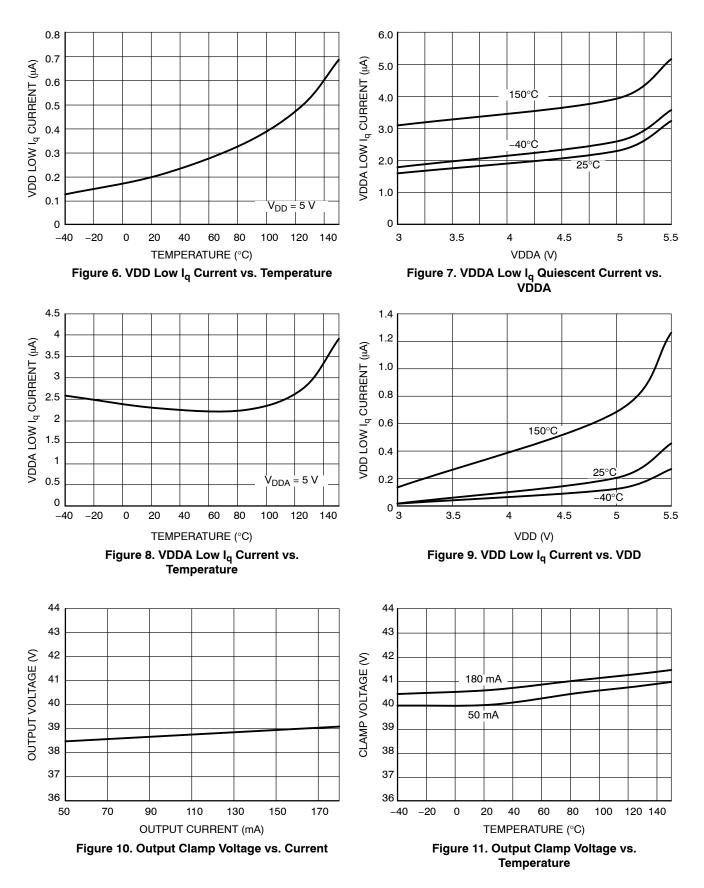

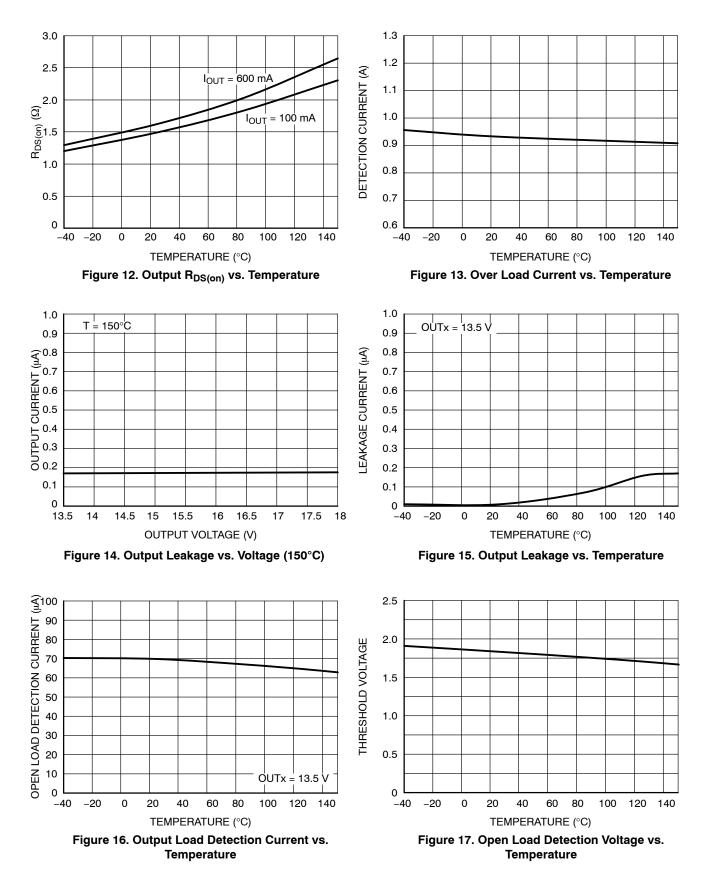

### **TYPICAL PERFORMANCE GRAPHS**

### **TYPICAL PERFORMANCE GRAPHS**

### **TYPICAL PERFORMANCE GRAPHS**

#### DETAILED OPERATING DESCRIPTION

#### **Power Outputs**

The NCV7240 provides eight independent 600mA power transistors with their source connection referenced to the ground pin and with their drain connection brought out to individual pins resulting in 8 independent low–side drivers. Output driver location on one side of the IC layout provides for optimum pcb layout to the loads.

Internal clamping structures are provided to limit transient voltages when switching inductive loads. Each output has an over load detection current of 0.6 A (min) where the drivers turn–off and stay latched off. An Over Load Current Shut–Down Delay Time of 3  $\mu$ s (min) is designed into the IC as a filter allowing for spikes in current which may occur during normal operation and allowing for protection from overload conditions.

Faults can be cleared with the SPI input register (command 00) or via a power-on-reset. Fault detection is provided in real time. Detection is provided both during output turn-on and with output already on. (See Page 18, Clearing the Fault Registers)

The NCV7240 is available in a SSOP-24 package.

#### **Output Control (SPI)**

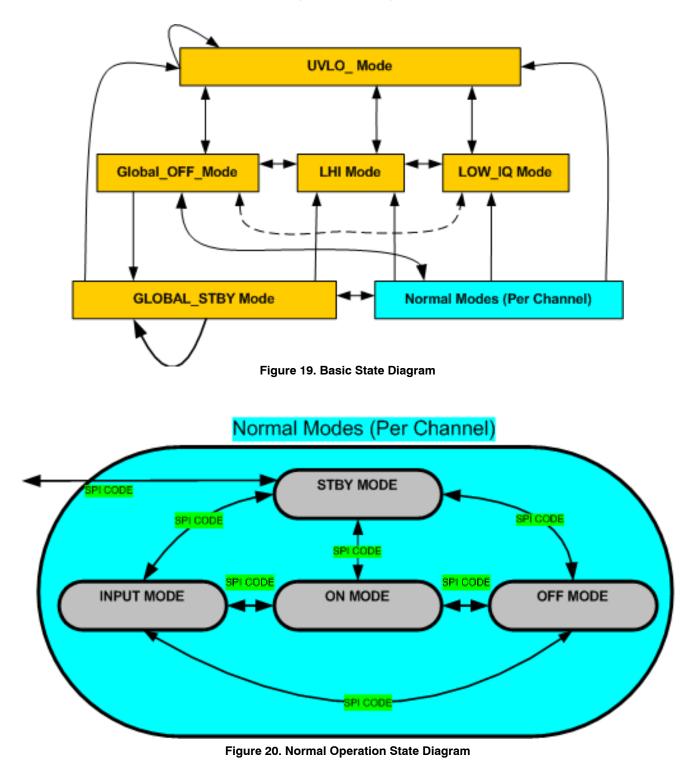

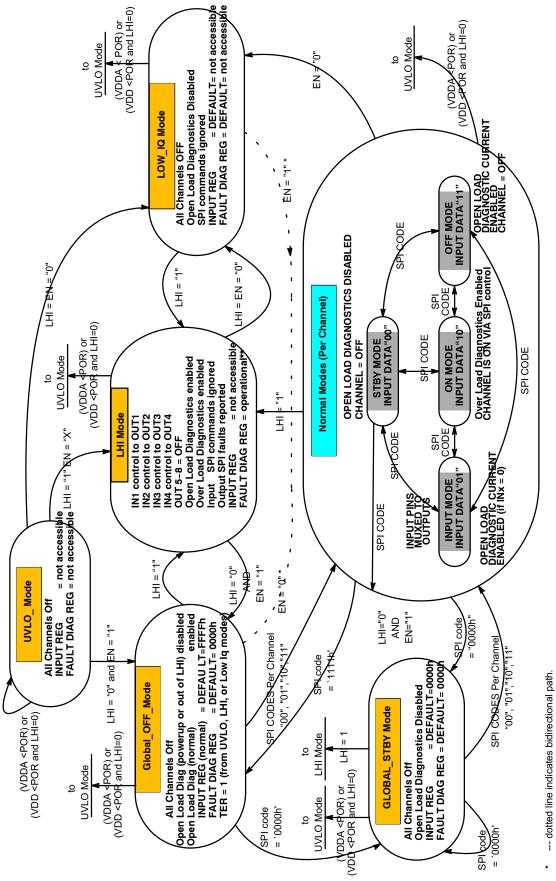

Each output driver is controlled via a digital SPI port after the device has powered up (out of POR) and enabled via the EN pin. The NCV7240 device will go through a power up reset each time the EN pin is toggled high resulting in a device setup of default values as described in the Register Specifics section. Standby Mode, Input Mode, ON Mode, and OFF Mode are all selectable via the SPI for each channel independently.

#### Power up, Power-On Reset (UVLO mode)

Both VDD and VDDA supply an independent power-on-reset function to the IC. Coming out of power-on-reset all input bits are set to a 1 (OFF Mode) and all output bits are set to a 0 except for the TER bit which is set to a 1. The device cannot operate without both supplies above their respective power-on reset thresholds with the exception of LHI mode. During LHI mode, VDD POR is ignored and the device is only affected by VDDA POR.

The NCV7240 powers up into the Global OFF Mode without the open circuit diagnostic current enabled. This allows the device to be turned on via EN = 0 to EN = 1 with LED loads avoiding illumination of the LED loads (reference Figure 21 State Diagram). All other paths to Global OFF Mode enable open circuit diagnostic current.

| Modes of<br>Operation   | Conditions                                        | Description                                                                                                                                                                                                               |

|-------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UVLO Mode               | VDD or VDDA below their respective POR thresholds | All outputs off in this mode.<br>Coming out of this mode<br>with EN = 1 sets all channels in the OFF mode<br>without open circuit diagnostic current enabled.<br>With LHI = 1 and EN = x, the part enters limp home mode. |

| OFF Mode                | SPI Control<br>(Command 11)                       | Output off.<br>Open circuit diagnostic current is disabled (powerup mode).<br>Open circuit diagnostic current is enabled (normal mode).                                                                                   |

| Global OFF Mode         | SPI Control<br>All Channels (Command 11)          | Output off.<br>Open circuit diagnostic current is disabled (powerup mode).<br>Open circuit diagnostic current is enabled (normal mode).                                                                                   |

| ON Mode                 | SPI Control<br>(Command 10)                       | Output on.                                                                                                                                                                                                                |

| Limp Home Mode<br>(LHI) | LHI = high, EN = x                                | Dedicated output turn on control of<br>OUT1-OUT4 using IN1-IN4.<br>OUT5-OUT8 are in OFF Mode.                                                                                                                             |

| Low lq Mode             | EN = LHI = low                                    | Provides a state with the lowest quiescent current for $V_{\text{DD}}$ and VDDA.                                                                                                                                          |

| Standby Mode            | SPI Control<br>(Command 00)                       | Provides an OFF state with<br>Open circuit diagnostic current disabled.                                                                                                                                                   |

| Global<br>Standby Mode  | SPI Control<br>All Channels (Command 00)          | Provides a reduced quiescent current mode.<br>Provides an OFF state with<br>Open circuit diagnostic current disabled.                                                                                                     |

| Input Mode              | SPI Control<br>(Command 01)                       | Directs output channel to be driven from INx input pins.                                                                                                                                                                  |

#### Table 1. MODES OF OPERATION

Figure 21. Detailed State Diagram

SO reports above VDD > POR

Operational down to VDD=0 V.

\*\*

#### Limp Home and PWM operation (INx control)

Pulse Width Modulation techniques are allowed utilizing the parallel inputs (INx).Output pins (OUTx) are programmed for use in conjunction with the INx pins using the SPI command (command 01). The LHI pin controls the operation of the INx pins.

#### <u>LHI = Low and EN = High</u>

With LHI=low, default pairs of outputs are controlled by the INx pins (via SPI programming).

IN1 controls channels OUT1 and OUT5. IN2 controls channels OUT2 and OUT6. IN3 controls channels OUT3 and OUT7. IN4 controls channels OUT4 and OUT8.

Alternatively, any of the eight channels can be commanded off (e.g. if OUT5 is commanded off via a SPI command, only OUT1 will be controlled via IN1).

Output pins (OUTx) are programmed for use in conjunction with the INx pins using the SPI command (command 01).

It is important to note faults occurring during PWM operation (LHI = low) must be cleared via the SPI port.

#### <u>LHI = High</u>

To go into limp home mode, bring LHI=high, the corresponding outputs of IN1–IN4 will turn on or off, and OUT5–OUT8 will be forced off.

During Limp Home Mode, over load and over temperature sensing are functional, and are reported via the SPI port. But, since input SPI commands are ignored with LHI = high, driver turn-off (overload or over temperature) occurring when LHI=high can only be re-initiated by toggling LHI or through a POR of VDDA.

All registers are reset coming out of LHI mode. The device enters OFF mode (EN = 1) or Low Iq Mode (EN = 0) depending on the state of the EN pin. Open Load diagnostics are disabled in both cases.

#### UVLO (Under Voltage Lockout with LHI = High)

A breach of VDDA Power–On Reset thresholds will cause the outputs to turn off and enter the UVLO mode. In LHI mode (LHI = 1), VDD POR is ignored. If VDD is below the operation of SO drive capability, fault information is preserved and can be retrieved when SO drive capability is restored.

#### TER

A transmission error bit (TER) is set ("1") when exiting the Limp Home Mode into Global Off Mode. See Frame Detection Transmission Error Section for operation details.

#### Enable Input (EN)

The EN input pin is a logic controlled input with a voltage threshold between 0.8 V and 2.0 V. The device powers up when EN goes from low to high, and exits Low Iq Mode (with LHI = 0 V) into global Off Mode. Device power up is also controlled via the Limp Home Input (LHI) as an OR'd condition. The EN input is a don't care when the LHI pin is driven from low to high. In this situation, the device enters Limp Home Mode.

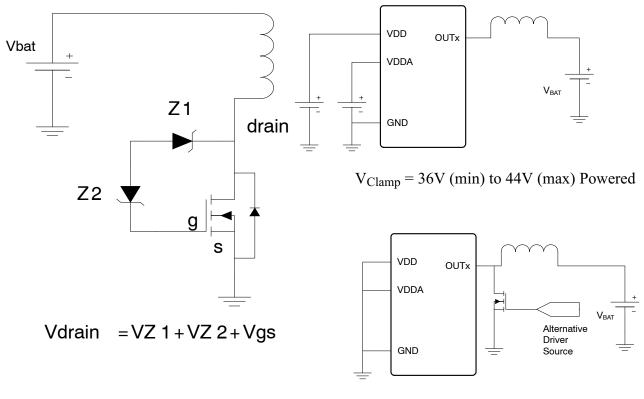

#### Output Drive Clamping

Internal zener diodes (Z1 & Z2, Figure 22) help to protect the output drive transistors from the expected fly back energy generated from an inductive load turning off. Z1 provides the voltage setting of the clamp (along with  $V_{gs}$  of the output transistor and Z2) while Z2 isolates Z1 from normal turn-on activity.

The output clamp voltage is specified between 36 V and 44 V. This includes clamping operation during unpowered input supplies (VDD and VDDA). Device protection will be provided when the load is driven from an alternative driver source. This is an important feature when considering protecting for load dump with an un–powered IC.

$V_{Clamp} = 36V \text{ (min) to } 44V \text{ (max) Un-powered}$

Figure 22. Output Clamp

#### **Over Temperature / Thermal Shutdown**

The NCV7240 incorporates eight individual thermal sensors located in proximity to each output driver. A channel is latched off upon the detection of an Over Temperature event. This allows operation of unaffected channels before, during, and after a channel detection of over temperature. The thermal shutdown detection threshold is typically 175°C with 25°C of hysteresis.

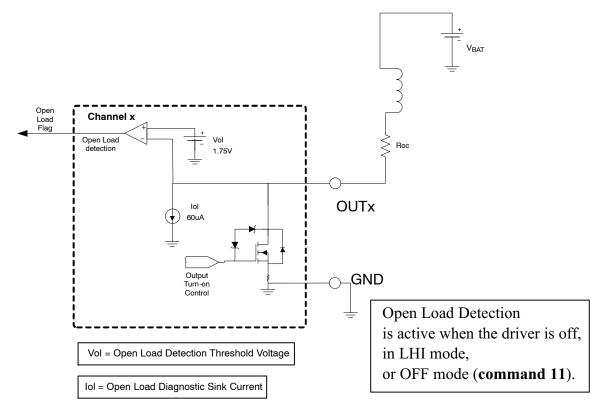

#### **Open Load Detection**

Open Load Detection is achieved for each output with the Open Load Detection Threshold Voltage reference voltage (Vol) and its' corresponding Open Load Diagnostic Sink Current (when the output driver (OUTx) is off). The output driver maintains its' functionality with and without the open bit set (i.e. it can turn on and off).

Roc is the theoretical resistance in series with the external inductive load. During normal operation, the open circuit impedance (Roc) is 0  $\Omega$ . This sets the voltage on OUTx to V<sub>BAT</sub> volts. As long as V<sub>BAT</sub> is above Vol no open circuit fault will be recognized. The voltage appearing on OUTx is a result of V<sub>BAT</sub> and the voltage drop across Roc realized by the current flow created by Iol.

The NCV7240 voltage level trip points are referenced to ground. The threshold range is between 1.0 V and 2.5 V.

With a nominal battery voltage (V<sub>BAT</sub>) of 14 V, the resultant worst case thresholds of detection are as follows.

OpenLoadDiagnosticSinkCurrent = OpenLoad Impedance

$$\frac{(14 \text{ V} - 2.5 \text{ V})}{100 \,\mu\text{A}} = 115 \,\text{k}\Omega \qquad \qquad \frac{(14 \text{ V} - 1.0 \text{ V})}{20 \,\mu\text{A}} = 650 \,\text{k}\Omega$$

Figure 23. Open Load Detection

NOTE: Detection of an open load condition is limited by the Parallel Control Output turn-off time and the Open Load Detection Time specifications. The maximum allowable frequency of operation for PWM (pulse width modulation) using the INx inputs is calculated from the maximum limits of these specifications. INx must be low for longer than the sum of these maximum specifications (50 µsec and 200 µsec). Assuming a 50% duty cycle yields a maximum frequency of operation of  $[1/(2*(50\mu + 200\mu))]=2$  kHz.

#### LED Loads

The NCV7240 features a power up feature for the Global OFF Mode enabling the part to power up in a mode without the open load diagnostic current enabled. This averts any unintended illumination of LED loads during power up.

#### **Programming Features**

The NCV7240 provides two registers.

- 1. Input Register. Input for IC mode state and output driver state control.

- 2. Output Register. Provides diagnostic information on the output driver condition.

#### **Clearing the Fault Registers**

Registers are reset with the following conditions.

- 1. Channel in Standby Mode. (corresponding addressed channel)

- 2. Power-on reset of VDD. (all channels)

- 3. Power-on reset of VDDA. (all channels)

- 4. EN low. (all channels)

- 5. Coming out of Limp Home Mode(LHI). (all channels)

#### SPI-Interface

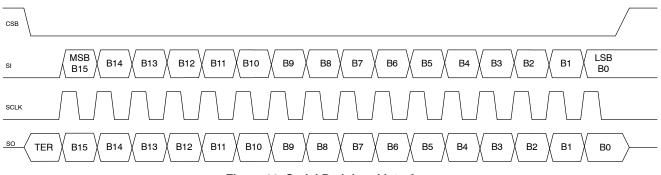

The device provides a 16 bit SPI-interface for output drive control and fault reporting. Data is imported into the NCV7240 through the SI (serial input) pin. Data is exported out of the NCV7240 through the SO (serial output) pin.

The input-frame (SI) (2 bits / channel) is used to command the output stages.

The response frame (SO) provides channel-specific (2 bits / channel) status information fault reporting.

Words should be composed of 16 bits MSB (most significant bit) transmitted first.

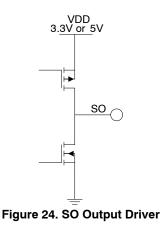

#### **SO Output Driver**

The digital power supply connection (VDD) to the SO output driver enables the system designer interface the NCV7240 to both 3.3V and 5V logic systems. Figure 24 shows the internal connection of the SO pin.

#### Over Load

Each output has an over load detection current of 0.6 A (min) where the drivers turn–off and stay latched off when an over load condition is detected. A latched off condition must be cleared via the SPI port before it can be turned on. An Over load Current Shut–Down Delay Time of 3  $\mu$ s (min) is designed into the IC as a filter allowing for spikes in current which may occur during normal operation and allowing for protection from overload conditions.

Overload is functional during Limp Home (LHI=high). Commands are ignored during Limp Home, but faults can still be retrieved via the SPI.

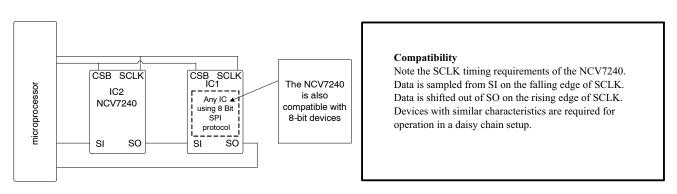

#### Frame Detection Transmission Error (TER)

The NCV7240 detects the number of bits transmitted after CSB goes low. Bit counts not a multiple of 8 (16 bit minimum) are reported as a fault on the TER bit. The transmission error information (TER) is available on SO after CSB goes low until the first rising SCLK edge. Reference the Serial Peripheral Interface diagram (Figure 29).

In addition to unqualified bit counts setting TER = 1, the bit will also be set by

- 1. Coming out of UVLO.

- 2. Transitioning from Limp Home Mode to Global Off Mode.

- 3. Transitioning from Low Iq Mode to Global Off Mode.

The TER bit is cleared by sending a valid SPI command.

The TER bit is multiplexed with the SPI SO data and OR'd with the SI input (Figure 25) to allow for reporting in a serial daisy chain configuration. A TER error bit as a "1" automatically propagates through the serial daisy chain circuitry from the SO output of one device to the SI input of the next during the TER retrieval time when CSB goes low to the 1st rising edge of the clock pulse. The SPI register controls the muxing of the output of the OR gate and the SO' output of the SPI register using the S mux select pin. This is shown in Figures 26 and 27 first as the daisy chained devices connected with no Transmission Error (Figure 26) and subsequently with a Transmission Error in device 1 propagating through to device 2 (Figure 27).

#### **TER False Reporting**

SI should be in a low state during TER status retrieval (from CSB going low to the 1<sup>st</sup> rising edge of the clock pulse) reporting the previous transmission status. Figure 28 demonstrates what could happen if SI is a one during TER status retrieval. In this situation a "1" on SI propagates to SO regardless of the state of TER. Hence a transmission error (TER) could be reported when it is not true.

NOTE: TER is valid from CSB going low until the 1<sup>st</sup> low-to-high transition of SCLK to allow for propagation of the SI signal. Reference Figure 29.

For proper TER status retrieval, SI should be in a low state.

#### **TER Information Retrieval**

TER information retrieval is as simple as bringing CSB high-to-low. No clock signals are required.

#### Figure 29. Serial Peripheral Interface

The timing diagram highlighted in Figure 29 shows the SPI interface communication. Note:

1. The MSB (most significant bit) is the first transmitted bit.

- 2. Data is sampled from SI on the falling edge of SCLK

- 3. Data is shifted out from SO on the rising edge of SCLK

- 4. SCLK should be in a low state when CSB makes a transition.

- 5. SI should be in a low state during TER retrieval time.

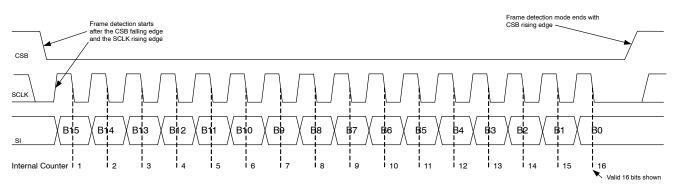

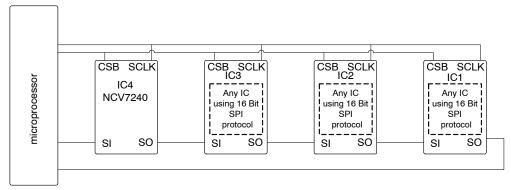

#### Frame Detection

Input word integrity (SI) is evaluated by the use of a frame consistency check. The word frame length is compared to an n \* 8 bit (where n is an integer) acceptable word length (16–bit minimum) before the data is latched into the input register. This guarantees the proper word length has been imported and allows for daisy chain operation applications with 8–bit SPI devices.

The frame length detector is enabled with the CSB falling edge and the SCLK rising edge.

Reference the valid SPI frame shown below. (Figure 29)

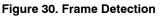

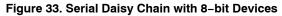

## DAISY CHAIN SETUP

#### **Serial Connection**

Daisy chain setups are possible with the NCV7240. The serial setup shown in Figure 31 highlights the NCV7240 along with any 16 bit device using a similar SPI protocol. Particular attention should be focused on the fact that the first 16 bits which are clocked out of the SO pin when the CSB pin transitions from a high to a low will be the Diagnostic Output Data from the Fault Output Register. These are the bits representing the status of the IC. Additional programming bits should be clocked in which follow the Diagnostic Output bits. The timing diagram shows a typical transfer of data from the microprocessor to the SPI connected IC's.

Figure 31. Serial Daisy Chain

Figure 32. Serial Daisy Chain Timing Diagram

|       | CLK = 16 bits | CLK = 32 bits | CLK = 48 bits | CLK = 64 bits |

|-------|---------------|---------------|---------------|---------------|

| IC4   | 1st CMD       | 2nd CMD       | 3rd CMD       | 4th CMD       |

| IC3   | IC4 DIAG      | 1st CMD       | 2nd CMD       | 3rd CMD       |

| IC2   | IC3 DIAG      | IC4 DIAG      | 1st CMD       | 2nd CMD       |

| IC1   | IC2 DIAG      | IC3 DIAG      | IC4 DIAG      | 1st CMD       |

| micro | IC1 DIAG      | IC2 DIAG      | IC3 DIAG      | IC4 DIAG      |

Table 2 refers to the transition of data over time of the Serial Daisy Chain setup of Figure 31 as word bits are shifted through the system. 64 bits are needed for complete transport of data in the example system. Each column of the table displays the status after transmittal of each word (in 16 bit increments) and the location of each word packet along the way.

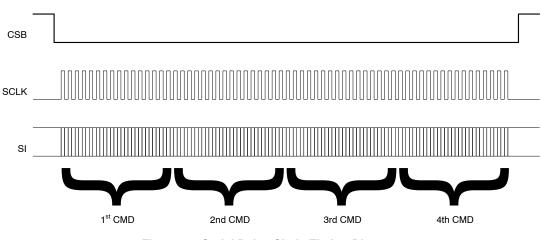

#### 8-bit Devices

The NCV7240 is also compatible with 8 bit devices due to the features of the frame detection circuitry. The internal bit counter of the NCV7240 starts counting clock pulses when CSB goes low. The 1st valid word consists of 16 bits and each subsequent word must be comprised of just 8-bits (reference the Frame Detection Section).

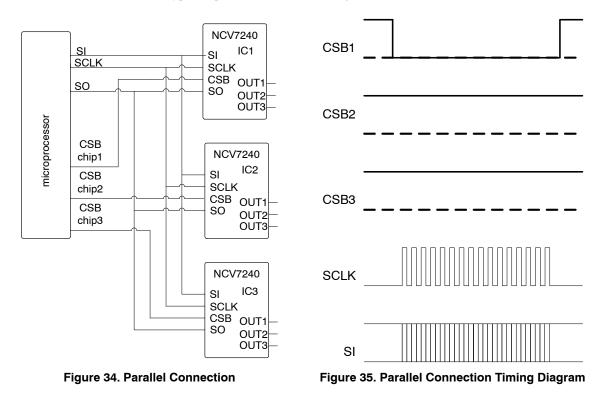

#### **Parallel Connection**

A more efficient way (time focused) to control multiple SPI compatible devices is to connect them in a parallel fashion and allow each device to be controlled in a multiplex mode. Figure 34 shows a typical connection between the microprocessor or microcontroller and multiple SPI compatible devices. In a serial daisy chain configuration, the programming information for the last device in the serial string must first pass through all the previous devices. The parallel control setup eliminates that requirement, but at the cost of additional control pins from the microprocessor for each individual CSB (chip select bar) pin for each controllable device. Serial data is only recognized by the device that is activated through its' respective CSB pin.

Figure 35 shows the waveforms for typical operation when addressing IC1.

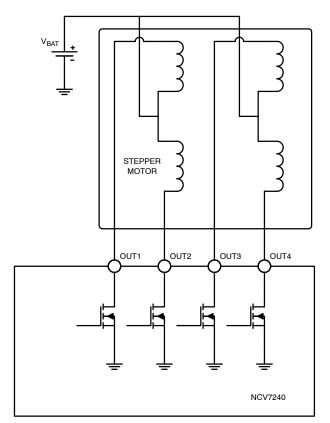

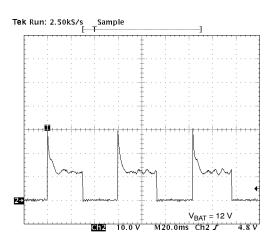

#### **Stepper Motor Operation**

The NCV7240 device is capable of driving stepper motors. Each stepper motor requires 4 low-side drive outputs. Consequently, each NCV7240 device is capable of driving two stepper motors. Figure 36 below illustrates a Unipolar stepper motor setup. For proper operation, the code listed in Table 3 should be used (and repeated) for one way operation (clockwise). For reverse direction, simply reverse the code and repeat (counterclockwise). Outputs 1–4 are utilized for one stepper usage. For a 2<sup>nd</sup> stepper motor, repeat the code used for outputs 1–4 to outputs 5–8. During operation waveforms similar to Figure 37 can be expected on the OUTx pins.

Figure 36. Stepper Motor Operation Setup

#### Table 3. NCV7240 STEPPER MOTOR CODE

Figure 37. Typical Stepper Motor Waveform (Unipolar Portescap 35L048L32U)

| OUT 4 | OUT 3 | OUT 2 | OUT 1 |

|-------|-------|-------|-------|

| OFF   | ON    | OFF   | ON    |

| ON    | OFF   | OFF   | ON    |

| ON    | OFF   | ON    | OFF   |

| OFF   | ON    | ON    | OFF   |

{Repeat}

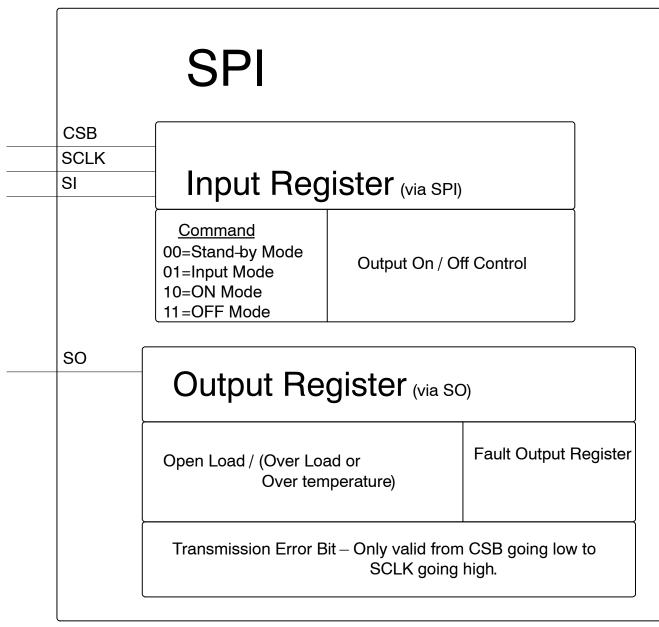

## Figure 38. SPI Register Overview

Figure 38 displays the functions controlled and reported via the SPI port. The input register controls the input source (parallel or SPI) and the SPI input data. The output register transmits the output fault bits and the frame detection integrity.

#### SI SPI Input Data (16-bit serial structure of input word)

The 16-bit data received (SI) is decoded into instructions for each channel per the table below.

After a power-on reset, all register bits are set to a 1.

#### Table 4. SPI INPUT DATA

| Chann | Channel 8 Channel 7 |     | nel 7 | Channel 6 Channel 5 |     |    | Channel 4 Channel 3 |    | nel 3 | Channel 2 |    | Channel 1 |    |    |    |

|-------|---------------------|-----|-------|---------------------|-----|----|---------------------|----|-------|-----------|----|-----------|----|----|----|

| MSE   | 3                   |     |       |                     |     |    |                     |    |       | LS        | в  |           |    |    |    |

| B15   | B14                 | B13 | B12   | B11                 | B10 | B9 | B8                  | B7 | B6    | B5        | B4 | B3        | B2 | B1 | B0 |

#### INPUT DATA REGISTER

| Field                  | Bits                             |         | Descri                                                                                       | ption                         |  |  |  |

|------------------------|----------------------------------|---------|----------------------------------------------------------------------------------------------|-------------------------------|--|--|--|

| channel x<br>(x = 1−8) | 15, 14                           | Command |                                                                                              |                               |  |  |  |

|                        | 13, 12<br>11, 10<br>9, 8<br>7, 6 | 00      | Channel Stand-by Mode<br>Fast channel turn off<br>Corresponding Channel Fault Register reset |                               |  |  |  |

|                        | 5, 4<br>3, 2                     |         | Diagnostic Current                                                                           | Disabled                      |  |  |  |

|                        | 1, 0                             | 01      | Input Mode<br>Channel Input directed to INx.<br>(reference PWM operation section).           |                               |  |  |  |

|                        |                                  |         | Diagnostic Current                                                                           | Enabled in OFF State.         |  |  |  |

|                        |                                  | 10      | ON Mode<br>Channel turned on.                                                                | ·                             |  |  |  |

|                        |                                  |         | Diagnostic Current                                                                           | Disabled                      |  |  |  |

|                        |                                  | 11      | OFF Mode<br>Channel turned off.                                                              |                               |  |  |  |

|                        |                                  |         | Diagnostic Current                                                                           | Enabled (Disabled after POR)* |  |  |  |

\*For proper LED load operation.

#### SO (fault diagnostic retrieval)

Output fault diagnostics from the output fault diagnostic register are shifted out on any 16 bit word clocked into Serial Input (SI).

Only output fault diagnostics and frame detection errors are available through the serial output (SO).

#### Table 5. SPI OUTPUT DATA

| TER                       | OL8 | D8 | OL7 | D7 | OL6 | D6 | OL5 | D5 | OL4 | D4 | OL3 | D3 | OL2 | D2 | OL1 | D1 |

|---------------------------|-----|----|-----|----|-----|----|-----|----|-----|----|-----|----|-----|----|-----|----|

| FAULT DIAGNOSTIC REGISTER |     |    |     |    |     |    |     |    |     |    |     |    |     |    |     |    |

| Field              | Bits                                                | Description                                                                                                                                                                                                                 |

|--------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TER                | CSB high-to-low<br>prior to 1st<br>SCLK low-to-high | Transmission Error.<br>0 Successful transmission in previous communication.<br>1 Frame detection error in previous transmission<br>or exiting Limp Home Mode, exiting UVLO Mode, or exiting Low Iq mode to Global Off Mode. |

| Oln<br>(n = 1 – 8) | 1, 3, 5,<br>7, 9, 11,<br>13, 15                     | Open Load<br>0 Normal Operation<br>1 Fault detected                                                                                                                                                                         |

| Dn<br>(n = 1 – 8)  | 0, 2, 4,<br>6, 8, 10,<br>12, 14                     | Over Load or Over Temperature<br>0 Normal Operation<br>1 Fault detected                                                                                                                                                     |

#### **Table 6. FAULT CONDITIONS**

| Output<br>Fault<br>Condition | Fault<br>Memory | Miscellaneous                                                                                                                                                                                                 |

|------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Open Load                    | Latched         | Detected in Driver Off State (1.75 V [Typ] threshold) when detection is enabled.<br>Reported in Output Fault Diagnostics Register until cleared via the SPI port.<br>Output will maintain turn-on capability. |

| Short to<br>Ground           | Latched         | Detected as part of the Open Load circuitry described above.                                                                                                                                                  |

| Short to V <sub>bat</sub>    | N/A             | Protected via Over Load and Over Temperature functions.                                                                                                                                                       |

| Over Load                    | Latched         | Detected in Driver On State<br>0.6 A [min], 1.3 A [max].<br>A latched off condition must be cleared via the SPI port before it can be turned on.                                                              |

| Over<br>Temperature          | Latched         | Detected in IC On State ( $T_J = 175^{\circ}C$ [Typ])<br>A latched off condition must be cleared via the SPI port before it can be turned on.                                                                 |

#### **DEVICE ORDERING INFORMATION**

| Part Number   | Package Type         | Shipping <sup>†</sup> |  |

|---------------|----------------------|-----------------------|--|

| NCV7240DPR2G  |                      |                       |  |

| NCV7240ADPR2G | SSOP-24<br>(Pb-Free) | 2500 / Tape & Reel    |  |

| NCV7240BDPR2G |                      |                       |  |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 98AON52092E Electronic versions are uncontrolled except when accessed directly from the Document Rep<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|--|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SSOP24 NB                                                                                                                                                                               | PAGE 1 OF 1 |  |  |  |  |  |  |

| ON Semiconductor and (iii) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights or others. |                                                                                                                                                                                         |             |  |  |  |  |  |  |

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales