#### 1.8V 20Gbps DP2.0 Linear ReDriver with AUX Listener & I2C Control

#### Features

- 4-to-4 Linear ReDriver<sup>™</sup> Channel Configuration with CTLE Gain Compensation up to 16dB @20Gbps

- Supports 4-lane DP2.0 (UHBR20/UHBR13/UHBR10)/HDBR3/ HBR2/RBR

- Ultra low Latency (< 300ps) for better Interoperability and Data throughput

- Individual Controls on CTLE Gain (6 to 16.2dB), Flat Gain (-4 to +2 dB)

- Integrated AUX Channel Listener for D3 Power Saving Mode

- I2C Slave Support with Speed up to 1MHz •

- Low Power DisplayPort Active (<350mW), D3 Power Down Mode (1.8mW)

- Single Power Supply: 1.8V +/-5%

- Industrial Temperature Support: -40°C to +85°C

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3) •

- For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/104/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please contact us or your local Diodes representative. https://www.diodes.com/quality/product-definitions/

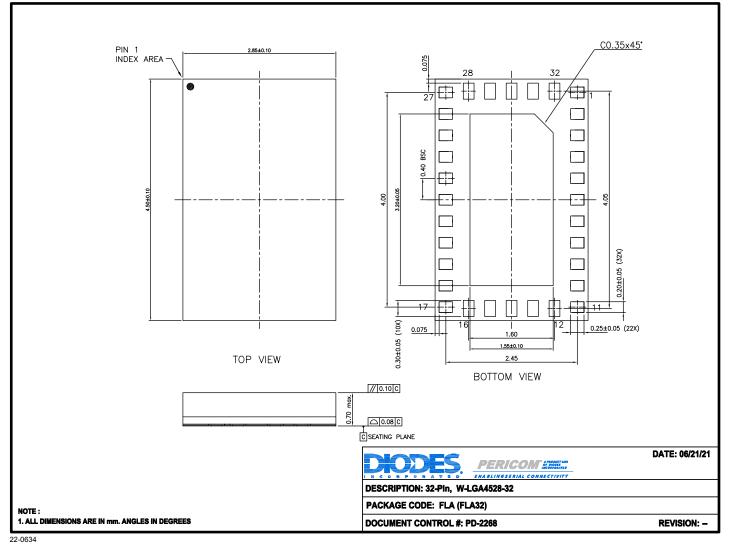

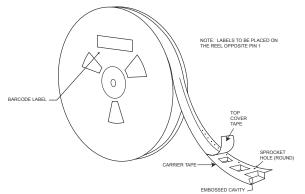

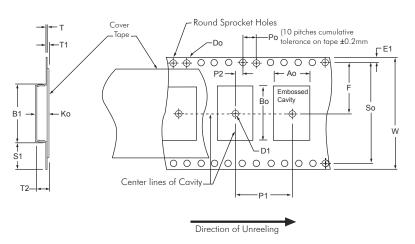

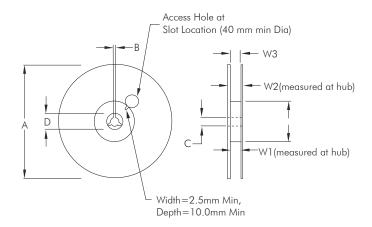

Packaging (Pb-free & Green):

Tiny 32-pin, WLGA, 2.85 x 4.5 mm (0.4 mm pitch) (FLA)

### Applications

- Laptop, Desktop and AIO PCs

- Workstation and Server

- **Docking Station**

- **Display Monitor**

- Gaming Console

- Active Cable

### Description

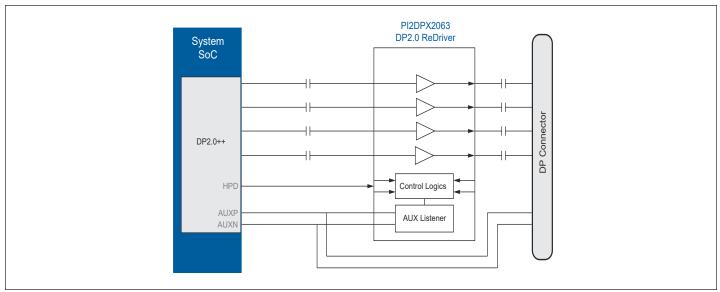

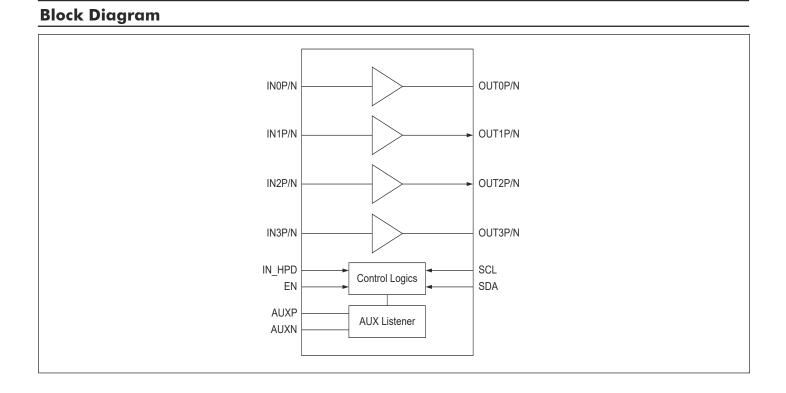

The DIODES<sup>™</sup> PI2DPX2063 is a 20Gbps DP2.0/DP1.4 linear Re-Driver in a 4-to-4 configuration operated by a 1.8v power supply. The device supports UHBR20 (DP2.0 20Gbps), UHBR13.5 (DP2.0 13.5Gbps), UHBR10 (DP2.0 10Gbps), HBR3 (DP1.4 8.1Gbps), HBR2 (DP1.2 5.4Gbps), HBR(DP1.1 2.7Gbps) and RBR(DP1.0 1.62Gbps) under various DisplayPort speeds. With the on-chip AUX channel listener, the device can automatically monitor the system operation status to enter D3 power saving mode.

The non-blocking linear ReDriver design ensures that the differential signals conveying pre-shoot and de-emphasis equalization waveforms from the transmitter side to the receiver side help optimize the overall channel link adjustment conducted by the system transmitter and receiver that has been equipped with DFE. The CTLE equalizers are implemented at the inputs of the ReDriver to compensate the channel loss and reduce the ISI jitters. The programmable flat gain adjustments support the eye diagram opening.

The CTLE EQ gains and flat gains are individually programmable on each channel for flexible tuning via I2C register settings.

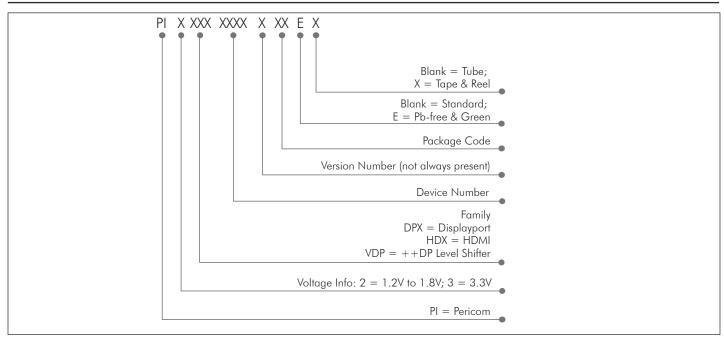

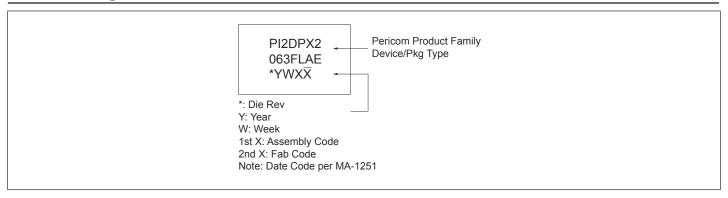

### **Ordering Information**

| Ordering Number | Package Code | Description          |

|-----------------|--------------|----------------------|

| PI2DPX2063FLAEX | FLA          | 32-Pin, W-LGA4528-32 |

| Notes:          |              |                      |

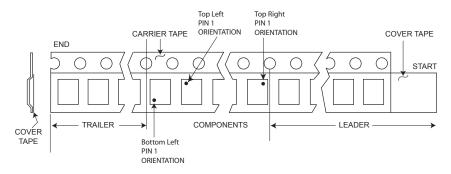

1. E = Pb-free and Green 2. X suffix = Tape/Reel

Notes:

2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free. 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

ReDriver is a trademark of Diodes Incorporated.

<sup>1.</sup> No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

DIODES is a trademark of Diodes Incorporated in the United States and other countries.

The Diodes logo is a registered trademark of Diodes Incorporated in the United States and other countries.

## **Revision History**

| Date        | Revision | Description                                                             |

|-------------|----------|-------------------------------------------------------------------------|

| August 2021 | 1        | Preliminary Datasheet Release                                           |

|             |          | Updated Absolute Maximum Ratings<br>Updated CTLE Equalization Gain      |

| July 2022   | 2        | Updated Feature<br>Updated Configuration Table<br>Updated Diodes Format |

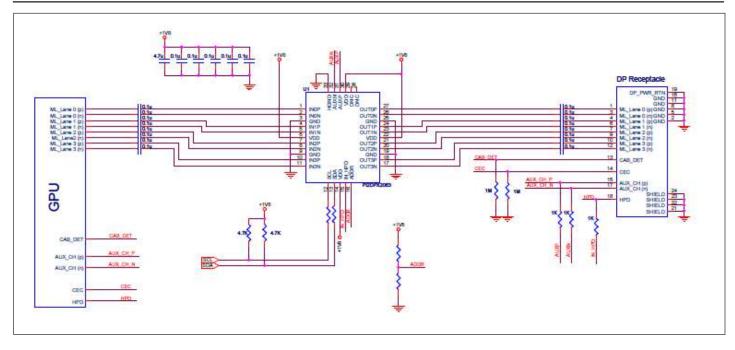

PI2DPX2063 in DP2.0 PC Motherboard Application

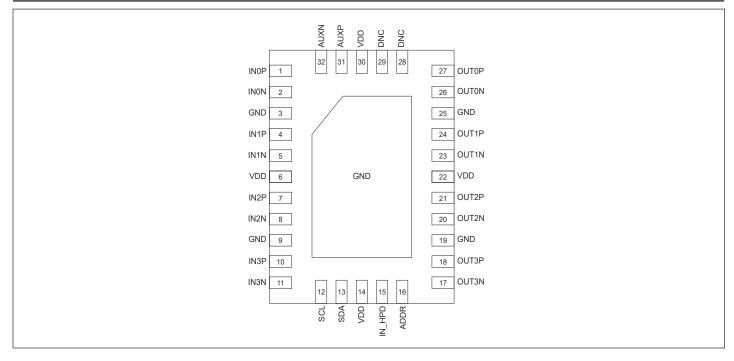

## **Pin Configuration (Top-Side View)**

### **Pin Description**

| Pin #                       | Pin Name | Туре   | Description                                                                                                           |  |  |  |  |  |

|-----------------------------|----------|--------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Power and GND               |          |        |                                                                                                                       |  |  |  |  |  |

| 6, 14, 22, 30               | VDD      | Power  | 1.8V power supply, ±5%                                                                                                |  |  |  |  |  |

| 3, 9, 19, 25, Center<br>Pad | GND      | Ground | Supply ground                                                                                                         |  |  |  |  |  |

| Control Pins                |          |        |                                                                                                                       |  |  |  |  |  |

| 12                          | SCL      | I      | SCL is I2C control bus clock. Open drain structure.                                                                   |  |  |  |  |  |

| 13                          | SDA      | I/O    | SDA is I2C control bus data. Open drain structure.                                                                    |  |  |  |  |  |

|                             | IN_HPD   | Ι      | Hot plug detection from Sink.                                                                                         |  |  |  |  |  |

| 15                          |          |        | With I2C (IN_HPD_HIZ) selectable internal 300k $\Omega$ pull-down resistor.                                           |  |  |  |  |  |

|                             |          |        | IN_HPD_HIZ='0', 300k $\Omega$ pull-down. Otherwise, the pin is HiZ                                                    |  |  |  |  |  |

| 16                          | ADDR     | I      | The I2C address select. 4-level input pin. With internal 100K $\Omega$ pull-up and 200K $\Omega$ pull-down resistors. |  |  |  |  |  |

|                             |          |        | External Pulldown resistor value is $68 \mathrm{K}\Omega$ .                                                           |  |  |  |  |  |

| High Speed I/O Pin          | ns       |        |                                                                                                                       |  |  |  |  |  |

| 18,                         | OUT3P,   |        |                                                                                                                       |  |  |  |  |  |

| 17                          | OUT3N    |        | Channel CML output terminals.                                                                                         |  |  |  |  |  |

| 27,                         | OUT0P,   | 0      | With selectable output termination between 50 $\Omega$ to VDD, 6k $\Omega$ to internal Vbi-<br>asTx or Hi-Z           |  |  |  |  |  |

| 26                          | OUT0N    |        |                                                                                                                       |  |  |  |  |  |

### **Pin Description Cont.**

| Pin #                 | Pin Name   | Туре | Description                                                                                                   |  |

|-----------------------|------------|------|---------------------------------------------------------------------------------------------------------------|--|

| 21,                   | OUT2P,     |      |                                                                                                               |  |

| 20                    | OUT2N      |      | Channel CML output terminals.                                                                                 |  |

| 24,                   | OUT1P,     | 0    | With selectable output termination between $50\Omega$ to VDD, $6K\Omega$ to internal VbiasTx or Hi-Z          |  |

| 23                    | OUT1N      |      |                                                                                                               |  |

| 1,                    | INOP,      |      |                                                                                                               |  |

| 2                     | INON       | т    | Channel CML input terminals.                                                                                  |  |

| 10,                   | IN3P,      | I    | With selectable input termination between $50\Omega$ to internal VbiasRx, or $78K\Omega$ to internal VbiasRx. |  |

| 11                    | IN3N       |      |                                                                                                               |  |

| 4,                    | IN1P,      |      |                                                                                                               |  |

| 5                     | IN1N       | т    | Channel CML input terminals.                                                                                  |  |

| 7,                    | IN2P,      | I    | With selectable input termination between $50\Omega$ to internal VbiasRx, or $78K\Omega$ to internal VbiasRx. |  |

| 8                     | IN2N       |      |                                                                                                               |  |

| Side Band Signal Pins |            |      |                                                                                                               |  |

| 29, 28                | DNC        |      | Do Not connect                                                                                                |  |

| 31, 32                | AUXP, AUXN | I/O  | DisplayPort AUX CH differential signal connections                                                            |  |

## **Operation Mode**

#### Table 1. Configuration Table

| OP_MODE<3:0>    | IN0   | IN1   | IN2   | IN3   | AUXP | AUXN | Mode                      |  |

|-----------------|-------|-------|-------|-------|------|------|---------------------------|--|

| 0000-0001       | _     | _     | _     | -     | _    | -    | Reserved                  |  |

|                 | OUT0  | OUT1  | OUT2  | OUT3  |      |      |                           |  |

| 0010            | (DP0) | (DP1) | (DP2) | (DP3) | _    | -    | 4-lane DP + AUX           |  |

| 0011            | OUT0  | OUT1  | OUT2  | OUT3  | _    | _    | 4-lane DP + AUX (flipped) |  |

| 0011            | (DP3) | (DP2) | (DP1) | (DP0) |      | _    | 4-lane DI + AOA (inpped)  |  |

| <0100> ~ <1111> | _     | _     | _     | -     | _    | —    | Reserved                  |  |

Notes: 1) <0010> default at power on.

#### I/O Termination Resistance under Different Conditions

| Symbol                     | Parameter                           | Resistance     | Units |

|----------------------------|-------------------------------------|----------------|-------|

| RX Terminal                |                                     |                |       |

| R <sub>in-pd</sub>         | Input res at EN=0                   | 78k to GND     | Ω     |

| R <sub>in-Active</sub>     | Input res at active mode condition  | 50 to VbiasRx1 | Ω     |

| R <sub>in-DP-standby</sub> | Input res in DP standby mode        | 78k to GND     | Ω     |

| R <sub>in-DP-active</sub>  | Input res in DP active mode         | 50 to VbiasRx1 | Ω     |

| R <sub>in-DP-D3</sub>      | Input res in DP D3 mode             | 78k to GND     | Ω     |

| TX Terminal                |                                     |                |       |

| R <sub>out-pd</sub>        | Output res at EN=0                  | 78k to GND     | Ω     |

| Rout-Active                | Output res at active mode condition | 50 to VDD      | Ω     |

| Rout-DP-standby            | Output res in DP standby mode       | 78k to GND     | Ω     |

| Rout-DP-active             | Output res in DP active mode        | 50 to VDD      | Ω     |

| R <sub>out-DP-D3</sub>     | Output res in DP D3 mode            | 78k to GND     | Ω     |

### **DisplayPort Mode**

By default, all channels will go to active mode if HPD bit = 1. The ON/OFF of each DP channel is controlled by the Aux lane count.

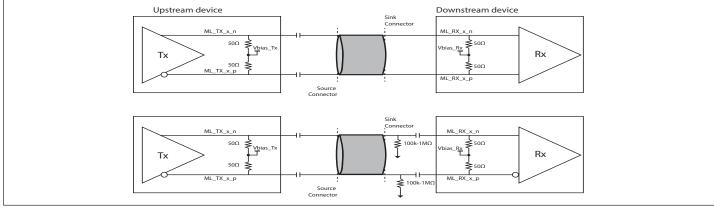

#### Figure 1. DisplayPort Main Link Connection Diagram

#### **DisplayPort Main Link**

The electrical sub-block of a DP Main-Link consists of up to four differential pairs. The DP TX drives doubly terminated, AC-coupled differential pairs in a manner compliant with the Main-Link Transmitter electrical specification.

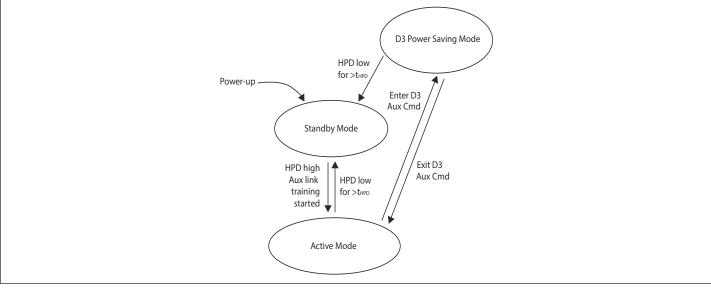

Figure 2. DisplayPort Operation Modes

| ,   | Table 2. Des | cription of DP Operatin | g | Mode |

|-----|--------------|-------------------------|---|------|

| . Г |              |                         |   |      |

| PM_State                                                                      | Mode                 | Description                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 Standby Mode Low power consumption (AUX listener is OFF); Main Link outputs |                      | Low power consumption (AUX listener is OFF); Main Link outputs are disabled                                                                                                                                                                                                                                                                            |

| 2                                                                             | Active Mode          | Data transfer (normal operation);<br>AUX listener is active. The AUX listener is actively monitoring for Link Training unless it is<br>disabled through I2C interface. After power-up and in active mode, all Main Link outputs are<br>enabled. AUX Link Training is necessary to overwrite the DPCD registers to enable/disable<br>Main Link outputs. |

| 3                                                                             | D3 Power Saving Mode | Low power consumption(AUX listener is active); Main Link outputs are disabled                                                                                                                                                                                                                                                                          |

## **CTLE Equalization, Flat Gain and Chip Enable Controls**

Table 3. CTLE Equalization Gain (Typical Values at FG = 0dB)

| I2C Register Setting EQ<2:0> |       |       | Equalizer Setting (dB) |               |               |               |               |

|------------------------------|-------|-------|------------------------|---------------|---------------|---------------|---------------|

| EQ<2>                        | EQ<1> | EQ<0> | @1.35GHz               | @2.5GHz       | @4GHz         | @5GHz         | @10GHz        |

| 0                            | 0     | 0     | -0.1 (Default)         | 0.1 (Default) | 0.7 (Default) | 1.3 (Default) | 6.0 (Default) |

| 0                            | 0     | 1     | 0.0                    | 0.6           | 1.6           | 2.5           | 8.5           |

| 0                            | 1     | 0     | 0.2                    | 1.3           | 2.8           | 4.1           | 10.8          |

| 0                            | 1     | 1     | 0.6                    | 2.2           | 4.3           | 5.8           | 12.7          |

| 1                            | 0     | 0     | 1.1                    | 3.5           | 6.0           | 7.7           | 14.2          |

| 1                            | 0     | 1     | 1.7                    | 4.8           | 7.6           | 9.3           | 15.2          |

| 1                            | 1     | 0     | 2.6                    | 6.3           | 9.2           | 10.8          | 15.8          |

| 1                            | 1     | 1     | 3.5                    | 7.5           | 10.4          | 11.8          | 16.2          |

Note: F: Floating, R: External resistor to ground.

#### Table 4. Flat Gain Setting (FG)

| I2C Regist | er FG[1:0] | Flat Gain Setting |

|------------|------------|-------------------|

| 0          | 0          | -4 dB             |

| 0 1        |            | -2 dB             |

| 1          | 0          | +0 dB (Default)   |

| 1          | 1          | +2 dB             |

### **Maximum Ratings**

(Above which useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature65°C to +150°C                        |

|----------------------------------------------------------|

| Junction Temperature                                     |

| Supply Voltage to Ground Potential0.5V to VDD+0.3V       |

| Voltage Input to High Speed Differential Pins0.5V to VDD |

| Voltage Input to Low Speed Pins (SCL, SDA)0.5V to +3.3V  |

| Voltage Input to Low Speed Pins (AUXP/N)0.5V to +3.3V    |

| ESD, HBM ±4000V                                          |

| ESD, CDM±1000V                                           |

|                                                          |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Thermal Information**

| Symbol   | Parameter                              | 32-Pin X2QFN Package | Units |

|----------|----------------------------------------|----------------------|-------|

| Theta JA | Junction to Ambient Thermal Resistance | 49.7                 | °C/W  |

#### **Recommended Operating Conditions**

| Symbol                | Parameter                      | Min.   | Тур. | Max. | Units |

|-----------------------|--------------------------------|--------|------|------|-------|

| V <sub>DD</sub>       | Supply Voltage                 | 1.71   | 1.8  | 1.89 | V     |

| V <sub>DD_Noise</sub> | Power Supply Noise Up to 50MHz |        |      | 50   | mVpp  |

| V <sub>RX_CM</sub>    | Input Source Common-Mode Noise |        |      | 150  | mVpp  |

| Cac_coupling          | System AC Coupling Capacitance | 75     |      | 265  | nF    |

| T <sub>A</sub>        | Ambient Temperature            | -40(1) |      | +85  | °C    |

Note:

1. The minimum temperature -40°C guaranteed by design

#### **Power Consumption**

| Symbol              | Parameter                       | Min. | Тур. | Max. | Units |

|---------------------|---------------------------------|------|------|------|-------|

| I <sub>ON_4DP</sub> | 4-lane DP2.0                    |      | 160  | 220  | mA    |

| I <sub>D3</sub>     | Display Port D3 power down mode |      | 1    | 1.6  | mA    |

| I <sub>ENB</sub>    | Disabled mode ( EN= Low)        |      | 8    | 30   | uA    |

#### **AC/DC Characteristics** $(VDD = 1.8 \pm 5\%, T_A = -40^{\circ}C \text{ to } 85^{\circ}C)$

| Symbol                  | Parameter                                                   | Conditions | Min. | Тур. | Max. | Units |  |  |  |  |

|-------------------------|-------------------------------------------------------------|------------|------|------|------|-------|--|--|--|--|

| V <sub>DD</sub>         | Supply Voltage                                              | —          | 1.71 | 1.8  | 1.89 | V     |  |  |  |  |

| Receiver (RX            | Receiver (RX) (100 Ω differential) Electrical Specification |            |      |      |      |       |  |  |  |  |

| R <sub>RX-DIFF-DC</sub> | DC Differential Input Impedance                             |            | 72   |      | 120  | Ω     |  |  |  |  |

| Symbol                                            | Parameter                                                                                                | Conditions                                                                         | Min.   | Тур. | Max. | Units  |

|---------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------|------|------|--------|

| R <sub>RX-SINGLE-</sub><br>DC                     | DC single ended input impedance<br>to guarantee RxDet                                                    | Measured with respect to<br>GND over a voltage of 500mV<br>max                     | 18     |      | 30   | Ω      |

| Z <sub>RX-HIZ-DC-</sub><br>PD                     | DC input CM input impedance for<br>V>0 during reset or power down                                        | (Vcm=0 to 500mV)                                                                   | 25     |      |      | kΩ     |

| Cac_coupling                                      | AC coupling capacitance                                                                                  |                                                                                    | 75     |      | 265  | nF     |

| V <sub>RX-CM-AC-P</sub>                           | Rx common mode peak voltage                                                                              | AC up to 5GHz                                                                      |        |      | 150  | mVpeak |

| V <sub>RX-CM-DC-</sub><br>Active-Idle-<br>Delta-P | Common mode peak voltage<br> AvgU0 (  VTX-D+ + VTX-D-  )/2 –AvgU1<br>(  VTX-D+ + VTX-D-  )/2             |                                                                                    |        |      | 200  | mVpeak |

| Transmitter                                       | (TX) Electrical Specification                                                                            |                                                                                    |        |      |      |        |

| V <sub>TX-DIFF-PP</sub>                           | Output differential p-p voltage<br>Swing                                                                 | Differential Swing<br> V <sub>TX-D+</sub> - V <sub>TX-D-</sub>                     |        | 1    |      | Vppd   |

| R <sub>TX-DIFF-DC</sub>                           | DC Differential TX Impedance                                                                             |                                                                                    | 72     |      | 120  | Ω      |

| V <sub>TX-RCV-DET</sub>                           | The amount of Voltage change al-<br>lowed during RxDet                                                   | Type-C Tx Spec +/-60mA                                                             |        |      | 600  | mV     |

| Cac-coupling                                      | AC coupling capacitance                                                                                  |                                                                                    | 75     |      | 265  | nF     |

| R <sub>TX-DC-CM</sub>                             | Common mode DC output Imped-<br>ance                                                                     |                                                                                    | 18     |      | 30   | Ω      |

| I <sub>TX-SHORT</sub>                             | Transmitter short circuit current<br>limit                                                               |                                                                                    |        |      | 60   | mA     |

| V <sub>TX-C</sub>                                 | Common-Mode Voltage                                                                                      | $ V_{TX-D+} + V_{TX-D-} /2$                                                        | VDD-1V |      | VDD  | V      |

| V <sub>TX-DC-CM</sub>                             | Instantaneous allowed DC com-<br>mon mode voltage at the connector<br>side of the AC coupling capacitors | $ V_{TX-D+} + V_{TX-D-} /2$                                                        | 0      |      | VDD  | V      |

| V <sub>TX-CM-AC-</sub><br>PP-Active               | Active mode TX AC common<br>mode voltage                                                                 | $V_{TX-D+} + V_{TX-D-}$ for both time and amplitude                                |        |      | 100  | mVpp   |

| VTX-Idle-Diff-<br>AC-pp                           | Idle mode AC common mode delta<br>voltage   V <sub>TX-D+</sub> –V <sub>TX-D-</sub>                       | Between D+ and D- in idle<br>mode. Use the HPF to remove<br>DC components. =1/LPF. |        |      | 10   | mVppd  |

| V <sub>TX-Idle-Diff-</sub><br>DC                  | Idle mode DC common mode delta<br>voltage   V <sub>TX-D+</sub> –V <sub>TX-D-</sub>                       | Between D+ and D- in idle<br>mode. Use the LPF to remove<br>AC components. =1/HPF. |        |      | 10   | mV     |

| Channel Perf                                      | formance                                                                                                 |                                                                                    |        |      |      |        |

| T <sub>pd</sub>                                   | Latency                                                                                                  | From input to output                                                               |        | 25   | 150  | ps     |

#### AC/DC Characteristics Cont.

| Symbol                                                                                                                           | Parameter                               | Conditions                                             | Min.       | Тур.  | Max.                        | Units               |  |

|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------|------------|-------|-----------------------------|---------------------|--|

|                                                                                                                                  |                                         | EQ<2:0> = 000                                          |            | 6     |                             |                     |  |

|                                                                                                                                  |                                         | EQ<2:0> = 001                                          |            | 8.5   |                             |                     |  |

|                                                                                                                                  |                                         | EQ<2:0> = 010                                          |            | 10.8  |                             |                     |  |

|                                                                                                                                  | Peaking gain (Compensation              | EQ<2:0> = 011                                          |            | 12.7  |                             | dF                  |  |

| G <sub>P_USB</sub>                                                                                                               | at 10GHz, relative to 100MHz,           | EQ<2:0> = 100                                          |            | 14.2  |                             | dB                  |  |

|                                                                                                                                  | 100mV <sub>p-p</sub> sine wave input)   | EQ<2:0> = 101                                          |            | 15.2  |                             |                     |  |

|                                                                                                                                  |                                         | EQ<2:0> = 110                                          |            | 15.8  |                             |                     |  |

|                                                                                                                                  |                                         | EQ<2:0> = 111                                          |            | 16.2  |                             |                     |  |

|                                                                                                                                  |                                         | Variation around typical                               | -2         |       | +2                          | dB                  |  |

|                                                                                                                                  |                                         | FG<1:0> = 00                                           |            | -4    |                             |                     |  |

|                                                                                                                                  |                                         | FG<1:0> = 01                                           |            | -2    |                             | 10                  |  |

| G <sub>F</sub>                                                                                                                   | Flat gain (100MHz, EQ<2:0>=000)         | FG<1:0> = 10                                           |            | 0     |                             | dB                  |  |

| GP_USB<br>GF<br>Vsw_100M<br>Vsw_10G<br>DDNEXT<br>DDFEXT <sup>(2)</sup><br>VNOISE_IN<br>VNOISE_IN<br>VNOISE_OUT<br>S11DM<br>S11CM |                                         | FG<1:0> = 11                                           |            | +2    |                             |                     |  |

|                                                                                                                                  |                                         | Variation around typical                               | -2         |       | +2 dB<br>+2 dB<br>910 mVppo | dB                  |  |

| V <sub>sw_100M</sub>                                                                                                             | Output linear swing (at 100MHz)         | EQ<2:0>=000                                            |            | 910   |                             | mVppd               |  |

| V <sub>sw_10G</sub>                                                                                                              | Output linear swing (at 10GHz)          | EQ<2:0>=000                                            |            | 800   |                             | mVppd               |  |

| DDNEXT                                                                                                                           | Differential near-end crosstalk         | 100MHz to 10GHz, Fig. 6                                |            | -30   |                             | dB                  |  |

| DDFEXT <sup>(2)</sup>                                                                                                            | Differential far-end crosstalk          | 100MHz to 10GHz, Fig. 7                                |            | -30   |                             | dB                  |  |

|                                                                                                                                  |                                         | 100MHz to 10GHz,<br>EQ<2:0>=000, FG<1:0>=10,<br>Fig. 8 |            | 0.6   |                             |                     |  |

| V NOISE_IN                                                                                                                       | Input-referred noise                    | 100MHz to 10GHz,<br>EQ<2:0>=111, FG<1:0>=10,<br>Fig. 8 |            | 0.3   |                             | mV <sub>RMS</sub>   |  |

| X7                                                                                                                               | Output of and a size                    | 100MHz to 10GHz,<br>EQ<2:0>=000, FG<1:0>=10,<br>Fig. 8 |            | 0.3   |                             |                     |  |

| V NOISE_OUT                                                                                                                      | Output-referred noise                   | 100MHz to 10GHz,<br>EQ<2:0>=111, FG<1:0>=10,<br>Fig. 8 |            | 0.5   |                             | - mV <sub>RMS</sub> |  |

| S11DM                                                                                                                            | Input differential mode return loss     | 10MHz to 10GHz differential mode                       | -11.5 -8.1 |       | dB                          |                     |  |

| S11CM                                                                                                                            | Input common mode return loss           | 1GHz to 10GHz common<br>mode                           | -10 -5     |       | dB                          |                     |  |

| S22DM                                                                                                                            | Output differential mode return<br>loss | 10MHz to 10GHz differential mode                       |            | -12.5 | -8.1                        | dB                  |  |

| S22CM                                                                                                                            | Output common mode return loss          | 1GHz to 10GHz common mode                              |            | -8    | -4                          | dB                  |  |

#### AC/DC Characteristics Cont.

| Symbol                             | Parameter                                                 | Conditions                                                                       | Min.   | Typ. | Max.  | Units |

|------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------|--------|------|-------|-------|

| DisplayPort                        | Electrical Specification                                  |                                                                                  |        |      |       |       |

| V <sub>TX-C</sub>                  | Common-Mode Voltage                                       | $ V_{TX-D+} + V_{TX-D-} /2$                                                      | VDD-1V |      | VDD   | V     |

| V <sub>TX-AC-CM</sub><br>HBR_RBR   | TX AC common mode voltage for<br>HRB and RBR              | Measured using an 8b/10b                                                         |        |      | 20    | mVrms |

| V <sub>TX-AC-</sub><br>CM_HBR2     | TX AC common mode voltage for<br>HBR2                     | pattern with 50% transition<br>density                                           |        |      | 30    | mVrms |

| V <sub>TX-DIFFp-p-</sub><br>Level0 | Differential peak-to-peak output<br>voltage swing Level 0 | Tested with Pre-emphasis at<br>Level 0= 0dB<br>Level 1= 3.5dB<br>Level 2= 6.0 dB | 0.34   | 0.4  | 0.46  | V     |

| V <sub>TX-DIFFp-p-</sub><br>Level1 | Differential peak-to-peak output<br>voltage swing Level 1 |                                                                                  | 0.51   | 0.6  | 0.68  | V     |

| V <sub>TX-DIFFp-p-</sub><br>Level2 | Differential peak-to-peak output<br>voltage swing Level 2 |                                                                                  | 0.69   | 0.8  | 0.92  | V     |

|                                    | UHBR20(20Gbps) TP2                                        |                                                                                  |        |      | 0.45  | UI    |

| F                                  | UHBR13(13.5Gbps) TP2                                      |                                                                                  |        |      | 0.45  | UI    |

|                                    | UHBR10(10Gbps) TP2                                        | Measured at Transmit output.                                                     |        |      | 0.38  | UI    |

| Tj TX Total<br>Iitter              | HBR3 (8.1Gbps)                                            | Prechannel loss from 2.5dB                                                       |        |      | 0.27  | UI    |

| Jitter                             | HBR2 (5.4Gbps)                                            | to 13dB                                                                          |        |      | 0.27  | UI    |

|                                    | HBR (2.7Gbps)                                             | -                                                                                |        |      | 0.294 | UI    |

|                                    | RBR (1.62Gbps)                                            |                                                                                  |        |      | 0.18  | UI    |

| AUX Listene                        | er Electrical Specification                               |                                                                                  |        |      |       |       |

| C <sub>in</sub>                    | Input capacitance at AUXP or<br>AUXN                      |                                                                                  |        |      | 10    | pF    |

| VT <sub>(AUX_lis-</sub><br>tener)  | Threshold of the AUX listener                             | VCC = 1.8V                                                                       | 100    |      | 220   | mVPPd |

Note:

1. Measured using a vector-network analyzer (VNA) with -30dBm power level applied to the adjacent input. The VNA detects the signal at the output of the victim channel. All other inputs and outputs are terminated with  $50\Omega$ .

2. Subtract the channel gain from the total gain to derive the actual crosstalk

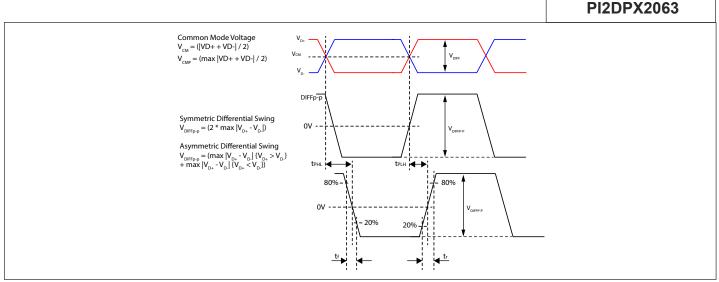

Figure 4. Definition of Peak-to-peak Differential Voltage

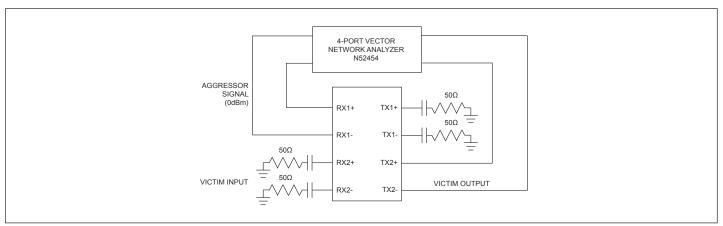

Figure 5. NEXT Crosstalk Definition

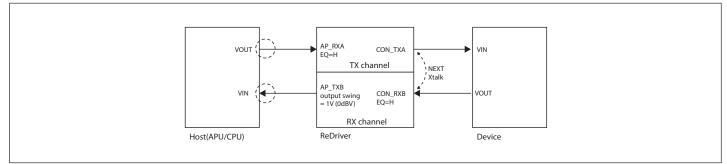

Figure 6. NEXT Channel-isolation Test Configuration

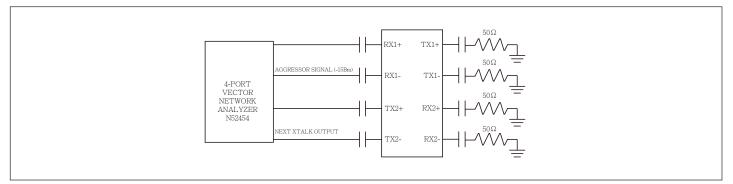

Figure 7. NEXT Channel-isolation Test Configuration

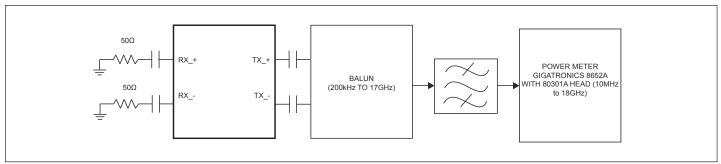

**Figure 8. Noise Test Configuration**

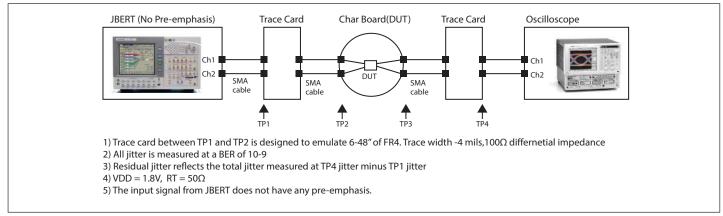

Figure 9. Channel Measurement Setup

Figure 10. High-speed Channel Test Circuit

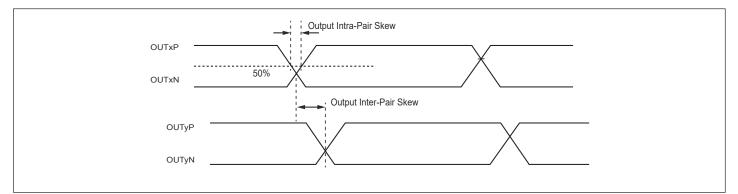

Figure 11. Intra and Inter-pair Differential Skew Definition

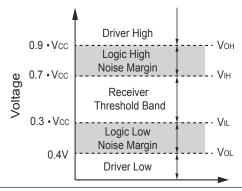

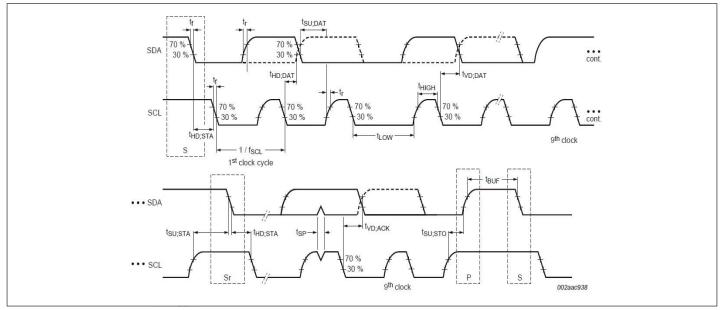

# **I2C Electrical Specification and Timing**

| Characteristics of the SDA | and SCL I/O Stages |

|----------------------------|--------------------|

|----------------------------|--------------------|

|                  |                                                                         |                                                                               | This S              | ilicon       | Fast-Mo                       | IIn:to       |       |

|------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------|--------------|-------------------------------|--------------|-------|

| Symbol           | Parameter                                                               | Conditions                                                                    | Min.                | Max.         | Min.                          | Max.         | Units |

| V <sub>IL</sub>  | LOW-level input voltage                                                 |                                                                               | -0.5                | $0.3 V_{DD}$ | -0.5                          | $0.3 V_{DD}$ | V     |

| V <sub>IH</sub>  | HIGH-level input voltage                                                |                                                                               | $0.7 V_{DD}$        |              | $0.7 V_{DD}$                  |              | V     |

| V <sub>hys</sub> | Hysteresis of Schmitt trigger inputs                                    |                                                                               | 0.05V <sub>DD</sub> |              | 0.05V <sub>DD</sub>           |              | V     |

| V <sub>OL1</sub> | LOW-level output voltage 1                                              | Open-drain or open-col-<br>lector at 3mA sink current;<br>V <sub>DD</sub> >2V | 0                   | 0.4          | 0                             | 0.4          | V     |

| I <sub>OL</sub>  | LOW-level output current                                                | V <sub>OL</sub> =0.4V                                                         | 20                  |              | 20                            |              | mA    |

| t <sub>of</sub>  | output fall time from $V_{IHmin}$ to $V_{ILmax}$                        |                                                                               | 12                  | 120          | 20×(V <sub>DD</sub><br>/5.5V) | 120          | ns    |

| t <sub>SP</sub>  | Pulse width of spikes that<br>must be suppressed by the<br>input filter |                                                                               | 0                   | 50           | 0                             | 50           | ns    |

| Ii               | Input current each I/O pin                                              | $0.1 V_{DD} < V_I < 0.9 V_{DDmax}$                                            | -10                 | +10          | -10                           | +10          | uA    |

| Ci               | Capacitance for each I/O pin                                            |                                                                               |                     | 10           |                               | 10           | pF    |

#### Characteristics of the SDA and SCL Bus Lines the Devices

|                     |                                                  |                                                        | This S | Silicon | Fast-Mo                       | TT   |         |

|---------------------|--------------------------------------------------|--------------------------------------------------------|--------|---------|-------------------------------|------|---------|

| Symbol              | Parameter                                        | Conditions                                             | Min.   | Max.    | Min.                          | Max. | - Units |

| f <sub>SCL</sub>    | SCL clock frequency                              |                                                        | 10     | 1000    | 0                             | 1000 | kHz     |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition             | After this period, the first clock pulse is generated. | 0.26   |         | 0.26                          |      | us      |

| t <sub>LOW</sub>    | LOW period of the SCL clock                      |                                                        | 0.5    |         | 0.5                           |      | us      |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                     |                                                        | 0.26   |         | 0.26                          |      | us      |

| t <sub>SU;STA</sub> | Set-up time for a repeated START condition       |                                                        | 0.26   |         | 0.26                          |      | us      |

| t <sub>SU;DAT</sub> | Data set-up time                                 |                                                        | 50     |         | 50                            |      | ns      |

| t <sub>r</sub>      | Rise time of both SDA and SCL signals            |                                                        |        | 120     |                               | 120  | ns      |

| tf                  | Fall time of both SDA and SCL signals            |                                                        | 12     | 120     | 20×(V <sub>DD</sub><br>/5.5V) | 120  | ns      |

| t <sub>SU;STO</sub> | Set-up time for STOP condi-<br>tion              |                                                        | 0.26   |         | 0.26                          |      | us      |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition |                                                        | 0.5    |         | 0.5                           |      | us      |

### Characteristics of the SDA and SCL Bus Lines the Devices Cont.

| Symbol              | Parameter                         | Conditions -                                        | This Silicon          |      | Fast-Mo               | IIn:to |       |

|---------------------|-----------------------------------|-----------------------------------------------------|-----------------------|------|-----------------------|--------|-------|

| Symbol              |                                   |                                                     | Min.                  | Max. | Min.                  | Max.   | Units |

| C <sub>b</sub>      | Capacitive load for each bus line |                                                     |                       | 550  |                       | 550    | pF    |

| t <sub>VD;DAT</sub> | Data valid time                   |                                                     |                       | 0.45 |                       | 0.45   | us    |

| t <sub>VD;ACK</sub> | Data valid acknowledge time       |                                                     |                       | 0.45 |                       | 0.45   | us    |

| V <sub>nL</sub>     | Noise margin at the LOW<br>level  | For each connected device<br>(including hysteresis) | $0.1 \mathrm{V_{DD}}$ |      | $0.1 V_{DD}$          |        | V     |

| V <sub>nH</sub>     | Noise margin at the HIGH<br>level | For each connected device<br>(including hysteresis) | $0.2 \mathrm{V_{DD}}$ |      | $0.2 \mathrm{V_{DD}}$ |        | V     |

### **Reference Electrical Specification and Timing (Extracted from I2C specification Rev2.6)** Characteristics of the SDA and SCL I/O Stages

| 0 1 1            | Parameter                                                               |                                                                                          | Standar             | d-Mode           | Fast-Mode                                    |                    | Fast-Mode Plus                               |                    | TT    |

|------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------|------------------|----------------------------------------------|--------------------|----------------------------------------------|--------------------|-------|

| Symbol           | Parameter                                                               | Conditions                                                                               | Min.                | Max.             | Min.                                         | Max.               | Min.                                         | Max.               | Units |

| V <sub>IL</sub>  | LOW-level input voltage <sup>(1)</sup>                                  |                                                                                          | -0.5                | $0.3 V_{\rm DD}$ | -0.5                                         | $0.3 V_{DD}$       | -0.5                                         | $0.3 V_{\rm DD}$   | V     |

| V <sub>IH</sub>  | HIGH-level input voltage <sup>(1)</sup>                                 |                                                                                          | $0.7 V_{\text{DD}}$ | (2)              | $0.7 V_{DD}$                                 | (2)                | $0.7 \mathrm{V_{DD}}^{(1)}$                  | (2)                | V     |

| V <sub>hys</sub> | Hysteresis of Schmitt trigger inputs                                    |                                                                                          |                     |                  | $0.05 V_{DD}$                                |                    | $0.05 V_{DD}$                                |                    | V     |

| V <sub>OL1</sub> | LOW-level output voltage 1                                              | Open-drain or open-<br>collector at 3mA sink<br>current; V <sub>DD</sub> > 2V            | 0                   | 0.4              | 0                                            | 0.4                | 0                                            | 0.4                | V     |

| V <sub>OL2</sub> | LOW-level output voltage 2                                              | Open-drain or open-<br>collector at 2mA sink<br>current <sup>(3)</sup> ; $V_{DD} \le 2V$ |                     |                  | 0                                            | $0.2V_{DD}$        | 0                                            | $0.2 V_{DD}$       | V     |

| T                |                                                                         | $V_{OL} = 0.4 V$                                                                         | 3                   |                  | 3                                            |                    | 20                                           |                    |       |

| I <sub>OL</sub>  | LOW-level output current                                                | $V_{OL} = 0.6 V^{(4)}$                                                                   |                     |                  | 6                                            |                    |                                              |                    | mA    |

| t <sub>of</sub>  | Output fall time from V <sub>IHmin</sub> to V <sub>ILmax</sub>          |                                                                                          |                     | 250(5)           | 20×(V <sub>DD</sub><br>/5.5V) <sup>(6)</sup> | 250(5)             | 20×(V <sub>DD</sub><br>/5.5V) <sup>(6)</sup> | 120(7)             | ns    |

| t <sub>SP</sub>  | Pulse width of spikes that must<br>be suppressed by the input<br>filter |                                                                                          |                     |                  | 0                                            | 50 <sup>(8)</sup>  | 0                                            | 50 <sup>(8)</sup>  | ns    |

| Ii               | Input current each I/O pin                                              | 0.1V <sub>DD</sub> <v<sub>I &lt; 0.9V<sub>D</sub>_<br/>Dmax</v<sub>                      | -10                 | +10              | -10 <sup>(9)</sup>                           | +10 <sup>(9)</sup> | -10 <sup>(9)</sup>                           | +10 <sup>(9)</sup> | μΑ    |

| Ci               | Capacitance for each I/O pin <sup>(10)</sup>                            |                                                                                          |                     | 10               |                                              | 10                 |                                              | 10                 | pF    |

Note:

1. Some legacy Standard-mode devices had fixed input levels of  $V_{IL}$  = 1.5V and  $V_{IH}$  = 3.0V. Refer to component datasheet.

2. Maximum  $V_{IH} = V_{DD(max)} + 0.5V$  or 5.5V, which ever is lower. See component datasheet.

3. The same resistor value to drive 3mA at 3.0V  $V_{DD}$  provides the same RC time constant when using  $< 2V V_{DD}$  with a smaller current draw.

4. In order to drive full bus load at 400kHz, 6mA IOL is required at 0.6V VOL. Parts not meeting this specification can still function, but not at 400kHz and 400pF. 5. The maximum t<sub>f</sub> for the SDA and SCL bus lines quoted in Table 10 (300ns) is longer than the specified maximum t<sub>of</sub> for the output stages (250ns). This allows series protection resistors (R<sub>S</sub>) to be connected between the SDA/SCL pins and the SDA/SCL bus lines as shown in Figure 45 without exceeding the maximum specified t<sub>f</sub>. 6. Necessary to be backwards compatible with Fast-mode.

7. In Fast-mode Plus, fall time is specified the same for both output stage and bus timing. If series resistors are used, designers should allow for this when considering bus timing.

8. Input filters on the SDA and SCL inputs suppress noise spikes of less than 50ns.

9. If  $V_{\rm DD}$  is switched off, I/O pins of Fast-mode and Fast-mode Plus device must not obstruct the SDA and SCL lines.

10. Special purpose device such as multiplexers and switches may exceed this capacitance because they connect multiple paths together.

Figure 12. I2C I/O Stage Noise Margin

#### Characteristics of the SDA and SCL Bus Line for Standard, Fast, and Fast-mode Plus I2C-bus Device (1)

| - I I               |                                                               |                                                        | Standar | rd-Mode             | Fast-M                        | lode   | Fast-Mode Plus                               |                     | <b>T</b> T <b>1</b> / |

|---------------------|---------------------------------------------------------------|--------------------------------------------------------|---------|---------------------|-------------------------------|--------|----------------------------------------------|---------------------|-----------------------|

| Symbol              | Parameter                                                     | Conditions                                             | Min.    | Max.                | Min.                          | Max.   | Min.                                         | Max.                | Units                 |

| f <sub>SCL</sub>    | SCL clock frequency                                           |                                                        | 0       | 100                 | 0                             | 400    | 0                                            | 1000                | KHz                   |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition                          | After this period, the first clock pulse is generated. | 4.0     |                     | 0.6                           |        | 0.26                                         |                     | μs                    |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                   |                                                        | 4.7     |                     | 1.3                           |        | 0.5                                          |                     | μs                    |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                  |                                                        | 4.0     |                     | 0.6                           |        | 0.26                                         |                     | μs                    |

| t <sub>SU;STA</sub> | Set-up time for a repeated<br>START condition                 |                                                        | 4.7     |                     | 0.6                           |        | 0.26                                         |                     | μs                    |

| t <sub>HD;DAT</sub> | Data hold time <sup>(2)</sup>                                 | CBUS compatible masters                                | 5.0     |                     |                               |        |                                              |                     | μs                    |

|                     |                                                               | I2C-Bus Devices                                        | 0(3)    | (4)                 | 0(3)                          | (4)    | 0                                            |                     |                       |

| t <sub>SU;DAT</sub> | Data set-up time                                              |                                                        | 250     |                     | 100(5)                        |        | 50                                           |                     | ns                    |

| t <sub>r</sub>      | Rise time of both SDA and SCL signals                         |                                                        |         | 1000                | 20                            | 300    |                                              | 120                 | ns                    |

| t <sub>f</sub>      | Fall time of both SDA and SCL signals <sup>(3)(6)(7)(8)</sup> |                                                        |         | 300                 | 20×(V <sub>DD</sub><br>/5.5V) | 300    | 20×(V <sub>DD</sub><br>/5.5V) <sup>(9)</sup> | 120(8)              | ns                    |

| t <sub>SU;STO</sub> | Set-up time for STOP condi-<br>tion                           |                                                        | 4.0     |                     | 0.6                           |        | 0.26                                         |                     | μs                    |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition              |                                                        | 4.7     |                     | 1.3                           |        | 0.5                                          |                     | μs                    |

| C <sub>b</sub>      | Capacitive load for each bus line <sup>(10)</sup>             |                                                        |         | 400                 |                               | 400    |                                              | 550                 | pF                    |

| t <sub>VD;DAT</sub> | Data valid time <sup>(11)</sup>                               |                                                        |         | 3.45 <sup>(4)</sup> |                               | 0.9(4) |                                              | 0.45 <sup>(4)</sup> | μs                    |

| 6                   | Description                                    |                                                        | Standard-Mode      |                     | Fast-Mode          |        | Fast-Mode Plus     |                     | <b>TT</b> •/ |

|---------------------|------------------------------------------------|--------------------------------------------------------|--------------------|---------------------|--------------------|--------|--------------------|---------------------|--------------|

| Symbol              | Parameter                                      | Conditions                                             | Min.               | Max.                | Min.               | Max.   | Min.               | Max.                | Units        |

| t <sub>VD;ACK</sub> | Data valid acknowledge<br>time <sup>(12)</sup> |                                                        |                    | 3.45 <sup>(4)</sup> |                    | 0.9(4) |                    | 0.45 <sup>(4)</sup> | μs           |

| V <sub>nL</sub>     | Noise margin at the LOW level                  | For each connected<br>device (including<br>hysteresis) | 0.1V <sub>DD</sub> |                     | 0.1V <sub>DD</sub> |        | 0.1V <sub>DD</sub> |                     | V            |

| V <sub>nH</sub>     | level                                          | For each connected<br>device (including<br>hysteresis) | 0.2V <sub>DD</sub> |                     | 0.2V <sub>DD</sub> |        | 0.2V <sub>DD</sub> |                     | V            |

Note:

1. All values referred to  $\rm V_{IH(min)}$  (0.3V\_{DD}) and  $\rm V_{IL(max)}$  (0.7V\_{DD}) levels.

2. t<sub>HD:DAT</sub> is the data hold time that is measured from the falling edge of SCL, applies to data in transmission and the acknowledge.

3. A device must internally provide a hold time of at least 300ns for the SDA signal (with respect to the VIH(min) of the SCL signal) to bridge the undefined region of the falling edge of SCL.

4. The maximum t<sub>HD:DAT</sub> could be 3.45µs and 0.9µs for Standard-mode and Fast-mode, but must be less than the maximum of t<sub>VD:DAT</sub> or t<sub>VD:ACK</sub> by a transition time. This maximum must only be met if the device does not stretch the LOW period (tLOW) of the SCL signal. If the clock stretches the SCL, the data must be valid by the set-up time before it releases the clock.

5. A Fast-mode I<sup>2</sup>C-bus device can be used in a Standard-mode I<sup>2</sup>C-bus system, but the requirement t<sub>SU:DAT</sub> 250ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line  $t_{r(max)} + t_{SU:DAT} = 1000 + 250 = 1250$  (according to the Standard-mode I<sup>2</sup>C-bus specification) before the SCL line is released. Also the acknowledge timing must meet this set-up time.

6. If mixed with Hs-mode device, faster fall times according to Table XX are allowed.

7. The maximum tf for the SDA and SCL bus lines is specified at 300ns. The maximum fall time for the SDA output stage tf is specified are 250ns. This allows series protection resistors to be connected in between the SDA and the SCL pins and the SDA/SCL bus lines without exceeding the maximum specified tf.

8. In Fast-mode Plus, fall time is specified the same for both output stage and bus timing. If series resistors are used, designers should allow for this when considering bus timing.

9. Necessary to be backwards compatible to Fast-mode.

10. The maximum bus capacitance allowable may vary from this value depending on the actual operating voltage and frequency of the application. Section XX discusses techniques for coping with higher bus capacitances.

11. t<sub>VS:DAT</sub> = time for data signal from SCL LOW to SDA output (HIGH or LOW, depending on which one is worse).

12. t<sub>VS:ACK</sub> = time for Acknowledgement signal from SCL LOW to SDA output (HIGH or LOW, depending on which one is worse).

Figure 13. Definition of Timing for F/S-mode Devices on the I2C Bus

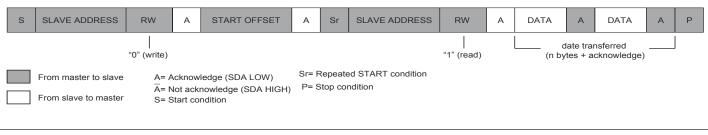

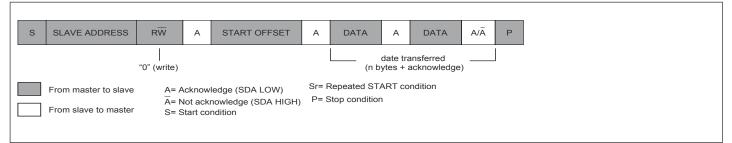

## **Detailed Programming Registers**

#### **I2C Slave Address Selections**

|    | I2C Slave Address Assignment |    |    |    |    |    |               |

|----|------------------------------|----|----|----|----|----|---------------|

| A6 | A5                           | A4 | A3 | A2 | A1 | A0 | ADDR (Pin 16) |

| 1  | 0                            | 1  | 0  | 0  | 0  | 0  | L             |

| 1  | 0                            | 1  | 0  | 0  | 0  | 1  | М             |

| 1  | 0                            | 1  | 0  | 0  | 1  | 0  | F             |

| 1  | 0                            | 1  | 0  | 0  | 1  | 1  | Н             |

#### **Indexed Read**

#### **Indexed Write**

#### **I2C Register Definitions**

| BYTE 0 (Rev | BYTE 0 (Revision and Vendor ID Register) |                    |                    |  |  |  |

|-------------|------------------------------------------|--------------------|--------------------|--|--|--|

| Bit         | Туре                                     | Power-up Condition | Comment            |  |  |  |

| 7           | RO                                       | 0                  |                    |  |  |  |

| 6           | RO                                       | 0                  |                    |  |  |  |

| 5           | RO                                       | 0                  | Revision ID = 0000 |  |  |  |

| 4           | RO                                       | 0                  |                    |  |  |  |

| 3           | RO                                       | 0                  |                    |  |  |  |

| 2           | RO                                       | 0                  |                    |  |  |  |

| 1           | RO                                       | 1                  | Diodes ID = 0011   |  |  |  |

| 0           | RO                                       | 1                  |                    |  |  |  |

| BitTypePower-up ConditionComment7RO06RO05RO04RO13RO02RO11RO00RO0                                                                                           | BYTE 1 (De | BYTE 1 (Device Type/Device ID Register) |                    |                          |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------------------|--------------------|--------------------------|--|--|--|

| 6RO05RO04RO13RO02RO11RO0                                                                                                                                   | Bit        | Туре                                    | Power-up Condition | Comment                  |  |  |  |

| 5RO04RO13RO02RO11RO0                                                                                                                                       | 7          | RO                                      | 0                  |                          |  |  |  |

| 5         RO         0           4         RO         1           3         RO         0           2         RO         1           1         RO         0 | 6          | RO                                      | 0                  |                          |  |  |  |

| 3         RO         0           2         RO         1           1         RO         0                                                                   | 5          | RO                                      | 0                  | Device Type = Active Mux |  |  |  |

| 2         RO         1           1         RO         0                                                                                                    | 4          | RO                                      | 1                  |                          |  |  |  |

| 1 RO 0 Device ID                                                                                                                                           | 3          | RO                                      | 0                  |                          |  |  |  |

| 1 RO 0                                                                                                                                                     | 2          | RO                                      | 1                  |                          |  |  |  |

| 0 RO 0                                                                                                                                                     | 1          | RO                                      | 0                  |                          |  |  |  |

|                                                                                                                                                            | 0          | RO                                      | 0                  |                          |  |  |  |

#### BYTE 2 (Byte Count Register 32 Bytes)

| Bit | Туре | Power-up Condition | Comment                            |

|-----|------|--------------------|------------------------------------|

| 7   | RO   | 0                  |                                    |

| 6   | RO   | 0                  |                                    |

| 5   | RO   | 1                  |                                    |

| 4   | RO   | 0                  | 10C Desister Date Count 22 hotes   |

| 3   | RO   | 0                  | I2C Register Byte Count = 32 bytes |

| 2   | RO   | 0                  |                                    |

| 1   | RO   | 0                  |                                    |

| 0   | RO   | 0                  |                                    |

## BYTE 3 (Channel Assignment of RXDET\_EN#)

| Bit | Туре | Power-up Condition | Comment                            |

|-----|------|--------------------|------------------------------------|

| 7   | R/W  | 0                  |                                    |

| 6   | R/W  | 0                  | Operation Mode Setting             |

| 5   | R/W  | 1                  | Refer to Table Configuration Table |

| 4   | R/W  | 0                  |                                    |

| 3   | R/W  | 0                  | Reserved                           |

| 2   | R/W  | 0                  | Reserved                           |

| 1   | R/W  | 0                  | Reserved                           |

| 0   | R/W  | 0                  | Reserved                           |

| BYTE 4 (Ov | BYTE 4 (Override the Power Down Control)            |                    |                                                                                                                     |  |  |  |

|------------|-----------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit        | Туре                                                | Power-up Condition | Comment                                                                                                             |  |  |  |

| 7          | R/W                                                 | 0                  | CON3 power down override<br>0 – Do not force the CON3 to power down state<br>1 – Force the CON3 to power down state |  |  |  |

| 6          | R/W                                                 | 0                  | CON2 power down override<br>0 – Do not force the CON2 to power down state<br>1 – Force the CON2 to power down state |  |  |  |

| 5          | R/W                                                 | 0                  | CON1 power down override<br>0 – Do not force the CON1 to power down state<br>1 – Force the CON1 to power down state |  |  |  |

| 4          | R/W                                                 | 0                  | CON0 power down override<br>0 – Do not force the CON0 to power down state<br>1 – Force the CON0 to power down state |  |  |  |

| 3          | R/W                                                 | 0                  |                                                                                                                     |  |  |  |

| 2          | R/W                                                 | 1                  | Reserved                                                                                                            |  |  |  |

| 1          | R/W                                                 | 0                  |                                                                                                                     |  |  |  |

| 0          | R/W                                                 | 0                  |                                                                                                                     |  |  |  |

| BYTE 5 (Eq | BYTE 5 (Equalization and Flat Gain Setting of CON0) |                    |                                                                                                                     |  |  |  |

| Bit        | Туре                                                | Power-up Condition | Comment                                                                                                             |  |  |  |

| 7          | R/W                                                 | 0                  | Reserved                                                                                                            |  |  |  |

| 6          | R/W                                                 | 0                  | CON0_EQ<2> Equalizer setting                                                                                        |  |  |  |

| 5          | R/W                                                 | 0                  | CON0_EQ<1> Equalizer setting                                                                                        |  |  |  |

| 4          | R/W                                                 | 0                  | CON0_EQ<0> Equalizer setting                                                                                        |  |  |  |

CON0\_FG<1> Flat gain setting

CON0\_FG<0> Flat gain setting

Reserved

Reserved

3

2

1

0

R/W

R/W

R/W

R/W

1

0

0

0

| BYTE 6 (Eq | YTE 6 (Equalization and Flat Gain Setting of CON1)  |                           |                              |  |  |

|------------|-----------------------------------------------------|---------------------------|------------------------------|--|--|

| Bit        | Туре                                                | Power-up Condition        | Comment                      |  |  |

| 7          | R/W                                                 | 0                         | Reserved                     |  |  |

| 6          | R/W                                                 | 0                         | CON1_EQ<2> Equalizer setting |  |  |

| 5          | R/W                                                 | 0                         | CON1_EQ<1> Equalizer setting |  |  |

| 4          | R/W                                                 | 0                         | CON1_EQ<0> Equalizer setting |  |  |

| 3          | R/W                                                 | 1                         | CON1_FG<1> Flat gain setting |  |  |

| 2          | R/W                                                 | 0                         | CON1_FG<0> Flat gain setting |  |  |

| 1          | R/W                                                 | 0                         | Reserved                     |  |  |

| 0          | R/W                                                 | 0                         | Reserved                     |  |  |

| BYTE 7 (Eq | BYTE 7 (Equalization and Flat Gain Setting of CON2) |                           |                              |  |  |

| Bit        | Туре                                                | Power-up Condition        | Comment                      |  |  |

| 7          | R/W                                                 | 0                         | Reserved                     |  |  |

| 6          | R/W                                                 | 0                         | CON2_EQ<2> Equalizer setting |  |  |

| 5          | R/W                                                 | 0                         | CON2_EQ<1> Equalizer setting |  |  |

| 4          | R/W                                                 | 0                         | CON2_EQ<0> Equalizer setting |  |  |

| 3          | R/W                                                 | 1                         | CON2_FG<1> Flat gain setting |  |  |

| 2          | R/W                                                 | 0                         | CON2_FG<0> Flat gain setting |  |  |

| 1          | R/W                                                 | 0                         | Reserved                     |  |  |

| 0          | R/W                                                 | 0                         | Reserved                     |  |  |