Ph. 480-503-4295 | NOPP@FocusLCDs.com TFT | DLED | CHARACTER | GRAPHIC | UWVD | SEGMENT | CUSTOM

# Graphic Display Module

Part Number G24064B-FTW-DW63

**Overview:**

- 240x64 Graphic LCD

- FSTN Gray

- 149.5x51.7mm Module

- Parallel and Serial Interface(s)

- White LED Backlight

- Transflective

- Wide Temp Range

- 3.0V

- LCD IC: NT7534

- RoHS Compliant

# **Graphic LCD Features**

Resolution: 240x64 Dots Interface(s): Parallel and Serial RoHS Compliant.

| General Information Items | Specification        | Unit    | Note |

|---------------------------|----------------------|---------|------|

| Ceneral information items | Main Panel           | Onit    | NOLE |

| Viewing Area (VA)         | 130.2 (H) x 37.6 (V) | mm      |      |

| LCD Type                  | FSTN Positive        |         |      |

| Viewing Angle             | 6:00                 | O'Clock |      |

| Polarizer                 | Transflective        |         |      |

| Resolution                | 240x64               | Dots    |      |

| Backlight Type            | LED                  |         |      |

| Backlight Color           | White                | mm      |      |

| LCD IC                    | NT7534*2             |         |      |

| Operating Temperature     | -20 to +70           | °C      |      |

| Storage Temperature       | -30 to +80           | °C      |      |

# **Mechanical Information**

|                | Item           |  | Тур.   | Max. | Unit | Note |

|----------------|----------------|--|--------|------|------|------|

|                | Horizontal (H) |  | 149.50 |      | mm   |      |

| Module<br>Size | Vertical (V)   |  | 51.70  |      | mm   |      |

| 0120           | Depth (D)      |  | 14.90  |      | mm   |      |

|                | Weight         |  | TBD    |      | g    |      |

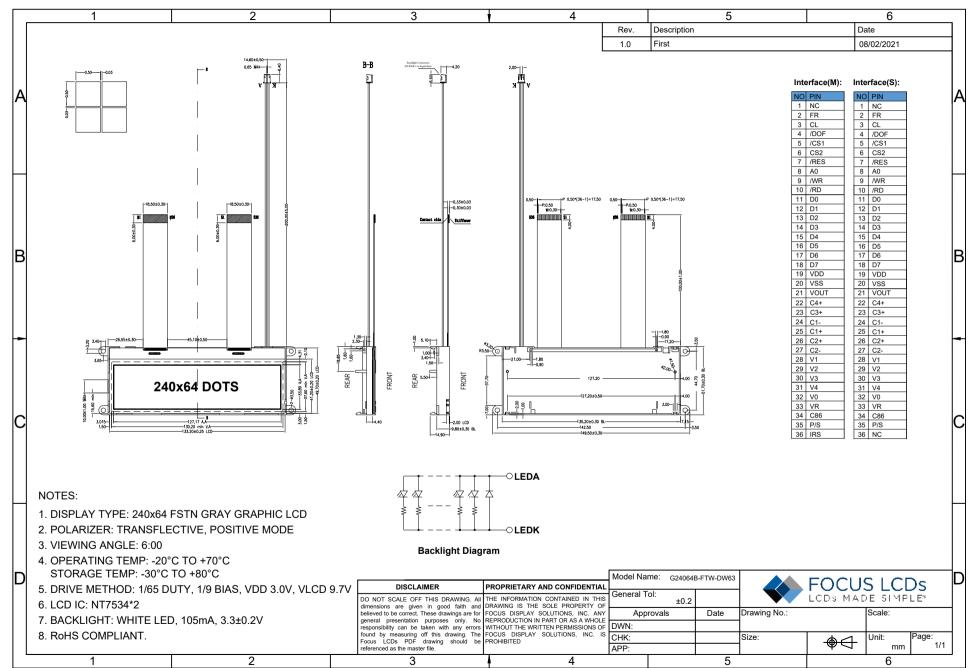

# 1. Outline Dimensions

# 2. Input Terminal Pin Assignment

| NO.   | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                      | I/O |  |  |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

| 1     | NC     |                                                                                                                                                                                                                                                                                                                                                                                                  |     |  |  |

| 2     | FR     | This is the liquid crystal alternative current signal I/O terminal. M/S="H": Output                                                                                                                                                                                                                                                                                                              | I/O |  |  |

| 3     | CL     | This is the display clock input terminal. When the NT7534 chips are used in master/slave mode, the various CL terminals must be connected.                                                                                                                                                                                                                                                       |     |  |  |

| 4     | /DOF   | This is the liquid crytal display blanking control terminal.<br>M/S="H": Output                                                                                                                                                                                                                                                                                                                  |     |  |  |

| 5     | /CS1   | This is the chip select signal. When /CS1="L" and CS2="H", then the chip                                                                                                                                                                                                                                                                                                                         |     |  |  |

| 6     | CS2    | select becomes active, and the data/command I/O is enabled.                                                                                                                                                                                                                                                                                                                                      |     |  |  |

| 7     | /RES   | When /RES is set to "L", the settings are initialized.                                                                                                                                                                                                                                                                                                                                           | I   |  |  |

| 8     | A0     | This is connected to the least significant bit of the normal MPU address<br>bus, and it determines whether the data bits are data or a command.<br>A0="H": Indicates that D0 to D7 are display data<br>A0="L": Indicates that D0 to D7 are control data                                                                                                                                          | 1   |  |  |

| 9     | /WR    | <ul> <li>When connected to an 8080 MPU, this is active LOW. This terminal connects to the 8080 MPU /WR signal. The signals on the data bus are latched at the rising edge of the /WR signal.</li> <li>When connected to a 6800 Series MPU, this is the read/write control signal input terminal. When R/W="H": Read, When R/W="L": Write</li> </ul>                                              | I   |  |  |

| 10    | /RD    | When connected to an 8080 MPU, it is active LOW. This pad is connected to the /RD signal of the 8080 MPU, and the NT7534 data bus is in an output status when this signal is "L".<br>When connected to a 6800 Series MPU, this is active HIGH. This is used as an enable clock input of the 6800 Series MPU.                                                                                     | I   |  |  |

| 11-18 | D0-D7  | This is an 8-bit bi-directional data bus that connects to an 8-bit or 16-bit standard MPU data bus.<br>When the serial interface is selected (P/S="L"), then D7 serves as the serial data input terminal (SI) and D6 serves as the serial clock input terminal (SCL). At this time, D0 to D5 are set to high impedance.<br>When the chip select is inactive, D0 to D7 are set to high impedance. | I/O |  |  |

| 19    | VDD    | Power Supply.                                                                                                                                                                                                                                                                                                                                                                                    | S   |  |  |

| 20    | VSS    | Ground.                                                                                                                                                                                                                                                                                                                                                                                          | S   |  |  |

| 21    | VOUT   | DC/DC voltage converter output.                                                                                                                                                                                                                                                                                                                                                                  | I/O |  |  |

| 22    | C4+    | Capacitor 4+ pad for internal DC/DC voltage converter.                                                                                                                                                                                                                                                                                                                                           | 0   |  |  |

| 23    | C3+    | Capacitor 3+ pad for internal DC/DC voltage converter.                                                                                                                                                                                                                                                                                                                                           | 0   |  |  |

| 24    | C1-    | Capacitor 1- pad for internal DC/DC voltage converter.                                                                                                                                                                                                                                                                                                                                           | 0   |  |  |

| 25    | C1+    | Capacitor 1+ pad for internal DC/DC voltage converter.                                                                                                                                                                                                                                                                                                                                           | 0   |  |  |

| 26    | C2+    | Capacitor 2+ pad for internal DC/DC voltage converter.                                                                                                                                                                                                                                                                                                                                           | 0   |  |  |

| 27    | C2-    | Capacitor 2- pad for internal DC/DC voltage converter.                                                                                                                                                                                                                                                                                                                                           | 0   |  |  |

| ·     |                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |  |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|--|

| 28-32 | V1<br>V2<br>V3                                                                                                                                                                                          | LCD driver supplies voltages. The voltage determined by the LCD cell is impedance-converted by a resistive driver or an operation amplifier for application. Voltages should be according to the following relationship:<br>V0≥V1≥V2≥V3≥V4≥VSS2                                                                                                                                                                                                                                                                                                                                                                                        |   |  |  |  |  |

|       | V4<br>V0When the on-chip operating power circuit is on, the following voltages are<br>supplied to V1 to V4 by the on-chip power circuit. Voltage selection is<br>performed by the LCD Bias Set command. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |  |  |  |  |

| 33    | VR                                                                                                                                                                                                      | Voltage adjustment pad. Applies voltage between V0 and VSS using a resistive divider.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I |  |  |  |  |

| 34    | C86                                                                                                                                                                                                     | This is the MPU interface switch terminal.<br>C86="H": 6800 Series MPU Interface<br>C86="L": 8080 Series MPU Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I |  |  |  |  |

| 35    | P/S                                                                                                                                                                                                     | This is the parallel data input/serial data input switch terminal.         P/S="H": Parallel data input         P/S="L": Serial data input.         The following applies depending on the P/S status:         P/S       Data/Command       Data       Read/Write       Serial Clock         "H"       A0       D0 to D7       /RD, /WR       -         "L"       A0       SI (D7)       Write only       SCL (D6)         When the P/S="L", D0 to D5 are HZ. D0 to D5 may be "H", "L" or Open. /       RD(E) and /WR (R/W) are fixed to either "H" or "L". With serial data input,         RAM display data reading is not supported. | I |  |  |  |  |

| 36    | IRS                                                                                                                                                                                                     | This terminal selects the resistors for the V0 voltage level adjustment.<br>IRS="H", Use the internal resistors.<br>IRS="L", Do not use the internal resistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | I |  |  |  |  |

I: Input, O: Output, S: Supply

| NO. | Symbol | Description                                                                                                                                  | I/O |  |  |  |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

| 1   | NC     |                                                                                                                                              |     |  |  |  |

| 2   | FR     | This is the liquid crystal alternative current signal I/O terminal.<br>M/S="L": Input                                                        |     |  |  |  |

| 3   | CL     | This is the display clock input terminal. When the NT7534 chips are used in master/slave mode, the various CL terminals must be connected.   | I/O |  |  |  |

| 4   | /DOF   | This is the liquid crytal display blanking control terminal.<br>M/S="L": Input                                                               |     |  |  |  |

| 5   | /CS1   | This is the chip select signal. When /CS1="L" and CS2="H", then the chip                                                                     |     |  |  |  |

| 6   | CS2    | select becomes active, and the data/command I/O is enabled.                                                                                  |     |  |  |  |

| 7   | /RES   | When /RES is set to "L", the settings are initialized.                                                                                       | I   |  |  |  |

| 8   | A0     | This is connected to the least significant bit of the normal MPU address bus, and it determines whether the data bits are data or a command. | I   |  |  |  |

|     |        | A0="H": Indicates that D0 to D7 are display data<br>A0="L": Indicates that D0 to D7 are control data                                         |     |  |  |  |

| 9     | /WR            | <ul> <li>When connected to an 8080 MPU, this is active LOW. This terminal connects to the 8080 MPU /WR signal. The signals on the data bus are latched at the rising edge of the /WR signal.</li> <li>When connected to a 6800 Series MPU, this is the read/write control signal input terminal. When R/W="H": Read, When R/W="L": Write</li> </ul> | Ι   |

|-------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 10    | /RD            | When connected to an 8080 MPU, it is active LOW. This pad is connected to the /RD signal of the 8080 MPU, and the NT7534 data bus is in an output status when this signal is "L".                                                                                                                                                                   | I   |

|       |                | When connected to a 6800 Series MPU, this is active HIGH. This is used as an enable clock input of the 6800 Series MPU.                                                                                                                                                                                                                             |     |

|       |                | This is an 8-bit bi-directional data bus that connects to an 8-bit or 16-bit standard MPU data bus.                                                                                                                                                                                                                                                 |     |

| 11-18 | D0-D7          | When the serial interface is selected (P/S="L"), then D7 serves as the serial data input terminal (SI) and D6 serves as the serial clock input terminal (SCL). At this time, D0 to D5 are set to high impedance.                                                                                                                                    | I/O |

|       |                | When the chip select is inactive, D0 to D7 are set to high impedance.                                                                                                                                                                                                                                                                               |     |

| 19    | VDD            | Power Supply.                                                                                                                                                                                                                                                                                                                                       | S   |

| 20    | VSS            | Ground.                                                                                                                                                                                                                                                                                                                                             | S   |

| 21    | VOUT           | DC/DC voltage converter output.                                                                                                                                                                                                                                                                                                                     | I/O |

| 22    | C4+            | Capacitor 4+ pad for internal DC/DC voltage converter.                                                                                                                                                                                                                                                                                              | 0   |

| 23    | C3+            | Capacitor 3+ pad for internal DC/DC voltage converter.                                                                                                                                                                                                                                                                                              | 0   |

| 24    | C1-            | Capacitor 1- pad for internal DC/DC voltage converter.                                                                                                                                                                                                                                                                                              | 0   |

| 25    | C1+            | Capacitor 1+ pad for internal DC/DC voltage converter.                                                                                                                                                                                                                                                                                              | 0   |

| 26    | C2+            | Capacitor 2+ pad for internal DC/DC voltage converter.                                                                                                                                                                                                                                                                                              | 0   |

| 27    | C2-            | Capacitor 2- pad for internal DC/DC voltage converter.                                                                                                                                                                                                                                                                                              | 0   |

| 28-32 | V1<br>V2<br>V3 | LCD driver supplies voltages. The voltage determined by the LCD cell is impedance-converted by a resistive driver or an operation amplifier for application. Voltages should be according to the following relationship: V0≥V1≥V2≥V3≥V4≥VSS2                                                                                                        | I/O |

|       | V4<br>V0       | When the on-chip operating power circuit is on, the following voltages are supplied to V1 to V4 by the on-chip power circuit. Voltage selection is performed by the LCD Bias Set command.                                                                                                                                                           |     |

| 33    | VR             | Voltage adjustment pad. Applies voltage between V0 and VSS using a resistive divider.                                                                                                                                                                                                                                                               | I   |

|       |                | This is the MPU interface switch terminal.                                                                                                                                                                                                                                                                                                          |     |

| 34    | C86            | C86="H": 6800 Series MPU Interface<br>C86="L": 8080 Series MPU Interface                                                                                                                                                                                                                                                                            | I   |

|       |                |                                                                                                                                                                                                                                                                                                                                                     |     |

|    | This is the parallel data input/serial data input switch terminal.<br>P/S="H": Parallel data input<br>P/S="L": Serial data input.<br>The following applies depending on the P/S status:              |                   |                    |                  |                        |                   |  |   |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------|------------------|------------------------|-------------------|--|---|

| 35 | P/S                                                                                                                                                                                                  | <b>P/S</b><br>"H" | Data/Command<br>A0 | Data<br>D0 to D7 | Read/Write<br>/RD, /WR | Serial Clock<br>- |  | I |

|    |                                                                                                                                                                                                      | "L"               | A0                 | SI (D7)          | Write only             | SCL (D6)          |  |   |

|    | When the P/S="L", D0 to D5 are HZ. D0 to D5 may be "H", "L" or Open. /<br>RD (E) and /WR (R/W) are fixed to either "H" or "L". With serial data input,<br>RAM display data reading is not supported. |                   |                    |                  |                        |                   |  |   |

| 36 | NC                                                                                                                                                                                                   | -                 |                    |                  |                        |                   |  | - |

I: Input, O: Output, S: Supply

# 3. LCD Optical Characteristics

| ltem           |      | Symbol           | Condition   | Min | Тур. | Мах | Unit   |

|----------------|------|------------------|-------------|-----|------|-----|--------|

| Contrast Ratio |      | CR               |             |     | 3    |     |        |

|                | On   | T <sub>on</sub>  |             |     | 150  | 250 | ms     |

| Response Time  | Off  | T <sub>off</sub> |             |     | 180  | 300 | ms     |

|                | Hor  | ΘL               | Ф=270°, 9Н  |     | 55   |     |        |

| Viewing Angle  | Hor. | Θ <sub>R</sub>   | Ф=90°, 3Н   |     | 55   |     |        |

| C₁≥2, 25°C     |      | Θτ               | Φ=180°, 12Η |     | 40   |     | degree |

|                | Ver. | Θ <sub>B</sub>   | Φ=0°, 6Η    |     | 70   |     |        |

# 4. Electrical Characteristics

### 4.1 Absolute Maximum Rating

| Characteristics       | Symbol | Min  | Мах  | Unit |

|-----------------------|--------|------|------|------|

| Supply Voltage        | VDD    | -0.3 | 4.0  | V    |

| Cupply Voltage        | Vout   | -0.3 | 15.0 | V    |

| Operating Temperature | TOP    | -20  | +70  | °C   |

| Storage Temperature   | TST    | -30  | +80  | °C   |

NOTE: If the absolute maximum rating of the above parameters is exceeded, even momentarily, the quality of the product may be degraded. Absolute maximum ratings specify the values which the product may be physically damaged if exceeded. Be sure to use the product within the range of the absolute maximum ratings.

### 4.2 DC Electrical Characteristics

| Characteristics     |         | Symbol | Condition | Min    | Тур. | Мах    | Unit |

|---------------------|---------|--------|-----------|--------|------|--------|------|

| LCD Driving Voltage |         | VLCD   |           |        | 9.7  |        | V    |

| Supply Voltage      |         | Logic  | VDD-GND   |        | 3.0  |        | V    |

|                     | H Level | VDD    |           | 0.8VDD |      | VDD    | V    |

| Input Voltage       | L Level | VIH    |           | VSS    |      | 0.2VDD | V    |

#### Condition:

1. VDD = 3.0V

2. 1/65 Duty, 1/9 Bias

# 5.0 Module Function

# 5.1 Timing Characteristics

| AO                                                                                   |                                                                                                                                                                                                                                          |                                            |                     | $ \rightarrow $                              | $\subset$                                                  |                                                                 |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------|----------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------|

| /CS1<br>(CS2                                                                         |                                                                                                                                                                                                                                          |                                            | toyos               | ×                                            |                                                            |                                                                 |

| /WR<br>/RD                                                                           |                                                                                                                                                                                                                                          | toouw, to                                  |                     | Ссни                                         | , Ссоня                                                    |                                                                 |

| D0~I<br>(Writ                                                                        |                                                                                                                                                                                                                                          | $\mathbf{i}$                               | toss 🔸              |                                              |                                                            | -<br>A                                                          |

| D0~I<br>(Rea                                                                         | D7 III                                                                                                                                                                                                                                   | taccs                                      |                     | ICH8                                         | FA ((                                                      | ) l'a                                                           |

| Inea                                                                                 | a) —                                                                                                                                                                                                                                     | 7                                          | all                 | 16                                           | -k                                                         |                                                                 |

|                                                                                      | F                                                                                                                                                                                                                                        |                                            | E                   |                                              | 1                                                          |                                                                 |

|                                                                                      | Parameter                                                                                                                                                                                                                                | Min.                                       | CU<br>Typ.          | (VDD=<br>Max.                                | = 2.7~<br>Unit                                             | 3.6V, Ta = -40 ~ +85°C<br>Condition                             |

| Symbol                                                                               | Parameter<br>Address hold time                                                                                                                                                                                                           | Min.                                       | С.<br>Тур.<br>-     |                                              | 1                                                          | Condition                                                       |

| Symbol<br>taнв                                                                       | Parameter<br>Address hold time<br>Address setup time                                                                                                                                                                                     | 100000                                     | 1.1300 (200-5)<br>K | Max.                                         | Unit                                                       |                                                                 |

| Symbol<br>tahb<br>tase                                                               | Parameter<br>Address hold time                                                                                                                                                                                                           | 0                                          | -                   | Max.                                         | Unit<br>ns                                                 | Condition                                                       |

| Symbol<br>tahb                                                                       | Parameter<br>Address hold time<br>Address setup time                                                                                                                                                                                     | 0                                          | -                   | Max.<br>-<br>-                               | Unit<br>ns<br>ns                                           | Condition                                                       |

| Symbol<br>taнв<br>tass<br>tcycs                                                      | Parameter<br>Address hold time<br>Address setup time<br>System cycle time                                                                                                                                                                | 0<br>0<br>240                              | -                   | Max.<br>-<br>-                               | Unit<br>ns<br>ns<br>ns                                     | Condition<br>A0                                                 |

| Symbol<br>tahe<br>tase<br>tcycs<br>tcclw<br>tcclr                                    | Parameter<br>Address hold time<br>Address setup time<br>System cycle time<br>Control low pulse width (write)                                                                                                                             | 0<br>0<br>240<br>120                       | -                   | Max.<br>-<br>-<br>-                          | Unit<br>ns<br>ns<br>ns<br>ns                               | Condition<br>A0<br>///////////////////////////////////          |

| Symbol<br>tahe<br>tase<br>tcyce<br>tcclw<br>tcclr<br>tcchw                           | Parameter<br>Address hold time<br>Address setup time<br>System cycle time<br>Control low pulse width (write)<br>Control low pulse width (read)                                                                                           | 0<br>0<br>240<br>120<br>120                | -                   | Max.<br>-<br>-<br>-<br>-                     | Unit<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns             | Condition<br>A0<br>/WR<br>/RD                                   |

| Symbol<br>tahe<br>tase<br>tcyce<br>tcclw                                             | Parameter<br>Address hold time<br>Address setup time<br>System cycle time<br>Control low pulse width (write)<br>Control low pulse width (read)<br>Control high pulse width (write)                                                       | 0<br>0<br>240<br>120<br>120<br>100         |                     | Max.<br>-<br>-<br>-<br>-<br>-                | Unit<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns             | Condition<br>A0<br>M/R<br>/RD<br>M/R<br>/RD                     |

| Symbol<br>tahe<br>tase<br>tcyce<br>tcclw<br>tcclr<br>tcchr<br>tcchr                  | Parameter<br>Address hold time<br>Address setup time<br>System cycle time<br>Control low pulse width (write)<br>Control low pulse width (read)<br>Control high pulse width (write)<br>Control high pulse width (read)                    | 0<br>240<br>120<br>120<br>100<br>100       | -                   | Max.<br>-<br>-<br>-<br>-<br>-<br>-           | Unit<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns       | Condition<br>A0<br>///RD<br>///RD<br>////////////////////////// |

| Symbol<br>tahe<br>tase<br>tcyce<br>tcclw<br>tcclr<br>tcchw<br>tcchr<br>tcchr<br>tcse | Parameter<br>Address hold time<br>Address setup time<br>System cycle time<br>Control low pulse width (write)<br>Control low pulse width (read)<br>Control high pulse width (write)<br>Control high pulse width (read)<br>Data setup time | 0<br>240<br>120<br>120<br>100<br>100<br>40 |                     | Max.<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | Unit<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns | Condition<br>A0<br>M/R<br>/RD<br>M/R<br>/RD                     |

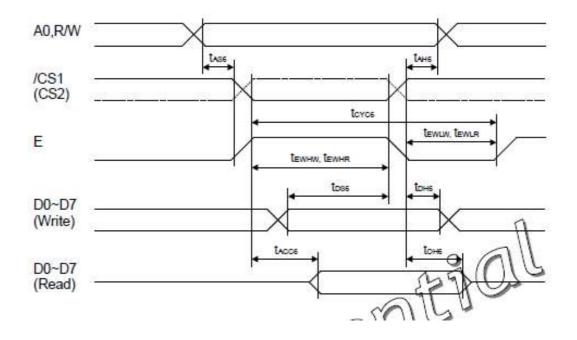

1. System Buses Read/Write Characteristics (for 8080 Series MPU)

|                   |                                  |      |      | (VDD= | 1.8~2  | 2.7V, Ta=-40 ~ +85°C) |

|-------------------|----------------------------------|------|------|-------|--------|-----------------------|

| Symbol            | Parameter                        | Min. | Тур. | Max.  | Unit   | Condition             |

| tанв              | Address hold time                | 0    | -    | -     | ns     | A0                    |

| tas8              | Address setup time               | 0    | -    | -     | ns     | AU                    |

| tcycs             | System cycle time                | 400  | -    | -     | ns     |                       |

| tccLw             | Control low pulse width (write)  | 150  | -    | -     | ns     | MR                    |

| <b>t</b> CCLR     | Control low pulse width (read)   | 150  | -    | -     | ns     | /RD                   |

| tсснw             | Control high pulse width (write) | 120  | -    | -     | ns     | MR                    |

| tссня             | Control high pulse width (read)  | 120  | -    | -     | ns     | /RD                   |

| toss              | Data setup time                  | 80   | -    | -     | ns     | DQ-D7                 |

| toнs              | Data hold time                   | 30   | -    | -     | ns     |                       |

| t <sub>ACC8</sub> | /RD access time                  | -    | -    | 240   | hun\$( | 00-D7, CL= 100pF      |

| tснв              | Output disable time              | 10   | -    | TOP   | hs     | 00-D7, CL- 100pr      |

System Buses Read/Write Characteristics (for 8080 Series MPU) (continued)

or less.

\*1. The input signal rise time and fall time (tr, tr) is specified at (5ns or less. (tr + tr) < (tcrcs - tccнw) for write, (tr + tr) < (tcrcs - tccнw) for read.</li>

\*2. All timing is specified using 20% and 88% of VDD as the reference.

\*3. tcclw and tcclk are specified as the overlap interval when /CS1 is low (CS2 is high) and /WR or /RD is low.

2. System Buses Read/Write Characteristics (for 6800 Series MPU)

|        |                                  | a             | (2)  | -     |       |                         |

|--------|----------------------------------|---------------|------|-------|-------|-------------------------|

|        | GE                               | $\frac{1}{1}$ |      | (VDD= | 2.7~3 | 3.6V, Ta = -40 ~ +85°C) |

| Symbol | Parameter                        | Mun           | Тур. | Max.  | Unit  | Condition               |

| tang   | Address hold time                | <b>0</b>      | -    | -     | ns    | A0, R/W                 |

| tase   | Address setup time               | 0             | -    | -     | ns    | 70,100                  |

| toyos  | System cycle time                | 240           | -    | -     | ns    |                         |

| tewнw  | Control low pulse width (write)  | 120           | -    | -     | ns    | E                       |

| tewhr  | Control low pulse width (read)   | 120           | -    | -     | ns    | E                       |

| tewuw  | Control high pulse width (write) | 100           | -    | -     | ns    | E                       |

| tewlr  | Control high pulse width (read)  | 100           | -    | -     | ns    | E                       |

| tose   | Data setup time                  | 40            | -    | -     | ns    | D0~D7                   |

| tоня   | Data hold time                   | 10            | -    | -     | ns    | 00-01                   |

| taccs  | /RD access time                  | -             | -    | 140   | ns    | D0~D7                   |

| tонс   | Output disable time              | 5             | -    | 50    | ns    | CL = 100pF              |

System Buses Read/Write Characteristics (for 6800 Series MPU) (continued)

|                                  |                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                           | (VDD=                                                                                                                                                                                                                                                 | 1.8~2                                                                                                                                                                                                                                                   | 2.7V, Ta = -40 ~ +85°C)                                                                                                                                                                                                                                                                          |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                        | Min.                                                                                                                                                                                                                                                            | Тур.                                                                                                                                                                                                                                                                                                                                                                                                      | Max.                                                                                                                                                                                                                                                  | Unit                                                                                                                                                                                                                                                    | Condition                                                                                                                                                                                                                                                                                        |

| Address hold time                | 0                                                                                                                                                                                                                                                               | -                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                      | A0, R/W                                                                                                                                                                                                                                                                                          |

| Address setup time               | 0                                                                                                                                                                                                                                                               | -                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                      | AU, R/W                                                                                                                                                                                                                                                                                          |

| System cycle time                | 400                                                                                                                                                                                                                                                             | -                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                  |

| Control low pulse width (write)  | 150                                                                                                                                                                                                                                                             | -                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                      | E                                                                                                                                                                                                                                                                                                |

| Control low pulse width (read)   | 150                                                                                                                                                                                                                                                             | -                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                      | E                                                                                                                                                                                                                                                                                                |

| Control high pulse width (write) | 120                                                                                                                                                                                                                                                             | -                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                      | E                                                                                                                                                                                                                                                                                                |

| Control high pulse width (read)  | 120                                                                                                                                                                                                                                                             | -                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                      | E                                                                                                                                                                                                                                                                                                |

| Data setup time                  | 80                                                                                                                                                                                                                                                              | -                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                      | DQ-D7                                                                                                                                                                                                                                                                                            |

| Data hold time                   | 30                                                                                                                                                                                                                                                              | -                                                                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                     | ns                                                                                                                                                                                                                                                      | 5 Pr                                                                                                                                                                                                                                                                                             |

| /RD access time                  | -                                                                                                                                                                                                                                                               | -                                                                                                                                                                                                                                                                                                                                                                                                         | 240                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                         | ple-ba                                                                                                                                                                                                                                                                                           |

| Output disable time              | 10                                                                                                                                                                                                                                                              | -                                                                                                                                                                                                                                                                                                                                                                                                         | ( TOP                                                                                                                                                                                                                                                 | hs                                                                                                                                                                                                                                                      | @L= 100pF                                                                                                                                                                                                                                                                                        |

|                                  | Address hold time<br>Address setup time<br>System cycle time<br>Control low pulse width (write)<br>Control low pulse width (read)<br>Control high pulse width (read)<br>Control high pulse width (read)<br>Data setup time<br>Data hold time<br>/RD access time | Address hold time       0         Address setup time       0         System cycle time       400         Control low pulse width (write)       150         Control low pulse width (read)       150         Control high pulse width (write)       120         Control high pulse width (read)       120         Data setup time       80         Data hold time       30         /RD access time       - | Address hold time0Address setup time0Address setup time0System cycle time400Control low pulse width (write)150Control low pulse width (read)150Control high pulse width (write)120Control high pulse width (read)120Data setup time80Data hold time30 | ParameterMin.Typ.Max.Address hold time0Address setup time0System cycle time400Control low pulse width (write)150Control low pulse width (read)150Control high pulse width (write)120Control high pulse width (read)120Data setup time80Data hold time30 | ParameterMin.Typ.Max.UnitAddress hold time0nsAddress setup time0nsSystem cycle time400nsControl low pulse width (write)150nsControl low pulse width (read)150nsControl high pulse width (read)120nsControl high pulse width (read)120nsData setup time80nsData hold time30ns/RD access time240ns |

\*1. The input signal rise time and fall time (tr, tr) is specified at (5ns or less. (tr + tr) < (tстсс - tewnw - tewnw) for write, (tr + tr) < (tстсе - tewne - tewne) for read.</li>

\*2. All timing is specified using 20% and 80% of VDD as the reference.

\*3. tewnw and tewne are specified as the overlap interval when /CS1 is low (CS2 is high) and E is high.

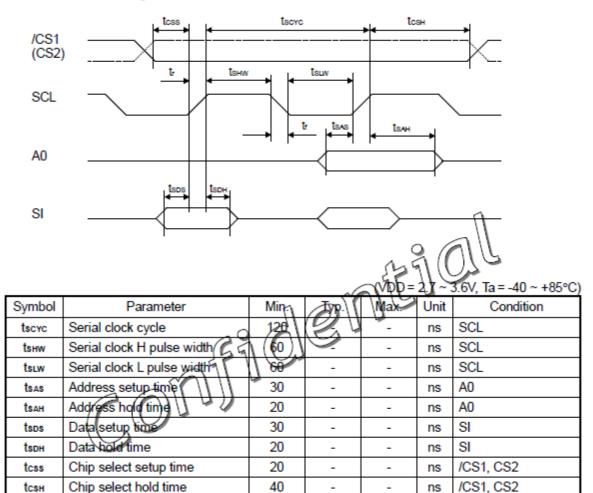

#### 3. Serial Interface Timing

#### Serial Interface Timing (continued)

|        |                            |      |      | (VDD= | 1.8~2 | 2.7V, Ta = -40 ~ +85°C) |

|--------|----------------------------|------|------|-------|-------|-------------------------|

| Symbol | Parameter                  | Min. | Тур. | Max.  | Unit  | Condition               |

| tscyc  | Serial clock cycle         | 200  | -    | -     | ns    | SCL                     |

| tsнw   | Serial clock H pulse width | 80   | -    | -     | ns    | SCL                     |

| tsıw   | Serial clock L pulse width | 80   | -    | -     | ns    | SCL                     |

| ts∡s   | Address setup time         | 60   | -    | -     | ns    | A0                      |

| tsaн   | Address hold time          | 30   | -    | -     | ns    | A0                      |

| tsps   | Data setup time            | 60   | -    | -     | ns    | SI                      |

| tsdн   | Data hold time             | 40   | -    | -     | ns    | SI                      |

| tcss   | Chip select setup time     | 40   | -    | -     | ns    | /CS1, CS2               |

| tсян   | Chip select hold time      | 100  | -    | -     | ns    | /C\$1, CS2              |

\*1. The input signal rise time and fall time (tr, tr) is specified as 15ns or less. \*2. All timing is specified using 20% and 80% of VDD as the standard.

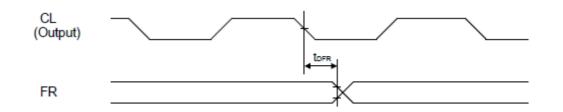

### 4. Display Control Timing

|                          |                 |      |         |      | (V       | /DD = 2.7 ~ 3.6V, Ta = -40 ~ +85°C) |  |  |  |  |  |  |

|--------------------------|-----------------|------|---------|------|----------|-------------------------------------|--|--|--|--|--|--|

| Symbol                   | Parameter       | Min. | Тур.    | Max. | Unit     | Condition                           |  |  |  |  |  |  |

| <b>t</b> dfr             | FR delay time   | -    | 20      | 80   | ns       | CL = 50 pF                          |  |  |  |  |  |  |

|                          |                 |      |         |      | . (V     | /DD=1.8~27V, Ta=-40~+85°C)          |  |  |  |  |  |  |

| Symbol                   | Parameter       | Min. | Тур.    | Max. | Unit     | いって ( Jondition                     |  |  |  |  |  |  |

| <b>t</b> DFR             | FR delay time   | -    | 40      | 160  | Jan Star | QL = 50 pF                          |  |  |  |  |  |  |

|                          | 5. Reset Timing |      |         |      |          |                                     |  |  |  |  |  |  |

| /RST<br>Intern<br>Status |                 | D    | uring R | eset |          |                                     |  |  |  |  |  |  |

|        | (VDD = 2.7 ~ 3.6V, Ta = -40 ~ +85 |      |      |      |      |           |  |  |  |  |  |  |  |  |

|--------|-----------------------------------|------|------|------|------|-----------|--|--|--|--|--|--|--|--|

| Symbol | Parameter                         | Min. | Тур. | Max. | Unit | Condition |  |  |  |  |  |  |  |  |

| tr     | Reset Time                        | -    | -    | 1.0  | μs   |           |  |  |  |  |  |  |  |  |

| trw    | Reset low pulse width             | 10   | -    | -    | μs   | /RES      |  |  |  |  |  |  |  |  |

|        | (VDD = 1.8 ~ 2.7V, Ta = -40 ~ +8 |      |      |      |      |           |  |  |  |  |  |  |  |

|--------|----------------------------------|------|------|------|------|-----------|--|--|--|--|--|--|--|

| Symbol | Parameter                        | Min. | Тур. | Max. | Unit | Condition |  |  |  |  |  |  |  |

| tĸ     | Reset Time                       | -    | -    | 2.0  | μs   |           |  |  |  |  |  |  |  |

| trw    | Reset low pulse width            | 20   | -    | -    | μs   | /RES      |  |  |  |  |  |  |  |

### 5.2 LCM Application

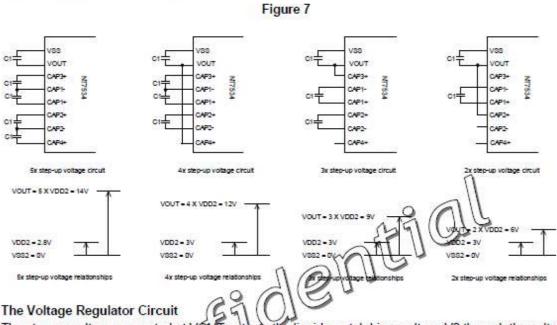

#### The Step-up Voltage Circuits

Using the step-up voltage circuits within the NT7534 chips it is possible to product 5X, 4X, 3X, 2X step-ups of the VDD2-VSS2 voltage levels.

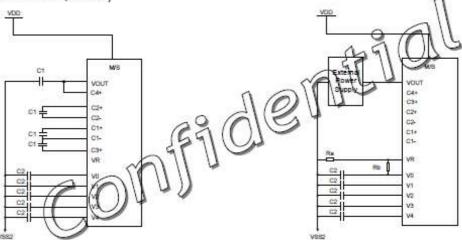

The Voltage Regulator Circuit The step-up voltage generated at YOUT outputs the liquid crystal driver voltage V0 through the voltage regulator circuit. Because the V17984 drips have an internal high-accuracy fixed voltage power supply with a 64-level electropic volume function and internal resistors for the V0 voltage regulator, systems can be constructed without having to include high-accuracy voltage regulator circuit components. Moreover, NT/534 has thermal gradients: approximately –0.05%/°C.

www.FocusLCDs.com

#### **High Power Mode**

The power supply circuit equipped in the NT7534 chips has very low power consumption (normal mode: /HPM="H"). However for LCDs or panels with large loads, this low-power power supply may cause display quality to degrade. When this occurs, setting the /HPM terminal to "L" (high power mode) can improve the quality of the display. We recommend that the display be checked on actual equipment to determine whether or not to use this mode.

Moreover, if the improvement to the display is inadequate even after the high power mode has been set, then it is necessary to add a Command Sequence when Built-in Power Supply is turned OFF. To turn off the built-in power supply, follow the command sequence as shown below to turn it off after making the system enter standby mode.

#### Reference Power Supply Circuit for Driving LCD Panel

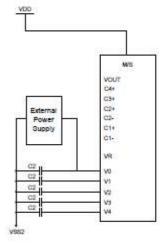

-When using all LCD power circuits (Voltage booster, regulator and follower) (In case of 4X boosting circuit and internal regulator resistors, IRS=1) --When not using voltage booster circuits (In case of external regulator resistors, IRS=0)

-When only using voltage follower

-When not using internal LCD power supply circuits

### 5.3 Command Table

|                                                            |    |     |     |    |     |     |        | Code   |               |                 |        |                  |                                                                         |            |  |            |  |           |  |          |  |         |  |    |                                                          |

|------------------------------------------------------------|----|-----|-----|----|-----|-----|--------|--------|---------------|-----------------|--------|------------------|-------------------------------------------------------------------------|------------|--|------------|--|-----------|--|----------|--|---------|--|----|----------------------------------------------------------|

| Command                                                    | A0 | /RD | /WR | D7 | D6  | D5  | D4     | D3     | D2            | D1              | D0     | Hex              | Function                                                                |            |  |            |  |           |  |          |  |         |  |    |                                                          |

| (1) Display OFF                                            | 0  | 1   | 0   | 1  | 0   | 1   | 0      | 1      | 1             | 1               | 0<br>1 | AEh<br>AFh       | Turn on LCD panel when high, and<br>turn off when low                   |            |  |            |  |           |  |          |  |         |  |    |                                                          |

| (2) Display Start Line Set                                 | 0  | 1   | 0   | 0  | 1   |     | Disp   | lay St | art Ad        | dress           |        | 40h<br>to<br>7Fh | Specifies RAM display line for<br>COM0                                  |            |  |            |  |           |  |          |  |         |  |    |                                                          |

| (3) Page Address Set                                       | 0  | 1   | 0   | 1  | 0   | 1   | 1      | F      | Page /        | Addres          | 55     | B0h<br>to<br>B8h | Set the display data RAM page in<br>Page Address register               |            |  |            |  |           |  |          |  |         |  |    |                                                          |

| (4) Column Address Set                                     | 0  | 1   | 0   | 0  | 0   | 0   | 1      | ŀ      | ligher<br>Ado | Colun<br>iress  | nn     | 00h<br>to        | Set 4 higher bits and 4 lower bits<br>of column address of display data |            |  |            |  |           |  |          |  |         |  |    |                                                          |

| (4) Column Address Sec                                     | 0  | 1   | 0   | 0  | 0   | 0   | 0      | L      | .ower<br>Ado  | Colum<br>iress  | In     | 18h              | RAM in register                                                         |            |  |            |  |           |  |          |  |         |  |    |                                                          |