#### FEATURES AND BENEFITS

- AEC-Q100 qualified (K version)

- Sinusoidal drive for low audible noise

- Minimum speed function

- Quiet startup adjustment feature

- High efficiency control algorithm

- Sensorless operation

- PWM speed input

- FG speed output

- Lock detection

- Short circuit protection (OCP)

- Overcurrent limit (OCL)

### PACKAGES:

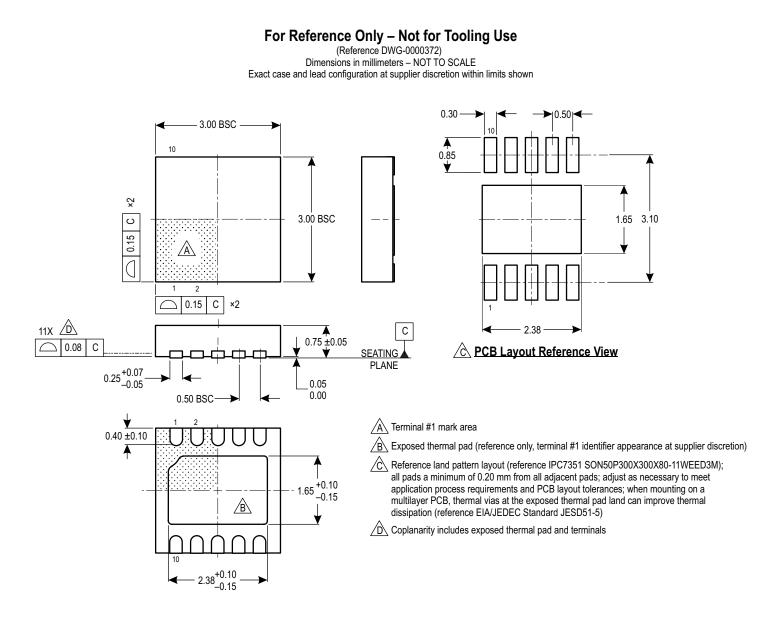

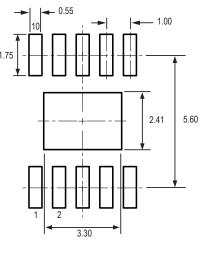

10-contact 3 mm × 3 mm DFN package with exposed thermal pad (suffix EJ)

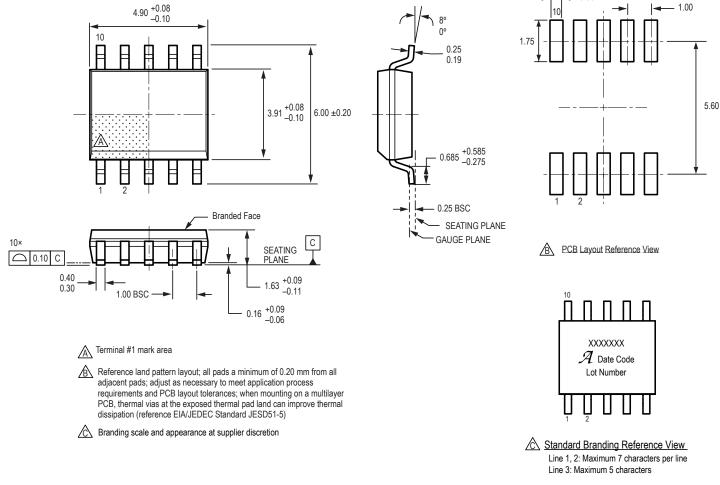

10-lead SOIC (suffix LN)

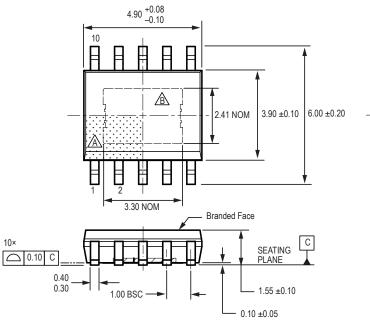

10-lead SOIC with exposed thermal pad (suffix LK)

Not to scale

### DESCRIPTION

The A5940 three phase motor driver incorporates sinusoidal drive to minimize audible noise and vibration for medium power fans.

A sinusoidal voltage profile is applied to the windings of the motor at startup to quietly startup and gradually ramp up the motor to desired speed. The voltage profile is selectable via SOFTST pin to allow proper operation with a wide range of motor characteristics.

The motor speed is controlled by applying a duty cycle command to the PWM input. The PWM input is allowed to operate over a wide frequency range.

The A5940 is supplied in a 10-contact 3 mm  $\times$  3 mm DFN package with exposed thermal pad (suffix EJ), a 10-lead SOIC (suffix LN), and a 10-lead SOIC with exposed thermal pad (suffix LK). The packages are lead (Pb) free, with 100% matte tin leadframe plating.

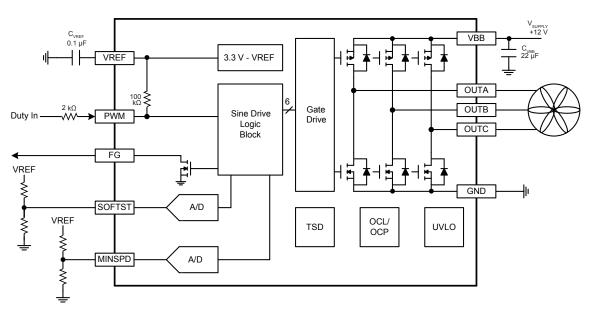

### **Typical Application**

### **SELECTION GUIDE**

| Part Number                 | Ambient Temperature Range                                                           | t Temperature Range Packing Package      |                                         |

|-----------------------------|-------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------|

| A5940GEJTR-T                | –40°C to 105°C                                                                      | 1500 pieces per 7-in. reel               | 10-contact DFN with exposed thermal pad |

| A5940GLKTR-T                | 040GLKTR-T -40°C to 105°C 3000 pieces per 13-in. reel 10-lead SOIC with exposed the |                                          | 10-lead SOIC with exposed thermal pad   |

| A5940GLNTR-T                | –40°C to 105°C                                                                      | 3000 pieces per 13-in. reel 10-lead SOIC |                                         |

| A5940KLKTR-T <sup>[1]</sup> | –40°C to 125°C                                                                      | 3000 pieces per 13-in. reel              | 10-lead SOIC with exposed thermal pad   |

<sup>[1]</sup> The A5940KLKTR-T variant is in production, however, it has been deemed Pre-End of Life. This variant is approaching end of life. Within a minimum of 6 months, this variant will enter its final, Last Time Buy, order phase. Date of status change: December 5, 2018.

#### **ABSOLUTE MAXIMUM RATINGS**

| Characteristic                             | Symbol               | Notes               | Rating                     | Unit |

|--------------------------------------------|----------------------|---------------------|----------------------------|------|

| Supply Voltage                             | V <sub>BB</sub>      |                     | 18                         | V    |

| Logic Input Voltage Range V <sub>PWM</sub> |                      | PWM                 | –0.3 to 6                  | V    |

| Logic Output (FG)                          | V <sub>FG</sub>      | FG (I < 5 mA)       | 18                         | V    |

| Analog Input                               | V <sub>IN</sub>      | MINSPD, SOFTST      | –0.3 to V <sub>REF</sub>   | V    |

| Output Current                             | I <sub>OUT</sub>     |                     | I <sub>OCL</sub>           | А    |

| Output Voltage                             | V <sub>OUT</sub>     | OUTA, OUTB, OUTC    | -1.2 to V <sub>BB</sub> +1 | V    |

| Operating Temperature Dange                |                      | G temperature range | -40 to 105                 | °C   |

| Operating Temperature Range                | T <sub>A</sub>       | K temperature range | -40 to 125                 | °C   |

| Maximum Junction Temperature               | T <sub>J</sub> (max) |                     | 150                        | °C   |

| Storage Temperature                        | T <sub>stg</sub>     |                     | 150                        | °C   |

#### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic             | Package | Symbol Test Conditions |                                            | Value | Unit |

|----------------------------|---------|------------------------|--------------------------------------------|-------|------|

|                            | EJ      |                        | 2-sided PCB with 1 in. <sup>2</sup> copper | 60    | °C/W |

| Package Thermal Resistance | LN      | R <sub>θJA</sub>       | Single-sided PCB                           | 130   | °C/W |

|                            | LK      |                        | 2-sided PCB with 1 in. <sup>2</sup> copper | 40    | °C/W |

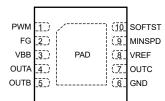

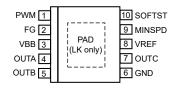

#### 10-contact DFN Pinout (suffix EJ)

10-lead SOIC Pinout (suffix LK/LN)

#### **Terminal List Table**

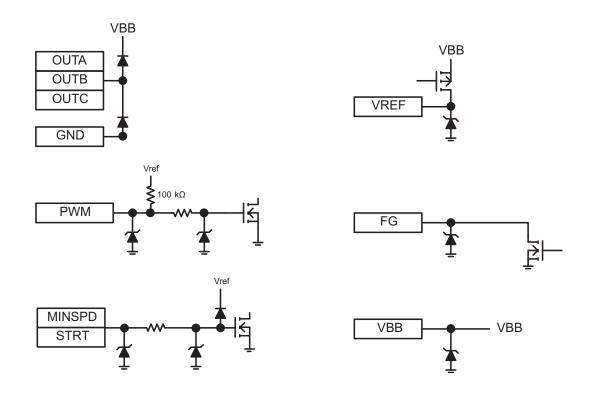

| Number | Name   | Function            |  |

|--------|--------|---------------------|--|

| 1      | PWM    | Logic input – speed |  |

| 2      | FG     | Speed output signal |  |

| 3      | VBB    | Input supply        |  |

| 4      | OUTA   | Motor terminal A    |  |

| 5      | OUTB   | Motor terminal B    |  |

| 6      | GND    | Ground              |  |

| 7      | OUTC   | Motor terminal C    |  |

| 8      | VREF   | Analog output       |  |

| 9      | MINSPD | Analog input        |  |

| 10     | SOFTST | Analog input        |  |

#### ELECTRICAL CHARACTERISTICS: Unless otherwise specified,

G version valid at T<sub>A</sub> = 25°C, V<sub>BB</sub> = 4 V to 18 V; K version valid at T<sub>J</sub> = -40°C to 125°C; V<sub>BB</sub> = 4 V to 18 V

| Characteristic                      | Symbol                 | Test Conditions                                        | Min. | Тур. | Max. | Unit |

|-------------------------------------|------------------------|--------------------------------------------------------|------|------|------|------|

| VBB Supply Current                  | I <sub>BB</sub>        | PWM = LOW                                              | _    | 8    | 12   | mA   |

|                                     |                        | I = 1 A, T <sub>J</sub> = 25°C, V <sub>BB</sub> = 12 V | _    | 1.25 | 1.5  | Ω    |

| Total Driver On-Resistance          |                        | Source driver                                          | 650  | 900  | 1200 | mΩ   |

| (Sink + Source)                     | R <sub>DS(on)</sub>    | Sink driver                                            | 250  | 350  | 450  | mΩ   |

|                                     |                        | I = 1 A, T <sub>J</sub> = 25°C, V <sub>BB</sub> = 4 V  | _    | 1.9  | 2.2  | Ω    |

| VREF Output Voltage                 | V <sub>REF</sub>       | I <sub>OUT</sub> = 5 mA                                | 3.2  | 3.3  | 3.4  | V    |

| Input Pull-Up Resistance (PWM)      | R <sub>PU</sub>        | PWM                                                    | 70   | 100  | 130  | kΩ   |

| Logic Input Low Level               | V <sub>IL</sub>        | PWM                                                    | _    | _    | 0.8  | V    |

| Logic Input High Level              | V <sub>IH</sub>        |                                                        | 2    | _    | _    | V    |

| Logic Input Hysteresis              | V <sub>HYS</sub>       |                                                        | 200  | 300  | 600  | mV   |

| Output Saturation Voltage           | V <sub>SAT</sub>       | I = 5 mA                                               | _    | _    | 0.3  | V    |

| FG Output Leakage                   | I <sub>FG</sub>        | V = 18 V, FG switch OFF                                | _    | _    | 1    | μA   |

| MOTOR FUNCTION                      |                        |                                                        |      |      |      |      |

| PWM Duty OF Threshold               | DC <sub>ON</sub>       |                                                        | 8.7  | 9    | 9.3  | %    |

| PWM Duty OFF Threshold              | DC <sub>OFF</sub>      |                                                        | 7.3  | 7.6  | 7.9  | %    |

| PWM Input Frequency Range           | f <sub>PWM</sub>       |                                                        | 0.1  | _    | 100  | kHz  |

| Motor PWM Freqency                  | f <sub>PWM</sub>       |                                                        | 21   | 24.4 | 28.8 | kHz  |

| MIN Speed Selection                 |                        | Relative to target                                     | 0.5  | -    | 0.5  | %    |

| Input Current (MINSPD, SOFTST pins) | I <sub>IN</sub>        | V <sub>IN</sub> = 0 to 5.5 V                           | -1   | 0    | 1    | μA   |

| PROTECTION                          |                        |                                                        |      |      |      |      |

| VBB Pin Undervoltage Lockout (UVLO) | V <sub>BBUVLO</sub>    | V <sub>BB</sub> rising                                 | _    | 3.75 | 3.95 | V    |

| VBB Pin UVLO Hysteresis             | V <sub>BBUVLOHYS</sub> |                                                        | 150  | 300  | 450  | mV   |

| Overcurrent Limit                   |                        | A5940K; T <sub>J</sub> = 25°C                          | 1.7  | 2.1  | 2.5  | А    |

|                                     | I <sub>OCL</sub>       | A5940G; T <sub>J</sub> = 25°C                          | 1.7  | -    | 2.7  | А    |

| Lock Timing                         | t <sub>OFF</sub>       |                                                        | 4.5  | 5    | 5.5  | s    |

| Thermal Shutdown Temperature        | T <sub>JTSD</sub>      | Temperature increasing                                 | 150  | 165  | 180  | °C   |

| Thermal Shutdown Hysteresis         | T <sub>JHYS</sub>      | Recovery = $T_{JTSD} - T_{JHYS}$                       | _    | 20   | _    | °C   |

Note 1: Specified limits are tested at a single temperature and assured across the operating temperature range by design and characterization.

# A5940

## **Three Phase Sensorless Sinusoidal Fan Driver**

### FUNCTIONAL DESCRIPTION

The A5940 targets fan applications to meet the objectives of low audible noise, minimal vibration, and high efficiency. Allegro's proprietary control algorithm results in a sinusoidal current waveshape that adapts to a variety of motor characteristics to dynamically optimize efficiency across a wide range of speeds.

The speed of the fan is controlled by variable duty cycle PWM input.

The PWM input duty is measured and converted to a 9-bit number. This 9-bit "demand" is applied to a PWM generator block to create the modulation profile. The modulation profile is applied to the three motor outputs, with 120 degree phase relationship, to create the sinusoidal current waveform as shown in Figure 1.

A BEMF detection "window" is opened on phase A modulation profile in order to measure the rotor position so as to define the modulation timing. The control system maintains the window to a small level in order to minimize the disturbance and approximate the ideal sinusoidal current waveform as much as possible.

Protection features include lock detection with restart, motor output short circuit, supply undervoltage monitor, and thermal shutdown.

Figure 1. Sinusoidal PWM

### **Speed Control**

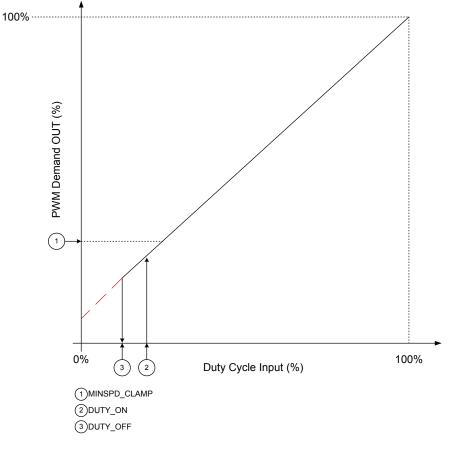

**PWM - Duty Cycle Input.** A duty cycle measurement circuit converts the applied duty to a demand value (9-bit resolution) to control speed of the fan.

The motor drive will be enabled if duty is larger than DC\_ON

The PWM input is filtered to prevent spurious noise from turning on or off unexpectedly.

There is an internal pull-up  $(100 \text{ k}\Omega)$  that will turn motor on to maximum speed if input signal is disconnected.

Figure 2. Speed Input Characteristic

**Lock Detect.** Speed is monitored to determine if rotor is locked. If a lock condition is detected, the IC will be disabled for  $t_{OFF}$  before an auto-restart is attempted.

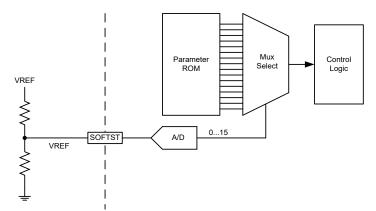

**FG.** Open drain output provides speed information to the system. FG changes state one period per electrical revolution of the motor (as shown in Figure 1). **Min Speed Function.** Connecting a resistor divider to VREF sets a voltage that is translated to a minimum speed clamp integer by a 4-bit A/D. Connect MINSPD to GND to turn motor off with low ( $< DC_{OFF}$ ) duty applied. The MINSPD pin should be connected to a voltage between VREF and GND and should not be left an open circuit.

A resistor divider in range 50 to 100 k $\Omega$  is recommended.

| V <sub>MINSPD</sub> | Code | Demand % |

|---------------------|------|----------|

| 0                   | 0    | 0        |

| 0.2                 | 51   | 10.0     |

| 0.4                 | 62   | 12.1     |

| 0.6                 | 73   | 14.3     |

| 0.8                 | 82   | 16.0     |

| 1                   | 93   | 18.2     |

| 1.2                 | 104  | 20.3     |

| 1.4                 | 115  | 22.5     |

| 1.6                 | 126  | 24.7     |

| 1.8                 | 137  | 26.8     |

| 2.0                 | 148  | 29       |

| 2.2                 | 159  | 31.1     |

| 2.4                 | 170  | 33.3     |

| 2.6                 | 181  | 35.4     |

| 2.8                 | 192  | 37.6     |

| VREF                | 203  | 39.7     |

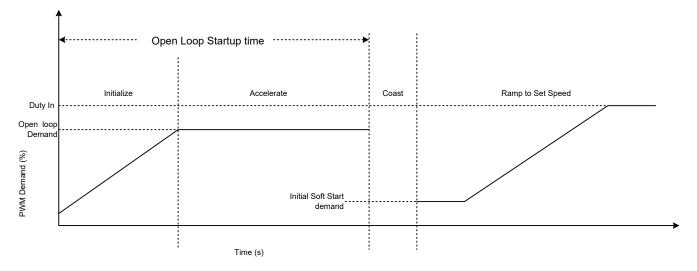

### **Quiet Startup Operation**

A5940 achieves quiet startup with the following sequence:

- 1. Slowly ramp PWM duty from low value to a chosen Open loop Demand level by stepping motor with a waveshaped sine drive modulation profile.

- 2. After the fixed open loop Time, the motor position is measured, an initial demand value applied, and slowly the demand is ramped to the final value which is calculated by the duty cycle measurement circuit.

- 3. The time to ramp to final value depends on Duty IN and Initial Soft Start demand as follows:

$t_{SS} = (target duty \% - Initial Demand \%) \times 8192 ms$

Example target duty = 50%, SOFTST = 15 = VREF (from parameter table Initial SS Demand = 25%)

$t_{SS} = (50-25)\% \times 8192 \text{ ms} \rightarrow 2.048 \text{ s}$

### Startup Adjustment

Various permutations of startup parameters are chosen via lookup table with A/D conversion. Sixteen choices of startup parameters are selected by applying voltage at pin SOFTST.

A resistor divider in the range of 50 to 100 k $\Omega$  is recommended. The SOFTST pin should be connected to a voltage between VREF and GND and should not be left open circuit.

The various selections have different choices for open loop duration, open loop demand, and initial demand value of soft start after the open loop startup period.

| V <sub>SOFTST</sub> | Selection | Open Loop<br>Time (s) | Open Loop<br>Demand (%) | Initial Soft Start<br>Demand (%) |

|---------------------|-----------|-----------------------|-------------------------|----------------------------------|

| GND                 | 0         | 1.1                   | 20.5                    | 11.1                             |

| 0.2                 | 1         | 1.1                   | 8.1                     | 6.2                              |

| 0.4                 | 2         | 1.1                   | 21.0                    | 11.1                             |

| 0.6                 | 3         | 1.1                   | 28.9                    | 23.8                             |

| 0.8                 | 4         | 1.1                   | 40.0                    | 14.4                             |

| 1.0                 | 5         | 1.1                   | 52.5                    | 11.1                             |

| 1.2                 | 6         | 1.1                   | 52.6                    | 23.8                             |

| 1.4                 | 7         | 1.1                   | 62.3                    | 23.8                             |

| 1.6                 | 8         | 1.1                   | 79.0                    | 11.1                             |

| 1.8                 | 9         | 1.1                   | 96.6                    | 11.1                             |

| 2.0                 | 10        | 1.9                   | 28.9                    | 14.4                             |

| 2.2                 | 11        | 1.9                   | 40.0                    | 23.8                             |

| 2.4                 | 12        | 1.9                   | 59.4                    | 37.9                             |

| 2.6                 | 13        | 1.9                   | 77                      | 37.9                             |

| 2.8                 | 14        | 1.9                   | 98.5                    | 48.8                             |

| VREF                | 15        | 1.9                   | 63.5                    | 23.8                             |

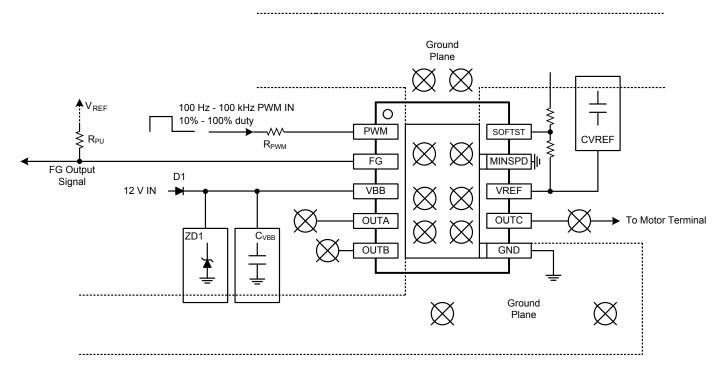

### **APPLICATION INFORMATION**

#### **Typical Application Circuit**

| Name             | Suggested Value   | Comment                                                                                                                                                                                                  |

|------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CVREF            | 0.1 µF, X5R, 10 V | Ceramic capacitor required                                                                                                                                                                               |

| CVBB             | 4.7 μf to 47 μF   | Power Supply Stabilization – Electrolytic or ceramic OK.                                                                                                                                                 |

| R <sub>FG</sub>  | 20 kΩ             | Optional – pull-up resistor for speed feedback                                                                                                                                                           |

| D1               | Not Installed     | May be required to isolate motor from system or for reverse polarity protection                                                                                                                          |

| ZD1              | Not Installed     | Optional TVS to limit max V <sub>BB</sub> due to transients due to motor generation or power line. Suggested to clamp below 18 V (EX : Fairchild SMBJ14A). Typically required if blocking diode D1 used. |

| R <sub>PWM</sub> | 1 kΩ              | Optional – If PWM wired to connector – R <sub>PWM</sub> will isolate IC pin from noise or overvoltage transients.                                                                                        |

Layout Notes:

- 1. Add thermal vias to exposed pad area. Add ground plane on top and bottom of PCB.

- 2. Place CVREF and CVBB as close as possible to IC.

**PIN DIAGRAMS**

### Package EJ, 10-Contact DFN

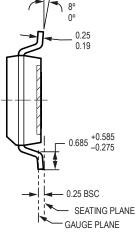

Package LN, 10-Lead SSOP

For Reference Only – Not for Tooling Use

(Reference DWG-0000385, Rev. 2) NOT TO SCALE Dimensions in millimeters Dimensions exclusive of mold flash, gate burrs, and dambar protrusions Exact case and lead configuration at supplier discretion within limits shown

Line 1: Part Number Line 2: Logo A, 4-digit Date Code Line 3: Characters 5, 6, 7, 8 of Assembly Lot Number

0.55

#### Package LK, 10-Lead eSOIC with Exposed Pad

## For Reference Only – Not for Tooling Use

(Reference DWG-0000380, Rev. 1) NOT TO SCALE Dimensions in millimeters Dimensions exclusive of mold flash, gate burrs, and dambar protrusions Exact case and lead configuration at supplier discretion within limits shown

A Terminal #1 mark area

A

Exposed thermal pad (bottom surface)

Reference land pattern layout; all pads a minimum of 0.20 mm from all adjacent pads; adjust as necessary to meet application process requirements and PCB layout tolerances; when mounting on a multilayer PCB, thermal vias at the exposed thermal pad land can improve thermal

dissipation (reference EIA/JEDEC Standard JESD51-5)

C PCB Layout Reference View

Standard Branding Reference View Line 1, 2: Maximum 7 characters per line Line 3: Maximum 5 characters

> Line 1: Part Number Line 2: Logo A, 4-digit Date Code Line 3: Characters 5, 6, 7, 8 of Assembly Lot Number

#### **Revision History**

| Number | Date             | Description                               |

|--------|------------------|-------------------------------------------|

| 1      | March 20, 2014   | Revised Package Drawing                   |

| 2      | July 17, 2014    | Added K version                           |

| 3      | March 30, 2016   | Corrected LK package drawing dimension    |

| 4      | July 26, 2018    | Minor editorial updates                   |

| 5      | February 5, 2019 | Product status changed to Pre-End-of-Life |

| 6      | April 1, 2019    | Corrected product status                  |

| 7      | July 28, 2021    | Updated package drawings                  |

| 8      | May 19, 2022     | Updated Overcurrent Limit (page 3)        |

Copyright 2022, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.