# CDB5466U Evaluation Board

### **Features**

- Active Energy-to-Pulse Conversions

- Simple Configuration Jumpers

- Current Channel Gain

- High-pass Filter

- Energy-to-pulse Output Frequency

- Energy Pulses

- Collected by On-board Microcontroller

- Available on External Header

- Viewable via LEDs

- Multiple Supply Voltage Selections

- USB Communication with PC

- On-board Voltage Reference

# **General Description**

The CS5466 is a low cost power/energy IC with pulse output for power measurement solutions. The CDB5466U Evaluation Board is an inexpensive tool designed to evaluate the functionality and performance of the CS5466.

The evaluation board is designed to output energy-topulse conversions upon power-up. The CS5466 data sheet should be read and consulted when using the CDB5466U evaluation board.

The evaluation board includes a microcontroller with a USB interface. The microcontroller and GUI (Graphical User Interface) provide a means to quickly register and evaluate the CS5466's energy-to-pulse outputs.

#### ORDERING INFORMATION

CDB5466U Evaluation Board

# **TABLE OF CONTENTS**

| LIST OF FIGURES                                             | 2               |

|-------------------------------------------------------------|-----------------|

| LIST OF TABLES                                              | 2               |

| 1. HARDWARE                                                 | 3               |

| 1.1 Introduction                                            |                 |

| 1.2 Evaluation Board Overview                               |                 |

| 1.2.1 Analog Section                                        |                 |

| 1.2.2 Digital Section                                       |                 |

| 1.2.3 Power Supply Section                                  |                 |

| 2. SOFTWARE                                                 |                 |

| 2.1 Installation Procedure                                  |                 |

| 2.2 Using the Software                                      |                 |

| 2.2.1 Start-Up Window                                       |                 |

| 2.2.2 CS5466 Pulse Rate Output Window                       |                 |

| 3. SCHEMATICS                                               |                 |

| 4. LAYOUT                                                   | 18              |

|                                                             |                 |

|                                                             |                 |

|                                                             | LIST OF FIGURES |

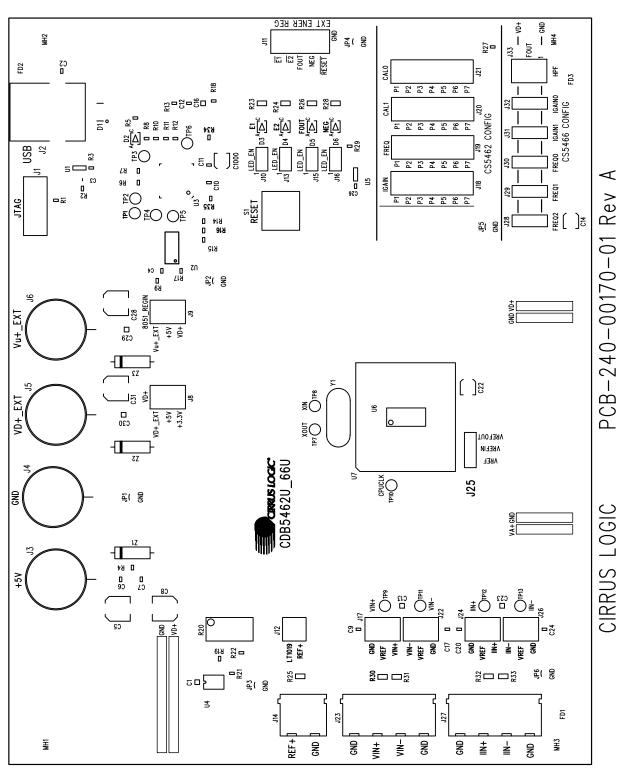

| Figure 1. CDB5466U Assembly Drawing                         | 3               |

| Figure 2. CDB5466U Start-up Window                          |                 |

| Figure 3. Alert Window                                      | 10              |

| Figure 4. Quit Window                                       |                 |

| Figure 5. CDB5466 Evaluation Board                          | 11              |

| Figure 6. CDB5466U Pulse Rate Output Window                 |                 |

| Figure 7. Analog Inputs                                     |                 |

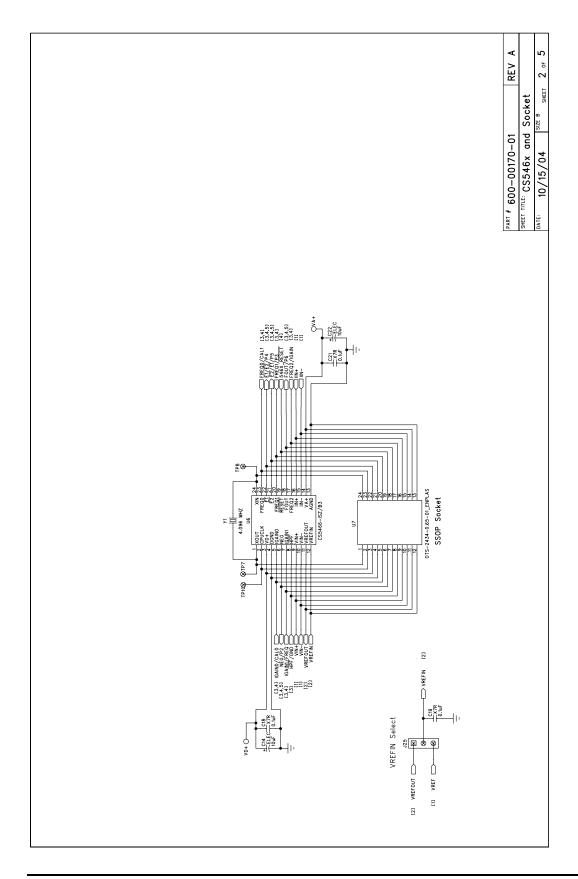

| Figure 8. CS546x and Socket                                 |                 |

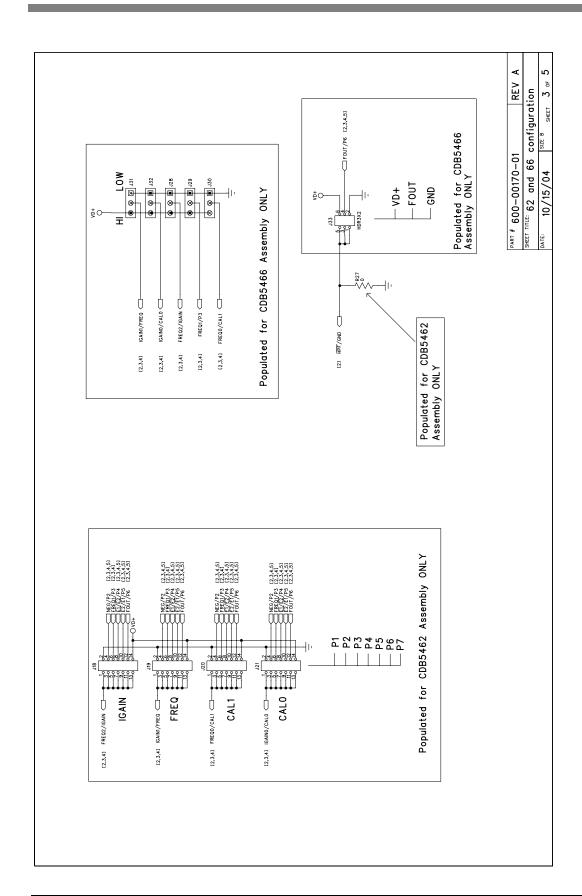

| Figure 9. CS5462 and CS5466 Configuration                   |                 |

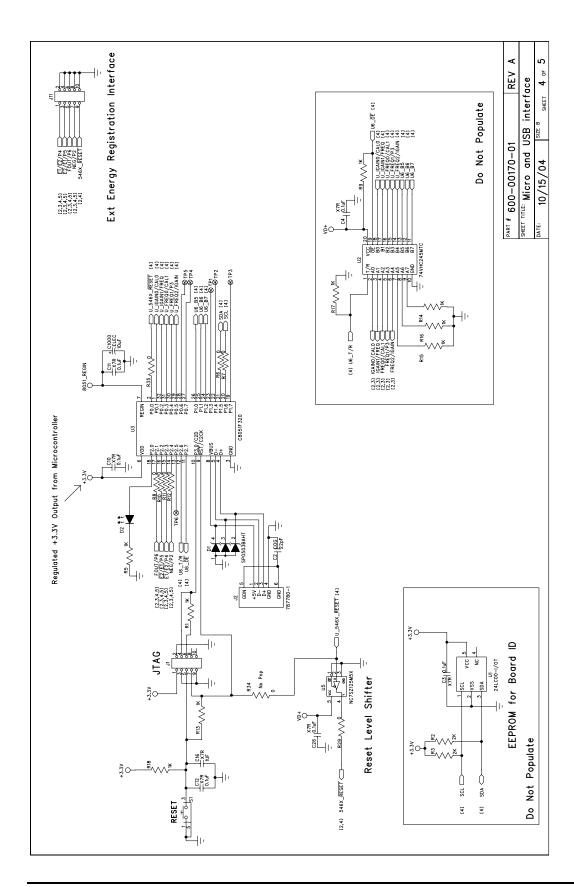

| Figure 10. Microcontroller and USB Interface                | 16              |

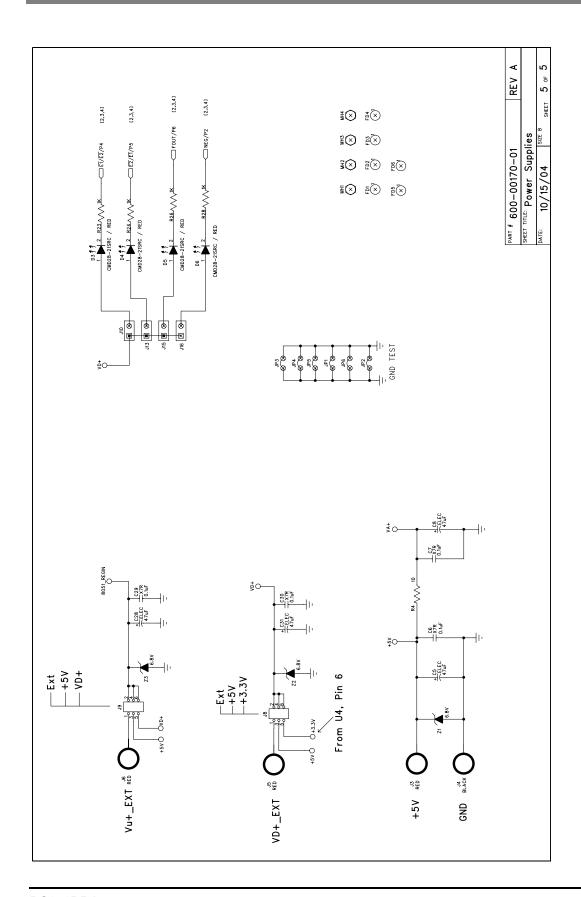

| Figure 11. Power Supply                                     |                 |

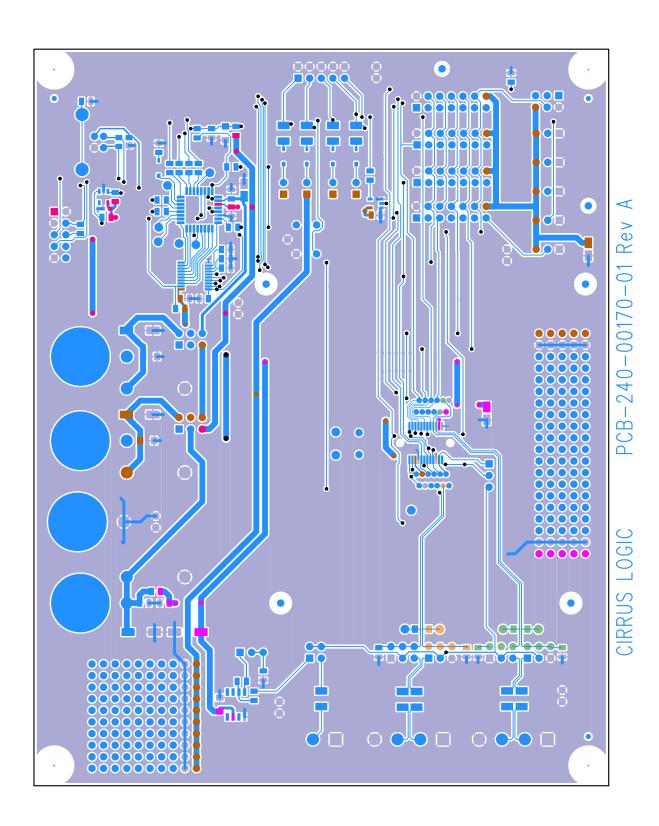

| Figure 1. Silk Screen                                       |                 |

| Figure 1. Topside Layer                                     |                 |

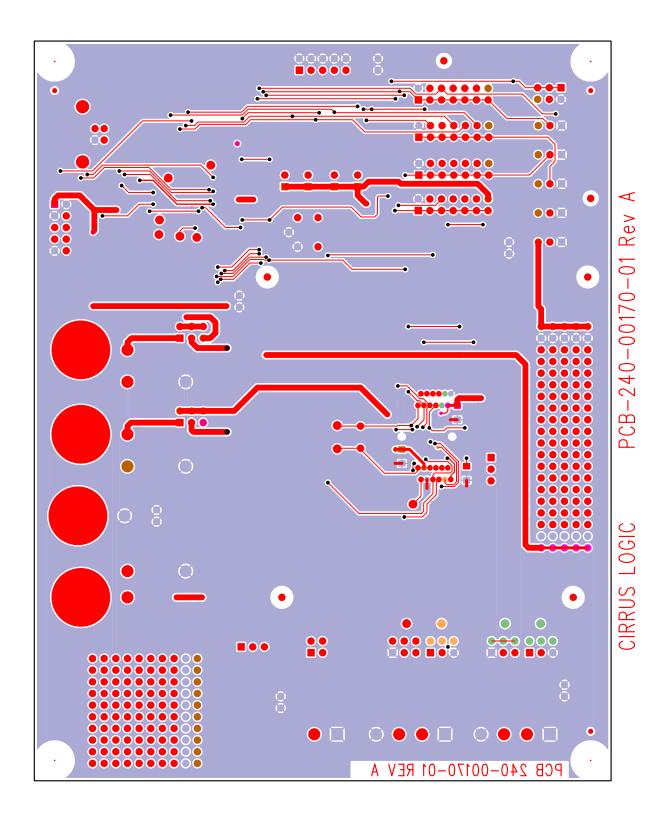

| Figure 1. Bottomside Layer                                  | 19              |

|                                                             |                 |

|                                                             |                 |

|                                                             | LIST OF TABLES  |

| Table 1. Voltage Reference Selection for VREF               | 4               |

| Table 2. Voltage Reference Selection for VREF               |                 |

| Table 3. Voltage and Current Channel Input Signal Selection | 5               |

| Table 4. Current Channel PGA Selection                      |                 |

| Table 5. HPF Option Selection                               |                 |

| Table 6. Energy Output Frequency                            |                 |

| Table 7. Power Supply Connections                           |                 |

#### 1. HARDWARE

### 1.1 Introduction

The CS5466 is a low cost power measurement solution combining two  $\Delta\Sigma$  analog-to-digital converters (ADCs), an energy-to-frequency converter, and energy pulse outputs on a single chip. It is designed to accurately measure and calculate energy for single phase, 2- or 3-wire power metering applications with minimal external components.

Low-frequency energy outputs,  $\overline{E1}$  and  $\overline{E2}$  supply average active power and can be used to drive a stepper motor or a mechanical counter; the high-frequency energy output FOUT is designed to assist in calibration; and *NEG* indicates negative energy.

The CS5466 has configuration pins which allow the selection of pulse output frequency, current channel input range, and the high-pass filter enable option. The CS5466 also has a power-on reset function which holds the part in reset until the supply reaches the proper level. The CDB5466U is shipped with a CS5466-ISZ device located at U6.

#### 1.2 Evaluation Board Overview

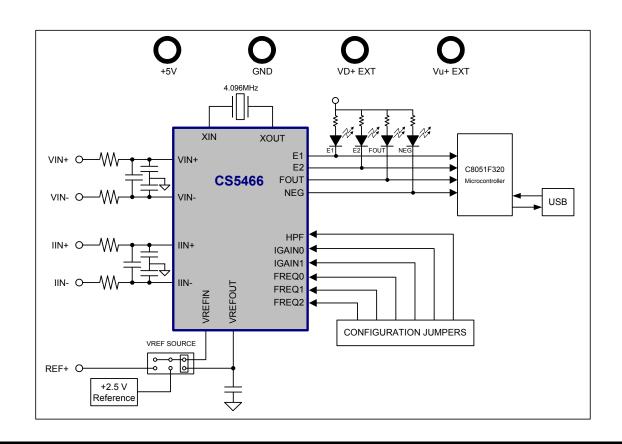

The CDB5466U evaluation board provides a quick path to evaluating the CS5466 Power Measurement IC. Figure 1 illustrates the placement of the terminals, jumpers and IC components. The jumper options are shown in the factory default positions.

Figure 1. CDB5466U Assembly Drawing

The CDB5466U evaluation board is partitioned into two main sections - analog and digital. The analog section consists of the CS5466 and a precision voltage reference that operates from a single +5 V power supply. The digital section consists of the microcontroller, the reset circuitry, and the USB interface. The digital section can operate from a +5 V or +3.3 V power supply. The evaluation board is epuipped with power supply connections that accommodate all of the various supply options of the CS5466.

The evaluation board is designed to output energy-to-pulse conversions upon power-up. Software that runs on a PC provides a GUI (Graphical User Interface) as a means to quickly register and evaluate the CS5466's energy-to-pulse outputs. To accomplish this, the board comes equipped with USB drivers and cable which physically interfaces the evaluation board to the PC. The software provides easy access to the energy outputs E1, E2, and FOUT and provides a means to display and evaluate the performance of the CS5466.

## 1.2.1 Analog Section

The CDB5466U evaluation board provides screw-type terminals (J23 and J27) to connect input signals to the voltage and current channels. The screw terminals are labeled as VIN+, VIN-, IIN+, and IIN-. A simple R-C network at each channel input provides a simple anti-alias filter.

The evaluation board provides three voltage reference options for VREFIN to the CS5466. The three voltage reference options include: VREFOUT from the CS5466, the on-board +2.5 V reference, and external REF+ (screw terminal J14). Table 1 and Table 2 illustrate the options available for VREFIN. With a jumper on J25 in the position

| Reference | Description                                  | J25                               |

|-----------|----------------------------------------------|-----------------------------------|

| VREFOUT   | Selects on-Chip<br>Reference (25ppm/°C)      | VREF O VREFIN O VREFOUT (Default) |

| VREF      | Selects External or<br>LT1019 Reference(J12) | VREF → VREFIN → VREFOUT □         |

Table 1. Internal Voltage Reference Selection for VREF

labeled *VREFOUT*, the reference is supplied by the on-chip voltage reference. With a jumper on J25 in the position labeled *VREF*, the reference is supplied by an off-chip voltage reference.

Table 2 illustrates the options available for VREF. With a jumper on J12 in position LT1019, the LT1019 provides a

| Reference | Description                                       | J12                               |  |  |

|-----------|---------------------------------------------------|-----------------------------------|--|--|

| LT1019    | Selects on-Board<br>LT1019 Reference<br>(5ppm/°C) | LT1019 VREF                       |  |  |

| REF+      | Selects External<br>Reference Source<br>(J6)      | LT1019 O VREF REF+ VREF (Default) |  |  |

Table 2. External Voltage Reference Selection for VREF

+2.5 V reference (the LT1019 was chosen for its low drift - typically 5ppm/°C). By setting the jumper on J12 to position *REF*+, an external voltage reference is supplied via screw terminal J14's *REF*+ input.

The three input signal options for the voltage (VIN±) and current (IIN±) channel input include: an external signal (screw terminals J23 and J27), *GND* or *VREF*. Table 3 illustrates the options available. By installing jumpers on J17

to position VIN+, J22 to position VN-, J24 to position IIN+ and J26 to position IIN-, the input voltage signal is supplied from the screw terminals J23 and J27. With a jumper on J17, J22, J24 and J26 in the GND position, the inputs are connected to analog ground (AGND). With a jumper on J17, J22, J24 and J26 in position VREF, the inputs are connected to the reference voltage selected on J12.

| INPUT        | Description                    | J17                                       | J22                                                       | J24                                       | J26                                         |

|--------------|--------------------------------|-------------------------------------------|-----------------------------------------------------------|-------------------------------------------|---------------------------------------------|

| VIN± or IIN± | Selects External<br>Signal     | GND □ O VIN+ VREF O O VIN+ VIN+ (Default) | VIN- □ O VIN-<br>VREF O O VIN-<br>GND → VIN-<br>(Default) | GND □ O IIN+ VREF O O IIN+ IIN+ (Default) | IIN- □ O IIN- VREF O O IIN- GND             |

| VIN± or IIN± | Selects External<br>Signal     | GND □ O VIN+ VREF O O VIN+ VIN+ • VIN+    | VIN- VIN-<br>VREF O O VIN-<br>GND O O VIN-                | GND □ O IIN+ VREF O O IIN+ IIN+  □ □ IIN+ | IIN- IIN- VREF O O IIN- GND O O IIN-        |

| GND          | Selects Grounding<br>the Input | GND VIN+ VREFO O VIN+ VIN+ O O VIN+       | VIN-  O VIN-<br>VREF O O VIN-<br>GND VIN-                 | GND IIN+ VREF O O IIN+ IIN+ O O IIN+      | IIN-□ O IIN-<br>VREF O O IIN-<br>GND ⊕ IIN- |

| VREFIN       | Selects Reference<br>Source    | GND   O VIN+ VREF  VIN+ VIN+ O O VIN+     | VIN- U O VIN-<br>VREF VIN-<br>GND O O VIN-                | GND □ O IIN+<br>VREF                      | IIN- O IIN-<br>VREF IIN-<br>GND O O IIN-    |

Table 3. Voltage and Current Channel Input Signal Selection

### 1.2.2 Digital Section

The digital section contains the microcontroller, USB interface, JTAG header, reset circuitry, and an external interface header (J11). The microcontroller interfaces the energy pulses,  $\overline{E1}$ ,  $\overline{E2}$ , and FOUT output by the CS5466 with the USB connection to the PC. The microcontroller also provides a hardware reset to the CS5466, which is level shifted to support both +3.3 V and +5 V digital operation. Interface header, J11, is provided to allow the CDB5466U to be connected to an external energy registration device. The energy output pins  $\overline{E1}$ ,  $\overline{E2}$ , FOUT and NEG are routed to LEDs which provide a simple visual check of the energy output pulses. Jumpers J10, J13, J15 and J16 are equipped at the factory with jumpers to enable the LEDs.

### 1.2.2.1 Current Channel Gain

To accommodate different current-sensing elements the current channel incorporates a programmable gain that can be set to one of four input ranges. Input pins IGAIN1 and IGAIN0 define the four gain selections and corresponding maximum input signal level. Jumpers J31 and J32 define the state of IGAIN1 and IGAIN0, respectively. Table 4 illustrates the options available. With jumpers J31 = J32 = GND the gain is set to 10x. With jumpers J31 = GND and J32 = FND the gain is set to 50x. With jumpers J31 = FND and J32 = FND the gain is set to 100x. With jumpers J31 = FND and J32 = FND the gain is set to 150x.

| Maximum  | Input Range | IGAIN1                                   | IGAIN0                                   |  |

|----------|-------------|------------------------------------------|------------------------------------------|--|

|          |             | J31                                      | J32                                      |  |

| ±250mV   | 10x         | VD+ □ IGAIN1 □ GND □ (Default)           | VD+ □ IGAIN0 • GND • (Default)           |  |

| ±50mV    | 50x         | VD+ □ IGAIN1 G GND                       | VD+ IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII |  |

| ±25mV    | 100x        | VD+ IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII | VD+ □ IGAINO  GND                        |  |

| ±16.67mV | 150x        | VD+ IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII | VD+ IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII |  |

**Table 4. Current Channel PGA Selection**

### 1.2.2.2 High-pass Filter

By removing the offset from either channel, no error component will be generated at DC when computing the active (real) power. Input pin *HPF* defines the three options, and J33 defines the state of the HPF pin.

- HPF is enabled in the voltage channel when jumper J33 = GND.

- HPF is enabled in the current channel when pin HPF is connected to pin FOUT.

- High-Pass Filter (HPF) is disabled when jumper J33 = VD+.

|                    | HPF                              |                                          |

|--------------------|----------------------------------|------------------------------------------|

| High Pass          | J33                              |                                          |

| Voltage<br>Channel | HPF Option is in Voltage Channel | HPFO O VD+ HPFO O FOUT HPF GND (Default) |

| Current<br>Channel | HPF Option is in Current Channel | HPFO O VD+ HPF  FOUT HPFO GND            |

| Disabled           | HPF Option is Disabled           | HPF                                      |

**Table 5. HPF Option Selection**

### 1.2.2.3 Energy Pulse Outputs

The CS5466 provides three output pins for energy registration. The  $\overline{E1}$  and  $\overline{E2}$  pins provide a simple interface from which energy can be registered. These pins are designed to directly connect to a stepper motor or electromechanical counter. The  $\overline{E1}$  and  $\overline{E2}$  outputs are available on header J11, pins 1 and 3, respectively. The pulse rate on the  $\overline{E1}$  and  $\overline{E2}$  pins are in the range of 0 to 4 Hz and all frequency settings are optimized to be used with standard meter constants. The FOUT pin is designated for system calibration, the pulse rate can be selected to reach a frequency of 8000 Hz. The FOUT output is available on header J11, pin 5.

# 1.2.2.4 Selecting Frequency of $\overline{E1}$ and $\overline{E2}$

The pulse rate on  $\overline{E1}$  and  $\overline{E2}$  can be set to one of four frequency ranges. Input pins *FREQ1* and *FREQ0* determine the maximum frequency on  $\overline{E1}$  and  $\overline{E2}$  for sine wave inputs with zero phase shift. The frequency of  $\overline{E2}$  is equal to the frequency of  $\overline{E1}$  with active-low alternating pulses. Table 6 illustrates the options available.

The maximum frequency on the  $\overline{E1}$  and  $\overline{E2}$  output pins is determined by the position of the jumpers on J28, J29 and J30, if the maximum peak differential signal applied to both channels is a sine wave with zero phase shift.

| Maximum Frequency for a Sine Wave |         |                                        | Frequency Select |                           |                           |                                        |

|-----------------------------------|---------|----------------------------------------|------------------|---------------------------|---------------------------|----------------------------------------|

|                                   |         |                                        | FREQ2            | FREQ1                     | FREQ0                     |                                        |

| E1 or E2                          | E1+E2   | FOUT                                   | J28              | J29                       | J30                       |                                        |

| 0.125 Hz                          | 0.25 Hz | 64x( <del>E1+E2</del> )                | 16 Hz            | VD+ O<br>FREQ2 G<br>GND   | VD+ O<br>FREQ1 GND        | VD+ O<br>FREQ0 P<br>GND                |

| 0.25 Hz                           | 0.5 Hz  | 32x( <del>E1+E2</del> )                | 16 Hz            | VD+ O<br>FREQ2 @<br>GND ■ | VD+ O<br>FREQ1 P<br>GND   | VD+ G<br>FREQ0 U<br>GND □              |

| 0.5Hz                             | 1.0 Hz  | 16x( <del>E1+E2</del> )                | 16 Hz            | VD+ O<br>FREQ2 G<br>GND   | VD+ ☐<br>FREQ1 ☐<br>GND ☐ | VD+ O<br>FREQ0 O<br>GND                |

| 1.0 Hz                            | 2.0 Hz  | 2048x( <del>E1</del> + <del>E2</del> ) | 4,096 Hz         | VD+ O FREQ2 GND (Default) | VD+ FREQ1 GND (Default)   | VD+ ☐<br>FREQ0 ☐<br>GND ☐<br>(Default) |

| 0.125 Hz                          | 0.25 Hz | 128x( <del>E1</del> + <del>E2</del> )  | 32 Hz            | VD+ G<br>FREQ2 GND □      | VD+ O<br>FREQ1 G          | VD+ O<br>FREQ0 GND                     |

| 0.25 Hz                           | 0.5 Hz  | 64x( <del>E1</del> + <del>E2</del> )   | 32 Hz            | VD+ G<br>FREQ2 GND □      | VD+ O<br>FREQ1 GND        | VD+ PFREQ0 ■ GND □                     |

| 0.5 Hz                            | 1.0 Hz  | 32x( <del>E1+E2</del> ) 32 Hz          |                  | VD+ G<br>FREQ2 GND □      | VD+ ☐<br>FREQ1 ☐<br>GND ☐ | VD+ O<br>FREQ0 O<br>GND                |

| 1.0 Hz                            | 2.0 Hz  | 16x( <del>E1</del> + <del>E2</del> )   | 32 Hz            | VD+ G<br>FREQ2 G          | VD+ ☐<br>FREQ1 ☐<br>GND ☐ | VD+ <b>1</b> FREQ0 <b>3</b> GND □      |

**Table 6. Energy Output Frequency**

# 1.2.3 Power Supply Section

Table 7 illustrates the power supply connections to the evaluation board. The +5 binding post (J3) supplies the positive analog supply (VA+) for the CS5466 and the +2.5 V reference. The  $VD+\_EXT$  binding post (J5) supplies the digital section of the CS5466 (VD+) and level shifters. Jumper J8 allows the VD+ supply to be sourced from the  $VD+\_EXT$  binding post (J5), the +5 V binding post (J3), or the regulated +3.3 V supply derived from the microcontroller. The  $Vu+\_EXT$  (J6) binding post supplies the positive supply for the 8051 processor (8051\_REGIN). Jumper J9 allows the 8051\_REGIN supply to be sourced from either the  $Vu+\_EXT$  binding post (J6), +5 V binding post (J3) or  $VD+\_EXT$  binding post (J5).

| Pov          | wer Supplie   | es         | Power Post Connections |     | VD+    | 8051-REGIN |         |                                              |                                               |                                                            |      |                                            |                                               |    |                                      |                                               |                                        |  |  |    |                                          |                                              |  |  |  |  |  |  |  |  |  |

|--------------|---------------|------------|------------------------|-----|--------|------------|---------|----------------------------------------------|-----------------------------------------------|------------------------------------------------------------|------|--------------------------------------------|-----------------------------------------------|----|--------------------------------------|-----------------------------------------------|----------------------------------------|--|--|----|------------------------------------------|----------------------------------------------|--|--|--|--|--|--|--|--|--|

| Analog (VA+) | Digital (VD+) | 8051 (Vu+) | +5V                    | GND | VD+EXT | VU+EXT     | J8      | J9                                           |                                               |                                                            |      |                                            |                                               |    |                                      |                                               |                                        |  |  |    |                                          |                                              |  |  |  |  |  |  |  |  |  |

|              |               |            |                        |     |        |            |         | NC                                           | VD+_EXT □ O VD+<br>+5                         | Vu+_EXT □ O 8051<br>+5 ● 8051<br>VD+ O O 8051<br>(Default) |      |                                            |                                               |    |                                      |                                               |                                        |  |  |    |                                          |                                              |  |  |  |  |  |  |  |  |  |

|              |               |            |                        |     |        | NC         | +5      | VD+_EXT□ O VD+<br>+5                         | Vu+_EXT = 8051<br>+5 O O 8051<br>VD+ O O 8051 |                                                            |      |                                            |                                               |    |                                      |                                               |                                        |  |  |    |                                          |                                              |  |  |  |  |  |  |  |  |  |

| +5           | +5 +5         | +5         | +5                     | +5  | +5     | +5         | +5      | +5                                           | +5 +5                                         | +5                                                         | +5   | +5                                         | 0                                             |    | NC                                   | VD+_EXT□ O VD+<br>+5                          | Vu+_EXT □ O 8051<br>+5 O O 8051<br>VD+ |  |  |    |                                          |                                              |  |  |  |  |  |  |  |  |  |

|              |               |            |                        |     |        |            |         |                                              |                                               |                                                            |      |                                            |                                               |    |                                      |                                               |                                        |  |  |    |                                          |                                              |  |  |  |  |  |  |  |  |  |

|              |               |            |                        |     |        |            |         |                                              |                                               |                                                            |      |                                            |                                               |    |                                      |                                               |                                        |  |  | +5 | VD+_EXT  VD+<br>+5 O O VD+<br>+3.3 O VD+ | Vu+_EXT  8051<br>+5 O O 8051<br>VD+ O O 8051 |  |  |  |  |  |  |  |  |  |

|              |               |            |                        |     |        |            |         |                                              |                                               | NC                                                         | J    | VD+_EXT  VD+<br>+5 O O VD+<br>+3.3 O O VD+ | Vu+_EXT □ O 8051<br>+5 O O 8051<br>VD+ ● 8051 |    |                                      |                                               |                                        |  |  |    |                                          |                                              |  |  |  |  |  |  |  |  |  |

|              | 12 2 15       |            |                        |     |        | NC         | NC      | VD+_EXT□ O VD+<br>+5 O O VD+<br>+3.3 • VD+   | Vu+_EXT □ O 8051<br>+5  8051<br>VD+ O O 8051  |                                                            |      |                                            |                                               |    |                                      |                                               |                                        |  |  |    |                                          |                                              |  |  |  |  |  |  |  |  |  |

| +5 +3.3      |               | ±3 3 ±5    | +3 3 +5                | +5  | +5     | +5         | +5      | +5                                           | +5                                            | +5 +5                                                      | +5 0 | 5 0                                        |                                               | +5 | VD+_EXT□ O VD+<br>+5 O O VD+<br>+3.3 | Vu+_EXT = 8051<br>+5 O O 8051<br>VD+ O O 8051 |                                        |  |  |    |                                          |                                              |  |  |  |  |  |  |  |  |  |

|              |               |            |                        |     | Ü      | +3.3       | NC      | VD+_EXT  VD+<br>+5 O O VD+<br>+3.3 O VD+     | Vu+_EXT □ O 8051<br>+5  8051<br>VD+ O O 8051  |                                                            |      |                                            |                                               |    |                                      |                                               |                                        |  |  |    |                                          |                                              |  |  |  |  |  |  |  |  |  |

|              |               |            |                        |     | . 0.0  | +5         | VD+_EXT | Vu+_EXT  8051<br>+5 O O 8051<br>VD+ O O 8051 |                                               |                                                            |      |                                            |                                               |    |                                      |                                               |                                        |  |  |    |                                          |                                              |  |  |  |  |  |  |  |  |  |

**Table 7. Power Supply Connections**

#### 2. SOFTWARE

The evaluation board comes with a USB cable to link the evaluation board to the PC. The evaluation software is available for download on the Cirrus Logic web site at <a href="http://www.cirrus.com/industrialsoftware">http://www.cirrus.com/industrialsoftware</a> and is designed to run under Windows<sup>®</sup> 2000 or Windows<sup>®</sup> XP.

#### 2.1 Installation Procedure

The CDB5466U is designed to perform active energy measurement and output energy pulse registration upon powering up. Evaluation software is available to aid in registering energy pulse outputs. To install the software, go to the Cirrus Logic WEB site at <a href="http://www.cirrus.com/industrialsoftware">http://www.cirrus.com/industrialsoftware</a> and refer to application note AN278.

# 2.2 Using the Software

Before launching the evaluation software, check all jumper settings on the CDB5466U evaluation board as described in Section 1, and connect the board to an open USB port on the PC using the provided cable. Once the board is powered on, the software program can be launched.

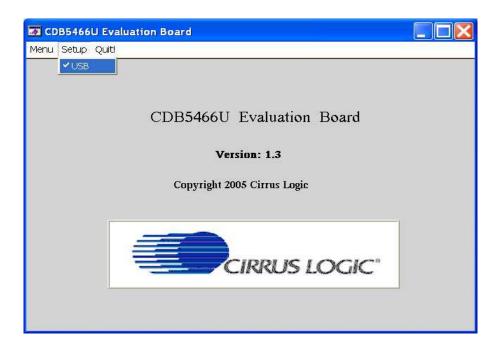

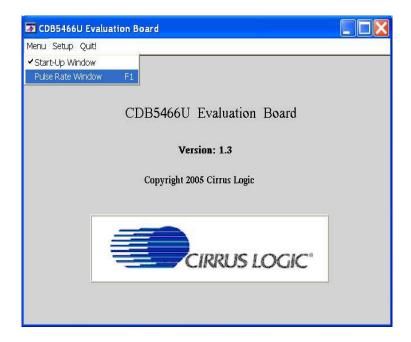

### 2.2.1 Start-Up Window

When the software is launched, the Start-Up window will appear. This window contains information concerning the software's title, revision number, copyright date, etc. See Figure 2.

Figure 2. CDB5466U Start-up Window

At the top of the screen is a menu bar which displays user options. The menu bar has three items; *Menu, Setup and Quit.* Initially *Menu* is disabled to prevent conflicts with other serial communications devices. After establishing communication with the CDB5466U evaluation board the *Menu* item will become available.

### 2.2.1.1 Setup

Setup presents the communication connections available to the CDB5466U Evaluation Board. The CDB5466U has one connection option available, *USB*. As depicted in Figure 2, if the *USB* setup is selected, the evaluation software will poll the CDB5466U, verifying the serial communication link is ready. At this point *USB* is checked indicating that the PC has successfully communicated with the CDB5466U Evaluation Board.

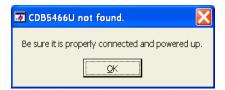

If the evaluation software is unable to establish a communication link with the CDB5466U a message window will appear, indicating that the initial communication has failed. See Figure 3.

Figure 3. Alert Window

Check to verify that the USB cable is connected properly and the power supply is on and connected properly to the CDB5466U.

### 2.2.1.2 Quit

Quit allows the user to exit the evaluation software. Upon selecting Quit, a message window appears and queries if exiting the evaluation software is desired. See Figure 4.

Figure 4. Quit Window

#### 2.2.1.3 Menu

*Menu* allows one selection option, Pulse Rate Window. The Pulse Rate Window provides a means to register the energy-to-pulse outputs. See Figure 5.

Figure 5. CDB5466 Evaluation Board

Upon selecting Pulse Rate Window, the CS5466 Pulse Rate Output Window will appear.

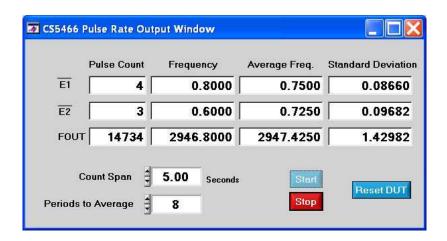

## 2.2.2 CS5466 Pulse Rate Output Window

The Pulse Rate Output Window provides a means to access the  $\overline{E1}$ ,  $\overline{E2}$  and FOUT pin of the CS5466. See Figure 6.

Figure 6. CDB5466U Pulse Rate Output Window

In the CS5466 Pulse Rate Output Window, the *Pulse Count*, *Frequency*, *Average Freq* and *Standard Deviation* are displayed for the three energy-to-pulse outputs.

**Count Span:** The Count Span entry allows for a time period to be specified for counting the energy pulses output by the CS5466. The Count Span is a decimal number having a range of 0.18 < Count Span < 167,772, with units of seconds.

**Periods to Average:** The Periods to Average entry allows an average to be performed on the pulses counted during the specified Count Span. The Periods to Average is an integer with a range of 1 < Periods to Average < 10,000.

**Reset DUT:** When this button is selected, the evaluation software will request the microcontroller to hardware reset the CS5466. The CS5466 will perform a reset as discussed in the CS5466 data sheet.

**Start/Stop:** Initially the *Stop* button is hidden. When the *Start* button is selected, the evaluation software will instruct the microcontroller to start counting the energy-to-pulse outputs from the CS5466. At this time the *Start* button is disabled and the *Stop* button will appear. The evaluation software will then collect the *Pulse Count* over a duration of time specified (in seconds) by the *Count Span*. The counted pulses will then be averaged over the specified *Periods to Average* entry. The *Pulse Count* and calculated *Frequency, Average Freq* and *Standard Deviation* will be displayed at the end of the cycle.

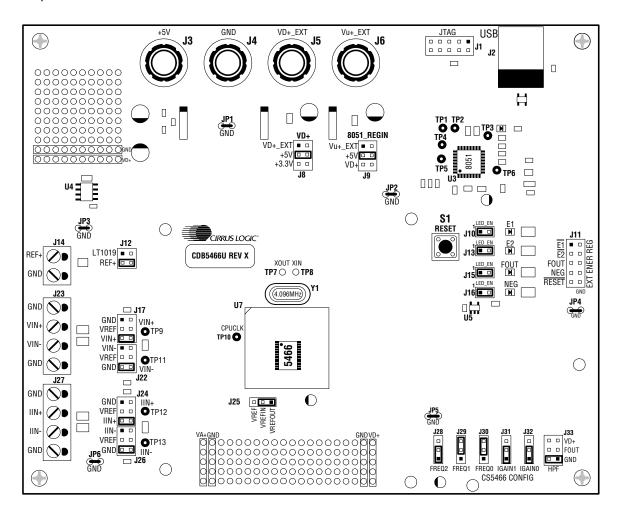

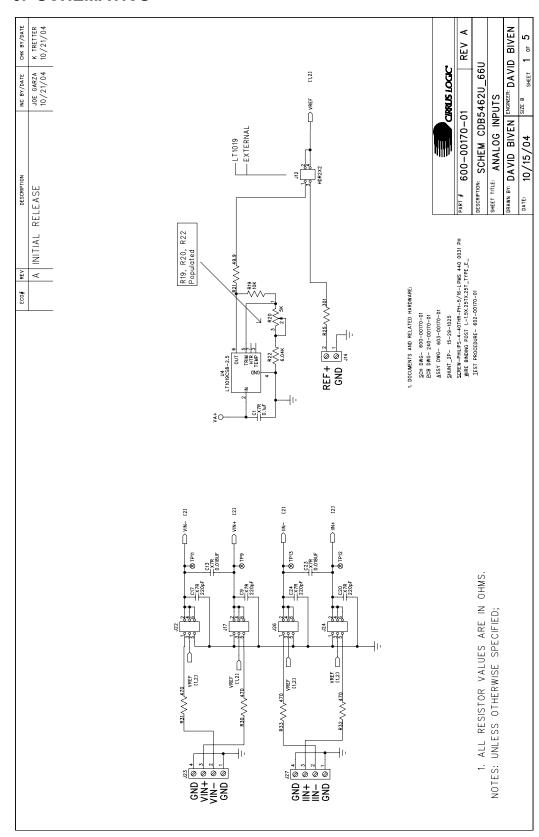

# 3. SCHEMATICS

Figure 7. Analog Inputs

Figure 8. CS546x and Socket

Figure 9. CS5462 and CS5466 Configuration

Figure 10. Microcontroller and USB Interface

Figure 11. Power Supply

# LAYOUT

CIRRUS LOGIC SILKSCREEN TOP

LOP SIDE

# **Contacting Cirrus Logic Support**

For all product questions and inquiries contact a Cirrus Logic Sales Representative. To find one nearest you go to <a href="https://www.cirrus.com">www.cirrus.com</a>

### IMPORTANT NOTICE

Cirrus Logic, Inc. and its subsidiaries ("Cirrus") believe that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (express or implied). Customers are advised to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability. No responsibility is assumed by Cirrus for the use of this information, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no license, express or implied under any patents, mask work rights, copyrights, trademarks, trade secrets or other intellectual property rights. Cirrus owns the copyrights associated with the information contained herein and gives consent for copies to be made of the information only for use within your organization with respect to Cirrus integrated circuits or other products of Cirrus. This consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR USE IN AIRCRAFT SYSTEMS, MILITARY APPLICATIONS, PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, AUTOMOTIVE SAFETY OR SECURITY DEVICES, LIFE SUPPORT PRODUCTS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK AND CIRRUS DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS' FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

Cirrus Logic, Cirrus, and the Cirrus Logic logo designs are trademarks of Cirrus Logic, Inc. All other brand and product names in this document may be trademarks or service marks of their respective owners.

Windows is a registered trademark of Microsoft Corporation.