## Low On-Resistance Wideband/Video Switches

#### **DESCRIPTION**

The DG641, DG642, DG643 are high performance monolithic video switches designed for switching wide bandwidth analog and digital signals. DG641 is a quad SPST, DG642 is a single SPDT, and DG643 is a dual SPDT function. These devices have exceptionally low on-resistances (5  $\Omega$  typ-DG642), low capacitance and high current handling capability.

To achieve TTL compatibility, low channel capacitances and fast switching times, the DG641, DG642, DG643 are built on the Vishay Siliconix proprietary D/CMOS process. Each switch conducts equally well in both directions when on, and blocks up to 14  $\rm V_{p-p}$  when off. An epitaxial layer prevents latchup.

#### **FEATURES**

- Wide bandwidth: 500 MHz

Low crosstalk at 5 MHz: 85 dB

- Low R<sub>DS(on)</sub>: 5 Ω, DG642

- TTL logic compatible

- Fast switching: t<sub>ON</sub> 50 ns

- · Single supply compatibility

- High current: 100 mA, DG642

#### **BENEFITS**

- · High precision

- · Improved frequency response

- · Low insertion loss

- Improved system performance

- · Reduced board space

- · Low power consumption

#### **APPLICATIONS**

- RF and video switching

- RGB switching

- · Video routing

- Cellular communications

- ATE

- Radar/FLIR systems

- Satellite receivers

- · Programmable filters

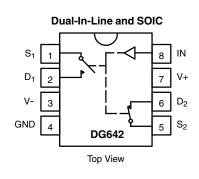

#### **FUNCTIONAL BLOCK DIAGRAM AND PIN CONFIGURATION**

| TRUTH TABLE (DG641) |  |  |  |  |

|---------------------|--|--|--|--|

| Logic Switch        |  |  |  |  |

| 0 OFF               |  |  |  |  |

| 1 ON                |  |  |  |  |

Logic "0" ≤ 0.8 V Logic "1" ≥ 2.4 V

| TRUTH TABLE (DG642) |                 |                 |  |  |

|---------------------|-----------------|-----------------|--|--|

| Logic               | SW <sub>1</sub> | SW <sub>2</sub> |  |  |

| 0                   | OFF             | ON              |  |  |

| 1                   | ON              | OFF             |  |  |

Logic "0" ≤ 0.8 V Logic "1" ≥ 2.4 V

|                 | <b>Dual-In-Line and SOIC</b> |                 |  |  |  |  |

|-----------------|------------------------------|-----------------|--|--|--|--|

|                 |                              |                 |  |  |  |  |

| IN <sub>1</sub> |                              | IN <sub>2</sub> |  |  |  |  |

| $D_1$           | 2 15                         | D <sub>2</sub>  |  |  |  |  |

| GND             | 3 7 14                       | GND             |  |  |  |  |

| S <sub>1</sub>  | 4 1 13                       | S <sub>2</sub>  |  |  |  |  |

| V-              | 5 12                         | V+              |  |  |  |  |

| S <sub>4</sub>  | 6 11                         | S <sub>3</sub>  |  |  |  |  |

| GND             | 7 10                         | GND             |  |  |  |  |

| D <sub>4</sub>  | B DG643 9                    | D <sub>3</sub>  |  |  |  |  |

|                 | Top View                     |                 |  |  |  |  |

| TRUTH TABLE (DG643) |                                                                           |     |  |  |  |  |  |

|---------------------|---------------------------------------------------------------------------|-----|--|--|--|--|--|

| Logic               | Logic SW <sub>1</sub> , SW <sub>2</sub> SW <sub>3</sub> , SW <sub>4</sub> |     |  |  |  |  |  |

| 0                   | OFF                                                                       | ON  |  |  |  |  |  |

| 1                   | ON                                                                        | OFF |  |  |  |  |  |

Logic "0" ≤ 0.8 V Logic "1" ≥ 2.4 V

| ORDERING INFORMATION |                    |             |  |  |

|----------------------|--------------------|-------------|--|--|

| Temp. Range          | Package            | Part Number |  |  |

| DG641                |                    | •           |  |  |

| - 40 °C to 85 °C     | 16-Pin Plastic DIP | DG641DJ     |  |  |

| - 40 °C to 85 °C     | 16-Pin Narrow SOIC | DG641DY     |  |  |

| DG642                |                    | •           |  |  |

| 40.00 + 05.00        | 8-Pin Plastic DIP  | DG642DJ     |  |  |

| - 40 °C to 85 °C     | 8-Pin Narrow SOIC  | DG642DY     |  |  |

| DG643                |                    | •           |  |  |

| - 40 °C to 85 °C     | 16-Pin Plastic DIP | DG643DJ     |  |  |

| - 40 C 10 65 C       | 16-Pin Narrow SOIC | DG643DY     |  |  |

| · · · · · · · · · · · · · · · · · · ·    |                                                | Symbol | Limit                                                            | Unit |  |

|------------------------------------------|------------------------------------------------|--------|------------------------------------------------------------------|------|--|

| V+ to V-                                 |                                                |        | - 0.3 to 21                                                      |      |  |

| V+ to GND                                |                                                |        | - 0.3 to 21                                                      |      |  |

| V- to GND                                |                                                |        | - 19 to + 0.3                                                    |      |  |

| Digital Inputs                           |                                                |        | (V-) - 0.3 V to (V+) + 0.3 V<br>or 20 mA, whichever occurs first | V    |  |

| $V_S, V_D$                               |                                                |        | (V-) - 0.3 V to (V+) + 14 V<br>or 20 mA, whichever occurs first  |      |  |

| Continuous Current (Any terminal excep   | ot S or D)                                     |        | 20                                                               |      |  |

| Continuous Current S or D                | DG641, DG643                                   |        | 75                                                               | mA   |  |

| Continuous Current 3 of D                | DG642                                          |        | 100                                                              |      |  |

| Current, S or D                          | DG641, DG643                                   |        | 200                                                              |      |  |

| (Pulsed at 1 ms, 10 % duty cycle max)    | DG642                                          |        | 300                                                              |      |  |

| Storage Temperature                      |                                                | Ì      | - 65 to 125                                                      | °C   |  |

|                                          | 8-Pin Plastic DIP and Narrow SOIC <sup>c</sup> |        | 300                                                              |      |  |

| Power Dissipation (Package) <sup>b</sup> | 16-Pin Plastic DIP <sup>d</sup>                |        | 470                                                              | mW   |  |

|                                          | 16-Pin Narrow SOICe                            | 1      | 600                                                              |      |  |

#### Notes:

- $a. \ Signals \ on \ S_X, \ D_X, \ or \ IN_X \ exceeding \ V+ \ or \ V- \ will \ be \ clamped \ by \ internal \ diodes. \ Limit \ forward \ diode \ current \ to \ maximum \ current \ ratings.$

- b. All leads welded or soldered to PC board.

- c. Derate 7.6 mW/°C above 75 °C.

- d. Derate 6 mW/°C above 75 °C.

- e. Derate 80 mW/°C above 75 °C.

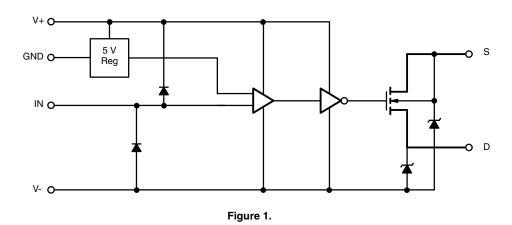

### **SCHEMATIC DIAGRAM** (Typical Channel)

| <b>SPECIFICATIONS</b> (for DG           | 641 and DG64        | 3)                                                                        |                    |               |                       |           |          |

|-----------------------------------------|---------------------|---------------------------------------------------------------------------|--------------------|---------------|-----------------------|-----------|----------|

|                                         |                     | Test Conditions Unless Otherwise Specified V+ = 15 V, V- = - 3 V          |                    | - 4           | Limits<br>40 °C to 85 | °C        |          |

| Parameter                               | Symbol              | $V_{INH} = 15 \text{ V}, V_{INL} = 0.8 \text{ V}^{e}$                     | Temp. <sup>a</sup> | Min.b         | Typ.c                 | Max.b     | Unit     |

| Analog Switch                           |                     |                                                                           |                    |               |                       |           |          |

| Analog Signal Range <sup>d</sup>        | V <sub>ANALOG</sub> | V- = - 5 V, V+ = 12 V                                                     | Full               | - 5           |                       | 8         | V        |

| Analog Signal Harige                    | VANALOG             | V- = GND V, V+ = 12 V                                                     | Full               | 0             |                       | 8         | , v      |

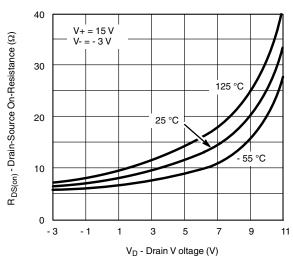

| Drain-Source On-Resistance              | R <sub>DS(on)</sub> | I <sub>S</sub> = - 10 mA, V <sub>D</sub> = 0 V                            | Room<br>Full       |               | 8                     | 15<br>20  | Ω        |

| R <sub>DS(on)</sub> Match               | $\Delta R_{DS(on)}$ | 3 , 5                                                                     | Room               |               | 1                     | 2         | 1        |

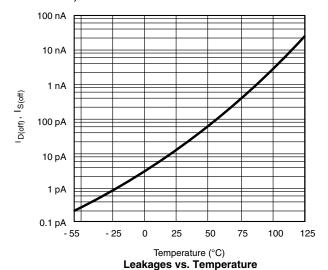

| Source Off Leakage Current              | I <sub>S(off)</sub> | V <sub>S</sub> = 0 V, V <sub>D</sub> = 10 V                               | Room<br>Full       | - 10<br>- 100 | - 0.02                | 10<br>100 |          |

| Drain Off Leakage Current               | I <sub>D(off)</sub> | V <sub>S</sub> = 10 V, V <sub>D</sub> = 0 V                               | Room<br>Full       | - 10<br>- 100 | - 0.02                | 10<br>100 | nA       |

| Channel On Leakage Current              | I <sub>D(on)</sub>  | $V_S = V_D = 0 V$                                                         | Room<br>Full       | - 10<br>- 100 | - 0.1                 | 10<br>100 |          |

| Digital Control                         |                     |                                                                           |                    |               |                       |           |          |

| Input Voltage High                      | V <sub>INH</sub>    |                                                                           | Full               | 2.4           |                       |           | V        |

| Input Voltage Low                       | V <sub>INL</sub>    |                                                                           | Full               |               |                       | 0.8       | <b>'</b> |

| Input Current                           | I <sub>IN</sub>     | V <sub>IN</sub> = GND or V+                                               | Room<br>Full       | - 1<br>- 20   | 0.05                  | 1<br>20   | μΑ       |

| Dynamic Characteristics                 |                     |                                                                           |                    |               |                       |           |          |

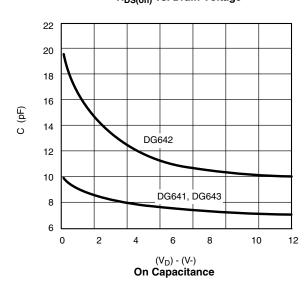

| On State Input Capacitance <sup>d</sup> | C <sub>S(on)</sub>  | $V_S = V_D = 0 V$                                                         | Room               |               | 10                    | 20        |          |

| Off State Output Capacitanced           | C <sub>S(off)</sub> | V <sub>S</sub> = 0 V                                                      | Room               |               | 4                     | 12        | pF       |

| Off State Input Capacitanced            | C <sub>D(off)</sub> | V <sub>D</sub> = 0 V                                                      | Room               |               | 4                     | 12        |          |

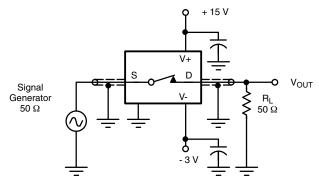

| Bandwidth                               | BW                  | $R_L = 50 \Omega$ , see figure 6                                          | Room               |               | 500                   |           | MH       |

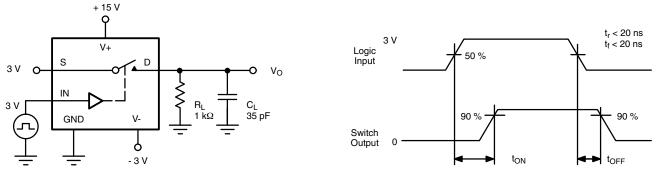

| Turn On Time                            | t <sub>ON</sub>     | $R_L = 1 \text{ k}\Omega, C_L = 35 \text{ pF}$                            | Room<br>Full       |               | 50                    | 70<br>140 | ns       |

| Turn Off Time                           | t <sub>OFF</sub>    | see figure 2                                                              | Room<br>Full       |               | 28                    | 50<br>85  | 113      |

| Charge Injection                        | Q                   | $C_L = 1000 \text{ pF}, V_D = 0 \text{ V}$<br>see figure 3                | Room               |               | - 19                  |           | рС       |

| Off Isolation                           | OIRR                | $R_{IN}$ = 75 $\Omega$ , $R_{L}$ = 75 $\Omega$<br>f = 5 MHz, see figure 4 | Room               |               | - 60                  |           | dB       |

| All Hostie Crosstalk                    | X <sub>TALK</sub>   | $R_{IN}$ = 10 $\Omega$ , $R_L$ = 75 $\Omega$<br>f = 5 MHz, see figure 5   | Room               |               | - 87                  |           | ub       |

| Power Supplies                          |                     |                                                                           |                    |               |                       |           |          |

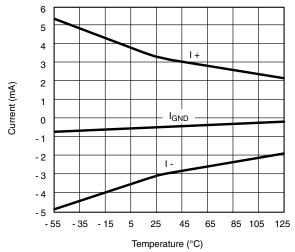

| Positive Supply Current                 | I+                  | V <sub>IN</sub> = 0 V or V <sub>IN</sub> = 5 V                            | Room<br>Full       |               | 3.5                   | 6<br>9    | - mA     |

| Negative Supply Current                 | l-                  | V <sub>IN</sub> = 0 v oi v <sub>IN</sub> = 5 v                            | Room<br>Full       | - 6<br>- 9    | - 3                   |           | IIIA     |

#### Notes:

- a. Room = 25  $^{\circ}$ C, Full = as determined by the operating temperature suffix.

- b. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

- c. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

- d. Guaranteed by design, not subject to production test.

- e.  $V_{IN}$  = input voltage to perform proper function.

|                                           |                       | Test Conditions                                                                          |              |               | Limits            |            |     |

|-------------------------------------------|-----------------------|------------------------------------------------------------------------------------------|--------------|---------------|-------------------|------------|-----|

|                                           |                       | Unless Otherwise Specified                                                               |              | - 4           | 0 °C to 85        | °C         |     |

| Parameter                                 | Symbol                | V+ = 15 V, V- = - 3 V<br>V <sub>INH</sub> = 2.4 V, V <sub>INL</sub> = 0.8 V <sup>e</sup> | Temp.a       | Min.b         | Typ. <sup>c</sup> | Max.b      | Uni |

| Analog Switch                             |                       |                                                                                          |              |               |                   |            |     |

| Analog Signal Range <sup>d</sup>          | V <sub>ANALOG</sub>   | V- = - 5 V, V+ = 12 V                                                                    | Full         | - 5           |                   | 8          | V   |

| Allalog Olgilar Harigo                    | VANALOG               | V- = GND V, V+ = 12 V                                                                    | Full         | 0             |                   | 8          | •   |

| Drain-Source On-Resistance                | R <sub>DS(on)</sub>   | I <sub>S</sub> = - 10 mA, V <sub>D</sub> = 0 V                                           | Room<br>Full |               | 5                 | 8<br>9     | Ω   |

| R <sub>DS(on)</sub> Match                 | $\Delta R_{DS(on)}$   |                                                                                          | Room         |               | 0.5               | 1          |     |

| Source Off Leakage Current                | I <sub>S(off)</sub>   | V <sub>S</sub> = 0 V, V <sub>D</sub> = 10 V                                              | Room<br>Full | - 10<br>- 200 | - 0.04            | 10<br>200  |     |

| Drain Off Leakage Current                 | I <sub>D(off)</sub>   | V <sub>S</sub> = 10 V, V <sub>D</sub> = 0 V                                              | Room<br>Full | - 10<br>- 200 | - 0.04            | 10<br>200  | nA  |

| Channel On Leakage Current                | I <sub>D(on)</sub>    | $V_S = V_D = 0 V$                                                                        | Room<br>Full | - 10<br>- 200 | - 0.2             | 10<br>200  |     |

| Digital Control                           |                       |                                                                                          |              |               |                   |            |     |

| Input Voltage High                        | V <sub>INH</sub>      |                                                                                          | Full         | 2.4           |                   |            | V   |

| Input Voltage Low                         | V <sub>INL</sub>      |                                                                                          | Full         |               |                   | 8.0        | ľ   |

| Input Current                             | I <sub>IN</sub>       | V <sub>IN</sub> = GND or V+                                                              | Room<br>Full | - 1<br>- 20   | 0.05              | 1<br>20    | μΑ  |

| Dynamic Characteristics                   |                       |                                                                                          |              |               |                   |            |     |

| On State Input Capacitance <sup>d</sup>   | C <sub>S(on)</sub>    | $V_S = V_D = 0 V$                                                                        | Room         |               | 19                | 40         |     |

| Off State Input Capacitance <sup>d</sup>  | C <sub>S(off)</sub>   | V <sub>D</sub> = 0 V                                                                     | Room         |               | 8                 | 20         | рF  |

| Off State Output Capacitance <sup>d</sup> | C <sub>D(off)</sub>   | V <sub>S</sub> = 0 V                                                                     | Room         |               | 8                 | 20         |     |

| Bandwidth                                 | BW                    | $R_L = 50 \Omega$ , see figure 6                                                         | Room         |               | 500               |            | MH  |

| Turn On Time                              | t <sub>ON</sub>       | $R_L = 1 \text{ k}\Omega, C_L = 35 \text{ pF}$                                           | Room<br>Full |               | 60                | 100<br>160 | ns  |

| Turn Off Time                             | t <sub>OFF</sub>      | see figure 2                                                                             | Room<br>Full |               | 40                | 60<br>100  | 110 |

| Charge Injection                          | Q                     | $C_L = 1000 \text{ pF}, V_D = 0 \text{ V}$<br>see figure 3                               | Room         |               | - 40              |            | рC  |

| Off Isolation                             |                       | $R_{IN}$ = 75 $\Omega$ , $R_{L}$ = 75 $\Omega$<br>f = 5 MHz, see figure 4                | Room         |               | - 63              |            | dE  |

| All Hostie Crosstalk                      | X <sub>TALK(AH)</sub> | $R_{IN} = 10 \Omega$ , $R_{L} = 75 \Omega$<br>f = 5 MHz, see figure 5                    | Room         |               | - 85              |            | uL. |

| Power Supplies                            |                       |                                                                                          |              |               |                   |            |     |

| Positive Supply Current                   | l+                    | V <sub>IN</sub> = 0 V or V <sub>IN</sub> = 5 V                                           | Room<br>Full |               | 3.5               | 6<br>9     | m/  |

| Negative Supply Current                   | I-                    | IN - O V OI VIN - O V                                                                    | Room<br>Full | - 6<br>- 9    | - 3               |            | ''' |

#### Notes:

- a. Room = 25  $^{\circ}$ C, Full = as determined by the operating temperature suffix.

- b. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

- c. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

- d. Guaranteed by design, not subject to production test.

- e.  $V_{IN}$  = input voltage to perform proper function.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

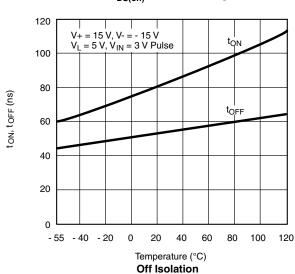

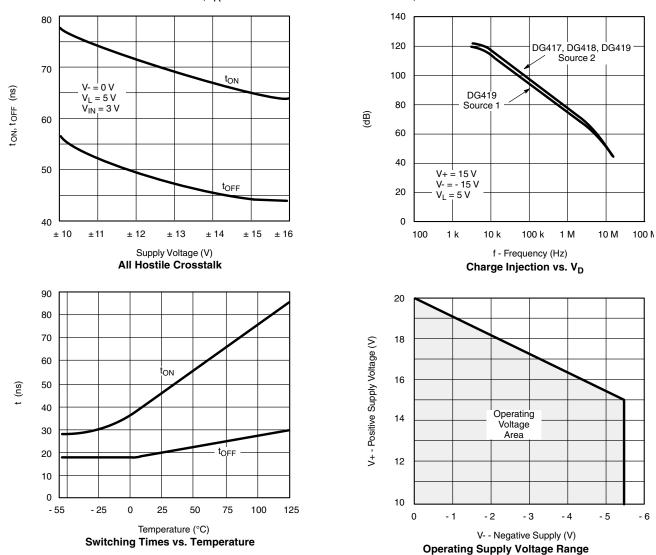

## **TYPICAL CHARACTERISTICS** ( $T_A = 25$ °C, unless otherwise noted)

**Supply Current vs. Temperature**

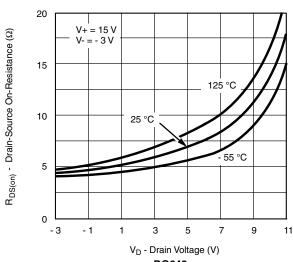

DG641, DG643 R<sub>DS(on)</sub> vs. Drain Voltage

DG642 R<sub>DS(on)</sub> vs. Drain Voltage

# **TYPICAL CHARACTERISTICS** ( $T_A = 25$ °C, unless otherwise noted)

#### **TEST CIRCUITS**

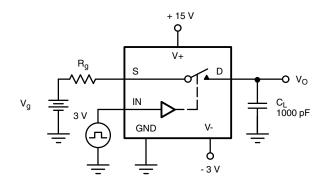

Figure 2. Switching Time

#### **TEST CIRCUITS**

$\Delta V_O$  = measured voltage error due to charge injection The charge injection in coulombs is Q = C\_L x  $\Delta V_O$

Figure 3. Charge Injection

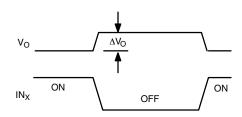

Figure 4. Off Isolation

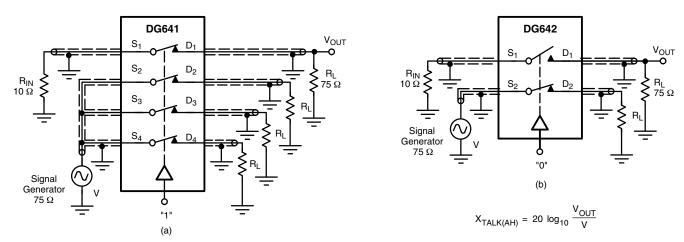

Figure 5. All Hostile Crosstalk - X<sub>TALK(AH)</sub>

#### **TEST CIRCUITS**

Figure 6. Bandwidth

#### **APPLICATIONS**

#### **Device Description**

The DG641, DG642, DG643 switches offer true bidirectional switching of high frequency analog or digital signals with minimum signal crosstalk, low insertion loss, and negligible non-linearity distortion and group delay.

Built on the Siliconix D/CMOS process, these switches provide excellent off-isolation with a bandwidth of around 500 MHz. The silicon-gate D/CMOS processing also yields fast switching speeds.

An on-chip regulator circuit maintains TTL input compatibility over the whole operating supply voltage range shown, easing control logic interfacing.

Circuit layout is facilitated by the interchangeability of source and drain terminals.

#### **Frequency Response**

A single switch on-channel exhibits both resistance  $[R_{DS(on)}]$  and capacitance  $[C_{S(on)}]$ . This RC combination has an attenuation effect on the analog signal - which is frequency dependent (like an RC low-pass filter). The - 3 dB bandwidth of the DG641, DG642, DG643 is typically 500 MHz (into 50  $\Omega$ ).

#### **Power Supplies**

Power supply flexibility is a useful feature of the DG641, DG642, DG643 series. It can be operated from a single positive supply (V+) if required (V- connected to ground). Note that the analog signal must not exceed V- by more than - 0.3 V to prevent forward biasing the substrate p-n junction. The use of a V- supply has a number of advantages:

1. It allows flexibility in analog signal handling, i.e., with  $V-=-5\ V$  and  $V+=12\ V$ ; up to  $\pm\ 5\ V$  ac signals can be controlled.

- 2. The value of on capacitance  $[C_{S(on)}]$  may be reduced. A property known as 'the body-effect' on the DMOS switch devices causes various parametric effects to occur. One of these effects is the reduction in  $C_{S(on)}$  for an increasing V body-source. Note however that to increase V- normally requires V+ to be reduced (since V+ to V- = 21 V max.). A reduction in V+ causes an increase in  $r_{DS(on)}$ , hence a compromise has to be achieved. It is also useful to note that tests indicate that optimum video linearity performance (e.g., differential phase and gain) occurs when V- is around 3 V.

- V- eliminates the need to bias the analog signal using potential dividers and large coupling capacitors.

#### **Decoupling**

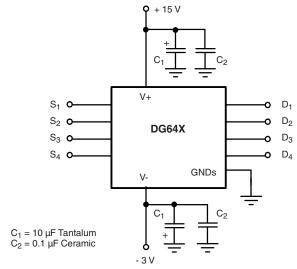

It is an established rf design practice to incorporate sufficient bypass capacitors in the circuit to decouple the power supplies to all active devices in the circuit. The dynamic performance of the DG641, DG642, DG643 series is adversely affected by poor decoupling of power supply pins. Also, of even more significance, since the substrate of the device is connected to the negative supply, adequate decoupling of this pin is essential. Suitable decoupling capacitors are 1- to 10  $\mu F$  tantalum bead, plus 10- to 100-nF ceramic or polyester.

#### Rules:

- Decoupling capacitors should be incorporated on all power supply pins (V+, V-). (see figure 7).

- 2. They should be mounted as close as possible to the device pins.

- Capacitors should be of a suitable type with good high frequency characteristics - tantalum bead and/or ceramic disc types are adequate.

#### **APPLICATIONS**

Figure 7. Supply Decoupling

#### **Board Layout**

PCB layout rules for good high frequency performance must also be observed to achieve the performance boasted by these analog switches. Some tips for minimizing stray effects are:

- Use extensive ground planes on double sided PCB, separating adjacent signal paths. Multilayer PCB is even better.

- 2. Keep signal paths as short as practically possible, with all channel paths of near equal length.

- Careful arrangement of ground connections is also very important. Star connected system grounds eliminate signal current, flowing through ground path parasitic resistance, from coupling between channels.

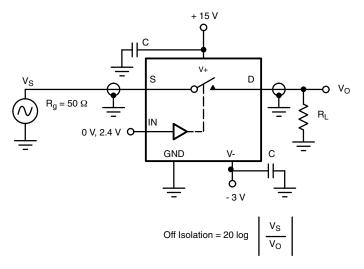

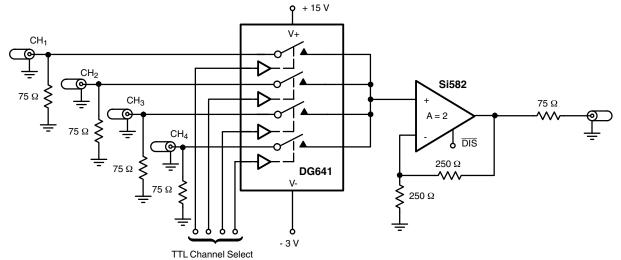

Figure 8 shows a 4-channel video multiplexer using a DG641.

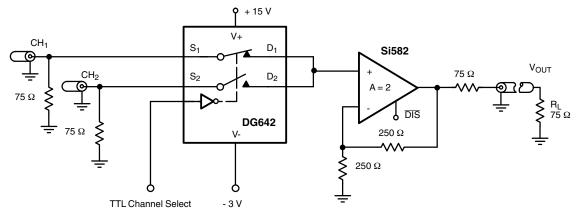

In Figure 9, two coax cables terminated on 75  $\Omega$  bring two video signals to the DG642 switch. The two drains tied together lower the on-state capacitance. An Si582 video amplifier drives a double terminated 75  $\Omega$  cable. The double terminated coax cable eliminates line reflections.

Figure 8. 4 by 1 Video Multiplexing Using the DG641

#### **APPLICATIONS**

Figure 9. 2-Channel Video Selector Using the DG642

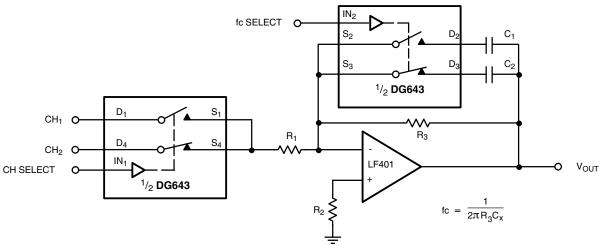

Figure 10. Active Low Pass Filter with Selectable Inputs and Break Frequencies

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see <a href="https://www.vishay.com/ppg?70058">www.vishay.com/ppg?70058</a>.

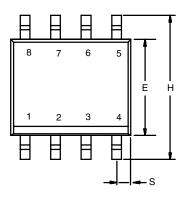

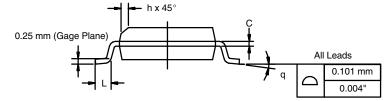

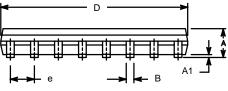

SOIC (NARROW): 8-LEAD JEDEC Part Number: MS-012

|                | MILLIM                         | MILLIMETERS INCH |        | HES   |  |  |

|----------------|--------------------------------|------------------|--------|-------|--|--|

| DIM            | Min                            | Max              | Min    | Max   |  |  |

| Α              | 1.35                           | 1.75             | 0.053  | 0.069 |  |  |

| A <sub>1</sub> | 0.10                           | 0.20             | 0.004  | 0.008 |  |  |

| В              | 0.35                           | 0.51             | 0.014  | 0.020 |  |  |

| С              | 0.19                           | 0.25             | 0.0075 | 0.010 |  |  |

| D              | 4.80                           | 5.00             | 0.189  | 0.196 |  |  |

| E              | 3.80                           | 4.00             | 0.150  | 0.157 |  |  |

| е              | 1.27 BSC                       |                  | 0.050  | ) BSC |  |  |

| Н              | 5.80                           | 6.20             | 0.228  | 0.244 |  |  |

| h              | 0.25                           | 0.50             | 0.010  | 0.020 |  |  |

| L              | 0.50                           | 0.93             | 0.020  | 0.037 |  |  |

| q              | 0°                             | 8°               | 0°     | 8°    |  |  |

| S              | 0.44                           | 0.64             | 0.018  | 0.026 |  |  |

| ECN: C-0652    | ECN: C-06527-Rev. I. 11-Sep-06 |                  |        |       |  |  |

DWG: 5498

Document Number: 71192 www.vishay.com 11-Sep-06

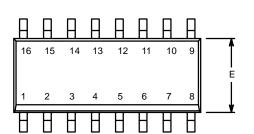

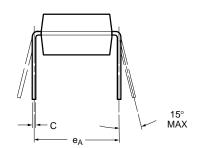

SOIC (NARROW): 16-LEAD JEDEC Part Number: MS-012

|                | MILLIN     | IETERS    | INC   | HES   |

|----------------|------------|-----------|-------|-------|

| Dim            | Min        | Max       | Min   | Max   |

| Α              | 1.35       | 1.75      | 0.053 | 0.069 |

| A <sub>1</sub> | 0.10       | 0.20      | 0.004 | 0.008 |

| В              | 0.38       | 0.51      | 0.015 | 0.020 |

| С              | 0.18       | 0.23      | 0.007 | 0.009 |

| D              | 9.80       | 10.00     | 0.385 | 0.393 |

| E              | 3.80       | 4.00      | 0.149 | 0.157 |

| е              | 1.27       | BSC       | 0.050 | BSC   |

| Н              | 5.80       | 6.20      | 0.228 | 0.244 |

| L              | 0.50       | 0.93      | 0.020 | 0.037 |

| 0              | 0°         | 8°        | 0°    | 8°    |

| ECNI- C O      | 2046 Day F | 00 1.1.04 |       |       |

ECN: S-03946-Rev. F, 09-Jul-01

DWG: 5300

www.vishay.com 02-Jul-01

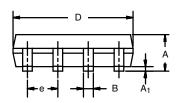

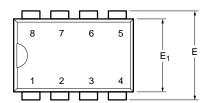

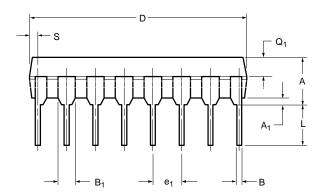

**PDIP: 8-LEAD**

|                                | MILLIM | IETERS | INC   | HES   |  |

|--------------------------------|--------|--------|-------|-------|--|

| Dim                            | Min    | Max    | Min   | Max   |  |

| Α                              | 3.81   | 5.08   | 0.150 | 0.200 |  |

| A <sub>1</sub>                 | 0.38   | 1.27   | 0.015 | 0.050 |  |

| В                              | 0.38   | 0.51   | 0.015 | 0.020 |  |

| B <sub>1</sub>                 | 0.89   | 1.65   | 0.035 | 0.065 |  |

| С                              | 0.20   | 0.30   | 0.008 | 0.012 |  |

| D                              | 9.02   | 10.92  | 0.355 | 0.430 |  |

| E                              | 7.62   | 8.26   | 0.300 | 0.325 |  |

| E <sub>1</sub>                 | 5.59   | 7.11   | 0.220 | 0.280 |  |

| e <sub>1</sub>                 | 2.29   | 2.79   | 0.090 | 0.110 |  |

| e <sub>A</sub>                 | 7.37   | 7.87   | 0.290 | 0.310 |  |

| L                              | 2.79   | 3.81   | 0.110 | 0.150 |  |

| $Q_1$                          | 1.27   | 2.03   | 0.050 | 0.080 |  |

| S                              | 0.76   | 1.65   | 0.030 | 0.065 |  |

| ECN: S-03946—Rev. E, 09-Jul-01 |        |        |       |       |  |

DWG: 5478

15° MAX

NOTE: End leads may be half leads.

Document Number: 71259 www.vishay.com 05-Jul-01

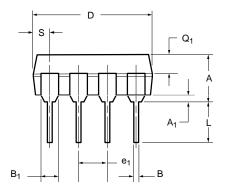

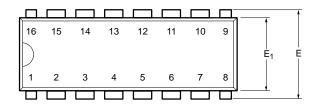

PDIP: 16-LEAD

|                                | MILLIN | IETERS | INC   | HES   |  |

|--------------------------------|--------|--------|-------|-------|--|

| Dim                            | Min    | Max    | Min   | Max   |  |

| Α                              | 3.81   | 5.08   | 0.150 | 0.200 |  |

| A <sub>1</sub>                 | 0.38   | 1.27   | 0.015 | 0.050 |  |

| В                              | 0.38   | 0.51   | 0.015 | 0.020 |  |

| B <sub>1</sub>                 | 0.89   | 1.65   | 0.035 | 0.065 |  |

| С                              | 0.20   | 0.30   | 0.008 | 0.012 |  |

| D                              | 18.93  | 21.33  | 0.745 | 0.840 |  |

| Е                              | 7.62   | 8.26   | 0.300 | 0.325 |  |

| E <sub>1</sub>                 | 5.59   | 7.11   | 0.220 | 0.280 |  |

| e <sub>1</sub>                 | 2.29   | 2.79   | 0.090 | 0.110 |  |

| e <sub>A</sub>                 | 7.37   | 7.87   | 0.290 | 0.310 |  |

| L                              | 2.79   | 3.81   | 0.110 | 0.150 |  |

| $Q_1$                          | 1.27   | 2.03   | 0.050 | 0.080 |  |

| S                              | 0.38   | 1.52   | .015  | 0.060 |  |

| ECN: S-03946—Rev. D, 09-Jul-01 |        |        |       |       |  |

Document Number: 71261 www.vishay.com 06-Jul-01 1

# APPLICATION NOTE

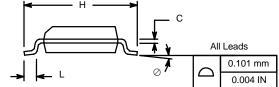

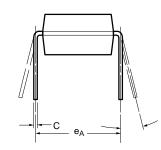

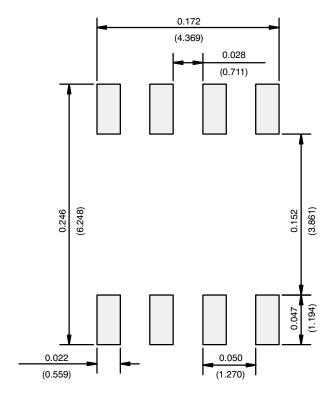

#### **RECOMMENDED MINIMUM PADS FOR SO-8**

Recommended Minimum Pads Dimensions in Inches/(mm)

Return to Index

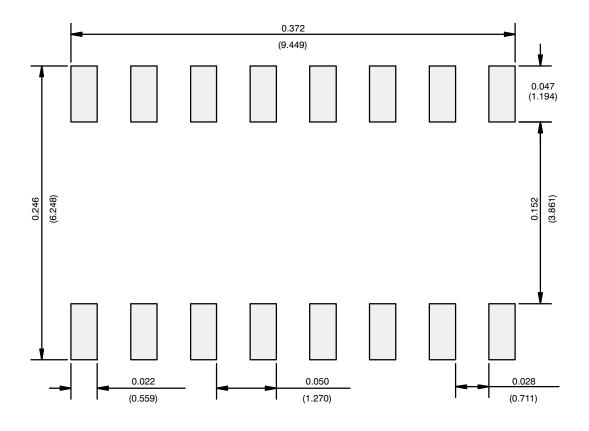

#### **RECOMMENDED MINIMUM PADS FOR SO-16**

Recommended Minimum Pads Dimensions in Inches/(mm)

Return to Index

Ш

## **Legal Disclaimer Notice**

Vishay

## **Disclaimer**

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.