Data sheet: technical data

### 1 General description

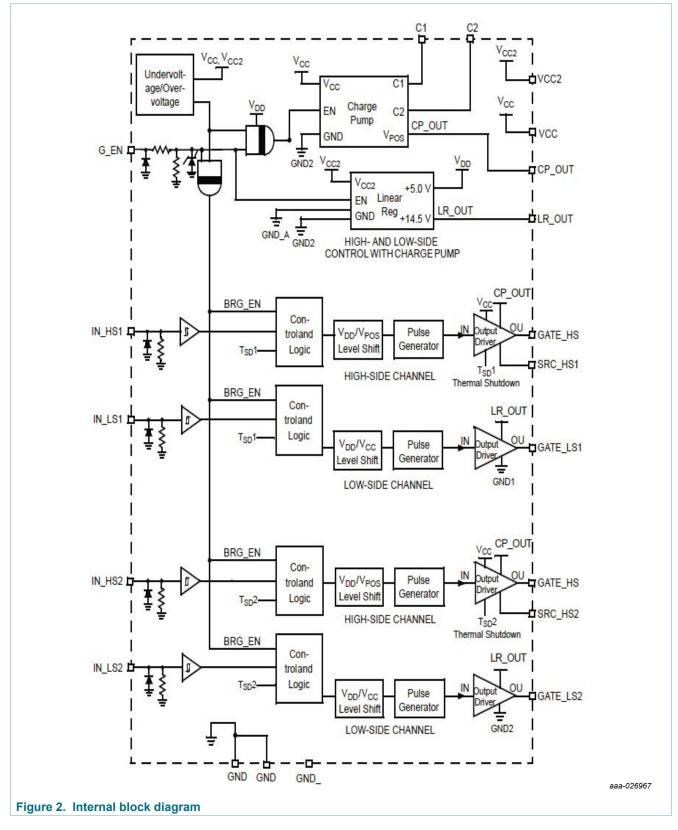

The 33883 is an H-bridge gate driver (also known as a full-bridge pre-driver) IC with integrated charge pump and independent high and low side gate driver channels. The gate driver channels are independently controlled by four separate input pins, thus allowing the device to be optionally configured as two independent high side gate drivers and two independent low side gate drivers. The low side channels are referenced to ground. The high side channels are floating.

The gate driver outputs can source and sink up to 1.0 A peak current pulses, permitting large gate-charge MOSFETs to be driven and/or high pulse- width modulation (PWM) frequencies to be utilized. A linear regulator is incorporated, providing a 15 V typical gate supply to the low side gate drivers. The 33883 is AEC-Q100 qualified.

This device powered by SMARTMOS technology.

#### 2 Features

- $V_{CC}$  operating voltage range from 5.5 V up to 55 V  $\,$

- V<sub>CC2</sub> operating voltage range from 5.5 V up to 28 V

- CMOS / LSTTL compatible I / O

- 1.0 A peak gate driver current

- Built-in high side charge pump

- Under-voltage lockout (UVLO)

- Over-voltage lockout (OVLO)

- Global enable with <10 μA Sleep mode

- Supports PWM up to 100 kHz

- Qualified in compliance with AEC-Q100

**H-Bridge Gate Driver IC**

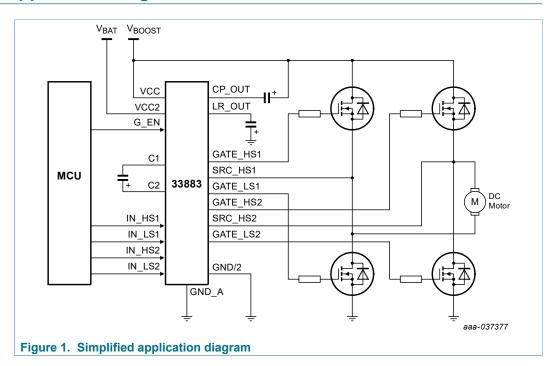

# 3 Simplified application diagram

# 4 Applications

- · Automotive: 12 V to high-voltage battery packs

- · E-bikes, e-scooters

- Energy Storage Systems (ESS)

- Uninterruptible Power Supply (UPS)

- · Battery junction box

# 5 Ordering information

Table 1. Orderable part variations

| Part number [1] | VDD         | Temperature (T <sub>J</sub> ) | Package                        |

|-----------------|-------------|-------------------------------|--------------------------------|

| MC33883HEG      | 5.5 to 55 V | -40 °C to 125 °C              | 20-pin 20 SOICW, 1.27 mm pitch |

[1] To order parts in tape and reel, add the R2 suffix to the part number.

**H-Bridge Gate Driver IC**

# 6 Internal block diagram

**H-Bridge Gate Driver IC**

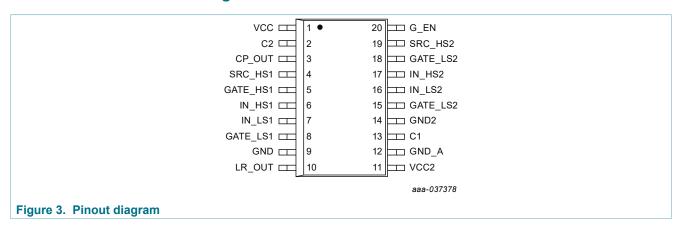

# 7 Pinning information

### 7.1 Pinout diagram

### 7.2 Pin definitions

For a detailed description of each pin, see Section 9 "Functional description".

Table 2. Pin definitions

| Pin<br>number | Pin name  | Pin function              | Definition                                                                        |

|---------------|-----------|---------------------------|-----------------------------------------------------------------------------------|

| 1             | VCC       | Supply Voltage 1          | Device power supply 1.                                                            |

| 2             | C2        | Charge Pump Capacitor     | External capacitor for internal charge pump.                                      |

| 3             | CP_OUT    | Charge Pump Out           | External reservoir capacitor for internal charge pump.                            |

| 4             | SRC_HS1   | Source 1 Output High Side | Source of high-side 1 MOSFET                                                      |

| 5             | GATE_HS 1 | Gate 1 Output High Side   | Gate of high-side 1 MOSFET.                                                       |

| 6             | IN_HS1    | Input High Side 1         | Logicinput control of high-side 1 gate (i.e., IN_HS1 logic HIGH = GATE_HS1 HIGH). |

| 7             | IN_LS1    | Input Low Side 1          | Logic input control of low-side 1 gate (i.e., IN_LS1 logic HIGH = GATE_LS1 HIGH). |

| 8             | GATE_LS1  | Gate 1 Output Low Side    | Gate of low-side 1 MOSFET.                                                        |

| 9             | GND1      | Ground 1                  | Device ground 1.                                                                  |

| 10            | LR_OUT    | Linear Regulator Output   | Output of internal linear regulator.                                              |

| 11            | VCC2      | Supply Voltage 2          | Device power supply 2.                                                            |

| 12            | GND_A     | Analog Ground             | Device analog ground.                                                             |

| 13            | C1        | Charge Pump Capacitor     | External capacitor for internal charge pump.                                      |

| 14            | GND2      | Ground 2                  | Device ground 2.                                                                  |

| 15            | GATE_LS2  | Gate 2 Output Low Side    | Gate of low-side 2 MOSFET.                                                        |

| 16            | IN_LS2    | Input Low Side 2          | Logic input control of low-side 2 gate (i.e., IN_LS2 logic HIGH = GATE_LS2 HIGH). |

| 17            | IN_HS2    | Input High Side 2         | Logicinput control of high-side 2 gate (i.e., IN_HS2 logic HIGH = GATE_HS2 HIGH). |

| 18            | GATE_HS 2 | Gate 2 Output High Side   | Gate of high-side 2 MOSFET.                                                       |

| 19            | SRC_HS2   | Source 2 Output High Side | Source of high-side 2 MOSFET.                                                     |

MC33883

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved.

**H-Bridge Gate Driver IC**

| Pin<br>number | Pin name | Pin function  | Definition                                                                                                  |

|---------------|----------|---------------|-------------------------------------------------------------------------------------------------------------|

| 20            | G_EN     | Global Enable | Logic input Enable control of device (i.e., G_EN logic HIGH = Full Operation, G_EN logic LOW = Sleep Mode). |

# 8 General product characteristics

### 8.1 Maximum ratings

#### Table 3. Maximum ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings might cause a malfunction or permanent damage to the device.

| Rating                                                                                      | Symbol                                         | Value           | Unit |

|---------------------------------------------------------------------------------------------|------------------------------------------------|-----------------|------|

| Supply Voltage 1                                                                            | V <sub>CC</sub>                                | -0.3 to 65      | V    |

| Supply Voltage 2 (1)                                                                        | V <sub>CC2</sub> [1]                           | -0.3 to 35      | V    |

| Linear Regulator Output Voltage                                                             | V <sub>LR_OUT</sub>                            | -0.3 to 18      | V    |

| High-Side Floating Supply Absolute Voltage                                                  | V <sub>CP_OUT</sub>                            | -0.3 to 65      | V    |

| High-Side Floating Source Voltage                                                           | V <sub>SRC_HS</sub>                            | -2.0 to 65      | V    |

| High-Side Source Current from CP_OUT in Switch ON State                                     | Is                                             | 250             | mA   |

| High-Side Gate Voltage                                                                      | V <sub>GATE_HS</sub>                           | -0.3 to 65      | V    |

| High-Side Gate Source Voltage (2)                                                           | V <sub>GATE_HS</sub> - V <sub>SRC_HS</sub> [2] | -0.3 to 20      | V    |

| High-Side Floating Supply Gate Voltage                                                      | V <sub>CP_OUT</sub> - V <sub>GATE_HS</sub>     | -0.3 to 65      | V    |

| Low-Side Gate Voltage                                                                       | V <sub>GATE_LS</sub>                           | –0.3 to 17      | V    |

| Wake-Up Voltage                                                                             | $V_{G\_EN}$                                    | -0.3 to 35      | V    |

| Logic Input Voltage                                                                         | V <sub>IN</sub>                                | -0.3 to 10      | V    |

| Charge Pump Capacitor Voltage                                                               | V <sub>C1</sub>                                | -0.3 to VLR_OUT | V    |

| Charge Pump Capacitor Voltage                                                               | V <sub>C2</sub>                                | -0.3 to 65      | V    |

| ESD Voltage Human Body Model on All Pins (VCC and VCC2 as Two Power Supplies) Machine Model | V <sub>ESD1</sub>                              | ±1500           | V    |

| Machine Model                                                                               | V <sub>ESD2</sub>                              | ±130            |      |

<sup>[1]</sup>  $V_{CC2}$  can sustain load dump pulse of 40 V, 400 ms, 2.0  $\Omega$ .

#### 8.2 Static electrical characteristics

#### **Table 4. Static electrical characteristics**

Characteristics noted under conditions  $V_{CC}$  = 12 V,  $V_{CC2}$  = 12 V,  $C_{CP}$  = 33 nF,  $G_{LR}$  = 4.5 V unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_{LR}$  = 25°C under nominal conditions unless otherwise noted.

| Symbol           | Parameter                                                    | Min | Тур | Max | Unit |

|------------------|--------------------------------------------------------------|-----|-----|-----|------|

| Operating cond   | itions                                                       |     |     |     |      |

| V <sub>CC</sub>  | Supply Voltage 1 for Output High-Side Driver and Charge Pump | 5.5 | _   | 55  | V    |

| V <sub>CC2</sub> | Supply Voltage 2 for Linear Regulation                       | 5.5 |     | 28  | V    |

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved.

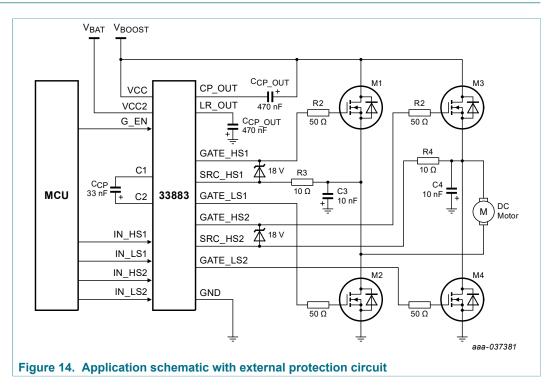

<sup>[2]</sup> In case of high current (SRC\_HS >100 mA) and high voltage (>20 V) between GATE\_HSX and SRC\_HS an external zener of 18 V is needed as shown in Figure 14.

<sup>[3]</sup> ESD1 testing is performed in accordance with the Human Body Model ( $C_{ZAP} = 100 \text{ pF}$ ,  $R_{ZAP} = 1500 \Omega$ ), ESD2 testing is performed in accordance with the Machine Model ( $C_{ZAP} = 200 \text{ pF}$ ,  $R_{ZAP} = 0 \Omega$ ).

# H-Bridge Gate Driver IC

| Symbol                 | Parameter                                                                             | Min                    | Тур | Max                              | Unit |

|------------------------|---------------------------------------------------------------------------------------|------------------------|-----|----------------------------------|------|

| V <sub>CP_OUT</sub>    | High-Side Floating Supply Absolute Voltage                                            | V <sub>CC</sub> + 4    | _   | V <sub>CC</sub> + 11<br>but < 65 | V    |

| Logic                  |                                                                                       |                        |     |                                  |      |

| V <sub>IH</sub>        | Logic 1 Input Voltage (IN_LS and IN_HS)                                               | 2.0                    | _   | 10                               | V    |

| V <sub>IL</sub>        | Logic 0 Input Voltage (IN_LS and IN_HS)                                               | _                      | _   | 0.8                              | V    |

| I <sub>N+</sub>        | Logic 1 Input Current                                                                 |                        |     |                                  | μA   |

|                        | V <sub>IN</sub> = 5.0 V                                                               | 200                    | _   | 1000                             | '    |

| V <sub>G_EN</sub>      | Wake-Up Input Voltage (G_EN)                                                          | 4.5                    | 5.0 | V <sub>CC2</sub>                 | V    |

| I <sub>G_EN</sub>      | Wake-Up Input Current (G_EN)  V <sub>G EN</sub> = 14 V                                | _                      | 200 | 500                              | μA   |

| 1                      | _                                                                                     |                        | 200 | 300                              | μ Λ  |

| I <sub>G_EN2</sub>     | Wake-Up Input Current (G_EN) $V_{G_EN} = 28 \text{ V}$                                | _                      | _   | 1.5                              | mA   |

| Linear regul           | ator                                                                                  |                        |     |                                  | ,    |

| V <sub>LR_OUT</sub>    | Linear regulator                                                                      |                        |     |                                  | V    |

|                        | $V_{LR\ OUT}$ @ $V_{CC2}$ from 15 V to 28 V, $I_{LOAD}$ from 0 mA to 20 mA            | 12.5                   |     | 16.5                             |      |

|                        | $V_{LR\_OUT}$ @ $I_{LOAD}$ = 20 mA                                                    | V <sub>CC2</sub> – 1.5 |     | _                                |      |

|                        | $V_{LR\_OUT}$ @ $I_{LOAD}$ = 20 mA, $V_{CC2}$ = 5.5 V, $V_{CC}$ = 5.5 V               | 4.0                    | _   | _                                |      |

| Charge pum             | р                                                                                     |                        |     |                                  |      |

| V <sub>CP_OUT</sub>    | Charge Pump Output Voltage, Reference to VCC                                          |                        |     |                                  | V    |

| _                      | VCC = 12 V, ILOAD = 0 mA, CCP_OUT = 1.0 $\mu$ F                                       | 7.5                    |     | _                                |      |

|                        | VCC = 12 V, ILOAD = 7.0 mA, CCP_OUT = 1.0 μF                                          | 7.0                    | _   |                                  |      |

|                        | VCC2 = VCC = $5.5 \text{ V}$ , ILOAD = $0 \text{ mA}$ , CCP_OUT = $1.0 \mu\text{F}$   | 2.3                    | _   | _                                |      |

|                        | VCC2 = VCC = $5.5 \text{ V}$ , ILOAD = $7.0 \text{ mA}$ , CCP_OUT = $1.0 \mu\text{F}$ | 1.8                    | _   | _                                |      |

|                        | VCC = 55 V, ILOAD = 0 mA, CCP_OUT = 1.0 $\mu$ F                                       | 7.5                    | _   | _                                |      |

|                        | VCC = 55 V, ILOAD = 7.0 mA, CCP_OUT = 1.0 $\mu$ F                                     | 7.0                    | _   | _                                |      |

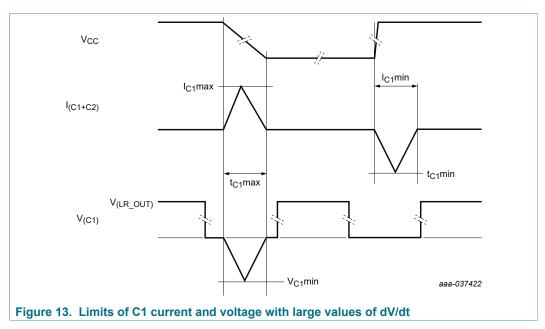

| I <sub>C1</sub>        | Peak Current Through Pin C1 Under Rapidly Changing VCC Voltages (see Figure 13)       | -2.0                   | _   | 2.0                              | Α    |

| V <sub>C1</sub> MIN    | Minimum Peak Voltage at Pin C1 Under Rapidly Changing VCC Voltages (see Figure 13)    | -1.5                   | _   | _                                | V    |

| Supply volta           | nne                                                                                   |                        |     |                                  |      |

| IV <sub>CCSLEEP</sub>  | Quiescent VCC Supply Current                                                          |                        |     |                                  |      |

| CCSLEEP                | $V_{GEN} = 0 \text{ V}$ and $V_{CC} = 55 \text{ V}$                                   | _                      |     | 10                               | μA   |

|                        | $V_{GEN} = 0$ V and $V_{CC} = 12$ V                                                   | _                      | _   | 10                               |      |

| IV <sub>CCOP</sub>     | Operating VCC Supply Current [1]                                                      |                        |     |                                  | mA   |

|                        | $V_{CC} = 55 \text{ V}$ and $V_{CC2} = 28 \text{ V}$                                  |                        | 2.2 | _                                |      |

|                        | $V_{CC} = 12 \text{ V}$ and $V_{CC2} = 12 \text{ V}$                                  | _                      | 0.7 | _                                |      |

| IV <sub>CCLOG</sub>    | Additional Operating VCC Supply Current for Each Logic Input Pin Active               |                        |     |                                  | mA   |

|                        | $V_{CC}$ = 55 V and $V_{CC2}$ = 28 V                                                  | _                      | _   | 5.0                              |      |

| IV <sub>CC2SLEEP</sub> | Quiescent VCC2 Supply Current                                                         |                        |     |                                  | mA   |

| CCZSLEEP               | $V_{GEN} = 0 \text{ V}$ and $V_{CC} = 12 \text{ V}$                                   |                        |     | 5.0                              |      |

|                        | $V_{GEN} = 0$ V and $V_{CC} = 28$ V                                                   | _                      | _   | 5.0                              |      |

| D. /                   | -                                                                                     |                        |     | 3.0                              |      |

| IV <sub>CC2OP</sub>    | Operating VCC2 Supply Current                                                         |                        |     |                                  | mA   |

|                        | $V_{CC} = 55 \text{ V}$ and $V_{CC2} = 28 \text{ V}$                                  | _                      | _   | 12                               |      |

|                        | $V_{CC}$ = 12 V and $V_{CC2}$ = 12 V                                                  | _                      | -   | 9.0                              | 1    |

### **H-Bridge Gate Driver IC**

| Symbol               | Parameter                                                                            |     | Min  | Тур | Max | Unit |

|----------------------|--------------------------------------------------------------------------------------|-----|------|-----|-----|------|

| IV <sub>CC2LOG</sub> | Additional Operating V <sub>CC2</sub> Supply Current for Each Logic Input Pin Active | [2] |      |     |     | mA   |

|                      | $V_{CC}$ = 55 V and $V_{CC2}$ = 28 V                                                 |     |      |     | 5.0 |      |

| UV                   | Undervoltage Shutdown VCC                                                            |     | 4.0  | 5.0 | 5.5 | V    |

| UV2                  | Undervoltage Shutdown VCC2                                                           | [3] | 4.0  | 5.0 | 5.5 | V    |

| OV                   | Overvoltage Shutdown VCC                                                             |     | 57   | 61  | 65  | V    |

| OV2                  | Overvoltage Shutdown VCC2                                                            |     | 29.5 | 31  | 35  | V    |

| Output               |                                                                                      |     |      |     |     |      |

| RDS                  | Output Sink Resistance (Turned Off)                                                  | [3] |      |     |     | Ω    |

|                      | Idischarge LSS = 50 mA, V <sub>SRC_HS</sub> = 0 V                                    |     | _    | _   | 22  |      |

| RDS                  | Output Source Resistance (Turned On)                                                 | [3] |      |     |     | Ω    |

|                      | Icharge HSS = 50 mA, V <sub>CP_OUT</sub> = 20 V                                      |     | _    | _   | 22  |      |

| ICHARGE HSS          | Charge Current of the External High-Side MOSFET Through                              | [4] |      |     |     | mA   |

|                      | GATE_HSn Pin                                                                         |     | _    | 100 | 200 |      |

| VMAX                 | Maximum Voltage (V <sub>GATE_HS</sub> - V <sub>SRC_HS</sub> )                        |     |      |     |     | V    |

|                      | INH = Logic 1, I <sub>S</sub> max = 5.0 mA                                           |     | _    | _   | 18  |      |

Logic input pin inactive (high impedance).

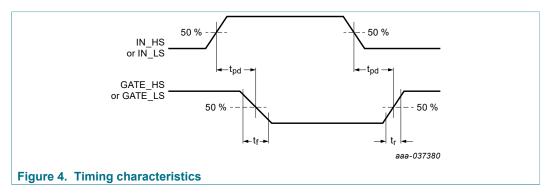

### 8.3 Dynamic electrical characteristics

#### Table 5. Dynamic electrical characteristics

Characteristics noted under conditions 7.0 V £  $V_{SUP} \le 18 \text{ V}$ ,  $-40^{\circ}\text{C} \le TA \le 125^{\circ}\text{C}$ , GND = 0.0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A$  = 25°C under nominal conditions unless otherwise noted.

| Symbol                 | Parameter                                                                                               |         | Min | Тур | Max | Unit |

|------------------------|---------------------------------------------------------------------------------------------------------|---------|-----|-----|-----|------|

| Timing characteristics |                                                                                                         |         |     |     |     |      |

| t <sub>PD</sub>        | Propagation Delay High Side and Low Side CLOAD = 5.0 nF, Between 50% Input to 50% Output (see Figure 4) | [1]     | _   | 200 | 300 | ns   |

| t <sub>R</sub>         | Turn-On Rise Time C <sub>LOAD</sub> = 5.0 nF, 10% to 90%, (see <u>Figure 4</u> )                        | [1] [2] | _   | 80  | 180 | ns   |

| t <sub>F</sub>         | Turn-Off Fall Time<br>C <sub>LOAD</sub> = 5.0 nF, 10% to 90%, (see <u>Figure 4</u> )                    | [1] [2] | _   | 80  | 180 | ns   |

C<sub>LOAD</sub> corresponds to a capacitor between GATE\_HS and SRC\_HS for the high side and between GATE\_LS and ground for low side.

High-frequency PWM-ing (» 20 kHz) of the logic inputs will result in greater power dissipation within the device. Care must be taken to remain within the package power handling rating.

The device may exhibit predictable behavior between 4.0 V and 5.5 V.

<sup>[3]</sup>

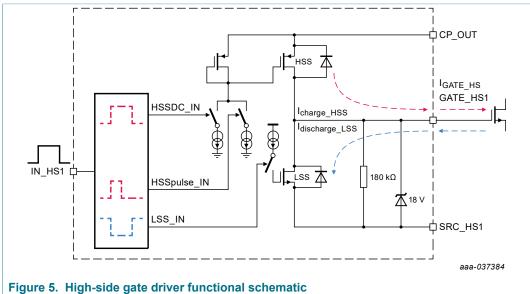

See Figure 5 for a description of charge current.

Rise time is given by time needed to change the gate from 1.0 V to 10 V (vice versa for fall time).

H-Bridge Gate Driver IC

### 8.4 Timing diagram

### 9 Functional description

#### 9.1 Introduction

The 33883 is an H-bridge gate driver (or full-bridge pre-driver) with integrated charge pump and independent high- and low-side driver channels. It has the capability to drive large gate-charge MOSFETs and supports high PWM frequency. In sleep mode its supply current is very low.

### 9.2 Functional pin description

#### 9.2.1 Supply voltage pins (VCC and VCC2)

The VCC and VCC2 pins are the power supply inputs to the device.  $V_{CC}$  is used for the output high-side drivers and the charge pump.  $V_{CC2}$  is used for the linear regulation. They can be connected together or independent with different voltage values. The device can operate with  $V_{CC}$  up to 55 V and  $V_{CC2}$  up to 28 V.

The VCC and VCC2 pins have undervoltage (UV) and overvoltage (OV) shutdown. If one of the supply voltage drops below the undervoltage threshold or rises above the overvoltage threshold, the gate outputs are switched LOW in order to switch off the external MOSFETs. When the supply returns to a level that is above the UV threshold or below the OV threshold, the device resumes normal operation according to the established condition of the input pins.

#### 9.2.2 Input high-side and low-side pins (IN HS1, IN HS2, IN LS1, IN LS2)

The IN\_HSn and IN\_LSn pins are input control pins used to control the gate outputs. These pins are 5.0 V CMOS-compatible inputs with hysteresis. IN\_HSn and IN\_LSn independently control GATE\_HSn and GATE\_LSn, respectively.

During wake-up, the logic is supplied from the G\_EN pin. There is no internal circuit to prevent the external high-side and low-side MOSFETs from conducting at the same time.

### 9.2.3 Source output high-side pins (SRC\_HS1 and SRC\_HS2)

The SRC\_HSn pins are the sources of the external high-side MOSFETs. The external high-side MOSFETs are controlled using the IN\_HSn inputs.

MC33883

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved

H-Bridge Gate Driver IC

# 9.2.4 Gate high-side and low-side pins (GATE\_HS1, GATE\_HS2, GATE\_LS1, GATE\_LS2)

The GATE\_HSn and GATE\_LSn pins are the gates of the external high- and low-side MOSFETs. The external high- and low-side MOSFETs are controlled using the IN\_HSn and IN\_LSn inputs.

#### 9.2.5 Global enable (G EN)

The G\_EN pin is used to place the device in a sleep mode. When the G\_EN pin voltage is a logic LOW state, the device is in sleep mode. The device is enabled and fully operational when the G\_EN pin voltage is logic HIGH, typically 5.0 V.

#### 9.2.6 Charge pump out (CP OUT)

The CP\_OUT pin is used to connect an external reservoir capacitor for the charge pump.

#### 9.2.7 Charge pump capacitor pins (C1 and C2)

The C1 and C2 pins are used to connect an external capacitor for the charge pump.

#### 9.2.8 Linear regulator output (LR\_OUT)

The LR\_OUT pin is the output of the internal regulator. It is used to connect an external capacitor.

#### 9.2.9 Ground pins (GND\_A, GND1, GND2)

These pins are the ground pins of the device. They should be connected together with a very low impedance connection.

### 9.3 Functional truth table

Table 6. Functional truth table

| Conditions                               | G_EN | IN_HSn | IN_LSn | Gate_HSn | Gate_LSn | Comments                                                                                                                                  |

|------------------------------------------|------|--------|--------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Sleep                                    | 0    | х      | х      | 0        | 0        | Device is in Sleep mode. The gates are at low state.                                                                                      |

| Normal                                   | 1    | 1      | 1      | 1        | 1        | Normal mode. The gates are controlled independently.                                                                                      |

| Normal                                   | 1    | 0      | 0      | 0        | 0        | Normal mode. The gates are controlled independently.                                                                                      |

| Undervoltage                             | 1    | х      | Х      | 0        | 0        | The device is currently in fault mode. The gates are at low state. Once the fault is removed, the 33883 recovers its normal mode.         |

| Overvoltage                              | 1    | х      | х      | 0        | 0        | The device is currently in fault mode. The gates are at low state. Once the fault is removed, the 33883 recovers its normal mode.         |

| Overtemperature on High-Side Gate Driver | 1    | 1      | х      | 0        | х        | The device is currently in fault mode. The high-side gate is at low state. Once the fault is removed, the 33883 recovers its normal mode. |

| Overtemperature on Low-Side Gate Driver  | 1    | х      | 1      | х        | 0        | The device is currently in fault mode. The low-side gate is at low state. Once the fault is removed, the 33883 recovers its normal mode.  |

MC33883

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved.

H-Bridge Gate Driver IC

### 9.4 Functional device operation

#### Driver characteristics

Figure 5 represents the external circuit of the high-side gate driver. In the schematic, HSS represents the switch that is used to charge the external high-side MOSFET through the GATE\_HS pin. LSS represents the switch that is used to discharge the external high-side MOSFET through the GATE  $\,$  HS pin. A 180 K $\Omega$  internal typical passive discharge resistance and a 18 V typical protection zener are in parallel with LSS. The same schematic can be applied to the external low-side MOSFET driver simply by replacing pin CP OUT with pin LR OUT, pin GATE HS with pin GATE LS, and pin SRC HS with GND.

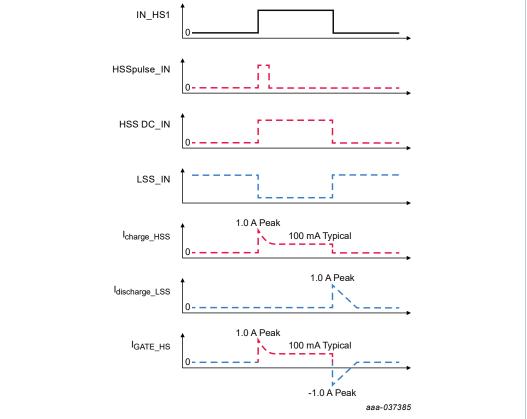

The different voltages and current of the high-side gate driver are illustrated in Figure 6. The output driver sources a peak current of up to 1.0 A for 200 ns to turn on the gate. After 200 ns, 100 mA is continuously provided to maintain the gate charged. The output driver sinks a high current to turn off the gate. This current can be up to 1.0 A peak for a 100 nF load.

#### **H-Bridge Gate Driver IC**

**Note:** GATE\_HS is loaded with a 100 nF capacitor in the chronograms. A smaller load will give lower peak and DC charge or discharge currents.

Figure 6. High-side gate driver chronograms

### 9.5 Modes of operation

### 9.5.1 Turn-on

For turn-on, the current required to charge the gate source capacitor  $C_{iss}$  in the specified time can be calculated as follows:

$$I_P = \frac{Q_G}{t_r} = \frac{80 \text{ nC}}{80 \text{ ns}} \approx 1.0 \text{ A}$$

Where  $Q_g$  is power MOSFET gate charge and  $t_r$  is peak current for rise time.

#### 9.5.2 Turn-off

The peak current for turn-off can be obtained in the same way as for turn-on, with the exception that peak current for fall time,  $t_f$ , is substituted for  $t_r$ :

$$I_P = \frac{Q_G}{t_f} = \frac{80 \text{ nC}}{80 \text{ ns}} \approx 1.0 \text{ A}$$

#### H-Bridge Gate Driver IC

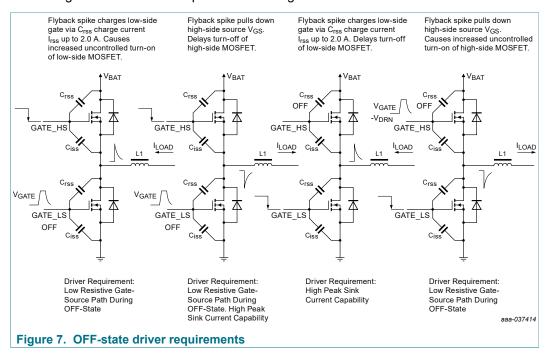

In addition to the dynamic current required to turn off or on the MOSFET, various application-related switching scenarios must be considered. These scenarios are presented in <u>Figure 7</u>. In order to withstand high dV/dt spikes, a low resistive path between gate and source is implemented during the OFF-state.

#### 9.5.3 Low-drop linear regulator

The low-drop linear regulator is supplied by  $V_{CC2}$ . If  $V_{CC2}$  exceeds 15.0 V, the output is limited to 14.5 V (typical).

The low-drop linear regulator provides the 5.0 V for the logic section of the driver, the  $V_{gs\_ls}$  buffered at LR\_OUT, and the +14.5 V for the charge pump, which generates the CP\_OUT The low-drop linear regulator provides 4.0 mA average current per driver stage.

In case of the full bridge, that means approximately 16 mA - 8.0 mA for the high side and 8.0 mA for the low side.

Note: The average current required to switch a gate with a frequency of 100 kHz is:

$$I_{\text{CP}} = Q_G * f_{\text{PWM}} = 80 \text{ nC} * 100 \text{ kHz} = 8.0 \text{ mA}$$

In a full-bridge application, only one high-side and one low-side switches on or off at the same time.

#### 9.5.4 Charge pump

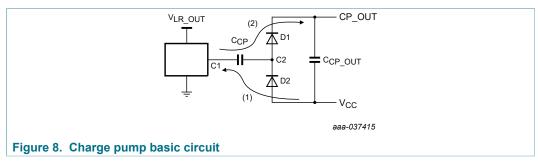

The charge pump generates the high-side driver supply voltage (CP\_OUT), buffered at CCP\_OUT. Figure 8 shows the charge pump basic circuit without load.

#### H-Bridge Gate Driver IC

When the oscillator is in low state [(1) in Figure 8],  $C_{CP}$  is charged through D2 until its voltage reaches  $V_{CC} - V_{D2}$ . When the oscillator is in high state (2),  $C_{CP}$  is discharged though D1 in  $C_{CP\_OUT}$ , and final voltage of the charge pump,  $V_{CP\_OUT}$ , is  $V_{cc} + V_{LR\_OUT} - 2_{VD}$ . The frequency of the 33883 oscillator is about 330 kHz.

#### 9.5.5 External capacitors choice

External capacitors on the charge pump and on the linear regulator are necessary to supply high peak current absorbed during switching.

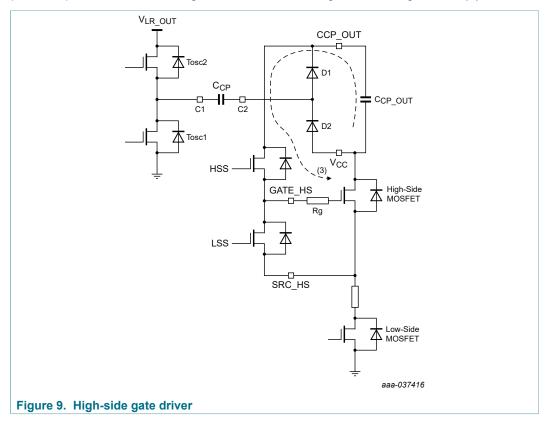

<u>Figure 9</u> represents a simplified circuitry of the high-side gate driver. Transistors Tosc1 and Tosc2 are the oscillator-switching MOSFETs. When Tosc1 is on, the oscillator is at low level. When Tosc2 is on, the oscillator is at high level. The capacitor  $C_{CP\_OUT}$  provides peak current to the high-side MOSFET through HSS during turn-on (3).

**H-Bridge Gate Driver IC**

#### 9.5.6 C<sub>CP</sub>

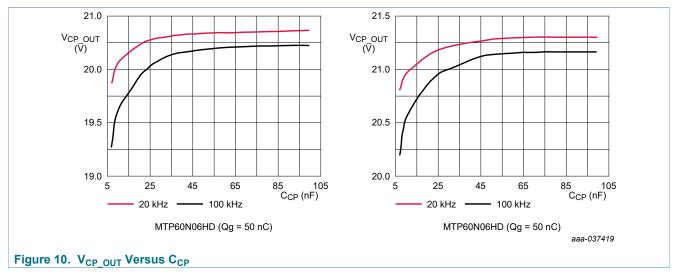

$C_{CP}$  choice depends on power MOSFET characteristics and the working switching frequency. Figure 10 contains two diagrams that depict the influence of  $C_{CP}$  value on  $V_{CP\_OUT}$  average voltage level. The diagrams represent two different frequencies for two power MOSFETs, MTP60N06HD and MPT36N06V.

The smaller the  $C_{CP}$  value is, the smaller the  $V_{CP\_OUT}$  value is. Moreover, for the same  $C_{CP}$  value, when the switching frequency increases, the average  $V_{CP\_OUT}$  level decreases. For most of the applications, a typical value of 33 nF is recommended.

### 9.5.7 C<sub>CP\_OUT</sub>

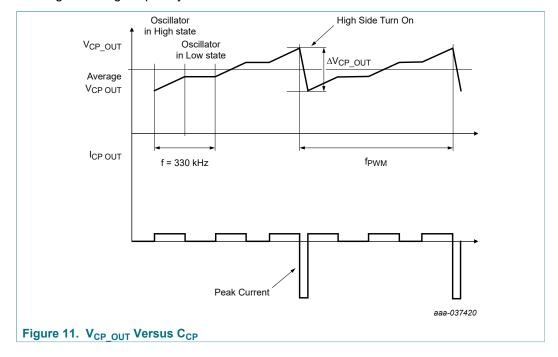

<u>Figure 11</u> depicts the simplified  $C_{CP\_OUT}$  current and voltage waveforms.  $f_{PWM}$  is the working switching frequency.

H-Bridge Gate Driver IC

As shown above, at high-side MOSFET turn-on  $V_{CP\_OUT}$  voltage decreases. This decrease can be calculated according to the  $C_{CP\_OUT}$  value as follows:

$$\Delta V_{\text{CP\_OUT}} = \frac{Q_G}{C_{\text{CP\_OUT}}}$$

Where Q<sub>g</sub> is power MOSFET gate charge.

### 9.5.8 C<sub>LR OUT</sub>

$C_{LR\_OUT}$  provides peak current needed by the low-side MOSFET turn-on.  $V_{LR\_OUT}$  decrease is as follows:

$$\Delta V_{\text{LR\_OUT}} = \frac{Q_G}{C_{\text{LR_OUT}}}$$

#### 9.5.9 Typical values of capacitors

In most working cases the following typical values are recommended for a well-performing charge pump:

$$C_{CP}$$

= 33 nF,  $C_{CP\ OUT}$  = 470 nF, and  $C_{LR\ OUT}$  = 470 nF

These values give a typical 100 mV voltage ripple on  $V_{CP\_OUT}$  and  $V_{LR\_OUT}$  with  $Q_g$  = 50 nC.

#### 9.6 Protection and diagnostic features

### 9.6.1 Gate protection

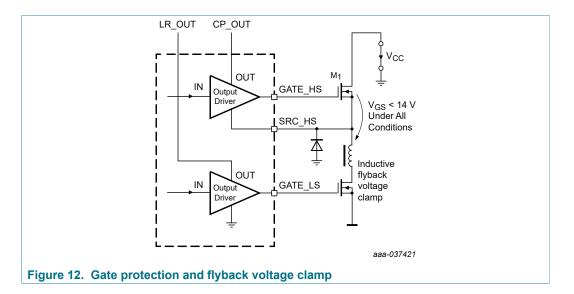

The low-side driver is supplied from the built-in low-drop regulator. The high-side driver is supplied from the internal charge pump buffered at CP\_OUT.

The low-side gate is protected by the internal linear regulator, which ensures that VGATE\_LS does not exceed the maximum VGS. Especially when working with the charge pump, the voltage at CP\_OUT can be up to 65 V. The high-side gate is clamped internally in order to avoid a VGS exceeding 18 V.

Gate protection does not include a fly-back voltage clamp that protects the driver and the external MOSFET from a fly-back voltage that can occur when driving inductive load. This fly-back voltage can reach high negative voltage values and needs to be clamped externally, as shown in <u>Figure 12</u>.

#### H-Bridge Gate Driver IC

### 9.6.2 Load dump and reverse battery

$V_{CC}$  and  $V_{CC2}$  can sustain load a dump pulse of 40 V and double battery of 24 V. Protection against reverse polarity is ensured by the external power MOSFET with the free-wheeling diodes forming a conducting pass from ground to  $V_{CC}$ . Additional protection is not provided within the circuit. To protect the circuit an external diode can be put on the battery line. It is not recommended putting the diode on the ground line.

#### 9.6.3 Temperature protection

There is temperature shutdown protection per each half-bridge. Temperature shutdown protects the circuitry against temperature damage by switching off the output drivers. Its typical value is 175 °C with an hysteresis of 15 °C.

### 9.6.4 DV/DT at V<sub>CC</sub>

V<sub>CC</sub> voltage must be higher than (SRC\_HS voltage minus a diode drop voltage) to avoid perturbation of the high-side driver.

In some applications a large dV / dt at pin C2 owing to sudden changes at  $V_{CC}$  can cause large peak currents flowing through pin C1, as shown in Figure 13.

For positive transitions at pin C2, the absolute value of the minimum peak current,  $I_{C1}$ min, is specified at 2.0 A for a  $t_{C1}$ min duration of 600 ns.

For negative transitions at pin C2, the maximum peak current,  $I_{C1}$ max, is specified at 2.0 A for a  $t_{C1}$ max duration of 600 ns. Current sourced by pin C1 during a large dV / dt will result in a negative voltage at pin C1 (Figure 13). The minimum peak voltage  $V_{C1}$ min is specified at -1.5 V for a duration of  $t_{C1}$ max = 600 ns. A series resistor with the charge pump capacitor (Ccp) capacitor can be added in order to limit the surge current.

H-Bridge Gate Driver IC

In the case of rapidly changing  $V_{CC}$  voltages, the large dV/dt may result in perturbations of the high-side driver, thereby forcing the driver into an OFF state. The addition of capacitors C3 and C4, as shown in Figure 14, reduces the dV/dt of the source line, consequently reducing driver perturbation. Typical values for R3 / R4 and C3 / C4 are 10  $\Omega$  and 10 nF, respectively.

### 9.6.5 DV/DT at V<sub>CC2</sub>

When the external high-side MOSFET is on, in case of rapid negative change of  $V_{CC2}$  the voltage ( $V_{GATE\_HS} - V_{SRC\_HS}$ ) can be higher than the specified 18 V. In this case a resistance in the SRC line is necessary to limit the current to 5.0 mA max. It will protect the internal zener placed between GATE\_HS and SRC pins.

In case of high current (SRC\_HS >100 mA) and high voltage (>20 V) between GATE\_HSX and SRC\_HS an external zener of 18 V is needed as shown in <u>Figure 14</u>.

**H-Bridge Gate Driver IC**

# 10 Typical applications

# 11 Packaging

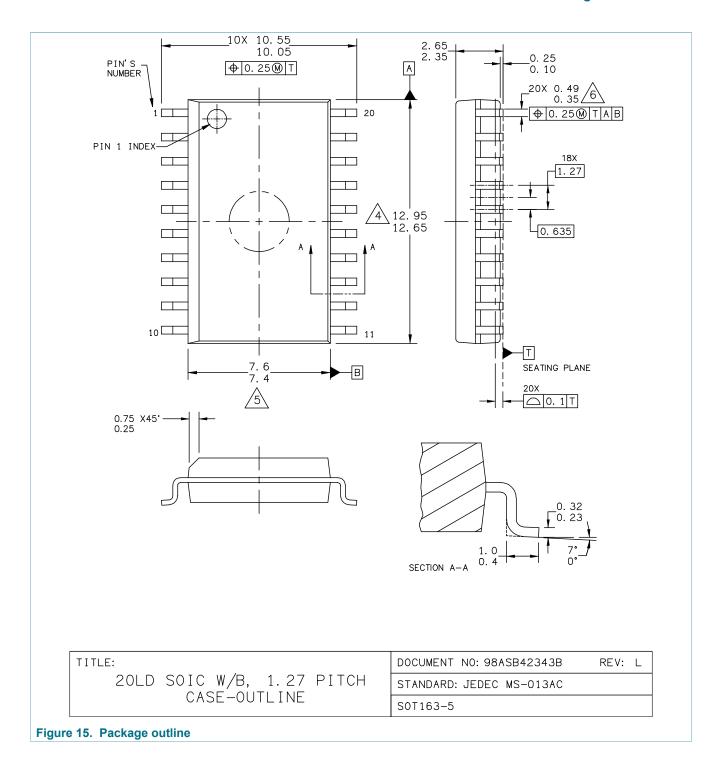

# 11.1 Package mechanical dimensions

Package dimensions are provided in package drawings. To find the most current package outline drawing, go to <a href="www.nxp.com">www.nxp.com</a> and perform a keyword search for the drawing's document number.

Table 7. Package Outline

| Package         | Package outline drawing number |

|-----------------|--------------------------------|

| 20-pin 20 SOICW | SOT163-5                       |

### H-Bridge Gate Driver IC

H-Bridge Gate Driver IC

# 12 Revision history

### Table 8. Revision history

| Document ID                                                                                                                                              | Release date                                                                                 | Data sheet status                                                                                                                                                                                                         | Change notice    | Supersedes         |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------|--|--|

| MC33883 v.11.0                                                                                                                                           | 20200427                                                                                     | Technical data                                                                                                                                                                                                            | 2020040161       | MC33883 v.10.0     |  |  |

| <ul> <li>Changed format to match latest NXP data sheet format</li> <li>Section 1 and Section 2: Added "Qualified in compliance with AEC-Q100"</li> </ul> |                                                                                              |                                                                                                                                                                                                                           |                  |                    |  |  |

| MC33883 v.10.0                                                                                                                                           | 10/2012                                                                                      | Technical data                                                                                                                                                                                                            | _                | MC33883 v.9.0      |  |  |

| Modifications                                                                                                                                            | <ul> <li>Updated Free</li> <li>Removed MC</li> </ul>                                         | erable part number from MCZ33883EG to MC33883HEG. escale form and style escale form the ordering information on Advance Information to Technical Data                                                                     |                  |                    |  |  |

| MC33883 v.9.0                                                                                                                                            | 1/2007                                                                                       | Technical data                                                                                                                                                                                                            | _                | MC33883 v.8.0      |  |  |

| Modifications                                                                                                                                            | <ul><li>Updated to th</li><li>Added MCZ3</li><li>Updated the p</li><li>Removed Pea</li></ul> | Revision History page the current Freescale format and style 3883EG/R2 to the Ordering Information to backage drawing to Rev. J tak Package Reflow Temperature During Reflow (solder reflow) the strom www.freescale.com. | parameter from T | able 3. Added note |  |  |

H-Bridge Gate Driver IC

# 13 Legal information

#### 13.1 Data sheet status

| Document status <sup>[1][2]</sup>       | Product status <sup>[3]</sup> | Definition                                                                                                                                                                                           |

|-----------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [short] Data sheet: product preview     | Development                   | This document contains certain information on a product under development. NXP reserves the right to change or discontinue this product without notice.                                              |

| [short] Data sheet: advance information | Qualification                 | This document contains information on a new product. Specifications and information herein are subject to change without notice.                                                                     |

| [short] Data sheet: technical data      | Production                    | This document contains the product specification. NXP Semiconductors reserves the right to change the detail specifications as may be required to permit improvements in the design of its products. |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions".

- The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

#### 13.2 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

Product specification — The information and data provided in a technical data data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the technical data data sheet.

#### 13.3 Disclaimers

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or  $consequential\ damages\ (including\ \hbox{-}\ without\ limitation\ \hbox{-}\ lost\ profits,\ lost$ savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

Suitability for use in automotive applications — This NXP Semiconductors product has been qualified for use in automotive applications. Unless otherwise agreed in writing, the product is not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or

MC33883

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved.

### **H-Bridge Gate Driver IC**

malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### 13.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

**NXP** — is a trademark of NXP B.V.

**SMARTMOS** — is a trademark of NXP B.V.

# H-Bridge Gate Driver IC

# **Tables**

| Tab. 1.<br>Tab. 2.<br>Tab. 3.<br>Tab. 4. | Orderable part variations       2         Pin definitions       4         Maximum ratings       5         Static electrical characteristics       5 | Tab. 5.<br>Tab. 6.<br>Tab. 7.<br>Tab. 8. | Dynamic electrical characteristics 7 Functional truth table 9 Package Outline 18 Revision history 20 |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------|

| Figur                                    | res                                                                                                                                                 |                                          |                                                                                                      |

| Fig. 1.                                  | Simplified application diagram2                                                                                                                     | Fig. 10.                                 | VCP OUT Versus CCP14                                                                                 |

| Fig. 2.                                  | Internal block diagram3                                                                                                                             | Fig. 11.                                 | VCP OUT Versus CCP14                                                                                 |

| Fig. 3.                                  | Pinout diagram4                                                                                                                                     | Fig. 12.                                 | Gate protection and flyback voltage clamp16                                                          |

| Fig. 4.                                  | Timing characteristics8                                                                                                                             | Fig. 13.                                 | Limits of C1 current and voltage with large                                                          |

| Fig. 5.                                  | High-side gate driver functional schematic 10                                                                                                       | Ü                                        | values of dV/dt17                                                                                    |

| Fig. 6.                                  | High-side gate driver chronograms11                                                                                                                 | Fig. 14.                                 | Application schematic with external                                                                  |

| Fig. 7.                                  | OFF-state driver requirements                                                                                                                       | · ·                                      | protection circuit18                                                                                 |

| Fig. 8.                                  | Charge pump basic circuit                                                                                                                           | Fig. 15.                                 | Package outline19                                                                                    |

| Fig. 9.                                  | High-side gate driver                                                                                                                               | •                                        | •                                                                                                    |

MC33883

# H-Bridge Gate Driver IC

### **Contents**

| 1     | General description                        | . 1 |

|-------|--------------------------------------------|-----|

| 2     | Features                                   | . 1 |

| 3     | Simplified application diagram             |     |

| 4     | Applications                               | 2   |

| 5     | Ordering information                       |     |

| 6     | Internal block diagram                     |     |

| 7     | Pinning information                        |     |

| 7.1   | Pinout diagram                             |     |

| 7.2   | Pin definitions                            |     |

| 8     | General product characteristics            |     |

| 8.1   | Maximum ratings                            | . 5 |

| 8.2   | Static electrical characteristics          |     |

| 8.3   | Dynamic electrical characteristics         |     |

| 8.4   | Timing diagram                             |     |

| 9     | Functional description                     |     |

| 9.1   | Introduction                               |     |

| 9.2   | Functional pin description                 |     |

| 9.2.1 | Supply voltage pins (VCC and VCC2)         | . 8 |

| 9.2.2 | Input high-side and low-side pins (IN_HS1, |     |

|       | IN_HS2, IN_LS1, IN_LS2)                    | 8   |

| 9.2.3 | Source output high-side pins (SRC_HS1 and  |     |

|       | SRC_HS2)                                   | . 8 |

| 9.2.4 | Gate high-side and low-side pins (GATE_    |     |

|       | HS1, GATE_HS2, GATE_LS1, GATE_LS2)         | 9   |

| 9.2.5 | Global enable (G_EN)                       |     |

| 9.2.6 | Charge pump out (CP_OUT)                   | 9   |

| 9.2.7 | Charge pump capacitor pins (C1 and C2)     | . 9 |

| 9.2.8 | Linear regulator output (LR_OUT)           | . 9 |

| 9.2.9 | Ground pins (GND_A, GND1, GND2)            | . 9 |

| 9.3   | Functional truth table                     | 9   |

| 9.4   | Functional device operation                | 10  |

| 9.5   | Modes of operation                         | 11  |

| 9.5.1 | Turn-on                                    | 11  |

| 9.5.2 | Turn-off                                   | 11  |

| 9.5.3 | Low-drop linear regulator                  | 12  |

| 9.5.4 | Charge pump                                | 12  |

| 9.5.5 | External capacitors choice                 | 13  |

| 9.5.6 | CCP                                        | 14  |

| 9.5.7 | CCP_OUT                                    | 14  |

| 9.5.8 | CLR_OUT                                    | 15  |

| 9.5.9 | Typical values of capacitors               |     |

| 9.6   | Protection and diagnostic features         | 15  |

| 9.6.1 | Gate protection                            |     |

| 9.6.2 | Load dump and reverse battery              | 16  |

| 9.6.3 | Temperature protection                     | 16  |

| 9.6.4 | DV/DT at VCC                               | 16  |

| 9.6.5 | DV/DT at VCC2                              |     |

| 10    | Typical applications                       | 18  |

| 11    | Packaging                                  |     |

| 11.1  | Package mechanical dimensions              |     |

| 12    | Revision history                           |     |

| 13    | Legal information                          |     |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.