# TMS57014A DUAL AUDIO DIGITAL-TO-ANALOG CONVERTER

**DWB PACKAGE**

SLAS077D - SEPTEMBER 1993 - REVISED NOVEMBER 1995

- Single 5-V Power Supply

- Sample Rates (F<sub>S</sub>) up to 48 kHz

- 18-Bit Resolution

- Pulse-Width-Modulation (PWM) Output

- De-emphasis Filter for Sample Rates of 32, 37.8, 44.1, and 48 kHz

- Mute With Zero-Data-Detect Flags

- Digital Attenuation to -60 dB

- Total Harmonic Distortion of 0.004%

Maximum

- Total-Channel Dynamic Range of 96 dB Minimum

- Serial-Port Interface

- Differential Architecture

- CMOS Technology

- 2s-Complement Data Format

#### (TOP VIEW) 28 DV<sub>DD</sub> INIT TEST 1 2 27 ∏ L1 ATT **∏** 3 26 AV<sub>DDL</sub> SHIFT 25 🛮 L2 LATCH | 5 24 ∏ AGNDL 23 XGND 256FSO **∏** 6 TEST $\Pi$ 7 22 **∏** XIN DGND **1**8 21 XOUT TEST [] 9 20 XV<sub>DD</sub> BCK **1** 10 19 ∏ AGNDR DATA 11 18∏ R2 LRCK 12 17 AV<sub>DDR</sub> MUTEL [ 13 16 R1 15 DV<sub>DD</sub> MUTER [ 14

#### description

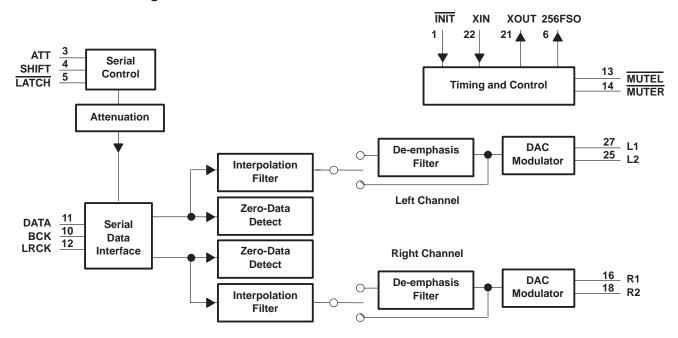

The TMS57014A is a stereo oversampled-sigma-delta digital-to-analog converter (DAC) designed for use in systems such as compact disks, digital audio tapes, multimedia, and video cassette recorders. The device provides high-resolution signal conversion. This device consists of two identical synchronous conversion paths for left and right audio channels. Other overhead functions provide on-chip timing and control.

Additional features include muting, attenuation, de-emphasis, and zero-data detection. Control words (16-bit) from a host controller or processor implement these functions.

The TMS57014A is characterized for operation from 0°C to 70°C.

#### **AVAILABLE OPTION**†

|             | PACKAGE                |

|-------------|------------------------|

| TA          | SMALL OUTLINE<br>(DWB) |

| 0°C to 70°C | TMS57014ADWBLE         |

<sup>†</sup> Available on tape and reel (LE) only.

This device contains circuits to protect its inputs and outputs against damage due to high static voltages or electrostatic fields; however, it is advised that precautions be taken to avoid application of any voltage higher than maximum-rated voltages to these high-impedance circuits. During storage or handling, the device leads should be shorted together or the device should be placed in conductive foam. In a circuit, unused inputs should always be connected to an appropriated logic voltage level, preferably either VCC or ground.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# functional block diagram

#### **Terminal Functions**

| TERM              | INAL    |     |                                                                                                                                                                               |

|-------------------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME              | NO.     | 1/0 | DESCRIPTION                                                                                                                                                                   |

| ATT               | 3       | I   | Serial control data. ATT is a 16-bit word configured as LSB first (see Tables 2, 3, and 4).                                                                                   |

| AV <sub>DDL</sub> | 26      | ı   | Analog power supply (left channel)                                                                                                                                            |

| AV <sub>DDR</sub> | 17      | ı   | Analog power supply (right channel)                                                                                                                                           |

| AGNDL             | 24      | I   | Analog ground (left channel)                                                                                                                                                  |

| AGNDR             | 19      | I   | Analog ground (right channel)                                                                                                                                                 |

| BCK               | 10      | I   | Bit clock input. BCK clocks serial audio data into the device.                                                                                                                |

| DATA              | 11      | I   | Audio data input. DATA can be configured as 16 or 18 bits with MSB or LSB first. DATA is 2s complement.                                                                       |

| DV <sub>DD</sub>  | 15, 28  | I   | Digital supply                                                                                                                                                                |

| DGND              | 8       | I   | Digital ground                                                                                                                                                                |

| INIT              | 1       | I   | Reset. When INIT is brought low, the device is reset. The device is activated on the rising edge of INIT. The LRCK signal must be applied to the device for a reset to occur. |

| LATCH             | 5       | I   | Serial-control data latch. Control data loads into the internal registers when LATCH is brought low.                                                                          |

| LRCK              | 12      | I   | Left/right clock. LRCK signifies whether the serial data is associated with the left-channel DAC (when high) or the right-channel DAC (when low).                             |

| MUTEL             | 13      | 0   | Left-channel mute flag active. When the left channel is mute or the data through the channel remains at zero for the system-register selected time, MUTEL is brought low.     |

| MUTER             | 14      | 0   | Right-channel mute flag active. When the right channel is mute or the data through the channel remains at zero for the system-register selected time, MUTER is brought low.   |

| L1                | 27      | 0   | Left PWM output 1                                                                                                                                                             |

| L2                | 25      | 0   | Left PWM output 2                                                                                                                                                             |

| R1                | 16      | 0   | Right PWM output 1                                                                                                                                                            |

| R2                | 18      | 0   | Right PWM output 2                                                                                                                                                            |

| SHIFT             | 4       | I   | Shift clock. SHIFT clocks the control data into the internal registers.                                                                                                       |

| TEST              | 2, 7, 9 | Ι   | All TEST inputs should be tied low.                                                                                                                                           |

| XIN               | 22      | I   | Master clock in. XIN derives all the key logic signals of the device. XIN runs at 512 $F_s$ , where $F_s$ is the sample rate.                                                 |

| XOUT              | 21      | 0   | Master clock out                                                                                                                                                              |

| $XV_{DD}$         | 20      | I   | Power supply for clock section                                                                                                                                                |

| XGND              | 23      | I   | Ground for clock section                                                                                                                                                      |

| 256FSO            | 6       | 0   | System clock out. 256FSO reflects the master clock input divided by 2. The rate is 256Fs, where F <sub>S</sub> is the sample rate.                                            |

## detailed description

The TMS57014A incorporates an interpolation impulse-response filter (FIR) and oversampled modulator. The pulse-width modulation (PWM) digital output feeds into an external low-pass filter to recover the analog audio signal.

Two control registers configure the device, the attenuation register controls the attenuation range and the system register controls additional functions (see register set section).

#### reset/initialization

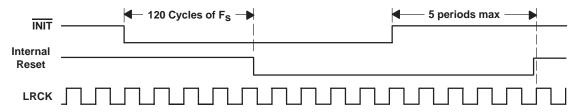

When  $\overline{\text{INIT}}$  is brought low, an internal reset signal becomes active approximately 120 cycles of the sampling frequency (F<sub>S</sub>) after the falling edge of  $\overline{\text{INIT}}$ . Under this condition, all internal circuits are initialized and the PWM output is held at zero data (50% duty cycle). When  $\overline{\text{INIT}}$  is brought high, the internal reset signal goes inactive for a maximum of five LRCK periods after the rising edge of  $\overline{\text{INIT}}$ . At this point, internal clocks are synchronous with LRCK and the PWM output is valid (see Figure 1). The LRCK signal must be applied for proper initialization.

#### reset/initialization (continued)

Figure 1. Reset Timing Relationships

## timing and control

The timing and control circuit generates and distributes necessary clocks throughout this design. XIN is the external master clock input. The sample rate of the data paths is set as LRCK = XIN/512. With a fixed oversampling ratio of 32x and each PWM output value requiring 16 XIN cycles, the effect of changing XIN is shown in Table 1.

The DAC can be operated at any conversion rate between 48 kHz and 32 kHz by choosing the appropriate master-clock frequency. Some of the functions of the converter, such as the de-emphasis filter, operate only at the frequencies in Table 1.

| XIN<br>(MHz) | 256FSO<br>(MHz) | LRCK<br>(kHz) |

|--------------|-----------------|---------------|

| 24.5760      | 12.2880         | 48.0          |

| 22.5792      | 11.2896         | 44.1          |

| 19.3536      | 9.6768          | 37.8          |

| 16.3840      | 8.1920          | 32.0          |

**Table 1. Master Clock to Sample Rate Comparison**

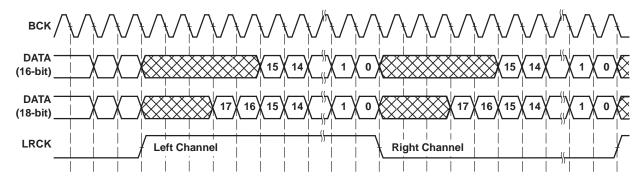

## digital-audio data interface

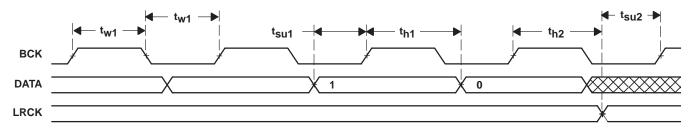

The conversion cycle is synchronized to the rising edge of LRCK, and the data must meet the setup requirements specified in the timing requirements table. The input data is 16 or 18 bits with the MSB or LSB first as selected in the system register. The BCK frequency must be equal to or greater than 32  $F_s$  for 16-bit data or 36 F<sub>S</sub> for 18-bit data where F<sub>S</sub> is the sample rate. Figure 2 illustrates the input timing.

Figure 2. Audio-Data Input Timing

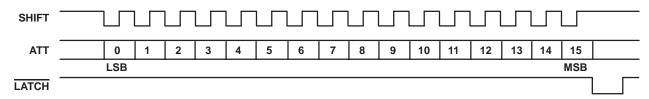

#### serial-control interface

This device uses the least-significant-bit-first format. Therefore, for a 16-bit word, D15 is the most significant bit and D0 is the least significant bit. Unless otherwise specified, all values are in 2s-complement format.

#### serial-control-data input

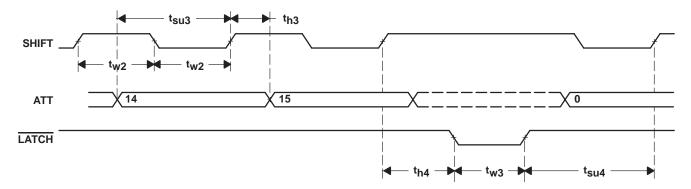

The 16-bit control-data input implements the device-control functions. The TMS57014A has two registers for this data: the system register and the attenuation register. The system register contains most of the system configuration information, and the attenuation register controls audio output level, de-emphasis, and mute. Figure 3 illustrates the input timing for ATT, SHIFT, and LATCH. The data loads internally on the falling edge of LATCH. The shift clock should be high for the LATCH setup time before LATCH goes low.

Figure 3. Control-Data-Input Timing

#### mute

When mute is activated, the output PWM becomes zero data (50% duty cycle). The two mute flags, MUTEL and MUTER, are independently set low based on the data in the respective channel being zero. This function becomes active under the following conditions:

- 1. When the zero-data detector detects that the input data has been zero for 2500 cycles of F<sub>S</sub> or 12500 cycles of F<sub>S</sub> (as selected in the control registers), output is 50% duty cycle.

- 2. When the MUTE register value is set high by means of the serial-control data.

- 3. When INIT is active (low), output is 50% duty cycle.

#### zero-data detect

After the input data remains zero for 2500 or 12500 cycles of  $F_S$  as set by the system register (D4, D5), the channel-mute flag becomes active. Zero-data detection is available for both channels independently, so the two outputs ( $\overline{\text{MUTER}}$  and  $\overline{\text{MUTEL}}$ ) indicate that zero data has been detected on the respective channel. The zero-detect register value in the serial-control data selects the detection period. The mute flag returns high immediately when nonzero input data is received.

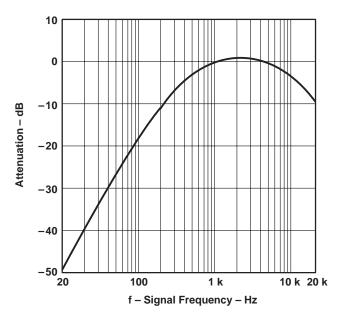

#### de-emphasis filter

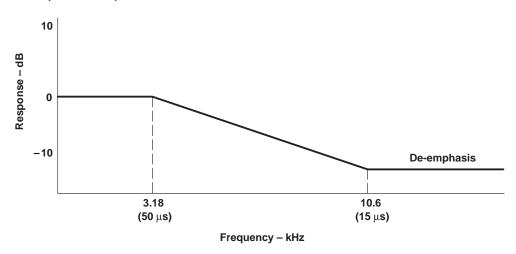

Four sets of de-emphasis-filter coefficients support four sampling rates ( $F_s$ ): 32, 37.8, 44.1, and 48 kHz. Internal register values select the filter coefficients. The internal register values enable or disable the filter. Figure 4 illustrates the de-emphasis characteristics.

Many audio sources have been recorded with pre-emphasis characteristics that are the inverse of the de-emphasis characteristics shown in Figure 4. This device provides reconstruction of the original frequency response.

### de-emphasis filter (continued)

Figure 4. De-emphasis Characteristics

## digital attenuation

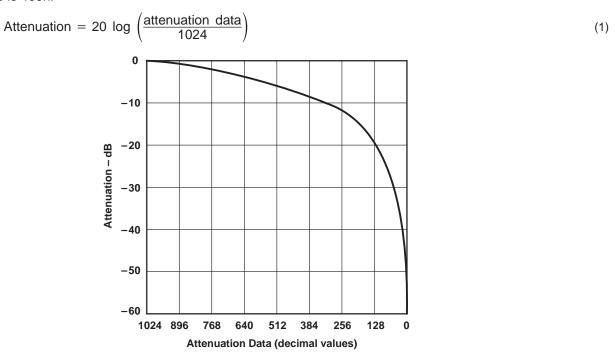

A value selected in the internal attenuation register determines the attenuation of the digital-audio-data input. The attenuation value is 11 bits long with a valid range of hex values from 400h to 000h. A data value of 001h corresponds to an attenuation value of -60 dB and a data value of 400h corresponds to 0 dB. The attenuation function is nonlinear (see equation 1). Figure 5 illustrates the attenuation function in dB. The default attenuation value is 400h.

Figure 5. Digital Attenuation Characteristics

## register set

Table 2 contains the register-set selection. Tables 3 and 4 list the bit functions.

Table 2. Register-Set Selection

| BI | TS | DESCRIPTION                    |  |  |  |

|----|----|--------------------------------|--|--|--|

| 15 | 14 | DESCRIPTION                    |  |  |  |

| 0  | 0  | Attenuation register           |  |  |  |

| 0  | 1  | System register                |  |  |  |

| 1  | Х  | Invalid condition <sup>†</sup> |  |  |  |

<sup>†</sup> Bit 15 should always be set to 0 when writing data for proper operation.

**Table 3. Attenuation-Register Bit Functions**

|    | ВІТ | s‡ |      | FUNCTION                       |

|----|-----|----|------|--------------------------------|

| 13 | 12  | 11 | 10-0 | FUNCTION                       |

| 0  | _   | _  | _    | De-emphasis off                |

| 1  | _   | _  | _    | De-emphasis on                 |

| _  | 0   | _  | _    | Channel mute off               |

| _  | 1   | _  | _    | Channel mute on                |

| _  | _   | 0  | _    | Bit 11 must be low             |

|    | _   | _  | 0    | Digital attenuation, mute      |

| _  | _   | _  | 1    | Digital attenuation, -60.2 dB§ |

| _  | _   | _  | 2    | Digital attenuation, -54.2 dB§ |

| _  | _   | _  | 3    | Digital attenuation, -50.7 dB§ |

| _  | _   | _  |      |                                |

| _  | _   | _  | 1FF  | Digital attenuation, -6.04 dB§ |

|    | _   | _  | 200  | Digital attenuation, -6.02 dB§ |

| _  | _   | _  | 201  | Digital attenuation, -6.00 dB§ |

| _  | _   | _  |      |                                |

|    | _   | _  | 3FF  | Digital attenuation, -0.01 dB§ |

| _  |     | _  | 400  | Digital attenuation, 0.00 dB§  |

<sup>‡</sup> Default value = 0400h

<sup>§</sup> The attenuation values shown are typical values. Refer to the digital attenuation section for a description of the attenuation function.

**Table 4. System-Register Bit Functions**

|    | вітѕ† |      |   |   |     |   |   | FUNCTION                                                  |

|----|-------|------|---|---|-----|---|---|-----------------------------------------------------------|

| 13 | 12    | 11-6 | 5 | 4 | 3-2 | 1 | 0 | FUNCTION                                                  |

| 0  | _     | _    | _ | _ | _   | _ | _ | MSB first, audio data                                     |

| 1  | _     | _    | _ | _ | _   | _ | _ | LSB first, audio data                                     |

| _  | 0     | _    | _ | _ | _   | _ | _ | 16-bit, audio data                                        |

| _  | 1     | _    | _ | _ | _   | _ | _ | 18-bit, audio data                                        |

| _  | _     | 0    | _ | _ | _   | _ | _ | Bits 11-6 must be low                                     |

| _  | _     | _    | 0 | _ | _   | _ | _ | Zero data detect period (2500 cycles of F <sub>S</sub> )  |

|    | _     | _    | 1 | _ | _   | _ | _ | Zero data detect period (12500 cycles of F <sub>S</sub> ) |

|    | _     | _    | _ | 0 | _   | _ |   | Bit 4 must be low                                         |

| _  | _     | _    | _ | _ | 0   | _ | _ | De-emphasis –44.1 kHz                                     |

| _  | _     | _    | _ | _ | 1   | _ | _ | De-emphasis –48.0 kHz                                     |

| _  | _     | _    | _ | _ | 2   | _ | _ | De-emphasis – 37.8 kHz                                    |

| _  | _     | _    | _ | _ | 3   | _ | _ | De-emphasis – 32.0 kHz                                    |

|    |       |      |   |   |     | 0 |   | LRCK and PWM are not synchronized                         |

|    | _     | _    | _ | _ | _   | 1 | _ | LRCK and PWM synchronized                                 |

|    | _     | _    | _ |   |     | _ | 0 | Bit 0 must be low                                         |

<sup>†</sup> Default value = 0000h

## interpolation filter

The interpolation filter used prior to the DAC increases the digital-data rate from the LRCK speed to the oversampled rate by interpolating with a ratio of 1:32. The oversampling modulator receives the output of this filter with de-emphasis as an option.

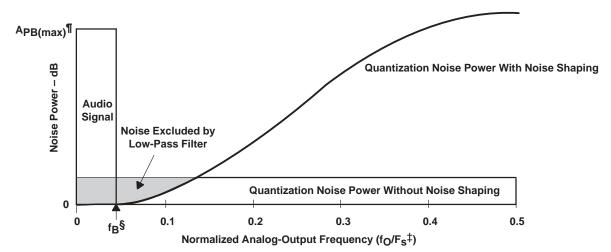

#### **DAC** modulator

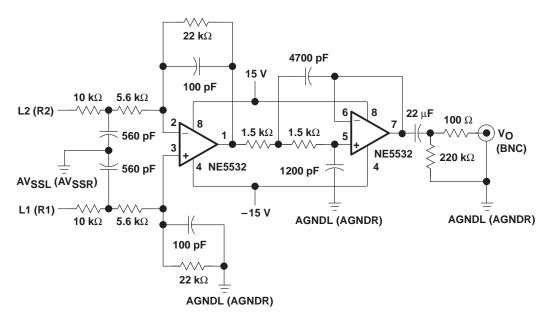

The DAC is a third-order modulator with 32 times oversampling. The DAC provides high-resolution, low-noise performance using a 15-value PWM output as shown in Figure 6.

$<sup>\</sup>ddagger$  f<sub>O</sub> is the output frequency at the low-pass filter output (V<sub>O</sub>) shown in Figure 7.

Figure 6. Oversampling Noise Power With and Without Noise Shaping

<sup>§</sup> f<sub>B</sub> is the highest frequency of interest within the baseband.

<sup>¶</sup> APB(max) is the passband maximum amplitude.

### PWM output (L2-L1 and R2-R1)

The L2-L1 and the R2-R1 output pairs are PWM signals with the L2-L1 differential pulse duration determining the left-channel analog voltage and the R2-R1 differential pulse duration determining the right-channel analog voltage.

Each DAC left and right output consists of 15 levels of PWM and provides a differential signal as the input to two external differential amplifiers configured as a low-pass filter to produce the left and right audio outputs (see Figure 7).

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Analog supply voltage range, left and right, AV <sub>DDL</sub> , AV <sub>DDR</sub> (see Note 1) |                                    |

|-------------------------------------------------------------------------------------------------|------------------------------------|

| Digital supply voltage range, DV <sub>DD</sub> (see Note 2)                                     | 0.3 V to 7 V                       |

| Clock supply voltage range, XV <sub>DD</sub> (see Note 3)                                       | 0.3 V to 7 V                       |

| Output voltage range, VO: L1, L2                                                                | 0.3 V to AV <sub>DDL</sub> + 0.3 V |

| R1, R2                                                                                          | 0.3 V to AV <sub>DDR</sub> + 0.3 V |

| Input voltage range, V <sub>I</sub>                                                             | 0.3 V to DV <sub>DD</sub> + 0.3 V  |

| Operating free-air temperature range, T <sub>A</sub>                                            | 0°C to 70°C                        |

| Case temperature for 10 seconds, T <sub>C</sub>                                                 | 260°C                              |

| Storage temperature range, T <sub>stg</sub>                                                     |                                    |

|                                                                                                 |                                    |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. Voltage values for maximum ratings are with respect to AGNDL and AGNDR respectively.

- 2. Voltage values for maximum ratings are with respect to DGND.

- 3. Voltage values for maximum ratings are with respect to XGND.

## recommended operating conditions (see Note 4)

|                                           |                                       |      | MIN                  | NOM  | MAX                                                                 | UNIT |  |

|-------------------------------------------|---------------------------------------|------|----------------------|------|---------------------------------------------------------------------|------|--|

| Analog supply voltage, left and right,    | AV <sub>DDL</sub> , AV <sub>DDR</sub> |      | 4.75                 | 5    | 5.25                                                                | V    |  |

| Digital supply voltage, DV <sub>DD</sub>  |                                       | 4.75 | 5                    | 5.25 | V                                                                   |      |  |

| Clock supply voltage, XV <sub>DD</sub>    |                                       |      | 4.75                 | 5    | 5.25                                                                | V    |  |

| High level input voltage. V.              | XIN                                   |      | 0.9 V <sub>DD</sub>  |      |                                                                     | V    |  |

| High-level input voltage, V <sub>IH</sub> | All other digital inputs              |      | 0.76 V <sub>DD</sub> |      | 5.25<br>5.25                                                        | V    |  |

| Low lovel input voltage. Viv              | XIN                                   |      |                      |      | 0.1 V <sub>DD</sub>                                                 | V    |  |

| Low-level input voltage, V <sub>IL</sub>  | All other digital inputs              |      |                      |      | 5.25<br>5.25<br>5.25<br>0.1 V <sub>DD</sub><br>0.24 V <sub>DD</sub> | V    |  |

| Load resistance at PWM, RL                |                                       |      |                      | 10   |                                                                     | kΩ   |  |

| Master clock frequency at XIN             |                                       |      | 16.3                 |      | 24.6                                                                | MHz  |  |

| Operating free-air temperature, TA        |                                       |      | 0                    |      | 70                                                                  | °C   |  |

NOTE 4:  $DV_{DD}$ ,  $AV_{DDL}$ ,  $XV_{DD}$  and  $AV_{DDR}$  tied together represents  $V_{DD}$ .

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

## digital interface, $AV_{DD} = DV_{DD} = 5 \text{ V} \pm 5\%$ (see Note 4)

|                                                   | PARAM                            | ETER           | TEST CONDITIONS           | MIN                  | TYP† | MAX | UNIT |

|---------------------------------------------------|----------------------------------|----------------|---------------------------|----------------------|------|-----|------|

|                                                   |                                  | 256FSO         | $I_{O} = -0.4 \text{ mA}$ | V <sub>DD</sub> -0.5 |      |     |      |

| \/                                                | High-level output voltage        | L1, L2, R1, R2 | $I_{O} = -12 \text{ mA}$  | V <sub>DD</sub> -0.5 |      |     | v    |

| VOH                                               | nigh-level output voltage        | XOUT           | $I_0 = -1.2 \text{ mA}$   | V <sub>DD</sub> −0.5 |      |     | V    |

|                                                   |                                  | MUTEL, MUTER   | $I_O = -1 \text{ mA}$     | V <sub>DD</sub> −0.5 |      |     |      |

|                                                   |                                  | 256FSO         | $I_O = 0.4 \text{ mA}$    |                      |      | 0.4 | V    |

| \ <sub>\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\</sub> | Low-level output voltage         | L1, L2, R1, R2 | I <sub>O</sub> = 12 mA    |                      |      | 0.5 |      |

| VOL                                               |                                  | XOUT           | $I_0 = 1.2 \text{ mA}$    |                      |      | 0.5 |      |

|                                                   |                                  | MUTEL, MUTER   | $I_O = 1 \text{ mA}$      |                      |      | 0.4 |      |

| lн                                                | High-level input current, any di | gital input    |                           |                      | ±1   | ±5  | μΑ   |

| Iμ                                                | Low-level input current, any dig | gital input    |                           |                      | ±1   | ±5  | μΑ   |

| Ci                                                | C <sub>i</sub> Input capacitance |                |                           |                      | 5    |     | pF   |

| Со                                                | Output capacitance               |                |                           |                      | 5    |     | pF   |

<sup>†</sup> All typical values are at  $T_A = 25$ °C.

NOTE 4: DV<sub>DD</sub>, AV<sub>DDL</sub>, XV<sub>DD</sub> and AV<sub>DDR</sub> tied together represents V<sub>DD</sub>.

## supplies, $AV_{DD} = DV_{DD} = 5 V \pm 5\%$ , no load

| PARAMETER                                                    | TEST CONDITIONS                                              | MIN | TYP <sup>†</sup> | MAX | UNIT |

|--------------------------------------------------------------|--------------------------------------------------------------|-----|------------------|-----|------|

| Analog power supply current                                  | AV <sub>DDL</sub> and AV <sub>DDR</sub> are shorted together |     | 15               |     | mA   |

| Digital power supply current                                 |                                                              |     | 15               |     | mA   |

| Total device supply current over operating temperature range |                                                              |     |                  | 60  | mA   |

| Power dissipation                                            |                                                              |     |                  | 350 | mW   |

<sup>†</sup> All typical values are at  $T_A = 25^{\circ}C$ .

# DAC modulator, AV<sub>DD</sub> = DV<sub>DD</sub> = 5 V $\pm$ 5%, sample rate (F<sub>s</sub>) = 44.1 kHz, full-scale input sine wave at 1 kHz, T<sub>A</sub> = 25°C, bandwidth is 20 Hz to 20 kHz

| PARAMETER                 | TEST CONDITIONS                                                    |                          | MIN | TYP <sup>†</sup> | MAX    | UNIT |

|---------------------------|--------------------------------------------------------------------|--------------------------|-----|------------------|--------|------|

| Resolution                | See Note 5                                                         |                          | 18  |                  |        | bits |

| Signal-to-noise ratio     | A-weighted, 20 Hz to 20 kHz,<br>See Figure 10, Table 5, and Note 5 | De-emphasis not selected | 96  | 100              |        | dB   |

| Total harmonic distortion | 20 Hz to 20 kHz, See Note 5                                        |                          |     | 0.003%           | 0.004% |      |

<sup>†</sup> All typical values are at  $T_A = 25$ °C.

NOTE 5: These specifications are measured at the output (VO) of the low-pass filter shown in Figure 7.

## filter characteristics, AV<sub>DD</sub> = DV<sub>DD</sub> = 5 V $\pm$ 5%, de-emphasis disabled

| PARAMETER               | TEST CONDITIONS                                    | MIN                 | TYP† I            | MAX                | UNIT |

|-------------------------|----------------------------------------------------|---------------------|-------------------|--------------------|------|

| Pass-band ripple        | Sample rate (E ) _ 49 kHz See Note E               | -0.002              | 0                 | 0.002              | dB   |

| Stop-band attenuation   | Sample rate (F <sub>S</sub> ) = 48 kHz, See Note 5 | 75                  |                   |                    | dB   |

| Pass band (-3 dB) (DAC) |                                                    | 0                   | 0.                | .46 F <sub>S</sub> | kHz  |

| Stop band               | See Note 5                                         | 0.54 F <sub>S</sub> |                   |                    | kHz  |

| Group delay             | 1                                                  |                     | 29/F <sub>S</sub> |                    | S    |

<sup>†</sup> All typical values are at T<sub>A</sub> = 25°C.

NOTE 5: These specifications are measured at the output (VO) of the low-pass filter shown in Figure 7.

# TMS57014A DUAL AUDIO DIGITAL-TO-ANALOG CONVERTER

SLAS077D - SEPTEMBER 1993 - REVISED NOVEMBER 1995

# timing requirements (see Figures 8 and 9 and Note 6)

|                  |                                 | MIN                  | MAX | UNIT |

|------------------|---------------------------------|----------------------|-----|------|

| t <sub>w1</sub>  | Pulse duration, BCK             | 160                  |     | ns   |

| t <sub>su1</sub> | Setup time, DATA before BCK↑    | 20                   |     | ns   |

| t <sub>h1</sub>  | Hold time, DATA after BCK↑      | 20                   |     | ns   |

| t <sub>su2</sub> | Setup time, LRCK before BCK↑    | 50                   |     | ns   |

| t <sub>h2</sub>  | Hold time, LRCK after BCK↑      | 50                   |     | ns   |

| t <sub>w2</sub>  | Pulse duration, SHIFT           | 100                  |     | ns   |

| t <sub>su3</sub> | Setup time, ATT before SHIFT↑   | 20                   |     | ns   |

| t <sub>h3</sub>  | Hold time, ATT after SHIFT↑     | 20                   |     | ns   |

| t <sub>w3</sub>  | Pulse duration, LATCH           | 100                  |     | ns   |

| t <sub>su4</sub> | Setup time, LATCH before SHIFT↑ | 100                  |     | ns   |

| t <sub>h4</sub>  | Hold time, LATCH after SHIFT↑   | t <sub>w2</sub> + 20 |     | ns   |

NOTE 6: All timing measurements were taken at the  $V_{\mbox{DD}}/2$  voltage level.

### PARAMETER MEASUREMENT INFORMATION

Figure 7. Analog Low-Pass Filter Recommended for Measuring the Dynamic Specifications of the TMS57014A

Figure 8. Audio-Data Serial Timing

Figure 9. Control-Data Serial Timing

# PARAMETER MEASUREMENT INFORMATION

Table 5. A-Weighted Data

| FREQUENCY | A WEIGHTING (dB) | FREQUENCY | A WEIGHTING (dB) |

|-----------|------------------|-----------|------------------|

| 25        | -44.6 ±2         | 800       | −0.1 ±1          |

| 31.5      | -39.2 ±2         | 1000      | 0 ± 0            |

| 40        | -34.5 ±2         | 1250      | 0.6 ±1           |

| 50        | -30.2 ±2         | 1600      | 1.0 ±1           |

| 63        | -26.1 ±2         | 2000      | 1.2 ±1           |

| 80        | -22.3 ±2         | 2500      | 1.2 ±1           |

| 100       | -19.1 ±1         | 3150      | 1.2 ±1           |

| 125       | -16.1 ±1         | 4000      | 1.0 ±1           |

| 160       | -13.2 ±1         | 5000      | 0.5 ±1           |

| 200       | -10.8 ±1         | 6300      | -0.1 ±1          |

| 250       | $-8.6 \pm 1$     | 8000      | -1.1 ±1          |

| 315       | -6.5 ±1          | 10000     | -2.4 ±1          |

| 400       | -4.8 ±1          | 12500     | -4.2 ±2          |

| 500       | -3.2 ±1          | 16000     | -6.5 ±2          |

| 630       | -1.9 ±1          |           |                  |

Figure 10. A-Weighted Function

#### APPLICATION INFORMATION

## circuit and layout considerations

The designer should follow these guidelines for the best device performance.

- Separate digital and analog ground planes should be used. All digital device functions should be over the

digital ground plane, and all analog device functions should be over the analog ground plane. The ground

planes should be connected at only one point to the direct power supply, and this is usually at the connector

edge of the board.

- A single crystal-controlled clock should synchronously generate all digital signals

- All power supply lines should include a  $0.1-\mu F$  and a  $1-\mu F$  capacitor. When clock noise is excessive, a toroidal inductance of 10  $\mu H$  should be placed in series with XV<sub>DD</sub> before connecting to DV<sub>DD</sub>.

- The digital input control signals should be buffered when they are generated off the card.

- Clock jitter should be minimized, and precautions taken to prevent clock overshoot. This minimizes any high-frequency coupling to the analog output.

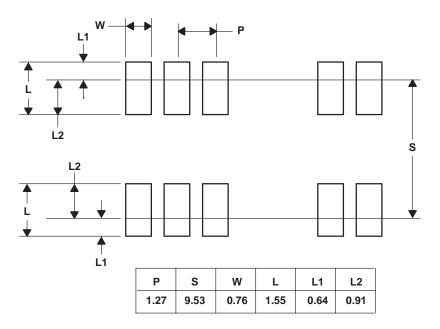

## **PCB** footprint

Figure 11 shows the printed-circuit-board (PCB) land pattern for the TMS57014A small-outline package.

NOTE A: All linear dimensions are in millimeters.

Figure 11. Land Pattern for PCB Layout

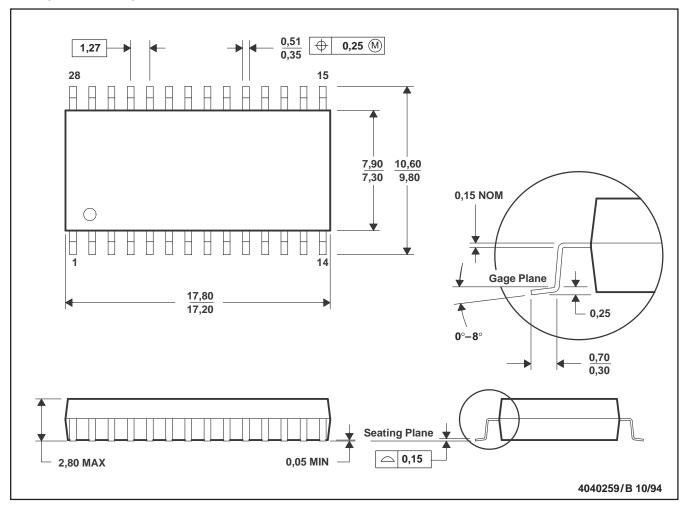

### **MECHANICAL DATA**

## DWB (R-PDSO-G28)

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions include mold flash or protrusion.

i.com 24-Jun-2005

#### PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins Package<br>Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|---------------------|-------------------------|------------------|------------------------------|

| TMS57014ADWBLE   | OBSOLETE              | SOP             | DWB                | 28                  | TBD                     | Call TI          | Call TI                      |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS) or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated