LM36923

SNVSA30A - MARCH 2015-REVISED OCTOBER 2016

# LM36923 Highly Efficient Triple-String White LED Driver

#### **Features**

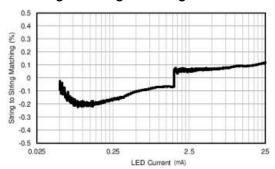

- 1% Matched Current Sinks Across (Process, Voltage, Temp)

- 3% Current Sink Accuracy Across (Process, Voltage, Temp)

- 11-Bit Dimming Resolution

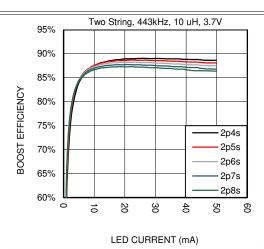

- Up to 91.6% Solution Efficiency

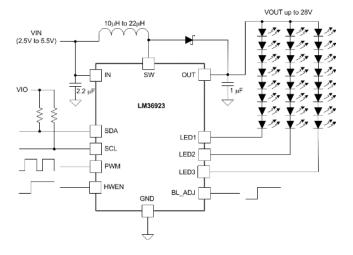

- Drives from One to Three Parallel LED Strings at up to 28 V

- **PWM Dimming Input**

- I<sup>2</sup>C Programmable

- Selectable 500-kHz and 1-MHz Switching Frequency with Optional -12% shift

- Auto Switch Frequency Mode (250 kHz, 500 kHz, 1 MHz)

- Four Configurable Overvoltage Protection Thresholds (17 V, 21 V, 25 V, 29 V)

- Four Configurable Overcurrent Protection Thresholds (750 mA, 1000 mA, 1250 mA, 1500 mA)

- Thermal Shutdown Protection

## 2 Applications

Power Source for Smart Phone and Tablet Backlighting

## 3 Description

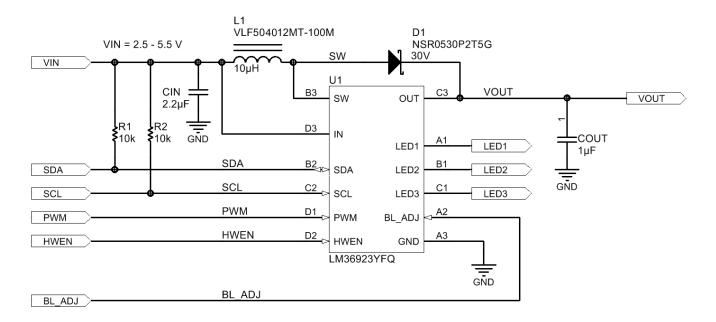

The LM36923 is an ultra-compact, highly efficient, threestring white-LED driver designed for LCD display backlighting. The device can power up to 8 series LEDs at up to 25 mA per string. An adaptive current regulation method allows for different LED voltages in each string while maintaining current regulation.

The LED current is adjusted via an I<sup>2</sup>C interface or through a logic level PWM input. The PWM duty cycle is internally sensed and mapped to an 11-bit current thus allowing for a wide range of PWM frequencies and noise-free operation.

The device operates over the 2.5-V to 5.5-V input voltage range and -40°C to 85°C temperature range.

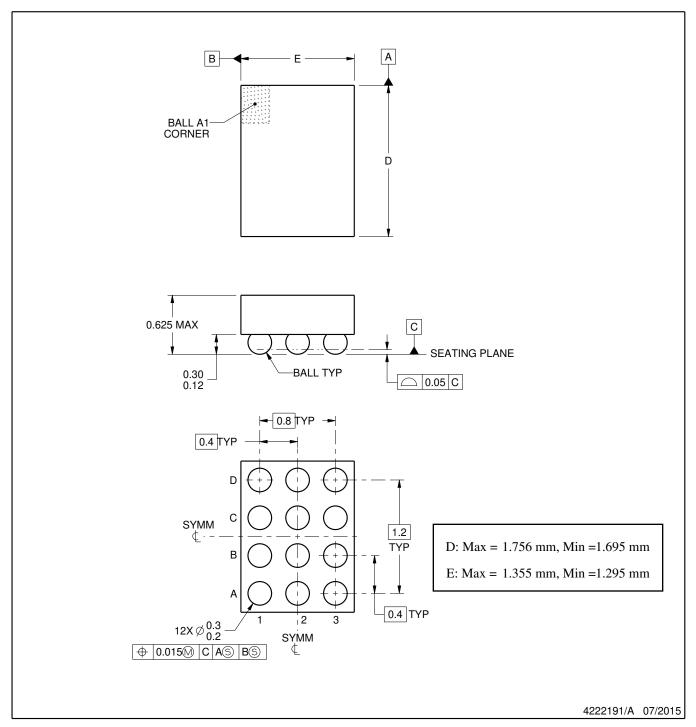

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (MAX)     |  |  |

|-------------|------------|---------------------|--|--|

| LM36923     | DSBGA (12) | 1.755 mm × 1.355 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### Simplified Schematic

## Typical String-to-String Matching vs LED Current

# **Table of Contents**

| 1 Features         1         7.5 Programming         2           2 Applications         1         7.6 Register Maps         2           3 Description         1         8 Applications and Implementation         2           4 Revision History         2         8.1 Application Information         2           5 Pin Configuration and Functions         3         8.2 Typical Application         2           6 Specifications         4         9 Power Supply Recommendations         3           6.1 Absolute Maximum Ratings         4         9.1 Input Supply Bypassing         3           6.2 ESD Ratings         4         10 Layout         3           6.3 Recommended Operating Conditions         4         10.1 Layout Guidelines         3           6.4 Thermal Information         4         10.2 Layout Example         4           6.5 Electrical Characteristics         5         11 Device and Documentation Support         4           6.7 Typical Characteristics         7         11.2 Receiving Notification of Documentation Updates         4           7.7 Detailed Description         10         11.3 Community Resources         4           7.2 Functional Block Diagram         10         11.5 Electrostatic Discharge Caution         4           7.3 Feature Description                                                                                                                                                                                                                  |   |                |    |                                                     |                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|----|-----------------------------------------------------|--------------------|

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1 | Features 1     |    | 7.5 Programming                                     | 2                  |

| 3 Description         1         8 Applications and Implementation         2           4 Revision History         2         8.1 Application Information         2           5 Pin Configuration and Functions         3         8.2 Typical Application         2           6 Specifications         4         9 Power Supply Recommendations         3           6.1 Absolute Maximum Ratings         4         9.1 Input Supply Bypassing         3           6.2 ESD Ratings         4         10 Layout         3           6.3 Recommended Operating Conditions         4         10.1 Layout Guidelines         3           6.4 Thermal Information         4         10.2 Layout Example         4           6.5 Electrical Characteristics         5         11 Device and Documentation Support         4           6.6 I²C Timing Requirements         6         11.1 Device Support         4           6.7 Typical Characteristics         7         11.2 Receiving Notification of Documentation Updates 4           7.1 Overview         10         11.3 Community Resources         4           7.2 Functional Block Diagram         10         11.5 Electrostatic Discharge Caution         4           7.3 Feature Description         11         11.6 Glossary         4           7.4 Device Functional Modes                                                                                                                                                                                                       | 2 | Applications 1 |    | 7.6 Register Maps                                   | 26                 |

| 4 Revision History       2       8.1 Application Information       2         5 Pin Configuration and Functions       3       8.2 Typical Application       2         6 Specifications       4       9 Power Supply Recommendations       3         6.1 Absolute Maximum Ratings       4       9.1 Input Supply Bypassing       3         6.2 ESD Ratings       4       10 Layout       3         6.3 Recommended Operating Conditions       4       10.1 Layout Guidelines       3         6.4 Thermal Information       4       10.2 Layout Example       4         6.5 Electrical Characteristics       5       11 Device and Documentation Support       4         6.6 I²C Timing Requirements       6       11.1 Device Support       4         6.7 Typical Characteristics       7       11.2 Receiving Notification of Documentation Updates       4         7 Detailed Description       10       11.3 Community Resources       4         7 Functional Block Diagram       10       11.4 Trademarks       4         7.2 Functional Block Diagram       10       11.5 Electrostatic Discharge Caution       4         7.3 Feature Description       11       11.6 Glossary       4         7.4 Device Functional Modes       16       12 Mechanical, Packaging, and Orderable    <                                                                                                                                                                                                                                             | 3 | • •            | 8  | Applications and Implementation                     | . 29               |

| 5 Pin Configuration and Functions         3         8.2 Typical Application         2           6 Specifications         4         9         Power Supply Recommendations         3           6.1 Absolute Maximum Ratings         4         9.1 Input Supply Bypassing         3           6.2 ESD Ratings         4         10.1 Layout         10.1 Layout Guidelines         3           6.3 Recommended Operating Conditions         4         10.2 Layout Example         3           6.4 Thermal Information         4         10.2 Layout Example         4           6.5 Electrical Characteristics         5         1         Device and Documentation Support         4           6.6 I <sup>2</sup> C Timing Requirements         6         11.1 Device Support         4           6.7 Typical Characteristics         7         11.2 Receiving Notification of Documentation Updates         4           7 Detailed Description         10         11.3 Community Resources         4           7 Indicate Provided Provi | 4 |                |    | 8.1 Application Information                         | 29                 |

| 6 Specifications       4       9 Power Supply Recommendations       3         6.1 Absolute Maximum Ratings       4       9.1 Input Supply Bypassing       3         6.2 ESD Ratings       4       10 Layout       3         6.3 Recommended Operating Conditions       4       10.1 Layout Guidelines       3         6.4 Thermal Information       4       10.2 Layout Example       4         6.5 Electrical Characteristics       5       11 Device and Documentation Support       4         6.6 I²C Timing Requirements       6       11.1 Device Support       4         6.7 Typical Characteristics       7       11.2 Receiving Notification of Documentation Updates 4         7 Detailed Description       10       11.3 Community Resources       4         7 Functional Block Diagram       10       11.5 Electrostatic Discharge Caution       4         7.3 Feature Description       11       11.6 Glossary       4         7.4 Device Functional Modes       16       12 Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | - | -              |    | 8.2 Typical Application                             | 29                 |

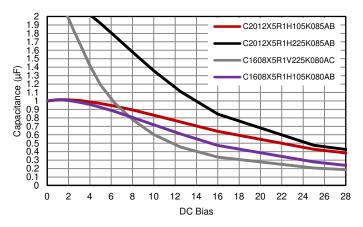

| 6.1 Absolute Maximum Ratings       4         6.2 ESD Ratings       4         6.3 Recommended Operating Conditions       4         6.4 Thermal Information       4         6.5 Electrical Characteristics       5         6.6 I <sup>2</sup> C Timing Requirements       6         6.7 Typical Characteristics       7         7 Detailed Description       10         7.1 Overview       10         7.2 Functional Block Diagram       10         7.3 Feature Description       11         7.4 Device Functional Modes       16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _ | <u> </u>       | 9  | Power Supply Recommendations                        | . 37               |

| 6.2 ESD Ratings       4         6.3 Recommended Operating Conditions       4         6.4 Thermal Information       4         6.5 Electrical Characteristics       5         6.6 I²C Timing Requirements       6         6.7 Typical Characteristics       7         7 Detailed Description       10         7.1 Overview       10         7.2 Functional Block Diagram       10         7.3 Feature Description       11         7.4 Device Functional Modes       16     10 Layout Example  10.2 Layout Example  10.3 Layout Example  10.4 Layout Example  10.5 Layout Example  10.6 Layout Example  10.7 Layout Example  11.1 Device Support  11.2 Receiving Notification of Documentation Updates  11.3 Community Resources  11.4 Trademarks  11.5 Electrostatic Discharge Caution  11.5 Electrostatic Discharge Caution  11.6 Glossary  11.6 Glossary  11.6 Glossary  11.7 Mechanical, Packaging, and Orderable         10       10         11       Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | • |                |    | 9.1 Input Supply Bypassing                          | 37                 |

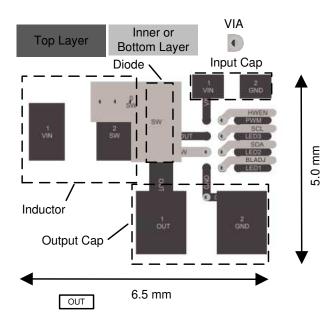

| 6.3       Recommended Operating Conditions       4       10.1       Layout Guidelines       3         6.4       Thermal Information       4       10.2       Layout Example       4         6.5       Electrical Characteristics       5       11       Device and Documentation Support       4         6.6       I²C Timing Requirements       6       11.1       Device Support       4         6.7       Typical Characteristics       7       11.2       Receiving Notification of Documentation Updates 4         7       Detailed Description       10       11.3       Community Resources       4         7.1       Overview       10       11.4       Trademarks       4         7.2       Functional Block Diagram       10       11.5       Electrostatic Discharge Caution       4         7.3       Feature Description       11       11.6       Glossary       4         7.4       Device Functional Modes       16       12       Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | · ·            | 10 |                                                     |                    |

| 6.4 Thermal Information       4       10.2 Layout Example       4         6.5 Electrical Characteristics       5       11 Device and Documentation Support       4         6.6 I²C Timing Requirements       6       11.1 Device Support       4         6.7 Typical Characteristics       7       11.2 Receiving Notification of Documentation Updates 4         7 Detailed Description       10       11.3 Community Resources       4         7.1 Overview       10       11.4 Trademarks       4         7.2 Functional Block Diagram       10       11.5 Electrostatic Discharge Caution       4         7.3 Feature Description       11       11.6 Glossary       4         7.4 Device Functional Modes       16       12 Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |                |    |                                                     |                    |

| 6.5       Electrical Characteristics       5         6.6       I²C Timing Requirements       6         6.7       Typical Characteristics       7         7       Detailed Description       10         7.1       Overview       10         7.2       Functional Block Diagram       10         7.3       Feature Description       11         7.4       Device Functional Modes       16     11 Device and Documentation Support  11.1 Device Support  11.2 Receiving Notification of Documentation Updates 4  11.3 Community Resources  11.4 Trademarks  11.5 Electrostatic Discharge Caution  11.5 Electrostatic Discharge Caution  11.6 Glossary  11.6 Glossary  11.7 Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 3              |    | 10.2 Layout Example                                 | 40                 |

| 6.6       I²C Timing Requirements       6       11.1       Device Support       4         6.7       Typical Characteristics       7       11.2       Receiving Notification of Documentation Updates 4         7       Detailed Description       10       11.3       Community Resources       4         7.1       Overview       10       11.4       Trademarks       4         7.2       Functional Block Diagram       10       11.5       Electrostatic Discharge Caution       4         7.3       Feature Description       11       11.6       Glossary       4         7.4       Device Functional Modes       16       12       Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |                | 11 | Device and Documentation Support                    | . 41               |

| 6.7 Typical Characteristics       7       11.2 Receiving Notification of Documentation Updates 4         7 Detailed Description       10       11.3 Community Resources       4         7.1 Overview       10       11.4 Trademarks       4         7.2 Functional Block Diagram       10       11.5 Electrostatic Discharge Caution       4         7.3 Feature Description       11       11.6 Glossary       4         7.4 Device Functional Modes       16       12 Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |                |    | 11.1 Device Support                                 | . 41               |

| 7       Detailed Description       10       11.3 Community Resources       4         7.1 Overview       10       11.4 Trademarks       4         7.2 Functional Block Diagram       10       11.5 Electrostatic Discharge Caution       4         7.3 Feature Description       11       11.6 Glossary       4         7.4 Device Functional Modes       16       12 Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |                |    | 11.2 Receiving Notification of Documentation Update | s <mark>4</mark> 1 |

| 7.1 Overview       10       11.4 Trademarks       4         7.2 Functional Block Diagram       10       11.5 Electrostatic Discharge Caution       4         7.3 Feature Description       11       11.6 Glossary       4         7.4 Device Functional Modes       16       12 Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7 |                |    | 11.3 Community Resources                            | 41                 |

| 7.2 Functional Block Diagram 10 11.5 Electrostatic Discharge Caution 4 7.3 Feature Description 11 11.6 Glossary 4 7.4 Device Functional Modes 16 12 Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | - |                |    | 11.4 Trademarks                                     | 41                 |

| 7.3 Feature Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |                |    | 11.5 Electrostatic Discharge Caution                | 41                 |

| 7.4 Device Functional Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | g .            |    | 11.6 Glossary                                       | 41                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |                | 12 |                                                     | . 4                |

# 4 Revision History

| CI | changes from Original (March 2015) to Revision A Page   |    |  |  |  |  |

|----|---------------------------------------------------------|----|--|--|--|--|

| •  | Changed pin name "VOUT" to "OUT"                        | 3  |  |  |  |  |

| •  | Changed pin name in Layout Example from 'VOUT' to 'OUT' | 39 |  |  |  |  |

Submit Documentation Feedback

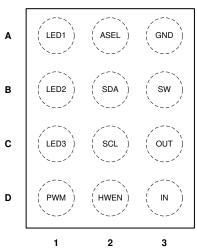

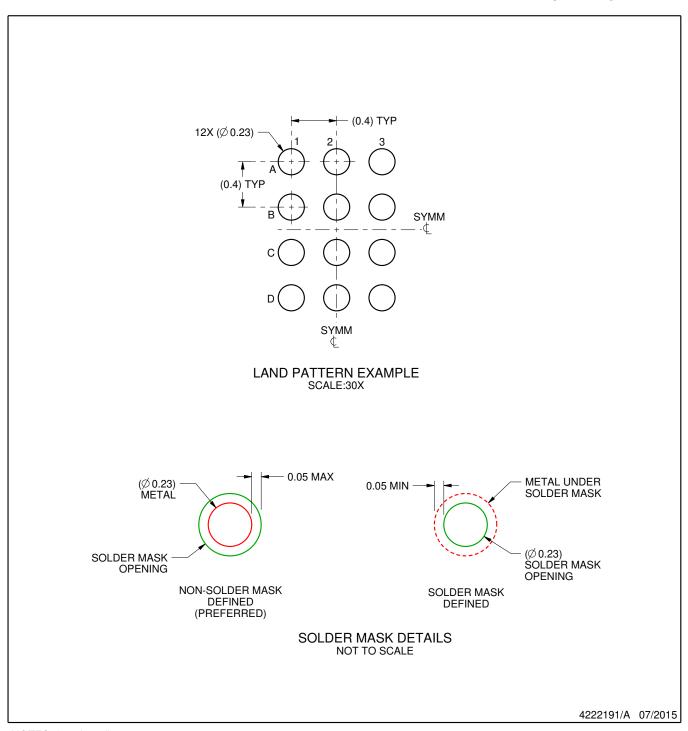

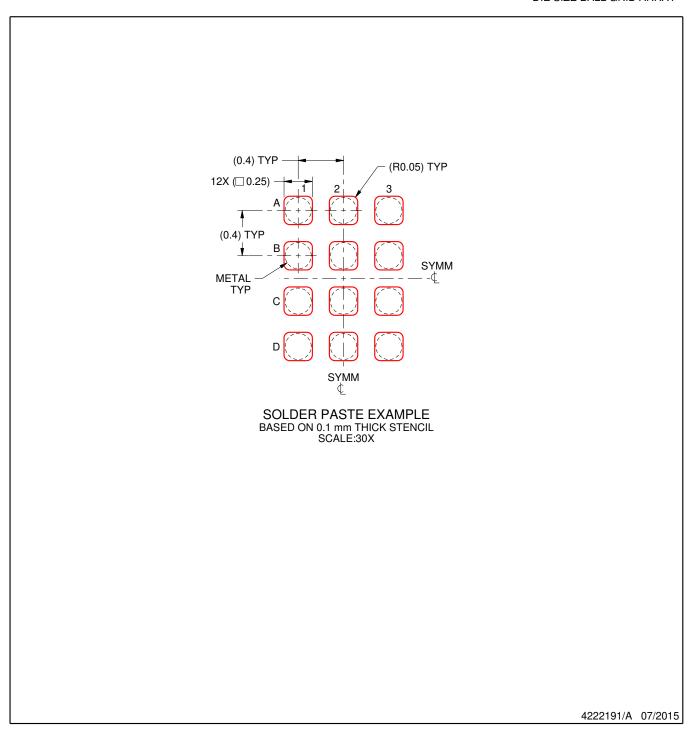

# 5 Pin Configuration and Functions

## **Pin Functions**

| D      | IN I   |        |                                                                                                                                         |

|--------|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------|

| PIN    |        | I/O    | DESCRIPTION                                                                                                                             |

| NUMBER | NAME   | ., 0   | 22331111 11311                                                                                                                          |

| A1     | LED1   | Input  | Input to current sink 1. The boost converter regulates the minimum voltage between LED1, LED2, LED3 to VHR.                             |

| A2     | BL_ADJ | Input  | LED current adjust input. When BL_ADJ is driven to a logic high voltage the LED current steps down to the programmed low current value. |

| А3     | GND    | Input  | Ground                                                                                                                                  |

| B1     | LED2   | Input  | Input pin to current sink 2. The boost converter regulates the minimum voltage between LED1, LED2 ,LED3 to VHR.                         |

| B2     | SDA    | I/O    | Data I/O for I <sup>2</sup> C-Compatible Interface.                                                                                     |

| В3     | SW     | Output | Drain Connection for internal low side NFET, and anode connection for external Schottky diode.                                          |

| C1     | LED3   | Input  | Input pin to current sink 3. The boost converter regulates the minimum voltage between LED1, LED2, LED3 to VHR.                         |

| C2     | SCL    | Input  | Clock Input for I <sup>2</sup> C-compatible interface.                                                                                  |

| C3     | OUT    | Input  | OUT serves as the sense point for overvoltage protection. Connect OUT to the positive pin of the output capacitor.                      |

| D1     | PWM    | Input  | Logic level input for PWM current control.                                                                                              |

| D2     | HWEN   | Input  | Hardware enable input. Drive HWEN high to bring the device out of shutdown and allow $I^2C$ writes or PWM control.                      |

| D3     | IN     | Input  | Input voltage connection. Bypass IN to GND with a minimum 2.2-μF ceramic capacitor.                                                     |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                |                                | MIN        | MAX | UNIT |

|--------------------------------|--------------------------------|------------|-----|------|

| IN                             | Input voltage                  | -0.3       | 6   | V    |

| OUT                            | Output overvoltage sense input | -0.3       | 30  | ٧    |

| SW                             | Inductor connection            | -0.3       | 30  | ٧    |

| LED1, LED2, LED3               | LED string cathode connection  | -0.3       | 30  | ٧    |

| HWEN, PWM, SDA,<br>SCL, BL_ADJ | Logic I/Os                     | -0.3       | 6   | V    |

| Maximum junction temp          | perature, T <sub>J_MAX</sub>   |            | 150 | °C   |

| Storage temperature, T         | -<br>stg                       | _65 150 °C |     |      |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |               |                                                                     | VALUE | UNIT |

|--------------------|---------------|---------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>   | ±2000 |      |

|                    | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as ±2000 V may actually have higher performance.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                |                               | MIN | MAX  | UNIT |

|--------------------------------|-------------------------------|-----|------|------|

| IN                             | Input voltage                 | 2.5 | 5.5  | V    |

| OUT                            | Overvoltage sense input       | 0   | 29.5 | V    |

| SW                             | Inductor connection           | 0   | 29.5 | ٧    |

| LED1, LED2, LED3               | LED string cathode connection | 0   | 29.5 | ٧    |

| HWEN, PWM, SDA,<br>SCL, BL_ADJ | Logic I/Os                    | 0   | 5.5  | ٧    |

## 6.4 Thermal Information

|                                   | THERMAL METRIC <sup>(1)</sup>                | YFQ (DSBGA)<br>12 PINS | UNIT |

|-----------------------------------|----------------------------------------------|------------------------|------|

| $R_{\theta JA}$                   | Junction-to-ambient thermal resistance       | 88.9                   |      |

| $R_{\theta JC(top)}$              | Junction-to-case (top) thermal resistance    | 0.7                    |      |

| $R_{\theta JB}$                   | Junction-to-board thermal resistance         | 43.9                   | °C/W |

| $\Psi_{	heta 	extsf{J}	extsf{T}}$ | Junction-to-top characterization parameter   | 2.9                    |      |

| $\Psi_{\thetaJB}$                 | Junction-to-board characterization parameter | 43.7                   |      |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Pins listed as ±500 V may actually have higher performance.

## 6.5 Electrical Characteristics

Limits apply over the full operating ambient temperature range ( $-40^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}$ ) and  $V_{IN} = 3.6 \text{ V}$ , typical values are at  $T_{A} = 25^{\circ}\text{C}$  (unless otherwise noted).

|                        | PARAMETER                                                                      | TEST CONDI                                                                          | TIONS                      | MIN  | TYP           | MAX   | UNI |  |

|------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------|------|---------------|-------|-----|--|

| BOOST                  |                                                                                |                                                                                     |                            |      |               |       |     |  |

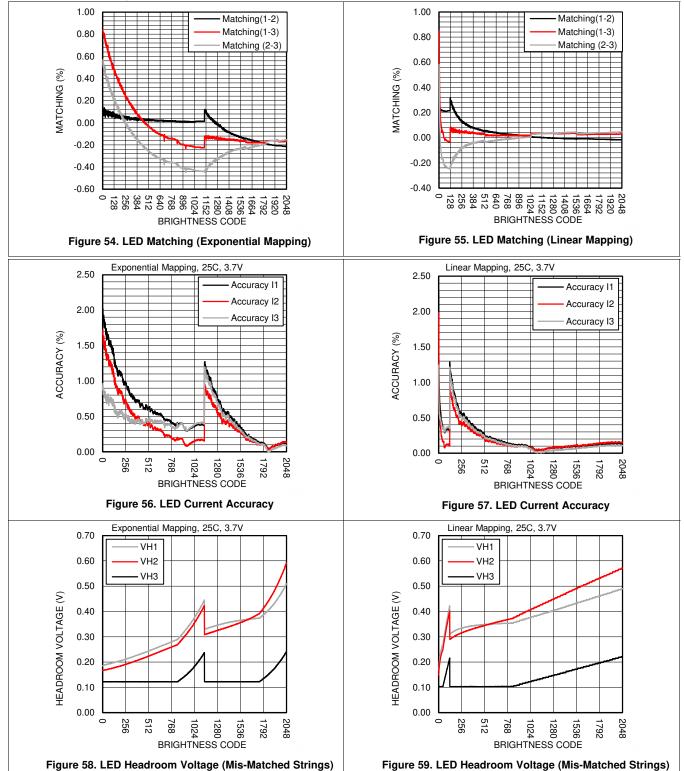

| I <sub>MATCH</sub> (1) | LED current matching $I_{LED1}$ to $I_{LED2}$ to $I_{LED3}$                    | 50 $\mu$ A $\leq$ I <sub>LED</sub> $\leq$ 25 mA, 2.7 (linear or exponential mode    |                            | -1%  | 0.1%          | 1%    |     |  |

| Accuracy               | Absolute Accuracy (I <sub>LED1</sub> , I <sub>LED2</sub> , I <sub>LED3</sub> ) | 50 μA $\leq$ I <sub>LED</sub> $\leq$ 25 mA, 2.7 (linear or exponential mode         |                            | -3%  | 0.1%          | 3%    |     |  |

| I <sub>LED_MIN</sub>   | Minimum LED current (per string)                                               | PWM or I <sup>2</sup> C current contro                                              | l (linear or               |      | 50            |       | μΑ  |  |

| I <sub>LED_MAX</sub>   | Maximum LED current (per string)                                               | exponential mode)                                                                   | T (IIII)Call OI            |      | 25            |       | mA  |  |

| R <sub>DNL</sub>       | IDAC ratio-metric DNL                                                          | exponential mode only                                                               |                            |      | 1/3<br>(0.3%) |       | LSE |  |

| .,                     | Regulated current sink                                                         | I <sub>LED</sub> = 25 mA                                                            |                            |      | 210           |       |     |  |

| $V_{HR}$               | headroom voltage                                                               | I <sub>LED</sub> = 5 mA                                                             |                            |      | 100           |       | m۷  |  |

| V <sub>HR_MIN</sub>    | Current sink minimum headroom voltage                                          | $I_{LED} = 95\%$ of nominal, $I_{LEI}$                                              | <sub>O</sub> = 5 mA        |      | 35            | 50    | m۷  |  |

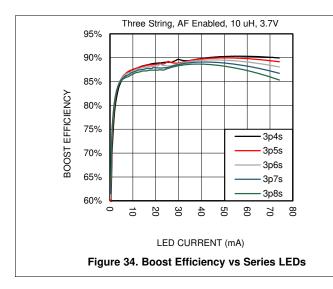

| Efficiency             | Typical efficiency                                                             | V <sub>IN</sub> = 3.7 V, I <sub>LED</sub> = 5 mA/st<br>Application circuit (3x7 LEI |                            |      | 87%           |       |     |  |

| R <sub>NMOS</sub>      | NMOS switch on resistance                                                      | I <sub>SW</sub> = 250 mA                                                            |                            |      | 0.25          |       | Ω   |  |

|                        | NMOS switch current limit                                                      |                                                                                     | OCP = 00                   | 575  | 750           | 875   |     |  |

| I                      |                                                                                | 2.7 V ≤ V <sub>IN</sub> ≤ 5 V                                                       | OCP = 01                   | 860  | 1000          | 1110  | mA  |  |

| I <sub>CL</sub>        |                                                                                |                                                                                     | OCP = 10                   | 1100 | 1250          | 1400  |     |  |

|                        |                                                                                |                                                                                     | OCP = 11                   | 1350 | 1500          | 1650  |     |  |

|                        | Output overvoltage protection                                                  |                                                                                     | OVP = 00                   | 16   | 17            | 17.5  | V   |  |

| $V_{OVP}$              |                                                                                | ON threshold, 2.7 V ≤ V <sub>IN</sub> ≤ 5 V                                         | OVP = 01                   | 20   | 21            | 21.5  |     |  |

| VOVP                   |                                                                                |                                                                                     | OVP = 10                   | 24   | 25            | 25.5  |     |  |

|                        |                                                                                |                                                                                     | OVP = 11                   | 28   | 29            | 29.5  |     |  |

| OVP<br>Hysteresis      |                                                                                |                                                                                     |                            |      | 0.5           |       | V   |  |

| $f_{\sf SW}$           | Switching frequency                                                            | 2.7 V ≤ V <sub>IN</sub> ≤ 5 V, boost frequency                                      | Boost frequency select = 0 | 475  | 500           | 525   | kH: |  |

| J 5W                   | Switching frequency                                                            | shift = 0                                                                           | Boost frequency select = 1 | 950  | 1000          | 1050  | MIZ |  |

| D <sub>MAX</sub>       | Maximum boost duty cycle                                                       |                                                                                     |                            | 92%  | 94%           |       |     |  |

| I <sub>SHDN</sub>      | Shutdown current                                                               | Chip enable bit = 0, SDA = $2.7 \text{ V} \le \text{V}_{\text{IN}} \le 5 \text{ V}$ | SCL = IN or GND,           |      | 1.2           | 5     | μΑ  |  |

| T <sub>SD</sub>        | Thermal shutdown                                                               |                                                                                     |                            |      | 135           |       | °C  |  |

|                        | Hysteresis                                                                     |                                                                                     |                            |      | 15            |       |     |  |

| PWM INPU               | Т                                                                              | 1                                                                                   |                            |      |               | 50    |     |  |

| $Min f_{PWM}$          |                                                                                | 0 1 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                                             |                            |      |               | 50    | Hz  |  |

| $Max f_{PWM}$          |                                                                                | Sample rate = 24 MHz                                                                |                            | 50   |               | 100 - | kH  |  |

|                        | M                                                                              | Sample rate = 24 MHz                                                                |                            |      |               | 183.3 | ns  |  |

| t <sub>MIN_ON</sub>    | Minimum pulse ON time                                                          | Sample rate = 4 MHz                                                                 |                            |      |               | 1100  |     |  |

|                        |                                                                                | Sample rate = 800 kHz                                                               |                            |      |               | 5500  |     |  |

|                        | Malassas and OFF C                                                             | Sample rate = 24 MHz                                                                |                            |      |               | 183.3 |     |  |

| t <sub>MIN_OFF</sub>   | Minimum pulse OFF time                                                         | Sample rate = 4 MHz                                                                 |                            |      |               | 1100  | ns  |  |

|                        |                                                                                | Sample rate = 800 kHz                                                               |                            |      |               | 5500  |     |  |

<sup>(1)</sup> LED Current Matching between strings is given as the worst case matching between any two strings. Matching is calculated as ((I<sub>LEDX</sub> – I<sub>LEDY</sub>)/(I<sub>LEDX</sub> + I<sub>LEDY</sub>) × 100.

## **Electrical Characteristics (continued)**

Limits apply over the full operating ambient temperature range ( $-40^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}$ ) and  $V_{IN} = 3.6 \text{ V}$ , typical values are at  $T_{A} = 25^{\circ}\text{C}$  (unless otherwise noted).

|                       | PARAMETER                                   | TEST CONDITIONS                                                                                     | MIN  | TYP | MAX             | UNIT |

|-----------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------|------|-----|-----------------|------|

| t <sub>START-UP</sub> | Turn-on delay from shutdown to backlight on | PWM input active, PWM = logic high,HWEN input from low to high, $f_{PWM}$ = 10 kHz (50% duty cycle) |      | 3.5 | 5               | ms   |

| PWM <sub>RES</sub>    | PWM input resolution                        | 1.6 kHz $\leq f_{\rm PWM} \leq$ 12 kHz, PWM hysteresis = 00, PWM sample rate = 11                   |      |     | 11              | bits |

| V <sub>IH</sub>       | Input logic high                            | HWEN, BL_ADJ, SCL, SDA, PWM inputs                                                                  | 1.25 |     | V <sub>IN</sub> | V    |

| V <sub>IL</sub>       | Input logic low                             | HWEN, BL_ADJ, SCL, SDA, PWM inputs                                                                  | 0    |     | 0.4             | V    |

|                       | PWM input glitch rejection                  | PWM pulse filter = 00                                                                               |      | 0   | 15              |      |

|                       |                                             | PWM pulse filter = 01                                                                               | 60   | 100 | 140             | 20   |

| t <sub>GLITCH</sub>   |                                             | PWM pulse filter = 10                                                                               | 90   | 150 | 210             | ns   |

|                       |                                             | PWM pulse filter = 11                                                                               | 120  | 200 | 280             |      |

|                       |                                             | Sample rate = 24 MHz                                                                                | 0.54 | 0.6 | 0.66            |      |

| t <sub>PWM STBY</sub> | PWM shutdown period                         | Sample rate = 4 MHz                                                                                 | 2.7  | 3   | 3.3             | ms   |

|                       |                                             | Sample rate = 800 kHz                                                                               | 22.5 | 25  | 27.5            |      |

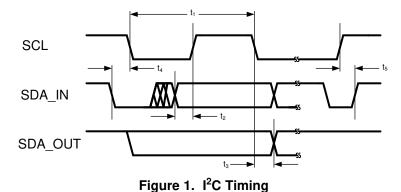

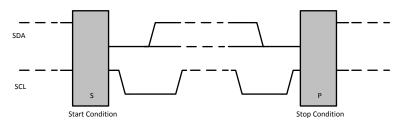

# 6.6 I<sup>2</sup>C Timing Requirements

|    |                                          | MIN | TYP | MAX | UNIT |

|----|------------------------------------------|-----|-----|-----|------|

| t1 | SCL clock period                         | 2.5 |     |     | μs   |

| t2 | Data in setup time to SCL high           | 100 |     |     | ns   |

| t3 | Data out stable after SCL low            | 0   |     |     | ns   |

| t4 | SDA low Setup Time to SCL low (start)    | 100 |     |     | ns   |

| t5 | SDA high hold time after SCL high (stop) | 100 |     |     | ns   |

Submit Documentation Feedback

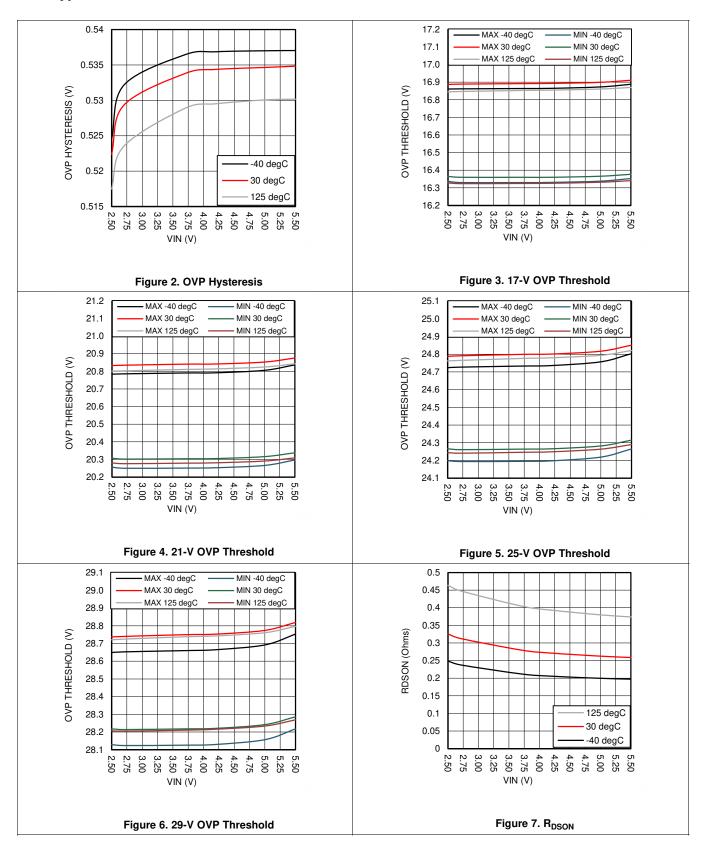

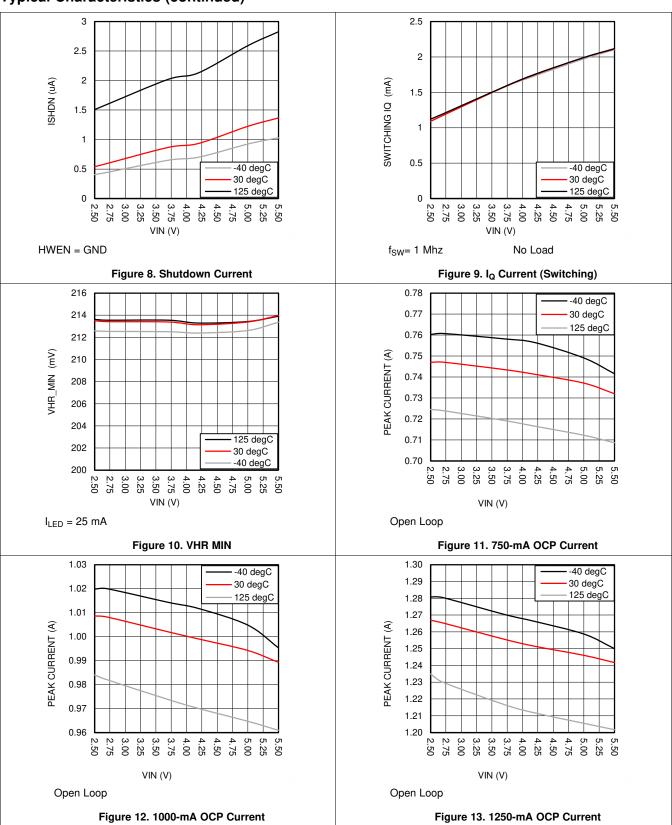

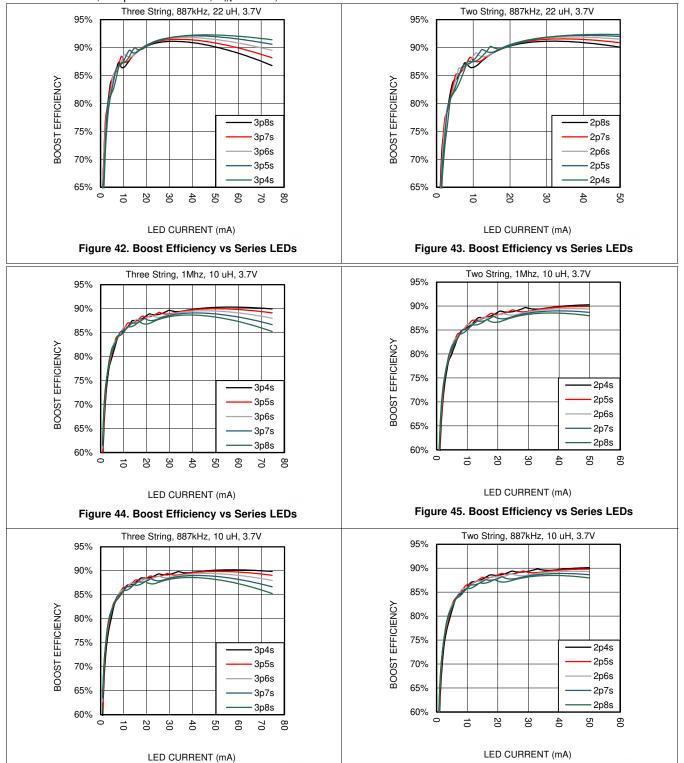

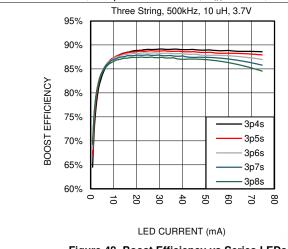

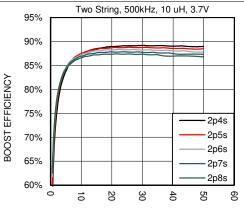

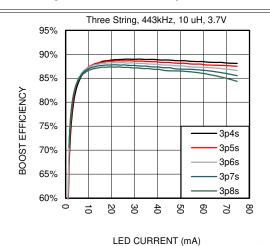

## 6.7 Typical Characteristics

# TEXAS INSTRUMENTS

## **Typical Characteristics (continued)**

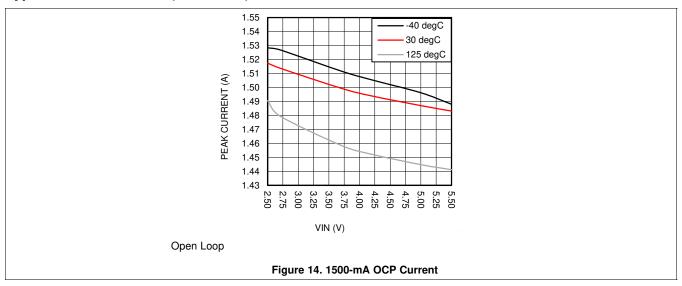

# **Typical Characteristics (continued)**

Submit Documentation Feedback

## 7 Detailed Description

#### 7.1 Overview

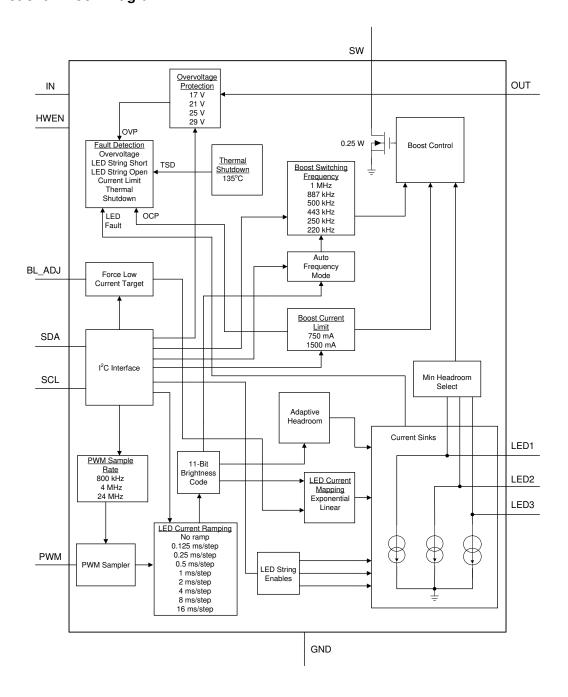

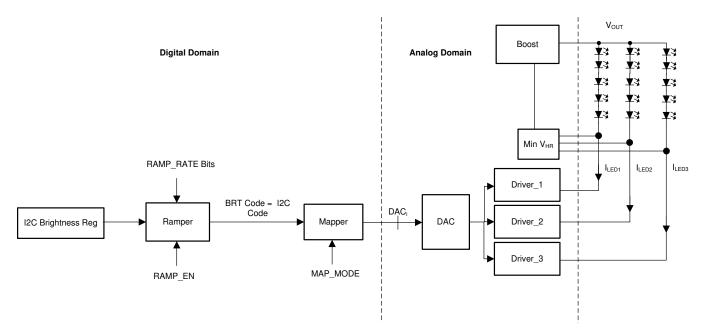

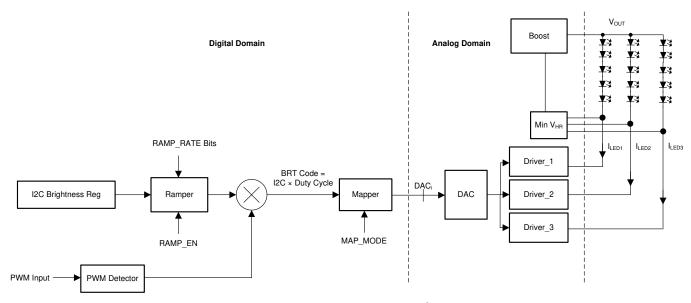

The LM36923 is an inductive boost plus 3 current sink white-LED driver designed for powering from one to three strings of white LEDs used in display backlighting. The device operates over the 2.5-V to 5.5-V input voltage range. The 11-bit LED current is set via an I<sup>2</sup>C interface, via a logic level PWM input, or a combination of both.

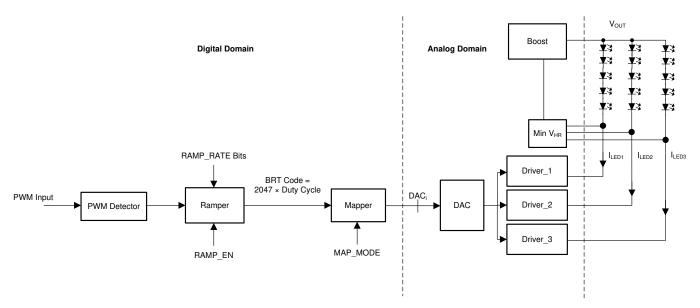

## 7.2 Functional Block Diagram

Submit Documentation Feedback

## 7.3 Feature Description

#### 7.3.1 Enabling the LM36923

The LM36923 has a logic level input HWEN which serves as the master enable/disable for the device. When HWEN is low the device is disabled, the registers are reset to their default state, the I<sup>2</sup>C bus is inactive, and the device is placed in a low-power shutdown mode. When HWEN is forced high the device is enabled, and I<sup>2</sup>C writes are allowed to the device.

#### 7.3.1.1 Current Sink Enable

Each current sink in the device has a separate enable input. This allows for a 1-string, 2-string, or 3-string application. The default is with three strings enabled. Once the correct LED string configuration is programmed, the device can be enabled by writing the chip enable bit high (register 0x10 bit[0]), and then either enabling PWM and driving PWM high, or writing a non-zero code to the brightness registers.

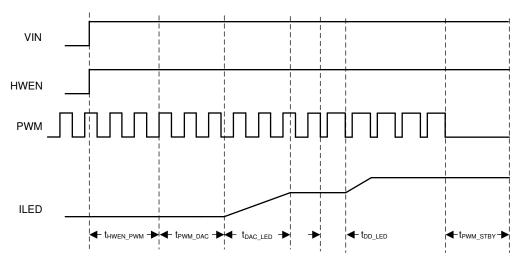

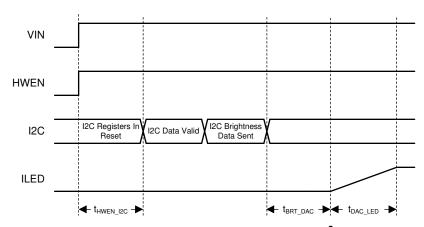

The default setting for the device is with the chip enable bit set to 1, PWM input enabled, and the device in linear mapped mode. Therefore, on power up once HWEN is driven high, the device enters the standby state and actively monitors the PWM input. After a non-zero PWM duty cycle is detected the LM36923 converts the duty cycle information to the linearly weighted 11-bit brightness code. This allows for operation of the device in a stand-alone configuration without the need for any I<sup>2</sup>C writes. Figure 15 and Figure 16 describe the start-up timing for operation with both PWM controlled current and with I<sup>2</sup>C controlled current.

Figure 15. Enabling the LM36923 via PWM

Figure 16. Enabling the LM36923 via I<sup>2</sup>C

Product Folder Links: *LM36923*

Copyright © 2015-2016, Texas Instruments Incorporated

## **Feature Description (continued)**

#### 7.3.2 LM36923 Start-Up

The LM36923 can be enabled or disabled in various ways. When disabled, the device is considered shutdown, and the quiescent current drops to I<sub>SHDN</sub>. When the device is in standby, it returns to the I<sub>SHDN</sub> current level retaining all programmed register values. Table 1 describes the different operating states for the LM36923.

Table 1. LM36923 Operating Modes

|                                         |            | I <sup>2</sup> C                                            |                                      |                                 | LED CUF                                                             | RRENT                                                                   |

|-----------------------------------------|------------|-------------------------------------------------------------|--------------------------------------|---------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------|

| LED STRING<br>ENABLES<br>0x10 bits[3:1] | PWM INPUT  | BRIGHTNESS<br>REGISTERS<br>0x18 bits[2:0]<br>0x19 bits[7:0] | BRIGHTNESS<br>MODE<br>0x11 bits[6:5] | DEVICE<br>ENABLE<br>0x10 bit[0] | (EXP MAPPING)<br>0x11 bit[7] = 1                                    | (LIN MAPPING)<br>0x11 bit[7] = 0                                        |

| XXX                                     | X          | XXX                                                         | XX                                   | 0                               | Off, device                                                         | disabled                                                                |

| 0                                       | X          | XXX                                                         | XX                                   | 1                               | Off, device                                                         | standby                                                                 |

| At least one enabled                    | Х          | 0                                                           | 00                                   | 1                               | Off, device i                                                       | n standby                                                               |

| At least one enabled                    | X          | Code > 000                                                  | 00                                   | 1                               | $I_{LED} = 50\mu A \times 1.003040572^{Code}$<br>See <sup>(1)</sup> | $I_{LED} = 37.806\mu A + 12.195\mu A \times Code$<br>See (1)            |

| At least one enabled                    | 0          | XXX                                                         | 01                                   | 1                               | Off, device in standby                                              |                                                                         |

| At least one enabled                    | PWM Signal | XXX                                                         | 01                                   | 1                               | $I_{LED} = 50\mu A \times 1.003040572^{Code}$<br>See <sup>(1)</sup> | $I_{LED} = 37.806\mu A + 12.195\mu A \times Code$<br>See <sup>(1)</sup> |

| At least one enabled                    | 0          | XXX                                                         | 10 or 11                             | 1                               | Off, device in standby                                              |                                                                         |

| At least one enabled                    | Х          | 0                                                           | 10 or 11                             | 1                               | Off, device in standby                                              |                                                                         |

| At least one enabled                    | PWM Signal | Code > 000                                                  | 10 or 11                             | 1                               | $I_{LED} = 50\mu A \times 1.003040572^{Code}$<br>See <sup>(1)</sup> | $I_{LED} = 37.806\mu A + 12.195\mu A \times Code$<br>See <sup>(1)</sup> |

<sup>(1)</sup> Code is the 11-bit code output from the ramper (see Figure 21, Figure 23, Figure 25, Figure 27). This can be the I<sup>2</sup>C brightness code, the converted PWM duty cycle or the 11-bit product of both.

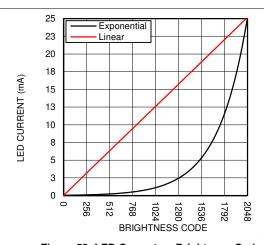

#### 7.3.3 Brightness Mapping

There are two different ways to map the brightness code (or PWM duty cycle) to the LED current: linear and exponential mapping.

#### 7.3.3.1 Linear Mapping

For linear mapped mode the LED current increases proportionally to the 11-bit brightness code and follows the relationship:

$$I_{LED} = 37.806\mu A + 12.195\mu A \times Code$$

(1)

This is valid from codes 1 to 2047. Code 0 programs 0 current. Code is an 11-bit code that can be the I<sup>2</sup>C brightness code, the digitized PWM duty cycle, or the product of the two.

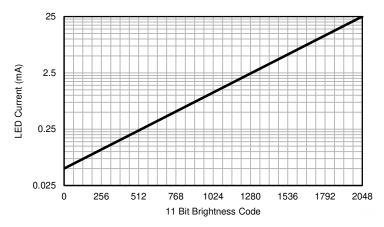

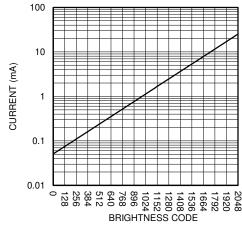

## 7.3.3.2 Exponential Mapping

In exponential mapped mode the LED current follows the relationship:

$$I_{LED} = 50\mu A \times 1.003040572^{Code} \tag{2}$$

This results in an LED current step size of approximately 0.304% per code. This is valid for codes from 1 to 2047. Code 0 programs 0 current. Code is an 11-bit code that can be the I<sup>2</sup>C brightness code, the digitized PWM duty cycle, or the product of the two. Figure 17 details the LED current exponential response.

The 11-bit (0.304%) per code step is small enough such that the transition from one code to the next in terms of LED brightness is not distinguishable to the eye. This therefore gives a perfectly smooth brightness increase between adjacent codes.

Figure 17. LED Current vs Brightness Code (Exponential Mapping)

## 7.3.4 PWM Input

The PWM input is a sampled input which converts the input duty cycle information into an 11-bit brightness code. The use of a sampled input eliminates any noise and current ripple that traditional PWM controlled LED drivers are susceptible to.

The PWM input uses logic level thresholds with  $V_{IH\_MIN} = 1.25 \text{ V}$  and  $V_{IL\_MAX} = 0.4 \text{ V}$ . Since this is a sampled input, there are limits on the max PWM input frequency as well as the resolution that can be achieved.

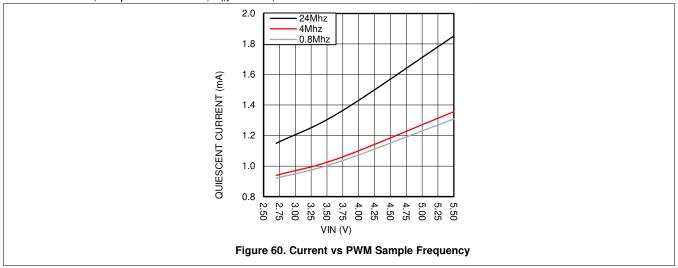

## 7.3.4.1 PWM Sample Frequency

There are four selectable sample rates for the PWM input. The choice of sample rate depends on three factors:

- 1. Required PWM Resolution (input duty cycle to brightness code, with 11 bits max)

- 2. PWM Input Frequency

- 3. Efficiency

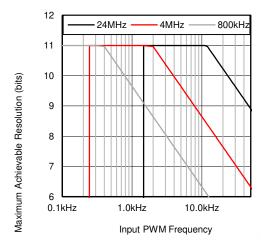

#### 7.3.4.1.1 PWM Resolution and Input Frequency Range

The PWM input frequency range is 50 Hz to 50 kHz. To achieve the full 11-bit maximum resolution of PWM duty cycle to the LED brightness code (BRT), the input PWM duty cycle must be  $\geq$  11 bits, and the PWM sample period (1/ $f_{\text{SAMPLE}}$ ) must be smaller than the minimum PWM input pulse width. Figure 18 shows the possible brightness code resolutions based on the input PWM frequency. The minimum PWM frequency for each PWM sample rate is described in *PWM Timeout*.

Figure 18. PWM Sample Rate, Resolution, and PWM Input Frequency

#### 7.3.4.1.2 PWM Sample Rate and Efficiency

Efficiency is maximized when the lowest  $f_{SAMPLE}$  is chosen since this lowers the quiescent operating current of the device. Table 2 describes the typical efficiency tradeoffs for the different sample clock settings.

**Table 2. PWM Sample Rate Trade-Offs**

| PWM SAMPLE RATE<br>(f <sub>SAMPLE</sub> ) | TYPICAL INPUT CURRENT, DEVICE ENABLED I <sub>LED</sub> = 10 mA/string, 2 x 7 LEDs | TYPICAL EFFICIENCY       |

|-------------------------------------------|-----------------------------------------------------------------------------------|--------------------------|

| (0x12 Bits[7:6])                          | $f_{SW}$ = 1 MHz                                                                  | $V_{IN} = 3.7 \text{ V}$ |

| 0                                         | 1.03 mA                                                                           | 90.7%                    |

| 1                                         | 1.05 mA                                                                           | 90.6%                    |

| 1X                                        | 1.35 mA                                                                           | 90.4%                    |

## 7.3.4.1.2.1 PWM Sample Rate Example

The number of bits of resolution on the PWM input varies according to the PWM Sample rate and PWM input frequency.

Table 3. PWM Resolution vs PWM Sample Rate

| PWM<br>FREQUENCY<br>(kHz) | RESOLUTION (PWM SAMPLE RATE = 800 kHz) (PWM SAMPLE RATE = 4 MHz) |     | RESOLUTION<br>(PWM SAMPLE RATE = 24 MHz) |  |

|---------------------------|------------------------------------------------------------------|-----|------------------------------------------|--|

| 0.4                       | 11                                                               | 11  | 11                                       |  |

| 2                         | 8.6                                                              | 11  | 11                                       |  |

| 12                        | 6.1                                                              | 8.4 | 11                                       |  |

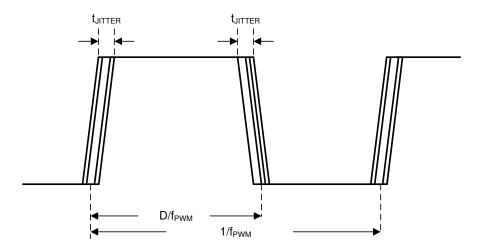

#### 7.3.4.2 PWM Hysteresis

To prevent jitter at the input PWM signal from feeding through the PWM path and causing oscillations in the LED current, the LM36923 offers 7 selectable hysteresis settings. The hysteresis works by forcing a specific number of 11-bit LSB code transitions to occur in the input duty cycle before the LED current changes. Table 4 describes the hysteresis. The hysteresis only applies during the change in direction of brightness currents. Once the change in direction has taken place, the PWM input must over come the required LSB(s) of the hysteresis setting before the brightness change takes effect. Once the initial hysteresis has been overcome and the direction in brightness change remains the same, the PWM to current response changes with no hysteresis.

**Table 4. PWM Input Hysteresis**

|                                        | MIN CHANGE IN PWM<br>PULSE WIDTH (Δt)                                                             | MIN CHANGE IN PWM<br>DUTY CYCLE (ΔD)                        | MIN ( $\Delta I_{LED}$ ), INCREASE FOR INITIAL CODE CHANGE |             |  |

|----------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------|-------------|--|

| HYSTERESIS SETTING<br>(0x12 Bits[4:2]) | REQUIRED TO CHANGE<br>LED CURRENT, AFTER<br>DIRECTION CHANGE<br>(for f <sub>PWM</sub> < 11.7 kHz) | REQUIRED TO CHANGE<br>LED CURRENT AFTER<br>DIRECTION CHANGE | EXPONENTIAL MODE                                           | LINEAR MODE |  |

| 000 (0 LSB)                            | 1/(f <sub>PWM</sub> × 2047)                                                                       | 0.05%                                                       | 0.30%                                                      | 0.05%       |  |

| 001 (1 LSB)                            | 1/(f <sub>PWM</sub> × 1023)                                                                       | 0.10%                                                       | 0.61%                                                      | 0.10%       |  |

| 010 (2 LSBs)                           | 1/(f <sub>PWM</sub> × 511)                                                                        | 0.20%                                                       | 1.21%                                                      | 0.20%       |  |

| 011 (3 LSBs)                           | 1/(f <sub>PWM</sub> × 255)                                                                        | 0.39%                                                       | 2.40%                                                      | 0.39%       |  |

| 100 (4 LSBs)                           | 1/(f <sub>PWM</sub> × 127)                                                                        | 0.78%                                                       | 4.74%                                                      | 0.78%       |  |

| 101 (5 LSBs)                           | $1/(f_{PWM} \times 63)$                                                                           | 1.56%                                                       | 9.26%                                                      | 1.56%       |  |

| 110 (6 LSBs)                           | $1/(f_{PWM} \times 31)$                                                                           | 3.12%                                                       | 17.66%                                                     | 3.12%       |  |

- D is  $t_{JITTER}$  x  $f_{PWM}$  or equal to #LSB's =  $\Delta D$  x 2048 codes.

- For 11-bit resolution, #LSBs is equal to a hysteresis setting of LN(#LSB's)/LN(2).

- For example, with a  $t_{JITTER}$  of 1  $\mu$ s and a  $f_{PWM}$  of 5 kHz, the hysteresis setting should be: LN(1  $\mu$  s x 5 kHz x 2048)/LN(2) = 3.35 (4 LSBs).

Figure 19. PWM Hysteresis Example

## 7.3.4.3 PWM Step Response

The LED current response due to a step change in the PWM input is approximately 2 ms to go from minimum LED current to maximum LED current.

#### 7.3.4.4 PWM Timeout

The LM36923 PWM timeout feature turns off the boost output when the PWM is enabled and there is no PWM pulse detected. The timeout duration changes based on the PWM Sample Rate selected which results in a minimum supported PWM input frequency. The sample rate, timeout, and minimum supported PWM frequency are summarized in Table 5.

Table 5. PWM Timeout and Minimum Supported PWM Frequency vs PWM Sample Rate

| SAMPLE RATE | TIMEOUT  | MINIMUM SUPPORTED PWM<br>FREQUENCY |

|-------------|----------|------------------------------------|

| 0.8 MHz     | 25 msec  | 48 Hz                              |

| 4 MHz       | 3 msec   | 400 Hz                             |

| 24 MHz      | 0.6 msec | 2000 Hz                            |

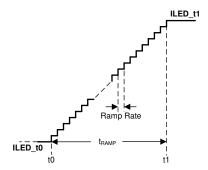

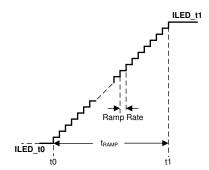

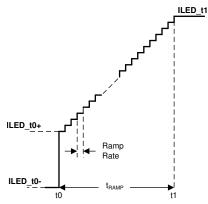

#### 7.3.5 LED Current Ramping

There are 8 programmable ramp rates available in the LM36923. These ramp rates are programmable as a time per step. Therefore, the ramp time from one current set-point to the next, depends on the number of code steps between currents and the programmed time per step. This ramp time to change from one brightness set-point (Code A) to the next brightness set-point (Code B) is given by:

$$\Delta t = Ramp\_rate \times (Code\ B - Code\ A - 1) \tag{3}$$

For example, assume the ramp is enabled and set to 1 ms per step. Additionally, the brightness code is set to 0x444 (1092d). Then the brightness code is adjusted to 0x7FF (2047d). The time the current takes to ramp from the initial set-point to max brightness is:

(4)

$$\Delta t = \frac{1ms}{step} \times (0x7FF - 0x444 - 1) = 954ms \tag{5}$$

Submit Documentation Feedback

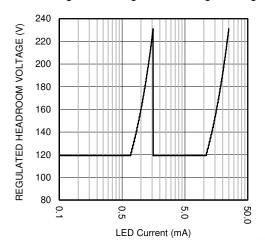

#### 7.3.6 Regulated Headroom Voltage

In order to optimize efficiency, current accuracy, and string-to-string matching the LED current sink regulated headroom voltage (VHR) varies with the target LED current. Figure 20 details the typical variation of VHR with LED current. This allows for increased solution efficiency as the dropout voltage of the LED driver changes. Furthermore, in order to ensure that both current sinks remain in regulation whenever there is a mismatch in string voltages, the minimum headroom voltage between VLED1, VLED2, VLED3 becomes the regulation point for the boost converter. For example, if the LEDs connected to LED1 require 12 V, the LEDs connected to LED2 require 12.5 V, and the LEDs connected to LED3 require 13 V at the programmed current, then the voltage at LED1 is VHR + 1 V, the voltage at LED2 is VHR + 0.5 V, and the voltage at LED3 is regulated at VHR. In other words, the boost makes the cathode of the highest voltage LED string the regulation point.

Figure 20. LM36923 Typical Exponential Regulated Headroom Voltage vs Programmed LED Current

#### 7.4 Device Functional Modes

Device Functional Modes describes the different operating modes and features available within the LM36923.

#### 7.4.1 Brightness Control Modes

The LM36923 has 4 brightness control modes:

- 1. I<sup>2</sup>C Only (brightness mode 00)

- 2. PWM Only (brightness mode 01)

- 3.  $I^2C \times PWM$  with ramping only between  $I^2C$  codes (brightness mode 10)

- 4.  $I^2C \times PWM$  with ramping between  $I^2C \times PWM$  changes (brightness mode 11)

## 7.4.1.1 PC Only (Brightness Mode 00)

In brightness control mode 00 the  $I^2C$  Brightness registers are in control of the LED current, and the PWM input is disabled. The brightness data (BRT) is the concatenation of the two brightness registers (3 LSBs) and (8 MSBs) (registers 0x18 and 0x19, respectively). The LED current only changes when the MSBs are written, meaning that to do a full 11-bit current change via  $I^2C$ , first the 3 LSBs are written and then the 8 MSBs are written. In this mode the ramper only controls the time from one  $I^2C$  brightness set-point to the next Figure 21.

Figure 21. Brightness Control 00 (I<sup>2</sup>C Only)

- 1. At time t0 the I<sup>2</sup>C Brightness Code is changed from 0x444 (1092d) to 0x7FF (2047d)

- 2. Ramp Rate programmed to 1ms/step

- 3. Mapping Mode set to Linear

- 4.  $ILED_t0 = 1092 \times 12.213 \,\mu\text{A} = 13.337 \,\text{mA}$

- 5.  $ILED_t1 = 2047 \times 12.213 \,\mu\text{A} = 25 \,\text{mA}$

- 6.  $t_{BAMP} = (t1 t0) = 1 \text{ ms/step} \times (2047 1092 1) = 954 \text{ ms}$

Figure 22. I<sup>2</sup>C Brightness Mode 00 Example (Ramp Between I<sup>2</sup>C Code Changes)

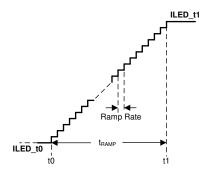

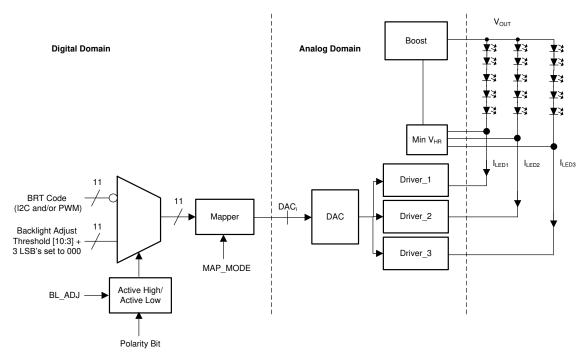

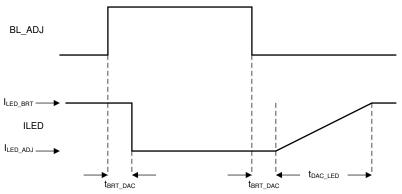

## 7.4.1.2 PWM Only (Brightness Mode 01)

In brightness mode 01, only the PWM input sets the brightness. The  $I^2C$  code is ignored. The LM36923 samples the PWM input, determines the duty cycle and this measured duty cycle is translated into an 11-bit digital code. The resultant code is then applied to the internal ramper (see Figure 23).

Figure 23. Brightness Control 01 (PWM Only)

- 1. At time to the PWM duty cycle changed from 25% to 100%

- 2. Ramp Rate programmed to 1 ms/step

- 3. Mapping Mode set to Linear

- 4. ILED  $t0 = 25 \text{ mA} \times 0.25 = 6.25 \text{ mA}$

- 5.  $ILED_t1 = 25 \text{ mA} \times 1 = 25 \text{ mA}$

- 6.  $t_{RAMP} = (t1 t0) = 1 \text{ms/step} \times (2047 \times 1 2047 \times 0.25 1) = 1534 \text{ ms}$

Figure 24. Brightness Control Mode 01 Example (Ramp Between Duty Cycle Changes)

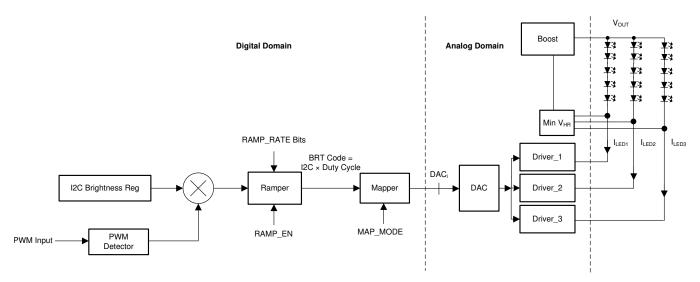

## 7.4.1.3 PC + PWM Brightness Control (Multiply Then Ramp) Brightness Mode 10

In brightness control mode 10 the I<sup>2</sup>C Brightness register and the PWM input are both in control of the LED current. In this case the I<sup>2</sup>C brightness code is multiplied with the PWM duty cycle to produce an 11-bit code which is then sent to the ramper. In this mode ramping is achieved between I<sup>2</sup>C x PWM currents (see Figure 25).

Figure 25. Brightness Control 10 (I<sup>2</sup>C + PWM)

- 1. At time t0 the I<sup>2</sup>C Brightness code changed from 0x444 (1092d) to 0x7FF (2047d)

- 2. At time t0 the PWM duty cycle changed from 50% to 75%

- 3. Ramp Rate programmed to 1ms/step

- 4. Mapping Mode set to Linear

- 5.  $ILED_t0 = 1092 \times 12.213 \,\mu\text{A} \times 0.5 = 6.668 \,\text{mA}$

- 6. ILED\_t1 =  $2047 \times 12.213 \,\mu\text{A} \times 0.75 = 18.75 \,\text{mA}$

- 7.  $t_{\text{BAMP}} = (t1 t0) = 1 \text{ms/step} \times (2047 \times 0.75 1092 \times 0.5 1) = 988 \text{ ms}$

Figure 26. Brightness Control Mode 10 Example (Multiply Duty Cycle then Ramp)

## 7.4.1.4 PC + PWM Brightness Control (Ramp Then Multiply) Brightness Mode 11

In brightness control mode 11 both the I<sup>2</sup>C brightness code and the PWM duty cycle control the LED current. In this case the ramper only changes the time from one I<sup>2</sup>C brightness code to the next. The PWM duty cycle is multiplied with the I<sup>2</sup>C brightness code at the output of the ramper (see Figure 27).

Figure 27. Brightness Control 11 (I<sup>2</sup>C + PWM)

- 1. At time t0 the I<sup>2</sup>C Brightness code changed from 0x444 (1092d) to 0x7FF (2047d)

- 2. At time t0 the PWM duty cycle changed from 50% to 75%

- 3. Ramp Rate programmed to 1 ms/step

- 4. Mapping Mode set to Linear

- 5. ILED\_t0- =  $1092 \times 12.213 \, \mu A \times 0.5 = 6.668 \, mA$

- 6. ILED  $t0+ = 1092 \times 12.213 \,\mu\text{A} \times 0.75 = 10.002 \,\text{mA}$

- 7.  $t_{RAMP} = (t1 t0) = 1 \text{ ms/step} \times (2047 1092 1) = 954 \text{ ms}$

Figure 28. Brightness Control Mode 11 Example (Ramp Current Then Multiply Duty Cycle)

## 7.4.2 Boost Switching Frequency