20A Integrated Power Stage "DrMOS" with Current and Temperature Monitoring

## **General Description**

**Typical Application**

The XR78021 is an integrated power stage containing a synchronous buck gate driver which is packaged with both half bridge MOSFETs designed to provide output currents up to 20Amps. Also known as "DrMOS" (Driver plus MOSFETs), the package design provides very low thermal impedance and excellent EMI performance by minimizing parasitic inductances. The ratio of the MOSFET  $R_{DS(ON)}$  is optimized for conversions from 12V rails to the low output voltages required for the latest processor and chipsets of computing systems.

Computing systems are demanding more and more telemetry of the power system. The XR78021 monitors internal temperature (TOUT pin) and uses that temperature information to provide a temperature corrected current output (IOUT pin) derived from the inductor DCR. The output current information has minimal phase delay and is suitable for use with current mode PWM and valley current mode constant on-time control.

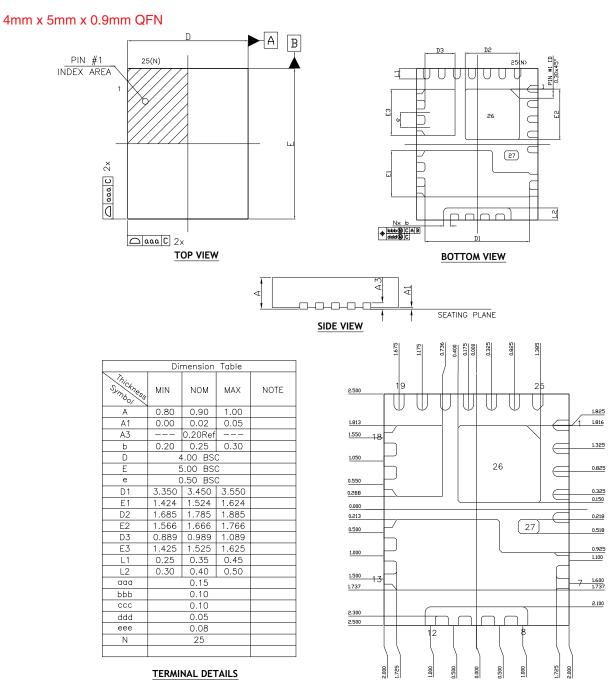

TOUT serves the secondary function of a fault flag for V<sub>CC</sub> UVLO and Over-Temp fault. The XR78021 is offered in a 4 x 5 x 0.9mm QFN package.

#### 12V CBST **VR13** Controller PHASE BOOST M TSENSEx TOUT/FAULT L SW **PWMx** PWM R C<sub>OUT</sub> CSIN+ ISENSEx IOUT XR78021 CSIN-20A DrMOS REFIN PGND GND REF S 5V Cvcc Vsense-Vsense+

Figure 1: Typical Application Circuit

### FEATURES

- 20A Integrated Power Stage

- Input Voltage Range: 4.5V to 17V

- Output Voltage Range: 0.6V to 3.3V

0.6V to 5.5V without current sense

- IMON output 5mV/A (DCR=0.29mΩ) with temperature compensation

XR78021

- Suitable for current mode control loops

- Trimmed and tested at 27°C

- TOUT output 8mV/°C with fault flags for V<sub>CC</sub> UVLO and temperature

- Designed for 3.3V tristate PWM outputs

- Boost pin refresh

4 x 5 x 0 9mm Bol

- 4 x 5 x 0.9mm RoHS compliant package

#### APPLICATIONS

- Servers

- Networking Equipment

- Industrial PC

Ordering Information - Back Page

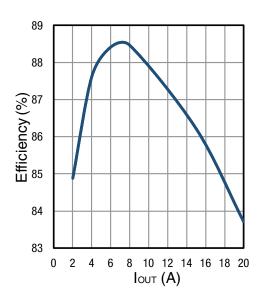

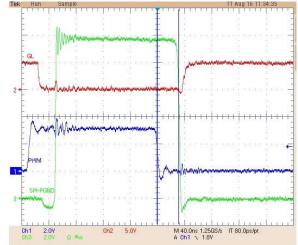

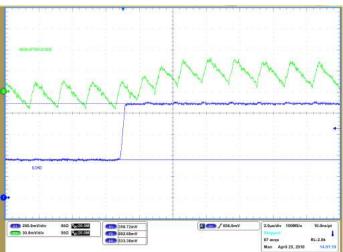

Figure 2: Efficiency 12VIN 1VOUT 600kHz

## **Absolute Maximum Ratings**

Stresses beyond the limits listed below may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition may affect device reliability and lifetime.

| $PV_{IN}$ –0.3V to 25V                                  |

|---------------------------------------------------------|

| SW, PHASE1V to 25V <sup>(1)</sup>                       |

| $V_{CC}$ –0.3V to 6V                                    |

| BOOST0.3V to 29V <sup>(2)</sup>                         |

| PWM, IOUT, GATEL, EN, TOUT–0.3V to $V_{CC}\text{+}0.3V$ |

| CSIN–, CSIN+–0.3V to $V_{CC}\text{+}0.3V$               |

| REFIN0.3V to 3.5V                                       |

| Storage Temperature Range65°C to 150°C                  |

| Peak Package Body Temperature 260°C                     |

| MSL                                                     |

| ESD rating (HBM – human body model) 2kV                 |

| ESD rating (CDM – Charged Device Model)750V             |

## **Operating Conditions**

| V <sub>CC</sub> 4.25V to 5.5V                                          |

|------------------------------------------------------------------------|

| PV <sub>IN</sub> 3V to 17V                                             |

| SW1V to 17V <sup>(1)</sup>                                             |

| $V_{CC},EN$ 0.3V to 5.5V                                               |

| CSIN–, CSIN+–0.3V to 3.3V                                              |

| Switching Frequency up to 1500kHz                                      |

| Junction Temperature Range $(T_J) \ldots -40^\circ C$ to $125^\circ C$ |

| JEDEC51 Package Thermal Resistance $\Theta_{JA}$ 24.2°C/W              |

| Thermal Resistance, $\Theta_{JCBOT}$                                   |

Note 1: SW pin's DC range is -1V, transient is -5V for less than 50ns. Note 2: No external voltage applied.

## **Electrical Characteristics**

Specifications are for Operating Junction Temperature of  $T_J = 27^{\circ}C$  only; limits applying over the full Operating Junction Temperature range are denoted by a "•". Typical values represent the most likely parametric norm at  $T_J = 27^{\circ}C$ , and are provided for reference purposes only. Unless otherwise indicated,  $PV_{IN}=12V$ ,  $V_{CC}=5V$ .

| Symbol                               | Parameter                                        | Conditions                                         | • | Min  | Тур  | Max | Units |

|--------------------------------------|--------------------------------------------------|----------------------------------------------------|---|------|------|-----|-------|

| DC Specifications                    | ;                                                |                                                    | _ |      |      |     |       |

| V <sub>VCC</sub>                     | V <sub>CC</sub> input range                      |                                                    | • | 4.25 | 5.0  | 5.5 | V     |

| I <sub>q_</sub> DC                   | Non-switching quiescent current                  | EN = Vcc, PWM floating                             |   |      |      | 5.1 | mA    |

| I <sub>q_shutdown</sub>              | Shutdown quiescent current                       | EN = 0V                                            |   |      |      | 300 | μA    |

| I <sub>q_leakage</sub>               | PV <sub>IN</sub> leakage current in tri-state    | EN = 5V, PWM = Tri-state                           |   |      | 0.1  |     | μA    |

| V <sub>UVLO</sub>                    | V <sub>CC</sub> UVLO Threshold                   | V <sub>CC</sub> rising                             |   | 3.5  | 3.7  | 3.9 | V     |

| V <sub>UVLO_HYST</sub>               | V <sub>CC</sub> UVLO Hysteresis                  | V <sub>CC</sub> falling                            |   |      | 300  |     | mV    |

| EN Input                             |                                                  |                                                    |   |      |      |     |       |

| V <sub>IH_EN</sub>                   | Logic level high, chip enabled                   |                                                    |   | 2    |      |     | V     |

| V <sub>IL_EN</sub>                   | Logic level low, chip shutdown                   |                                                    |   |      |      | 0.8 | V     |

| t <sub>DLY_ENH</sub>                 | Delay EN transitions from 0 to 1                 |                                                    |   |      | 4.4  |     | us    |

| t <sub>DLY_ENL</sub>                 | Delay EN transitions from 1 to 0                 |                                                    |   |      | 37   | 45  | ns    |

| R <sub>PLD_EN</sub>                  | Enable pull down resistance                      |                                                    |   |      | 570  |     | kΩ    |

| PWM Input                            |                                                  |                                                    |   |      |      |     |       |

| V <sub>IH_PWM</sub> Logic level high |                                                  |                                                    |   | 2.5  |      |     | V     |

| V <sub>IL_PWM</sub>                  | Logic level low                                  |                                                    |   |      |      | 0.8 | V     |

| V <sub>PWM_HYST</sub>                | PWM hysteresis                                   | Active to tristate or tristate to active           |   | 80   | 110  | 140 | mV    |

| V <sub>TRI_PWM</sub>                 | Tristate voltage measured on PWM                 | PWM = FLOAT                                        |   | 1.4  | 1.65 | 1.8 | V     |

| R <sub>IN_PWM</sub>                  | PWM input resistance                             | EN = HIGH                                          |   |      | 8    |     | kΩ    |

| t <sub>PD_IH</sub>                   | PWM high propagation delay                       | PWM logic low $\rightarrow$ high to SW high        |   |      | 40   |     | ns    |

| t <sub>PD_IL</sub>                   | PWM low propagation delay                        | PWM logic high $\rightarrow$ low to SW low         |   |      | 40   |     | ns    |

| t <sub>PD_IL_TRI</sub>               | PWM low to tristate propagation delay            | PWM logic low $\rightarrow$ tristate to GL falling |   |      | 25   | 45  | ns    |

| t <sub>PD_TRI_IH</sub>               | PWM tristate to high propagation delay           | PWM tristate → logic high to SW >1V                |   |      | 25   |     | ns    |

| t <sub>MIN_ONTIME</sub>              | Minimum on-time measured at SW                   | 15ns < PWM Input < 30ns                            |   |      | 40   |     | ns    |

| t <sub>MIN_PWM</sub>                 | Minimum pulse width resulting in no output pulse |                                                    |   |      | 15   |     | ns    |

## **Electrical Characteristics (continued)**

Specifications are for Operating Junction Temperature of  $T_J = 27^{\circ}C$  only; limits applying over the full Operating Junction Temperature range are denoted by a "•". Typical values represent the most likely parametric norm at  $T_J = 27^{\circ}C$ , and are provided for reference purposes only. Unless otherwise indicated,  $PV_{IN}=12V$ ,  $V_{CC}=5V$ .

| Symbol                                                               | Parameter                                                                   | Conditions                                                                     | •                                    | Min   | Тур   | Max   | Units |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------|-------|-------|-------|-------|

| TOUT Output                                                          |                                                                             |                                                                                |                                      |       |       |       |       |

| V <sub>TOUT_SLOPE</sub>                                              | Temperature sense slope                                                     | nse slope $0^{\circ}C \le T_J \le 125^{\circ}C$                                |                                      | 7.8   | 8.0   | 8.2   | mV/°C |

| T <sub>SNSOFFSET</sub>                                               | Temperature sense offset (27°C)                                             |                                                                                |                                      | 0.798 | 0.816 | 0.834 | °C    |

| ITOUT_SOURCE                                                         | TOUT source current                                                         | TMON driven down 2%                                                            |                                      |       | 22    |       | mA    |

| I <sub>TOUT_SINK</sub>                                               | TOUT sink current                                                           | TMON driven up 2%                                                              |                                      |       | 75    |       | μA    |

| R <sub>PLD_TOUT</sub>                                                | TOUT pull down resistance                                                   |                                                                                |                                      |       | 30    |       | kΩ    |

| V <sub>TOUT_OH</sub>                                                 | TOUT fault level high                                                       | TEMP fault active                                                              |                                      | 2.6   | 3.3   | 3.6   | V     |

| I <sub>TOUT_SC</sub>                                                 | TOUT short circuit source current                                           | TOUT = 0V                                                                      |                                      | 5     |       |       | mA    |

| V <sub>TOUT_OL</sub>                                                 | TOUT fault level low V <sub>CC</sub> UVLO fault active. No external pullup. |                                                                                |                                      | 1     | 280   | mV    |       |

| Current Monitor (IM                                                  | ON) Specifications                                                          |                                                                                |                                      |       |       |       |       |

| I <sub>BIAS_CSIN</sub>                                               | CSIN+ and CSIN- input bias current                                          |                                                                                |                                      | -100  | ±1    | 100   | nA    |

| V <sub>OS_CSIN</sub>                                                 | Input referred offset voltage                                               | CSIN+ = CSIN- = REFIN; Measure<br>input referred offset from REFIN             | -450                                 |       |       | 450   | μV    |

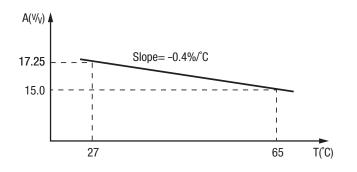

| G <sub>65°C_IMON</sub>                                               | Gain of IMON amplifier at 65°C                                              | $T_J = 65^{\circ}C, V_{CC} = 5V, V_{REFIN} = 1.2V, \\ V_{OUT} = 1.2V$          |                                      |       | 15.0  |       | V/V   |

| G <sub>27°C_IMON</sub>                                               | Gain of IMON amplifier at 27°C                                              | $T_J = 27^{\circ}C$ , $V_{CC} = 5V$ , $V_{REFIN} = 1.2V$ ,<br>$V_{OUT} = 1.2V$ | 16.73                                |       | 17.25 | 17.77 | V/V   |

| f <sub>UNITY_IMON</sub>                                              | Unity Gain Bandwidth of IMON signal<br>path C <sub>IOUT</sub> = 10pF        |                                                                                |                                      | 10    |       | MHz   |       |

| t <sub>DELAY</sub>                                                   | IMON propagation delay                                                      |                                                                                |                                      |       | 90    |       | ns    |

| S <sub>R</sub>                                                       | Slew rate of IOUT                                                           |                                                                                |                                      |       | 4     |       | V/µs  |

| VICM_CSIN                                                            | Common mode input voltage range                                             | V <sub>CC</sub> = 4.25V                                                        |                                      | 0     |       | 2.5   | V     |

| VICM_CSIN                                                            | Common mode input voltage range                                             | V <sub>CC</sub> ≥ 5.0V                                                         |                                      | 0     |       | 3.3   | V     |

| I <sub>SINK_IOUT</sub>                                               | IOUT sink current                                                           | V <sub>IOUT</sub> - V <sub>REFIN</sub> rises 2% from 150mV                     |                                      | 1.2   | 1.5   |       | mA    |

| ISOURCE_IOUT                                                         | IOUT source current                                                         | V <sub>IOUT</sub> - V <sub>REFIN</sub> falls 2% from 150mV                     |                                      | 1.4   | 5.1   |       | mA    |

| Fault Flag – Tempe                                                   | rature                                                                      | 1                                                                              |                                      |       |       |       |       |

| T <sub>OT_HIGH</sub>                                                 | Over temperature rising trip threshold                                      |                                                                                |                                      |       | 140   |       | °C    |

| T <sub>OT_LOW</sub>                                                  | Over temperature hysteresis                                                 |                                                                                |                                      |       | 25    |       | °C    |

| BOOST UVLO and                                                       | C <sub>BOOST</sub> Refresh – High Side Gate Di                              | ive                                                                            |                                      |       |       |       |       |

| V <sub>BOOST-SW_START</sub> Gate voltage required to start switching |                                                                             | Voltage rising                                                                 |                                      |       | 3.5   |       | V     |

| V <sub>BOOST-SW_HYST</sub>                                           | UVLO hysteresis                                                             |                                                                                |                                      |       | 200   |       | mV    |

| VBOOST-SW_REFRESH                                                    | Gate voltage required to activate<br>C <sub>BOOST</sub> refresh             | Voltage falling, PWM = Tristate > 5us 3.                                       |                                      | 3.5   |       | V     |       |

| V <sub>REFRESH_HYST</sub>                                            | C <sub>BOOST</sub> refresh hysteresis                                       | Voltage rising, PWM = Tristate > 5us                                           | Voltage rising, PWM = Tristate > 5us |       | 200   |       | mV    |

## **Electrical Characteristics (Continued)**

Specifications are for Operating Junction Temperature of  $T_J = 27^{\circ}C$  only; limits applying over the full Operating Junction Temperature range are denoted by a "•". Typical values represent the most likely parametric norm at  $T_J = 27^{\circ}C$ , and are provided for reference purposes only. Unless otherwise indicated,  $PV_{IN}=12V$ ,  $V_{CC}=5V$ .

| Symbol                            | Parameter                         | Conditions                      | • | Min | Тур | Max | Units |

|-----------------------------------|-----------------------------------|---------------------------------|---|-----|-----|-----|-------|

| High-Side MOSFET                  |                                   |                                 |   |     |     |     |       |

| BV <sub>DSS</sub>                 | Drain to source breakdown voltage | $V_{GS} = 0V$                   |   | 30  |     |     | V     |

| D                                 | Drain to source on resistance     | $T_{\rm J} = 27^{\circ} \rm C$  |   |     | 4.7 |     | mΩ    |

| R <sub>DS(ON)</sub>               |                                   | $T_{\rm J} = 65^{\circ} \rm C$  |   |     | 5.6 |     | mΩ    |

| Low-Side MOSFET                   |                                   |                                 |   |     |     |     |       |

| BV <sub>DSS</sub>                 | Drain to source breakdown voltage | $V_{GS} = 0V$                   |   | 30  |     |     | V     |

| R <sub>DS(ON)</sub> Drain to sour | Drain to source on resistance     | $T_J = 27^{\circ}C$             |   |     | 2.9 |     | mΩ    |

|                                   | Drain to source on resistance     | $T_{\rm J} = 65^{\circ}{\rm C}$ |   |     | 3.4 |     | mΩ    |

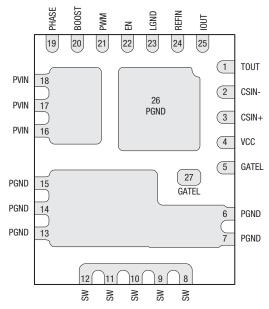

# **Pin Configuration**

Bottom View, 4mm x 5mm x 0.9mm QFN

## **Pin Functions**

| Pin Number                                                           | Pin Name                                                                                                                                                                                                                                                                | Description                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                    | TOUT/ FAULT                                                                                                                                                                                                                                                             | The voltage at this pin is defined by the equation 8mV * (Celsius Temperature) + 0.6V. This pin will be pulled low under an UVLO condition. This pin will be pulled to 3.3V when an Over Temp fault is detected.                                                                                                                       |

| 2                                                                    | CSIN-                                                                                                                                                                                                                                                                   | Inverting input to the current sense amplifier. Connect to LGND if the current sense amplifier is not used.                                                                                                                                                                                                                            |

| 3                                                                    | CSIN+                                                                                                                                                                                                                                                                   | Non-inverting input to the current sense amplifier. Connect to LGND if the current sense amplifier is not used.                                                                                                                                                                                                                        |

| 4                                                                    | VCC                                                                                                                                                                                                                                                                     | Bias voltage for BOTH control logic and gate drivers. This VCC pin is monitored by an UVLO circuit. Connect a high quality low ESR 2.2µF X6S 10V 0402 ceramic capacitor.                                                                                                                                                               |

| 5, 27                                                                | GATEL                                                                                                                                                                                                                                                                   | Synchronous MOSFET driver pins that can be connected to a test point in order to observe the waveform.                                                                                                                                                                                                                                 |

| 8-12                                                                 | SW                                                                                                                                                                                                                                                                      | Switch node of synchronous buck converter.                                                                                                                                                                                                                                                                                             |

| 6, 7, 13-15, 26                                                      | PGND                                                                                                                                                                                                                                                                    | Power grounds of the synchronous MOSFET and also the MOSFET drivers.                                                                                                                                                                                                                                                                   |

| 16-18 100F 1206 ceramic capacitors and a 0.1uF 0402 ceramic capacito |                                                                                                                                                                                                                                                                         | High current input voltage connection. Recommended operating range is 4.5V to 17V. Connect at least two 10uF 1206 ceramic capacitors and a 0.1uF 0402 ceramic capacitor. Place the capacitors as close as possible to PVIN pins and PGND pins (pin 15). The 0.1µF 0402 capacitor should be on the same side of the PCB as the XR78021. |

| 19                                                                   | PHASE                                                                                                                                                                                                                                                                   | The internal switch node dedicated for Bootstrap capacitor connection.                                                                                                                                                                                                                                                                 |

| 20                                                                   | BOOST                                                                                                                                                                                                                                                                   | Bootstrap capacitor connection. Connect a 0.22µF capacitor from BOOST to PHASE (pin 19). The bootstrap capacitor provides the charge to turn on the control MOSFET.                                                                                                                                                                    |

| 21                                                                   | PWM Tri-State PWM input: "High" turns control MOSFET on; "Tri-state" turns both MOSFETs off; "Low" turns the synchronous MOSFET on. Body braking and diode emulation can be controlled by placing the PWM input tri-state. 3.3V logic level PWM input and VCC tolerant. |                                                                                                                                                                                                                                                                                                                                        |

| 22                                                                   | EN Pulling EN high enables the driver; pulling EN low disables the driver and enter low-quiescent current mode.<br>Floating this pin is not recommended. However a low current pull-down is embedded to keep the driver off if pin is floating. Pin is VCC tolerant.    |                                                                                                                                                                                                                                                                                                                                        |

| 23                                                                   | LGND                                                                                                                                                                                                                                                                    | Signal ground. All signals are referenced to this pin.                                                                                                                                                                                                                                                                                 |

| 24                                                                   | REFIN                                                                                                                                                                                                                                                                   | Reference voltage input from the PWM controller. IOUT signal is referenced to the voltage on this pin. Connect to LGND if the current sense amplifier is not used.                                                                                                                                                                     |

| 25                                                                   | IOUT                                                                                                                                                                                                                                                                    | Current output signal. Voltage on this pin is equal to $V_{REFIN}$ + Gain * ( $V_{CSIN+} - V_{CSIN-}$ ). Float this pin if the current sense amplifier is not used. Gain = 15 @ 65°C, Gain = 17.25 @ 27°C                                                                                                                              |

## **Typical Performance Characteristics**

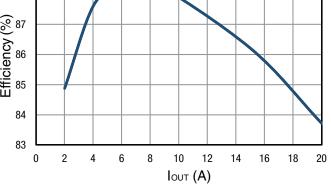

Figure 4: Efficiency –  $12V_{IN}$ ,  $1V_{OUT}$ , 600kHz

Figure 6: PWM Low to SW Delay

Figure 8: CS Input Signal vs IOUT (2.5V output, 1A - 8A load, L = 470nH, using TI TPS53658 controller on HPE G10 DL380 board)

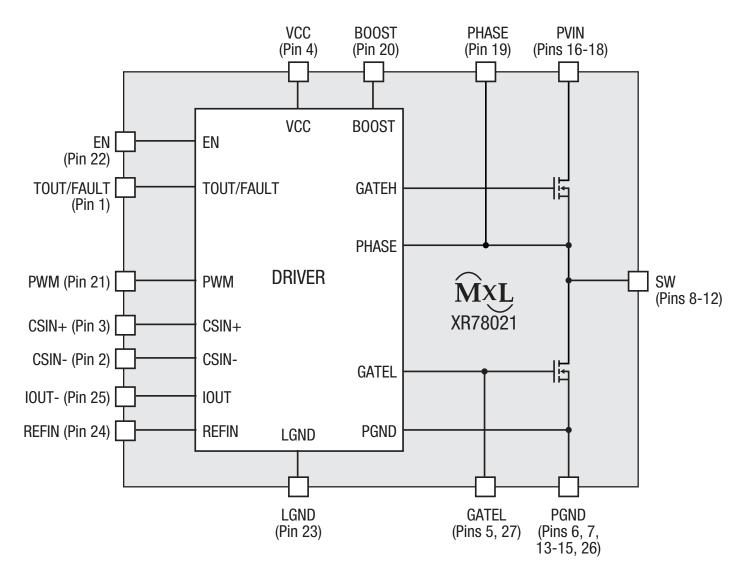

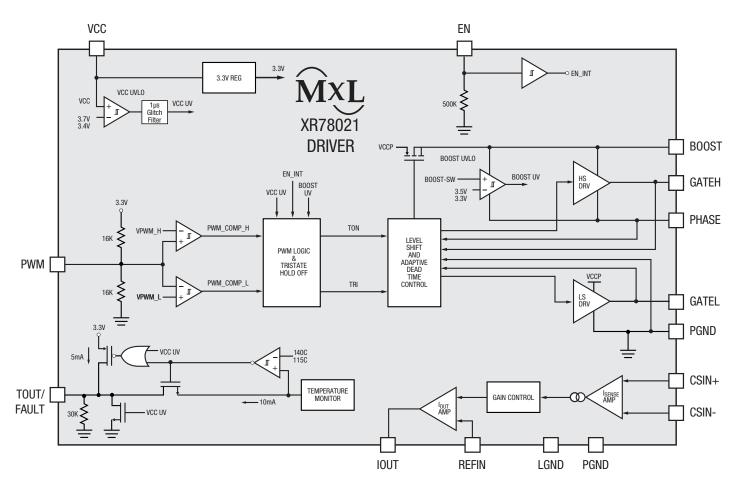

**Functional Block Diagram**

Figure 9: High Level Block Diagram

Figure 10: Driver Detailed Block Diagram

## **Applications Information**

#### **Functional Description**

The XR78021 is a 20A "DrMOS" (Driver plus MOSFETs) integrating a high speed, MOSFET driver IC and a pair of Power MOSFETs in a half bridge configuration which can operate up to 1.5MHz.

The XR78021 incorporates an accurate, high speed Current Sense Amplifier (CSA) optimized for use with inductor DCR sensing and achieves spot on inductor current sensing and reporting for use by the PWM Controller. The CSA provides noise immunity along with temperature compensated signal gain to compensate for DCR change with temperature. The sensed current information is referenced to the REFIN pin and is available at IOUT pin as an equivalent voltage.

The XR78021 provides real-time temperature monitoring and reporting output along with fault reporting of Over-Temperature (OT) and VCC under voltage via the TOUT/ FAULT pin. When the temperature exceeds 140°C, temperature reporting ceases and pulls the TOUT/FAULT pin high to flag OT. Once the temperature drops below 115°C, the fault is disabled and temperature reporting continues on the TOUT/FAULT pin. VCC UV pulls the TOUT/FAULT pin low.

The XR78021 monitors the voltage between BOOST and PHASE and automatically refreshes the voltage across the bootstrap capacitor if it is in tristate longer than a preset duration. This feature avoids gradual depletion of the bootstrap capacitor voltage when the power stage stays in tristate for long periods of time.

The EN pin supports deep sleep mode whereby if the EN pin is pulled low, the XR78021 shuts down most of the internal circuits and the driver, thereby drawing less than  $300\mu$ A of quiescent current.

The PWM input pin is a 3.3V logic input with tristate feature and is VCC tolerant.

#### PWM Input and Tri-State

The PWM Input receives the PWM control signal from the controller IC. The PWM input is designed to be compatible with standard controllers using two-state logic (HIGH and LOW) and advanced controllers that incorporate "tristate" logic (HIGH, LOW and TRISTATE). When the PWM input is high, the control MOSFET is turned on and the synchronous MOSFET is turned off. When the PWM input is low, the control MOSFET is turned off and the synchronous MOSFET is turned on. If the PWM input is floated, the XR78021 will force the PWM into tristate with a nominal 1.65V. Both MOSFETs are turned off and the SW node will tristate.

#### Current Sensing and Reporting (IMON)

The current sensing/reporting circuit is called IMON in this datasheet. IMON monitors the instantaneous inductor current using DCR sensing across the CSIN+ and CSIN-pins, gains up this signal by 17.25V/V at 27°C, level shifts up by voltage at REFIN and drives the IOUT pin. In other words:

$$[V_{IOUT} - V_{REFIN}](V) = 17.25(V/V) \times I_{L}(A) \times DCR(\Omega)$$

REFIN is commonly connected to a controller reference voltage.

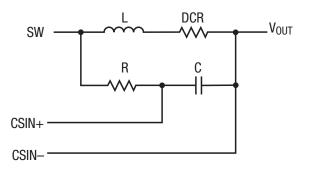

DCR sensing is implemented by placing an R-C across the inductor and monitoring the voltage across the C (Figure 11). Inductor current I<sub>L</sub> results in a voltage across the DCR which is given by  $V = I_L \times DCR$ . If the inductor time constant is matched (i.e., RC = L/DCR), then voltage across C matches I<sub>L</sub> × DCR in magnitude and phase.

Figure 11: DCR Sensing

As an example consider a  $0.33\mu$ H-0.29m $\Omega$  inductor. The inductor time constant is  $0.33\mu$ H /  $0.29m\Omega = 1138$ us. Let C = 0.22uF, then calculate R =  $1138\mu$ s /  $0.22\mu$ F =  $5173\Omega$ . Now the voltage across C should match magnitude and phase of I<sub>L</sub> x DCR. If inductor current I<sub>L</sub> = 1A then V<sub>IOUT</sub>-V<sub>REFIN</sub> =  $1A \times 0.29m\Omega \times 17.25$ V/V = 5mV.

MAXLINEAR

Therefore the IMON amplifier will produce a 5mV/A signal when DCR =  $0.29m\Omega$ . Gain of the IMON is temperature compensated in order to compensate for DCR increase as a function of temperature (Figure 12). In other words IMON will output 5mV/A regardless of operating temperature, when DCR =  $0.29m\Omega$ .

Figure 12: IMON Gain Versus Temperature

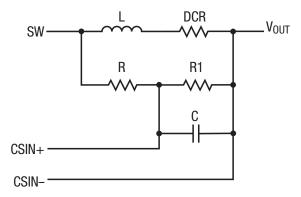

If it is required to have IMON output of 5mV/A with a DCR > 0.29m $\Omega$ , then a voltage divider must be used. This can be implemented by placing a voltage divider across L as shown in Figure 13. Calculate R1 from:

$R1 = R / ((DCR / 0.29m\Omega) - 1)$

Where  $R=10k\Omega$  nominal.

To match inductor's time constant, calculate C from:

$$C = (L / DCR) ((R + R1) / (R1 x R))$$

Figure 13: Voltage Divider Across the Inductor

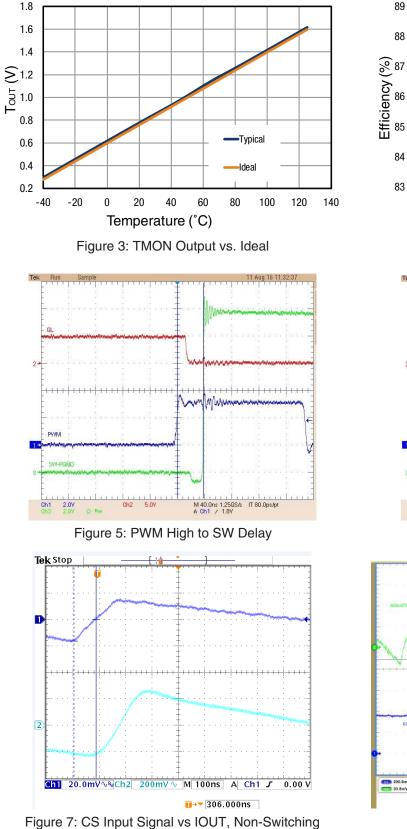

### Temperature Sensing And Reporting (TOUT/FAULT)

XR78021 has an integrated internal temperature sensing circuit that produces a linear voltage slope of 8mV/°C with a 0.6V offset at 0°C. This linearly varying voltage is available at the TOUT/FAULT pin under normal operating conditions.

The voltage at TOUT/FAULT pin during temperature reporting is given as:

$V_{TOUT/FAULT}$  (V) = 0.6V + (Temperature in °C x 0.008V/°C) Therefore at a die temperature of 65°C,

$V_{\text{TOUT/FAULT}}$  (V) = 0.6V + (65°C X 0.008V/°C) = 1.12V

A typical graph of TOUT versus temperature is shown in Figure 3. In a multi-phase system, the TOUT/FAULT pins of several XR78021 can be connected together to create a system in which the highest temperature on the bus will drive the bus.

#### Fault Sensing And Reporting (TOUT/FAULT)

VCC under-voltage VCC UVLO and Over-Temperature OT faults are constantly monitored and flagged via the TOUT/ FAULT pin.

The VCC UVLO circuit monitors the VCC input. During power up, the MOSFETs are held off until VCC reaches 3.7V nominal. If at any time VCC drops below 3.4V nominal, the MOSFETs are turned off and a VCC UVLO fault is flagged by pulling the TOUT/FAULT low.

The Over-Temperature circuit monitors the driver temperature and if it exceeds 140°C, the TOUT/FAULT pin is pulled high. The TOUT/FAULT pin resumes temperature monitoring once the junction temperature falls below 115°C.

#### Boost UVLO and Refresh

The Boost UVLO circuit monitors the voltage between BOOST and SW. During power up,  $V_{BOOST}$  -  $V_{SW}$  must reach 3.5V before the control FET is allowed to switch. If at any time  $V_{BOOST}$  -  $V_{SW}$  drops below 3.3V, the control FET is turned off.

The BOOST refresh circuit is activated if PWM stays in tristate > 5 $\mu$ s and V<sub>BOOST</sub> - V<sub>SW</sub> drops below 3.3V. The refresh circuit will then apply short GL pulses to the synchronous FET until V<sub>BOOST</sub> - V<sub>SW</sub> reaches 3.5V.

#### Bootstrap Capacitor (C<sub>BST</sub>)

Use a high quality  $0.22 \mu F$  capacitor as close to PHASE and BOOST pins as possible.

#### VCC Decoupling Capacitor (CVCC)

Use a minimum of  $2.2\mu F$  high quality ceramic capacitor. Place as close as possible to VCC and LGND, and route with low impedance traces.

## **Mechanical Dimensions**

- ALL DIMENSIONS ARE IN MILLIMETERS, ANGLES ARE IN DEGREES.

Drawing No.: POD-00000085 Revision: B.1

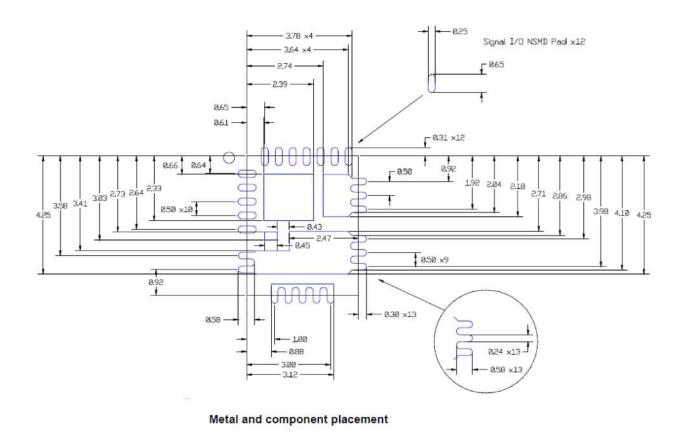

## **Recommended Land Pattern and Stencil**

### 4mm x 5mm x 0.9mm QFN

#### PCB COPPER

NOTE 1 : LEAD LAND WIDTH SHOULD BE EQUAL TO NOMINAL PART LEAD WIDTH. NOTE 2 : MINIMUM LEAD SPACE TO SPACE SHOULD BE >/= 0.2mm TO PREVENT SHORTING. NOTE 3 : LEAD LAND LENGTH SHOULD BE EQUAL TO MAXIMUM PART LEAD LENGTH +0.15 -0.3mm OUTBOARD EXTENSION AND 0 TO +0.05mm INBOARD EXTENSION. THE OUTBOARD EXTENSION ENSURES A LARGE AND VISIBLE TOE FILLET AND THE INBOARD EXTENSION WILL ACCOMODATE ANY PART MISALIGNMENT AND ENSURE A FILLET. NOTE 4 : CENTER PAD LAND LENGTH AND WIDTH SHOULD BE EQUAL TO MAXIMUM PART PAD LENGTH AND WIDTH. BUT, MIN 0.2mm SPACE AMONG PADS SHOULD BE KEPT TO PREVENT SHORTING. NOTE 5 : ONLY 0.15~0.3mm DIAMETER VIA SHALL BE PLACED IN THE AREA OF THE POWER PAD LANDS AND CONNECTED TO POWER PLANES TO MINIMIZE THE NOISE EFFECT ON THE IC AND TO IMPROVE THERMAL PERFORMANCE.

Drawing No.: POD-0000085

Revision: B.1

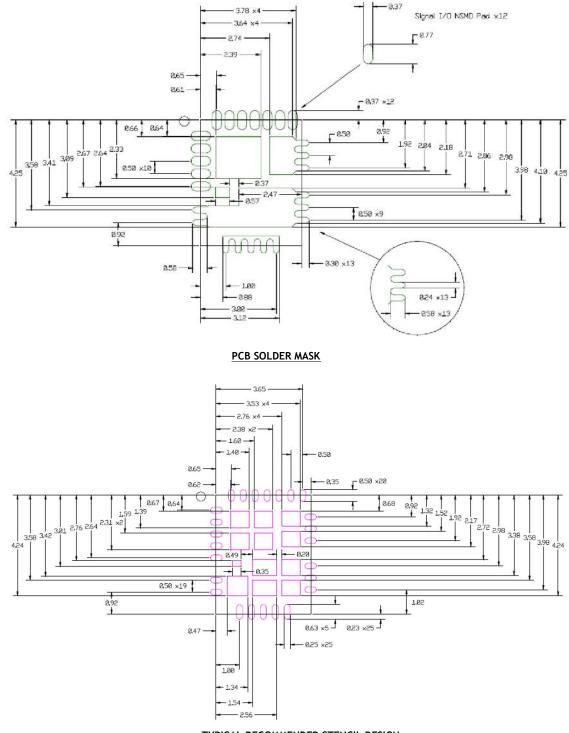

## **Recommended Land Pattern and Stencil, Continued**

#### 4mm x 5mm x 0.9mm QFN

TYPICAL RECOMMENDED STENCIL DESIGN

Drawing No.: POD-0000085

Revision: B.1

## Ordering Information<sup>(1)</sup>

| Part Number   | Operating Temperature Range               | Lead-free         | Package               | Packaging Method |

|---------------|-------------------------------------------|-------------------|-----------------------|------------------|

| XR78021ELTR-F | $-40^{\circ}C \le T_{J} \le 125^{\circ}C$ | No <sup>(2)</sup> | 4mm x 5mm x 0.9mm QFN | Reel             |

NOTE:

1. Refer to www.maxlinear.com/XR78021 for most up-to-date Ordering Information.

2. RoHS Compliant with 7(a) Exemption taken. Lead based die adhesive is used between the die and lead frame.

## **Revision History**

| Revision | Date           | Description                                                                                                                  |

|----------|----------------|------------------------------------------------------------------------------------------------------------------------------|

| 1A       | July 2017      | Initial Release                                                                                                              |

| 1B       | September 2017 | Minor graphical corrections to Figure 10: Driver Detailed Block Diagram. Clarified lead-free status in ordering information. |

| 2A       | July 2019      | Electrical Table updated based upon corner lot simulation. No change to final test limits.                                   |

Maximear, mc. 5966 La Place Court Suite 100 Carlsbad, CA 92008 Tel.:+1 (760) 692-0711 Fax: +1 (760) 444-8598 www.maxlinear.com

The content of this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by MaxLinear, Inc. MaxLinear, Inc. assumes no responsibility or liability for any errors or inaccuracies that may appear in the informational content contained in this guide. Complying with all applicable copyright laws is the responsibility of the user. Without limiting the rights under copyright, no part of this document may be reproduced into, stored into, a retrieval system, or transmitted in any form or by any means (electronic, mechanical, photocopying, recording, or otherwise), or for any purpose, without the express written permission of MaxLinear, Inc.

Maxlinear, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless MaxLinear, Inc. receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of MaxLinear, Inc. is adequately protected under the circumstances.

MaxLinear, Inc. may have patents, patent applications, trademarks, copyrights, or other intellectual property rights covering subject matter in this document. Except as expressly provided in any written license agreement from MaxLinear, Inc., the furnishing of this document does not give you any license to these patents, trademarks, copyrights, or other intellectual property.

MaxLinear, the MaxLinear logo, and any MaxLinear trademarks, MxL, Full-Spectrum Capture, FSC, G.now, AirPHY and the MaxLinear logo are all on the products sold, are all trademarks of MaxLinear, Inc. or one of MaxLinear's subsidiaries in the U.S.A. and other countries. All rights reserved. Other company trademarks and product names appearing herein are the property of their respective owners.

© 2017 - 2019 MaxLinear, Inc. All rights reserved