This product is obsolete.

This information is available for your convenience only.

For more information on Zarlink's obsolete products and replacement product lists, please visit

http://products.zarlink.com/obsolete\_products/

ZL40510/14 Dual Output DVD and CD 4 Channel Laser Diode Drivers

Data Sheet

August 2006

#### Features

- Single 5 V supply (±10%)

- 150 mA low-noise read channel with 100 x current gain

- Three 500 mA write channels with 240 x gain

- Combined channel output 700 mA

- · Dual output for DVD/CD laser

- · Rise and fall times 1 ns typical

- Oscillator, 500 MHz, 100 mA with external resistor control of frequency and amplitude

- Power Up/Down control

- LVDS control signals

- > 2 kV ESD

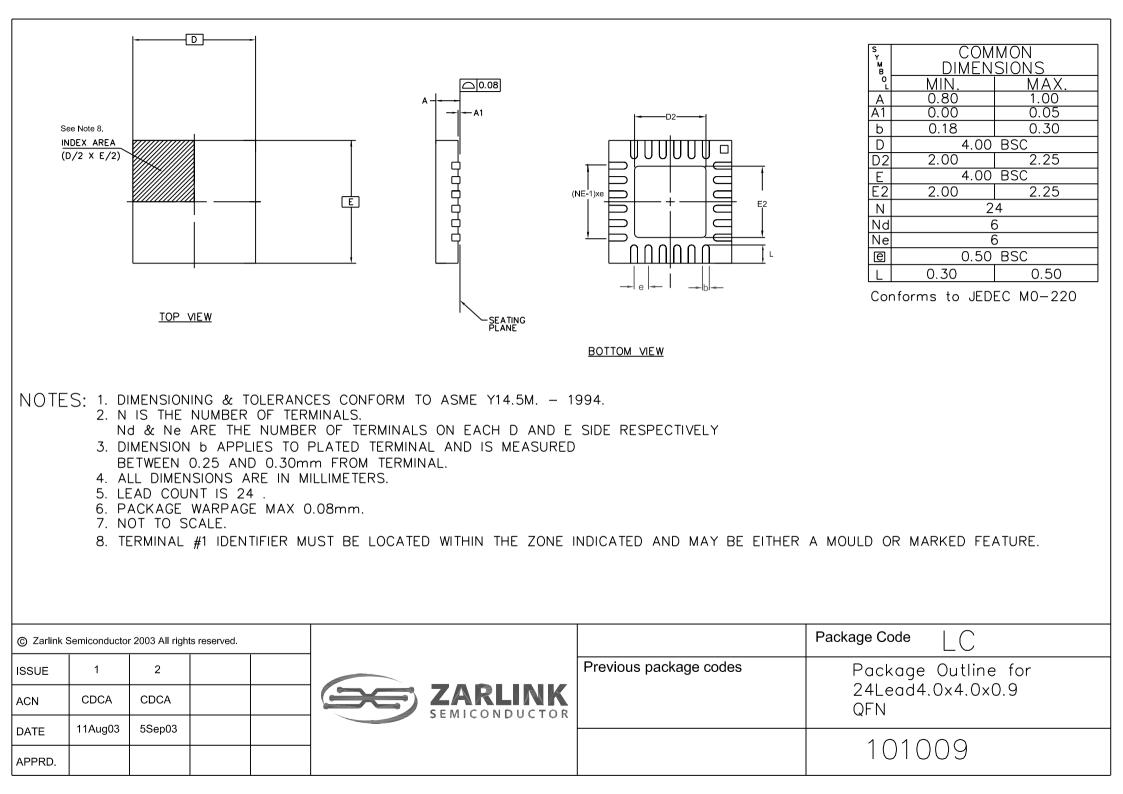

- Low R<sub>th</sub> QFN package

- Contact Zarlink for available Custom Gain and Input Impedance options

# Ordering Information

|                                                                                                | jjj                                                                              |                                                                                                                                |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| ZL40510LDE<br>ZL40510LDF<br>ZL40510LDG<br>ZL40514LDE<br>ZL40514LDF<br>ZL40514LDF<br>ZL40514LDG | 24 Pin QFN<br>24 Pin QFN<br>24 Pin QFN<br>24 Pin QFN<br>24 Pin QFN<br>24 Pin QFN | Tubes, Bake & Drypack<br>Tape & Reel<br>Trays, Bake & Drypack<br>Tubes, Bake & Drypack<br>Tape & Reel<br>Trays, Bake & Drypack |

|                                                                                                | -40°C to +8                                                                      | 5°C                                                                                                                            |

#### Applications

- DVD±RW/RAM

- DVD±R

- CD-RW

- CD-R

- · Write optical drives

- Laser Diode current switch

- Supports double density DVD

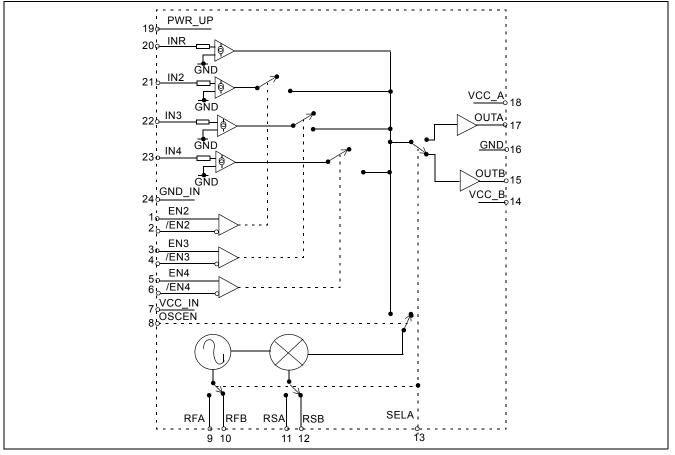

#### Figure 1 - Functional Block Diagram

Zarlink Semiconductor Inc. Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc. Copyright 2004-2006, Zarlink Semiconductor Inc. All Rights Reserved.

1

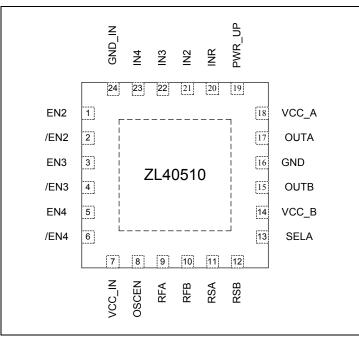

Figure 2 - Pinout of 4x4 mm 24 Pin QFN (top view)

## Description

The ZL40510/14 are high performance laser drivers capable of driving two separate cathode grounded laser diodes (e.g., 650 nm and 780 nm laser diodes).

The ZL40510/14 contain a 150 mA low-noise read channel (ChR), and three 500 mA write channels (Ch2, Ch3 and Ch4). The read channel amplifies the positive current supplied at its reference input, INR, by a fixed factor of 100. Write channels amplify the positive currents supplied at its reference inputs IN2, IN3, and IN4 by a fixed factor of 240.

An on-chip RF oscillator is provided for the reduction of laser mode hopping noise.

The ZL40510 offers higher tolerance performance.

# **Table of Contents**

| 1.0 Application Notes                                                                                   | 5 |

|---------------------------------------------------------------------------------------------------------|---|

| 1.1 Read and Write Channel Operation                                                                    | 5 |

| 1.2 On-chip RF Oscillator                                                                               |   |

| 1.3 Thermal Considerations                                                                              | 5 |

| 1.4 Electrical and Optical Pulse Response                                                               | 5 |

| 1.5 Specified Electrical Performance with 15 mm Interconnect and Zarlink ZLE40510/14 Evaluation Board 7 | , |

| 1.6 Application Layout Guide Lines                                                                      | , |

| 1.7 ZLE40510/14 Interconnect                                                                            | 3 |

| 2.0 Application Diagram                                                                                 | ) |

| 3.0 Evaluation Boards From Zarlink Semiconductor                                                        |   |

| 4.0 Optical Pulse Response                                                                              | ) |

| 5.0 Pin List                                                                                            | I |

| 6.0 Characteristic Curves                                                                               | } |

| 7.0 I/O Diagrams                                                                                        | ŀ |

| 8.0 Timing Waveforms                                                                                    |   |

| 9.0 Timing Diagrams                                                                                     | , |

| 10.0 Example Waveforms                                                                                  | 3 |

| 10.1 Write Waveform                                                                                     |   |

| 10.2 Oscillator Waveform                                                                                | 3 |

# List of Figures

| Figure 1 - Functional Block Diagram                                           | . 1 |

|-------------------------------------------------------------------------------|-----|

| Figure 2 - Pinout of 4x4 mm 24 Pin QFN (top view)                             | . 2 |

| Figure 3 - Pulse Response Model                                               | . 6 |

| Figure 4 - ZLE40510/14 Application Board Electrical Interconnect              | . 8 |

| Figure 5 - Application Schematic Diagram.                                     | . 9 |

| Figure 6 - Typical Optical Eye Diagram Response*                              |     |

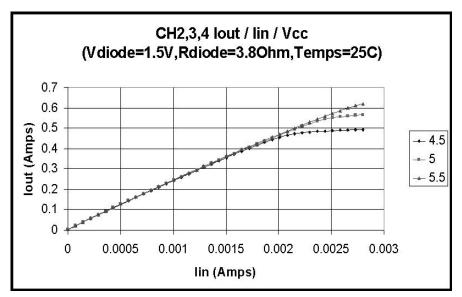

| Figure 7 - Write Channel 2, 3 and 4 IP/OP Transfer Characteristic/Temp        | 18  |

| Figure 8 - Read Channel IP/OP Transfer Characteristic/Temp                    | 18  |

| Figure 9 - Write Channel 2, 3 or 4 IP/OP Transfer Characteristic/Vcc.         | 19  |

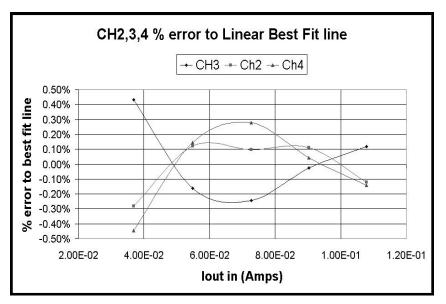

| Figure 10 - Write Channel 2, 3 or 4 IP/OP Best Fit Line% Error                | 19  |

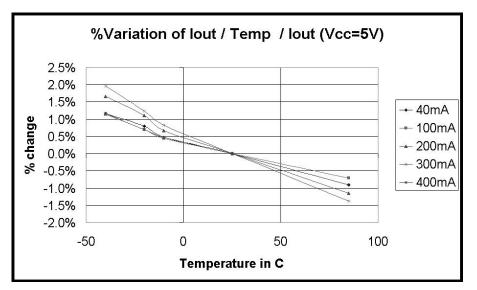

| Figure 11 - Write Channel 2, 3 or 4 $\Delta$ lout% Variation with Temperature | 20  |

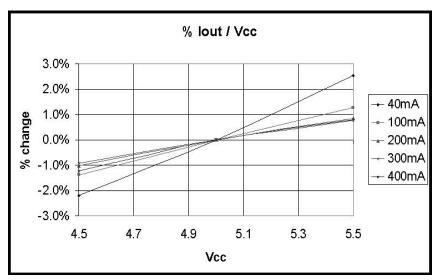

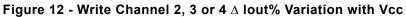

| Figure 12 - Write Channel 2, 3 or 4 $\triangle$ lout% Variation with Vcc      | 20  |

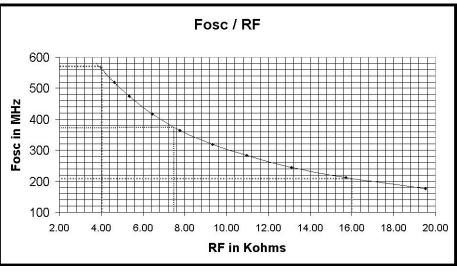

| Figure 13 - Oscillator Frequency/RF                                           |     |

| Vcc = 5 V, Temp = 25°C                                                        | 21  |

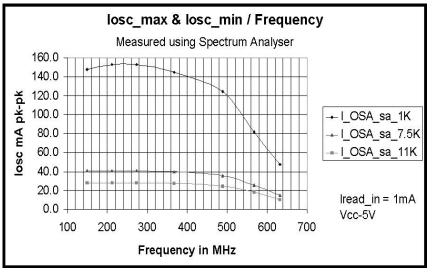

| Figure 14 - losc Out/Frequency/                                               |     |

| RS = 1 K, 7.5 K, 11 K, Vcc = 5 V, Temp = 25°C                                 | 21  |

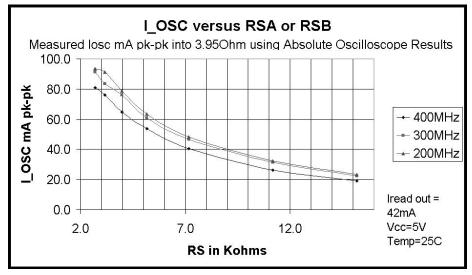

| Figure 15 - losc Amplitude mA pk-pk/RSA or RSB                                | ~~  |

| Vcc = 5 V, Temp = 25°C                                                        | 22  |

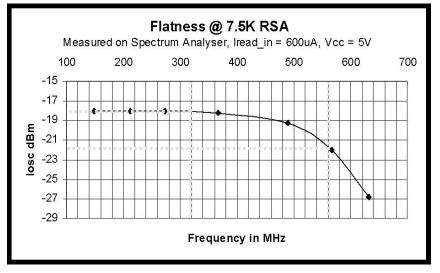

| Figure 16 - losc/Frequency                                                    | ~~  |

| RS = 7.5 K, Vcc = 5 V, Temp = 25°C                                            |     |

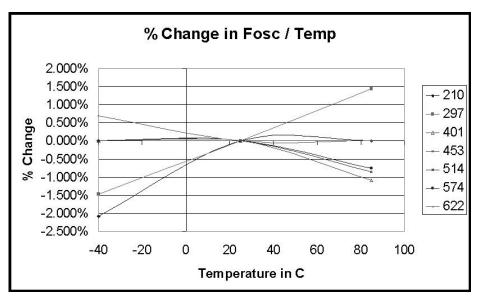

| Figure 17 - △ Freq% Variation with Temperature                                | 23  |

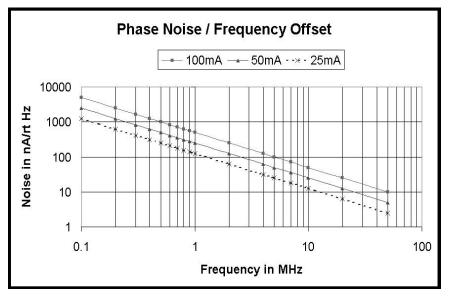

| Figure 18 - Oscillator Noise Spectral Density                                 | 22  |

| Vcc = 5 V, Temp = 25°C                                                        |     |

| Figure 19 - CMOS/LVTTL Input (PWR_UP, OSCEN)                                  |     |

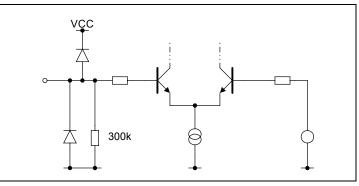

| Figure 20 - Oscillator Resistors (RF, RS).                                    |     |

| Figure 21 - Read Current Input (INR)                                          |     |

| Figure 22 - Output (OUTA, OUTB).                                              |     |

| Figure 23 - Write Current Input (IN2, IN3, IN4)                               |     |

| Figure 24 - LVDS Input (EN2, /EN2), (EN3, /EN3), (EN4, /EN4)                  |     |

| Figure 25 - Timing of Read or Write Channels.                                 |     |

| Figure 26 - Output Waveform Showing Addition of Read and Write Levels.        |     |

| Figure 27 - Example of Write Waveform                                         |     |

| Figure 28 - Example of Oscillator Waveform Superimposed on the Read Waveform  | 28  |

# 1.0 Application Notes

#### 1.1 Read and Write Channel Operation

The read channel is activated by applying a 'High' signal to the PWR\_UP pin. In this mode, the fast write channels can be enabled by applying a 'High' signal to the respective pair of write enable pins (EN2, /EN2), (EN3, /EN3) or (EN4, /EN4). The output currents of the four channels are summed together and output as a composite signal at either OUTA (if SELA select is 'High') or OUTB (if SELA select is 'Low'). This provides the ability to drive two different laser diodes with just one ZL40510/14.

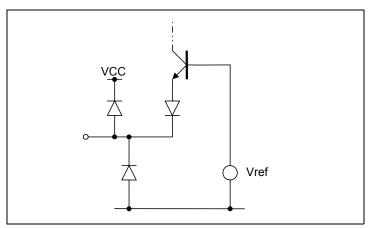

Voltage control of the channel reference inputs (INR, IN2, IN3 and IN4) can be achieved quite easily using an external resistor  $R_{ref}$  in series with the reference channel input to convert a given reference potential  $V_{ref}$  to an input current,  $I_{in}$ :

$$I_{in} = \frac{V_{ref}}{R_{ref} + R_{in}},$$

where  $R_{in}$  is the input impedance of the respective reference channel.

#### 1.2 On-chip RF Oscillator

An on-chip RF oscillator is enabled if OSCEN = 'High', and its output signal is added to the appropriate current output (OUTA, if SELA select is 'High', or OUTB, if SELA select is 'Low'). The oscillator amplitude is set by an external resistor from RSA or RSB to GND. Its frequency is set by an external resistor RFA or RFB to GND. RSA and RFA are selected when SELA is 'High'.

The oscillator signal is summed with the programmed Write and Read levels before amplification to the output. The oscillator signal has zero DC level and +1\_pk to -1\_pk signal swing. Consequently, if the programmed DC level from the Write and Read Channels is less than the PK level programmed for the Oscillator, the combined signal will be clipped on the negative cycle of the signal. This will increase the harmonic content of the output signal and reduce the pk to pk amplitude output.

## 1.3 Thermal Considerations

Package thermal resistance is 40°C/W under the EIA/JESD51-3 compliant PCB test board condition.

Users should ensure that the junction temperature does not exceed 150°C. Thermal resistance from junction to case and to ambient is very much dependent on how the IC is mounted onto the board, on the PCB layout and on any heat extraction arrangements.

Power consumption and system ambient operating temperature limits should be noted and careful thermal gradient calculations undertaken to ensure that the junction temperature never exceeds 150°C.

#### 1.4 Electrical and Optical Pulse Response

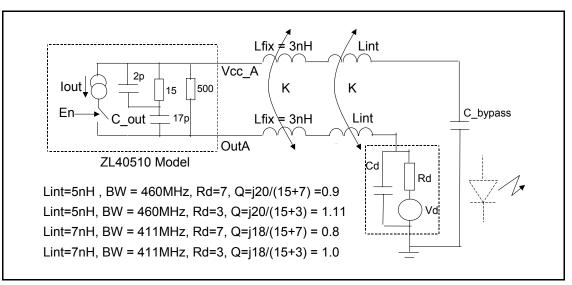

Figure 3 - Pulse Response Model

Figure 3 illustrates a simplified model of the typical ZL40510/14 and the application. The ZL40510/14 consists of an ideal switched current source and an equivalent model of the ZL40510/14 output stage. The Electrical Model for the Laser Diode is a Voltage source Vd (V\_on) in series with the On Resistance Rd all in parallel with the Junction Capacitance Cd. This simplified model approximately represents the Laser Diode Electrical load when operated beyond the Laser Threshold. To a first approximation, the Optical output is proportional to the current flow in the Resistor Rd.

The Laser Diode and the ZL40510/14 are connected together by interconnect tracks with the return current passing through the supply decoupling bypass capacitor between ground and output Vcc.

The ZL40510/14 can be approximated to an ideal switched programmed current source with a propagation delay of lout\_on (1.2 nS) and a switch transition time of 400 ps. The final output electrical pulse response parameters, Trise, Tfall, Overshoot and Undershoot are determined by the combined electrical network as illustrated in Figure 3.

For example, the Rise Time and Fall Time for large current steps can be slew rate limited by the combined interconnect and fixed interconnect inductance. The Fixed Inductance represents that associated with packaging and minimum interconnect distance. The Interconnect Inductance is that associated with the additional tracking between Laser Diode and the ZL40510/14 to accommodate application physical limitations.

For example, if a pulse of 360 mA amplitude (40 mA to 400 mA) is to be switched in a time of 1 nS with the Vd = 1.6 V, then the maximum volt drop across the interconnect inductance is approximately 3.5 V (maximum Vpin for 500 mA output) – 1.6 V (Vdiode) = 1.9 V. Consequently, L\*di/dt < 1.9 V. Hence, L < 1.9/ (0.36A/1 nS) = 5.3 nH.

Small current step size Rise and Fall time will be determined by the Bandwidth of the combined network. This is dominated by the Interconnect Inductance and the output Capacitance. Similarly, the overshoot and undershoot will be determined by the Q of the network. This is a function of the Source Impedance from the ZL40510/14, the Interconnect inductance and the Load impedance of the Laser Diode. Figure 3 includes example simplified estimates of the Q and BW of the combined Laser Diode, ZL40510/14 and interconnect network for two different interconnect inductance values (5 nH and 7 nH) and two different Diode On resistance (3 Ohm and 7 Ohm). This simple analysis illustrates the change in BW and Q of the network depending on these parameters. This in turn effects the Rise Time and Fall time and the Overshoot and Undershoot performance achieved in the application.

#### 1.5 Specified Electrical Performance with 15 mm Interconnect and Zarlink ZLE40510/14 Evaluation Board

The specified performance in the table are results based on the electrical measurements and simulations across full process corners using the Zarlink Evaluation Board using a 3.9 Ohm resistive load to ground.

The track interconnect between ZL40510/14 and the 3.9 Ohm Resistor is 15 mm long and uses a 2 mm wide track on single sided FR4 board. The return path is via two 2 mm wide tracks spaced 0.25 mm either side of the track between output and the 3.9 Ohm resistor. The combined forward and return path forms a co planar transmission line with a characteristic impedance of approximately 120 Ohms.

The tight coupled return paths carrying the return current reduce the effective series inductance (Leff) which can be approximated to:

Leff = 2 \* Lint \* (1 - K) + 2 \* Lfix \* (1 - K).

The ZLE40510 board has two positions for the Laser Diode at two different distances. (15 and 30 mm).

- The measured value of Leff is 7 nH

- The estimated value of Leff = 2 \* 8 (1 − 0.5) = 8 nH

The actual pulse response achieved in an application is thus dependent on the application.

#### 1.6 Application Layout Guide Lines

Minimize interconnect inductance by:

- a. Using Short Interconnect Distance

- b. Use wide interconnect tracks

- c. Keep the return path tightly coupled to the forward path.

## 1.7 ZLE40510/14 Interconnect

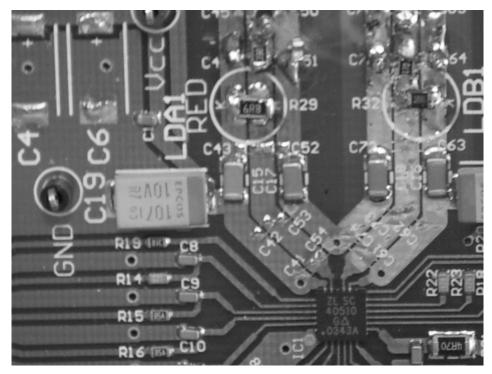

Figure 4 - ZLE40510/14 Application Board Electrical Interconnect

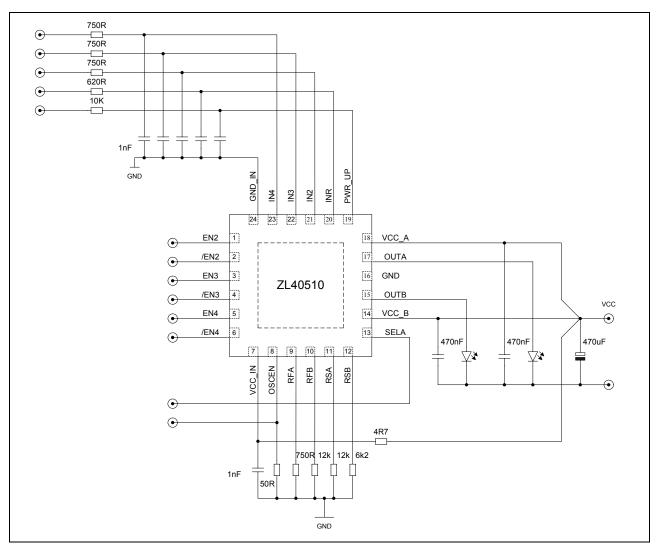

# 2.0 Application Diagram

Figure 5 - Application Schematic Diagram

# 3.0 Evaluation Boards From Zarlink Semiconductor

Zarlink Semiconductor provides an LDD evaluation board. This is primarily for those interested in performing their own assessment of the operation of the LDDs. Figure 5 shows a recommended application configuration. The inputs are connected via side launch SMA connectors.

Please order as ZLE40510.

## 4.0 Optical Pulse Response

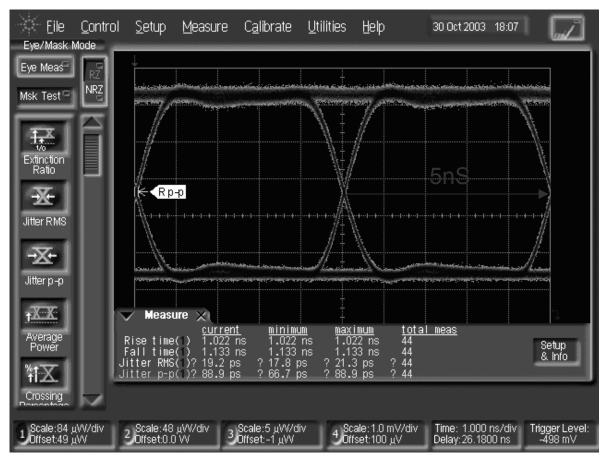

Figure 6 - Typical Optical Eye Diagram Response\*

\* (Measured using Sanyo DL-7140-201S Infra Red Laser Mounted on ZLE40510 Application Board) (I read = 50 mA, I write =125 mA, at 15 mm with 200 MHz PRBS Pattern)

Figure 6 illustrates the typical optical response measured with the ZL40510/14 mounted on the ZLE40510/14 application board driving a Sanyo DL-7140-201S Infra Red Laser. The test condition is driving a PRBS pattern at 200 MHz clock rate which is representative of a 16X DVD write pattern using Block Write Strategy with minimum write pulse of 2T duration.

The Sanyo DL-7140-201S Infra Red Laser Diode On resistance is typically 3 Ohms which is representative of the On resistance of the Latest generation 250 mW pulsed High Power Red Laser Diodes that are targeted at 16X and 8X DVD.

The pulse is measured stepping from a low level which is above the laser threshold thus avoiding the laser turn on transient which can distort the measured response.

The ZL40510/14 exhibits excellent pulse response characteristics when used with the optimum interconnect.

# 5.0 Pin List

| Pin No. | Pin name | Туре    | Function                                                             |

|---------|----------|---------|----------------------------------------------------------------------|

| 1       | EN2      | LVDS    | Positive digital control input for channel 2                         |

| 2       | /EN2     | LVDS    | Negative digital control input for channel 2                         |

| 3       | EN3      | LVDS    | Positive digital control input for channel 3                         |

| 4       | /EN3     | LVDS    | Negative digital control input for channel 3                         |

| 5       | EN4      | LVDS    | Positive digital control input for channel 4                         |

| 6       | /EN4     | LVDS    | Negative digital control input for channel 4                         |

| 7       | VCC_IN   | supply  | +5 V Input power supply                                              |

| 8       | OSCEN    | digital | Oscillator enable control input, high active (TTL)                   |

| 9       | RFA      | analog  | Resistor to GND sets oscillator frequency when SELA = 'High'         |

| 10      | RFB      | analog  | Resistor to GND sets oscillator frequency when SELA = 'Low'          |

| 11      | RSA      | analog  | Resistor to GND sets oscillator amplitude when SELA = 'High'         |

| 12      | RSB      | analog  | Resistor to GND sets oscillator amplitude when SELA = 'Low'          |

| 13      | SELA     | digital | Output select input; 'High' selects OUTA, 'Low' selects OUTB (TTL)   |

| 14      | VCC_B    | supply  | Output B Vcc                                                         |

| 15      | OUTB     | analog  | Current output source B                                              |

| 16      | GND      | supply  | Ground                                                               |

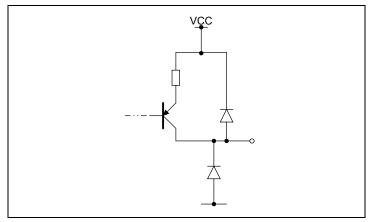

| 17      | OUTA     | analog  | Current output source A                                              |

| 18      | VCC_A    | supply  | Output A Vcc                                                         |

| 19      | PWR_UP   | digital | Digital chip enable control input, high active (CMOS)                |

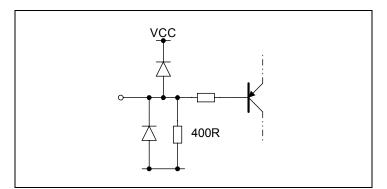

| 20      | INR      | analog  | Current input, R <sub>in</sub> = 400 Ohms to GND                     |

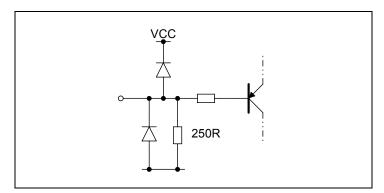

| 21      | IN2      | analog  | Current input, R <sub>in</sub> = 250 Ohms to GND (Optional 500 Ohms) |

| 22      | IN3      | analog  | Current input, R <sub>in</sub> = 250 Ohms to GND (Optional 500 Ohms) |

| 23      | IN4      | analog  | Current input, R <sub>in</sub> = 250 Ohms to GND (Optional 500 Ohms) |

| 24      | GND_IN   | supply  | Ground for input circuit                                             |

#### Absolute Maximum Ratings

| Characteristic                                                             | Min. | Тур. | Max.               | Units | Comments |

|----------------------------------------------------------------------------|------|------|--------------------|-------|----------|

| Supply voltage (VCC, VCC_IN)                                               | -0.5 |      | 6.0                | V     |          |

| Input voltage (INR, IN2, IN3, IN4)                                         | -0.5 |      | 6.0                | V     |          |

| Input voltage<br>(PWR_UP, EN2, /EN2, EN3, /EN3, EN4,<br>/EN4, OSCEN, SELA) | -0.5 |      | (VCC_I<br>N + 0.5) | V     |          |

| Output voltage (OUTA, OUTB)                                                | -0.5 |      | Vcc                | V     |          |

| Junction temperature                                                       |      |      | 150                | °C    |          |

#### **Operating Range**

| Characteristic                        | Min. | Тур. | Max.             | Units | Comments                 |

|---------------------------------------|------|------|------------------|-------|--------------------------|

| Supply voltage (VCC, VCC_IN)          | 4.5  |      | 5.5              | V     |                          |

| Input voltage (INR)                   |      |      | 0.7              | V     |                          |

| Input voltage (IN2, IN3, IN4)         |      |      | 0.7              | V     |                          |

| Output voltage (OUTA, OUTB)           | -0.3 |      | (VCCA,<br>B-0.9) | V     |                          |

| RF                                    | 1    |      |                  | kΩ    | External resistor to GND |

| RS                                    | 1    |      |                  | kΩ    | External resistor to GND |

| Operating temperature range, junction | 0    |      | 150              | °C    |                          |

#### Package Thermal Resistance

|              | Junction to               |                              |       |                                            |

|--------------|---------------------------|------------------------------|-------|--------------------------------------------|

| Package Type | Case<br>R <sub>thJC</sub> | ambient<br>R <sub>thJA</sub> | Units | Comments                                   |

| 24 pin QFN   |                           | 40                           | K/W   | Exposed paddle soldered to multi-layer PCB |

**Electrical Characteristics** Vcc = 5 V,  $T_{amb}$  = 25°C, INR = 400  $\mu$ A, IN2 = IN3 = IN4 = 160  $\mu$ A, PWR\_UP = High, Ch2, Ch3, Ch4 disabled, OSCEN = Low, unless otherwise specified.

| Characteristic                                                    | Min. | Тур. | Max. | Units | Comments                                                                                  | Туре |

|-------------------------------------------------------------------|------|------|------|-------|-------------------------------------------------------------------------------------------|------|

| Supply Current (into VCC-pin)                                     |      |      |      |       | l                                                                                         |      |

| Supply current, power down, I <sub>ccPD</sub>                     |      | 80   | 220  | μA    | ENABLE = Low                                                                              | A    |

| Supply current, read mode, oscillator disabled, I <sub>ccR0</sub> |      | 69   | 84   | mA    | INR = 400 μA                                                                              | A    |

| Supply current, read mode, oscillator enabled, I <sub>ccR1</sub>  |      | 70   | 85   | mA    | OSCEN = High, RF = 6.8 kOhm,<br>RS = 8.2 kOhm,                                            | A    |

| Supply current, write mode, $I_{ccW}$                             |      | 210  | 250  | mA    | Ch2, Ch3, Ch4 enabled                                                                     | В    |

| Supply current, input off                                         |      | 18   |      | mA    | Ch2, Ch3, Ch4 enabled<br>INR = IN2 = IN3 = IN4 = 0                                        | В    |

| SeIA & OscEn Digital Inputs                                       |      |      |      |       | •                                                                                         |      |

| Logic low voltage                                                 |      |      | 0.8  | V     |                                                                                           | А    |

| Logic high voltage                                                | 2.2  |      |      | V     |                                                                                           | А    |

| Threshold level                                                   |      | 1.68 |      | V     | Temperature stabilised                                                                    | В    |

| Logic low input current                                           | -50  |      |      | μA    | V <sub>in</sub> = 0 V                                                                     | В    |

| Logic high input current                                          |      |      | 50   | μA    | V <sub>in</sub> = 3.3 V                                                                   | В    |

| Power_Up Digital Input                                            |      | •    |      | •     |                                                                                           |      |

| Logic low voltage                                                 |      |      | 0.5  | V     | CMOS compatible level                                                                     | А    |

| Logic high voltage                                                | 2.7  |      |      | V     | CMOS compatible level                                                                     | А    |

| Logic low input current                                           | -50  |      |      | μA    | V <sub>in</sub> = 0 V                                                                     | В    |

| Logic high input current                                          |      |      | 50   | μA    | V <sub>in</sub> = 3.3 V                                                                   | В    |

| LVDS Digital Inputs                                               |      | 1    |      | 1     |                                                                                           | 1    |

| Input voltage range                                               | 0    |      | 2.4  | V     |                                                                                           | В    |

| Differential input voltage                                        | 100  |      | 600  | mV    | V(EN2~/EN2) LVDS Compatible<br>V(EN3~/EN3) LVDS Compatible<br>V(EN4~/EN4) LVDS Compatible | A    |

| Differential Input impedance                                      | 87   | 110  | 133  | Ω     |                                                                                           | В    |

| Common mode input impedance                                       |      | 10   |      | kΩ    | internal resistor to Vcc                                                                  | В    |

|                                                                   | •    | •    |      | •     | •                                                                                         | -    |

Note: A = 100% Tested B = Guaranteed by Characterization and Design C = Guaranteed by Simulation

| Characteristic                                                           | Min. | Тур. | Max. | Units      | Comments                                                                           | Туре |

|--------------------------------------------------------------------------|------|------|------|------------|------------------------------------------------------------------------------------|------|

| Current Outputs (OutA & OutB)                                            |      |      | 1    |            |                                                                                    |      |

| Output current, ChR                                                      | 150  | 200  |      | mA         | $V_{out} \le 3.5 \text{ V}$                                                        | В    |

| Output current, Ch2, Ch3, Ch4                                            | 500  |      |      | mA         | Channel enabled,<br>INR = 0 $\mu$ A, V <sub>out</sub> $\leq$ 3.5 V,lin = 2.8 mA    | A    |

| Total output current                                                     | 700  |      |      | mA         | Ch2, 3, 4 enabled, $V_{out} \le 3.5 \text{ V}$                                     | А    |

| Write Output current, zero input,<br>I <sub>out0</sub> (ZL40510)         |      |      | 12   | mA         | INR = IN2 = IN3 = IN4 = 0 $\mu$ A,<br>Ch2, or Ch3 or Ch4 enabled                   | A    |

| Write Output current, zero input,<br>I <sub>out0</sub> ( <b>ZL40514)</b> |      |      | 15   | mA         | INR = IN2 = IN3 = IN4 = 0 $\mu$ A,<br>Ch2, or Ch3 or Ch4 enabled                   |      |

| Read Output current, zero input,<br>I <sub>out0</sub>                    |      |      | 2.5  | mA         | INR = IN2 = IN3 = IN4 = 0 $\mu$ A, Ch2, 3 & 4 disabled                             | A    |

| Input impedance (INR)                                                    | 330  | 400  | 470  | Ω          | R <sub>in</sub> is to GND                                                          | В    |

| Input impedance (IN2, IN3, IN4)                                          | 205  | 250  | 295  | Ω          | R <sub>in</sub> is to GND                                                          | В    |

| l <sub>out</sub> supply sensitivity (any channel)                        | -5   |      | +5   | %/V        | I <sub>out</sub> = 40 mA to 300 mA                                                 | В    |

| I <sub>out</sub> temperature sensitivity<br>(any channel)                |      | 300  |      | ppm/°<br>C | I <sub>out</sub> = 40 mA to 300 mA,<br>I <sub>in</sub> temp coefficient = 0 ppm/°C | В    |

| I <sub>out</sub> current output noise                                    |      | 3    |      | nA/<br>√Hz | I <sub>out</sub> = 50 mA lnR = 500 uA                                              | В    |

| Current Output OutA & OutB                                               |      |      |      |            | I                                                                                  |      |

| Current gain, ChR, best fit                                              | 85   | 100  | 115  | mA/m<br>A  | I <sub>out</sub> = 20 mA to 80 mA †Note 1                                          | A    |

| Current gain, Ch2, best fit                                              | 205  | 240  | 275  | mA/m<br>A  | I <sub>out</sub> = 20 mA to 120 mA † Note 2                                        | A    |

| Current gain, Ch3, best fit                                              | 205  | 240  | 275  | mA/m<br>A  | I <sub>out</sub> = 20 mA to 120 mA † Note 2                                        | A    |

| Current gain, Ch4, best fit                                              | 205  | 240  | 275  | mA/m<br>A  | I <sub>out</sub> = 20 mA to 120 mA † Note 2                                        | A    |

| ZL40510                                                                  |      |      |      |            | I                                                                                  |      |

| Output current offset, ChR, best fit.                                    | -1   |      | 8    | mA         | I <sub>out</sub> = 20 mA to 80 mA † Note 1                                         | A    |

| Output current offset, Ch2, best fit                                     | -4   |      | 12   | mA         | I <sub>out</sub> = 20 mA to 120 mA † Note 2                                        | A    |

| Output current offset, Ch3, best fit                                     | -4   |      | 12   | mA         | I <sub>out</sub> = 20 mA to 120 mA † Note 2                                        | A    |

# ZL40510/14

| Characteristic                                 | Min. | Тур. | Max. | Units | Comments                                    | Туре |

|------------------------------------------------|------|------|------|-------|---------------------------------------------|------|

| Output current offset, Ch4, best fit           | -4   |      | 12   | mA    | I <sub>out</sub> = 20 mA to 120 mA † Note 2 | A    |

| ZL40514                                        |      |      | 1    |       |                                             |      |

| Output current offset, ChR, best fit. Note 3   | -1   |      | 8    | mA    | I <sub>out</sub> = 20 mA to 80 mA † Note 1  | A    |

| Output current offset, Ch2, best fit. Note 4   | -7   |      | 15   | mA    | I <sub>out</sub> = 20 mA to 120 mA † Note 2 | A    |

| Output current offset, Ch3, best fit. Note 4   | -7   |      | 15   | mA    | I <sub>out</sub> = 20 mA to 120 mA † Note 2 | A    |

| Output current offset, Ch4, best fit. Note 4   | -7   |      | 15   | mA    | I <sub>out</sub> = 20 mA to 120 mA † Note 2 | A    |

| ZL40510 & ZI40514                              |      |      | 1    | L     |                                             |      |

| Output current linearity (any channel). Note 3 | -3.5 |      | 1.5  | %     | I <sub>out</sub> = 20 mA to 120 mA † Note 2 | A    |

| Gain tracking, Ch2 to Ch3 to Ch4               | -2.5 |      | +2.5 | %     | I <sub>out</sub> = 20 mA to 120 mA † Note 2 | A    |

Note: A = 100% Tested B = Guaranteed by Characterization and Design C= Guaranteed by Design

Note 1: Gain, offset and linearity of a channel are derived from a best fit line (linear regression graph) to the following three operating points: lout = 20mA, 50mA and 80mA.

Gain, offset and linearity of a channel are derived from a best fit line (linear regression graph) to the following three operating points: lout = 20mA, 70mA and 120mA. Note 2:

Note 3: Best Fit output line through 20mA,50mA,80mA

Note 4: Best Fit output line through 20mA,70mA,120mA

† Electrical measurement into 3.9 Ohm to Gnd

Data Sheet

| Characteristic                                                | Min. | Тур. | Max. | Units | Comments                                                       | Туре |

|---------------------------------------------------------------|------|------|------|-------|----------------------------------------------------------------|------|

| Timing                                                        |      |      | 1    |       | 1                                                              |      |

| Current Output OutA & OutB                                    |      |      |      |       |                                                                |      |

| Channel rise time, (10% to 90%), t <sub>r2</sub>              |      | 0.9  | 1.2  | ns    | 40 to 375 mA, Ch2, 3 or 4 pulsed<br>† ‡                        | В    |

| Channel fall time, (10% to 90%), t <sub>f2</sub>              |      | 1.1  | 1.4  | ns    | 40 to 375 mA, Ch2, 3 or 4 pulsed<br>† ‡                        | В    |

| Output current overshoot (any write channel)                  |      |      | 13   | %     | 40 to 375 mA Ch2 3, 4 pulsed <sup>†</sup>                      | В    |

| Output current undershoot (any write channel)                 |      |      | 13   | %     | 40 to 375 mA Ch2 3, 4 pulsed <sup>†</sup>                      | В    |

| Channel to Channel Enable<br>Skew Tr                          |      | 50   |      | ps    |                                                                | В    |

| Channel to Channel Enable<br>Skew Tf                          |      | 25   |      | ps    |                                                                | В    |

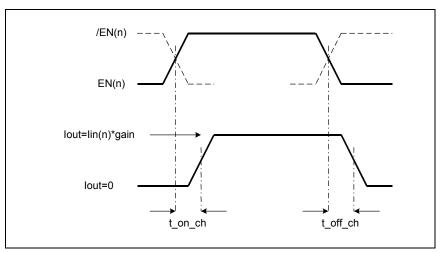

| $\rm I_{out}$ ON propagation delay, $\rm t_{onCh}$            |      | 1.4  | 1.8  | ns    | 50% En High-Low to 50% I <sub>out</sub> ,<br>any write channel | В    |

| I <sub>out</sub> OFF propagation delay,<br><sup>t</sup> offCh |      | 1.2  | 1.6  | ns    | 50% En Low-High to 50% I <sub>out</sub> ,<br>any write channel | В    |

| Amplifier -3dB bandwidth (ChR)                                | 23   | 43   | 68   | MHz   | INR = 400 μA                                                   | С    |

| Amplifier -3dB bandwidth (Ch2, 3, 4)                          | 6    | 11   | 16   | MHz   | IN2, IN3, IN4 = 400 μA                                         | С    |

| Power_Up & SelA                                               |      |      | 1    |       | 1                                                              | 1    |

| Power_Up time, t <sub>on</sub>                                |      | 1.5  | 3.5  | μS    | 50% Enable Low-High to 50%                                     | С    |

| Power_Up time, t <sub>off</sub>                               |      | 20   | 33   | ns    | 50% Enable High-Low to 50%<br>I <sub>out</sub>                 | С    |

| Output A select delay                                         |      | 5    | 8    | ns    | 50% DVD/CD select Low-High to 50% I <sub>OUTA</sub>            | С    |

| Output A deselect delay                                       |      | 5    | 8    | ns    | 50% DVD/CD select High-Low to 50% I <sub>OUTA</sub>            | С    |

Note: A = 100% Tested B = Guaranteed by Characterization and Design C= Guaranteed by Design † (EN2, /EN2), (EN3, /EN3), (EN4, /EN4) input pulse rise and fall time = 0.4 ns.

+ Parameter is measured Electrical Pulse Response using 3.9 Ohm load to gnd and Zarlink Application Board. Pulse response performance parameters Trise, Tfall, Overshoot and Undershoot can be limited by interconnect inductance. Optical Response is influenced by Laser Diode response. See Application Notes.

**Electrical Dynamic Characteristics** Vcc = 5 V,  $T_{amb}$  = 25°C, INR = 400 uA, IN2 = IN3 = IN4 = 160  $\mu$ A, PWR\_UP = High, Ch2, Ch3, Ch4 disabled, OSCEN = Low, unless otherwise specified.

| Characteristic                                | Min. | Тур. | Max. | Units          | Comments                                                                  | Туре |

|-----------------------------------------------|------|------|------|----------------|---------------------------------------------------------------------------|------|

| Oscillator                                    |      |      |      |                |                                                                           | l    |

| Frequency adjust range Low                    |      |      | 250  | MHz            | RF = 16 k $\Omega$ , OSCEN = High                                         | В    |

| Frequency adjust range High                   | 575  |      |      | MHz            | RF = 2 kΩ, OSCEN = High                                                   | В    |

| Frequency tolerance (ZL40510)                 | 338  | 375  | 412  | MHz            | RF = 7.5 kΩ, OSCEN = High                                                 | Α    |

| Frequency tolerance (ZL40514)                 | 322  | 375  | 428  | MHz            | RF = 7.5 kΩ, OSCEN = High                                                 | Α    |

| Frequency temperature coefficient             |      | 200  |      | ppm/<br>°C     | RF = 7.5 kΩ, OSCEN = High                                                 | С    |

| Amplitude adjust range Low (RS=11K $\Omega$ ) |      |      | 36   | mA pk<br>to pk | RS = 11 kΩ, OSCEN = High<br>RF=9 K (350 MHz) InR = 1 mA                   | В    |

| Amplitude adjust range High (RS=1K $\Omega$ ) | 100  |      |      | mA pk<br>to pk | RS = 1 kΩ, OSCEN = High<br>RF = 9 K (330 MHz) InR = 1 mA                  | В    |

| Third Harmonic                                |      | -30  |      | dBC            | RS = 10 kΩ to 2 kΩ, OSCEN =<br>High<br>RF = 9 K (330 MHz)<br>InR = 400 uA | С    |

| Second Harmonic                               |      | -20  |      | dBC            | RS = 10 kΩ to 2 kΩ, OSCEN =<br>High<br>RF = 9 K (330 MHz)<br>InR = 400 uA | С    |

| Amplitude tolerance                           | -20  | 0    | 20   | %              | Fosc= 250 MHz to 450 MHz,<br>OSCEN = High, RS 1%                          | С    |

| Amplitude (RS = 7.5 K)                        |      | 42   |      | mA pk<br>to pk | f = 375 MHz, RS = 7.5 kΩ,<br>OSCEN = High                                 | С    |

| Amplitude flatness                            |      | 4    |      | dB             | RS = 7.5 kΩ, RF = 9 kΩ to 4 kΩ                                            | В    |

| Amplitude temperature coefficient             |      | 800  |      | ppm/<br>°C     | RF = 5.6 kΩ, OSCEN = High                                                 | С    |

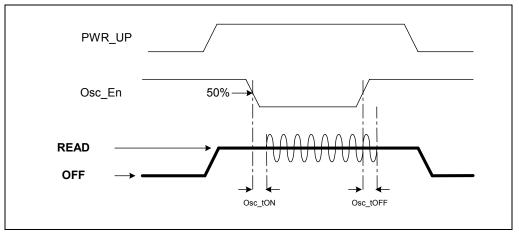

| Oscillator enable time, t <sub>onOsc</sub>    |      |      | 2    | ns             | 50% OSCEN High-Low to 50%                                                 | В    |

| Oscillator disable time, $t_{\rm offOsc}$     |      |      | 3    | ns             | 50% OSCEN Low-High to 50%                                                 | В    |

Note: A = 100% Tested B = Guaranteed by Characterization and Design C= Guaranteed by Design † (EN2, /EN2), (EN3, /EN3), (EN4, /EN4) pulse rise and fall time = 0.4 ns.

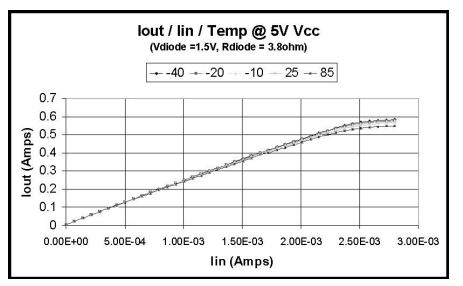

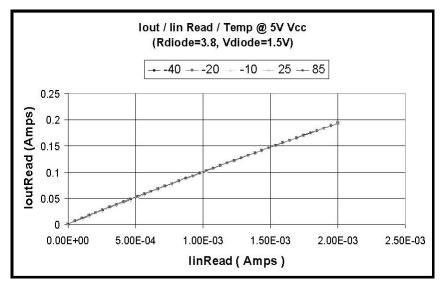

## 6.0 Characteristic Curves

Figure 7 - Write Channel 2, 3 and 4 IP/OP Transfer Characteristic/Temp

Figure 8 - Read Channel IP/OP Transfer Characteristic/Temp

Figure 9 - Write Channel 2, 3 or 4 IP/OP Transfer Characteristic/Vcc

Figure 10 - Write Channel 2, 3 or 4 IP/OP Best Fit Line% Error

Figure 11 - Write Channel 2, 3 or 4  $\vartriangle$  lout% Variation with Temperature

Figure 13 - Oscillator Frequency/RF Vcc = 5 V, Temp = 25°C

Figure 14 - losc Out/Frequency/ RS = 1 K, 7.5 K, 11 K, Vcc = 5 V, Temp =  $25^{\circ}C$

Figure 15 - losc Amplitude mA pk-pk/RSA or RSB Vcc = 5 V, Temp = 25°C

Figure 16 - losc/Frequency RS = 7.5 K, Vcc = 5 V, Temp =  $25^{\circ}C$

Figure 17 -  $\Delta$  Freq% Variation with Temperature

Figure 18 - Oscillator Noise Spectral Density Vcc = 5 V, Temp = 25°C

# 7.0 I/O Diagrams

Figure 19 - CMOS/LVTTL Input (PWR\_UP, OSCEN)

Figure 20 - Oscillator Resistors (RF, RS)

Figure 21 - Read Current Input (INR)

Figure 22 - Output (OUTA, OUTB)

Figure 23 - Write Current Input (IN2, IN3, IN4)

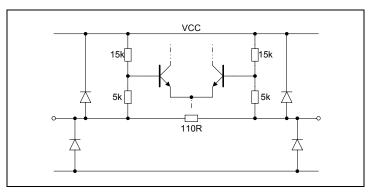

Figure 24 - LVDS Input (EN2, /EN2), (EN3, /EN3), (EN4, /EN4)

# 8.0 Timing Waveforms

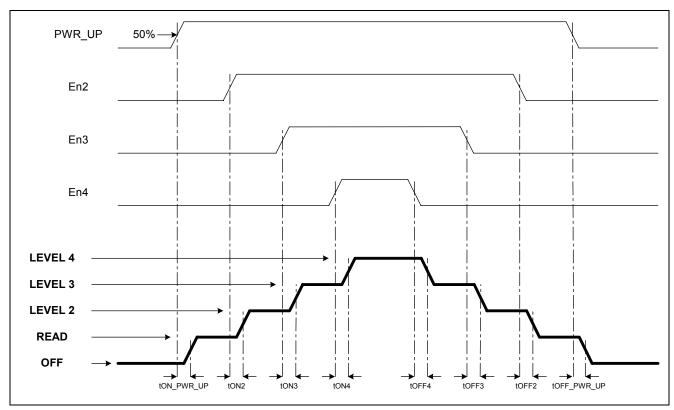

Applying logic levels to the inputs, as shown in Table 1, gives the output waveform shown in Figure 26.

| PWR_UP                                                   | EN2 | EN3 | EN4 | OUTPUT  |

|----------------------------------------------------------|-----|-----|-----|---------|

| 0                                                        | Х   | Х   | Х   | OFF     |

| 1                                                        | 0   | 0   | 0   | READ    |

| 1                                                        | 1   | 0   | 0   | LEVEL 2 |

| 1                                                        | 1   | 1   | 0   | LEVEL 3 |

| 1                                                        | 1   | 1   | 1   | LEVEL 4 |

| Note: 1 = logic high, 0 = logic low and X = "don't care" |     |     |     |         |

Table 1 - Output Function for Set Logic Inputs

# 9.0 Timing Diagrams

Figure 25 - Timing of Read or Write Channels

Figure 26 - Output Waveform Showing Addition of Read and Write Levels

#### 10.0 Example Waveforms

#### 10.1 Write Waveform

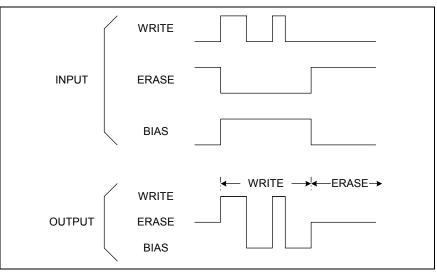

The Write output waveform may be produced as shown in example 1, Figure 27. The Erase level is set by switching off both the Bias level and the Write level. The Write switching waveform is produced by switching off the Erase level and Switching on the Bias level and then modulating that with the Write level. The peak of the Write waveform is the sum of the Bias and the Write levels.

Figure 27 - Example of Write Waveform

NOTES:

- 1. Only the Write signal changes to modulate the output during the Write pulse.

- 2. Each of the Write Channels can provide up to 500 mA. It is not necessary to add together the output of more than one Write Channel to achieve 500 mA.

#### 10.2 Oscillator Waveform

The Oscillator may be enabled independently and is summed with the selected level.

Figure 28 - Example of Oscillator Waveform Superimposed on the Read Waveform

NOTE: The amplitude of the Oscillator must be less than the programmed DC output level to avoid clipping and subsequent increase in harmonic distortion.

# For more information about all Zarlink products visit our Web Site at

#### www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in and I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE