www.ti.com

# TMS320DM368 Digital Media System-on-Chip (DMSoC)

Check for Samples: TMS320DM368

# 1 TMS320DM368 Digital Media System-on-Chip (DMSoC)

# 1.1 Features

- Highlights

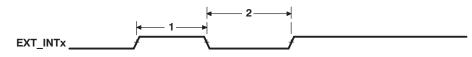

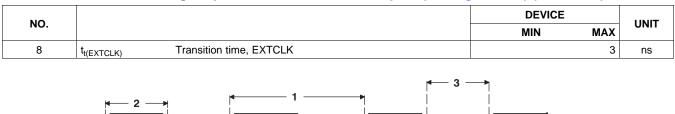

- High-Performance Digital Media System-on-Chip (DMSoC)

- 432-MHz ARM926EJ-S Clock Rate

- Two Video Image Co-processors (HDVICP, MJCP) Engines

- Supports a Range of Encode, Decode, and Video Quality Operations

- Video Processing Subsystem

- HW Face Detect Engine

- Resize Engine from 1/16x to 8x

- 16-Bit Parallel AFE (Analog Front-End) Interface Up to 120 MHz

- 4:2:2 (8-/16-bit) Interface

- 8-/16-bit YCC and Up to 24-Bit RGB888

Digital Output

- 3 DACs for HD Analog Video Output

- Hardware On-Screen Display (OSD)

- Capable of 1080p 30fps H.264 video processing

- Peripherals include EMAC, USB 2.0 OTG, DDR2/NAND, 5 SPIs, 2 UARTs, 2 MMC/SD/SDIO, Key Scan

- 8 Different Boot Modes and Configurable Power-Saving Modes

- Pin-to-pin and software compatible with DM365

- Extended temperature (-40°C 85°C) available

- 3.3-V and 1.8-V I/O, 1.35-V Core

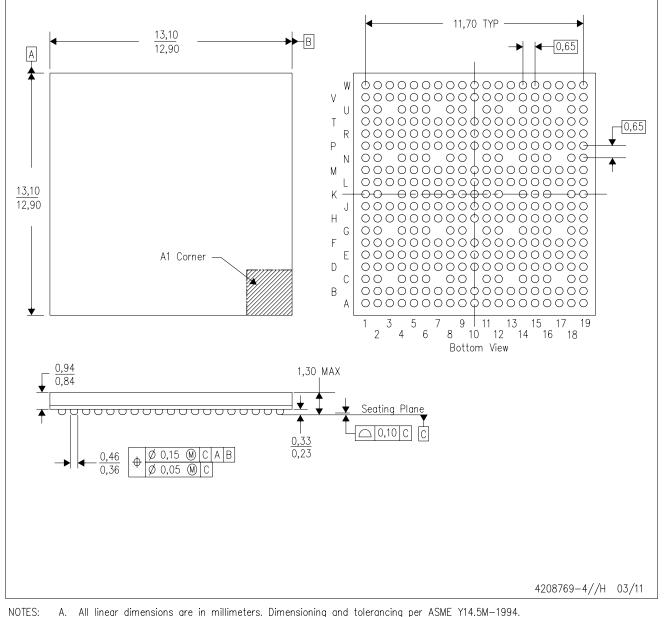

- 338-Pin Ball Grid Array at 65nm Process Technology

- High-Performance Digital Media System-on-Chip (DMSoC)

- 432-MHz ARM926EJ-S Clock Rate

- 4:2:2 (8-/16-Bit) Interface

- Capable of 1080p 30fps H.264 video processing

- Pin compatible with DM365 processors

- Fully Software-Compatible With ARM9™

- Extended temperature available for 432-MHz

device

- ARM926EJ-S<sup>™</sup> Core

- Support for 32-Bit and 16-Bit (Thumb® Mode) Instruction Sets

- DSP Instruction Extensions and Single Cycle MAC

- ARM® Jazelle® Technology

- Embedded ICE-RT Logic for Real-Time Debug

- ARM9 Memory Architecture

- 16K-Byte Instruction Cache

- 8K-Byte Data Cache

- 32K-Byte RAM

- 16K-Byte ROM

- Little Endian

- Two Video Image Co-processors (HDVICP, MJCP) Engines

- Support a Range of Encode and Decode Operations

- H.264, MPEG4, MPEG2, MJPEG, JPEG, WMV9/VC1

- Video Processing Subsystem

- Front End Provides:

- HW Face Detect Engine

- Hardware IPIPE for Real-Time Image

Processing

- Resize Engine

- Resize Images From 1/16x to 8x

- Separate Horizontal/Vertical Control

- Two Simultaneous Output Paths

- IPIPE Interface (IPIPEIF)

- Image Sensor Interface (ISIF) and CMOS

Imager Interface

- 16-Bit Parallel AFE (Analog Front End) Interface Up to 120 MHz

- Glueless Interface to Common Video

Decoders

- BT.601/BT.656/BT.1120 Digital YCbCr 4:2:2 (8-/16-Bit) Interface

- Histogram Module

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

- Lens distortion correction module (LDC)

- Back End Provides:

- Hardware On-Screen Display (OSD)

- Composite NTSC/PAL video encoder output

- 8-/16-bit YCC and Up to 24-Bit RGB888

Digital Output

- 3 DACs for HD Analog Video Output

- LCD Controller

- BT.601/BT.656 Digital YCbCr 4:2:2

(8-/16-Bit) Interface

- Analog-to-Digital Convertor (ADC)

- Power Management and Real Time Clock Subsystem (PRTCSS)

- Real Time Clock

- 16-Bit Host-Port Interface (HPI)

- 10/100 Mb/s Ethernet Media Access Controller (EMAC) Digital Media

- IEEE 802.3 Compliant

- Supports Media Independent Interface (MII)

- Management Data I/O (MDIO) Module

- Key Scan

- Voice Codec

- External Memory Interfaces (EMIFs)

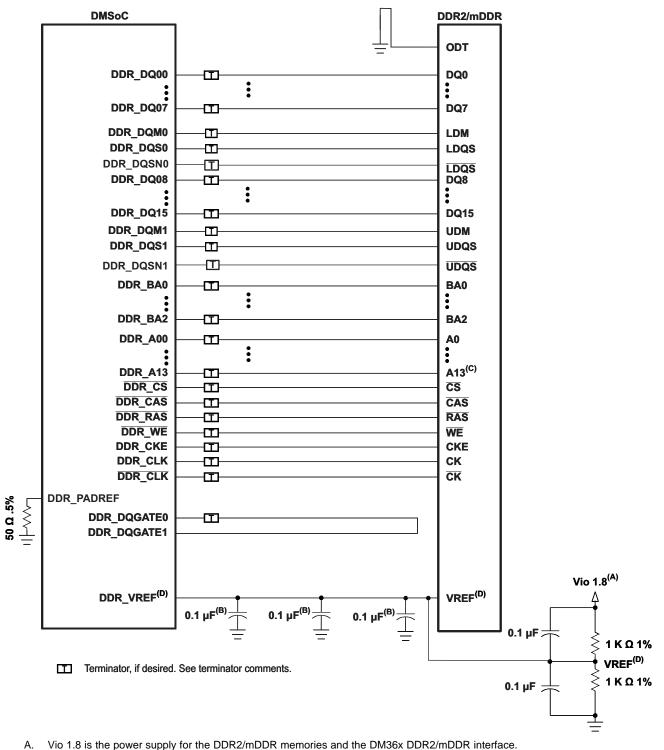

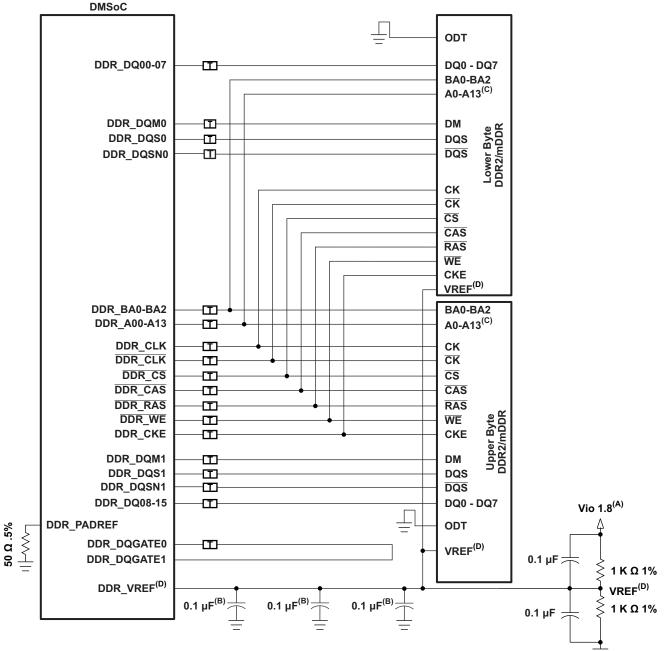

- DDR2 and mDDR SDRAM 16-bit wide EMIF With 256 MByte Address Space (1.8-V I/O)

- Asynchronous16-/8-bit Wide EMIF (AEMIF)

- Flash Memory Interfaces

- NAND (8-/16-bit Wide Data)

- 16 MB NOR Flash, SRAM

- OneNAND(16-bit Wide Data)

- Flash Card Interfaces

- Two Multimedia Card (MMC) / Secure Digital (SD/SDIO)

- SmartMedia/xD

- Enhanced Direct-Memory-Access (EDMA) Controller (64 Independent Channels)

- USB Port with Integrated 2.0 High-Speed PHY that Supports

- USB 2.0 High-Speed Device

- USB 2.0 High-Speed Host (mini-host, supporting one external device)

- USB On The Go (HS-USB OTG)

- Four 64-Bit General-Purpose Timers (each

configurable as two 32-bit timers)

- One 64-Bit Watch Dog Timer

- Two UARTs (One fast UART with RTS and CTS Flow Control)

- Five Serial Port Interfaces (SPI) each with two Chip-Selects

- One Master/Slave Inter-Integrated Circuit (I<sup>2</sup>C) Bus™

- One Multi-Channel Buffered Serial Port (McBSP)

- I2S

- AC97 Audio Codec Interface

- S/PDIF via Software

- Standard Voice Codec Interface (AIC12)

- SPI Protocol (Master Mode Only)

- Direct Interface to T1/E1 Framers

- Time Division Multiplexed Mode (TDM)

- 128 Channel Mode

- Four Pulse Width Modulator (PWM) Outputs

- · Four RTO (Real Time Out) Outputs

- Up to 104 General-Purpose I/O (GPIO) Pins (Multiplexed with Other Device Functions)

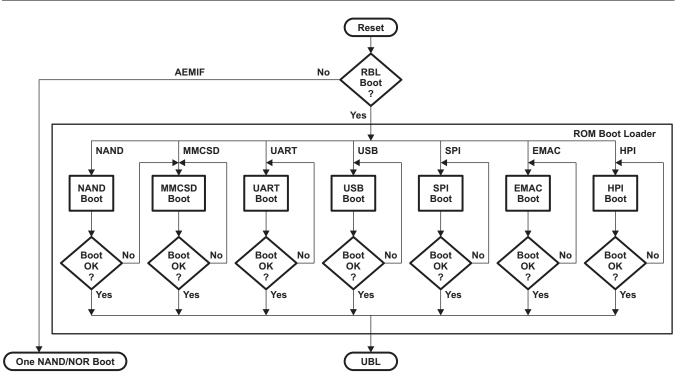

- Boot Modes

- On-Chip ARM ROM Bootloader (RBL) to Boot From NAND Flash, MMC/SD, UART, USB, SPI, EMAC, or HPI

- AEMIF (NOR and OneNAND)

- Configurable Power-Saving Modes

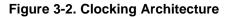

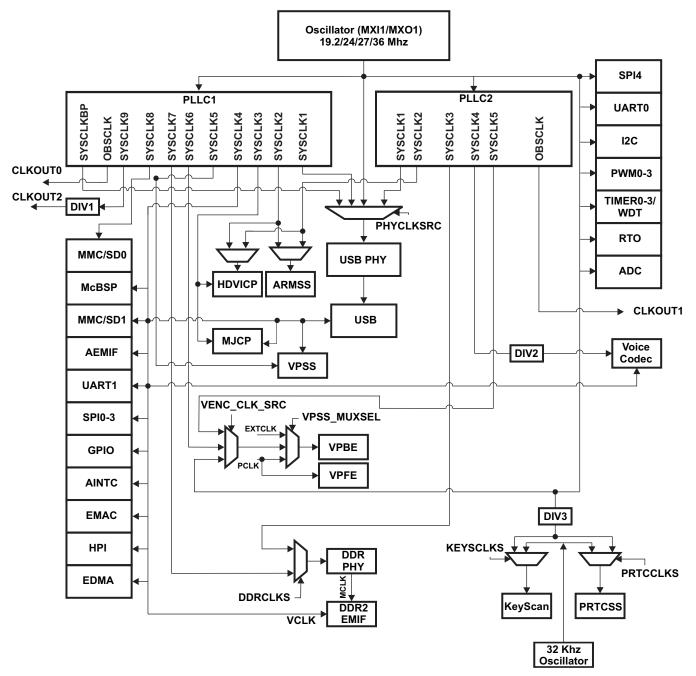

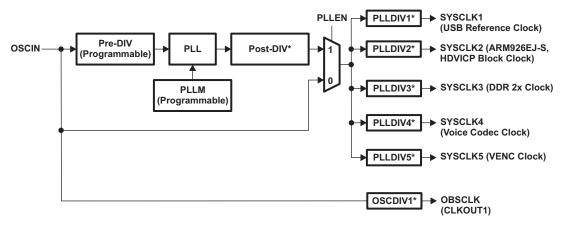

- Crystal or External Clock Input (typically 19.2 MHz, 24 MHz, 27 MHz or 36 MHz)

- Flexible PLL Clock Generators

- Debug Interface Support

- IEEE-1149.1 (JTAG<sup>™</sup>) Boundary-Scan-Compatible

- ETB (Embedded Trace Buffer) with 4K-Bytes Trace Buffer memory

- Device Revision ID Readable by ARM

- 338-Pin Ball Grid Array (BGA) Package (ZCE Suffix), 0.65-mm Ball Pitch

- 65nm Process Technology

- 3.3-V and 1.8-V I/O, 1.35-V Internal

- Community Resources

- TI E2E Community

- TI Embedded Processors Wiki

2

SPRS668C-APRIL 2010-REVISED JUNE 2011

### 1.2 Description

Developers can now deliver crystal clear multi-format video at up to 1080p H.264 at 30fps (encode and closed-looped decode) in their digital video designs without concerns of video format support, constrained network bandwidth, limited system storage capacity or cost with the new TMS320DM368 DaVinci<sup>™</sup> video processors from Texas Instruments Incorporated (TI).

The DM368 is capable of achieving HD video processing at 1080p 30fps H.264 and is completely pin-to-pin compatible with the DM365 processors, using the same ARM926EJ-S core running at 432 MHz. This ARM9-based DM368 device supports production-qualified H.264BP/MP/HP, MPEG-4, MPEG-2, MJPEG and VC1/WMV9 codecs providing customers with the flexibility to select the right video codec for their application. These codecs run on independent coprocessors (HDVICP and MJCP) offloading all compression needs from the main ARM core. This allows developers to obtain optimal performance from the ARM for their applications, including their multi-channel, multi-stream and multi-format needs.

Video surveillance designers achieve greater compression efficiency to provide more storage without straining the network bandwidth. Developers of media playback and camera-driven applications, such as video doorbells, digital signage, digital video recorders, portable media players and more can take advantage of the low power consumption and can ensure interoperability, as well as product scalability by taking advantage of the full suite of codecs supported on the DM368.

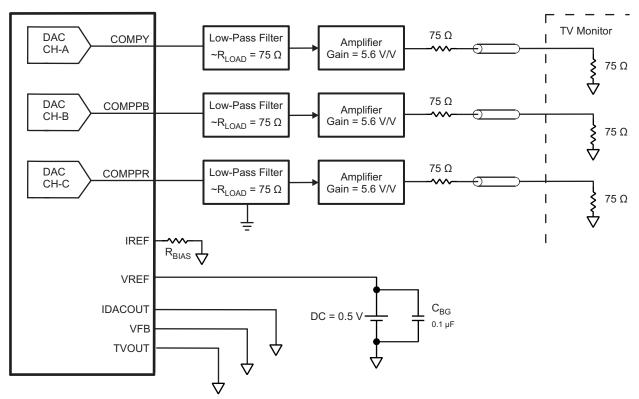

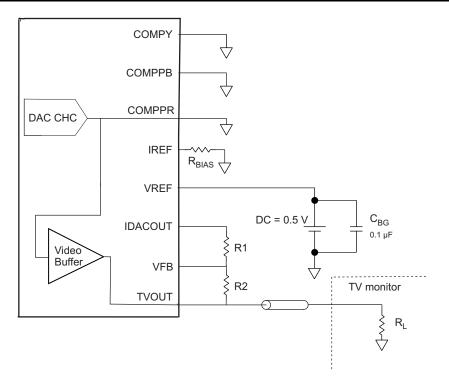

Along with multi-format HD video, the DM368 also features a suite of peripherals saving developers on system cost and complexity to enable a seamless interface to most additional external devices required for video applications. The image sensor interface is flexible enough to support CCD, CMOS, and various other interfaces such as BT.656, BT1120. The DM368 also offers a high level of integration with HD display support, including three built-in 10-bit HD analog video digital-to-analog converters (DACs), DDR2/mDDR, Ethernet MAC, USB 2.0, integrated audio, host port interface (HPI), analog-to digital converter and many more features saving developers on overall system costs, as well as real estate on their circuit boards allowing for a slimmer, sleeker design.

www.ti.com

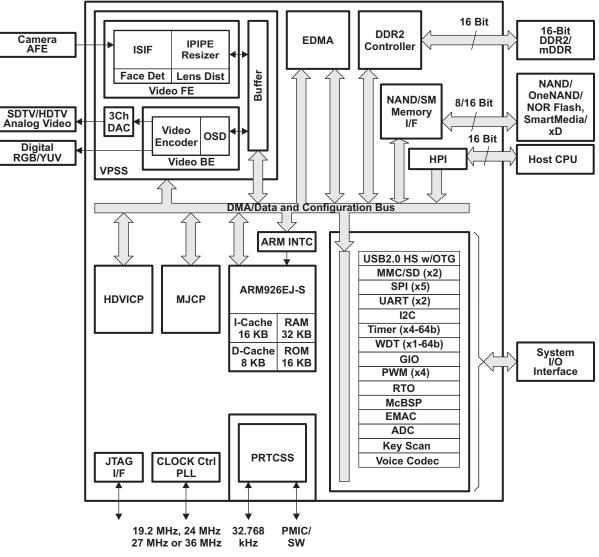

## 1.3 Functional Block Diagram

Figure 1-1 shows the functional block diagram of the TMS320DM368 device.

Figure 1-1. Functional Block Diagram

## TEXAS INSTRUMENTS

#### www.ti.com

| 1   |            | 320DM368 Digital Media System-on-Chip<br>SoC)                                                                                                         | . <u>1</u> |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|     | 1.1        | Features                                                                                                                                              | . 1        |

|     | 1.2        | Description                                                                                                                                           | . <u>3</u> |

|     | 1.3        | Functional Block Diagram                                                                                                                              |            |

| Rev | /ision     | History (Revision C)                                                                                                                                  |            |

| 2   |            | ce Overview                                                                                                                                           |            |

|     | 2.1        | Device Characteristics                                                                                                                                | . 7        |

|     | 2.2        | Device Compatibility                                                                                                                                  | . <u>8</u> |

|     | 2.3        | ARM Subsystem Overview                                                                                                                                |            |

|     | 2.4        | System Control Module                                                                                                                                 | <u>12</u>  |

|     | 2.5        | Power Management                                                                                                                                      | <u>13</u>  |

|     | 2.6        | Memory Map Summary                                                                                                                                    | 14         |

|     | 2.7        | Pin Assignments                                                                                                                                       | <u>16</u>  |

|     | 2.8        | Terminal Functions                                                                                                                                    | <u>21</u>  |

|     | 2.9        | Device Support                                                                                                                                        | <u>46</u>  |

| 3   | Devi       | ce Configurations                                                                                                                                     | <u>50</u>  |

|     | 3.1        | System Module Registers                                                                                                                               | <u>50</u>  |

|     | 3.2        | Boot Modes                                                                                                                                            | <u>51</u>  |

|     | 3.3        | Device Clocking                                                                                                                                       | <u>54</u>  |

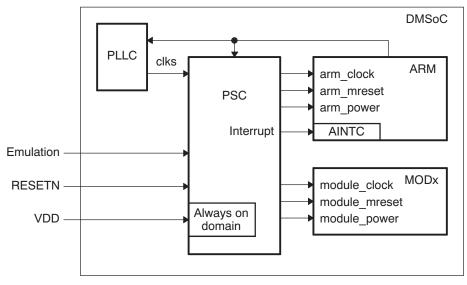

|     | 3.4        | Power and Sleep Controller (PSC)                                                                                                                      | <u>61</u>  |

|     | 3.5        | Pin Multiplexing                                                                                                                                      | <u>63</u>  |

|     | 3.6        | Device Reset                                                                                                                                          | <u>64</u>  |

|     | 3.7        | Default Device Configurations                                                                                                                         | <u>64</u>  |

|     | 3.8        | Debugging Considerations                                                                                                                              | <u>69</u>  |

| 4   | Syst       | em Interconnect                                                                                                                                       | <u>70</u>  |

| 5   |            | ce Operating Conditions                                                                                                                               | <u>71</u>  |

|     | 5.1        | Absolute Maximum Ratings Over Operating Case Temperature Range                                                                                        |            |

|     | (Unle      | ss Otherwise Noted)                                                                                                                                   | <u>71</u>  |

|     | 5.2<br>5.3 | Recommended Operating Conditions<br>Electrical Characteristics Over Recommended<br>Ranges of Supply Voltage<br>and Operating Case Temperature (Unless | <u>72</u>  |

|     |            | Otherwise Noted)                                                                                                                                      | <u>74</u>  |

# TMS320DM368

#### SPRS668C-APRIL 2010-REVISED JUNE 2011

| 6 |      | heral Information and Electrical ifications                | 76          |

|---|------|------------------------------------------------------------|-------------|

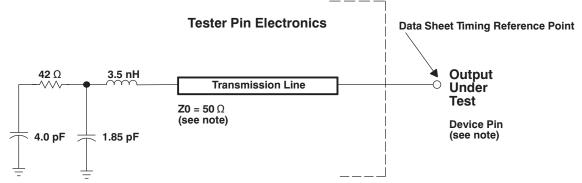

|   | 6.1  | Parameter Information Device-Specific Information          |             |

|   |      |                                                            |             |

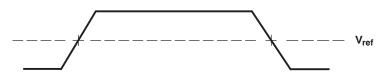

|   | 6.2  | Recommended Clock and Control Signal Transition            |             |

|   |      | Behavior                                                   | . <u>77</u> |

|   | 6.3  | Power Supplies                                             | . <u>77</u> |

|   | 6.4  | Power-Supply Sequencing                                    | . <u>78</u> |

|   | 6.5  | Reset                                                      | . <u>80</u> |

|   | 6.6  | Oscillators and Clocks                                     | . <u>81</u> |

|   | 6.7  | Power Management and Real Time Clock<br>Subsystem (PRTCSS) | . <u>85</u> |

|   | 6.8  | General-Purpose Input/Output (GPIO)                        | . <u>87</u> |

|   | 6.9  | EDMA Controller                                            | . <u>89</u> |

|   | 6.10 | External Memory Interface (EMIF)                           | . <u>99</u> |

|   | 6.11 | MMC/SD                                                     | <u>120</u>  |

|   | 6.12 | Video Processing Subsystem (VPSS) Overview                 |             |

|   |      |                                                            | <u>123</u>  |

|   | 6.13 | USB 2.0                                                    | <u>147</u>  |

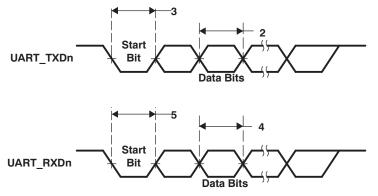

|   | 6.14 | Universal Asynchronous Receiver/Transmitter (UART)         | <u>155</u>  |

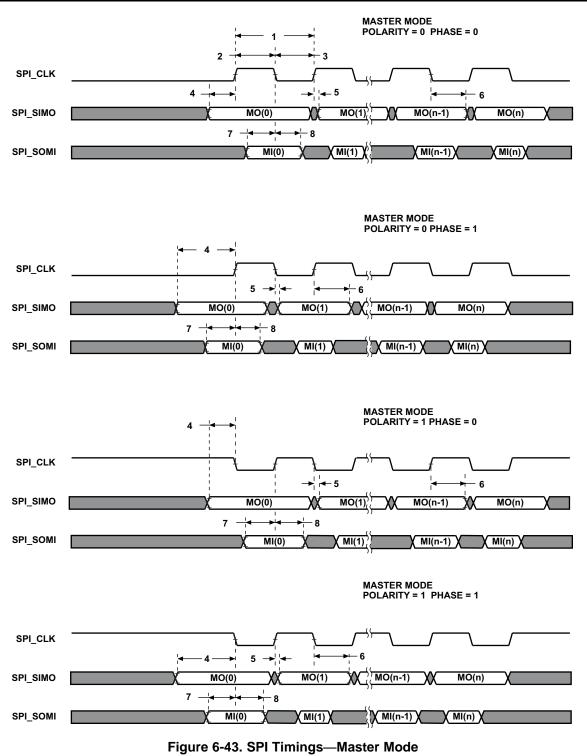

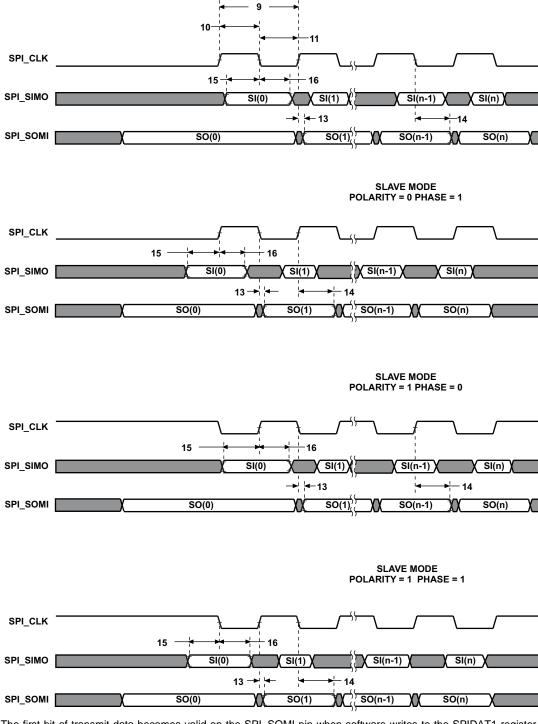

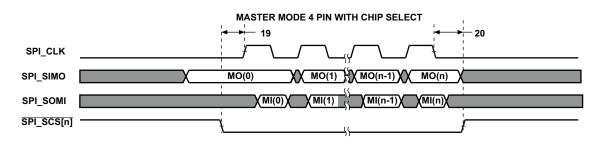

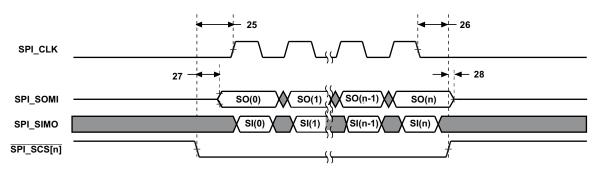

|   | 6.15 | Serial Port Interface (SPI)                                | <u>157</u>  |

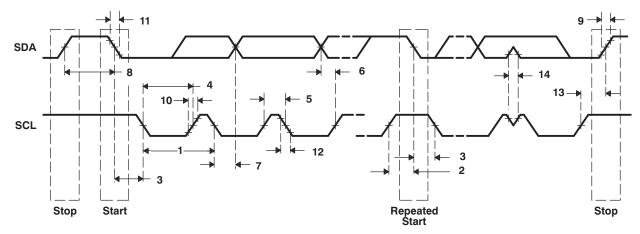

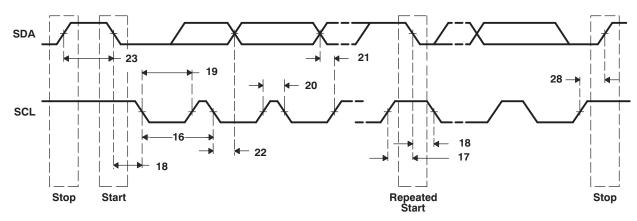

|   | 6.16 | Inter-Integrated Circuit (I2C)                             | <u>167</u>  |

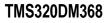

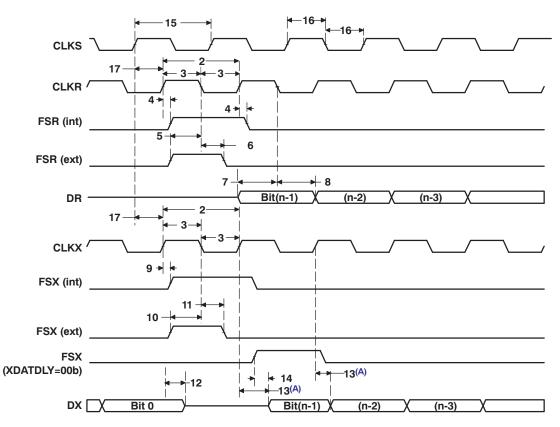

|   | 6.17 | Multi-Channel Buffered Serial Port (McBSP)                 | <u>170</u>  |

|   | 6.18 | Timer                                                      | <u>179</u>  |

|   | 6.19 | Pulse Width Modulator (PWM)                                | <u>181</u>  |

|   | 6.20 | Real Time Out (RTO)                                        | <u>183</u>  |

|   | 6.21 | Ethernet Media Access Controller (EMAC)                    | <u>185</u>  |

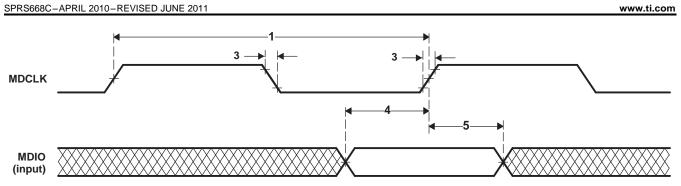

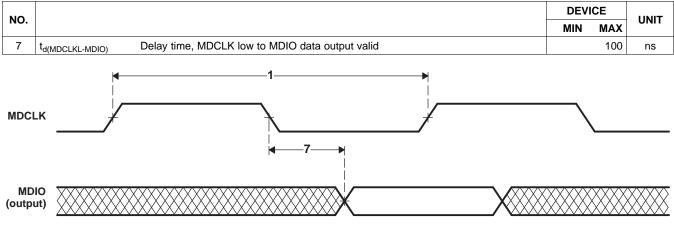

|   | 6.22 | Management Data Input/Output (MDIO)                        | <u>191</u>  |

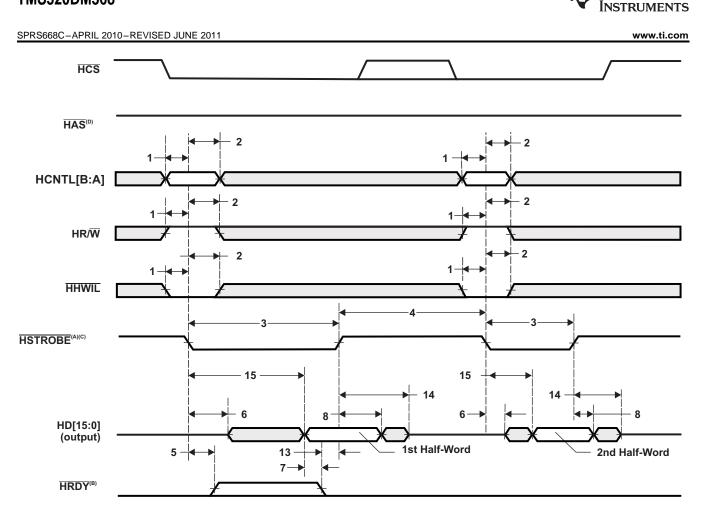

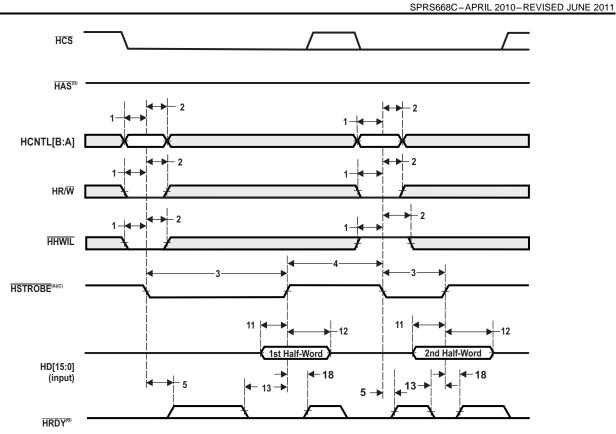

|   | 6.23 | Host-Port Interface (HPI) Peripheral                       | <u>193</u>  |

|   | 6.24 | Key Scan                                                   | <u>197</u>  |

|   | 6.25 | Analog-to-Digital Converter (ADC)                          | <u>199</u>  |

|   | 6.26 | Voice Codec                                                | <u>199</u>  |

|   | 6.27 | IEEE 1149.1 JTAG                                           | 201         |

| 7 | Mech | anical Data                                                | <b>204</b>  |

|   | 7.1  | Thermal Data for ZCE                                       | <u>204</u>  |

|   | 7.2  | Packaging Information                                      | <u>204</u>  |

### **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

highlights the technical changes made to the SPRS668B device-specific data sheet to make it a SPRS668C revision.

### **Revision C Updates**

| See           | Additions/Changes/Deletions                               |

|---------------|-----------------------------------------------------------|

| Global        | Removed sentence stating "micro-vias are not required."   |

| Figure 2-2    | Corrected J5 pin name.                                    |

| Table 2-5     | Changed TYPE of VREF pin from A I/O to A I.               |

| Table 2-5     | Changed TYPE of VCOM pin from AI to AO.                   |

| Section 3.2.1 | Added 24 MHz reference clock to ARM ROM Boot - UART mode. |

| Table 6-21    | Updated first table note.                                 |

| Table 6-22    | Updated second table note.                                |

| Table 6-26    | Updated table and added table note.                       |

# 2 Device Overview

#### 2.1 Device Characteristics

Table 2-1 provides an overview of the DMSoC. The table shows significant features of the device, including the peripherals, capacity of on-chip RAM, ARM operating frequency, the package type with pin count, etc.

|                                                              | HARDWARE FEATURES                                          | DEVICE                                                                                                   |

|--------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|                                                              | DDR2 / mDDR Memory Controller                              | DDR2 / mDDR (16-bit bus width)                                                                           |

|                                                              | Asynchronous EMIF (AEMIF)                                  | Asynchronous (8/16-bit bus width) RAM,<br>Flash (NOR, NAND, OneNAND)                                     |

|                                                              | Flash Card Interfaces                                      | Two MMC/SD<br>One SmartMedia/xD                                                                          |

|                                                              | EDMA                                                       | 64 independent DMA channels<br>Eight QDMA channels                                                       |

|                                                              | Timers                                                     | Four 64-Bit General Purpose (each<br>configurable as two separate 32-bit timers)<br>One 64-Bit Watch Dog |

|                                                              | UART                                                       | Two (one with RTS and CTS flow control)                                                                  |

| <b>D</b> · · · ·                                             | SPI                                                        | Five (each supports two slave devices)                                                                   |

| Peripherals                                                  | I <sup>2</sup> C                                           | One (Master/Slave)                                                                                       |

| Not all peripherals pins are available at the same time (For | 10/100 Ethernet MAC with Management Data I/O               | One                                                                                                      |

| more detail, see the Device                                  | Multi-Channel Buffered Serial Port [McBSP]                 | One McBSP                                                                                                |

| Configuration section).                                      | Power Management and Real Time Clock Subsystem (PRTCSS)    | RTC (32.768kHz), GPIO                                                                                    |

|                                                              | Key Scan                                                   | 4 x 4 Matrix, 5 x 3 Matrix                                                                               |

|                                                              | Voice Codec                                                | One                                                                                                      |

|                                                              | Analog-to-Digital Converter (ADC)                          | 6-channel, 10-bit Interface                                                                              |

|                                                              | General-Purpose Input/Output Port                          | Up to 104                                                                                                |

|                                                              | Pulse width modulator (PWM)                                | Four outputs                                                                                             |

|                                                              | Configurable Video Ports                                   | One Input (VPFE)<br>One Output (VPBE)                                                                    |

|                                                              | USB 2.0                                                    | High Speed Device<br>High Speed Host<br>On The Go (HS-USB-OTG)                                           |

|                                                              | Wireless Interfaces                                        | Through SDIO                                                                                             |

|                                                              | RTO                                                        | Four Channels                                                                                            |

| On-Chip CPU Memory                                           | Organization                                               | ARM<br>16-KB I-cache, 8-KB D-cache, 32-KB RAM,<br>16-KB ROM                                              |

| JTAG BSDL_ID                                                 | JTAGID register (address location: 0x01C4 0028)            | See Section 6.27.1, JTAG Register<br>Description(s)                                                      |

| CPU Frequency (Maximum)                                      | MHz                                                        | ARM: 432-MHz                                                                                             |

| Voltaga                                                      | Core (V)                                                   | 1.35 V                                                                                                   |

| Voltage                                                      | I/O (V)                                                    | 3.3 V, 1.8 V                                                                                             |

| PLL Options                                                  | Reference frequency options<br>Configurable PLL controller | 19.2 MHz, 24 MHz, 27 MHz, 36 MHz<br>PLL bypass, programmable PLL                                         |

| BGA Package                                                  | 13 x 13 mm                                                 | 338-Pin BGA (ZCE)                                                                                        |

| Process Technology                                           |                                                            | 65 nm                                                                                                    |

## Table 2-1. Characteristics of the Processor

TEXAS INSTRUMENTS

www.ti.com

#### Table 2-1. Characteristics of the Processor (continued)

|                               | HARDWARE FEATURES                                                             | DEVICE |

|-------------------------------|-------------------------------------------------------------------------------|--------|

| Product Status <sup>(1)</sup> | Product Preview (PP),<br>Advance Information (AI),<br>or Production Data (PD) | PD     |

(1) PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

### 2.2 Device Compatibility

The ARM926EJ-S RISC CPU is compatible with other ARM9 CPUs from ARM Holdings plc.

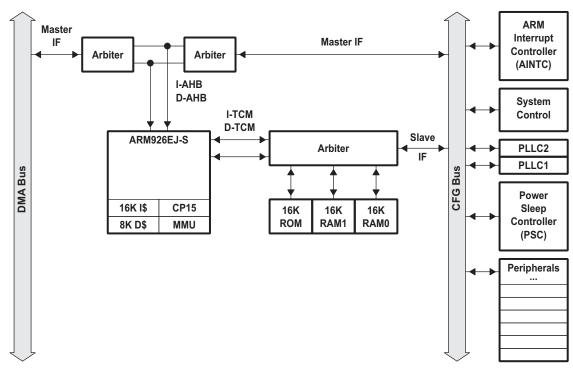

## 2.3 ARM Subsystem Overview

The ARM Subsystem contains components required to provide the ARM926EJ-S (ARM) master control of the overall device system, including the components of the ARM Subsystem, the peripherals, and the external memories.

The ARM is responsible for handling system functions such as system-level initialization, configuration, user interface, user command execution, connectivity functions, interface and control of the subsystem, etc. The ARM is master and performs these functions because it has a large program memory space and fast context switching capability, and is thus suitable for complex, multi-tasking, and general-purpose control tasks.

## 2.3.1 Components of the ARM Subsystem

The ARM Subsystem consists of the following components:

- · ARM926EJ-S RISC processor, including:

- coprocessor 15 (CP15)

- MMU

- 16KB Instruction cache

- 8KB Data cache

- Write Buffer

- Java accelerator

- ARM Internal Memories

- 32KB Internal RAM (32-bit wide access)

- 16KB Internal ROM (ARM bootloader for non-AEMIF boot modes)

- Embedded Trace Module and Embedded Trace Buffer (ETM/ETB)

- System Control Peripherals

- ARM Interrupt Controller

- PLL Controller

- Power and Sleep Controller

- System Control Module

The ARM also manages/controls all the device peripherals.

Figure 2-1 shows the functional block diagram of the ARM Subsystem.

Figure 2-1. ARM Subsystem Block Diagram

### 2.3.2 ARM926EJ-S RISC CPU

The ARM Subsystem integrates the ARM926EJ-S processor. The ARM926EJ-S processor is a member of ARM9 family of general-purpose microprocessors. This processor is targeted at multi-tasking applications where full memory management, high performance, low die size, and low power are all important. The ARM926EJ-S processor supports the 32-bit ARM and 16 bit THUMB instruction sets, enabling the user to trade off between high performance and high code density. Specifically, the ARM926EJ-S processor supports the ARMv5TEJ instruction set, which includes features for efficient execution of Java byte codes, providing Java performance similar to Just in Time (JIT) Java interpreter, but without associated code overhead.

The ARM926EJ-S processor supports the ARM debug architecture and includes logic to assist in both hardware and software debug. The ARM926EJ-S processor has a Harvard architecture and provides a complete high performance subsystem, including:

- ARM926EJ -S integer core

- CP15 system control coprocessor

- Memory Management Unit (MMU)

- Separate instruction and data Caches

- Write buffer

- · Separate instruction and data Tightly-Coupled Memories (TCMs) [internal RAM] interfaces

- Separate instruction and data AHB bus interfaces

- Embedded Trace Module and Embedded Trace Buffer (ETM/ETB)

For more complete details on the ARM9, refer to the ARM926EJ-S Technical Reference Manual, available at http://www.arm.com

# 2.3.3 CP15

The ARM926EJ-S system control coprocessor (CP15) is used to configure and control instruction and data caches, Tightly-Coupled Memories (TCMs), Memory Management Unit (MMU), and other ARM subsystem functions. The CP15 registers are programmed using the MRC and MCR ARM instructions, when the ARM in a privileged mode such as supervisor or system mode.

## 2.3.4 MMU

The ARM926EJ-S MMU provides virtual memory features required by operating systems such as Linux, WindowCE, ultron, ThreadX, etc. A single set of two level page tables stored in main memory is used to control the address translation, permission checks and memory region attributes for both data and instruction accesses. The MMU uses a single unified Translation Lookaside Buffer (TLB) to cache the information held in the page tables. The MMU features are:

- Standard ARM architecture v4 and v5 MMU mapping sizes, domains and access protection scheme.

- Mapping sizes are:

- 1MB (sections)

- 64KB (large pages)

- 4KB (small pages)

- 1KB (tiny pages)

- Access permissions for large pages and small pages can be specified separately for each quarter of the page (subpage permissions)

- Hardware page table walks

- Invalidate entire TLB, using CP15 register 8

- Invalidate TLB entry, selected by MVA, using CP15 register 8

- Lockdown of TLB entries, using CP15 register 10

### 2.3.5 Caches and Write Buffer

The size of the Instruction Cache is 16KB, Data cache is 8KB. Additionally, the Caches have the following features:

- Virtual index, virtual tag, and addressed using the Modified Virtual Address (MVA)

- Four-way set associative, with a cache line length of eight words per line (32-bytes per line) and with two dirty bits in the Dcache

- Dcache supports write-through and write-back (or copy back) cache operation, selected by memory region using the C and B bits in the MMU translation tables.

- Critical-word first cache refilling

- Cache lockdown registers enable control over which cache ways are used for allocation on a line fill, providing a mechanism for both lockdown, and controlling cache corruption

- Dcache stores the Physical Address TAG (PA TAG) corresponding to each Dcache entry in the TAG RAM for use during the cache line write-backs, in addition to the Virtual Address TAG stored in the TAG RAM. This means that the MMU is not involved in Dcache write-back operations, removing the possibility of TLB misses related to the write-back address.

- Cache maintenance operations provide efficient invalidation of, the entire Dcache or Icache, regions of the Dcache or Icache, and regions of virtual memory.

The write buffer is used for all writes to a noncachable bufferable region, write-through region and write misses to a write-back region. A separate buffer is incorporated in the Dcache for holding write-back for cache line evictions or cleaning of dirty cache lines. The main write buffer has 16-word data buffer and a four-address buffer. The Dcache write-back has eight data word entries and a single address entry.

# 2.3.6 Tightly Coupled Memory (TCM)

ARM internal RAM is provided for storing real-time and performance-critical code/data and the Interrupt

Vector table. ARM internal ROM boot modes include NAND, MMC/SD, UART, USB, SPI, EMAC, and HPI. The RAM and ROM memories interfaced to the ARM926EJ-S via the tightly coupled memory interface that provides for separate instruction and data bus connections. Since the ARM TCM does not allow instructions on the D-TCM bus or data on the I-TCM bus, an arbiter is included so that both data and instructions can be stored in the internal RAM/ROM. The arbiter also allows accesses to the RAM/ROM from extra-ARM sources (e.g., EDMA or other masters). The ARM926EJ-S has built-in DMA support for direct accesses to the ARM internal memory from a non-ARM master. Because of the time-critical nature of the TCM link to the ARM internal memory, all accesses from non-ARM devices are treated as DMA transfers.

Instruction and Data accesses are differentiated via accessing different memory map regions, with the instruction region from 0x0000 through 0x7FFF and data from 0x10000 through 0x17FFF. Placing the instruction region at 0x0000 is necessary to allow the ARM Interrupt Vector table to be placed at 0x0000, as required by the ARM architecture. The internal 32-KB RAM is split into two physical banks of 16KB each, which allows simultaneous instruction and data accesses to be accomplished if the code and data are in separate banks.

### 2.3.7 Advanced High-performance Bus (AHB)

The ARM Subsystem uses the AHB port of the ARM926EJ-S to connect the ARM to the configuration bus and the external memories. Arbiters are employed to arbitrate access to the separate D-AHB and I-AHB by the configuration bus and the external memories bus.

## 2.3.8 Embedded Trace Macrocell (ETM) and Embedded Trace Buffer (ETB)

To support real-time trace, the ARM926EJ-S processor provides an interface to enable connection of an Embedded Trace Macrocell (ETM). The ARM926ES-J Subsystem also includes the Embedded Trace Buffer (ETB). The ETM consists of two parts:

- Trace Port provides real-time trace capability for the ARM9.

- Triggering facilities provide trigger resources, which include address and data comparators, counter, and sequencers.

The device trace port is not pinned out and is instead only connected to the Embedded Trace Buffer. The ETB has a 4KB buffer memory. ETB enabled debug tools are required to read/interpret the captured trace data.

# 2.3.9 ARM Memory Mapping

The ARM memory map is shown in Table 2-3 and Table 2-4. This section describes the memories and interfaces within the ARM's memory map.

### 2.3.9.1 ARM Internal Memories

The ARM has access to the following ARM internal memories:

- 32KB ARM Internal RAM on TCM interface, logically separated into two 16KB pages to allow simultaneous access on any given cycle if there are separate accesses for code (I-TCM bus) and data (D-TCM) to the different memory regions.

- 16KB ARM Internal ROM

### 2.3.9.2 External Memories

The ARM has access to the following External memories:

- DDR2 / mDDR Synchronous DRAM

- Asynchronous EMIF / OneNAND / NOR

- NAND Flash

www.ti.com

- Flash card devices:

- MMC/SD

- xD

- SmartMedia

# 2.3.10 Peripherals

The ARM has access to all of the peripherals on the device.

# 2.3.11 ARM Interrupt Controller (AINTC)

The device ARM Interrupt Controller (AINTC) has the following features:

- Supports up to 64 interrupt channels (16 external channels)

- Interrupt mask for each channel

- Each interrupt channel can be mapped to a Fast Interrupt Request (FIQ) or to an Interrupt Request (IRQ) type of interrupt.

- · Hardware prioritization of simultaneous interrupts

- Configurable interrupt priority (2 levels of FIQ and 6 levels of IRQ)

- · Configurable interrupt entry table (FIQ and IRQ priority table entry) to reduce interrupt processing time

The ARM core supports two interrupt types: FIQ and IRQ. See the ARM926EJ-S Technical Reference Manual for detailed information about the ARM's FIQ and IRQ interrupts. Each interrupt channel is mappable to an FIQ or to an IRQ type of interrupt, and each channel can be enabled or disabled. The INTC supports user-configurable interrupt-priority and interrupt entry addresses. Entry addresses minimize the time spent jumping to interrupt service routines (ISRs). When an interrupt occurs, the corresponding highest priority ISR's address is stored in the INTC's ENTRY register. The IRQ or FIQ interrupt routine can read the ENTRY register and jump to the corresponding ISR directly. Thus, the ARM does not require a software dispatcher to determine the asserted interrupt.

# 2.4 System Control Module

The system control module is a system-level module containing status and top-level control logic required by the device. The system control module consists of a miscellaneous set of status and control registers, accessible by the ARM and supporting all of the following system features and operations:

- Device identification

- Device configuration

- Pin multiplexing control

- Device boot configuration status

- ARM interrupt and EDMA event multiplexing control

- Special peripheral status and control

- Timer64

- USB PHY control

- VPSS clock and video DAC control and status

- DDR VTP control

- Clockout circuitry

- GIO de-bounce control

- Power management

- Deep sleep

- Bandwidth Management

- Bus master DMA priority control

For more information on the System Control Module refer to Section 3, *Device Configurations* and the *TMS320DM36x DMSoC ARM Subsystem* Reference Guide (literature number <u>SPRUFG5</u>).

#### 2.5 Power Management

The device is designed for minimal power consumption. There are two components to power consumption: active power and leakage power. Active power is the power consumed to perform work and scales with clock frequency and the amount of computations being performed. Active power can be reduced by controlling the clocks in such a way as to either operate at a clock setting just high enough to complete the required operation in the required time-line or to run at a clock setting until the work is complete and then drastically cut the clocks (e.g. to PLL Bypass mode) until additional work must be performed. Leakage power is due to static current leakage and occurs regardless of the clock rate. Leakage, or standby power, is unavoidable while power is applied and scales roughly with the operating junction temperatures. Leakage power can only be avoided by removing power completely from a device or subsystem. The device includes several power management modes which are briefly described in Table 2-2. See the *TMS320DM36x DMSoC ARM Subsystem* Reference Guide (literature number <u>SPRUFG5</u>) for more information on power management.

| POWER MGMT.<br>APPLICATION<br>SCENARIO | PRTCSS | CORE<br>POWER | OSC.<br>POWER | PLL<br>CNTRLR.                    | ARM926<br>CLOCK | GIO,<br>UART,<br>I2C<br>CLOCKS | SPI,<br>PWM,<br>TIMER<br>CLOCKS | OTHER<br>PERIPH.<br>CLOCKS | DDR<br>CLOCK/<br>MODE           | DESCRIPTION                                                                                                                                                                                                  |

|----------------------------------------|--------|---------------|---------------|-----------------------------------|-----------------|--------------------------------|---------------------------------|----------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PRTCSS                                 | Active | Off           | Off           | Off                               | Off             | Off                            | Off                             | Off                        | Off                             | This condition<br>consumes the lowest<br>possible power, except<br>for the PRTCSS.                                                                                                                           |

| Deep Sleep Mode <sup>(1)</sup>         | Active | On            | Off           | Bypass<br>Mode<br>(not<br>Active) | Off             | Off                            | Off                             | Off                        | Suspend /<br>"Self-<br>Refresh" | This mode consumes<br>the second lowest<br>possible power, except<br>for PRTCSS and core<br>power, where only the<br>deep sleep circuit is on<br>in this mode.                                               |

| Standby                                | Active | On            | On            | Bypass<br>Mode                    | Off             | On                             | Off                             | Off                        | Suspend /<br>"Self-<br>Refresh" | This condition keeps<br>the minimum possible<br>modules powered-on<br>in order to wake up the<br>device. Clocks are<br>suspended except for<br>GIO (interrupts),<br>UART, and I2C (in<br>slave mode).        |

| Low-power<br>(PLL Bypass Mode)         | Active | On            | On            | Bypass<br>Mode                    | On              | On / Off                       | On / Off                        | On / Off                   | Suspend /<br>"Self-<br>Refresh" | Most clocks are<br>suspended, except for<br>ARM, GIO, UART,<br>SPI, I2C, PWM, and<br>timers. Since ARM will<br>not have access to<br>DDR, its internal<br>Cache will be either<br>frozen or not<br>accessed. |

| System Running<br>(PLL Mode)           | Active | On            | On            | PLL Mode                          | On              | On / Off                       | On / Off                        | On / Off                   | Nominal<br>Clock /<br>Operation | The device, including<br>system PLLs, are on.<br>This condition<br>conserves the least<br>amount of power.                                                                                                   |

Table 2-2. Power Management Conditions

(1) For more details, see TMS320DM36x DMSoC ARM Subsystem Reference Guide (literature number SPRUFG5)

## 2.6 Memory Map Summary

Table 2-3 shows the memory map address ranges of the device. Table 2-4 depicts the expanded map of the Configuration Space (0x01C0 0000 through 0x01FF FFFF). The device has multiple on-chip memories associated with its processor and various subsystems. To help simplify software development a unified memory map is used where possible to maintain a consistent view of device resources across all bus masters. The bus masters are the ARM, EDMA, EMAC, USB, HPI, MJCP, HDVICP and VPSS. The Master Peripherals are EMAC, USB, and HPI. Please refer to Section 4 for more details.

| Start Address | End Address | Size (Bytes) | ARM<br>Mem Map            | EDMA<br>Mem Map          | Master Periph<br>Mem Map | VPSS<br>Mem Map     |

|---------------|-------------|--------------|---------------------------|--------------------------|--------------------------|---------------------|

| 0x0000 0000   | 0x0000 3FFF | 16K          | ARM RAM0<br>(Instruction) |                          |                          |                     |

| 0x0000 4000   | 0x0000 7FFF | 16K          | ARM RAM1<br>(Instruction) | Reserved                 | Reserved                 |                     |

| 0x0000 8000   | 0x0000 BFFF | 16K          | ARM ROM<br>(Instruction)  |                          |                          |                     |

| 0x0000 C000   | 0x0000 FFFF | 16K          | Reserved                  |                          |                          |                     |

| 0x0001 0000   | 0x0001 3FFF | 16K          | ARM RAM0 (Data)           | ARM RAM0                 | ARM RAM0                 |                     |

| 0x0001 4000   | 0x0001 7FFF | 16K          | ARM RAM1 (Data)           | ARM RAM1                 | ARM RAM1                 |                     |

| 0x0001 8000   | 0x0001 BFFF | 16K          | ARM ROM                   | ARM ROM                  | ARM ROM                  |                     |

| 0x0001 C000   | 0x000F FFFF | 912K         | Reserved                  |                          |                          |                     |

| 0x0010 0000   | 0x01BB FFFF | 26M          |                           |                          |                          |                     |

| 0x01BC 0000   | 0x01BC 0FFF | 4K           | ARM ETB Mem               |                          |                          |                     |

| 0x01BC 1000   | 0x01BC 17FF | 2K           | ARM ETB Reg               | Reserved                 |                          |                     |

| 0x01BC 1800   | 0x01BC 18FF | 256          | ARM IceCrusher            |                          |                          | Reserved            |

| 0x01BC 1900   | 0x01BC FFFF | 59136        | Reserved                  |                          |                          |                     |

| 0x01BD 0000   | 0x01BF FFFF | 192K         |                           |                          |                          |                     |

| 0x01C0 0000   | 0x01FF FFFF | 4M           | CFG Bus<br>Peripherals    | CFG Bus<br>Peripherals   | CFG Bus<br>Peripherals   |                     |

| 0x0200 0000   | 0x09FF FFFF | 128M         | ASYNC EMIF (Data)         | ASYNC EMIF (Data)        |                          |                     |

| 0x0A00 0000   | 0x11EF FFFF | 127M - 16K   | Reserved                  | Reserved                 |                          |                     |

| 0x11F0 0000   | 0x11F1 FFFF | 128K         | MJCP DMA Port             | MJCP DMA Port            |                          |                     |

| 0x11F2 0000   | 0x11FF FFFF | 896K         | Reserved                  | Reserved                 |                          |                     |

| 0x1200 0000   | 0x1207 FFFF | 512K         | HDVICP DMA Port1          | HDVICP DMA Port1         | 1                        | HDVICP<br>DMA Port1 |

| 0x1208 0000   | 0x120F FFFF | 512K         | Reserved                  | HDVICP DMA Port2         | Reserved                 |                     |

| 0x1210 0000   | 0x1217 FFFF | 512K         | -                         | HDVICP DMA Port3         |                          |                     |

| 0x1218 0000   | 0x1FFF FFFF | 222.5M       |                           | Reserved                 |                          |                     |

| 0x2000 0000   | 0x2000 7FFF | 32K          | DDR EMIF Control<br>Regs  | DDR EMIF Control<br>Regs |                          |                     |

| 0x2000 8000   | 0x41FF FFFF | 544M-32K     |                           |                          |                          |                     |

| 0x4200 0000   | 0x49FF FFFF | 128M         | Reserved                  | Reserved                 |                          |                     |

| 0x4A00 0000   | 0x7FFF FFFF | 864M         |                           |                          |                          |                     |

| 0x8000 0000   | 0x8FFF FFFF | 256M         | DDR EMIF                  | DDR EMIF                 | DDR EMIF                 | DDR EMIF            |

| 0x9000 0000   | 0xFFFF FFFF | 1792M        | Reserved                  | Reserved                 | Reserved                 | Reserved            |

#### Table 2-3. Memory Map

#### www.ti.com

|                                   |              | Address      |      |

|-----------------------------------|--------------|--------------|------|

| Region                            | Start        | End          | Size |

| EDMA CC                           | 0x01C0 0000  | 0x01C0 FFFF  | 64K  |

| EDMA TCO                          | 0x01C1 0000  | 0x01C1 03FF  | 1K   |

| EDMA TC1                          | 0x01C1 0400  | 0x01C1 07FF  | 1K   |

| EDMA TC2                          | 0x01C1 0800  | 0x01C1 0BFF  | 1K   |

| EDMA TC3                          | 0x01C1 0C00  | 0x01C1 0FFF  | 1K   |

| Reserved                          | 0x01C1 1000  | 0x01C1 FFFF  | 60 K |

| UART0                             | 0x01C2 0000  | 0x01C2 03FF  | 1K   |

| Reserved                          | 0x01C2 0400  | 0x01 20 7FFF | 1K   |

| Timer 3                           | 0x01C2 0800  | 0x01C2 0BFF  | 1K   |

| Real-time out                     | 0x01C2 0C00  | 0x01C2 0FFF  | 1K   |

| I2C                               | 0x01C2 1000  | 0x01C2 13FF  | 1K   |

| Timer 0                           | 0x01C2 1400  | 0x01C2 17FF  | 1K   |

| Timer 1                           | 0x01C2 1800  | 0x01C2 1BFF  | 1K   |

| Timer 2                           | 0x01C2 1C00  | 0x01C2 1FFF  | 1K   |

| PWM0                              | 0x01C2 2000  | 0x01C2 23FF  | 1K   |

| PWM1                              | 0x01C2 2400  | 0x01C2 27FF  | 1K   |

| PWM2                              | 0x01C2 2800  | 0x01C2 2BFF  | 1K   |

| PWM3                              | 0x01C2 2C00  | 0x01C2 2FFF  | 1K   |

| SPI4                              | 0x01C2 3000  | 0x01C2 37FF  | 2K   |

| Timer 4                           | 0x01C2 3800  | 0x01C2 3BFF  | 1K   |

| ADCIF                             | 0x01C2 3C00  | 0x01C2 3FFF  | 1K   |

| Reserved                          | 0x01C2 4000  | 0x01C3 4FFF  | 112K |

| System Module                     | 0x01C4 0000  | 0x01C4 07FF  | 2K   |

| PLL Controller 1                  | 0x01C4 0800  | 0x01C4 0BFF  | 1K   |

| PLL Controller 2                  | 0x01C4 0C00  | 0x01C4 0FFF  | 1K   |

| Power/Sleep Controller            | 0x01C4 1000  | 0x01C4 1FFF  | 4K   |

| Reserved                          | 0x01C4 2000  | 0x01C4 7FFF  | 24K  |

| ARM Interrupt Controller          | 0x01C4 8000  | 0x01C4 83FF  | 1K   |

| Reserved                          | 0x01 C4 8400 | 0x01C63FFF   | 111K |

| USB OTG 2.0 Regs / RAM            | 0x01C6 4000  | 0x01C6 5FFF  | 8K   |

| SPI0                              | 0x01C6 6000  | 0x01C6 67FF  | 2K   |

| SPI1                              | 0x01C6 6800  | 0x01C6 6FFF  | 2K   |

| GPIO                              | 0x01C6 7000  | 0x01C6 77FF  | 2K   |

| SPI2                              | 0x01C6 7800  | 0x01C6 FFFF  | 2K   |

| SPI3                              | 0x01C6 8000  | 0x01C6 87FF  | 2K   |

| Reserved                          | 0x01C6 8800  | 0x01C6 87FF  | 2K   |

| PRTCSS Interface Registers        | 0x01C6 9000  | 0x01C6 93FF  | 1K   |

| KEYSCAN                           | 0x01C6 9400  | 0x01C6 97FF  | 1K   |

| HPI                               | 0x01C6 9800  | 0x01C6 9FFF  | 2K   |

| Reserved                          | 0x01C6 A000  | 0x01C6 FFFF  | 24K  |

| VPSS Subsystem                    |              |              |      |

| SP System Configuration Registers | 0x01C7 0000  | 0x01C7 00FF  | 256  |

| VPBE Clock Control Register       | 0x01C7 0200  | 0x01C7 02FF  | 256  |

| Resizer Registers                 | 0x01C7 0400  | 0x01C7 07FF  | 1K   |

| IPIPE Registers                   | 0x01C7 0800  | 0x01C7 0FFF  | 2K   |

| ISIF Registers                    | 0x01C7 1000  | 0x01C7 11FF  | 512  |

TEXAS INSTRUMENTS

www.ti.com

| IPIPEIF Registers             | 0x01C7 1200 | 0x01C7 12FF | 768          |

|-------------------------------|-------------|-------------|--------------|

| Reserved                      | 0x01C7 1400 | 0x01C7 17FF | 768          |

| FDIF Registers                | 0x01C7 1800 | 0x01C7 1BFF | 1K           |

| OSD Registers                 | 0x01C7 1C00 | 0x01C7 1CFF | 256          |

| Reserved                      | 0x01C7 1D00 | 0x01C7 1DFF | 256          |

| VENC Registers                | 0x01C7 1E00 | 0x01C7 1FFF | 512          |

| Reserved                      | 0x01C7 2000 | 0x01CF FFFF | 568K         |

| Multimedia / SD 1             | 0x01D0 0000 | 0x01D0 1FFF | 8K           |

| McBSP                         | 0x01D0 2000 | 0x01D0 3FFF | 8K           |

| Reserved                      | 0x01D0 4000 | 0x01D0 5FFF | 8K           |

| UART1                         | 0x01D0 6000 | 0x01D0 63FF | 1K           |

| Reserved                      | 0x01D0 6400 | 0x01D0 7FFF | ЗK           |

| EMAC Control Registers        | 0x01D0 7000 | 0x01D0 9FFF | 0x01D44K7FFF |

| EMAC Control Module RAM       | 0x01D0 8000 |             | 8K           |

| EMAC Control Module Registers | 0x01D0 A000 | 0x01D0 AFFF | 4K           |

| EMAC MDIO Control Registers   | 0x01D0 B000 | 0x01D0 B7FF | 2K           |

| Voice Codec                   | 0x01D0 C000 | 0x01D0 C3FF | 1K           |

| Reserved                      | 0x01D0 C400 | 0x01D0 FFFF | 17K          |

| ASYNC EMIF Control            | 0x01D1 0000 | 0x01D1 0FFF | 4K           |

| Multimedia / SD 0             | 0x01D1 1000 | 0x01D1 FFFF | 60K          |

| Reserved                      | 0x01D2 0000 | 0x01D3 FFFF | 128K         |

| Reserved                      | 0x01D4 0000 | 0x01DF FFFF | 768K         |

| Reserved                      | 0x01E0 0000 | 0x01FF FFFF | 2M           |

| ASYNC EMIF Data (CE0)         | 0x0200 0000 | 0x03FF FFFF | 32M          |

| ASYNC EMIF Data (CE1)         | 0x0400 0000 | 0x05FF FFFF | 32M          |

| Reserved                      | 0x0600 0000 | 0x09FF FFFF | 64M          |

| Reserved                      | 0x0A00 0000 | 0x0FFF FFFF | 96M          |

### Table 2-4. ARM Configuration Bus Access to Peripherals (continued)

## 2.7 Pin Assignments

Extensive use of pin multiplexing is used to accommodate the largest number of peripheral functions in the smallest possible package. Pin multiplexing is controlled using a combination of hardware configuration at device reset and software programmable register settings.

### 2.7.1 Pin Map (Bottom View)

Figure 2-2 through Figure 2-5 show the pin assignments in four quadrants (A, B, C, and D).

TEXAS INSTRUMENTS

www.ti.com

SPRS668C-APRIL 2010-REVISED JUNE 2011

|   |          |                     |          |          |            |                               |                    |                      |                         | В | С               |

|---|----------|---------------------|----------|----------|------------|-------------------------------|--------------------|----------------------|-------------------------|---|-----------------|

|   |          |                     |          |          |            |                               |                    |                      |                         | A | D               |

| J | PWCTRIO2 | PWCTRIO1            | PECTRIO0 | PWCTRIO4 | PWCTRIO3   | V <sub>DD12</sub> _<br>prtcss | V <sub>DDS18</sub> | CV <sub>DD</sub>     | V <sub>SS</sub>         |   | -<br> <br> <br> |

| н | RTCXO    | V <sub>SS_32K</sub> | RESET    | EMU1     | TRST       | V <sub>DDS33</sub>            | CV <sub>DD</sub>   | CV <sub>DD</sub>     | V <sub>SS</sub>         |   |                 |

| G | RTCXI    | TMS                 | N.B.     | TDO      | EMU0       | CV <sub>DD</sub>              | N.B.               | CV <sub>DD</sub>     | V <sub>DDA18_</sub> ADC |   |                 |

| F | GIO20    | RTCK                | GIO21    | тск      | TDI        | VDDS33                        | Vdds33             | V <sub>SSA_ADC</sub> | V <sub>SSA18_</sub> VC  |   |                 |

| E | GIO16    | GIO18               | GIO19    | GIO17    | VDD18_SLDO | GPIO46                        | GIO44              | ADC_CH0              | VDDA18_VC               |   |                 |

| D | GIO14    | GIO15               | GIO13    | Vddram   | GIO49      | GIO1                          | ADC_CH4            | ADC_CH3              | Vssa33_vc               |   |                 |

| С | GIO12    | GIO9                | N.B.     | GIO2     | GIO3       | GIO47                         | N.B.               | MICIN                | LINEO                   |   |                 |

| в | GIO11    | GIO10               | GIO6     | GIO5     | GIO0       | GPIO45                        | ADC_CH1            | MICIP                | SPP                     |   |                 |

| A | RSV0     | GIO8                | GIO7     | GIO4     | GIO48      | ADC_CH5                       | ADC_CH2            | VCOM                 | SPN                     |   |                 |

| ' | 1        | 2                   | 3        | 4        | 5          | 6                             | 7                  | 8                    | 9                       |   |                 |

(1) N.B stands for No-Ball.

| Figure | 2-2. | ZCE | Pin | Мар | [Quadrant A] |

|--------|------|-----|-----|-----|--------------|

|--------|------|-----|-----|-----|--------------|

www.ti.com

#### SPRS668C-APRIL 2010-REVISED JUNE 2011

| _ | 1               | 2                   | 3          | 4          | 5                 | 6                  | 7                        | 8                | 9                      | _          |

|---|-----------------|---------------------|------------|------------|-------------------|--------------------|--------------------------|------------------|------------------------|------------|

| w | V <sub>SS</sub> | GIO32               | GIO35      | GIO36      | GIO41             | DDR_<br>DQM1       | DDR_<br>DQ12             | DDR_<br>DQ8      | DDR_<br>DQ6            |            |

| v | GIO28           | GIO23               | GIO33      | GIO34      | GIO38             | DDR_<br>DQ15       | DDR_<br>DQ14             | DDR_<br>DQ11     | DDR_<br>DQ5            |            |

| U | GIO26           | GIO29               | N.B.       | GIO31      | GIO40             | DDR_<br>DQSN1      | N.B.                     | DDR_DQ9          | DDR_<br>DQSN0          |            |

| т | GIO25           | GIO27               | GIO24      | GIO30      | GIO37             | GIO43              | DDR_DQS1                 | DDR_<br>DQGATE0  | DDR_<br>DQGATE1        |            |

| R | RSV1            | GIO22               | Vpp        | RSV2       | GIO39             | GIO42              | DDR_DQ13                 | DDR_DQ10         | DDR_DQ7                |            |

| Ρ | USB_DM          | VSSA18_USB          | Vssa33_usb | Vdda33_usb | VDDS33            | V <sub>DDS33</sub> | V <sub>DDS18</sub>       | V <sub>SS</sub>  | V <sub>DD18</sub> _DDR |            |

| N | USB_DP          | USB_VBUS            | N.B.       | VDDA18_PLL | Vdd18_usb         | V <sub>DDS33</sub> | N.B.                     | V <sub>SS</sub>  | V <sub>DD18</sub> _DDR |            |

| М | USB_ID          | PWRCNTON            | PWRST      | Vssa       | VDDA12LDO_<br>USB | CV <sub>DD</sub>   | V <sub>SS</sub>          | V <sub>SS</sub>  | V <sub>SS</sub>        |            |

| L | MXI1            | V <sub>SS_MX1</sub> | PWCTRO3    | PWCTRO2    | PWCTR01           | V <sub>DDMXI</sub> | V <sub>SS</sub>          | V <sub>SS</sub>  | V <sub>SS</sub>        |            |

| к | MXO1            | PWCTR00             | N.B.       | PWCTRIO6   | PWCTRI05          | VDD18_PRTCSS       | V <sub>DD12_PRTCSS</sub> | CV <sub>DD</sub> | V <sub>SS</sub>        |            |

| 2 |                 |                     |            |            |                   |                    |                          |                  |                        | B C<br>A D |

(1) N.B stands for No-Ball.

www.ti.com

SPRS668C-APRIL 2010-REVISED JUNE 2011

| 10                    | 11              | 12                     | 13               | 14                                | 15     | 16      | 17       | 18      | 19              |  |

|-----------------------|-----------------|------------------------|------------------|-----------------------------------|--------|---------|----------|---------|-----------------|--|

| DDR_DQ4               | DDR_CLK         | DDR_CLK                | DDR_WE           | DDR_BA0                           | DDR_A2 | DDR_A6  | DDR_A8   | DDR_A11 | V <sub>SS</sub> |  |

| DDR_DQ3               | DDR_DQ1         | DDR_CAS                | DDR_BA2          | DDR_A1                            | DDR_A5 | DDR_A10 | DDR_A12  | EM_A13  | EM_A11          |  |

| N.B.                  | DDR_DQ0         | DDR_RAS                | N.B.             | DDR_A0                            | DDR_A4 | DDR_A9  | N.B.     | EM_A12  | EM_A10          |  |

| DDR_DQS0              | DDR_DQM0        | DDR_CS                 | DDR_BA1          | DDR_A3                            | DDR_A7 | DDR_A13 | EM_A7    | EM_A9   | EM_A8           |  |

| DDR_DQ2               | DDR_<br>PADREFP | V <sub>DD18</sub> _ddr | DDR_CKE          | V <sub>DD</sub> _<br>AEMIF1_18_33 | EM_A3  | EM_A5   | EM_BA1   | EM_A6   | EM_A4           |  |

| V <sub>DD18_DDR</sub> | DDR_VREF        | V <sub>DD18</sub> _ddr | V <sub>SS</sub>  | V <sub>DD</sub> _<br>AEMIF1_18_33 | EM_D12 | EM_D14  | EM_BA0   | EM_D15  | EM_D13          |  |

| N.B.                  | Vdd18_ddr       | V <sub>SS</sub>        | N.B.             | V <sub>SS</sub>                   | EM_D8  | EM_D11  | N.B.     | EM_D10  | EM_D9           |  |

| CV <sub>DD</sub>      | V <sub>SS</sub> | CV <sub>DD</sub>       | CV <sub>DD</sub> | VDDS18                            | EM_CLK | EM_ADV  | EM_CE[0] | EM_A2   | EM_A1           |  |

| V <sub>SS</sub>       | V <sub>SS</sub> | V <sub>DDS33</sub>     | CV <sub>DD</sub> | V <sub>DD</sub> _<br>AEMIF2_18_33 | EM_D4  | EM_D7   | EM_A0    | EM_D6   | EM_D5           |  |

| V <sub>SS</sub>       | V <sub>SS</sub> | CV <sub>DD</sub>       | N.B.             | V <sub>DD</sub> _<br>AEMIF2_18_33 | EM_D3  | EM_D1   | N.B.     | EM_D0   | EM_D2           |  |

|                       |                 |                        |                  |                                   |        |         |          |         |                 |  |

B C A D

(1) N.B stands for No-Ball.

# Figure 2-4. ZCE Pin Map [Quadrant C]

SPRS668C-APRIL 2010-REVISED JUNE 2011

| С |                    |                        |                           |                           |                    |                |                  |                  |                  |                  |   |

|---|--------------------|------------------------|---------------------------|---------------------------|--------------------|----------------|------------------|------------------|------------------|------------------|---|

| D |                    |                        |                           |                           |                    |                |                  |                  |                  |                  |   |

|   | V <sub>SS</sub>    | V <sub>SS</sub>        | CV <sub>DD</sub>          | V <sub>SS</sub>           | CV <sub>DD</sub>   | EM_WE          | MMCSD0_CLK       | EM_CE[1]         | EM_WAIT          | EM_OE            |   |

|   | V <sub>SS</sub>    | V <sub>DDS18</sub>     | CV <sub>DD</sub>          | V <sub>DDS33</sub>        | V <sub>DDS18</sub> | MMCSD0_<br>CMD | MMCSD0_<br>DATA3 | MMCSD0_<br>DATA2 | MMCSD0_<br>DATA0 | MMCSD0_<br>DATA1 |   |

|   | N.B.               | V <sub>SS</sub>        | V <sub>SS</sub>           | N.B.                      | V <sub>DDS18</sub> | HSYNC          | YOUT7            | N.B.             | VSYNC            | YOUT6            |   |

|   | V <sub>DDS33</sub> | V <sub>SSA12_DAC</sub> | V <sub>DD_ISIF18_33</sub> | V <sub>DD_ISIF18_33</sub> | V <sub>SS</sub>    | YOUT5          | YOUT3            | YOUT1            | YOUT4            | YOUT2            |   |

|   | VDDA33_VC          | VSSA18_<br>DAC         | VDDA12_DAC                | C_WE_<br>FIELD            | V <sub>SS</sub>    | COUT5          | YOUT0            | COUT4            | COUT7            | COUT6            |   |

|   | VDDA18_DAC         | VREF                   | YIN4                      | PCLK                      | YIN1               | YINO           | COUT3            | COUTO            | COUT1            | COUT2            |   |

|   | N.B.               | COMPPR                 | YIN7                      | N.B.                      | HD                 | CIN6           | CIN2             | N.B.             | FIELD            | LCD_OE           |   |

|   | VFB                | IDACOUT                | COMPY                     | YIN5                      | VD                 | YIN2           | CIN5             | CIN0             | VCLK             | EXTCLK           |   |

|   | TVOUT              | IREF                   | СОМРРВ                    | YIN6                      | YIN3               | CIN7           | CIN4             | CIN3             | CIN1             | V <sub>SS</sub>  |   |

| Ľ | 10                 | 11                     | 12                        | 13                        | 14                 | 15             | 16               | 17               | 18               | 19               | - |

(1) N.B stands for No-Ball.

www.ti.com

#### 2.8 Terminal Functions

Table 2-5 provides a complete pin description list which shows external signal names, the associated pin (ball) numbers along with the mechanical package designator, the pin type, whether the pin has any internal pullup or pulldown resistors, and a functional pin description. For more detailed information on device configuration, peripheral selection, multiplexed/shared pins, and debugging considerations, see Section 3.

| Name                | BGA<br>ID | <b>Type</b><br>(1) | Group | Power<br>Supply <sup>(2)</sup> | IPU<br>IPD <sup>(3)</sup> | Reset<br>State | Description <sup>(4)</sup>                                                                                                                    |

|---------------------|-----------|--------------------|-------|--------------------------------|---------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| CIN7 <sup>(5)</sup> | A15       | I/O                | ISIF  | V <sub>DD_ISIF18_33</sub>      | IPD                       | Input          | Standard ISIF Analog Front End (AFE): raw[7]                                                                                                  |

|                     |           |                    |       |                                |                           |                | YCC 16-bit: time multiplexed between chroma:<br>CB/CR[07]                                                                                     |

|                     |           |                    |       |                                |                           |                | YCC 08-bit (which allows for 2 simultaneous decoder inputs), it is time multiplexed between luma and chroma of the upper channel. Y/CB/CR[07] |

| CIN6 <sup>(5)</sup> | C15       | I/O                | ISIF  | V <sub>DD_ISIF18_33</sub>      | IPD                       | Input          | Standard ISIF Analog Front End (AFE): raw[6]                                                                                                  |

|                     |           |                    |       |                                |                           |                | YCC 16-bit: time multiplexed between chroma:<br>CB/CR[06]                                                                                     |

|                     |           |                    |       |                                |                           |                | YCC 08-bit (which allows for 2 simultaneous decoder inputs), it is time multiplexed between luma and chroma of the upper channel. Y/CB/CR[06] |

| CIN5 <sup>(5)</sup> | B16       | I/O                | ISIF  | V <sub>DD_ISIF18_33</sub>      | IPD                       | Input          | Standard ISIF Analog Front End (AFE): raw[5]                                                                                                  |

|                     |           |                    |       |                                |                           |                | YCC 16-bit: time multiplexed between chroma:<br>CB/CR[05]                                                                                     |

|                     |           |                    |       |                                |                           |                | YCC 08-bit (which allows for 2 simultaneous decoder inputs), it is time multiplexed between luma and chroma of the upper channel. Y/CB/CR[05] |

| CIN4 <sup>(5)</sup> | A16       | I/O                | ISIF  | V <sub>DD_ISIF18_33</sub>      | IPD                       | Input          | Standard ISIF Analog Front End (AFE): raw[4]                                                                                                  |

|                     |           |                    |       |                                |                           |                | YCC 16-bit: time multiplexed between chroma: CB/CR[04]                                                                                        |

|                     |           |                    |       |                                |                           |                | YCC 08-bit (which allows for 2 simultaneous decoder inputs), it is time multiplexed between luma and chroma of the upper channel. Y/CB/CR[04] |

| CIN3 (5)            | A17       | I/O                | ISIF  | V <sub>DD_ISIF18_33</sub>      | IPD                       | Input          | Standard ISIF Analog Front End (AFE): raw[3]                                                                                                  |

|                     |           |                    |       |                                |                           |                | YCC 16-bit: time multiplexed between chroma:<br>CB/CR[03]                                                                                     |

|                     |           |                    |       |                                |                           |                | YCC 08-bit (which allows for 2 simultaneous decoder inputs), it is time multiplexed between luma and chroma of the upper channel. Y/CB/CR[03] |

| CIN2 <sup>(5)</sup> | C16       | I/O                | ISIF  | V <sub>DD_ISIF18_33</sub>      | IPD                       | Input          | Standard ISIF Analog Front End (AFE): raw[2]                                                                                                  |

|                     |           |                    |       |                                |                           |                | YCC 16-bit: time multiplexed between chroma:<br>CB/CR[02]                                                                                     |

|                     |           |                    |       |                                |                           |                | YCC 08-bit (which allows for 2 simultaneous decoder inputs), it is time multiplexed between luma and chroma of the upper channel. Y/CB/CR[02] |

| Table | 2-5. | Pin | Descri | ptions |

|-------|------|-----|--------|--------|

|-------|------|-----|--------|--------|

(1) I = Input, O = Output, Z = High impedance, S = Supply voltage, GND = Ground, A = Analog signal.

- (2) Specifies the operating I/O supply voltage for each signal. See Section 6.3 , Power Supplies for more detail.

- (3) PD = pull-down, PU = pull-up. (To pull up a signal to the opposite supply rail, a 1 k $\Omega$  resistor should be used.)

- (4) To reduce EMI and reflections, depending on the trace length, approximately 22 Ω to 50 Ω damping resistors are recommend on the following outputs placed near the device: YOUT(0-7), COUT(0-7), HSYNC, VSYNC, LCD\_OE, FIELD, and, VCLK. The trace lengths should be minimized.

- (5) The Y input (YIN[7:0]) and C input (CIN[7:0]) buses can be swapped by programming the field bit YCINSWP in the VPFE CCD Configuration (CCDCFG) register (0x01C7 0136h).

- IF YCINSWP bit is 0 (default) YIN[7:0] = Y signal / CIN[7:0] = C signal .

IF YCINSWP bit is 1 YIN[7:0] = C signal / CIN[7:0] = Y signal

For more information, see the TMS320DM36x Video Processing Front End (VPFE) Reference Guide (literature number SPRUFG8).

Table 2-5. Pin Descriptions (continued)

| Name                                                         | BGA<br>ID | <b>Type</b><br>(1) | Group                   | Power<br>Supply <sup>(2)</sup> | IPU<br>IPD <sup>(3)</sup> | Reset<br>State | Description <sup>(4)</sup>                                                                                                                    |

|--------------------------------------------------------------|-----------|--------------------|-------------------------|--------------------------------|---------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| CIN1 <sup>(5)</sup>                                          | A18       | I/O                | ISIF                    | V <sub>DD_ISIF18_33</sub>      | IPD                       | Input          | Standard ISIF Analog Front End (AFE): raw[1]                                                                                                  |

|                                                              |           |                    |                         |                                |                           |                | YCC 16-bit: time multiplexed between chroma:<br>CB/CR[01]                                                                                     |

|                                                              |           |                    |                         |                                |                           |                | YCC 08-bit (which allows for 2 simultaneous decoder inputs), it is time multiplexed between luma and chroma of the upper channel. Y/CB/CR[01] |

| CIN0 <sup>(5)</sup>                                          | B17       | I/O                | ISIF                    | V <sub>DD_ISIF18_33</sub>      | IPD                       | Input          | Standard ISIF Analog Front End (AFE): raw[0]                                                                                                  |

|                                                              |           |                    |                         |                                |                           |                | YCC 16-bit: time multiplexed between chroma: CB/CR[00]                                                                                        |

|                                                              |           |                    |                         |                                |                           |                | YCC 08-bit (which allows for 2 simultaneous decoder inputs), it is time multiplexed between luma and chroma of the upper channel. Y/CB/CR[00] |

| YIN7 <sup>(5)</sup> / GIO103<br>/SPI3_SCLK                   | C12       | I/O                | ISIF/<br>GIO /<br>SPI3  | V <sub>DD_ISIF18_33</sub>      | IPD                       | Input          | Standard ISIF Analog Front End (AFE): raw[15]                                                                                                 |

|                                                              |           |                    |                         |                                |                           |                | YCC 16-bit: time multiplexed between luma: Y[07]                                                                                              |

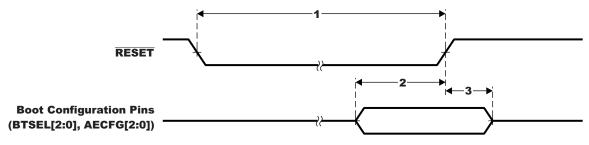

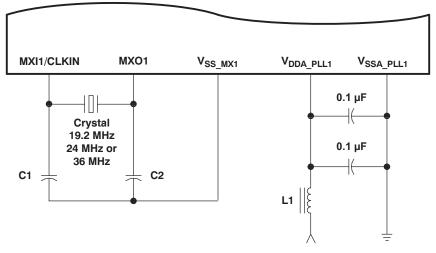

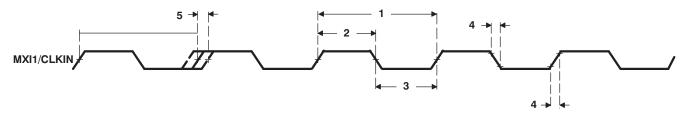

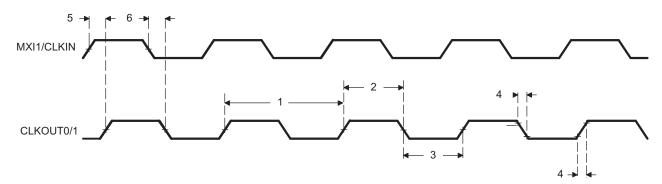

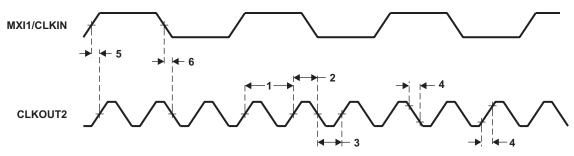

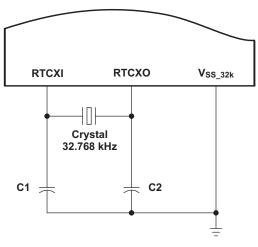

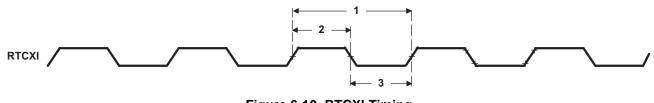

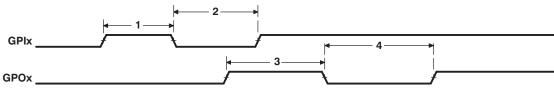

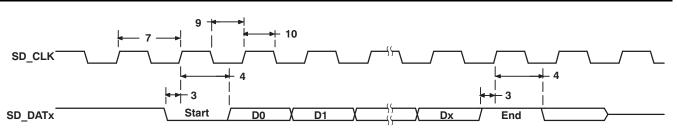

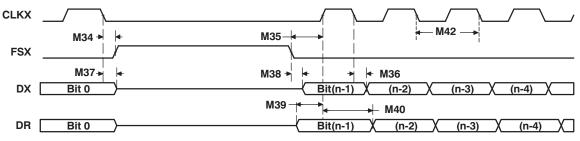

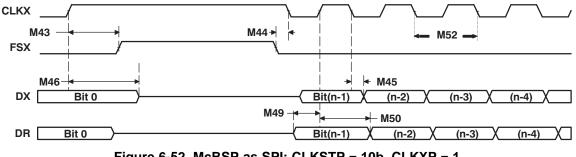

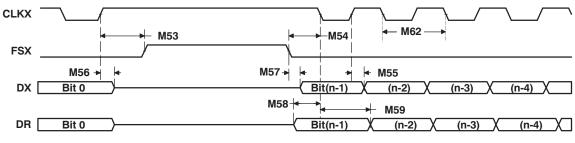

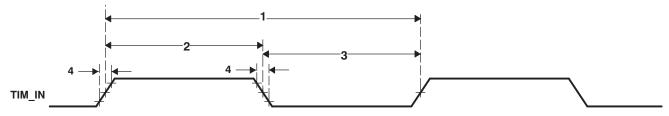

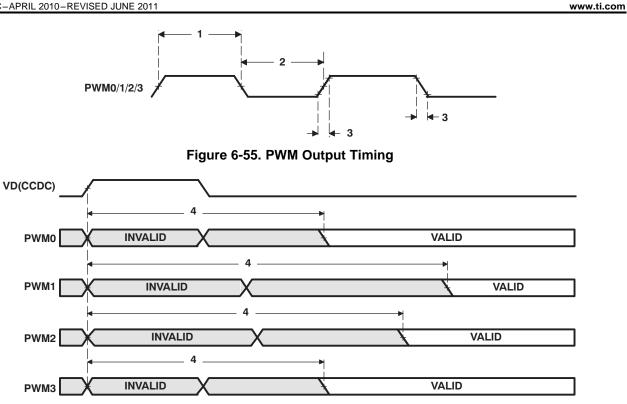

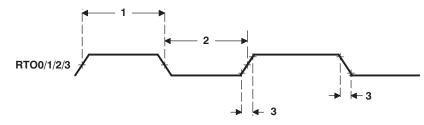

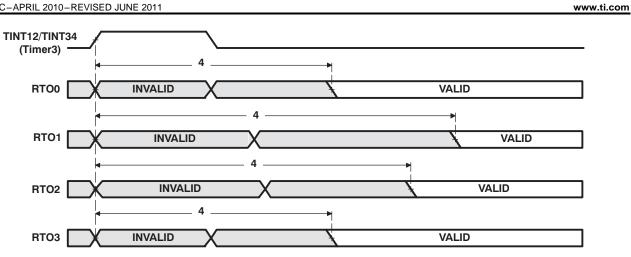

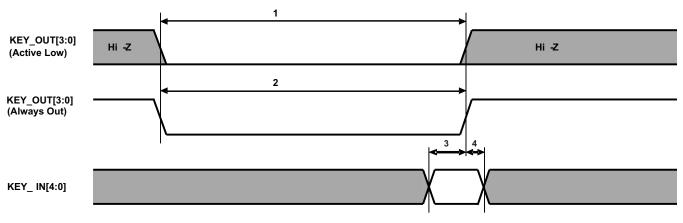

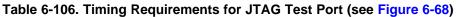

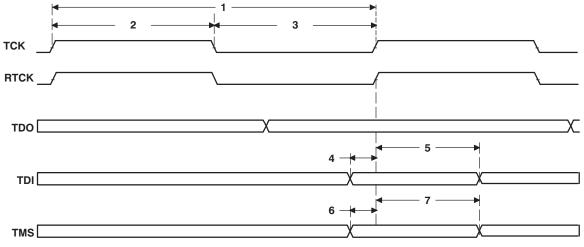

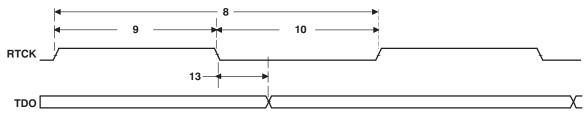

|                                                              |           |                    |                         |                                |                           |                | YCC 08-bit (which allows for 2 simultaneous decoder inputs), it is time multiplexed between luma and chroma of the lower channel. Y/CB/CR[07] |