## **Multiple-Output Regulator for Automotive LCD Displays**

## FEATURES AND BENEFITS

- Automotive-grade AEC-Q100 qualified

- Five individual output supplies

- Independent control of each output voltage

- 350 kHz to 2.25 MHz switching frequency with external synchronization capability

- <10 µA shutdown current

- Preprogrammed power-up and shutdown sequences

- Overcurrent, overvoltage, short circuit, and thermal overload protection

## **APPLICATIONS:**

- GPS

- Infotainment

- Medium LCDs

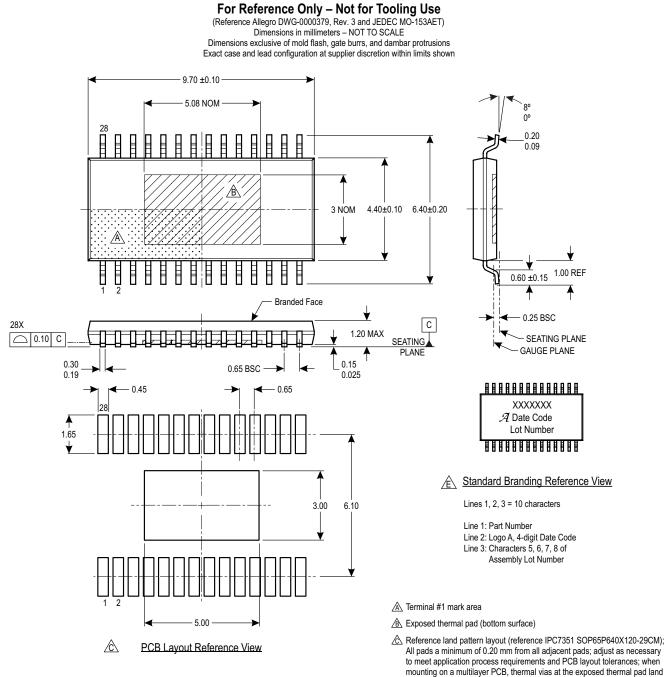

# PACKAGE: 28-pin TSSOP with exposed thermal pad (suffix LP)

Not to scale

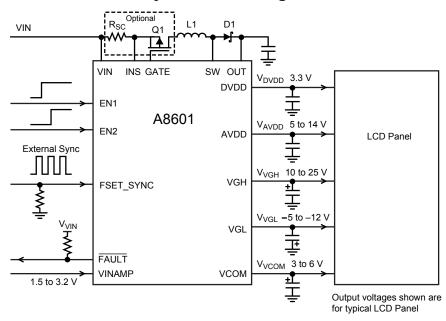

## DESCRIPTION

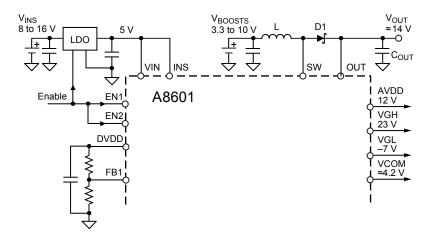

The A8601 is a fixed frequency, multiple-output supply for LCD bias. Its switching frequency can be either programmed or synchronized with an external clock signal between 350 kHz and 2.25 MHz, to minimize interference with AM and FM radio bands.

A total of five output voltages are provided, from three linear regulators and two charge-pump regulators. Each output voltage can be adjusted independently. During power-up and shutdown, the outputs are turned on and off in preprogrammed sequences, to meet the sequencing requirements for specific LCD panels.

Short-circuit protection is provided for all outputs. The boost switch is protected against overcurrent and overvoltage. Input disconnect protection is achieved by driving an external P-MOSFET.

The 28-pin exposed thermal pad TSSOP package allows operation at high ambient temperatures. It is lead (Pb) free with 100% matte-tin leadframe plating.

## System Block Diagram

#### **Selection Guide**

| Part Number  | Packing*                    | Programming                                                     |

|--------------|-----------------------------|-----------------------------------------------------------------|

| A8601KLPTR-T | 4000 pieces per 13-in. reel | Contact Allegro Sales for<br>VCOM regulator factory trim option |

\*Contact Allegro<sup>TM</sup> for additional packing options.

#### Absolute Maximum Ratings<sup>1,2</sup>

| Characteristic                  | Symbol                                                      | Notes                                     | Rating                                             | Unit |

|---------------------------------|-------------------------------------------------------------|-------------------------------------------|----------------------------------------------------|------|

| VIN and INS Pin Voltage         | V <sub>VIN</sub> , V <sub>INS</sub>                         | All voltages measured with respect to GND | -0.3 to 6.5                                        | V    |

|                                 |                                                             | Continuous                                | -0.6 to 22                                         | V    |

| SW Pin Voltage <sup>3,4</sup>   | V <sub>SW</sub>                                             | Voltage spikes (pulse width < 100 ns)     | -1 to 40                                           | V    |

| OUT Pin Voltage                 | V <sub>OUT</sub>                                            |                                           | -0.3 to 22                                         | V    |

| AVDD and FB2 Pin Voltage        | V <sub>AVDD</sub> , V <sub>FB2</sub>                        |                                           | -0.3 to<br>V <sub>OUT</sub> + 0.3                  | V    |

| CP11 Pin Voltage                | V <sub>CP11</sub>                                           | Positive charge pump                      | -0.3 to<br>V <sub>CP12</sub> + 0.3                 | V    |

| CP12 Pin Voltage                | V <sub>CP12</sub>                                           | Positive charge pump                      | -0.3 to 27                                         | V    |

| VGH Pin Voltage                 | V <sub>VGH</sub>                                            | Positive charge pump                      | -0.3 to 27                                         | V    |

| FB4 Pin Voltage                 | V <sub>FB4</sub>                                            | Positive charge pump                      | -0.3 to<br>V <sub>VGH</sub> + 0.3                  | V    |

| CP21 Pin Voltage                | V <sub>CP21</sub>                                           | Negative charge pump                      | –0.3 to 14                                         | V    |

| CP22, VGL and FB3 Pin Voltage   | V <sub>CP22</sub> , V <sub>VGL</sub> ,<br>V <sub>FB3</sub>  | Negative charge pump                      | -14 to 0.3                                         | V    |

| EN1, EN2, and FAULT Pin Voltage | V <sub>EN1</sub> , V <sub>EN2</sub> ,<br>V <sub>FAULT</sub> |                                           | -0.3 to 5.5                                        | V    |

| BIAS Pin Voltage                | V <sub>BIAS</sub>                                           |                                           | –0.3 to lower of:<br>5.5 or V <sub>VIN</sub> + 0.3 | V    |

| VCOM Pin Voltage                | V <sub>VCOM</sub>                                           |                                           | –0.3 to lower of:<br>7 or V <sub>AVDD</sub> + 0.3  | V    |

| PGND and GNDVCOM Pin Voltage    | V <sub>PGND</sub> ,<br>V <sub>GNDVCOM</sub>                 |                                           | -0.3 to 0.3                                        | V    |

| All other pins <sup>5</sup>     | _                                                           |                                           | -0.3 to 7                                          | V    |

| Operating Ambient Temperature   | T <sub>A</sub>                                              | K temperature range                       | -40 to 125                                         | °C   |

| Maximum Junction Temperature    | T <sub>J</sub> (max)                                        |                                           | 150                                                | °C   |

| Storage Temperature             | T <sub>stg</sub>                                            |                                           | -55 to 150                                         | °C   |

<sup>1</sup> Stresses beyond those listed in this table may cause permanent damage to the device. The Absolute Maximum ratings are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics table is not implied. Exposure to Absolute Maximum-rated conditions for extended periods may affect device reliability.

<sup>2</sup> All voltages referenced to AGND.

<sup>3</sup> The SW pin has internal clamp diodes to GND. Applications that forward bias this diode should take care not to exceed the IC package power dissipation limits. Note: Exact energy specification to be determined.

<sup>4</sup> The switch DMOS is self-protected. If voltage spikes exceeding 40 V are applied, the device would conduct and absorb the energy safely.

$^5$  When V<sub>VIN</sub> = 0 (no power), all inputs are limited by –0.3 to 5.5 V.

Thermal Characteristics: May require derating at maximum conditions; see application information

| Characteristic             | Symbol          | Test Conditions*                       | Value | Unit |

|----------------------------|-----------------|----------------------------------------|-------|------|

| Package Thermal Resistance | $R_{\theta JA}$ | On 4-layer PCB based on JEDEC standard | 28    | °C/W |

\*Additional thermal information available on the Allegro website.

## Multiple-Output Regulator for Automotive LCD Displays

#### **Table of Contents**

| Characteristic Performance           | 10 |  |

|--------------------------------------|----|--|

| Functional Description               | 15 |  |

| Linear Regulators                    | 15 |  |

| VCOM Regulator                       | 15 |  |

| Charge Pumps                         | 16 |  |

| Boost Controller                     | 18 |  |

| Switching Frequency                  | 19 |  |

| Continuous Conduction Mode Operation | 20 |  |

| Input Disconnect Switch              | 21 |  |

| FAULT Conditions                     | 22 |  |

| Pre-Output Fault Detection           | 23 |  |

| General Fault Detection              | 23 |  |

| Application Information              | 24 |  |

| Output Voltage Selection             | 24 |  |

| Output Capacitance                   | 25 |  |

| Operating with Separate VIN and      |    |  |

| Boost Supplies                       | 26 |  |

| Thermal Analysis                     | 26 |  |

| Component Selection Recommendations  | 28 |  |

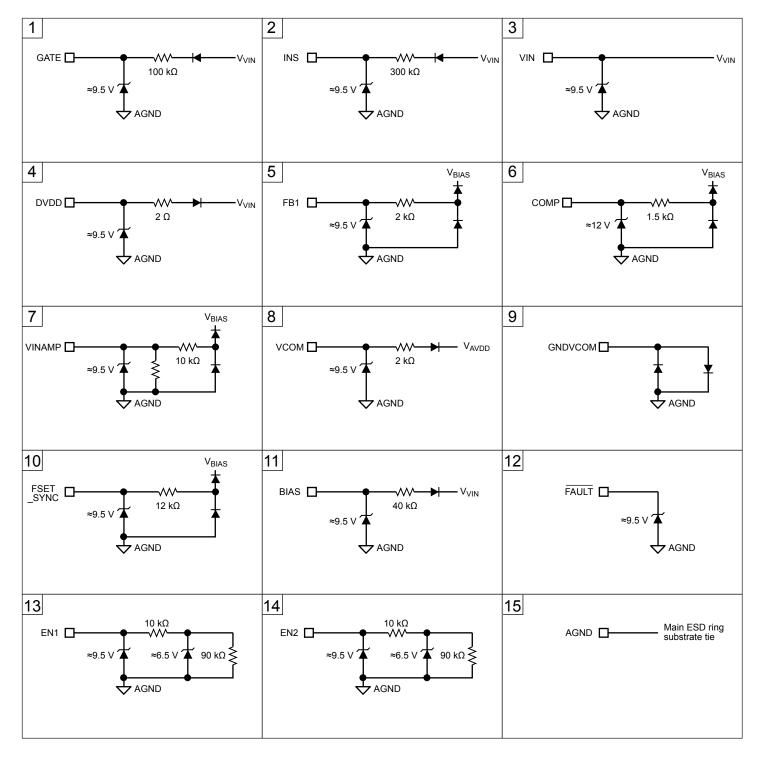

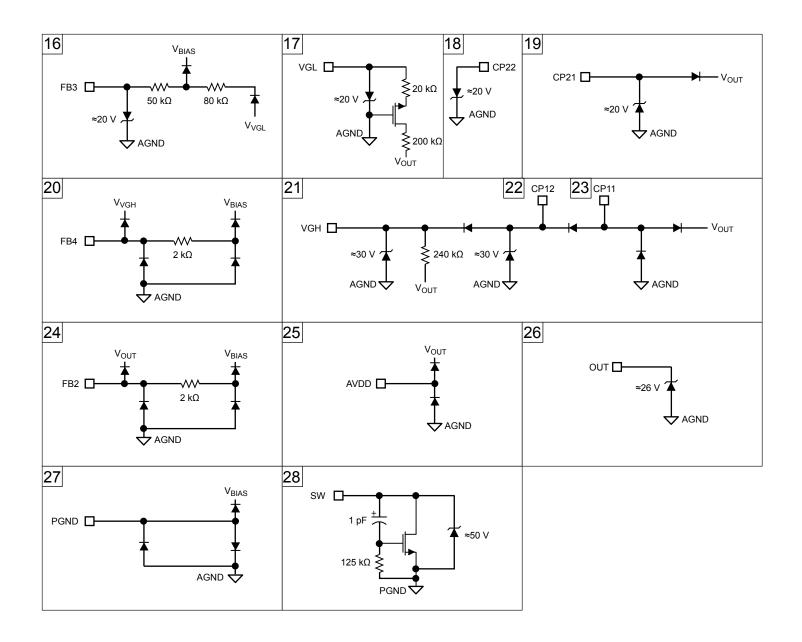

| I/O pin Equivalent Circuit Diagrams  | 29 |  |

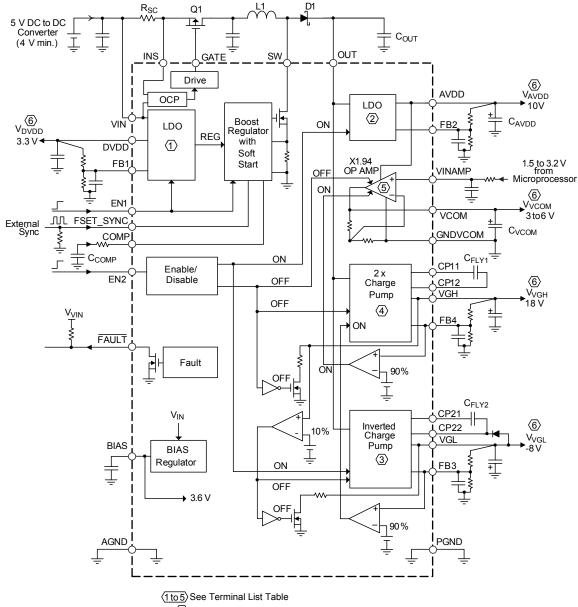

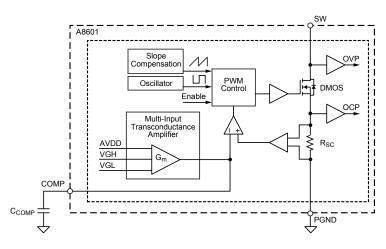

**Functional Block Diagram**

$\langle \widehat{\mathbf{6}} \rangle$  Output voltages shown are for a typical LCD panel

## Multiple-Output Regulator for Automotive LCD Displays

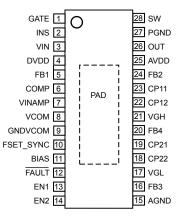

#### **Pinout Diagram**

#### **Terminal List Table**

| Number | Name          | Function                                                                                                                                         | Number | Name          | Function                                                                                                                                |

|--------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1      | GATE          | Gate driver for input disconnect P-MOSFET                                                                                                        | 15     | AGND          | Analog GND reference for signals; connect to ground plane                                                                               |

| 2      | INS           | High-side sense for input overcurrent detection                                                                                                  | 16     | FB3           | Connect to resistor divider network to set V <sub>VGL</sub>                                                                             |

| 3      | VIN           | Input supply voltage (4.0 to 5.5 V) for the IC                                                                                                   |        | (VGL)         | Inverted charge pump output                                                                                                             |

| 4      | DVDD          | Output from internal LDO (item 1 in Functional Block Diagram) powered by VIN                                                                     | 17     | VGL           | (item 3 in Functional Block Diagram)                                                                                                    |

| 5      | FB1<br>(DVDD) | Connect to resistor divider network to set<br>DVDD                                                                                               | 18     | CP22          | Capacitor terminal for inverted charge pump<br>(item 3 in Functional Block Diagram); refer to<br>Negative Charge Pump section for usage |

| 6      | COMP          | Compensation pin, connect to external COMP capacitor                                                                                             | 19     | CP21          | Capacitor terminal for inverted charge pump<br>(item 3 in Functional Block Diagram)                                                     |

| 7      | VINAMP        | Control voltage from external microprocessor                                                                                                     | 20     | FB4<br>(VGH)  | Connect to resistor divider network to set $V_{VGH}$                                                                                    |

| 8      | VCOM          | Output from operational amplifier (item 5 in<br>Functional Block Diagram), controlled by<br>VINAMP                                               | 21     | VGH           | 2× charge pump (item 4 in Functional Block<br>Diagram) output                                                                           |

| 9      | GNDVCOM       | Ground reference for VCOM                                                                                                                        | 22     | CP12          | Capacitor terminals for charge pump                                                                                                     |

|        |               | Input for synchronizing boost and charge                                                                                                         | 23     | CP11          | (item 4 in Functional Block Diagram)                                                                                                    |

| 10     | FSET_SYNC     | pump signals switching frequency to external<br>clock signal; alternatively, it can be connected<br>to an external resistor to set the switching | 24     | FB2<br>(AVDD) | Connect to external resistor network to set $V_{\text{AVDD}}$                                                                           |

|        |               | frequency                                                                                                                                        | 25     | AVDD          | Output from internal LDO (item 2 in Functional Block Diagram) powered by V <sub>OUT</sub>                                               |

| 11     | BIAS          | Output from internal 3.6 V bias regulator;<br>connect to GND via 0.1 µF ceramic capacitor                                                        | 26     | OUT           | Connect to boost output for internal LDO and charge pump regulators                                                                     |

| 12     | FAULT         | Open-drain output, pulls low in error condition                                                                                                  |        |               | 0110                                                                                                                                    |

| 13     | EN1           | Enable pin for DVDD output; system can only<br>be enabled after V <sub>VIN</sub> is above UVLO level<br>(refer to Startup Timing Diagram)        | 27     | PGND          | Power ground for internal boost switch;<br>connect this pin to ground terminal of<br>output ceramic capacitor(s)                        |

|        |               | Enable pin for the voltage outputs other than                                                                                                    | 28     | SW            | Boost converter switch node                                                                                                             |

| 14     | EN2           | DVDD; it can be activated only after $V_{VIN}$ is above UVLO and EN1 = high.                                                                     | -      | PAD           | Exposed pad (substrate of IC); solder to GND plane for better thermal conduction                                                        |

## **ELECTRICAL CHARACTERISTICS**<sup>1</sup>: Valid at $V_{VIN} = 5 V$ , EN1=EN2= high, $f_{SW} = 2 MHz$ , $V_{DVDD} = 3.3 V$ , $V_{AVDD} = 10 V$ , $V_{VGH} = 20 V$ , $V_{VCH} = -8 V$ , $T_{1} = T_{0} = -40^{\circ}$ C to 125°C, unless otherwise specified

| Characteristics                                       | Symbol                    | Test Conditions                                     |   | Min. | Тур.             | Max. | Unit |

|-------------------------------------------------------|---------------------------|-----------------------------------------------------|---|------|------------------|------|------|

| Input Voltage and Current                             | ·                         |                                                     |   |      | •                |      |      |

| Input Voltage                                         | V <sub>VIN</sub>          |                                                     | • | 4.0  | _                | 5.5  | V    |

| VIN Pin Undervoltage Lockout<br>(UVLO) Threshold      | V <sub>UVLO</sub>         | V <sub>VIN</sub> rising                             | • | 3.6  | _                | 4.0  | V    |

| VIN Pin UVLO Hysteresis                               | V <sub>UVLO(HYS)</sub>    |                                                     |   | _    | 0.15             | 0.25 | V    |

| Shutdown Bias Current                                 | I <sub>VINBIAS(SD)</sub>  | Current into VIN pin, EN1 = low                     | • | _    | 5                | 50   | μA   |

| Standby Bias Current                                  | I <sub>VINBIAS(STB)</sub> | EN1 = high, EN2 = low, no load at DVDD pin          |   | _    | 2                | -    | mA   |

| Operating Bias Current                                | I <sub>VINBIAS(OP)</sub>  | EN1 = high, EN2 = high                              |   | -    | 6.5              | -    | mA   |

| Boost Switch                                          |                           |                                                     |   |      | ~                |      |      |

| Switch Peak Current Limit                             | I <sub>SW(MAX)</sub>      | Cycle-by-cycle current limit                        | • | 1.3  | _                | 2.0  | А    |

| Switch On-Resistance                                  | R <sub>DS(on)</sub>       | I <sub>SW</sub> = 0.5 A                             |   | _    | 0.5              | -    | Ω    |

| Switch Minimum On-Time                                | t <sub>ON(MIN)</sub>      |                                                     |   | 50   | 72               | 95   | ns   |

| Switch Minimum Off-Time                               | t <sub>OFF(MIN)</sub>     |                                                     |   | 33   | 50               | 75   | ns   |

| SW Pin Leakage Current                                | I <sub>SW(LKG)</sub>      | V <sub>SW</sub> = 5 V, EN1 = low                    |   | _    | 0.1              | _    | μA   |

| OUT Pin Leakage Current                               | I <sub>OUT(LKG)</sub>     | V <sub>OUT</sub> = 5 V, EN1 = low                   |   | _    | 0.1              | _    | μA   |

| SW Pin Secondary Overvoltage<br>Protection (OVP)      | V <sub>SW(OVP)</sub>      |                                                     | • | 17.4 | 19.2             | 21.2 | V    |

| SW Pin Secondary OVP Minimum Pulse Width <sup>4</sup> | t <sub>SW(OVP)</sub>      | V <sub>SW</sub> ≥ OVP level                         |   | _    | 40               | -    | ns   |

| Switching Frequency / Synchroniza                     | tion                      |                                                     |   |      |                  |      |      |

| FSET_SYNC Pin Voltage                                 | V <sub>FSETSYNC</sub>     |                                                     |   | _    | 1.0              | -    | V    |

| FSET_SYNC Pin Current                                 | IFSETSYNC                 | Without using external synchronization signal       |   | 34   | _                | 220  | μA   |

| Switching Frequency                                   | f <sub>SW</sub>           | $R_{FSET\_SYNC} = 5.1 \text{ k}\Omega$              | • | 1.81 | 2.0              | 2.17 | MHz  |

| Synchronization Frequency                             | f <sub>SYNC</sub>         | External logic signal connected to<br>FSET_SYNC pin | • | 0.35 | _                | 2.25 | MHz  |

| Synchronization Minimum On-Time                       | t <sub>SYNC(ON)</sub>     |                                                     | • | 150  | _                | -    | ns   |

| Synchronization Minimum Off-Time                      | t <sub>SYNC(OFF)</sub>    |                                                     | • | 150  | _                | -    | ns   |

| Input Disconnect                                      |                           | •                                                   |   |      |                  |      |      |

| GATE Pin Sink Current                                 | I <sub>GATE(SNK)</sub>    | V <sub>GATE</sub> = V <sub>VIN</sub> , no fault     |   | _    | 100              | -    | μA   |

| GATE Pin Source Current                               | I <sub>GATE(SRC)</sub>    | V <sub>GATE</sub> = 0 V, fault tripped              |   | _    | 130              | _    | mA   |

| GATE Voltage at Off Condition                         | V <sub>GATE(OFF)</sub>    | EN1 = EN2 = low, or fault tripped                   |   | _    | V <sub>VIN</sub> | _    | V    |

| INS Trip Point                                        | V <sub>INS(TRIP)</sub>    | Between VIN and INS pins                            | • | 85   | 100              | 115  | mV   |

| INS Trip Blanking Time                                | t <sub>INS(BLANK)</sub>   | Sensed voltage = 2 × input current limit            |   | 1.5  | _                | 3    | μs   |

Continued on the next page...

**ELECTRICAL CHARACTERISTICS**<sup>1</sup> (continued): Valid at  $V_{VIN} = 5 V$ , EN1=EN2= high,  $f_{SW} = 2 MHz$ ,  $V_{DVDD} = 3.3 V$ ,  $V_{AVDD} = 10 V$ ,  $V_{VGH} = 20 V$ ,  $V_{VGL} = -8 V$ ,  $T_J = T_A = 25^{\circ}$ C, except • indicates specifications guaranteed for  $T_J = T_A = -40^{\circ}$ C to 125°C, unless otherwise specified

| Characteristics                                                     | Symbol                | Test Conditions                                                                                             |   | Min.  | Тур.  | Max.                   | Unit |

|---------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------|---|-------|-------|------------------------|------|

| Feedback Pins                                                       |                       | •                                                                                                           |   |       |       | · · ·                  |      |

|                                                                     | N                     | FB1, FB2, and FB4 pins                                                                                      |   | _     | 2.40  | -                      | V    |

| Feedback Sense Voltage                                              | V <sub>FBx</sub>      | FB3 pin                                                                                                     |   | _     | -1.8  | -                      | V    |

|                                                                     | N                     | FB1, FB2, and FB4 pins; V <sub>FBx</sub> rising                                                             |   | _     | 2.88  | -                      | V    |

| Output Overvoltage Fault Threshold                                  | V <sub>FBx(OV)</sub>  | V <sub>FB3</sub> falling                                                                                    |   | _     | -2.16 | -                      | V    |

| Output Linder veltage Fault Threehold                               | M                     | FB1, FB2, and FB4 pins; V <sub>FBx</sub> falling                                                            |   | _     | 1.92  | -                      | V    |

| Output Undervoltage Fault Threshold                                 | V <sub>FBx(UV)</sub>  | V <sub>FB3</sub> rising                                                                                     |   | _     | -1.44 | -                      | V    |

| Feedback Input Currents                                             |                       | FB1, FB2, and FB4 pins; $V_{FBx}$ = 2.4 V                                                                   |   | -     | -0.5  | -                      | μA   |

| Feedback input Currents                                             | I <sub>FBx</sub>      | V <sub>FB3</sub> = -1.8 V                                                                                   |   | -     | 0.5   | -                      | μA   |

|                                                                     |                       | FB1 pin                                                                                                     |   | 9     | 10    | 11                     | kΩ   |

| Feedback Load Resistance <sup>2</sup>                               | R <sub>FBx</sub>      | FB2 pin                                                                                                     |   | 24    | 25    | 26                     | kΩ   |

|                                                                     |                       | FB3 and FB4 pins                                                                                            |   | 47.5  | 50    | 52.5                   | kΩ   |

| Output Regulators                                                   |                       |                                                                                                             |   |       |       |                        |      |

| DVDD Output Voltage                                                 | V <sub>DVDD</sub>     | V <sub>VIN</sub> = 4.0 to 5.5 V                                                                             | • | 2.4   | _     | V <sub>VIN</sub> - 0.6 | V    |

| AVDD Output Voltage                                                 | V <sub>AVDD</sub>     | V <sub>VIN</sub> = 4.0 to 5.5 V                                                                             | • | 4.4   | -     | 14.8                   | V    |

| VCOM Output Voltage                                                 | V <sub>VCOM</sub>     | $V_{VIN}$ = 4.0 to 5.5 V, $V_{AVDD}$ > $V_{VCOM}$ + 1.5 V                                                   | • | 2.9   | -     | 6.8                    | V    |

| VGH Output Voltage                                                  | V <sub>VGH</sub>      | V <sub>VIN</sub> = 4.0 to 5.5 V                                                                             | • | 2.4   | -     | 26                     | V    |

| VGL Output Voltage                                                  | V <sub>VGL</sub>      | V <sub>VIN</sub> = 4.0 to 5.5 V                                                                             | • | -12.9 | -     | -5                     | V    |

| Dropout for DVDD Regulator                                          | V <sub>DVDD(DO)</sub> | Between VIN and DVDD pins;<br>V <sub>FB1</sub> = 2.33 V, I <sub>OUT</sub> = 50 mA                           | • | _     | _     | 0.6                    | V    |

| Boost Minimum Headroom for AVDD<br>Regulator                        | V <sub>AVDD(DO)</sub> | Defined as $V_{OUT} - V_{AVDD}$ ; $V_{FB2} = 2.33$ V,<br>$I_{OUT} = 100$ mA                                 |   | _     | 2     | -                      | V    |

| Boost Minimum Headroom for VGH<br>Regulator                         | V <sub>VGH(DO)</sub>  | Defined as $V_{OUT} - V_{VGH}$ / 2;<br>V <sub>FB4</sub> = 2.33 V, I <sub>OUT</sub> = 8 mA                   |   | _     | 2.4   | -                      | V    |

| Boost Minimum Headroom for VGL<br>Regulator                         | V <sub>VGL(DO)</sub>  | Defined as V <sub>OUT</sub> – (–V <sub>VGL</sub> );<br>V <sub>FB3</sub> = –1.75 V, I <sub>OUT</sub> = –8 mA |   | _     | 3.6   | -                      | V    |

| Output Pull-Down Resistor During<br>Shutdown (AVDD, VCOM, VGH, VGL) | R <sub>OUTPD</sub>    | EN1 = high, EN2 = low                                                                                       |   | _     | 250   | -                      | Ω    |

| Logic Inputs                                                        |                       | •                                                                                                           |   |       |       |                        |      |

| Input Logic High                                                    | V <sub>IH</sub>       | EN1, EN2, FSET_SYNC pins                                                                                    | • | 1.8   | _     | -                      | V    |

| Input Logic Low                                                     | V <sub>IL</sub>       | EN1, EN2, FSET_SYNC pins                                                                                    | • | _     | _     | 0.8                    | V    |

| nternal Pull-Down Resistance toAGND                                 | R <sub>ENx(PD)</sub>  | EN1, EN2 pins                                                                                               |   | _     | 100   | _                      | kΩ   |

Continued on the next page ...

**ELECTRICAL CHARACTERISTICS**<sup>1</sup> (continued): Valid at  $V_{VIN} = 5 V$ , EN1=EN2= high,  $f_{SW} = 2 MHz$ ,  $V_{DVDD} = 3.3 V$ ,  $V_{AVDD} = 10 V$ ,  $V_{VGH} = 20 V$ ,  $V_{VGL} = -8 V$ ,  $T_J = T_A = 25^{\circ}$ C, except • indicates specifications guaranteed for  $T_J = T_A = -40^{\circ}$ C to 125°C, unless otherwise specified

| Characteristics                                 | Symbol                  | Test Conditions                                                                                                                                           |   | Min. | Тур. | Max. | Unit  |

|-------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|------|------|-------|

| Output Current Capacity                         |                         |                                                                                                                                                           |   |      |      |      |       |

| DVDD Overcurrent Protection (OCP)<br>Trip Level | I <sub>DVDD(OCP)</sub>  |                                                                                                                                                           |   | 50   | _    | 90   | mA    |

| AVDD OCP Trip Level                             | I <sub>AVDD(OCP)</sub>  | Includes i <sub>VCOM</sub>                                                                                                                                |   | 200  | _    | 350  | mA    |

| VCOM OCP Trip Level                             | I <sub>VCOM</sub>       |                                                                                                                                                           |   | 60   | -    | 110  | mA    |

| VGH OCP Trip Level                              | i <sub>VGH</sub>        |                                                                                                                                                           |   | 14   | -    | 32   | mA    |

| VGL OCP Trip Level                              | i <sub>VGL</sub>        | Current into VGL pin                                                                                                                                      |   | 14   | -    | 32   | mA    |

| Output Voltage Accuracy                         |                         |                                                                                                                                                           |   |      |      |      |       |

| DVDD Load Regulation                            | V <sub>DVDDreg</sub>    | V <sub>DVDD</sub> = 3.3 V, I <sub>LOAD</sub> = 10 to 50 mA                                                                                                | • | -0.1 | _    | 0.1  | V     |

| AVDD, VGL and VGH Load<br>Regulation            | V <sub>xreg</sub>       | I <sub>LOAD</sub> = 10% to 100% of I <sub>x(OCP)</sub> (min)                                                                                              | • | -0.1 | _    | 0.1  | V     |

| DVDD Accuracy <sup>3</sup>                      | err <sub>DVDD</sub>     | V <sub>DVDD</sub> = 3.30 V                                                                                                                                | • | -2.5 | -    | 2.5  | %     |

| AVDD Accuracy <sup>3</sup>                      | err <sub>AVDD</sub>     | V <sub>AVDD</sub> = 10.0 V                                                                                                                                | • | -2.1 | -    | 2.1  | %     |

| VGH Accuracy <sup>3</sup>                       | err <sub>VGH</sub>      | V <sub>VGH</sub> = 20.0 V                                                                                                                                 | • | -2.5 | -    | 2.5  | %     |

| VGL Accuracy <sup>3</sup>                       | err <sub>VGL</sub>      | V <sub>VGL</sub> = -8.0 V                                                                                                                                 | • | -2.5 | _    | 2.5  | %     |

| VCOM Operational Amplifier                      |                         |                                                                                                                                                           |   |      |      |      |       |

| VCOM Gain <sup>4</sup>                          | A <sub>VCOM</sub>       | Defined as V <sub>VCOM</sub> / V <sub>VINAMP</sub> ;<br>1.5 V < V <sub>VINAMP</sub> < 3.21 V, –30°C < T <sub>A</sub> <<br>85°C, I <sub>LOAD</sub> = 25 mA | • | 1.92 | 1.94 | 1.96 | V/V   |

| VCOM Load Regulation <sup>4</sup>               | V <sub>VCOMreg</sub>    | I <sub>LOAD</sub> = 5 to 50 mA                                                                                                                            | • | -5   | -    | 5    | mV    |

| VCOM Temperature Coefficient <sup>4</sup>       | TC <sub>VCOM</sub>      | −30°C < T <sub>A</sub> < 85°C, I <sub>LOAD</sub> = 25 mA                                                                                                  | • | -50  | -    | 50   | μV/°C |

| Input Resistance to AGND                        | R <sub>VINAMP(PD)</sub> | VINAMP pin                                                                                                                                                |   | _    | 100  | -    | kΩ    |

| Dropout for VCOM from AVDD                      | V <sub>VCOM(DO)</sub>   | $V_{AVDD}$ = 7 V, $I_{VCOM}$ = 60 mA                                                                                                                      |   | _    | -    | 1.5  | V     |

| FAULT Pin                                       |                         |                                                                                                                                                           |   |      |      |      |       |

| FAULT Pull-Down Voltage                         | V <sub>FAULT(PD)</sub>  | Fault condition asserted,<br>pull-up current = 1 mA                                                                                                       |   | _    | _    | 0.4  | V     |

| FAULT Pin Leakage Current                       | I <sub>FAULT(LKG)</sub> | Fault condition cleared, pull-up to 5 V                                                                                                                   |   | _    | _    | 1    | μA    |

Continued on the next page ...

**ELECTRICAL CHARACTERISTICS**<sup>1</sup> (continued): Valid at  $V_{VIN} = 5 V$ , EN1=EN2= high,  $f_{SW} = 2MHz$ ,  $V_{DVDD} = 3.3 V$ ,  $V_{AVDD} = 10 V$ ,  $V_{VGH} = 20 V$ ,  $V_{VGL} = -8 V$ ,  $T_J = T_A = 25^{\circ}$ C, except • indicates specifications guaranteed for  $T_J = T_A = -40^{\circ}$ C to 125°C, unless otherwise specified

| Characteristics                          | Symbol                | Test Conditions                                                                                                     | Min. | Тур. | Max. | Unit |

|------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Fault Timers                             |                       |                                                                                                                     |      | •    | •    |      |

| Soft-Start Time-Out                      | t <sub>SS(TO)</sub>   | Maximum time allowed for any output to reach 90% of its target                                                      | 40   | 50   | 60   | ms   |

| Shutdown Time-Out                        | t <sub>SDN(TO)</sub>  | Maximum time allowed for VGH to fall to<br>10% and VGL to 30% of their respective<br>targets; EN1 = high, EN2 = low | 40   | 50   | 60   | ms   |

| Overcurrent Protection (OCP)<br>Time-Out | t <sub>OCP(TO)</sub>  | Maximum time allowed for any output to stay in an overcurrent fault condition before shutdown                       | 40   | 50   | 60   | ms   |

| Restart Delay                            | t <sub>RESTART</sub>  | Delay time after fault shutdown until the next<br>retry (repeats until Fault counter = 8)                           | 80   | 100  | 120  | ms   |

| Fault Counter Reset Time                 | t <sub>fault</sub>    | Time required after setting EN1 = low until<br>Fault counter clears                                                 | 1    | _    | _    | μs   |

| Thermal Shutdown (TSD) Protection        |                       | · · · · ·                                                                                                           |      |      | •    |      |

| TSD Threshold                            | T <sub>TSD</sub>      | Temperature rising                                                                                                  | _    | 165  | -    | °C   |

| TSD Hysteresis <sup>4</sup>              | T <sub>TSD(HYS)</sub> |                                                                                                                     | -    | 20   | -    | °C   |

<sup>1</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>2</sup> Net parallel resistance required at FBx pin in order to meet accuracy.

<sup>3</sup> Output voltage is set to required nominal value using external sense resistor network. Output current at 50% of minimum OCP trip level. Accuracy does not include mismatch error caused by external sense resistor network.

<sup>4</sup> Ensured by design and characterization, not production tested.

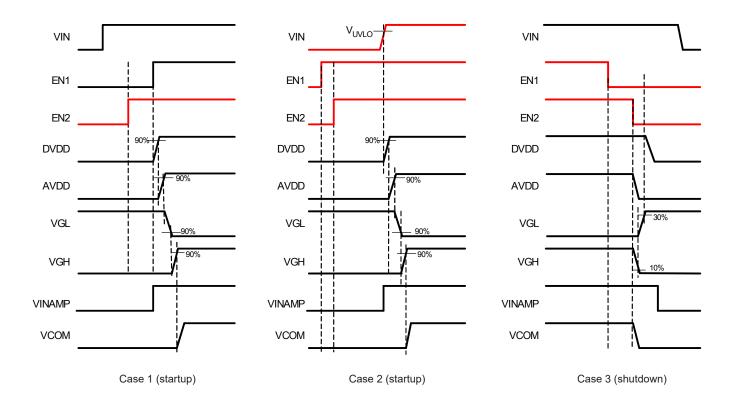

## VIN EN1 EN2 90% DVDD t<100 ms 90% AVDD :: 11 30% VGL 90% 90% VGH 10% 11 VINAMP

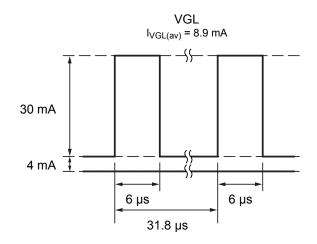

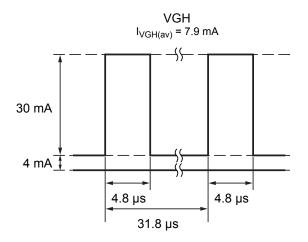

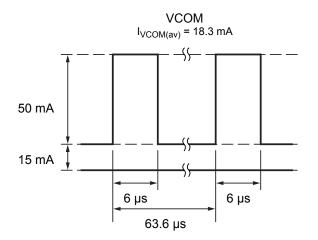

### **Characteristic Performance**

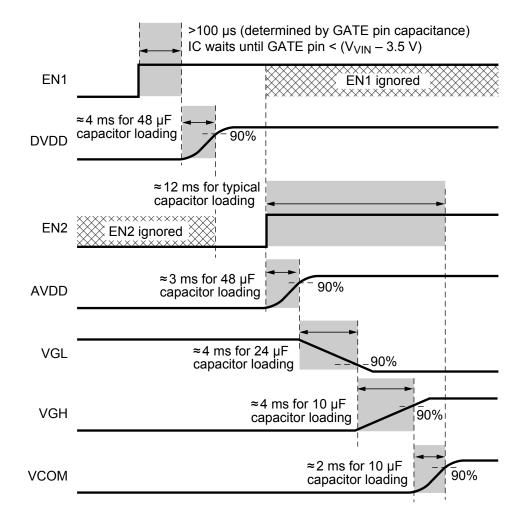

Startup and Shutdown Sequences (Normal Operation)

#### Notes:

VCOM

- Normal system startup should follow the above sequence (VIN  $\rightarrow$  EN1  $\rightarrow$  EN2).

- EN1 can only be asserted after VIN is above UVLO level, V<sub>UVLO</sub>. If asserted before that, it is ignored until VIN rises above V<sub>UVLO</sub>.

- EN2 can only be asserted when DVDD is >90% target voltage. If asserted before that, it is ignored until the condition is met.

- VGH is enabled only after the magnitude of VGL has reached >90% of its target voltage.

- VCOM output is enabled only after VGH has reached >90% of its target voltage. (A valid VINAMP must be asserted prior to this.)

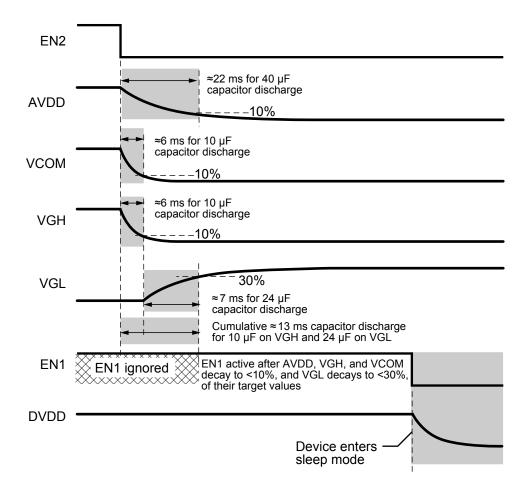

- System shutdown should start with EN2 = low, followed by EN1 = low.

- VGL shutdown can only start after VGH has dropped to 10% its original target voltage, or the VGH shutdown time-out interval has expired.

- EN1 = low can only be asserted when VGL has fallen below 30% of its target voltage. If asserted before that, it is ignored until the condition is met or the VGL shutdown time-out interval has expired.

#### Startup and Shutdown Sequences (Irregular)

#### Notes:

- Case 1 (startup). During a startup sequence, if EN2 goes high before EN1 goes high, EN2 is ignored until EN1 also goes high and DVDD has risen to 90% of its target voltage.

- Case 2 (startup). During a startup sequence, while VIN is below the UVLO level, V<sub>UVLO</sub>, the IC is in sleep mode. If either EN1 or EN2 goes high while the IC is still in sleep mode, they are ignored until VIN exceeds V<sub>UVLO</sub>.

- Case 3 (shutdown). During a shutdown sequence, if EN1 goes low before EN2 goes low, EN1 is ignored until EN2 also goes low and VGL has fallen to 30% of its target voltage, or the VGL shutdown time-out interval has expired.

### Startup Timing Diagram

Notes:

• Startup ramps are based on internal timing and are assumed to have ± 20% variation.

• An internal pull-down resistor of 250  $\Omega$  is applied to each of the regulator outputs AVDD, VGL, VGH, and VCOM as soon as EN1 = high. That means if any output capacitor was previously charged, it would be discharged by this pull-down resistor. The pull-down is removed just before each regulator is enabled.

#### **Shutdown Timing Diagram**

Notes:

- All exponential decays are based on external capacitance and internal pull-down resistance (250  $\Omega$  each for AVDD, VCOM, VGH, and VGL). The external DC load is assumed to be off or negligible.

- If any of the outputs AVDD, VCOM, or VGH does not decay to below 10% of target voltage after 50 ms, starting from EN2 is low, it is bypassed and the rest of the shutdown sequence continues without it.

- For VGL, the shutdown detection threshold is set at 30%. Only if the magnitude of VGL has dropped below 30%, when EN1 goes low the IC will shut down completely. After shutdown, all internal pull-down resistors are released, and output capacitor voltages will decay according to external load resistances.

## A8601

## **Functional Description**

The A8601 is a flexible multi-voltage regulator designed for LCD panel bias applications. It utilizes a high-efficiency boost converter, together with space-saving low-dropout regulator and charge pump circuits to provide five independently adjustable voltage outputs:

- DVDD: Typically 3.3 V. Nominal output current 20 mA, maximum 100 mA. This output is from a low-dropout regulator (item 1 in the Functional Block Diagram) powered by VIN. It is available while EN1 is high.

- AVDD: Typically between 5 and 13.3 V. Nominal current 100 mA. This output is from a low-dropout regulator (item 2 in the Functional Block Diagram) powered by VOUT. It is only available when both EN1 and EN2 are high.

- VCOM: Typically between 3 and 6 V at 50 mA. This voltage is programmable by applying a control voltage at the VINAMP pin (1.5 to 3.2 V from the application microprocessor). The power supply of this regulator is internally connected to AVDD.

- VGL: Typically between -11 and -5.4 V at 4 mA. This voltage is generated by an inverted charge pump, which is powered by VOUT.

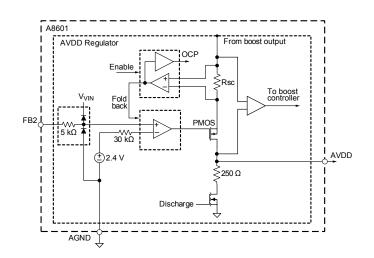

Figure 1. Representative linear regulator (AVDD shown)

• VGH: Typically between 14.5 and 24.6 V at 4 mA. This voltage is generated by a 2× charge pump, which is powered by VOUT.

#### **Linear Regulators**

The A8601 uses low-dropout linear regulators (LDO) to provide DVDD from VIN, and AVDD from boost output voltage. A representative block diagram is shown in figure 1. Each LDO is protected against output short or overloading by its own internal OCP limits. Refer to the Fault Conditions section for details.

The AVDD circuit monitors the voltage drop across its LDO (item 2 in the Functional Block Diagram). If this voltage drop is less than 2 V, the AVDD circuit sends a control signal to cause the boost voltage to increase. This ensures there is always enough headroom for regulation.

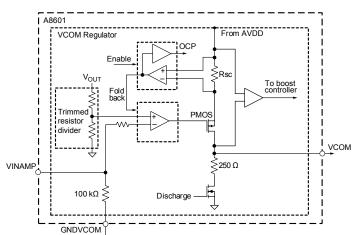

#### **VCOM Regulator**

The VCOM output voltage is determined by the input voltage of VINAMP (see figure 2), according to the following relation:

$$V_{\rm VCOM} = V_{\rm VINAMP} \times 1.94 \tag{1}$$

Figure 2. VCOM regulator

The valid range for VINAMP is between 1.5 and 3.2 V, which gives a V<sub>VCOM</sub> range of 2.9 to 6.2 V (provided that AVDD is at least 1.5 V higher than V<sub>VCOM</sub>). Beyond this range, the linearity of VCOM cannot be guaranteed.

The supply voltage of VCOM is taken from AVDD. In order to ensure there is enough headroom, AVDD must be at least 1.5 V higher than VCOM.

During the startup sequence, VCOM is allowed to ramp up only after VGH has reached 90% of its target voltage. A valid VINAMP must be asserted prior to VCOM ramp up. If VINAMP starts low (< 1.2 V), the A8601 waits as long as 50 ms for a valid VINAMP to be asserted. If VINAMP is not asserted by that time limit, a fault is generated.

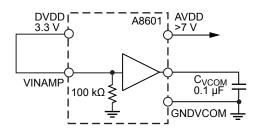

If VCOM is not required, the VCOM pin can be left open, but a small output capacitor (approximately 0.1  $\mu$ F) must be present to prevent oscillation. Make sure to connect VINAMP to a suitable voltage such as DVDD at 3.3 V. The connection to DVDD can be divided as shown in figure 3, according to the AVDD level required.

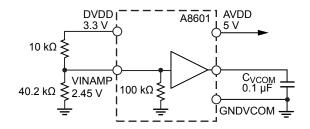

#### **Charge Pumps**

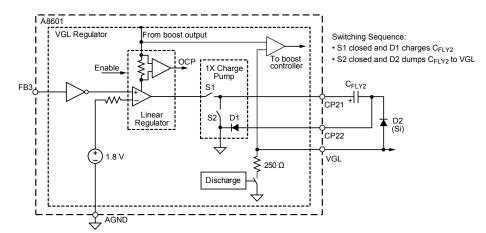

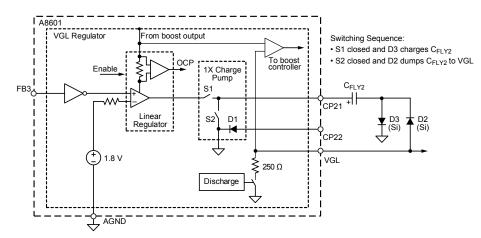

The A8601 uses a  $2 \times$  charge pump to generate VGH from boost voltage, and an inverting charge pump to generate VGL. Representative block diagrams are shown in figure 4.

The frequency of the charge pumps is the same as the boost switching frequency (or external SYNC frequency)

When an external SYNC signal is used, it is internally converted into a clock signal with the same frequency, but at 50% duty cycle.

Recommended values of the external flying capacitor, C<sub>FLYx</sub>, on

Figure 3. Configuration for unused VCOM: (upper panel) V\_{AVDD} > 7 V, and (lower panel) V\_{AVDD} = 5 V.

Figure 4A. 2× charge pump for VGH regulator

Figure 4B. Inverting (negative) charge pump for VGL regulator

Figure 4C. Inverting (negative) charge pump for VGL regulator, full output current (14 mA)

the CPxx pins depends on the switching frequency as shown in the following table; a voltage rating of 25 V is sufficient:

| Switching Frequency<br>(MHz) | C <sub>FLYx</sub><br>(μF) |

|------------------------------|---------------------------|

| 2                            | ≈0.1                      |

| 1                            | 0.22                      |

| 0.350                        | 0.47                      |

For the inverted (negative) charge pump, an external silicon diode is used between the VGL and CP22 pins. However, at high temperatures and switching frequencies (such as 125°C and 2 MHz), the maximum VGL output current is limited to about 8 mA. To achieve the full output current, 14 mA, it is necessary to use two external diodes, as shown in figure 4C.

The value of the flying capacitor can be calculated as follows:

1. The equivalent series resistance of the flying capacitor is:

$$\mathrm{ESR}_{\mathrm{FLY2}} = 1/(f_{\mathrm{SW}} \times C_{\mathrm{FLY2}}) \tag{2}$$

2. Assuming a flying capacitor ripple voltage of 100 mV, and a maximum output current of 20 mA, the series resistance is:

$$R_{\rm FLY2} = 0.1 \, (V) / 0.02 \, (A) \le 5 \, \Omega$$

3. Therefore at an  $f_{SW}$  of 2 MHz, the required capacitance,  $C_{FLY2},$  is 0.1  $\mu F.$

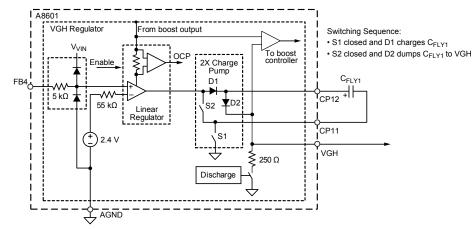

#### **Boost Controller**

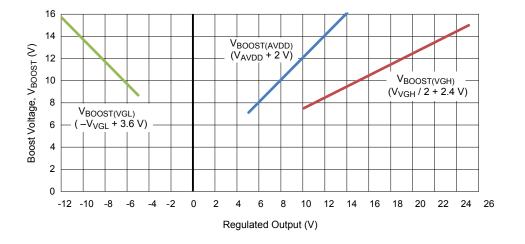

The A8601 contains an integrated DMOS switch and PWM controller to drive a boost converter. The input voltage,  $V_{VIN}$ , (5 V nominal) is boosted to an intermediate voltage,  $V_{OUT}$ , which is the lowest voltage required to keep all outputs within regulation. That is, the effective boost voltage is the highest of the boost requirement of the individual regulators, as illustrated in figure 5.

For example: assume the output requirements for a certain LCD panel are:  $V_{AVDD} = 10$  V,  $V_{VGH} = 18.5$  V and  $V_{VGL} = -7$  V, then:

• AVDD (LDO 2):  $V_{OUT} \ge V_{AVDD} + 2$  (V) = 12 V

• VGH (2× Charge Pump):  $V_{\rm OUT} \ge 0.5 \times V_{\rm VGH} + 2.4$  (V) = 11.65 V

• VGL (Inverted Charge Pump):  $V_{OUT} \ge -V_{VGL} + 3.6 \text{ (V)} = 10.6 \text{ V}$

In this example, AVDD has the highest requirement, so the intermediate voltage will be regulated at a  $V_{OUT}$  of 12 V approximately. However, if  $V_{VGH}$  were increased to 23 V, it would be the highest, and then the boost converter would increase the intermediate voltage to 13.9 V to satisfy the charge pump circuit.

Figure 5. Boost voltage requirement with respect to VGL, AVDD, and VGH

A block diagram of the A8601 boost controller circuit is shown in figure 6. The external COMP capacitor,  $C_{COMP}$ , is typically a 0.1 to 1  $\mu$ F MLCC.

The controller is protected against overvoltage and overcurrent fault conditions.

- The OVP threshold,  $V_{SW(OVP)}$ , is internally set at approximately 19 V typical. Under normal operating conditions, the boost voltage should always be lower than 16 V (as shown in figure 5), so only in the event of a fault will OVP be tripped (for example: output diode open, or wrong sense resistor values).

- The switching current limit,  $I_{SW(MAX)}$ , is protected by a pulseby-pulse OCP threshold (1.5 A typical). In the event of a heavy load or during a transient, the SW peak current may reach OCP level momentarily. In this case, the present on-time period is terminated immediately, but no signal is generated on the FAULT pin.

- In the event of a catastrophic failure (such as shorted inductor), the SW current may exceed 150% of the OCP threshold. In this case, the IC is shut down immediately.

#### **Switching Frequency**

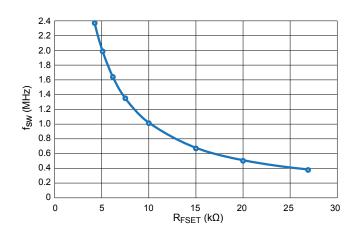

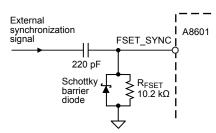

The boost stage switching frequency,  $f_{SW}$ , of the A8601 can be programmed by using an external resistor between the FSET\_SYNC pin to GND, or it can be synchronized to an external clock frequency between 350 kHz and 2.25 MHz.

During startup, the A8601 senses the FSET\_SYNC pin for any external SYNC signal. If periodic logic transitions are detected (Low < 0.8 V or High > 1.8 V), this is evaluated as an external

clock signal, and the boost switching frequency is synchronized to it. If no periodic signal is detected, the bias current flowing through FSET\_SYNC pin is used to determine the switching frequency. The bias current is set by an external resistor,  $R_{FSET}$ , on the FSET\_SYNC pin. The relation between  $R_{FSET}$  and switching frequency is given as:

$$R_{\rm FSET} = 10.21 / (f_{\rm SW} - 0.0025)$$

(3)

where  $R_{FSET}$  is in k $\Omega$  and  $f_{SW}$  is in MHz.

This relationship is charted in figure 7. For example, to get a switching frequency of 2 MHz requires an  $R_{FSET}$  of 5.11 k $\Omega$ .

Figure 7. Switching frequency versus FSET resistance

Figure 6. Boost controller circuit

Suppose the A8601 is started up with a valid external SYNC signal, but the SYNC signal is lost during normal operation. In that case, one of the following happens:

- If the external SYNC signal is high impedance (open), the A8601 continues normal operation, at the switching frequency set by  $R_{FSET}$ . No FAULT flag is generated.

- If the external SYNC signal is low (shorted to ground), the A8601 begins a shutdown sequence, at the switching frequency set by the internal 1 MHz oscillator. The FAULT pin is pulled low and the internal error counter is increased by 1.

Note: If the outcome of the second scenario is not acceptable, the circuit shown in figure 8 can be used to prevent generating a fault when the external SYNC signal goes low. When the circuit is used, after the external SYNC signal goes low, the A8601 will continue to operate normally at the switching frequency set by  $R_{FSET}$ . No FAULT flag is generated.

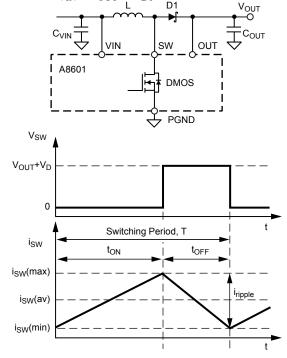

#### **Continuous Conduction Mode Operation**

It is often preferable for a boost converter to operate in continuous conduction mode (CCM) in order to reduce switching noise and input ripple. However, whether the converter can operate in CCM or discontinuous conduction mode (DCM) is determined by many parameters, including input/output voltages, output current, switching frequency, and inductor value. This is explained as follows, using simplified basic equations for a boost converter (refer to figure 9):

During SW on-time, t<sub>ON</sub>:

$$i_{\text{ripple}} = V_{\text{VIN}} / L \times t_{\text{ON}}$$

(4)

$$= V_{\rm VIN} / L \times T \times D \tag{5}$$

where T is the switching period of the boost converter and D is the duty cycle,  $t_{ON} / T$ .

Figure 8. Low FSET SYNC signal fault counteraction circuit

During SW off-time, t<sub>OFF</sub>:

$$\mathbf{i}_{\text{ripple}} = (V_{\text{OUT}} + V_{\text{D1}} - V_{\text{VIN}}) / L \times t_{\text{OFF}}$$

(5)

$$= (V_{\rm OUT} + V_{\rm D1} - V_{\rm VIN}) / L \times T \times (1 - D) \quad (7)$$

therefore:

$$V_{\rm OUT} + V_{\rm D1} = V_{\rm VIN} \times 1 / (1 - D)$$

(8)

In order to operate in CCM, the minimum inductor current must be greater than zero amperes. This means:

$$i_{SW}(\min) = i_{SW}(av) - i_{ripple} / 2 \ge 0, \text{ or }$$

(9)

$$i_{ripple} \le 2 \times i_{SW}(av)$$

Average input current is directly related to the input power and voltage, as given by:

$$V_{SW}(av) = P_{VIN} / V_{VIN} = (P_{OUT} / \eta) / V_{VIN}$$

(10)

where  $\eta$  is the efficiency of the boost converter (typically around 80%). Ripple current is determined by inductance, period, and duty cycle, as given by:

$$F_{\text{ripple}} = V_{\text{VIN}} / L \times T \times D \tag{11}$$

where D is  $1 - V_{VIN} / (V_{OUT} + V_{D1})$  from equation 8.

Figure 9. Continuous and discontinuous conduction mode factors

Allegro MicroSystems 955 Perimeter Road Manchester, NH 03103-3353 U.S.A. www.allegromicro.com For a given  $V_{VIN}$  and  $V_{OUT}$ , the duty cycle is fixed. Furthermore, for a given output power, the average input current also is fixed. Therefore, the only way to reduce ripple current is either to switch at a higher frequency (a shorter period) or to use a larger inductance.

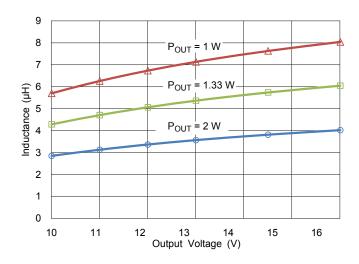

Figure 10 shows that the minimum inductance required to ensure CCM operation increases with higher output voltage (hence also with higher duty cycle), for a boost regulator with fixed input voltage and output power. Note that the chart is calculated at an  $f_{SW}$  of 1 MHz. If the frequency is reduced by half, to 500 kHz, the inductance requirement is doubled.

When selecting the boost inductor, pay attention to the following parameters:

- Inductance. This usually determines whether the boost converter operates in DCM or CCM. Refer to figure 10, or calculate minimum required inductance using the equations provided.

- DCR. Lower resistance is preferred to reduce conduction loss.

- $\bullet$  Saturation current.  $I_{SAT}$  should be greater than 1.5 A, and preferably 2 A.

- $\bullet$  Heating current.  $I_{\rm HEATING}$  should be greater than 1.5  $A_{\rm RMS}$

- $\bullet$  Physical size. Smaller size typically means lower  $I_{\text{SAT}}$  and higher DCR.

The minimum SW on-time and off-time determine the range of duty cycle, and hence the range of boost output voltage. They do not affect whether the converter operates in CCM or DCM.

Figure 10. Minimum inductance for CCM as a function of output voltage (at V<sub>VIN</sub> = 5.5 V and  $f_{SW}$  = 1 MHz)

For example, assume  $f_{SW}$  is 2 MHz (T = 500 ns),  $t_{ON(MIN)}$  is 95 ns, and  $t_{OFF(MIN)}$  is 75 ns. Then:

$$D(\min) = t_{ON(MIN)} / T = 95 \text{ (ns)} / 500 \text{ (ns)} = 19\%$$

$$D(\max) = 1 - t_{OFF(MIN)} / T = 1 - 75 \text{ (ns)} / 500 \text{ (ns)} = 85\%$$

Further, assume  $V_{VIN}$  is 4.0 to 5.5 V and  $V_{D1}$  is 0.4 V. Then the possible  $V_{OUT}$  is between 6.4 and 20.7 V. This is wider than the range required by individual regulators under all possible output combinations. Therefore, the minimum on-time and off-time are not limiting factors in output regulation.

$$\begin{split} V_{OUT}(min) &= V_{VIN}(max) \times 1/(1-D(min)) - V_{D1} = 6.4 \text{ V} \\ V_{OUT}(max) &= V_{VIN}(min) \times 1/(1-D(max)) - V_{D1} = 26.7 \text{ V} \end{split}$$

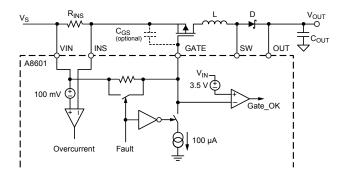

#### Input Disconnect Switch

The A8601 has a gate driver for an external PMOS, in order to provide input disconnect protection function (figure11). During normal startup, the PMOS is turned on gradually to avoid a large inrush current. In the event there is a direct short at the boost stage (either SW or OUT shorted to GND), a high input current would cause the PMOS to turn off. See the Fault Conditions section for details.

The input disconnect current threshold is calculated by:

$$I_{\rm VIN(MAX)} = V_{\rm INS(TH)} / R_{\rm INS}$$

(12)

where  $V_{INS(TH)} = 100 \text{ mV typical}$ .

Figure 11. Input disconnect switch circuit

Under normal operation, the input current is protected by the cycle-by-cycle boost switch current limit,  $I_{SW(MAX)}$ , 1.5 A (typ). Only in the event of a direct short at the boost output (SW pin) will the input disconnect switch be activated. Therefore, the input disconnect current threshold should be set slightly higher than the switch current limit; for example, choose an  $R_{INS}$  of 0.047  $\Omega$  to set an  $I_{VIN(MAX)}$  of 2 A approximately.

During a normal power-up sequence, as soon as EN1 reaches high, the A8601 begins pulling the GATE pin low by a 100  $\mu$ A current. How quickly the external PMOS turns on depends on the gate capacitance C<sub>GS</sub>. If the gate capacitance is very low, the inrush current may momentarily exceed 2 A and trip the input disconnect protection. In this case, an external C<sub>GS</sub> capacitor may be added to slow down the PMOS turn-on. A typical value of 4.7 nF should be sufficient in most cases.

When selecting the external PMOS, check the following parameters:

- $\bullet$  Drain-source breakdown voltage,  $V_{(BR)VDSS}$  , should exceed -20~V

- $\bullet$  Gate threshold voltage should be fully conducting at  $V_{GS}$  = -4 V, and cut-off at -1 V

- $R_{DS(on)}$  is rated at  $V_{GS} = -4.5$  V or similar, not at -10 V; derate for higher temperatures

#### **FAULT Conditions**

The A8601 has extensive fault detection mechanisms, to protect against all perceivable faults at the IC level (pin open, pin short to GND, pin short to neighboring pins, and so forth) and at the system level (external component open/short, component value changes from -50% to +100%, and so forth).

All feedback pins (FB1, FB2, FB3, and FB4) are monitored for overvoltage and undervoltage faults during normal operation.

In case of an output short, or an open/short in the sense resistor network, the magnitude of the sensed voltage may make a sudden change that is either +20% over, or -20% under the target voltage. This will trigger the OVP/UVP fault and force the A8601 to shut down.

OVP/UVP detections are disabled during the startup sequence. If any output fails to reach 90% of its target voltage within a timeout period,  $t_{SS(TO)}$  (50 ms typical), a fault is generated and then the A8601 shuts down.

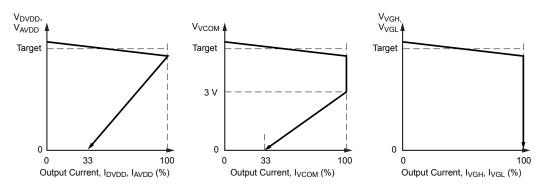

Each regulator output (DVDD, AVDD, VGH, VGL and VCOM) is protected by its own independent overcurrent limit. When an output current exceeds its limit, the corresponding regulator goes into overcurrent protection mode to protect itself from damage. See figure 11 for illustrations of the protection characteristics.

If the overcurrent condition persists for 50 ms, all regulators are turned off following the normal shutdown sequence. The same applies when there is an overvoltage fault detected at any of the feedback pins, except that the offending regulator is turned off immediately. The other outputs then shut down following normal sequence.

In general, if a fault is detected, the A8601 halts operation and pulls the  $\overline{FAULT}$  pin low. It then attempts to restart operation after a delay,  $t_{RESTART}$ , of 100 ms typical. Internally there is a Fault counter that keeps track of how many times any fault has occurred. If the Fault counter reaches eight, the A8601 is completely shut down. The Fault counter is cleared by a completed shutdown sequence with EN1=EN2=low, or by a power reset ( $V_{VIN}$  drops below UVLO). During startup, all regulators go through a soft-start process, to prevent excessive inrush current from tripping OCP. The same applies to the turn-on of the external input disconnect PMOS.

Figure 11. Overcurrent protection characteristics for DVDD, AVDD, VCOM, VGH, and VGL

#### **Pre-Output Fault Detection**

When EN1 turns on the A8601, a startup sequence is followed before the regulators are powered up. The sequence checks for extreme conditions and proceeds as described in table 1.

#### **General Fault Detection**

The faults described in table 2 are continuously monitored, whether during startup, normal operation, or shutdown.

| Step<br>Number | Step<br>Description                 | Fault Description                                                                                      | Fault<br>Tripped? |

|----------------|-------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------|

| 1              | Check VIN UVLO                      | A8601 remains powered-down until V <sub>VIN</sub> is above V <sub>UVLO</sub> .                         | No                |

| 2              | Power-up internal rail              | A8601 initializes.                                                                                     | No                |

| 3              | Check internal rail UVLO            | BIAS charges internal rail indefinitely, until V <sub>BIAS</sub> is above UVLO.                        | No                |

| 4              | Check all FBx pins for short to GND | Any FBx pin is detected as shorted after $t_{SS(TO)}$ .                                                | Yes               |

| 5              | Turn on DVDD                        | FB1 pin does not reach >90% of target (2.4 V) after t <sub>SS(TO)</sub> .                              | Yes               |

| 5              | Turn on input disconnect            | Pull-down on GATE pin does not reach < $V_{VIN}$ – 3.5 V after $t_{SS(TO)}$ .                          | Yes               |

| 6              | Turn on SW and AVDD if<br>EN2 = H   | FB2 pin does not reach >90% of target (2.4 V) after t <sub>SS(TO)</sub> .                              | Yes               |

| 7              | Turn on VGL                         | FB3 pin does not reach >90% of target (–1.8 V) after t <sub>SS(TO)</sub> .                             | Yes               |

| 8              | Turn on VGH                         | FB4 pin does not reach >90% of target (2.4 V) after t <sub>SS(TO)</sub> .                              | Yes               |

| 9              | Turn on VCOM                        | VCOM pin does not reach >90% of target (V <sub>VINAMP</sub> × A <sub>VCOM</sub> ) after $t_{SS(TO)}$ . | Yes               |

#### Table 1. Pre-Output Fault Detection Sequence

#### **Table 2. General Fault Detection**

| Fault Description                                                                                                                         | A8601 Response to Fault                                                                                                                                                                           | Fault Tripped?                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| T <sub>TSD</sub> exceeded                                                                                                                 | Shutdown immediately, without using shutdown sequence. Fault counter increased by one, retry after $t_{RESTART}$ , and temperature has dropped by $T_{TSD(HYS)}$ .                                | Yes; $\overline{FAULT}$ set during $t_{RESTART}$ |

| $V_{FB1},V_{FB2},V_{FB3},orV_{FB4}$ 20% under target                                                                                      | Shutdown using shutdown sequence.<br>Fault counter increased by one, retry after t <sub>RESTART</sub> .                                                                                           | Yes; $\overline{FAULT}$ set during $t_{RESTART}$ |

| V <sub>FB1</sub> , V <sub>FB2</sub> , V <sub>FB3</sub> , or V <sub>FB4</sub><br>20% over target                                           | Over-target regulator rail shut down without shutdown sequence.<br>Other regulator rails shut down using shutdown sequence.<br>Fault counter increased by one, retry after t <sub>RESTART</sub> . | Yes; $\overline{FAULT}$ set during $t_{RESTART}$ |

| V <sub>UVLO</sub> reached                                                                                                                 | Shutdown without using shutdown sequence.<br>Fault counter reset to 0, retry after t <sub>RESTART</sub> .                                                                                         | No                                               |

| BIAS UVLO                                                                                                                                 | Shutdown without using shutdown sequence. Fault counter reset to 0, retry after $t_{\text{RESTART}}$ .                                                                                            | No                                               |

| $\begin{array}{l} Overcurrent \mbox{ limit for } i_{DVDD}, \\ i_{AVDD},  i_{VCOM},  i_{VGH}, \mbox{ or } i_{VGL} \\ exceeded \end{array}$ | Over-limit regulator rail goes into current fold-back or current limit. Shutdown using shutdown sequence after $t_{OCP(TO)}$ . Fault counter increased by one, retry after $t_{RESTART}$ .        | Yes; $\overline{FAULT}$ set during $t_{RESTART}$ |

| $V_{\text{INS}(\text{TRIP})}$ exceeded                                                                                                    | Shutdown without using shutdown sequence.<br>Fault counter increased by one, retry after t <sub>RESTART</sub> .                                                                                   | Yes; FAULT set during t <sub>RESTART</sub>       |

| V <sub>SW(OVP)</sub> exceeded                                                                                                             | Shutdown without using shutdown sequence.<br>Fault counter increased by one, retry after t <sub>RESTART</sub> .                                                                                   | Yes; FAULT set during t <sub>RESTART</sub>       |

| $I_{SW(MAX)} {}^{\times}  150\%$ of OCP limit exceeded                                                                                    | Shutdown without using shutdown sequence.<br>Fault counter increased by one, retry after t <sub>RESTART</sub> .                                                                                   | Yes; FAULT set during t <sub>RESTART</sub>       |

VOUT

**Š** ⊾1

≷R2

VREF

$\sim$

$R_7$

25 kΩ

FB>

FB

A8601

A8601

5 kΩ

30 kΩ

∘V<sub>REF</sub>

AGND

5 kΩ

$\sim$

30 kO

∘V<sub>REF</sub>

AGND

### **Application Information**

#### **Output Voltage Selection**

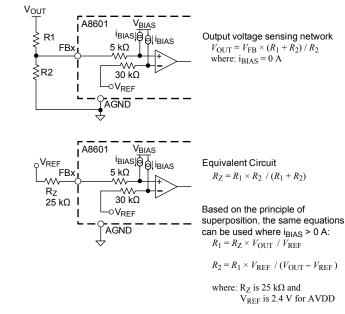

Each output voltage of DVDD, AVDD, VGH, or VGL is selected using a simple voltage-sensing (resistor divider) network, as shown in figure 12.

In actual implementation there is a small bias current that is flowing out from each positive FBx pin, and the direction is reversed for any negative FBx pin. This is necessary to detect any pin-open fault at an FBx pin. As shown in figure 13, a common bias current is injected into both the (+) and the (-) terminals of the operational-amplifier. Due to the principal of superposition, the same set of equations as in figure 1 can be used to determine values for R1 and R2 in figure 13.

$V_{FB}$  is the regulation voltage for the feedback pins, and it is specified as 2.40 V for FB1 (DVDD), FB2 (AVDD), and FB4 (VGH). For FB3 it is specified as -1.80 V. The following considerations affect voltage selection:

• To cancel the offset error introduced by input bias currents, and to assure regulation loop stability, it is necessary to keep the

Output voltage sensing network

$V_{OUT} = V_{FB} \times (R_1 + R_2) / R_2$ where:  $V_{FB} = V_{REF}$

Equivalent Circuit

$R_Z = R_1 \times R_2 / (R_1 + R_2)$

Combining the two equations:

$R_1 = R_Z \times V_{OUT} / V_{REF}$  $R_2 = R_1 \times V_{REF} / (V_{OUT} - V_{REF})$

where:  $R_Z$  is 25 k $\Omega$  and

V<sub>REF</sub> is 2.4 V for AVDD

external equivalent resistance, that is, the parallel resistance of R1 and R2, as follows:

| Pin        | Parallel Resistance<br>(kΩ) |

|------------|-----------------------------|

| FB1 (DVDD) | 10 ± 1                      |

| FB2 (AVDD) | 25 ± 1                      |

| FB3 (VGL)  | 50 ± 2.5                    |

| FB4 (VGH)  | 50 ± 2.5                    |

|            |                             |

- To reduce the mismatch error of the sensing network, consider using 0.5% or 0.2% resistors for the resistor divider.

- To reduce effects of switching noises coupled into the FBx pins, add an external filter capacitor (typically a 47 pF MLCC) between the FBx pin and GND. The capacitor should be placed as close as possible to the respective FBx pin.

Table 3 provides some examples of voltage sensing network component values, using E96 1% resistors.

Figure 13. The figure 12 circuits with the same bias current injected into both inputs of the operational amplifier

#### **Output Capacitance**

The boost stage requires an output capacitor,  $C_{OUT}$ . Use an MLCC with a capacitance of approximately 4.7 to 10 µF and a voltage rating of 25 V. The temperature rating should be either X5R or X7R. Do not use Y5V, which has a very large variation with temperature. Another point to note is the capacitance of MLCC is specified at a 0 V bias. To account for the degradation when the rated DC voltage is applied to an MLCC, the capacitance should be derated by as much as 50%. The derating factor is typically less if the capacitor is physically larger (for example, choose a 1206 package instead of an 0805) and has a higher voltage rating (for example, 50 V instead of 25 V).

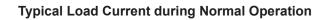

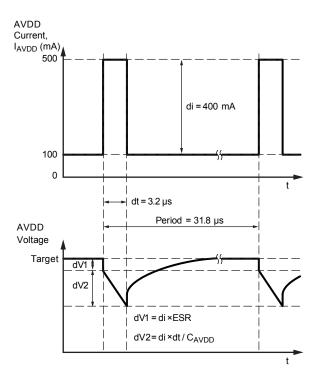

To ensure system stability, each output (DVDD, AVDD, VGL, VGH, and VCOM) is required to have an external MLCC with a minimum output capacitance of  $2 \pm 0.1 \mu$ F. However, greater capacitance may be required to satisfy transient current requirements. This is illustrated in figure 14. The AVDD load current makes a step from 100 mA (steady state current) to 500 mA, for a duration of 3.2 µs only. Because the linear regulator for AVDD takes a finite time to respond to this load change, the voltage dip is determined primarily by the output capacitance, C<sub>AVDD</sub>.

The corresponding voltage step, dV1, is determined by the ESR of the output capacitor. When using an MLCC with very low ESR (several m $\Omega$ ), this drop is only several mV and can be omitted.

Figure 14. AVDD output voltage transient caused by a step change in load current

| Output V <sub>FBx</sub><br>[Pin] (V) |                         | Goal Output Values     |                         | Calculated Resistor<br>Divider Values |                        | Actual Resistor<br>Divider Values |                        | Calculated Output Values |                         |                                                         |

|--------------------------------------|-------------------------|------------------------|-------------------------|---------------------------------------|------------------------|-----------------------------------|------------------------|--------------------------|-------------------------|---------------------------------------------------------|

|                                      | V <sub>FBx</sub><br>(V) | R <sub>Z</sub><br>(kΩ) | V <sub>out</sub><br>(V) | R <sub>1</sub><br>(kΩ)                | R <sub>2</sub><br>(kΩ) | R <sub>1</sub><br>(kΩ)            | R <sub>2</sub><br>(kΩ) | R <sub>z</sub><br>(kΩ)   | V <sub>OUT</sub><br>(V) | V <sub>OUT</sub><br>Resistor<br>Divider<br>Error<br>(%) |

| DVDD<br>[FB1]                        | 2.4                     | 10                     | 3.3                     | 13.75                                 | 36.67                  | 13.7                              | 36.5                   | 9.96                     | 3.3                     | 0.02                                                    |

| AVDD                                 | 2.4                     | 05                     | 7                       | 72.92                                 | 38.04                  | 73.2                              | 38.3                   | 25.14                    | 6.99                    | -0.19                                                   |

| [FB2]                                | [FB2] 2.4               | 25                     | 12.8                    | 133.33                                | 30.77                  | 133                               | 30.9                   | 25.07                    | 12.73                   | -0.55                                                   |

| VGH                                  | 1 0.1                   | 2.4 50                 | 14.5                    | 302.08                                | 59.92                  | 300                               | 59                     | 49.3                     | 14.6                    | 0.71                                                    |

| [FB4] 2.4                            | 50                      | 24.6                   | 512.5                   | 55.41                                 | 511                    | 54.9                              | 49.57                  | 24.74                    | 0.56                    |                                                         |

| VGL<br>[FB3] –1.8                    | 50                      | -5.4                   | 150                     | 75                                    | 150                    | 75                                | 50                     | -5.4                     | 0.00                    |                                                         |

|                                      | -1.0                    | 50                     | -11                     | 305.56                                | 59.78                  | 309                               | 60.4                   | 50.52                    | -11.01                  | 0.08                                                    |

#### Table 3. Examples of Sensing Network Component Values

Note: Use of series E96 1% resistors assumed.

The second voltage step, dV2, is determined by the output capacitance. For example, assume  $C_{AVDD} = 20 \ \mu\text{F}$ , then:

$$dV2 = 0.4 (A) \times 3.2 (\mu s) / 20 (\mu F) = 64 mV$$

#### **Operating with Separate VIN and Boost Supplies**

If necessary, the A8601 can be powered by a 5 V LDO for VIN, while the boost stage can be powered by a different supply such as 3.3 V. This is illustrated in figure 15.

The LDO for VIN should have an output voltage of 5 V  $\pm 10\%$ . The LDO supply current is the sum of the A8601 bias current (approximately 6 mA at 2 MHz) and the DVDD output current.

The boost supply voltage is independent from the VIN voltage. A reasonable range for the boost supply is between 3.3 and 10 V. The boost supply current is determined by the output power of boost stage, as outlined in the Thermal Analysis section.

The boost output voltage,  $V_{OUT}$ , is always higher than its input,  $V_{BOOSTS}$ . Therefore, it is necessary to keep the boost supply voltage below a certain level. This can be determined for a boost converter as follows:

$$V_{\rm OUT} = V_{\rm BOOSTS} / (1 - D)$$

(13)

where D is the duty cycle.

Assume a boost PWM frequency of 2 MHz (period = 500 ns). The A8601 minimum on-time,  $t_{ON(MIN)}$ , is 95 ns worst-case. That results in a minimum PWM duty cycle of 19%.

For a  $V_{BOOSTS}$  of 12 V, and a D of 0.19, the calculated  $V_{OUT}$  would be 14.8 V. This is higher than the 14 V required by the

A8601 output regulators in figure 15. Higher  $V_{OUT}$  levels result in excessive power loss and may trigger OVP at the SW pin.

#### **Thermal Analysis**

The thermal resistance,  $R_{\theta JA}$ , of the TSSOP-28 thermally enhanced package is 28°C/W. For long term reliability, the package junction temperature should be kept at 150°C or below. Assuming a maximum ambient temperature of 85°C, the power dissipation budget,  $P_D(max)$ , is:

$$P_{\rm D}(\max) = (T_{\rm J}(\max) - T_{\rm A}(\max)) / R_{\theta \rm JA}$$

(14)