**Features**

### High-Efficiency Power-Management IC with I2C Control for 2-Cell Li+ Battery Operated Devices

#### **General Description**

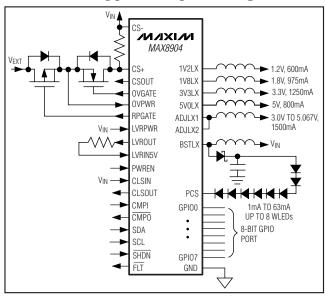

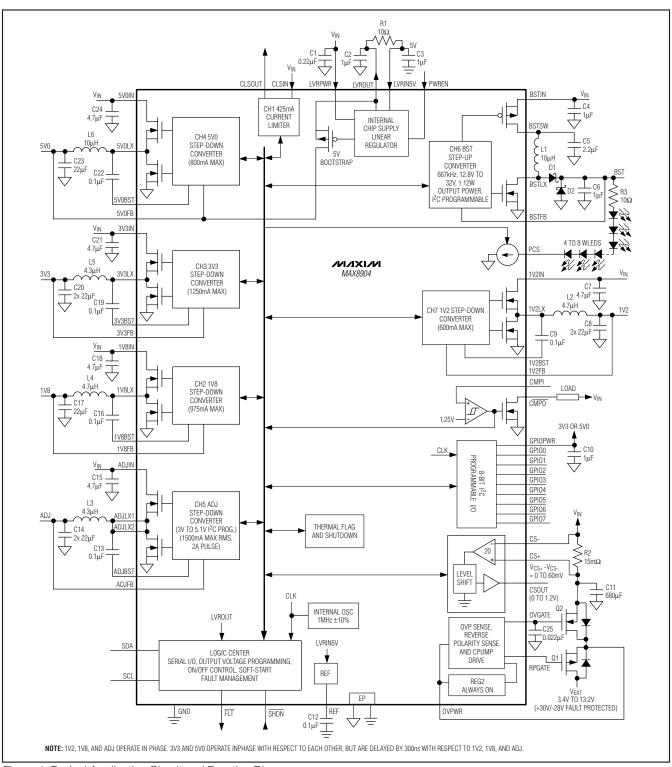

The MAX8904 power-management IC provides a complete power-supply solution for 2-cell Li+ handheld/Li-Poly applications such as point-of-sale terminals, digital SLR cameras, digital video cameras and ultra-mobile PCs.

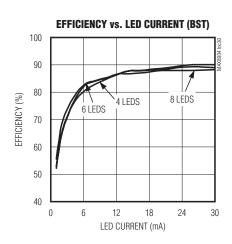

The MAX8904 includes five step-down converters (1V2, 1V8, 3V3, 5V0, and ADJ) with internal MOSFETs and +1%/-3% accurate output voltages for processor core, memory, I/O, and other system power rail requirements. LCD backlighting is supported by a WLED boost converter that can provide 35mA for up to 8 WLEDs. This boost converter is also configurable as a 6-bit programmable voltage source that can provide up to 63mA of output current. A 500mA, internal MOSFET, current-limited switch (CLS), allows system designers to control input power to external peripheral devices.

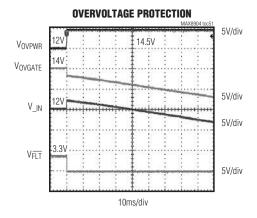

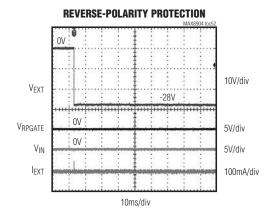

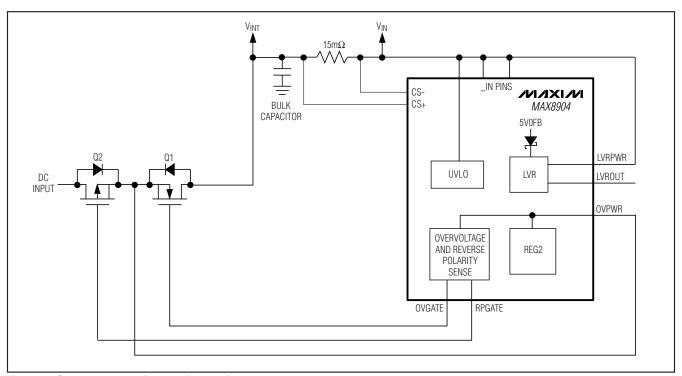

The MAX8904 controls an external n-MOSFET for input overvoltage protection (13.5V, typ) and an external p-MOSFET for reverse polarity protection (up to -28V) of downstream circuits. System input current monitoring for power management is facilitated by an on-board current-sense amplifier (CSA) with differential inputs and a 1.2V full scale, ground-referenced analog output.

A 400kHz, I<sup>2</sup>C interface supports output voltage setting of the ADJ power rail and boost regulator (voltage source mode), WLED current setting for the boost regulator (WLED current regulator mode), GPIO control, and enable/disable of ADJ, 5V0, boost regulator, CSA blocks. The I<sup>2</sup>C interface also enables the host processor to read on-board fault status registers when interrupted by the MAX8904 FLT pin under system fault conditions.

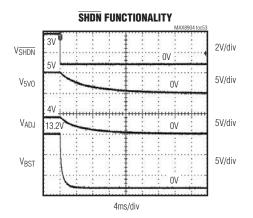

An emergency shutdown input, SHDN allows converters preselected through I2C to turn off immediately under power-fail conditions, thus saving valuable firmware execution time. An uncommitted, active-low, 14V open-drain comparator (CMP) with a 1.25V internal reference is also provided in the MAX8904. The MAX8904 PWREN logic input turns on the 1V2, 1V8, 3V3, and 5V0 default power rails.

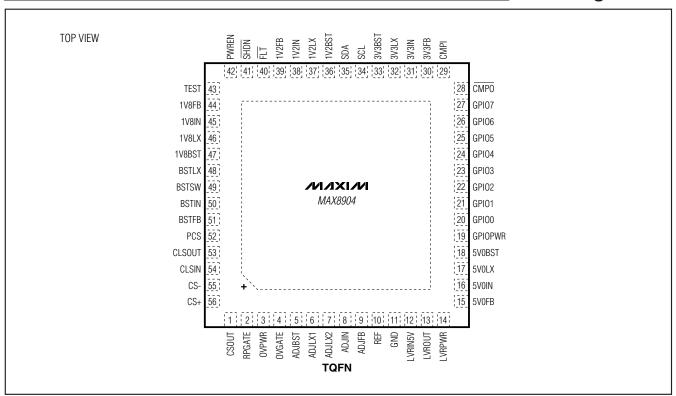

The MAX8904 is available in a 56-pin, 7mm x 7mm TQFN package.

**Applications**

Point-of-Sale Terminals Digital Video Cameras Digital SLR Cameras Ultra-Mobile PCs

Pin Configuration appears at end of data sheet.

#### ♦ 3.4V to 13.2V Input Voltage Range

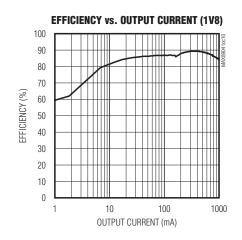

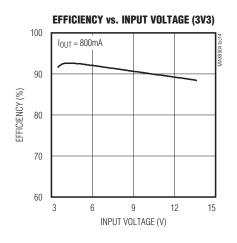

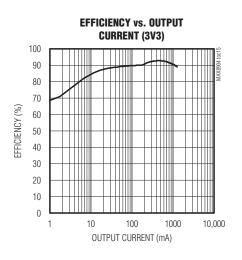

- 1MHz, Up to 90% Efficient, Synchronous DC-DC **Step-Down Converters**

- ♦ Power Converters 1V2, 1V8, and ADJ Operated Out-of-Phase with Respect to 3V3 and 5V0

- ♦ 667kHz Step-Up Converter Provides Up to 32V Output for Driving Up to Eight WLEDs

- ♦ Internal Compensation on All Power Converters

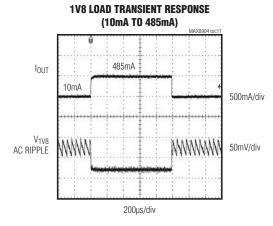

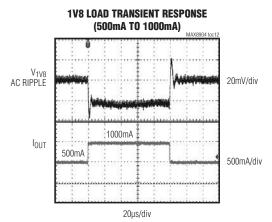

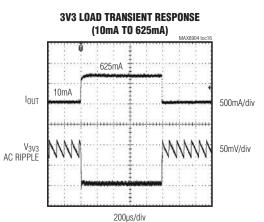

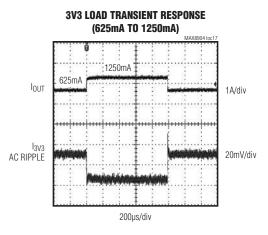

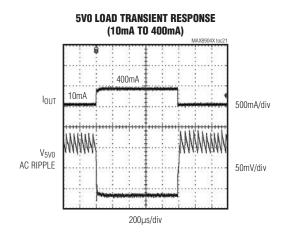

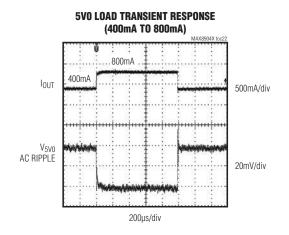

- **♦** Fast Line and Load Transient Responses

- ♦ Internal Soft-Start and Short-Circuit Protection on **All Power Converter Outputs**

- ♦ Input Overvoltage and Reverse Polarity Protection

- ♦ 250ms Fault Timer-Based Protection for Overload. Short Circuit

- ♦ I<sup>2</sup>C Serial Interface for On/Off Control, Output Voltage, WLED Current, GPIO Setting, Fault Monitoring

- ♦ < 15µA Standby Current Over Operating Voltage Range and Temperature

- ♦ Compact, 56-Pin, 7mm x 7mm TQFN Package

#### **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE                    |

|--------------|----------------|--------------------------------|

| MAX8904ETN+T | -40°C to +85°C | 56 THIN QFN-EP*<br>(7mm x 7mm) |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

#### **Typical Operating Circuit**

<sup>\*</sup>EP = Exposed pad.

#### **ABSOLUTE MAXIMUM RATINGS**

| OVPWR to GNDRPGATE to GND            |                                        |

|--------------------------------------|----------------------------------------|

| OVPWR to RPGATE                      | 0.3V to +22V                           |

| OVGATE to CS+                        | 0.3V to +6V                            |

| BSTFB to GND                         |                                        |

| BSTLX to Exposed Pad (EP)            | 0.3V to +40V                           |

| BSTSW to BSTIN                       | 16V to +0.3V                           |

| LVRPWR, BSTIN, BSTSW, 1V2IN, 3V3IN   | I, 1V8IN, ADJIN,                       |

| 5V0IN, CMPO, CLSIN to EP             | 0.3V to +16V                           |

| GPIO_ to EP                          | 0.3V to +6V                            |

| CS+, CS- to GND                      | 0.3V to +16V                           |

| CS+ to CS                            | 0.3V to +0.3V                          |

| CLSOUT to GND                        |                                        |

| LVROUT to GND0                       | $.3V$ to $(V_{LVRPWR} + 0.3V)$         |

| 1V2FB, 1V8FB, 3V3FB, 5V0FB, ADJFB,   | REF, CSOUT,                            |

| CMPI to GND0                         | $.3V \text{ to } (V_{LVRIN5V} + 0.3V)$ |

| 1V2BST to 1V2LX, 1V8BST to 1V8LX, 3V | /3BST to 3V3LX,                        |

| 5V0BST to 5V0LX, ADJBST to ADJLX     | <0.3V to +6V                           |

| LVRIN5V, LVROUT, SHDN, PWREN, FL     | T, SDA, SCL,                           |

| GPIOPWR to GND                       | 0.3V to +6V                            |

|                                      |                                        |

| PCS to GND0.3 EP to GND GPIOPWR to LVRIN5V LVROUT to LVRIN5V                                                        | 0.3V to +0.3V<br>6V to +0.3V |

|---------------------------------------------------------------------------------------------------------------------|------------------------------|

| ADJLX_, 5V0LX, 3V3LX, 1V8LX, 1V2LX, BSTLX (Note 1)                                                                  |                              |

| 56-Pin TQFN-EP Single-Layer PCB (derate 27.8mW/°C above +70°C)                                                      |                              |

| 56-Pin TQFN-EP Multilayer PCB (derate 40mW/°C above +70°C)                                                          |                              |

| Junction-to-Case Thermal Resistance (θ <sub>J</sub> C)<br>Junction-to-Ambient Thermal Resistance (θ <sub>J</sub> C) | (Note 2) 0.8°C/W             |

| Single-Layer PCBMultilayer PCB                                                                                      |                              |

| Operating Temperature Range Junction Temperature                                                                    | 40°C to +85°C<br>+150°C      |

| Storage Temperature Range<br>Lead Temperature (soldering, 10s)                                                      |                              |

|                                                                                                                     |                              |

- **Note 1:** \_LX pins have internal clamp diodes to \_IN and EP. Applications that forward bias these diodes should take care not to exceed the device's power-dissipation limits.

- **Note 2:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 7.2V, EP = GND, V_{PWREN} = 5V, _LX$  unconnected,  $C_{REF} = 0.1\mu F$ ; when  $V_{IN}$  is specified, it implies all \_IN pins;  $T_A = -40^{\circ}C$  to +85°C. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted. Limits are 100% production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range are guaranteed by design and characterization.)

| PARAMETER                                                                                                 | SYMBOL                                                                | CONDITIONS                                                                                                                     | MIN | TYP | MAX  | UNITS |

|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|-------|

| COMMON BLOCKS                                                                                             |                                                                       |                                                                                                                                |     |     |      |       |

|                                                                                                           |                                                                       | V_IN falling, OVP circuit not used                                                                                             | 3.6 |     | 14   |       |

| nput Operating Supply Range  nput Standoff Voltage  Standby Mode Supply Current  Quiescent Supply Current | V                                                                     | V_IN rising, OVP circuit not used                                                                                              | 5.8 |     | 14   | V     |

| Input Operating Supply Range                                                                              | V_IN                                                                  | V_IN falling, OVP circuit used                                                                                                 | 3.6 |     | 12.8 | V     |

|                                                                                                           |                                                                       | V_IN rising, OVP circuit used                                                                                                  | 5.8 |     | 13.2 |       |

| Input Standoff Voltage                                                                                    | Vovewr                                                                |                                                                                                                                |     |     | 28   | V     |

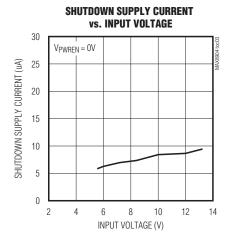

| Standby Mode Supply Current                                                                               | I_IN +<br>ILVRPWR +<br>ICS_                                           | V_IN = 13.2V; all channels off                                                                                                 |     | 5.5 |      | μА    |

| Quiescent Supply Current<br>(CH7 + CH2 + CH3 + CH4 Only)                                                  | ΔIQLVRPWR<br>+ I1V2IN +<br>I1V8IN +<br>I3V3IN +<br>I5V0IN +<br>I5V0FB | No switching, V <sub>1V2FB</sub> = 1.3V,<br>V <sub>1V8FB</sub> = 1.9V, V <sub>3V3FB</sub> = 3.4V,<br>V <sub>5V0FB</sub> = 5.1V |     | 100 | 165  | μА    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{\_IN} = 7.2V, EP = GND, V_{PWREN} = 5V, \_LX$  unconnected,  $C_{REF} = 0.1\mu F$ ; when  $V_{\_IN}$  is specified, it implies all  $\_IN$  pins;  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted. Limits are 100% production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range are guaranteed by design and characterization.)

| PARAMETER                                  | SYMBOL           | СО                                         | NDITIONS               | MIN   | TYP   | MAX   | UNITS           |

|--------------------------------------------|------------------|--------------------------------------------|------------------------|-------|-------|-------|-----------------|

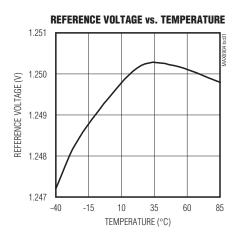

| DEE Outside Malta and                      |                  | I <sub>REF</sub> = 0µA                     |                        | 1.240 | 1.250 | 1.260 |                 |

| REF Output Voltage                         | VREF             | I <sub>REF</sub> = 10µA                    |                        |       | 1.249 |       | V               |

| OSC Frequency                              | fosc             |                                            |                        | 0.9   | 1     | 1.1   | MHz             |

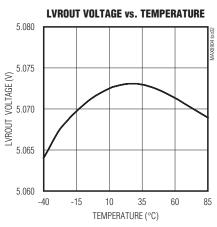

| LVROUT Output Voltage                      |                  | 5.4V < V <sub>L</sub> V <sub>R</sub> PWR < | : 14V                  | 4.9   | 5.1   | 5.3   | V               |

| LVRPWR Undervoltage Lockout                |                  | V <sub>LVRPWR</sub> rising                 |                        | 5.3   | 5.55  | 5.8   | V               |

| Threshold                                  |                  | V <sub>LVRPWR</sub> falling                |                        | 3.2   | 3.4   | 3.6   | V               |

| LVRIN5V Undervoltage Lockout               |                  | V <sub>LVRIN5V</sub> rising                |                        |       | 3.45  |       | V               |

| Threshold                                  |                  | V <sub>L</sub> VRIN5V falling              |                        |       | 2.6   |       | \ \ \           |

| SHDN Input High Voltage                    | VIH              | 3V < V <sub>L</sub> VRIN5V < 5             | 5.5V                   | 1.6   |       |       | V               |

| SHDN Input Low Voltage                     | V <sub>IL</sub>  | 3V < V <sub>LVRIN5V</sub> < 5              | 5.5V                   |       |       | 0.5   | V               |

| SHDN Pullup Resistance to LVRIN5V          |                  |                                            |                        |       | 1     |       | МΩ              |

| SHDN Pulldown Resistance to GND            |                  |                                            |                        |       | 2     |       | ΜΩ              |

| PWREN Input High Voltage                   | VIH              | 3.4V < V <sub>LVRPWR</sub> <               | : 14V                  | 1.6   |       |       | V               |

| PWREN Input Low Voltage                    | VIL              | 3.4V < V <sub>LVRPWR</sub> <               | : 14V                  |       |       | 0.5   | V               |

| PWREN Pulldown Resistance                  |                  |                                            |                        |       | 1     |       | МΩ              |

| PWREN Deglitch Delay                       |                  | Rising                                     |                        |       | 10    |       | μs              |

| FLT Output-Voltage Low                     | V <sub>FLT</sub> | $I_{\overline{FLT}} = 20mA$                |                        | 0     |       | 0.4   | V               |

| TIT On an Duning Landson Comment           |                  | \ F F\\                                    | T <sub>A</sub> = +25°C |       | 0.01  | 0.1   | 1.              |

| FLT Open-Drain Leakage Current             |                  | V <sub>FLT</sub> = 5.5V                    | $T_A = +85^{\circ}C$   |       | 0.1   |       | <del>Ι</del> μΑ |

| FAULT Timer Delay                          | tfault           |                                            |                        |       | 250   |       | ms              |

| Overtemperature Warning Flag               |                  | Rising (Note 3) (bi                        | it D3 of register 0Dh) | 110   | 120   | 130   | °C              |

| Overtemperature Warning Flag<br>Hysteresis |                  |                                            |                        |       | 10    |       | °C              |

| Thermal Shutdown Latch<br>Threshold        |                  | (Note 3)                                   |                        | 140   | 152   | 165   | °C              |

| INPUT VOLTAGE PROTECTION                   |                  | •                                          |                        | •     |       |       |                 |

| OVPWR Undervoltage Lockout                 |                  | Vovewa rising                              |                        | 3.75  | 4     | 4.25  |                 |

| Threshold                                  |                  | Vovewa falling                             |                        | 2.7   | 2.85  | 3.0   | V               |

| OVPWR_UVLO_Rising to OVGATE Startup Delay  | tstartup         | Vovpwr > Vovpwr_uvlo_rising                |                        |       | 32    |       | ms              |

| OVD TI                                     | .,,              | V <sub>OVPWR</sub> rising                  |                        | 13.3  | 13.65 | 14    | .,              |

| OVP Threshold                              | Vovp             | Hysteresis                                 |                        |       | 0.17  |       | V               |

| OVGATE Charge Current                      | IOVGATE_CHG      | V <sub>OVGATE</sub> = 7.2V                 |                        |       | 10    |       | μΑ              |

| OVGATE Discharge Resistance                | RDCHG            | $V_{CS+} = 14.1V, V_{CS+}$                 | VGATE = 15.1V          |       | 40    |       | Ω               |

|                                            |                  | İ                                          |                        |       | Γ0    |       | 1.0             |

| RPGATE Pulldown Resistor                   | RRPGATE          |                                            |                        |       | 50    |       | kΩ              |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 7.2V, EP = GND, V_{PWREN} = 5V, _LX$  unconnected,  $C_{REF} = 0.1\mu F$ ; when  $V_{IN}$  is specified, it implies all \_IN pins;  $T_A = -40^{\circ}C$  to +85°C. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted. Limits are 100% production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range are guaranteed by design and characterization.)

| PARAMETER                                                   | SYMBOL                 | CONDITIO                                                                  | ONS                                           | MIN   | TYP      | MAX   | UNITS  |

|-------------------------------------------------------------|------------------------|---------------------------------------------------------------------------|-----------------------------------------------|-------|----------|-------|--------|

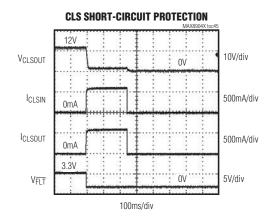

| CH1 (CURRENT-LIMITED SWITC                                  | H)                     |                                                                           |                                               |       |          |       |        |

| Current-Limited Switch On-Resistance                        | Roncls                 | I <sub>CLS</sub> = 400mA                                                  |                                               | 200   | 300      | 425   | m_     |

| Current Limit                                               | ILIMCLS                | V <sub>CLSIN</sub> = 12V, V <sub>CLSOUT</sub> =                           | = 9V                                          | 450   |          | 600   | mA     |

| Overcurrent Fault Latch-Off Delay                           | tolflt                 |                                                                           |                                               |       | 250      |       | ms     |

| Fault Voltage                                               | VACT                   | VCLSIN - VCLSOUT > 1V,                                                    | 150mV hysteresis                              |       | 1        |       | V      |

| Thermal Loop Threshold                                      | THMTH                  | Current-limit-foldback ten threshold (Note 3)                             | mperature                                     | 110   | 120      | 130   | °C     |

| CL COLIT Lookaga Current                                    | la, an umuya           | V <sub>CLSIN</sub> = 14V,                                                 | $T_A = +25^{\circ}C$                          |       | 0.01     | 1     |        |

| CLSOUT Leakage Current                                      | ICLSOUTLKG             | V <sub>CLSOUT</sub> = 0                                                   | $T_A = +85^{\circ}C$                          |       | 0.1      |       | μΑ     |

| CH2 (1V8 STEP-DOWN CONVER                                   | TER)                   |                                                                           |                                               |       |          |       |        |

| Output Voltage                                              | V <sub>1V8FB</sub>     | No load                                                                   |                                               | 1.800 | 1.818    | 1.836 | V      |

| Operating Frequency                                         | f <sub>1V8LX</sub>     |                                                                           |                                               |       | 1        |       | MHz    |

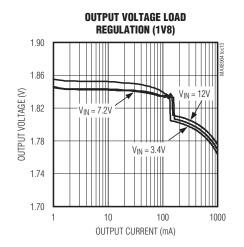

| Load Regulation                                             |                        |                                                                           |                                               |       | -2.5     |       | %/A    |

| Line Regulation                                             |                        | $V_{1V8IN} = 3.4V \text{ to } 14V$                                        |                                               |       | 0.04     |       | %/V    |

| Idle-Mode Trip Level                                        |                        | (Note 4)                                                                  |                                               |       | 150      |       | mA     |

| 1V8LX Leakage Current                                       | I <sub>1V8LXLKG</sub>  | $V_{1V8LX} = 0, 14V,$<br>$V_{1V8IN} = 14V$                                | $T_A = +25^{\circ}C$ $T_A = +85^{\circ}C$     | -5    | 0.01     | +5    | μΑ     |

| 1V8BST Leakage Current                                      | I <sub>1V8BSTLKG</sub> | V <sub>1</sub> V <sub>8</sub> BST = 5V + V <sub>1</sub> V <sub>8</sub> IN | $T_{A} = +25^{\circ}C$ $T_{A} = +85^{\circ}C$ |       | 0.01     | 0.1   | μΑ     |

| Low-Side Switch On-Resistance                               | RONLS1V8               |                                                                           | 7,                                            |       | 0.185    |       |        |

| High-Side Switch On-Resistance                              | R <sub>ONHS1V8</sub>   |                                                                           |                                               |       | 0.27     |       |        |

| High-Side Switch Current Limit                              | ILIMHS1V8              |                                                                           |                                               | 1.3   | 1.43     | 1.6   | A      |

| Low-Side Switch Turn-Off Current                            |                        |                                                                           |                                               |       | 10       |       | mA     |

| Output-OK (1V8OK) Threshold                                 |                        | (Bit D3 of register 0Fh)                                                  | Rising<br>Falling                             |       | 94<br>90 |       | %      |

| Soft-Start Rate                                             |                        |                                                                           | I aming                                       |       | 1        |       | V/ms   |

| LX Discharge Resistance                                     |                        | PWREN = GND                                                               |                                               |       | 350      |       | ¥/1110 |

| Output-OK (1V8OK) Fault Blanking Time After Soft-Start Done |                        |                                                                           |                                               |       | 2        |       | ms     |

\_\_\_\_\_\_/N/XI/N

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 7.2V, EP = GND, V_{PWREN} = 5V, _LX$  unconnected,  $C_{REF} = 0.1\mu F$ ; when  $V_{JN}$  is specified, it implies all \_IN pins;  $T_A = -40^{\circ}C$  to +85°C. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted. Limits are 100% production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range are guaranteed by design and characterization.)

| PARAMETER                                                         | SYMBOL                           | CONDIT                                                                    | IONS                                      | MIN      | TYP   | MAX   | UNITS  |

|-------------------------------------------------------------------|----------------------------------|---------------------------------------------------------------------------|-------------------------------------------|----------|-------|-------|--------|

| CH3 (3V3 STEP-DOWN CONVER                                         | TER)                             |                                                                           |                                           | II.      |       |       | l .    |

| Output Voltage                                                    | V <sub>3V3FB</sub>               | No load                                                                   |                                           | 3.349    | 3.383 | 3.416 | V      |

| Operating Frequency                                               | f <sub>3V3LX</sub>               |                                                                           |                                           |          | 1     |       | MHz    |

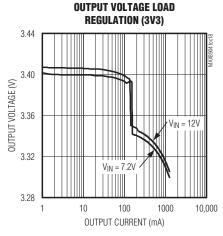

| Load Regulation                                                   |                                  |                                                                           |                                           |          | -1.1  |       | %/A    |

| Line Regulation                                                   |                                  | $V_{3V3IN} = 3.4V \text{ to } 14V$                                        |                                           |          | 0.04  |       | %/V    |

| Idle-Mode Trip Level                                              |                                  | (Note 4)                                                                  |                                           |          | 150   |       | mA     |

| 3V3LX Leakage Current                                             | l3v3lxlkG                        | $V_{3V3LX} = 0, 14V,$<br>$V_{3V3IN} = 14V$                                | $T_A = +25^{\circ}C$ $T_A = +85^{\circ}C$ | -5       | 0.01  | +5    | μΑ     |

| 3V3BST Leakage Current                                            | l <sub>3V3BSTLKG</sub>           | $V_{3V3BST} = 5V + V_{3V3IN}$                                             | $T_A = +25^{\circ}C$ $T_A = +85^{\circ}C$ |          | 0.01  | 0.1   | μΑ     |

| Low-Side Switch On-Resistance                                     | R <sub>ONLS3V3</sub>             |                                                                           | 1A = +65 C                                |          | 0.185 |       |        |

| High-Side Switch On-Resistance                                    | RONHS3V3                         |                                                                           |                                           |          | 0.185 |       |        |

| High-Side Switch Current Limit                                    | ILIMHS3V3                        |                                                                           |                                           | 1.8      | 2     | 2.2   | A      |

| Low-Side Switch Turn-Off Current                                  | ILIIVII 100 V 3                  |                                                                           |                                           | 1.0      | 10    | ۷.۲   | mA     |

| Lew Glad Gwildin Fairi Girl Garrent                               |                                  |                                                                           | Rising                                    |          | 94    |       | 1117 ( |

| Output-OK (3V3OK) Threshold                                       |                                  | (Bit D4 of register 0Fh)                                                  | Falling                                   |          | 90    |       | %      |

| Maximum Duty Cycle                                                |                                  |                                                                           | [ · · · · · · · · · · · · · · · · · · ·   |          | 95    |       | %      |

| Soft-Start Rate                                                   |                                  |                                                                           |                                           |          | 1     |       | V/ms   |

| LX Discharge Resistance                                           |                                  | PWREN = GND                                                               |                                           |          | 175   |       | _      |

| Output-OK (3V3OK) Fault<br>Blanking Time After Soft-Start<br>Done |                                  |                                                                           |                                           |          | 2     |       | ms     |

| CH4 (5V0 STEP-DOWN CONVER                                         | TER)                             |                                                                           |                                           | <u> </u> |       |       |        |

| Output Voltage                                                    | V <sub>5</sub> V <sub>0</sub> FB | No load                                                                   |                                           | 5.000    | 5.050 | 5.100 | V      |

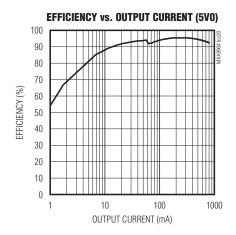

| Operating Frequency                                               | f <sub>5V0LX</sub>               |                                                                           |                                           |          | 1     |       | MHz    |

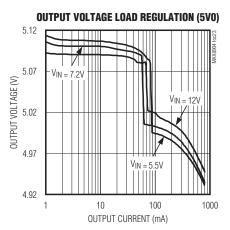

| Load Regulation                                                   |                                  |                                                                           |                                           |          | -1.25 |       | %/A    |

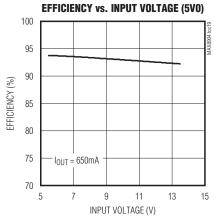

| Line Regulation                                                   |                                  | $V_{5V0IN} = 5.4V \text{ to } 14V$                                        |                                           |          | 0.04  |       | %/V    |

| Idle-Mode Trip Level                                              |                                  | (Note 4)                                                                  |                                           |          | 60    |       | mA     |

| 5V0LX Leakage Current                                             | In vol. VI. IV.O.                | $V_{5V0LX} = 0, 14V,$                                                     | $T_A = +25^{\circ}C$                      | -5       | +0.01 | +5    | μA     |

| 3VOLA Leakage Current                                             | l5V0LXLKG                        | V <sub>5</sub> V <sub>0</sub> IN = 14V                                    | T <sub>A</sub> = +85°C                    |          | 0.1   |       | μΑ     |

| 5V0BST Leakage Current                                            | l <sub>5</sub> vobstlkg          | V <sub>5</sub> V <sub>0</sub> BST = 5V + V <sub>5</sub> V <sub>0</sub> IN | $T_A = +25^{\circ}C$                      |          | 0.01  | 0.1   | μA     |

| 5 v 5 5 o Loanage Ourion                                          | SVUBSILKG                        | *300031 - 00 + V500IN                                                     | $T_A = +85^{\circ}C$                      |          | 0.1   |       | μ/ \   |

| Low-Side Switch On-Resistance                                     | Ronls5vo                         |                                                                           |                                           |          | 0.27  |       | _      |

| High-Side Switch On-Resistance                                    | Ronhs5vo                         |                                                                           |                                           |          | 0.27  |       | _      |

| High-Side Switch Current Limit                                    | ILIMHS5V0                        |                                                                           |                                           | 1.26     | 1.4   | 1.54  | А      |

| Low-Side Switch Turn-Off Current                                  |                                  |                                                                           |                                           |          | 10    |       | mA     |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 7.2V, EP = GND, V_{PWREN} = 5V, _LX unconnected, C_{REF} = 0.1 \mu F; when V_{IN} is specified, it implies all _IN pins; T_A = -40 °C to +85 °C. Typical values are at T_A = +25 °C, unless otherwise noted. Limits are 100% production tested at T_A = +25 °C. Limits over the operating temperature range are guaranteed by design and characterization.)$

| PARAMETER                                                      | SYMBOL                                                                    | CONDIT                                                                 | ONS                                       | MIN  | TYP   | MAX   | UNITS |

|----------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------|------|-------|-------|-------|

| Output OV (FVOOV) Throughold                                   |                                                                           | (Dit DE of register OFb)                                               | Rising                                    |      | 94    |       | 0/    |

| Output-OK (5V0OK) Threshold                                    |                                                                           | (Bit D5 of register 0Fh)                                               | Falling                                   |      | 90    |       | %     |

| Soft-Start Rate                                                |                                                                           |                                                                        |                                           |      | 1     |       | V/ms  |

| LX Discharge Resistance                                        |                                                                           | PWREN = GND                                                            |                                           |      | 350   |       |       |

| Output-OK (5V0OK) Fault Blanking<br>Time After Soft-Start Done |                                                                           |                                                                        |                                           |      | 2     |       | ms    |

| CH5 (ADJ STEP-DOWN CONVER                                      | TER)                                                                      |                                                                        |                                           | 1    |       |       | I.    |

| Quiescent Supply Current                                       | Δ(I <sub>QL</sub> VRPWR<br>+ I <sub>5</sub> V0FB) +<br>I <sub>ADJIN</sub> | No switching (CH5 only ADJSP register = 1Fh                            | ), V <sub>ADJFB</sub> = 4V,               |      | 65    | 100   | μA    |

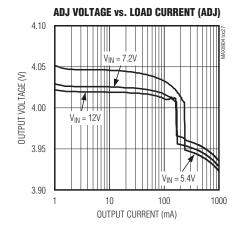

| Output Voltage Adjust Range                                    | V <sub>ADJFB</sub>                                                        |                                                                        |                                           | 3    |       | 5.067 | V     |

| Operating Frequency                                            | fadjlx_                                                                   |                                                                        |                                           |      | 1     |       | MHz   |

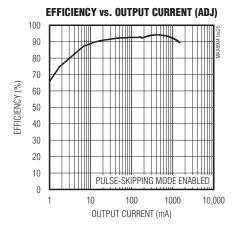

| Output Voltage Accuracy                                        |                                                                           | No load                                                                |                                           | -1   | 0     | +1    | %     |

| Load Regulation                                                |                                                                           |                                                                        |                                           |      | -0.75 |       | %/A   |

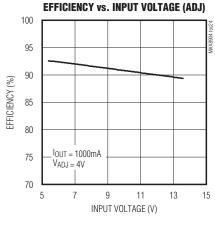

| Line Regulation                                                |                                                                           | V <sub>ADJIN</sub> = 5.4V to 14V, V<br>ADJSP register = 1Fh            | ADJFB = 4V,                               |      | 0.04  |       | %/V   |

| Idle-Mode Trip Level                                           |                                                                           | (Note 4)                                                               |                                           |      | 180   |       | mA    |

| ADJLX_ Leakage Current                                         | I <sub>ADJLX</sub> _                                                      | V <sub>ADJLX</sub> = 0, 14V,<br>V <sub>ADJIN</sub> = 14V               | $T_A = +25^{\circ}C$ $T_A = +85^{\circ}C$ | -5   | 0.01  | +5    | μΑ    |

| ADJBST Leakage Current                                         | ladjbstlkg                                                                | VADJBST = 5V + VADJIN                                                  | $T_A = +25^{\circ}C$ $T_A = +85^{\circ}C$ |      | 0.01  | 0.1   | μΑ    |

| Low-Side Switch On-Resistance                                  | Ronlsadj                                                                  | 7.55                                                                   | .A .ss c                                  |      | 0.185 |       |       |

| High-Side Switch On-Resistance                                 | RONHSADJ                                                                  |                                                                        |                                           |      | 0.185 |       | _     |

| High-Side Switch Current Limit                                 | ILIMHSADJ                                                                 |                                                                        |                                           | 2.7  | 3.0   | 3.3   | A     |

| Low-Side Switch Turn-Off Current                               |                                                                           |                                                                        |                                           |      | 10    |       | mA    |

| Output-OK (ADJOK) Threshold                                    |                                                                           | (Bit D6 of register 0Fh)                                               | Rising                                    |      | 94    |       | %     |

|                                                                |                                                                           | (=::=::::::::::::::::::::::::::::::::::                                | Falling                                   |      | 90    |       |       |

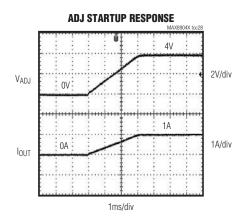

| Soft-Start Rate                                                |                                                                           |                                                                        |                                           |      | 1     |       | V/ms  |

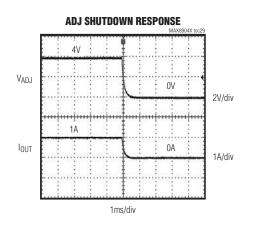

| LX Discharge Resistance                                        |                                                                           | ADJEN = logic 0 (bit D3                                                | of register 07h)                          |      | 175   |       | _     |

| Output-OK (ADJOK) Fault Blanking<br>Time After Soft-Start Done |                                                                           |                                                                        |                                           |      | 2     |       | ms    |

| CH6 (BST STEP-UP CONVERTER                                     | R)                                                                        |                                                                        |                                           |      |       |       |       |

| Quiescent Supply Current                                       | ΔI <sub>QL</sub> VRPWR<br>+ I <sub>BSTIN</sub>                            | No switching (CH6 only (bit D4 of register 09h), BSTVSP register (0Ch) | V <sub>BSTFB</sub> = 14V,                 |      | 100   |       | μΑ    |

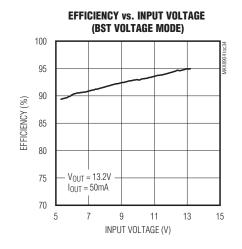

| Typical Output Voltage Range                                   | Voctor                                                                    | Current mode                                                           |                                           | 17.4 |       | 33.5  | V     |

| rypical Output voltage halige                                  | V <sub>BSTFB</sub>                                                        | Voltage mode (typical D                                                | AC codes)                                 | 12.5 |       | 18.7  | v     |

| Overvoltage Protection Range                                   |                                                                           | Current mode (typical D                                                | AC codes)                                 | 17.4 |       | 36    | V     |

| Overvoltage Protection Accuracy                                |                                                                           | Current mode, V <sub>BSTFB</sub> =                                     | = 26.7V                                   | -3   |       | +3    | %     |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{\_IN} = 7.2V, EP = GND, V_{PWREN} = 5V, \_LX$  unconnected,  $C_{REF} = 0.1\mu F$ ; when  $V_{\_IN}$  is specified, it implies all  $\_IN$  pins;  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted. Limits are 100% production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range are guaranteed by design and characterization.)

| PARAMETER                                       | SYMBOL                           | CON                                                   | CONDITIONS                                    |       | TYP   | MAX   | UNITS |

|-------------------------------------------------|----------------------------------|-------------------------------------------------------|-----------------------------------------------|-------|-------|-------|-------|

| Output Voltage Accuracy                         |                                  | Voltage mode, BSTV                                    | SP register (0Ch) = 10h                       | -3    |       | +3    | %     |

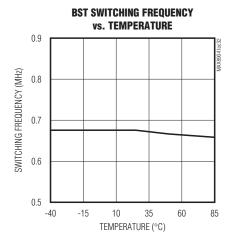

| Operating Frequency                             | fBSTLX                           |                                                       |                                               |       | 667   |       | kHz   |

| Minimum Duty Cycle                              |                                  |                                                       |                                               |       | 10    |       | %     |

| Maximum Duty Cycle                              |                                  |                                                       |                                               | 90    | 93    | 97    | %     |

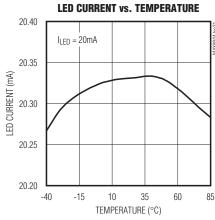

| PCS Current Accuracy                            | Inco                             | BSTCSP register                                       | T <sub>A</sub> = +25°C                        | 31.04 | 32    | 32.96 | mA    |

| FC3 Current Accuracy                            | I <sub>PCS</sub>                 | (0Bh) = 20h                                           | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ | 30.4  |       | 33.6  | IIIA  |

| PCS Leakage Current                             | IPCSLKG                          | V <sub>PCS</sub> = 0 to                               | T <sub>A</sub> = +25°C                        |       | 0.01  | 1     | μΑ    |

| 1 C3 Leakage Current                            | IPCSLKG                          | LVRIN5V                                               | T <sub>A</sub> = +85°C                        |       | 0.1   |       | μΑ    |

|                                                 |                                  | V <sub>BSTSW</sub> = 0, V <sub>BSTIN</sub>            | $T_A = +25$ °C                                |       | 0.01  | 5     |       |

| BSTSW Leakage Current                           | I <sub>BSTSWLKG</sub>            | = 14V, BSTEN =<br>logic 0 (bit D4 of<br>Register 09h) | T <sub>A</sub> = +85°C                        |       | 0.1   |       | μΑ    |

| DOTLY Lands on Occurrent                        |                                  |                                                       | T <sub>A</sub> = +25°C                        |       | 0.01  | 5     |       |

| BSTLX Leakage Current                           | IBSTLXLKG                        | $V_{BSTLX} = 0 \text{ to } 36V$                       | T <sub>A</sub> = +85°C                        |       | 1     |       | μΑ    |

| BSTSW Switch On-Resistance                      | RONBSTSW                         |                                                       |                                               |       | 0.1   |       | _     |

| BSTLX Switch On-Resistance                      | RONBSTLX                         |                                                       |                                               |       | 0.3   |       | _     |

| BSTSW Switch Short-Circuit<br>Current Limit     | I <sub>LIMBSTSW</sub>            |                                                       |                                               |       | 1.35  |       | А     |

| BSTLX Switch Current Limit                      | ILIMBSTLX                        |                                                       |                                               |       | 1.13  |       | А     |

| Output Voltage OK (BSTOK)                       |                                  | (Bit D7 of register                                   | Rising, voltage mode only                     |       | 95    |       | 0/    |

| Threshold                                       |                                  | 0Fh)                                                  | Falling, voltage mode only                    |       | 90    |       | %     |

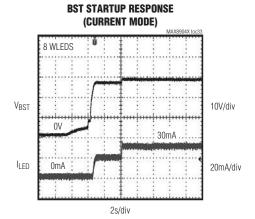

| Soft-Start Time                                 |                                  | Voltage mode and c                                    | urrent mode                                   |       | 4.096 |       | ms    |

| BSTOK Fault Blanking Time After Soft-Start Done |                                  | Voltage mode and c                                    | current mode                                  |       | 1.024 |       | ms    |

| CH7 (1V2 STEP-DOWN CONVER                       | TER)                             |                                                       |                                               |       |       |       |       |

| Output Voltage                                  | V <sub>1</sub> V <sub>2</sub> FB | No load                                               |                                               | 1.200 | 1.212 | 1.224 | V     |

| Operating Frequency                             | f <sub>1V2LX</sub>               |                                                       |                                               |       | 1     |       | MHz   |

| Load Regulation                                 |                                  |                                                       |                                               |       | -2.5  |       | %/A   |

| Line Regulation                                 |                                  | $V_{1V2IN} = 3.4V \text{ to } 14V$                    | /                                             |       | 0.04  |       | %/V   |

| Idle-Mode Trip Level                            |                                  | (Note 4)                                              |                                               |       | 200   |       | mA    |

| 1V2LX Leakage Current                           | lavory ve                        | $V_{1V2LX} = 0, 14V,$                                 | T <sub>A</sub> = +25°C                        | -5    | 0.01  | +5    | ^     |

| 1VZLA Leakage Current                           | <sup>I</sup> 1V2LXLKG            | $V_{1V2IN} = 14V$                                     | T <sub>A</sub> = +85°C                        |       | 0.1   |       | μA    |

| 1V2BST Leakage Current                          | I <sub>1</sub> V2BSTLKG          | V <sub>1</sub> V <sub>2</sub> BST = 5V +              | T <sub>A</sub> = +25°C                        |       | 0.01  | 0.1   | μA    |

| 112501 Leanage Outlett                          | IIVZBSILKG                       | V <sub>1</sub> V <sub>2</sub> IN                      | $T_A = +85^{\circ}C$                          |       | 0.1   |       | μΛ    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{LIN} = 7.2V, EP = GND, V_{PWREN} = 5V, LX unconnected, C_{REF} = 0.1 \mu F$ ; when  $V_{LIN}$  is specified, it implies all \_IN pins;  $T_A = -40^{\circ}C$  to +85°C. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted. Limits are 100% production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range are guaranteed by design and characterization.)

| PARAMETER                                                         | SYMBOL                                 | CON                                                                                | DITIONS                                                 | MIN   | TYP           | MAX   | UNITS |

|-------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------|-------|---------------|-------|-------|

| Low-Side Switch On-Resistance                                     | R <sub>ONLS1V2</sub>                   |                                                                                    |                                                         |       | 0.185         |       | _     |

| High-Side Switch On-Resistance                                    | Ronhs1v2                               |                                                                                    |                                                         |       | 0.27          |       | _     |

| High-Side Switch Current Limit                                    | ILIMHS1V2                              |                                                                                    |                                                         | 1.08  | 1.2           | 1.32  | А     |

| Low-Side Switch Turn-Off Current                                  |                                        |                                                                                    |                                                         |       | 10            |       | mA    |

| Output-OK (1V2OK) Threshold                                       |                                        | (Bit D2 of register 0Fh)                                                           | Rising<br>Falling                                       |       | 94<br>90      |       | %     |

| Soft-Start Rate                                                   |                                        |                                                                                    |                                                         |       | 1             |       | V/ms  |

| LX Discharge Resistance                                           |                                        | PWREN = GND                                                                        |                                                         |       | 175           |       | _     |

| Output-OK (1V2OK) Fault<br>Blanking Time After Soft-Start<br>Done |                                        |                                                                                    |                                                         |       | 2             |       | ms    |

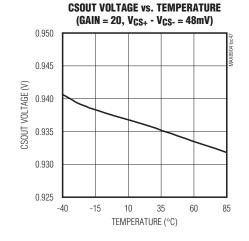

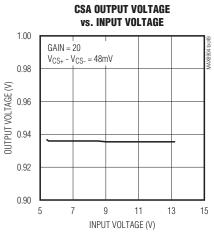

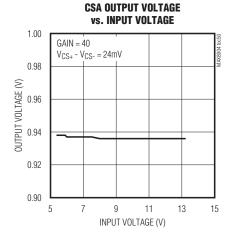

| CSA (CURRENT-SENSE AMPLIF                                         | ER)                                    |                                                                                    |                                                         |       |               |       |       |

| Differential Input Range                                          | V <sub>CS+</sub> - V <sub>CS-</sub>    | V <sub>L</sub> V <sub>R</sub> PWR = V <sub>C</sub> S- =                            | 5.4V to 14V                                             | 0     |               | 60    | mV    |

| Maximum CSOUT Output<br>Capacitive Load                           | C <sub>LOAD</sub>                      | (Note 3)                                                                           |                                                         |       |               | 50    | рF    |

| CSOUT Pulldown Resistor                                           | R <sub>PD</sub>                        |                                                                                    |                                                         |       | 350           |       | k_    |

| Bandwidth                                                         |                                        |                                                                                    |                                                         |       | 150           |       | kHz   |

| Common-Mode Voltage Range                                         | VCMR                                   |                                                                                    |                                                         | 5.4   |               | 14    | V     |

| Common-Mode Rejection                                             | CMR                                    | V <sub>LVRPWR</sub> = V <sub>CS-</sub> = V <sub>CS+</sub> = V <sub>CS-</sub> + 24m |                                                         |       | 100           |       | dB    |

| CS_ Input Current                                                 | (I <sub>CS-</sub> + I <sub>CS+</sub> ) | V <sub>L</sub> V <sub>R</sub> PWR = V <sub>C</sub> S <sub>-</sub> =                | $V_{CS+} = 5.4V \text{ to } 13.2V$                      |       | 2             | 4     | μΑ    |

| CS+/CS- Input-Referred Offset                                     | Viocs                                  | Gain = 20, V <sub>CS+</sub> = 5.4V to 14V                                          | V <sub>CS</sub> - = V <sub>L</sub> V <sub>R</sub> PWR = | -2.0  | 0             | +2.0  | mV    |

|                                                                   |                                        |                                                                                    | $V_{CS+} - V_{CS-} = 48mV$ , gain = 20                  |       | 1             | 5     |       |

| CSOUT Voltage Accuracy                                            |                                        | $V_{LVRPWR} = 5.4V$ to 14V                                                         | $V_{CS+} - V_{CS-} = 24mV$ , gain = 20                  |       | 2             | 5     | %     |

|                                                                   |                                        |                                                                                    | $V_{CS+} - V_{CS-} = 24mV$ , gain = 40                  |       | 1             | 5     |       |

| CSOUT Load Current                                                | ICSOUT                                 | V <sub>CS+</sub> - V <sub>CS-</sub> = 48m                                          | V, gain = 20                                            |       |               | 20    | μΑ    |

| 00 Flag (DIT D4 of Davids 2011)                                   |                                        | (Bit D6 of register                                                                | Rising,<br>CSFLGEN = logic 1                            | 0.912 | 0.912 0.96 1. | 1.008 |       |

| CS Flag (BIT D1 of Register 0Dh)                                  |                                        | 09h)                                                                               | Falling,<br>CSFLGEN = logic 1                           | 0.862 | 0.91          | 0.958 | V     |

| Start-Up Time                                                     |                                        |                                                                                    |                                                         |       |               | 60    | μs    |

| CSOUT Clamp Voltage                                               | VCSOUTCLP                              |                                                                                    |                                                         | 1.215 | 1.242         | 1.270 | V     |

3 \_\_\_\_\_\_\_/NIXI/N

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{\_IN} = 7.2V, EP = GND, V_{PWREN} = 5V, \_LX$  unconnected,  $C_{REF} = 0.1\mu F$ ; when  $V_{\_IN}$  is specified, it implies all  $\_IN$  pins;  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted. Limits are 100% production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range are guaranteed by design and characterization.)

| PARAMETER                             | SYMBOL          | со                            | NDITIONS               | MIN              | TYP  | MAX               | UNITS |

|---------------------------------------|-----------------|-------------------------------|------------------------|------------------|------|-------------------|-------|

| GPIO LOGIC INPUT/OUTPUT               | •               |                               |                        | •                |      |                   |       |

| GPIOPWR UVLO                          |                 | Rising                        |                        |                  | 2.8  |                   | V     |

| GPIOPWR UVLU                          |                 | Falling                       |                        |                  | 2.5  |                   | V     |

| Input Threshold                       |                 | Rising                        |                        | 0.7 x<br>VGPIOPW | R    |                   | V     |

| Input Threshold                       |                 | Falling                       |                        |                  | V    | 0.25 x<br>GPIOPWR | V     |

| Output-Voltage Low                    |                 | IGPIO_ = -20mA, or            | oen-drain output       |                  |      | 0.5               | V     |

| Onen Drein Leekene Current            |                 | V                             | T <sub>A</sub> = +25°C |                  | 0.01 | 0.1               | ^     |

| Open-Drain Leakage Current            |                 | V <sub>GPIO</sub> _ = 5.5V    | $T_A = +85^{\circ}C$   |                  | 0.1  |                   | μΑ    |

| Minimum Input Data Setup Time         | t <sub>DS</sub> |                               |                        |                  | 100  |                   | ns    |

| Minimum Input Data Hold Time          | tDH             |                               |                        |                  | 1    |                   | μs    |

| Minimum Delay to Output<br>Data Valid |                 |                               |                        |                  | 5    |                   | μs    |

|                                       |                 |                               | Input mode             |                  | 1    |                   | M_    |

| Pullup Resistor from GPIO_ to GPIOPWR |                 | VGPIOPWR = 5V                 | Open-drain output mode |                  | 10   |                   | k_    |

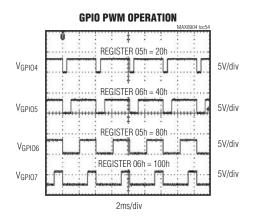

| GPIO_ PWM Clock Frequency             |                 |                               |                        |                  | 244  |                   | Hz    |

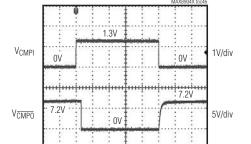

| OPEN-DRAIN COMPARATOR                 | •               |                               |                        |                  |      |                   | •     |

| CMPI Input Current                    | ICMPI           | V <sub>CMPI</sub> = 600mV     |                        |                  | 0.01 |                   | μΑ    |

| CMPI Threshold                        | VCMPI           | Rising                        |                        | 1.2125           | 1.25 | 1.2875            | V     |

| CMPI Hysteresis                       | VCMPIHYS        |                               |                        |                  | 40   |                   | mV    |

| CMPO Delay                            | t CMPO          | 25mV overdrive                |                        |                  | 5    |                   | μs    |

| Output-Voltage Low                    | V CMPO          | $I_{\overline{CMPO}} = -20mA$ |                        |                  |      | 0.4               | V     |

| Open-Drain Leakage Current            | ICMPOLKG        | V <del>CMPO</del> = 14V       | $T_A = +25^{\circ}C$   |                  | 0.01 | 1.0 µA            |       |

| Open Drain Leakage Guitelli           | ICIVIPOLAG      | A CINIEO — 14A                | $T_A = +85^{\circ}C$   |                  | 0.1  |                   | μΛ    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 7.2V, EP = GND, V_{PWREN} = 5V, _LX$  unconnected,  $C_{REF} = 0.1\mu F$ ; when  $V_{IN}$  is specified, it implies all \_IN pins;  $T_A = -40^{\circ}C$  to +85°C. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted. Limits are 100% production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range are guaranteed by design and characterization.)

| PARAMETER                                | SYMBOL           | CONDITIONS               | MIN                            | TYP             | MAX | UNITS |

|------------------------------------------|------------------|--------------------------|--------------------------------|-----------------|-----|-------|

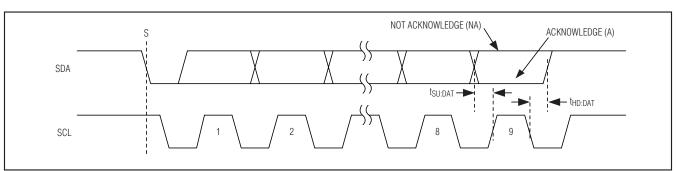

| I <sup>2</sup> C SERIAL INPUT/OUTPUT AND | LOGIC            |                          | •                              |                 |     | •     |

| Logic Input Low Voltage                  | VIL              |                          |                                |                 | 0.8 | V     |

| Logic Input High Voltage                 | VIH              |                          | 2.0                            |                 |     | V     |

| Input Leakage Current                    | ILKG             |                          | -1                             |                 | +1  | μΑ    |

| Output-Voltage Low                       | V <sub>OL</sub>  | I <sub>SINK</sub> = 3mA  |                                |                 | 0.4 | V     |

| Input/Output Capacitance                 | C <sub>I/O</sub> |                          |                                | 10              |     | рF    |

| Serial-Clock Frequency                   | fscl             |                          |                                |                 | 400 | kHz   |

| Clock Low Period                         | tLOW             |                          | 1.3                            |                 |     | μs    |

| Clock High Period                        | thigh            |                          | 0.6                            |                 |     | μs    |

| BUS Free Time                            | t <sub>BUF</sub> |                          | 1.3                            |                 |     | μs    |

| START Setup Time                         | tsu:sta          |                          | 0.6                            |                 |     | μs    |

| START Hold Time                          | thd:STA          |                          | 0.6                            |                 |     | μs    |

| STOP Setup Time                          | tsu:sto          |                          | 0.6                            |                 |     | μs    |

| Data-In Setup Time                       | tsu:dat          |                          | 100                            |                 |     | ns    |

| Data-In Hold Time                        | thd:dat          |                          | 0                              |                 | 900 | ns    |

| Receive SCL/SDA Minimum Rise<br>Time     | t <sub>R</sub>   | (Note 5)                 |                                | 0 + 0.1<br>CBUS |     | ns    |

| Receive SCL/SDA Maximum Rise Time        | t <sub>R</sub>   | (Note 5)                 |                                | 300             |     | ns    |

| Receive SCL/SDA Minimum Fall Time        | t <sub>F</sub>   | (Note 5)                 |                                | 0 + 0.1<br>CBUS |     | ns    |

| Receive SCL/SDA Maximum Fall Time        | t <sub>F</sub>   | (Note 5)                 |                                | 300             |     | ns    |

| Transmit SDA Fall Time                   | t <sub>F</sub>   | C <sub>BUS</sub> = 400pF | 20 + 0.1<br>x C <sub>BUS</sub> |                 | 300 | ns    |

| Pulse Width of Spike Suppressed          | tsp              | (Note 6)                 |                                | 50              |     | ns    |

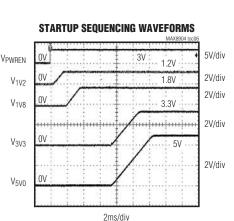

| SEQUENCER                                |                  |                          | <u> </u>                       |                 |     |       |

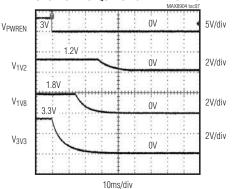

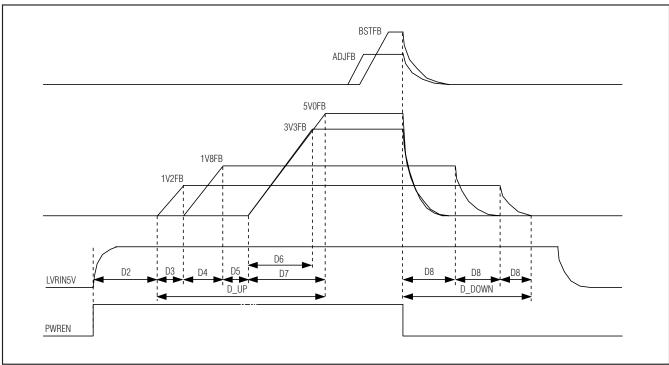

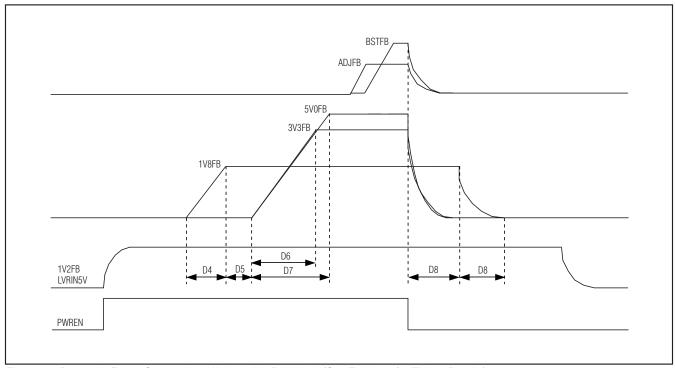

| POWER-UP SEQUENCING                      |                  |                          |                                |                 |     |       |

| 1V8 VOK to 3V3 Start Delay               |                  |                          |                                | 3.6             |     | ms    |

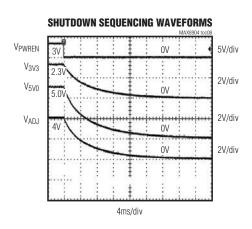

| POWER-DOWN SEQUENCING                    |                  |                          |                                |                 |     |       |

| 3V3 Disable to 1V8 Disable Delay         |                  |                          |                                | 15              |     | ms    |

| 1V8 Disable to 1V2 Disable Delay         |                  |                          |                                | 15              |     | ms    |

- **Note 3:** Not tested. Design guidance only.

- **Note 4:** The idle-mode current threshold is the transition point between fixed-frequency PWM operation and idle-mode operation. The specification is given in terms of output load current for inductor values specified in Figure 1.

- Note 5: CBUS = total capacitance of one bus line in pF. Rise and fall times are measured between 0.1 x VBUS and 0.9 x VBUS.

- Note 6: Input filters on SDA and SCL suppress noise spikes < 50ns.

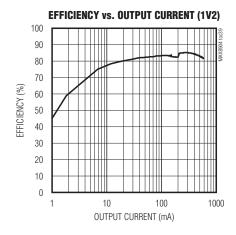

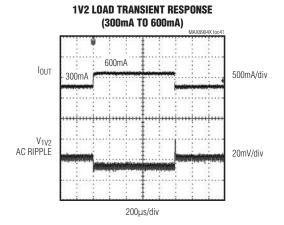

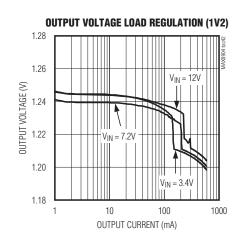

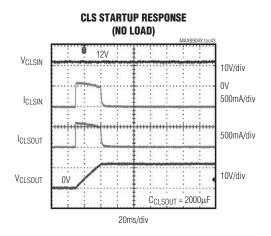

#### **Typical Operating Characteristics**

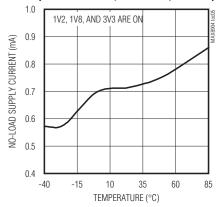

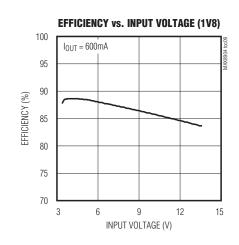

$(V_{IN} = 7.2V, V_{PWREN} = 3V, \overline{SHDN} \text{ unconnected}, V_{ADJ} = 4V, C_{REF} = 0.1 \mu F, circuit of Figure 1, T_A = +25 °C, unless otherwise noted.)$

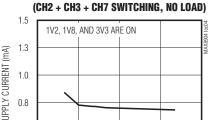

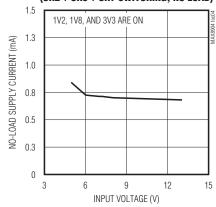

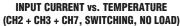

INPUT CURRENT vs. INPUT VOLTAGE

#### SHUTDOWN SEQUENCING WAVEFORMS

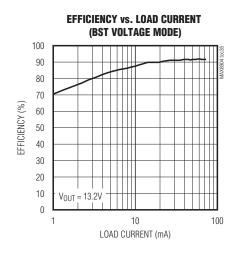

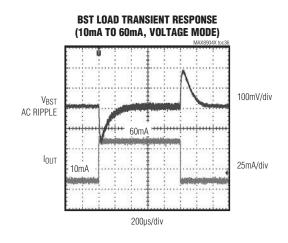

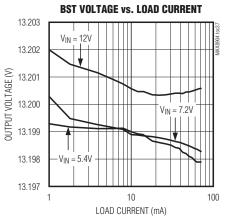

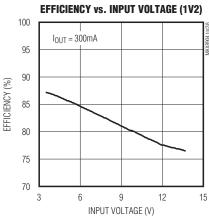

#### Typical Operating Characteristics (continued)

$(V_{IN} = 7.2V, V_{PWREN} = 3V, \overline{SHDN} \text{ unconnected}, V_{ADJ} = 4V, C_{REF} = 0.1 \mu F, circuit of Figure 1, T_A = +25 °C, unless otherwise noted.)$

#### Typical Operating Characteristics (continued)

(V<sub>IN</sub> = 7.2V, V<sub>PWREN</sub> = 3V, SHDN unconnected, V<sub>ADJ</sub> = 4V, C<sub>REF</sub> = 0.1μF, circuit of Figure 1, T<sub>A</sub> = +25°C, unless otherwise noted.)

#### Typical Operating Characteristics (continued)

(VIN = 7.2V, VPWREN = 3V, SHDN unconnected, VADJ = 4V, CREF = 0.1µF, circuit of Figure 1, TA = +25°C, unless otherwise noted.)

# 2000mA 1A/div 10UT 200 mA 1 50mV/div

200µs/div

ADJ LOAD TRANSIENT RESPONSE (200mA TO 2000mA TO 200mA)

#### Typical Operating Characteristics (continued)

(V<sub>IN</sub> = 7.2V, V<sub>PWREN</sub> = 3V, SHDN unconnected, V<sub>ADJ</sub> = 4V, C<sub>REF</sub> = 0.1μF, circuit of Figure 1, T<sub>A</sub> = +25°C, unless otherwise noted.)

#### Typical Operating Characteristics (continued)

(V<sub>IN</sub> = 7.2V, V<sub>PWREN</sub> = 3V, SHDN unconnected, V<sub>ADJ</sub> = 4V, C<sub>REF</sub> = 0.1μF, circuit of Figure 1, T<sub>A</sub> = +25°C, unless otherwise noted.)

###

200µs/div

#### Typical Operating Characteristics (continued)

(VIN = 7.2V, VPWREN = 3V, SHDN unconnected, VADJ = 4V, CREF = 0.1µF, circuit of Figure 1, TA = +25°C, unless otherwise noted.)

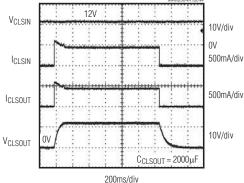

### CLS STARTUP AND SHUTDOWN RESPONSE (425mA LOAD) MAX8994X toc44

10μs/div

**OPEN-DRAIN COMPARATOR**

#### Typical Operating Characteristics (continued)

(V<sub>IN</sub> = 7.2V, V<sub>PWREN</sub> = 3V, SHDN unconnected, V<sub>ADJ</sub> = 4V, C<sub>REF</sub> = 0.1μF, circuit of Figure 1, T<sub>A</sub> = +25°C, unless otherwise noted.)

### Pin Description

| PIN  | NAME              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | CSOUT             | Output Voltage of the Current-Sense Amplifier. CSOUT is referenced to analog ground, GND. Its full-scale voltage is 1.2V for 60mV differential input voltage at CS+ and CS                                                                                                                                                                                                                                                                                                                                                           |

| 2    | RPGATE            | External p-MOSFET Gate Control Node for Reverse Polarity Protection. Internal reverse polarity sense circuitry controls the gate so that power is applied to the following n-MOSFET stage if and only if proper (positive) polarity of power is applied. If reverse polarity input power is applied, the p-MOSFET is kept off to protect the n-MOSFET stage and the IC.                                                                                                                                                              |

| 3    | OVPWR             | Supply Voltage and Overvoltage Detection Node for the Overvoltage Protection Circuitry. Connect OVPWR to system external supply in the absence of reverse polarity protection p-MOSFET. When reverse polarity protection p-MOSFET is used, connect OVPWR to the source of the reverse polarity protection p-MOSFET.                                                                                                                                                                                                                  |

| 4    | OVGATE            | External n-MOSFET Gate Control Node for Input Overvoltage Protection. The external n-MOSFET is turned on as long as VOVPWR is less than 13.3V. The external n-MOSFET is immediately turned off by pulling OVGATE low, when VOVPWR exceeds 13.3V, and the IC asserts the FLT output. The external n-MOSFET is turned back on when VOVPWR falls below OVP threshold. Note that the I <sup>2</sup> C interface is always alive, is independent of the overvoltage protection circuit, and turns off only when VLVROUT falls below 3.4V. |

| 5    | ADJBST            | ADJ Step-Down Converter Boost Capacitor Connection. Connect a 0.1µF ceramic capacitor between ADJBST and ADJLX                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6, 7 | ADJLX1,<br>ADJLX2 | ADJ Step-Down Converter Switching Node. Connect an inductor between ADJLX_ and the output of the ADJ converter. Connect a 0.1µF ceramic capacitor between ADJLX_ and ADJBST. Connect ADJLX1 to ADJLX2.                                                                                                                                                                                                                                                                                                                               |

| 8    | ADJIN             | ADJ Step-Down Converter Supply Input. Bypass ADJIN to power ground with a 4.7µF ceramic capacitor. Connect ADJIN to the input power supply node, V <sub>IN</sub> .                                                                                                                                                                                                                                                                                                                                                                   |

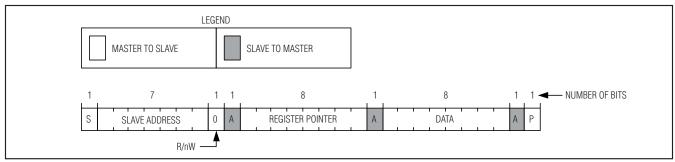

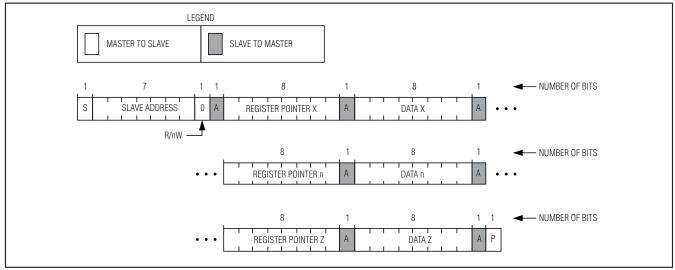

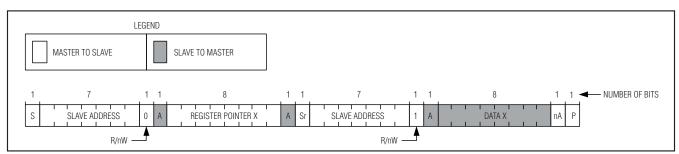

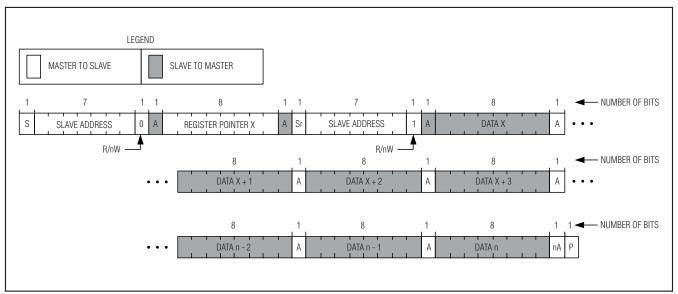

| 9    | ADJFB             | ADJ Step-Down Converter Feedback Input. Connect two 22µF or a 47µF output ceramic capacitor from the output inductor to power ground, and route the sense trace to ADJFB.                                                                                                                                                                                                                                                                                                                                                            |