# ві-смоs іс Fan Motor Driver Single-Phase Full-Wave Driver

http://onsemi.com

#### Overview

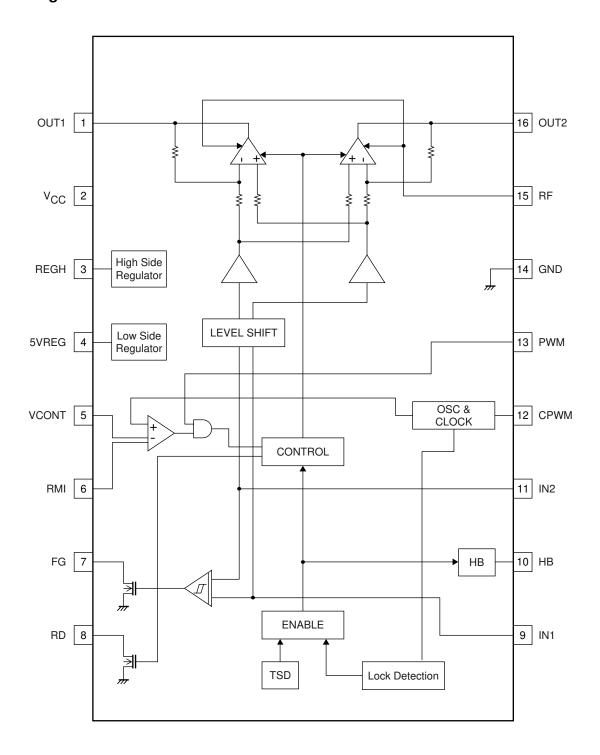

The LV8068V is single-phase bipolar fan motor is driven, through BTL output linear driver, at high efficiency, low power, and low noise by suppressing the reactive power. The BTL output can put PWM control by an outside signal together, which is optimum for the CPU cooler, etc.

#### **Functions**

- Single-phase full-wave operating by BTL output (BTL amplifier gain : +49dB)

- Speed control available by PWM input

- The characteristic of the motor rotational speed adjust by "VCONT" voltage

- The characteristic of the motor rotational minimum speed adjust by "RMI" voltage

- Hall bias output terminal (VHB = 1.32V (typ))

- Built-in Quick Start circuit

- Startup support function (50% Duty Start)

- FG (rotate detection) output terminal (Open drain output)

- RD (Lock detection) output terminal (Open drain output)

- Built-in Current Limiter circuit (limit at I<sub>O</sub> = 250mA with Rf = 1 connection, the limiter value determined with Rf.)

- Built-in lock protection and automatic return circuit

- Built-in thermal shut-down (TSD) circuit

### **Specitications**

### **Maximum Ratings** at Ta = 25°C

| Parameter                       | Symbol               | Conditions      | Ratings     | Unit |

|---------------------------------|----------------------|-----------------|-------------|------|

| Maximum supply voltage          | V <sub>CC</sub> max  |                 | 18          | V    |

| OUT pin output current          | I <sub>OUT</sub> max | In regular mode | 1.2         | Α    |

| OUT pin output voltage handling | V <sub>OUT</sub> max |                 | 18          | V    |

| RD output voltage handling      | V <sub>RD</sub> max  |                 | 18          | V    |

| RD output current               | I <sub>RD</sub> max  |                 | 5           | mA   |

| FG output voltage handling      | V <sub>FG</sub> max  |                 | 18          | V    |

| FG output current               | I <sub>FG</sub> max  |                 | 5           | mA   |

| HB output current               | I <sub>HB</sub> max  |                 | 10          | mA   |

| PWM input voltage handling      | VPWM max             |                 | 7           | V    |

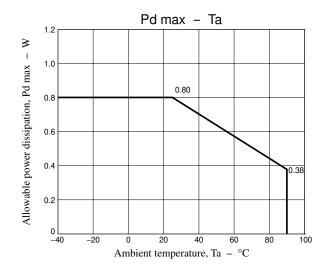

| Allowable power dissipation     | Pd max               | IC On board*    | 0.8         | W    |

| Operating temperature           | Topr                 |                 | -40 to +90  | °C   |

| Storage temperature             | Tstg                 |                 | -55 to +150 | °C   |

<sup>\*</sup> Specified board : 114.3mm × 76.1mm × 1.6mm, glass epoxy board

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### **Recommended Operating Conditions** at Ta = 25°C

| Parameter                            | Parameter Symbol Conditions |                                     | Ratings          | Unit |

|--------------------------------------|-----------------------------|-------------------------------------|------------------|------|

| Operating supply voltage1            | V <sub>CC</sub> op1         | Active at all circuit               | 6.0 to 16.0      | ٧    |

| Operating supply voltage2            | V <sub>CC</sub> op2         | Start-up with PWM=H and RMI=VCONT=L | 4.0 to 6.0       | ٧    |

| Hall input common-mode input voltage | VICM                        |                                     | 0.3 to 5VREG-1.5 | ٧    |

| range                                |                             |                                     |                  |      |

| VCONT input voltage range            | VCONTIN                     |                                     | 0.3 to 5VREG     | V    |

| RMI input voltage range              | VRMIIN                      |                                     | 0.3 to 5VREG     | ٧    |

| PWM input frequency range            | FPWMIN                      |                                     | 20 to 50         | kHz  |

# **Electrical Characteristics** at Ta = 25°C, $V_{CC} = 12.0$ V

| Parameter                            | Symbol              | Conditions                            | Ratings              |                      |                      | Unit   |

|--------------------------------------|---------------------|---------------------------------------|----------------------|----------------------|----------------------|--------|

| Parameter                            | Symbol              | Conditions                            | min                  | typ                  | max                  | Offile |

| Circuit current                      | Icc                 |                                       |                      | 6                    | 8                    | mA     |

| 5VREG output voltage                 | VRGL                | I5VREG = 5mA                          | 4.7                  | 5.0                  | 5.3                  | ٧      |

| REGH output voltage                  | VRGH                | IREGH = 5mA                           | V <sub>CC</sub> -4.6 | V <sub>CC</sub> -4.2 | V <sub>CC</sub> -3.9 | V      |

| HB bias voltage                      | VHB                 | IHB = 5mA                             | 1.22                 | 1.32                 | 1.42                 | V      |

| Hall Input bias current              | IHIN                |                                       |                      |                      | 1                    | μΑ     |

| Output ON voltage                    | VO                  | I <sub>O</sub> = 250mA, source + sink |                      | 0.35                 | 0.5                  | V      |

| Current limiter                      | VRF                 |                                       | 200                  | 250                  | 300                  | mV     |

| Hall amplifier output offset voltage | V <sub>IN</sub> OFS |                                       | -10                  |                      | 10                   | mV     |

| Hall amplifier voltage gain          | GH                  |                                       | 44                   | 49                   |                      | dB     |

| PWM pin bias current                 | IPWM                | PWM = GND                             | -20                  | -10                  | -3                   | μА     |

| PWM pin input Low level              | V <sub>PWM</sub> L  |                                       | 0                    |                      | 0.7                  | V      |

| PWM pin input High level             | V <sub>PWM</sub> H  |                                       | 2.5                  |                      | 5VREG                | ٧      |

| PWM input smallest pulse width       | TPWM                | Design guarantee*                     |                      | 5                    |                      | μs     |

| CPWM charge current                  | ICPC                |                                       | 13                   | 18                   | 23                   | μА     |

| CPWM discharge current               | ICPD                |                                       | 13                   | 18                   | 23                   | μА     |

| CPWM charge/ discharge current ratio | ICPRTO              | ICPRTO = ICPC/ICPD                    | 0.7                  | 1                    | 1.2                  |        |

| CPWM oscillation High level          | VCPH                |                                       | 3.3                  | 3.5                  | 3.8                  | V      |

| CPWM oscillation Low level           | VCPL                |                                       | 0.7                  | 1.0                  | 1.3                  | V      |

| CPWM oscillation amplitude width     | VCPA                |                                       | 2.3                  | 2.5                  | 2.7                  | V      |

| VCONT pin input bias current         | ICONT               |                                       |                      |                      | 1                    | μΑ     |

| RMI pin input bias current           | IRMI                |                                       |                      | _                    | 1                    | μА     |

| RD output Low-level voltage          | VRD                 | IRD = 3mA                             |                      | •                    | 0.3                  | V      |

<sup>\*:</sup> Design guarantee: Indicates a design target value. These parameters are not tested in the independent IC.

Continued on next page.

Caution 1) Absolute maximum ratings represent the values which cannot be exceeded for any length of time.

Caution 2) Even when the device is used within the range of absolute maximum ratings, as a result of continuous usage under high temperature, high current, high voltage, or drastic temperature change, the reliability of the IC may be degraded. Please contact us for the further details.

Continued from preceding page.

| Parameter                             | Cumbal           | Conditions            | Ratings |     |      | I I min |

|---------------------------------------|------------------|-----------------------|---------|-----|------|---------|

| Parameter                             | Symbol           | Conditions            | min     | typ | max  | Unit    |

| RD output leakage current             | I <sub>RDL</sub> | VRD = 18V             |         |     | 10   | μΑ      |

| FG output Low-level voltage           | V <sub>FG</sub>  | I <sub>FG</sub> = 3mA |         |     | 0.3  | V       |

| FG output leakage current             | I <sub>FGL</sub> | V <sub>FG</sub> = 18V |         |     | 10   | μΑ      |

| FG comparator hysteresis width        | ΔVFG             |                       | ±2      | ±4  | ±10  | mV      |

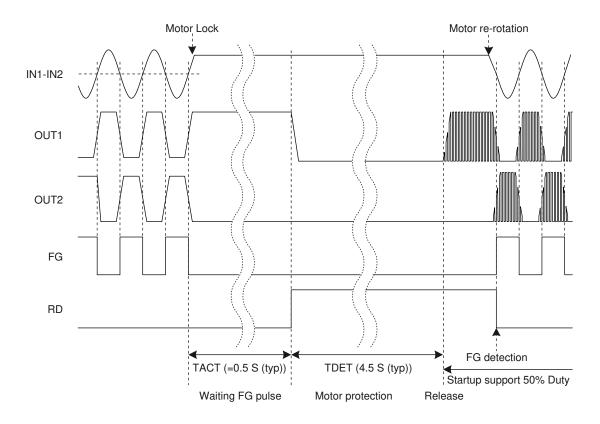

| Output ON time in Lock-detection      | TACT             | CPWM = 100pF          | 0.35    | 0.5 | 0.65 | sec     |

| Output OFF time in Lock-detection     | TDET             | CPWM = 100pF          | 3.0     | 4.5 | 6.0  | sec     |

| Output ON/OFF ratio in Lock-detection | TRTO             | TRTO = TDET/TACT      | 7       | 9   | 11   |         |

| Thermal shutdown oprating temperature | TSD              | Design guarantee*     |         | 180 |      | °C      |

| Thermal shutdown hysteresis width     | ΔTSD             | Design guarantee*     |         | 40  |      | °C      |

<sup>\*</sup> Design guarantee: Indicates a design target value. These parameters are not tested in the independent IC.

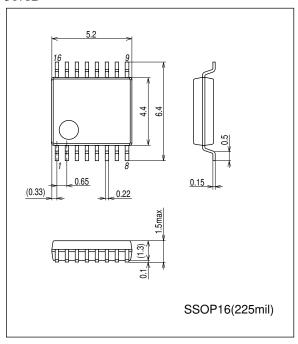

# **Package Dimensions**

unit : mm (typ)

3178B

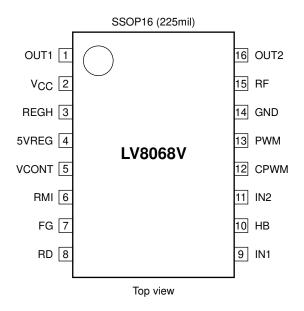

# **Pin Assignment**

# **Block Diagram**

# **Pin Function**

| PIN FUI |                  | Eunation                                                       | Equivalent organit |

|---------|------------------|----------------------------------------------------------------|--------------------|

| Pin No. | Pin name<br>OUT1 | Function  Motor driver output pin                              | Equivalent circuit |

|         |                  |                                                                |                    |

| 16      | OUT2             | Motor driver output pin                                        | 15                 |

| 2       | VCC              | Voltage supply pin                                             |                    |

| 3       | REGH             | Regulator voltage output pin for internal circuit (Upper side) | 3                  |

| 4       | 5VREG            | Regulator voltage output pin for internal circuit (Lower side) | 4                  |

| 5       | VCONT            | Output duty control pin for CPWM                               |                    |

| 6       | RMI              | Output minimum duty control pin for CPWM                       | 5                  |

| 7       | FG               | FG pulse output pin                                            |                    |

| 8       | RD               | RD pulse output pin                                            | 8 * **             |

| 9       | IN1              | Hall input - pin                                               |                    |

| 11      | IN2              | Hall input + pin                                               | 9 11               |

| 10      | НВ               | Hall bias output pin                                           |                    |

Continued on next page.

| Continued fro | tinued from preceding page. |                                                            |                    |  |  |  |  |  |

|---------------|-----------------------------|------------------------------------------------------------|--------------------|--|--|--|--|--|

| Pin No.       | Pin name                    | Function                                                   | Equivalent circuit |  |  |  |  |  |

| 12            | CPWM                        | Capacitor connection pin for PWM oscillator and Main clock |                    |  |  |  |  |  |

| 13            | PWM                         | PWM control input pin                                      |                    |  |  |  |  |  |

| 14            | GND                         |                                                            |                    |  |  |  |  |  |

| 15            | RF                          | Reference voltage pin for current limiter                  |                    |  |  |  |  |  |

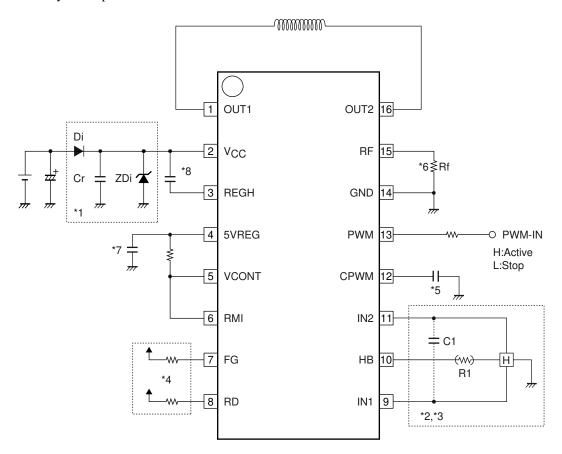

### **Sample Application Circuit**

1. Speed control by PWM pin

- \*1 When the diode Di is used to prevent device destruction from reverse connection, the capacitor Cr must be inserted to assure a path for regenerative currents.

- Similarly, if there no nearby capacitors on the fan power supply line, the capacitor Cr is also required to increase reliability. When a protection diode against reverse connection is used, if supply voltage increases due to coil kickback, connect zener diode between power supply and GND.

- \*2 The Hall element is biased at a constant voltage of approximately 1.3V from the HB pin. Thus the LV8068V provides a stable Hall output with excellent temperature characteristics. If the Hall output is needed to adjust the amplitude, use the resistor R1 as shown in the figure.

- \*3 When the wiring from the Hall output to IC Hall input is long, noise may be carried through the wiring. In this case, insert the capacitor C1 as shown in the figure.

- \*4 FG/RD pin is open collector (drain) output. This pin must be left open if unused.

- \*5 It is a capacitor for PWM oscillations. (Cpwm = 100pF, fpwm = about 33kHz (typ))

- \*6 The current limiter is activated when the voltage between current detection resistor exceeds 0.25V between GND and RF. The current limiter is activated at  $I_O = 250 \text{mA}$  when  $R_L = 1\Omega$ . Setting is made with the Rf resistance. Short-circuit GND and RF when the current-limiter PWM is not to be used.

- \*7 Please insert enough capacitor value between GND and RGL for stabilization on a terminal.

- \*8 Please insert enough capacitor value between Vcc and RGH for stabilization on a terminal.

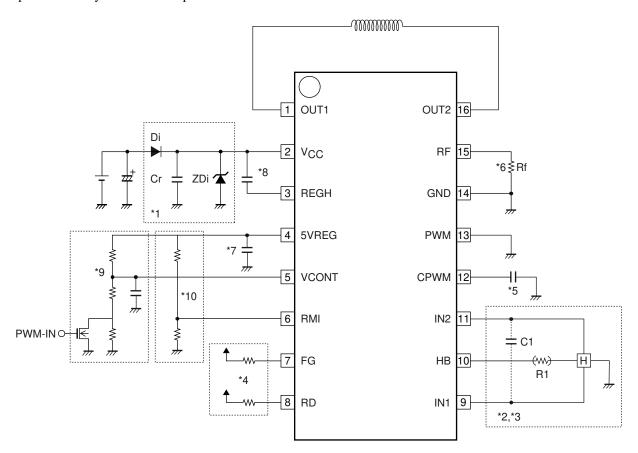

#### 2. Speed control by VCONT/RMI pin

- \*1 When the diode Di is used to prevent device destruction from reverse connection, the capacitor Cr must be inserted to assure a path for regenerative currents.

- Similarly, if there no nearby capacitors on the fan power supply line, the capacitor Cr is also required to increase reliability. When a protection diode against reverse connection is used, if supply voltage increases due to coil kickback, connect zener diode between power supply and GND.

- \*2 The Hall element is biased at a constant voltage of approximately 1.3V from the HB pin. Thus the LV8068V provides a stable Hall output with excellent temperature characteristics. If the Hall output is needed to adjust the amplitude, use theresistor R1 as shown in the figure.

- \*3 When the wiring from the Hall output to IC Hall input is long, noise may be carried through the wiring. In this case, insert the capacitor C1 as shown in the figure.

- \*4 FG/RD pin is open collector (drain) output. This pin must be left open if unused.

- \*5 It is a capacitor for PWM oscillations. (Cpwm = 100pF, fpwm = about 33kHz (typ))

- \*6 The current limiter is activated when the voltage between current detection resistor exceeds 0.25V between GND and RF. The current limiter is activated at  $I_O = 250 \text{mA}$  when  $R_L = 1\Omega$ . Setting is made with the Rf resistance. Short-circuit GND and RF when the current limiter PWM is not to be used.

- \*7 Please insert enough capacitor value between GND and RGL for stabilization on a terminal.

- \*8 Please insert enough capacitor value between Vcc and RGH for stabilization on a terminal.

- \*9 VCONT is speed control pin. For the control method ,refer to the timing chart.

- \*10 RMI is minimum speed setting pin. When you do not use RMI, please make pull-up to 5VREG

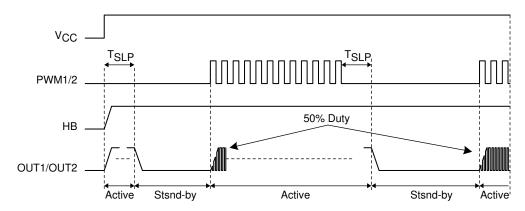

# **Timing Chart**

### 1. Stand-by/Start-up

- $*T_{SLP} = 400\mu s \text{ (typ)}$

- \*When PWM signal is input "L" level for continuousness TSLP, it becones the Stand-by mode by detecting above situation.

- \*When "H" level is input, it becomes the Active mode at once.

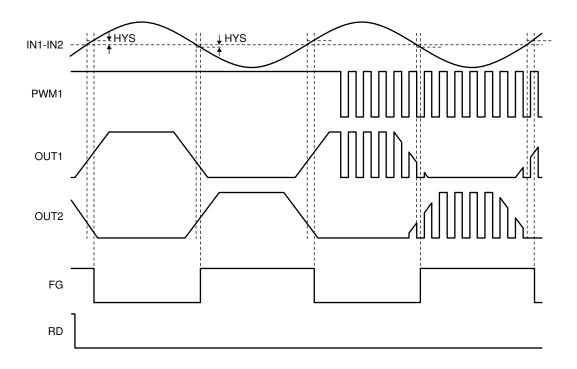

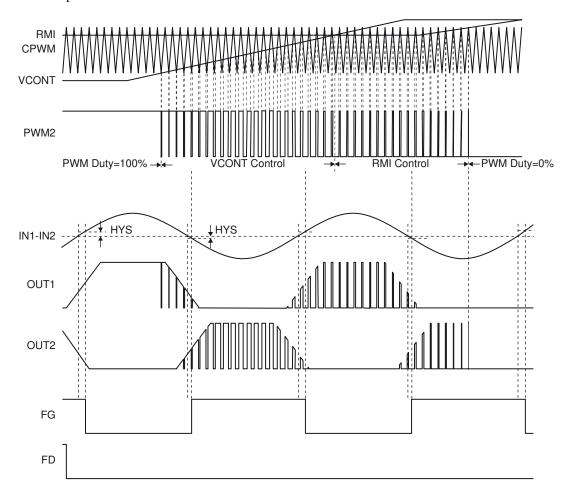

### 2. In Regular-Rotation

### • PWM pin control

• Truth table of mode in Regular-Rotation at PWM pin

| IN1 | IN2 | PWM | OUT1 | OUT2 | FG    | Mode       |

|-----|-----|-----|------|------|-------|------------|

|     | Н   | Н   | L    |      | Drive |            |

| Н   | L   | L   | L    | L    | L     | Regenerate |

|     |     | Н   | L    | Н    | OFF   | Drive      |

|     | Н   | L   | L    | L    | OFF   | Regenerate |

# • VCONT/RMI pin control

• Truth table of mode in Regular-Rotation at VCONT/RMI pin

| IN1 | IN2 | *PWM2 | OUT1 | OUT2 | FG   | Mode       |

|-----|-----|-------|------|------|------|------------|

| 11  | H L | Н     | Н    | L    | ,    | Drive      |

| Н   |     | L     | L    | L    | L    | Regenerate |

|     |     | Н     | L    | Н    | 0.55 | Drive      |

|     | Н   | L     | L    | L    | OFF  | Regenerate |

<sup>\*:</sup> IC's internal signal

#### 3. In Motor-Lock

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa