# PSR Single-Stage AC-DC LED Driver with High PF

#### **FEATURES**

- Primary side control without secondary feedback circuit

- Single-stage active PFC for high power factor and low THD

- High current accuracy ±3%

- ➤ No Dimming (FT8260/2x)

- > Three-level ON/Off Dimming (FT8261x)

- Ultra-low start up current

- Cycle-by-cycle current limit

- Over-voltage protection

- Short-circuit protection

- Over temperature protection

- Under voltage lockout protection

### **APPLICATIONS**

- > AC/DC LED driver applications

- Signal and decorative LED light

- E14/E27/PAR30/PAR38/GU10 LED lamp

- > T8/T10 LED String

### **DESCRIPTION**

The FT8260/1/2x is a single stage primary-side-control offline LED controller with high power factor, low THD and excellent current accuracy for isolated LED lighting applications.

The accurate current control from the primary side significantly simplifies the LED lighting system design by eliminating the secondary side feedback components and the opto-coupler.

The extremely low start-up current and quiescent current of FT8260/1/2x reduce the power consumption, resulting in excellent efficiency.

The multi-protection function of the FT8260/1/2x greatly enhances the system reliability and safety. The FT8260/1/2x features fruitful protection functions such as over-voltage protection, short-circuit protection, cycle-by-cycle current limit, over-temperature protection, VCC UVLO protection.

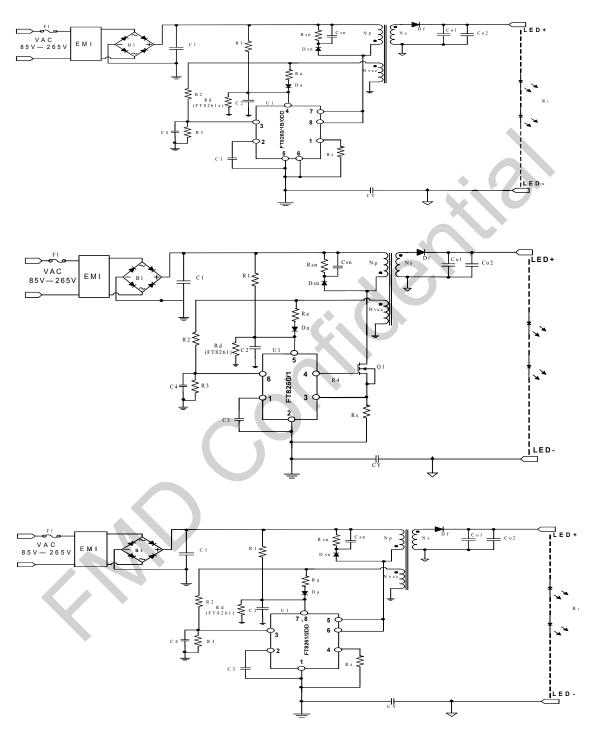

## **TYPICAL APPLICATION CIRCUIT**

Figure 1: Typical Application Circuit

## **ABSOLUTE MAXIMUM RATINGS**

| VCC to GND                  | 0.3V to +25V   |

|-----------------------------|----------------|

| Analog Inputs and Outputs   | 0.3V to 6V     |

| D to GND                    | 0.3V to 650V   |

| Operating Temperature Range | 40°C to +125°C |

| Junction Temperature        | 40°C to +150°C |

| Storage Temperature Range   | 55℃ to +150℃   |

| ESD Protection HBM          |                |

| ESD Protection MM           | 200V           |

<sup>\*</sup> Stresses exceed those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at conditions beyond those listed in the specification is not guaranteed. Prolonged exposure to extreme conditions may affect device reliability or functionality.

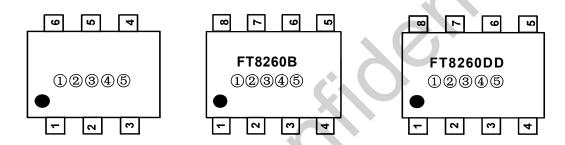

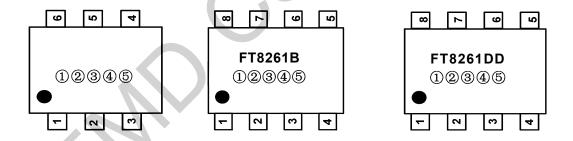

## **PIN CONFIGURATION**

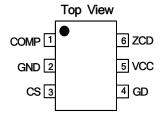

Figure 2.1: FT8260/1

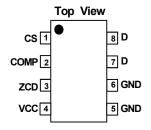

Figure 2.2: FT8260/1B/0DD

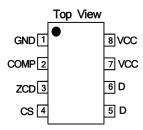

Figure 2.3: FT8261/2DD

## **TERMINAL DESCRIPTION**

| No.    | PIN  | FUNCTION                                                                               |

|--------|------|----------------------------------------------------------------------------------------|

| 1 COMP |      | Internal EA's output. This pin connects a capacitor to ground to stabilize the current |

| 1      | COMP | control loop                                                                           |

| 2      | GND  | Ground                                                                                 |

| 3      | cs   | Current sense pin. This pin connects a current sense resistor to GND                   |

| 4      | GD   | Gate drive output pin. Clamped to 13V to avoid excessive gate drive voltage            |

| 5      | VCC  | Power supply                                                                           |

|        |      | Zero current detection pin. A negative edge triggers the turn on signal of the         |

|        |      | external MOSFET. Connecting this pin through a resistor divider from the auxiliary     |

| 6      | ZCD  | winding to GND. Over-voltage condition is detected through ZCD. If ZCD voltage is      |

|        |      | higher than the over-voltage protection (OVP) threshold after a blanking time of       |

|        |      | 1us, the over-voltage condition is detected                                            |

Table 1.1 FT8260/1 terminal description

| No. | PIN  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1   | cs   | Current sense pin. This pin connects a current sense resistor to GND                                                                                                                                                                                                                                                                                                             |  |  |

| 2   | СОМР | Internal EA's output. This pin connects a capacitor to ground to stabilize the curre control loop                                                                                                                                                                                                                                                                                |  |  |

| 3   | ZCD  | Zero current detection pin. A negative edge triggers the turn on signal of the internal MOSFET. Connecting this pin through a resistor divider from the auxiliary winding to GND. Over-voltage condition is detected through ZCD. If ZCD voltage is higher than the over-voltage protection (OVP) threshold after a blanking time of 1us, the over-voltage condition is detected |  |  |

| 4   | VCC  | Power supply                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 5,6 | GND  | Ground                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 7,8 | D    | Internal power MOSFET drain                                                                                                                                                                                                                                                                                                                                                      |  |  |

Table1.2 FT8260/1B/0DD terminal description

| No. | PIN  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                         |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GND  | Ground                                                                                                                                                                                                                                                                                                                                                                           |

| 2   | СОМР | Internal EA's output. This pin connects a capacitor to ground to stabilize the current control loop                                                                                                                                                                                                                                                                              |

| 3   | ZCD  | Zero current detection pin. A negative edge triggers the turn on signal of the internal MOSFET. Connecting this pin through a resistor divider from the auxiliary winding to GND. Over-voltage condition is detected through ZCD. If ZCD voltage is higher than the over-voltage protection (OVP) threshold after a blanking time of 1us, the over-voltage condition is detected |

| 4   | CS   | Current sense pin. This pin connects a current sense resistor to GND                                                                                                                                                                                                                                                                                                             |

| 5,6 | D    | Internal power MOSFET drain                                                                                                                                                                                                                                                                                                                                                      |

| 7,8 | VCC  | Power supply                                                                                                                                                                                                                                                                                                                                                                     |

Table1.3 FT8261/2DD terminal description

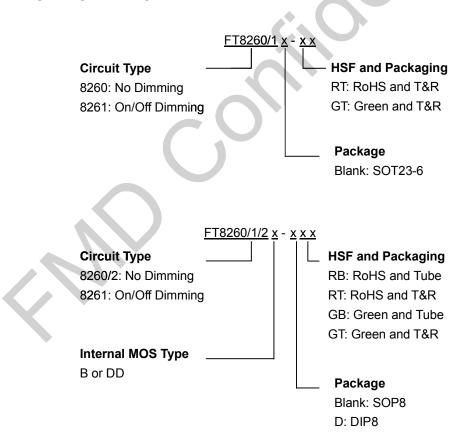

## ORDERING INFORMATION

| Part No. | Dimming Method         | Integrated<br>MOS | Power | Package | Remark |

|----------|------------------------|-------------------|-------|---------|--------|

| FT8260   | N/A                    | N/A               | 30W   | SOT23-6 |        |

| FT8260B  | N/A                    | 650V, 2A          | 7W    | SOP8    |        |

| FT8260DD | N/A                    | 650V, 4A          | 18W   | DIP8    | NRND   |

| FT8262DD | N/A                    | 650V, 4A          | 18W   | DIP8    | RND    |

| FT8261   | 3-level On-Off Dimming | N/A               | 30W   | SOT23-6 |        |

| FT8261B  | 3-level On-Off Dimming |                   | 7W    | SOP8    |        |

| FT8261DD | 3-level On-Off Dimming | 650V, 4A          | 18W   | DIP8    |        |

Table 2

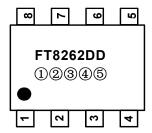

FT8260DD: Not Recommended for New Design

FT8262DD: Recommended for New Design, pin to pin vs FT8261DD

## **MARKING RULE**

Figure 3.1 FT8260x marking rule

Figure 3.2 FT8261x marking rule

Figure 3.3 FT8262DD marking rule

12345 for internal reference

## **BLOCK DIAGRAM**

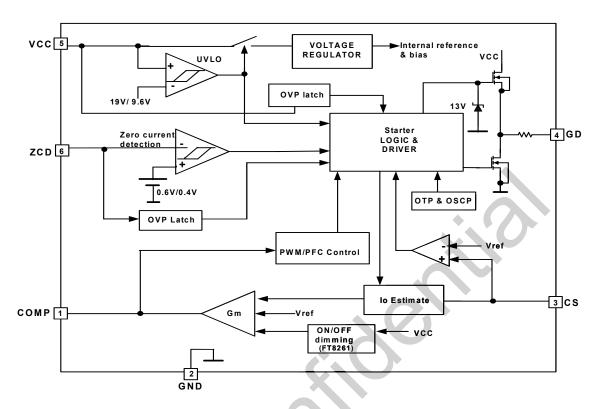

Figure 4.1 FT8260/1 Block Diagram

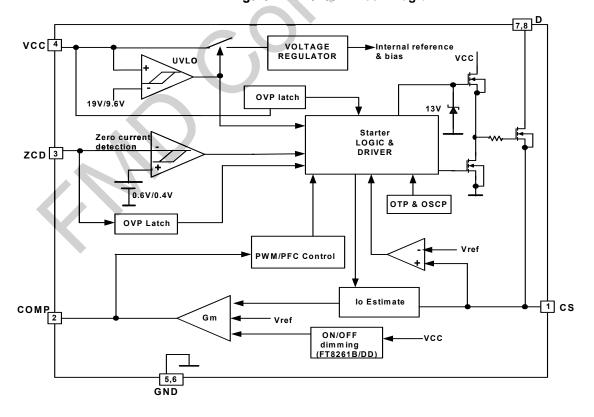

Figure 4.2 FT8260/1B/0DD Block Diagram

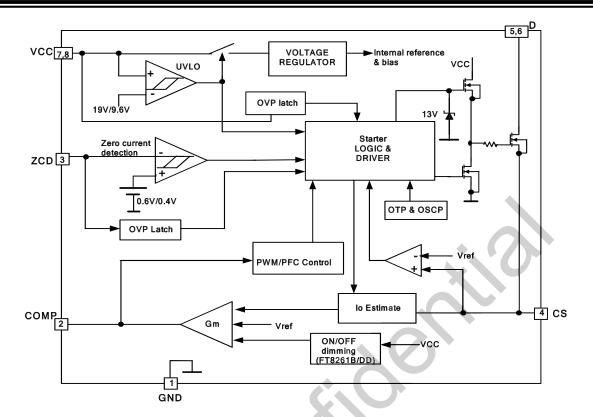

Figure 4.3 FT8261/2DD Block Diagram

## **ELECTRICAL CHARACTERISTICS**

(Tj = 25°C, VCC = 16V, unless otherwise specified)

| Symbol                  | Parameter               | Test Condition                             | Min   | Тур  | Max | Unit |

|-------------------------|-------------------------|--------------------------------------------|-------|------|-----|------|

| SUPPLY VOLT             | TAGE & SUPPLY CURRENT   |                                            |       |      |     |      |

| VCC <sub>on</sub>       | Turn-on threshold       |                                            |       | 19   |     | V    |

| VCC <sub>off</sub>      | Turn-off threshold      |                                            |       | 9.6  |     | V    |

| VCC <sub>OVP</sub>      | VCC over voltage        |                                            |       | 24   |     | V    |

| Istart-up               | Start-up current        |                                            |       | 23   |     | uA   |

| Iq                      | Quiescent Current       | No switching                               |       | 1.1  |     | mA   |

| Iclamp                  | VCC clamp current       |                                            |       | 3.5  |     | mA   |

| ERROR AMPL              | IFIER                   |                                            | •     |      |     |      |

| $V_{FB}$                | Feedback Input Voltage  |                                            |       | 0.4  |     | V    |

| V <sub>COMP</sub>       | Lower Clamp Voltage     |                                            |       | 0.9  |     | V    |

| V <sub>COMP_OVP</sub>   | OSCP COMP voltage       |                                            |       | 2.6  |     | V    |

|                         | NSE COMPARATOR          | •                                          |       |      |     |      |

|                         | Over current protection | _                                          |       |      |     |      |

| $V_{CSmax}$             | voltage                 |                                            |       | 1.8  |     | V    |

|                         | Leading Edge blanking   | A. (                                       |       |      |     |      |

| $t_{LEB}$               | time                    |                                            | ,     | 380  |     | ns   |

| ZERO CURRE              | NT DETECTOR             |                                            |       |      |     |      |

|                         | Zero Current Detect     |                                            |       |      |     | V    |

| $V_{ZCD\_T}$            | threshold               | (1)                                        |       | 0.4  |     |      |

| .,                      | Zero Current Detect     | (1) 0.2                                    |       | 0.0  |     |      |

| $V_{ZCD\_Hy}$           | Hystestic               |                                            |       | 0.2  |     | V    |

| V                       | ZCD over voltage        | 1us delay after                            | after |      |     | V    |

| $V_{ZCD\_OVP}$          | threshold               | turn-off                                   |       | 3.2  |     |      |

| LOGIC                   |                         |                                            |       |      |     |      |

| t <sub>START</sub>      | Start Timer period      |                                            |       | 140  |     | us   |

| $T_{off\_min}$          | Minimum off time        |                                            |       | 6.4  |     | us   |

| T <sub>on_max</sub>     | Maximum on time         |                                            |       | 24   |     | us   |

| GATE DRIVER             | R (FT8260/1)            | •                                          | •     |      |     |      |

| I <sub>GD</sub> -source | Max source current      |                                            |       | 65   |     | mA   |

| I <sub>GD</sub> -sink   | Max sink current        |                                            |       | -160 |     | mA   |

| Power MOSFE             | ET (FT8260/1B)          | •                                          | •     |      |     |      |

| _                       | Static drain-source on  | ., ,.,,                                    |       |      |     |      |

| R <sub>DSON</sub>       | resistance              | V <sub>GS</sub> =10V,I <sub>DS</sub> =0.5A |       | 4.5  |     | Ω    |

| D) /                    | Drain-source breakdown  | \/ =0\/1 =050::4                           |       |      |     | ν,   |

| BV <sub>DSS</sub>       | voltage                 | V <sub>GS</sub> =0V,I <sub>DS</sub> =250uA | 650   |      |     | V    |

| I <sub>DSS</sub>        | Drain-source leakage    | \\ -0\\\\ 050\\                            |       |      | 40  | ,    |

|                         | current                 | V <sub>GS</sub> =0V,V <sub>DS</sub> =650V  |       |      | 10  | uA   |

| I <sub>DMAX</sub>       | Maximum drain current   | Vd=3V                                      |       | 0.65 |     | Α    |

| Power MOSFET (FT8260/1/2DD) |                                   |                                            |     |     |     |                        |  |  |

|-----------------------------|-----------------------------------|--------------------------------------------|-----|-----|-----|------------------------|--|--|

| R <sub>DSON</sub>           | Static drain-source on resistance | V <sub>GS</sub> =10V,I <sub>DS</sub> =0.5A |     | 2.3 |     | Ω                      |  |  |

| BV <sub>DSS</sub>           | Drain-source breakdown voltage    | V <sub>GS</sub> =0V,I <sub>DS</sub> =250uA | 650 |     |     | V                      |  |  |

| I <sub>DSS</sub>            | Drain-source leakage current      | V <sub>GS</sub> =0V,V <sub>DS</sub> =650V  |     |     | 10  | uA                     |  |  |

| I <sub>DMAX</sub>           | Maximum drain current             | Vd=3V                                      |     | 1.3 |     | Α                      |  |  |

| ON-OFF DIMMI                | NG (FT8261x)                      |                                            |     |     |     |                        |  |  |

|                             | On-off Dimming level 1            | FT8261x                                    |     | 100 |     | %                      |  |  |

| K <sub>DIM</sub>            | On-off Dimming level 2            | FT8261x                                    |     | 50  |     | %                      |  |  |

|                             | On-off Dimming level 3            | FT8261x                                    |     | 25  |     | %                      |  |  |

| T <sub>ONOFF</sub>          | Time interval of On-off Dimming   | FT8261x, R1=280k,<br>C2=10uF, Rd=750k      |     |     | 1.5 | S                      |  |  |

| T <sub>RESET</sub>          | Time interval of Shutdown         | FT8261x, R1=280k,<br>C2=10uF, Rd=750k      | 2.5 |     |     | S                      |  |  |

| OVER TEMPER                 | OVER TEMPERATURE PROTECTION       |                                            |     |     |     |                        |  |  |

| OTP                         | OTP shut down                     |                                            |     | 150 |     | $^{\circ}\mathbb{C}$   |  |  |

| OTP-hys                     | OTP release                       |                                            |     | 130 |     | $^{\circ}\!\mathbb{C}$ |  |  |

Table 3

- (1) Parameters guaranteed by design, functionality tested in production.

- (2) FT8260DD is not recommended for new design.

## **FUNCTIONAL DESCRIPTION**

#### **Real Current Control**

FT8260/1/2x accurately regulates LED current by sensing the primary side information. The LED current can be easily set as following (refer to figure 1):

$$I_{out} = \frac{1}{2}*\frac{V_{\scriptscriptstyle FB}}{R_{\scriptscriptstyle S}}*\frac{N_{\scriptscriptstyle P}}{N_{\scriptscriptstyle S}}$$

Where  $N_P$  is the primary winding and  $N_S$  is the secondary winding;  $V_{FB}$  (=400mV) is the internal voltage reference and  $R_S$  is the external current sensing resistor.

#### **Power Factor Correction**

High power factor is achieved by constant on operation. By connecting a 1uF~2.2uF capacitor between the COMP pin and ground, the COMP pin voltage is relatively constant, constant on time is achieved by simple circuit structure.

#### Start Up

During start-up process, VCC is charged through a start-up resistor. As VCC reaches VCCon voltage, COMP pin is pre-charged by an internal circuit. After COMP reaches 0.9V and the internal control loop is settled, a starter signal is sent to GD Pin to power up the converter. The power is then supplied by the auxiliary winding once the voltage of the winding is high enough. The PWM signal is shut down if VCC goes below VCCoff threshold voltage, COMP Pin is then discharged to ground.

### **Line Compensation**

An offset current proportional to instantaneous mains voltage streams out CS pin. A compensation resistor inversely proportional to the offset current is added between ZCD Pin and transformer auxiliary winding to achieve excellent line compensation; the compensation resistor can be adjusted externally.

#### Zero current switching

The IC is switched on when the transformer is demagnetized after MOSFET's minimum off time about 6.4us typically. Internal circuitry connected to the ZCD pin detects the end of the secondary stroke. After MOSFET's minimum off time, if no demagnetization signal is detected on the ZCD pin, the controller generates a startup signal typically 140us after the last GD signal.

#### Leading Edge Blanking (LEB)

A turn on spike on CS pin will inevitably appear when the power MOSFET is switched on. At the beginning of each switching pulse, the current-limit comparator is disabled for around 380nsec to avoid premature termination. The gate driver output cannot be switched off during the blanking period.

### Output Over Voltage Protection (OUTovp)

Refer to figure 1, the voltage of ZCD pin is set by R2, R3 and auxiliary winding due to the coupling polarity between the auxiliary winding and the secondary winding of the transformer. Once the ZCD voltage exceeds 3.2V after a blanking time about 1us to allow the leakage inductance ringing fully damped, ZCD OVP is triggered, the IC stops switching, It can be reset by re-starting the voltage on pin VCC.

The OVP voltage can be adjusted by the equation:

$$V_{OUT\_OVP} = 3.2 * (1 + \frac{R2}{R3}) * \frac{N_S}{N_{VCC}} + V_{Df}$$

Where  $N_S$  is secondary winding,  $N_{VCC}$  is the auxiliary winding,  $V_{Df}$  is the forward bias voltage of the secondary diode.

### VCC Over Voltage Protection (VCCovp)

Once the VCC voltage exceeds 24V and last for about 6us, VCC OVP is triggered, the IC stops switching, VCC voltage will be pulled down. It can be reset by re-starting the voltage on pin VCC. It is recommended to set the VCC normal operating voltage between 11V and 22V.

#### **Output Short Circuit Protection**

When output short circuit detected, the system works at low frequency (Fop=7KHz), so the power consumption is low, meanwhile COMP pin voltage will rise. When COMP voltage exceeds 2.6V, the power MOSFET will be shut down immediately. It can be reset by re-starting the voltage on pin VCC.

#### **Over Current Protection**

FT8260/1/2x immediately turns off the power MOSFET once the voltage at CS pin exceeds 1.8V. This cycle by cycle current limitation scheme prevents the relevant components, such as power MOSFET, transformer, etc. from damage.

#### **Over Temperature Protection**

The thermal protection circuitry in the FT8260/1/2x senses the die temperature after start up. When the temperature on die rises to  $150^{\circ}$ C, the power MOSFET will be shut down immediately and will remain switched off until the temperature on die falls to  $130^{\circ}$ C.

### ON-OFF-Dimming (For FT8261x only)

Compare to Triac dimming, ON-OFF dimming is a simple and green solution to LED lighting applications. FT8261x enables three-level ON/OFF dimming function with proper choice of VCC capacitor and discharge resistor Rd. By simply counting the number of wall switch toggling, the output power cycles through the 100%, 50% and 25% settings, in that order. There are two parameters governing the ON/OFF action. If mains switch is turned off and stays off for longer than  $T_{RESET}$ , the turning off is regarded as true turning-off action, hence any subsequent turning on will output rated 100% power. If the wall switch is turned on and off or toggles in less than  $T_{ONOFF}$  apart, the output will go through 100%, 50%, 25% rated power levels and repeat the process.  $T_{RESET}$  and  $T_{ONOFF}$  can be set by the VCC capacitor, C2 and the resistor between VCC and GND, Rd. Typical settings are given in Table 3.

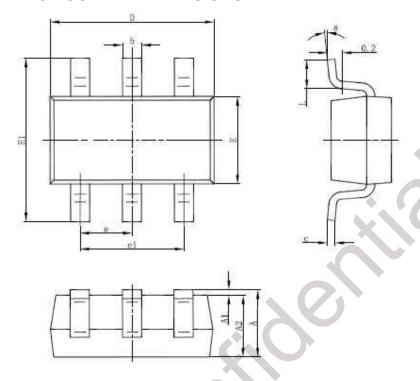

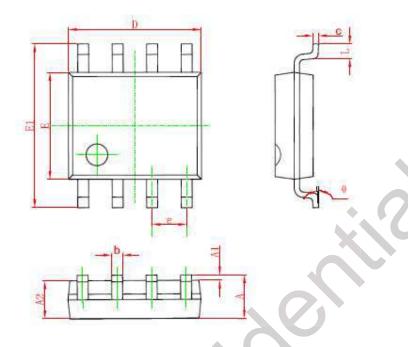

## **SOT23-6 PACKAGE OUTLINE DIMENSIONS**

|          |                           |                   | ~         |             |

|----------|---------------------------|-------------------|-----------|-------------|

| Symbol   | Dimensions In Millimeters |                   | Dimension | s In Inches |

| Oyiliboi | Min                       | Max               | Min       | Max         |

| Α        | 1.050                     | 1.250             | 0.041     | 0.049       |

| A1       | 0.000                     | 0.100             | 0.000     | 0.004       |

| A2       | 1.050                     | 1.150             | 0.041     | 0.045       |

| b        | 0.300                     | 0.500             | 0.012     | 0.020       |

| С        | 0.100                     | 0.200             | 0.004     | 0.008       |

| D        | 2.820                     | 3.020             | 0.111     | 0.119       |

| E        | 1.500                     | 1.700             | 0.059     | 0.067       |

| E1       | 2.650                     | 2.950             | 0.104     | 0.116       |

| е        | 0.950                     | 0.950 (BSC) 0.037 |           | (BSC)       |

| e1       | 1.800                     | 2.000             |           | 0.079       |

| L        | 0.300                     | 0.600             |           | 0.024       |

| θ        | 0°                        | 8°                | 0°        | 8°          |

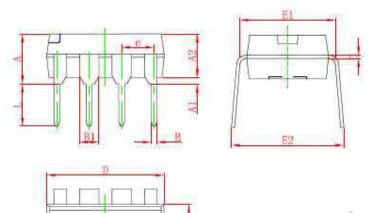

## **SOP8 PACKAGE OUTLINE DIMENSIONS**

|        | Dimensions in Millimeters |       | Dimension      | s in Inches |

|--------|---------------------------|-------|----------------|-------------|

| Symbol | Mix                       | Max   | Min            | Max         |

| А      | 1.350                     | 1.750 | 0.053          | 0.069       |

| A1     | 0.100                     | 0.250 | 0.004          | 0.010       |

| A2     | 1.350                     | 1.550 | 0.053          | 0.061       |

| b      | 0.330                     | 0.510 | 0.013          | 0.020       |

| С      | 0.170                     | 0.250 | 0.006          | 0.010       |

| D      | 4.700                     | 5.100 | 0.185          | 0.200       |

| E      | 3.800                     | 4.000 | 0.150          | 0.157       |

| E1     | 5.800                     | 6.200 | 0.228          | 0.244       |

| е      | 1.270                     | (BSC) | C) 0.050 (BSC) |             |

| L      | 0.400                     | 1.270 | 0.016          | 0.050       |

| θ      | 0°                        | 8°    | 0°             | 8°          |

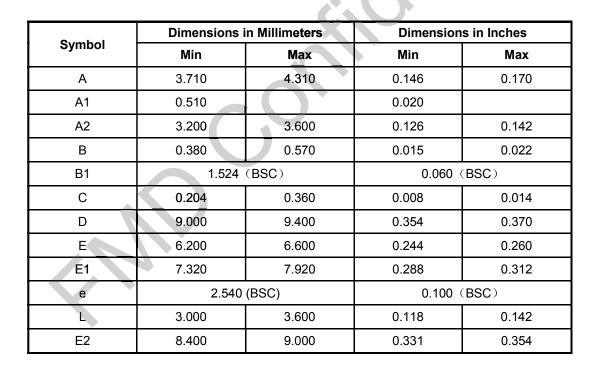

## **DIP8 PACKAGE OUTLINE DIMENSIONS**

## Fremont Micro Devices (SZ) Limited

#5-8, 10/F, Changhong Building, Ke-Ji Nan 12 Road, Nanshan District, Shenzhen

Tel: (86 755) 86117811 Fax: (86 755) 86117810

### Fremont Micro Devices (Hong Kong) Limited

#16, 16/F, Blk B, Veristrong Industrial Centre, 34-36 Au Pui Wan Street, Fotan, Shatin, Hong Kong

Tel: (852) 27811186 Fax: (852) 27811144

### Fremont Micro Devices (USA), Inc.

42982 Osgood Road Fremont, CA 94539

Tel: (1-510) 668-1321 Fax: (1-510) 226-9918

Web Site: http://www.fremontmicro.com/

<sup>\*</sup> Information furnished is believed to be accurate and reliable. However, Fremont Micro Devices, Incorporated (BVI) assumes no responsibility for the consequences of use of such information or for any infringement of patents of other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of Fremont Micro Devices, Incorporated (BVI). Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. Fremont Micro Devices, Incorporated (BVI) products are not authorized for use as critical components in life support devices or systems without express written approval of Fremont Micro Devices, Incorporated (BVI). The FMD logo is a registered trademark of Fremont Micro Devices, Incorporated (BVI). All other names are the property of their respective owners.