# 2-wire serial sound control IC BH3856S / BH3856FS

The BH3856S and BH3856FS are signal processing ICs designed for volume and tone control in televisions, mini component stereo systems, and other audio products. Their two-line serial control (I<sup>2</sup>C BUS) enables them to control volume and tone on the basis of signals from a microcomputer, etc.

#### Applications

Televisions, [Video equipped television], personal computer televisions, mini component stereo systems, car stereos.

#### Features

- 1) I<sup>2</sup>C BUS facilitates direct serial control from a microcomputer of volume (main volume), balance (left / right), and tone (bass, treble). DC control is also possible.

- 2) Volume is produced by a low-distortion, low-noise VCA. Designed to minimize step noise.

- 3) Stable standard voltage supply and built-in I/O buffer mean that few attachments are needed. SSOP-A32 package designed to save space.

- 4) Matrix surround yields powerful sound.

#### ● Absolute maximum ratings (Ta = 25°C)

| Parameter                                 |          | Symbol   | Limits   | Unit  |

|-------------------------------------------|----------|----------|----------|-------|

| Power supply voltage                      |          | Vcc 10.0 |          | V     |

| Power dissipation                         | BH3856S  | Pd       | 1200*1   | mW    |

| Power dissipation                         | BH3856FS | Pu       | 850 *2   | IIIVV |

| Operating temperature Storage temperature |          | Topr     | -40~+85  | °C    |

|                                           |          | Tstg     | -55~+150 | °C    |

\*1 Reduced by 12mW for each increase in Ta of 1°C over 25°C.

\*2 Reduced by 6.8mW for each increase in Ta of 1°C over 25°C.

#### •Recommended operating conditions (Ta = 25°C)

| Parameter            | Symbol | Min. | Тур. | Max. | Unit |

|----------------------|--------|------|------|------|------|

| Power supply voltage | Vcc    | 6.0  | 9    | 9.5  | V    |

Note : I<sup>2</sup>C BUS is a registered trademark of Philips.

# BH3856S / BH3856FS

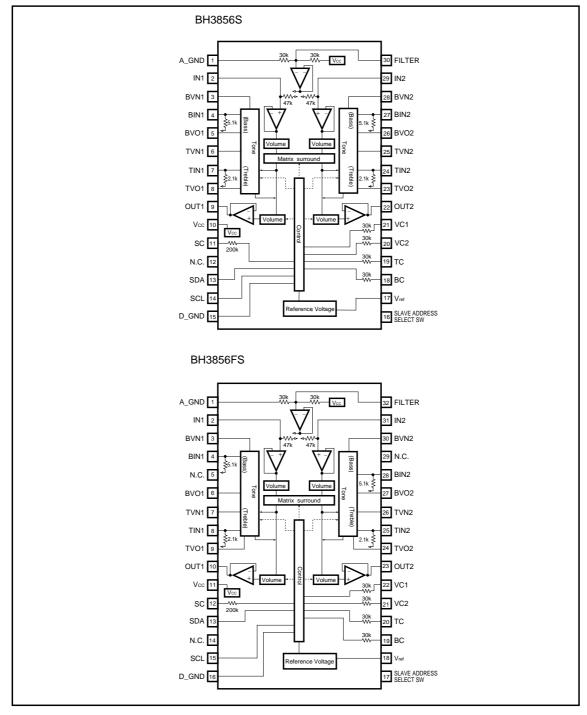

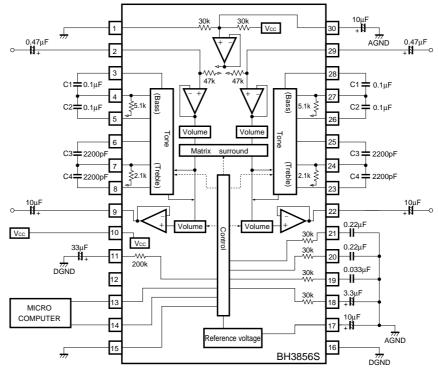

#### Block diagram

# Audio ICs

### Pin descriptions

| Pin     | No.       | Pin name | Function                                            |  |  |  |  |

|---------|-----------|----------|-----------------------------------------------------|--|--|--|--|

| BH3856S | BH3856FS  | Tinname  |                                                     |  |  |  |  |

| 1       | 1         | A_GND    | Analog ground                                       |  |  |  |  |

| 2       | 2         | IN1      | Channel 1 volume input                              |  |  |  |  |

| 3       | 3         | BVN1     | Channel 1 bass filter                               |  |  |  |  |

| 4       | 4         | BIN1     | Channel 1 bass filter                               |  |  |  |  |

| 5       | 6         | BVO1     | Channel 1 bass filter                               |  |  |  |  |

| 6       | 7         | TVN1     | Channel 1 treble filter                             |  |  |  |  |

| 7       | 8         | TIN1     | Channel 1 treble filter                             |  |  |  |  |

| 8       | 9         | TVO1     | Channel 1 treble filter                             |  |  |  |  |

| 9       | 10        | OUT1     | Channel 1 volume output                             |  |  |  |  |

| 10      | 11        | Vcc      | Power supply                                        |  |  |  |  |

| 11      | 12        | SC       | Time constant pin for prevention of switching shock |  |  |  |  |

| 13      | 13        | SDA      | SDA data input pin                                  |  |  |  |  |

| 14      | 15        | SCL      | SCL data input pin                                  |  |  |  |  |

| 15      | 16        | D_GND    | Digital ground                                      |  |  |  |  |

| 16      | 17        | SASS     | Slave address selection pin                         |  |  |  |  |

| 17      | 18        | Vref     | Reference voltage output                            |  |  |  |  |

| 18      | 19        | BC       | Time constant pin for prevention of switching shock |  |  |  |  |

| 19      | 20        | TC       | Time constant pin for prevention of switching shock |  |  |  |  |

| 20      | 21        | VC2      | Time constant pin for prevention of switching shock |  |  |  |  |

| 21      | 22        | VC1      | Time constant pin for prevention of switching shock |  |  |  |  |

| 22      | 23        | OUT2     | Channel 2 volume output                             |  |  |  |  |

| 23      | 24        | TVO2     | Channel 2 treble filter                             |  |  |  |  |

| 24      | 25        | TIN2     | Channel 2 treble filter                             |  |  |  |  |

| 25      | 26        | TVN2     | Channel 2 treble filter                             |  |  |  |  |

| 26      | 27        | BVO2     | Channel 2 bass filter                               |  |  |  |  |

| 27      | 28        | BIN2     | Channel 2 bass filter                               |  |  |  |  |

| 28      | 30        | BVN2     | Channel 2 bass filter                               |  |  |  |  |

| 29      | 31        | IN2      | Channel 2 volulme input                             |  |  |  |  |

| 30      | 32        | FILTER   | Filter                                              |  |  |  |  |

| 12      | 5, 14, 29 | N.C.     | Not connected internally.                           |  |  |  |  |

### Audio ICs

| Symbol       | Pin voltage  | Equivalent circuit                          | Description                                                                                                                           |

|--------------|--------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| IN1<br>IN2   | 4.5V<br>4.5V | 2pin<br>31pin<br>4.GND 2/1Vcc               | Main volume input pin.<br>Designed for input impedance of 47kΩTyp.).                                                                  |

| BVN1<br>BVN2 | 4.5V<br>4.5V | Vac<br>50kG<br>A_GND<br>A_GND               | Pin for low band filter connection.                                                                                                   |

| BIN1<br>BIN2 | 4.5V<br>4.5V | 4pin<br>28pin<br>A_GND                      | Pin for low band filter connection.                                                                                                   |

| BVO1<br>BVO1 | 4.5V<br>4.5V | Voc<br>Spin<br>27pin<br>A_GND               | Pin for low band filter connection.                                                                                                   |

| FILTER       | 5.2V         | Voc<br>4_GND<br>Voc<br>30kΩ<br>30kΩ<br>30kΩ | Filter input pin.<br>Please install a capacitor of about 10µF to<br>the filter pin.<br>Has built-in precharge and discharge circuits. |

| TVN1<br>TVN2 | 4.5V<br>4.5V | Vcc<br>25k2<br>A_GND<br>A_GND               | Pin for high band filter connection.                                                                                                  |

| TIN1<br>TIN2 | 4.5V<br>4.5V | Vcc<br>8pin<br>25pin<br>2.1kΩ<br>4_GND      | Pin for high band filter connection.                                                                                                  |

\*The pin numbers are for the BH3856S.

# Audio ICs

| Symbol                       | Pin voltage  | Equivalent Circuit                                                     | Description                                                                                                                                                                                                                                                                                   |

|------------------------------|--------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TVO1<br>TVO2                 | 4.5V<br>4.5V | Vcc<br>25k0<br>A_GND<br>24pin                                          | Pin for high band filter connection.                                                                                                                                                                                                                                                          |

| OUT1<br>OUT2                 | 4.5V<br>4.5V | Vcc<br>10pin<br>24pin<br>A_GND                                         | Main volume output pin.<br>OUT1 is the volume output for Channel 1.<br>OUT2 is the volume output for Channel 2.                                                                                                                                                                               |

| SC<br>BC<br>TC<br>VC1<br>VC2 | _            | Vac<br>Digual<br>12pn<br>12pn<br>12pn<br>22pn<br>22pn<br>21pn<br>A_GND | For prevention of shock noise during<br>step switching.<br>SC : Surround pin<br>BC : Bass pin<br>TC : Treble pin<br>VC1 : Volume pin (Channel 1)<br>VC2 : Volume pin (Channel 2)                                                                                                              |

| Vref                         | 3.8V         | 18pin<br>A_GND                                                         | 3.8V regulator output pin.<br>Output requires capacitor for stopping<br>oscillation. Output pin has built-in precharge<br>and discharge circuits, so there is no problen<br>with start-up or shut-down even with a large<br>capacitor. This pin is for connection to the<br>high-band filter. |

| SDA<br>SCL<br>SASS           | _            | Vcc<br>2kQ<br>13pin<br>15pin<br>17pin<br>A_GND                         | <ul> <li>I<sup>2</sup>C bass input pin<br/>SDA : serial data line<br/>SCL : serial clock line</li> <li>Slave address selection pin<br/>SASS: slave address selection switch</li> </ul>                                                                                                        |

| Vcc                          | -            | Power supply voltage pin.                                              |                                                                                                                                                                                                                                                                                               |

| A_GND                        | -            | Analog GND pin. Connected to IC board.                                 |                                                                                                                                                                                                                                                                                               |

| D_GND                        | -            | Digital GND pin. Separate from Analog GND pin.                         |                                                                                                                                                                                                                                                                                               |

\*The pin numbers are for the BH3856S.

| TONE =                                            | ALL FLA | T, Rg = | 600Ω, I | R∟ = 10 | kΩ)   |                                                   |

|---------------------------------------------------|---------|---------|---------|---------|-------|---------------------------------------------------|

| Parameter                                         | Symbol  | Min.    | Тур.    | Max.    | Unit  | Conditions                                        |

| Quiescent current                                 | la      | -       | 20      | 27      | mA    | No signal                                         |

| Maximum input                                     | Vim     | 2.3     | 2.5     | _       | Vrms  | THD=1%, VOL=-20dB (ATT)                           |

| Maximum output                                    | Vom     | 2.3     | 2.5     | _       | Vrms  | THD=1%                                            |

| Voltage gain                                      | Gv      | -1.5    | 0       | +1.5    | dB    | V <sub>IN</sub> =1Vrms                            |

| Maximum attenuation                               | ATT     | 90      | 110     | -       | dB    | Vo=1Vrms                                          |

| Crosstalk                                         | Vст     | 70      | 80      | _       | dB    | Vo=1Vrms                                          |

| Low ronge control width                           | VB Max. | +12     | +15     | +18     | dB    | 100Hz, VIN=100mVrms                               |

| Low range control width                           | VB Min. | -18     | -15     | -12     | dB    | 100Hz, VIN=100mVrms                               |

| High range control width                          | VT Max. | +12     | +15     | +18     | dB    | 100kHz, V <sub>IN</sub> =100mVrms                 |

|                                                   | VT Min. | -18     | -15     | -12     | dB    | 100kHz, V <sub>IN</sub> =100mVrms                 |

| Matrix surround single-channel gain               | Gsr     | 4       | 6       | 8       | dB    | Vo=1Vrms *                                        |

| Total Harmonic distortion                         | THD     | -       | 0.01    | 0.1     | %     | Vo=0.5Vrms, BPF=400Hz~30kHz                       |

| Output noise voltage                              | VN01    | -       | 45      | 65      | μVrms | No signal, VOL=Max., Rg=0 *                       |

| Residual output noise voltage                     | VMNO    | -       | 2       | 10      | μVrms | No signal, VOL=–∞, R <sub>g</sub> =0 *            |

| Reference power supply output voltage             | Vref    | 3.5     | 3.8     | 4.1     | V     | Iref=3mA                                          |

| Reference power supply<br>output current capacity | Iref    | 3.0     | 10      | _       | mA    | V <sub>ref</sub> > 3.7V                           |

| Channel balance                                   | Gсв     | -1.5    | 0       | +1.5    | dB    | channel 1 taken as the standard for measurements. |

| Input impedance                                   | Rın     | 33      | 47      | 61      | kΩ    | f=1kHz                                            |

| Output impedance                                  | Rout    | -       | -       | 10      | Ω     | f=1kHz                                            |

| Ripple rejection ratio                            | RR      | 40      | -       | _       | dB    | f=100Hz, V <sub>RR</sub> =1Vrms                   |

| Input high level voltage                          | Vін     | 4       | -       | _       | V     | SCL, SDA                                          |

| Input low level voltage                           | Vil     | -       | _       | 1       | V     | SCL, SDA                                          |

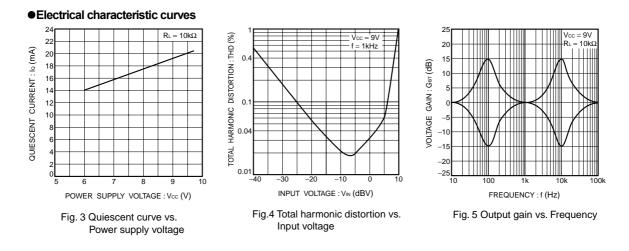

#### • Electrical characteristics (unless otherwise noted, Ta = 25°C, V $\infty$ = 9V, f = 1kHz, BW = 20 ~ 20kHz, VOL = Max., TONE = ALL FLAT, Rg = 600 $\Omega$ , RL = 10k $\Omega$ )

\* Measurement performed using Matsushita Communication Industrial VP-9690A DIN AUDIO filter (average value wave detection, effective value display). © Not designed for radiation resistance.

Signal input occurs in equiphase.

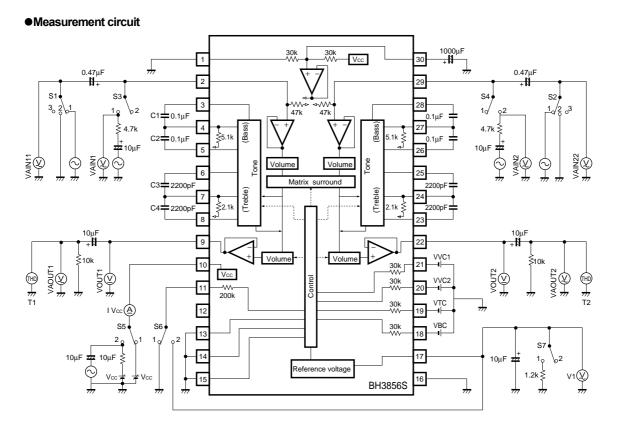

Units : R [Ω] C [F]

Fig.1

Note : Diagram depicts the BH3856S.

### Audio ICs

#### •Performing data settings

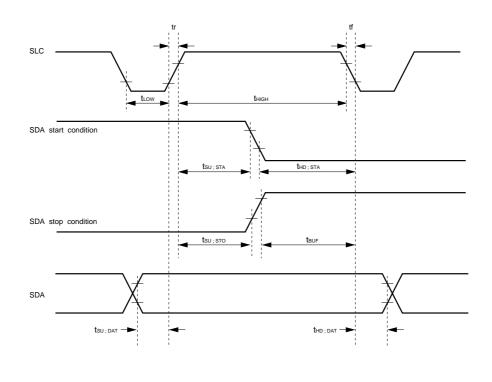

#### (1) I<sup>2</sup>C BUS timing

| Parameter                                                                                              | Symbol       | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------------------------------------------------------|--------------|------|------|------|------|

| SCL clock frequency                                                                                    | fsc∟         | 0    | -    | 100  | kHz  |

| SCL clock hold time, HIGH state                                                                        | tніgн        | 4    | _    | -    | μs   |

| SCL clock hold time, LOW state                                                                         | t∟ow         | 4.7  | _    | -    | μs   |

| SDA and SDL signal start-up time                                                                       | tr           | -    | -    | 1    | μs   |

| SDA and SDL signal shut-down time                                                                      | tf           | -    | _    | 0.3  | μs   |

| Set-up time for re-send [start] conditions                                                             | tsu;sta      | 4.7  | _    | -    | μs   |

| Hold time (re-send) [start] conditions<br>(After hold time ends, initial clock<br>pulse is generated.) | thd;sta      | 4    | _    | _    | μs   |

| Set time for [stop] conditions.                                                                        | tsu;sto      | 4.7  | -    | -    | μs   |

| Bus free time between [stop] condition<br>and [start] condition                                        | <b>t</b> BUF | 4.7  | -    | -    | μs   |

| Data set-up time                                                                                       | tsu;dat      | 250  | -    | -    | ns   |

$\label{eq:tsu} \begin{array}{l} t_{\text{SU}\,;\,\text{STA}} = start \mbox{ code set-up time.} \\ t_{\text{HD}\,;\,\text{STA}} = start \mbox{ code hold time.} \\ t_{\text{SU}\,;\,\text{STO}} = stop \mbox{ code set-up time.} \end{array}$

$\label{eq:bus} \begin{array}{l} t_{\text{BUF}} = bus \ free \ time. \\ t_{\text{SU}\,;\,\text{DAT}} = data \ set\text{-up time.} \\ t_{\text{HD}\,;\,\text{DAT}} = data \ hold \ time. \end{array}$

I<sup>2</sup>C BUS timing rules

### Audio ICs

| (2) I <sup>2</sup> C BUS data format |

|--------------------------------------|

|--------------------------------------|

|   | (2)10 | , DOS uala ionnal |      |                |      |         |      |      |

|---|-------|-------------------|------|----------------|------|---------|------|------|

|   |       | MSB LSE           |      | MSB LSB        |      | MSB LSB |      |      |

|   | S     | Slave address     | A    | Select address | A    | Data    | A    | Р    |

| - | 1bit  | 8bit              | 1bit | 8bit           | 1bit | 8bit    | 1bit | 1bit |

| •S                                | = start condition (start bit recognition)                                               |

|-----------------------------------|-----------------------------------------------------------------------------------------|

| <ul> <li>Slave address</li> </ul> | = IC recognition. Upper 7 bits are random. Bottom bit is "L" for the sake of overwrite. |

| • A                               | = acknowledge bit (recognition of acknowledgment)                                       |

| Select address                    | = selection between volume, bass, treble and matrix surround.                           |

| • Data                            | = volume and tone data                                                                  |

| • P                               | = stop condition (stop bit recognition)                                                 |

(3) BH3856S / BH3856FS slave address

| N | /ISB |    |    |    |    |    |    | LSE | 3 |

|---|------|----|----|----|----|----|----|-----|---|

|   | A6   | A5 | A4 | A3 | A2 | A1 | A0 | R/W |   |

|   | 1    | 0  | 0  | 0  | 0  | 0  | А  | 0   |   |

Slave address selection

1) A = 1 (10000010) [SASS pin HIGH] 2) A = 0 (1000000) [SASS pin LOW]

(4) Interface protocol

1) Basic protocol

| s | Slave addres | s   | А | Select addres | s   | А | Data    | А | Ρ |

|---|--------------|-----|---|---------------|-----|---|---------|---|---|

|   | MSB          | LSB |   | MSB           | LSB |   | MSB LSB |   |   |

2) Auto increment (Select address increases (+1) by the value of the data.)

| S | Slave address | А | Select addre | SS  | A |     | Data 1, data 2,data N |     | А | Ρ |

|---|---------------|---|--------------|-----|---|-----|-----------------------|-----|---|---|

|   | MSB LSB       |   | MSB          | LSB |   | MSB |                       | LSB |   |   |

(Example 1) The address data specified by select address is taken as data 1. (Example 2) The address data specified by select address +1 is taken as data 2. (Example 3) The address data specified by select address +N-1 is taken as data N.

3) Structure with which transmission is not possible (In this case, only select address 1 is set.)

| s | Slave address | A | Select ac | ldress 1 | А | Da  | ta  | А | Select addre | ss 2 | А | Da  | ta  | А | Ρ |   |

|---|---------------|---|-----------|----------|---|-----|-----|---|--------------|------|---|-----|-----|---|---|---|

|   | MSB LS        | В | MSB       | LSB      |   | MSB | LSB |   | MSB          | LSB  | l | MSB | LSB |   |   | - |

Note : Following transmission of data, data transmitted as select address 2 will not be recognized as select address 2, but as data.

| Function         |     | Select address |   |   |   |   | MSB Data |    |     |     |     |     | LSB |     |     |     |

|------------------|-----|----------------|---|---|---|---|----------|----|-----|-----|-----|-----|-----|-----|-----|-----|

| Function         | MSB |                |   |   |   |   | D7       | D6 | D5  | D4  | D3  | D2  | D1  | D0  |     |     |

| ① Volume ch1 (L) | 0   | 0              | 0 | 0 | 0 | 0 | 0        | 0  | VL7 | VL6 | VL5 | VL4 | VL3 | VL2 | VL1 | VL0 |

| 1 Volume ch2 (R) | 0   | 0              | 0 | 0 | 0 | 0 | 0        | 1  | VR7 | VR6 | VR5 | VR4 | VR3 | VR2 | VR1 | VR0 |

| 2 Bass           | 0   | 0              | 0 | 0 | 0 | 0 | 1        | 0  | 0   | 0   | BA5 | BA4 | BA3 | BA2 | BA1 | BA0 |

| ③Treble          | 0   | 0              | 0 | 0 | 0 | 0 | 1        | 1  | 0   | 0   | TR5 | TR4 | TR3 | TR2 | TR1 | TR0 |

| ④ Surround       | 0   | 0              | 0 | 0 | 0 | 1 | 0        | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | SR0 |

#### (5) Specification of select address and data

\*The auto increment function cycles the select address in the manner shown in Figure A.

$\begin{array}{ccc} (\mathsf{Fig. A}) & \textcircled{0} \rightarrow \textcircled{1} \rightarrow \textcircled{2} \\ & \uparrow & \downarrow \\ & \textcircled{4} \leftarrow \leftarrow \overleftarrow{3} \end{array}$

\*The cycle commences from the initially specified select address.

#### (6) Surround data

| Function            | MSB Data |    |    |    |    |    |    |    |  |  |

|---------------------|----------|----|----|----|----|----|----|----|--|--|

|                     | D7       | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |  |

| Matrix surround OFF | 0        | 0  | 0  | 0  | 0  | 0  | 0  | 0  |  |  |

| Matrix surround ON  | 0        | 0  | 0  | 0  | 0  | 0  | 0  | 1  |  |  |

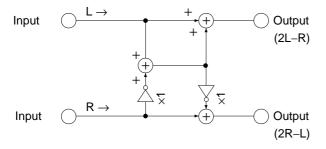

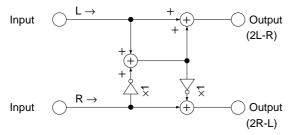

#### (7) Matrix surround

### Audio ICs

| ,           | <b>`</b>      | , |             |               |   |             |               |

|-------------|---------------|---|-------------|---------------|---|-------------|---------------|

| ATT<br>(dB) | DATA<br>(HEX) |   | ATT<br>(dB) | DATA<br>(HEX) | • | ATT<br>(dB) | DATA<br>(HEX) |

| 0           | FF            |   | -19         | 85            |   | -56         | 42            |

| -1          | E4            |   | -20         | 82            |   | -58         | 3F            |

| -2          | D8            |   | -22         | 7C            |   | -60         | 3C            |

| -3          | CF            |   | -24         | 78            |   | -62         | 39            |

| -4          | C8            |   | -26         | 74            |   | -64         | 36            |

| -5          | C2            |   | -28         | 70            |   | -66         | 34            |

| -6          | BD            |   | -30         | 6D            |   | -68         | 32            |

| -7          | B8            |   | -32         | 6A            |   | -70         | 2F            |

| -8          | B2            |   | -34         | 68            |   | -72         | 2D            |

| -9          | AD            |   | -36         | 65            |   | -74         | 2A            |

| -10         | A9            |   | -38         | 61            |   | -76         | 28            |

| -11         | A5            |   | -40         | 5C            |   | -78         | 26            |

| -12         | A0            |   | -42         | 59            |   | -80         | 24            |

| -13         | 9C            |   | -44         | 55            |   | -82         | 22            |

| -14         | 98            |   | -46         | 52            |   | -84         | 20            |

| -15         | 94            |   | -48         | 4E            |   | -86         | 1E            |

| -16         | 90            |   | -50         | 4B            |   | -90         | 1A            |

| -17         | 8C            |   | -52         | 48            |   | -100        | 13            |

| -18         | 89            |   | -54         | 45            |   | -112        | 00            |

(8) Volume attenuation (reference values)

Note : All figures in this table are reference values. When using this IC, check this table carefully and perform the appropriate setting.

#### (9) Bass / Treble gain settings (reference values)

| ATT<br>(dB) | DATA<br>(HEX) | - | ATT<br>(dB) | DATA<br>(HEX) |

|-------------|---------------|---|-------------|---------------|

| 15          | ЗF            | • | 0           | 1F            |

| 14          | 38            | - | -1          | 1C            |

| 13          | 35            |   | -2          | 1B            |

| 12          | 33            | - | -3          | 19            |

| 11          | 31            | _ | -4          | 18            |

| 10          | 2F            | _ | -5          | 17            |

| 9           | 2E            | _ | -6          | 16            |

| 8           | 2D            | _ | -7          | 15            |

| 7           | 2C            | - | -8          | 13            |

| 6           | 2B            | _ | -9          | 12            |

| 5           | 2A            | _ | -10         | 11            |

| 4           | 29            | _ | -11         | 0F            |

| 3           | 27            | _ | -12         | 0D            |

| 2           | 26            |   | -13         | 0B            |

| 1           | 25            | _ | -14         | 08            |

| 0           | 1F            | - | -15         | 05            |

Notes : (1) The gain values in the treble and bass data setting tables above are based on the assumption that the filter constants have been set so that maximum and minimum gain are equal to the peak and bottom values listed in the frequency characteristics drawings.

(2) All figures in this table are reference values. When using this IC, check this table carefully and perform the appropriate setting.

#### Application example

Fig.2

Note : Diagram depicts the BH3856S.

#### Operation notes

#### (1) Operating power supply voltage range

As long as the operating power supply voltage and ambient temperature are kept within the specified range, the basic circuits are guaranteed to function, but be sure to check the constants as well as the element settings, voltage settings, and temperature settings.

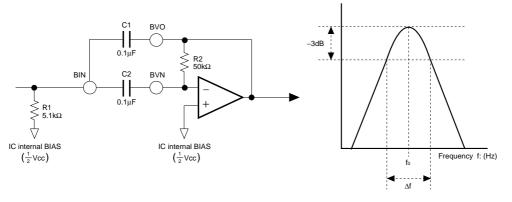

#### (2) Bass filter

# \*B.P.F. composed of multiple feedback active fo can be varied according to the value of C.BIN (theoretical equation)

$$f_{0} = \frac{1}{2\pi} \times \left(\frac{1}{R_{1}R_{2}C_{1}C_{2}}\right)^{\frac{1}{2}} \qquad Q \coloneqq \left(\left(\frac{1}{R_{2}C_{1}C_{2}}\right)^{\frac{1}{2}} \times (C_{1} + C_{2})\right)^{-1}$$

$$G = \frac{R_{2}}{5k\Omega} \times \left(1 + \frac{C_{1}}{C_{2}}\right)^{-1} \qquad Note : Filter gain is calculated using the equation on the left. Total output gain is the sum of the gain for each of the internal circuits.$$

(When  $R_1 = 5.1k\Omega$ ,  $R_2 = 50k\Omega$ ,  $C_1 = C_2 = C$ )

$$f_0 = \frac{1.0 \times 10^{-5}}{C}$$

Q = 1.57 G = 5.0

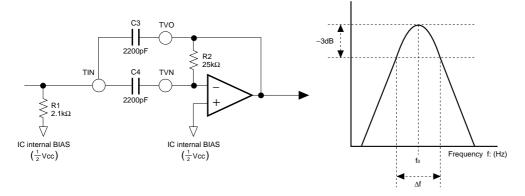

#### (3) About the treble filter

\*The band-pass filter is constructed using a multiple-feedback active filter. fo can be varied by changing the value of the capacitors.

(Theoretical formulas)

$$f_0 = \frac{1}{2\pi} \times \left(\frac{1}{R_1 R_2 C_3 C_4}\right)^{\frac{1}{2}}$$

$$G = \frac{R_2}{5k\Omega} \times \left(1 + \frac{C_3}{C_4}\right)^{-1}$$

Note

$\frac{R_1}{R_2C_3C_4} \int_{-1}^{\frac{1}{2}} \times (C_3 + C_4) \int_{-1}^{-1}$ The filter gain is given by the formula on the left, but the total output gain is determined by the this in combination with the internal circuit.

(When  $R_1 = 2.1k\Omega$ ,  $R_2 = 25k\Omega$ ,  $C_3 = C_4 = C$ )

$$f_0 = \frac{2.2 \times 10^{-5}}{C}$$

Q = 1.73 G = 2.5

#### (4) I<sup>2</sup>C BUS control

High-frequency digital signals are input on the SCL and SDA terminals, so ensure that the wiring and PCB pattern is designed in such a way as to ensure that these signals do not interfere with the analog signal system. If you are not using I<sup>2</sup>C BUS control (i.e. you are using DC control), connect the SCL, SDA and SASS terminals to GND (do not leave them disconnected).

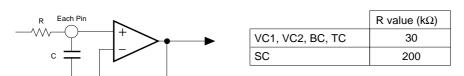

#### (5) Step switching noise

The VC1, VC2, TC, BC and SC terminals have components connected to them the application example. The values of these components may need to be changed depending on the signal level setting and PCB pattern.

Investigate carefully before deciding on the values of the various circuit constants.

The equivalent circuit for these terminals is given below (an integrator circuit is set at the first stage to slow the variation).

#### (6) Volume and tone level settings

This specification sheet gives reference values for the amount of attenuation and gain with respect to the serial control data. The internal D / A convertor is an R-2R circuit, and data exists for the places where continuous variation does not occur between data. Use this when fine setting is required. The setting limits are up to 8 bits for volume (256 steps) and 6 bits (64 steps) for tone.

#### (7) Digital / analog separation

The digital and analog power supplies and grounds for this IC (BH3856) are completely separate. The digital circuits are supplied from a stable reference source that is on the chip ( $V_{ref}(3.8V)$ ). For this reason, there is no need to worry about timing shifts, on interference due to digital noise.

(8) Matrix surround

\*The matrix surround circuit construction is as shown in the diagram above. The gain is obtained from the formulas in the diagram.

| Phase Gain          | 0dB |

|---------------------|-----|

| Negative Phase Gain | 6dB |

(However, reverse-phase gain is for input to one channel only)

(9) DC control

An internal impedance of  $30k\Omega$  is seen from the VC1, VC2, TC and BC terminals, are  $200k\Omega$  is seen from the SC (pin 11) terminal, so with regard to DC control, we recommend direct control with the voltage source. When using variable volume, take the impedance into consideration when making the setting.

Note : The DC control voltage range is 0V to Vref.

Do not apply voltages above Vref to the terminals.

(10) GND

• As shown in the application circuit example, connect the external component GND to the analog GND.

However, the GND for the capacitor connected to the Vrefterminal should be connected to the digital GND.

• If a capacitor with goof high-frequency characteristics is connected in parallel with the capacitor connected to Vref, the

performances of the circuit with respect to static noise will improve (we recommend a ceramic capacitor of between  $0.001 \mu$ F and  $0.1 \mu$ F)

• When using long digital and analog ground lines, take care to ensure that there is no potential difference between the two ground lines.

### Audio ICs

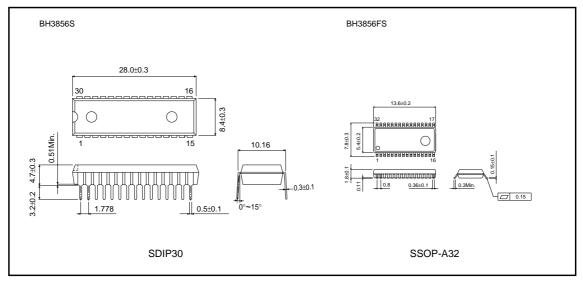

#### •External dimensions (Units : mm)

#### Notes

- No technical content pages of this document may be reproduced in any form or transmitted by any means without prior permission of ROHM CO.,LTD.

- The contents described herein are subject to change without notice. The specifications for the product described in this document are for reference only. Upon actual use, therefore, please request that specifications to be separately delivered.

- Application circuit diagrams and circuit constants contained herein are shown as examples of standard use and operation. Please pay careful attention to the peripheral conditions when designing circuits and deciding upon circuit constants in the set.

- Any data, including, but not limited to application circuit diagrams information, described herein are intended only as illustrations of such devices and not as the specifications for such devices. ROHM CO.,LTD. disclaims any warranty that any use of such devices shall be free from infringement of any third party's intellectual property rights or other proprietary rights, and further, assumes no liability of whatsoever nature in the event of any such infringement, or arising from or connected with or related to the use of such devices.

- Upon the sale of any such devices, other than for buyer's right to use such devices itself, resell or otherwise dispose of the same, no express or implied right or license to practice or commercially exploit any intellectual property rights or other proprietary rights owned or controlled by

- ROHM CO., LTD. is granted to any such buyer.

- Products listed in this document use silicon as a basic material.

Products listed in this document are no antiradiation design.

The products listed in this document are designed to be used with ordinary electronic equipment or devices (such as audio visual equipment, office-automation equipment, communications devices, electrical appliances and electronic toys).

Should you intend to use these products with equipment or devices which require an extremely high level of reliability and the malfunction of with would directly endanger human life (such as medical instruments, transportation equipment, aerospace machinery, nuclear-reactor controllers, fuel controllers and other safety devices), please be sure to consult with our sales representative in advance.

About Export Control Order in Japan

Products described herein are the objects of controlled goods in Annex 1 (Item 16) of Export Trade Control Order in Japan.

In case of export from Japan, please confirm if it applies to "objective" criteria or an "informed" (by MITI clause) on the basis of "catch all controls for Non-Proliferation of Weapons of Mass Destruction.