TOSHIBA BiCMOS Integrated Circuit Silicon Monolithic

# TB9044AFNG

#### DCDC Convertor & Multi Output Regulator

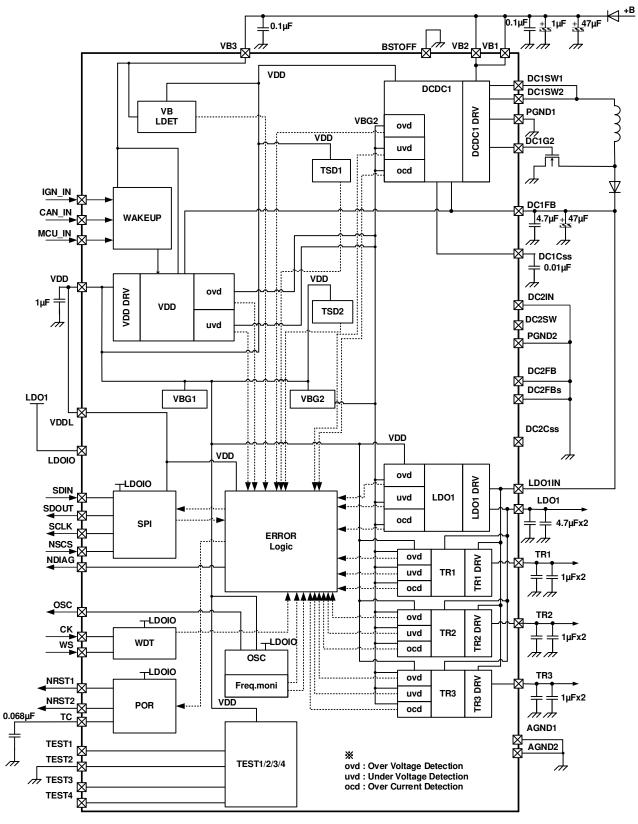

TB9044AFNG is a multi output power supply IC for automotive system power supply incorporating a DCDC convertor, a series power supply and 3 tracking regulators. Both high efficiency and low noise output are concurrently achieved by a DCDC power supply and a series power supply, respectively.

It incorporates various monitoring functions for abnormalities in power supply and MCU, and enables transmitting monitoring statuses to an external system via SPI communication.

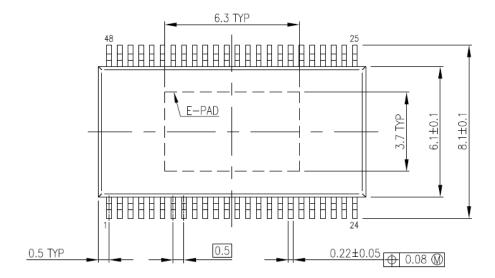

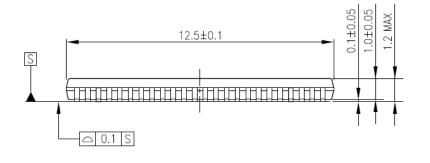

HTSSOP48-P-300-0.50 Weight: 204.6mg (typ.)

#### 1 Features

- DCDC convertor circuits

- DCDC1: Synchronous rectifying buck-boost convertor with built-in 6V output

- 4built-in output series power supply circuits

- LDO1: Output voltage 5.0V

- > TR1 to 3 output voltage LDO1 and tuning voltage (3 ch)

- Output voltage monitoring & reset output

- High voltage & low voltage & overcurrent monitoring

- Power-on reset (2-channel output pins)

- Watchdog timer

- Built-in SPI communication

- To output notification signals for various abnormalities in a power supply function

- 2-channel built-in reference voltage circuits (Main function and monitoring function)

- Built-in oscillator circuit

- Built-in frequency monitoring function for oscillator circuit

- Built-in Analog BIST

- Built-in Logic BIST

- Operating temperature range: -40 to 125 °C

- Package: HTSSOP48-P-300-0.50

- AEC-Q100 Qualified

- TM-SIL<sup>TM</sup>

- Developed according to ISO 26262 ASIL-D

- Safety Manual and Safety Analysis Report

- Functional redundancy and built-in ABIST and LBIST

- > SPI interface with CRC check

The product(s) is/are compatible with RoHS regulations (EU directive 2011 / 65 / EU) as indicated, if any, on the packaging label ("[[G]]/RoHS COMPATIBLE", "[[G]]/RoHS [[Chemical symbol(s) of controlled substance(s)]]", "RoHS COMPATIBLE" or "RoHS COMPATIBLE, [[Chemical symbol(s) of controlled substance(s)]]>MCV").

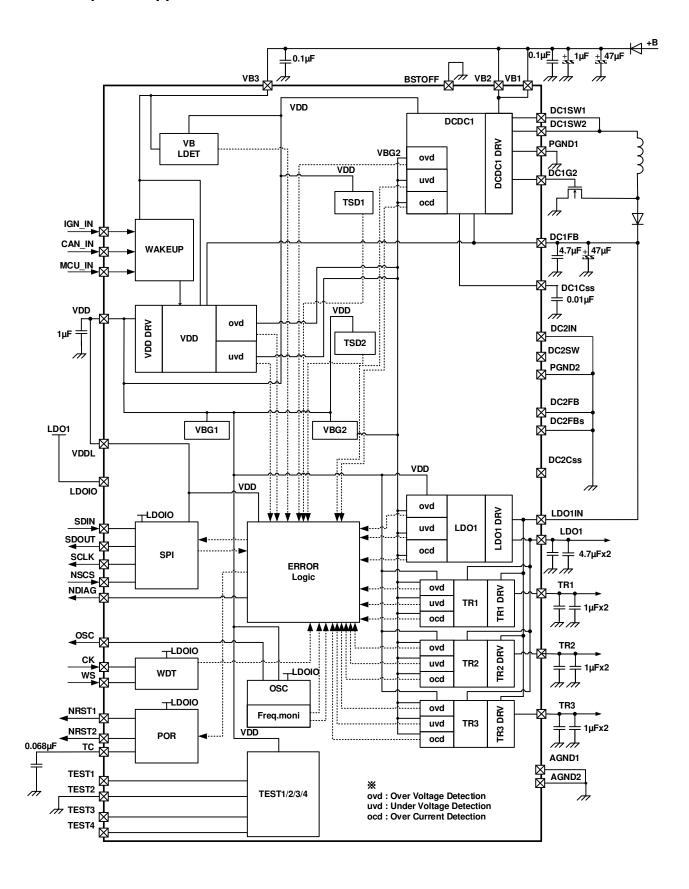

#### 2 Block diagram

Note: The block diagram may show some of the functional blocks, circuits, or constants in abbreviated or simplified format for clarity in describing the relevant features.

# 3 Pin description

| No. | Pin<br>name | I/O  | Function                                                         | Configuration | Pull-u   | p/down       | Remarks                                                                   |

|-----|-------------|------|------------------------------------------------------------------|---------------|----------|--------------|---------------------------------------------------------------------------|

| 1   | LDOIO       | I    | Pull-up power supply of MCU I/F pin and IO buffer connection pin | _             | _        | _            | Connect it to LDO1.                                                       |

| 2   | TEST1       | I    | Test pin                                                         | BIP           | _        | <del>-</del> | Leave this pin open.                                                      |

| 3   | VDDL        | l    | Logic power input pin                                            | <u> </u>      | _        | _            | Connect it to VDD.                                                        |

| 4   | VDD         | 0    | VDD power output pin for internal circuit                        | DMOS          |          | _            | <del></del>                                                               |

| 5   | BSTOFF      | ı    | Switching pin between buck-boost mode/buck mode                  | CMOS          | PD       | 50kΩ         | Connection to AGND in buck- boost mode, connection to VDD in buck mode.   |

| 6   | DC1Css      | I/O  | DCDC1 soft start time setting pin                                | CMOS          | <u> </u> | <u> </u>     | <del></del>                                                               |

| 7   | MCU_IN      | I    | Wake-up signal input pin from MCU                                | CMOS          | PD       | 100kΩ        | <del></del>                                                               |

| 8   | SDIN        | <br> | SPI serial data input pin                                        | CMOS          | PD       | 50kΩ         | <del></del>                                                               |

| 9   | SDOUT       | 0    | SPI serial data output pin                                       | CMOS          |          |              | <u> </u>                                                                  |

| 10  | SCLK        | I    | SPI clock input pin                                              | CMOS          | PD       | 50kΩ         | <del></del>                                                               |

| 11  | NSCS        | I    | SPI chip select pin                                              | CMOS          | PU       | 50kΩ         | It is pulled up to LDOIO inside IC.                                       |

| 12  | NC          | -    | Non connection pin — — —                                         |               | <u> </u> | _            | Leave this pin open.                                                      |

| 13  | TR1         | 0    | Tracker output 1                                                 | DMOS          |          |              | <del>-</del>                                                              |

| 14  | TR2         | 0    | Tracker output 2                                                 | DMOS          |          |              | <u> </u>                                                                  |

| 15  | TR3         | 0    | Tracker output 3                                                 | DMOS          |          | <u> </u>     | <u> </u>                                                                  |

| 16  | AGND1       | -    | GND                                                              |               |          | <u> </u>     | <u> </u>                                                                  |

| 17  | NRST1       | 0    | Reset signal output pin 1 (for MCU)                              | O.D.          | PU       | 4.7kΩ        | It is pulled up to LDOIO inside IC.                                       |

| 18  | OSC         | 0    | Clock output                                                     | CMOS          |          |              | <del>-</del>                                                              |

| 19  | NDIAG       | 0    | Output pin for flag signal notifying error information           | O.D.          | PU       | 4.7kΩ        | It is pulled up to LDOIO inside IC.                                       |

| 20  | TEST2       | ı    | Test pin                                                         | CMOS          | PD       | 50kΩ         | Connect it to GND.                                                        |

| 21  | CK          | I    | Watchdog clock input pin                                         | CMOS          | PD       | 50kΩ         | <u> </u>                                                                  |

| 22  | TC          | I/O  | Time setting capacitor pin for reset timer                       | CMOS          |          | _            | <del>_</del>                                                              |

| 23  | TEST3       | 0    | Test pin                                                         | CMOS          | _        | _            | Leave this pin open.                                                      |

| 24  | WS          | ı    | Switching pin between ON/OFF of watchdog function                | CMOS          | PD       | 50kΩ         | Function turned<br>on at L input and<br>function turned off<br>at H input |

| 25  | NRST2       | 0    | Reset signal output pin 2 (for driver)                           | O.D.          | PU       | 4.7kΩ        | It is pulled up to LDOIO inside IC.                                       |

| 26  | TEST4       | 0    | Test pin                                                         | CMOS          | _        | _            | Leave this pin open.                                                      |

| 27  | DC2Css      | _    | _                                                                | _             | _        | _            | Leave this pin open.                                                      |

| 28  | DC2FBs      | _    |                                                                  | _             | _        |              | Connect it to GND.                                                        |

| 29  | DC2FB       | _    | _                                                                | _             | _        | _            | Connect it to GND.                                                        |

| 30  | PGND2       | _    |                                                                  |               | _        | _            | Connect it to GND.                                                        |

| 31  | DC2SW       | _    |                                                                  |               |          | <u> </u>     | Leave this pin open.                                                      |

| 32  | NC          |      | Non connection pin                                               |               |          | _            | Leave this pin open.                                                      |

| No. | Pin<br>name | I/O | Function                                     | Configuration | Pull-u | ıp/down | Remarks                                                   |

|-----|-------------|-----|----------------------------------------------|---------------|--------|---------|-----------------------------------------------------------|

| 33  | DC2IN       | I   | DCDC2 input pin                              | _             | _      | _       | Connect it to GND.                                        |

| 34  | AGND2       | _   | GND                                          | <del>_</del>  |        | _       | <del>_</del>                                              |

| 35  | LDO1        | 0   | Series power supply LDO1 output pin          | CMOS          |        | _       | <del>_</del>                                              |

| 36  | NC          | _   | Non connection pin                           | _             | _      | _       | Leave this pin open.                                      |

| 37  | LDO1IN      | I   | Series power supply LDO1 input pin           | <del>-</del>  |        | _       | <del>-</del>                                              |

| 38  | DC1FB       | I   | DCDC1 output voltage feed-back detection pin | DMOS          |        | _       | <del>_</del>                                              |

| 39  | DC1G2       | 0   | DCDC1 GATE driver pin                        | DMOS          |        | _       | Leave this pin<br>open if boost<br>mode is not in<br>use. |

| 40  | PGND1       | _   | DCDC1 GND pin                                | <u>—</u>      | _      | _       | Connect it to GND.                                        |

| 41  | DC1SW1      | 0   | DCDC1 switching output pin 1                 | DMOS          | _      | _       | This pin is to be short-circuited with DC1SW2.            |

| 42  | DC1SW2      | 0   | DCDC1 switching output pin 2                 | DMOS          | _      | _       | This pin is to be<br>short-circuited<br>with DC1SW1.      |

| 43  | VB1         | I   | Power supply voltage input pin 1             | _             |        | _       | _                                                         |

| 44  | VB2         | I   | Power supply voltage input pin 2             | <del>_</del>  |        |         | <del>-</del>                                              |

| 45  | VB3         | I   | Power supply voltage input pin 3             | <u> </u>      |        |         | <u> </u>                                                  |

| 46  | NC          |     | Non connection pin                           | _             | _      | _       | Leave this pin open.                                      |

| 47  | CAN_IN      | I   | Wake-up signal from CAN                      | DMOS          | PD     | 250kΩ   | <del></del>                                               |

| 48  | IGN_IN      | I   | Input pin for wake-up signal from IGN        | DMOS          | PD     | 250kΩ   | <del>_</del>                                              |

# 4 Pin layout

|          |            | 1      |    |

|----------|------------|--------|----|

| 1 LDOIO  |            | IGN_IN | 48 |

| 2 TEST1  |            | CAN_IN | 47 |

| 3 VDDL   |            | NC     | 46 |

| 4 VDD    |            | VB3    | 45 |

| 5 BSTOFF |            | VB2    | 44 |

| 6 DC1Css | <u>_</u>   | VB1    | 43 |

| 7 MCU_IN |            | DC1SW2 | 42 |

| 8 SDIN   |            | DC1SW1 | 41 |

| 9 SDOUT  | <b>W</b> 9 | PGND1  | 40 |

| 10 SCLK  |            | DC1G2  | 39 |

| 11 NSCS  |            | DC1FB  | 38 |

| 12 NC    | +>         | LDO1IN | 37 |

| 13 TR1   | +>         | NC     | 36 |

| 14 TR2   |            | LDO1   | 35 |

| 15 TR3   |            | AGND2  | 34 |

| 16 AGND1 | <b>—</b>   | DC2IN  | 33 |

| 17 NRST1 |            | NC     | 32 |

| 18 OSC   | $\Box$     | DC2SW  | 31 |

| 19 NDIAG |            | PGND2  | 30 |

| 20 TEST2 |            | DC2FB  | 29 |

| 21 CK    |            | DC2FBs | 28 |

| 22 TC    |            | DC2Css | 27 |

| 23 TEST3 |            | TEST4  | 26 |

| 24 WS    |            | NRST2  | 25 |

#### 5 Functional description

Some of the functional blocks of the block diagram of this chapter, the circuit or constant labels, might have been omitted or simplified for clarity.

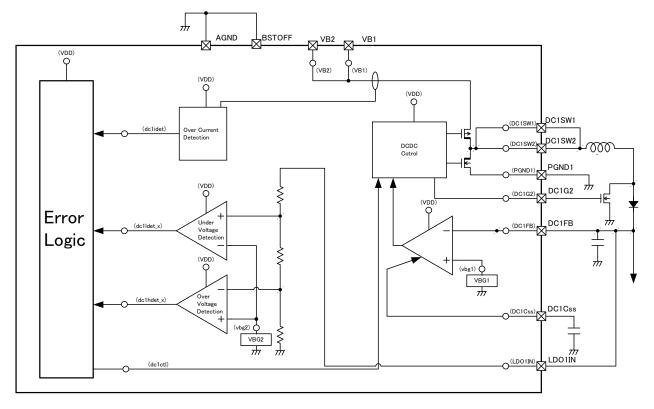

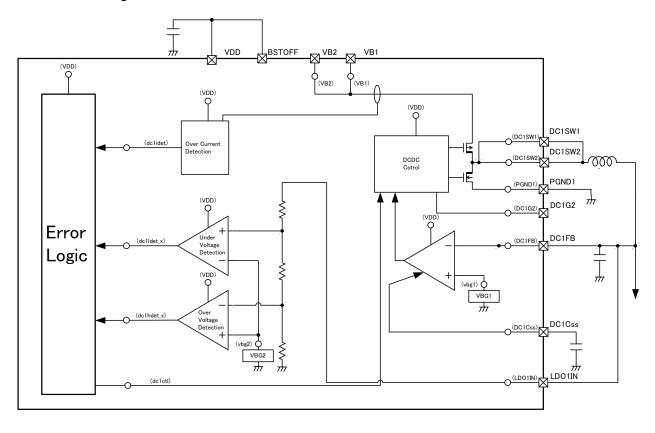

# 5-1.DCDC Convertor DCDC1

It is buck-boost DCDC convertor with input voltage VB1/2 and 6V output voltage. For buck mode, it is a synchronous rectifying type incorporating output driver MOS and rectification MOS. For boost mode, it is a diode rectifying type having external driver MOS and rectifier diode.

- ♦ Switching frequency is 400 kHz (typ.).

- It incorporates functions of overcurrent detection and high/low voltage detection (not used in low voltage detection).

- ♦ It incorporates phase compensating capacitor.

- ♦ The capacitor connected to DC1Css pin can control voltage rising time.

- ♦ Buck mode enables use of DCDC convertor for buck mode (with BSTOFF = VDD set). Switching between buck-boost mode and buck mode during IC operation must not be performed.

## At the time of using DCDC convertor for buck-boost mode

#### At the time of using DCDC convertor for buck mode

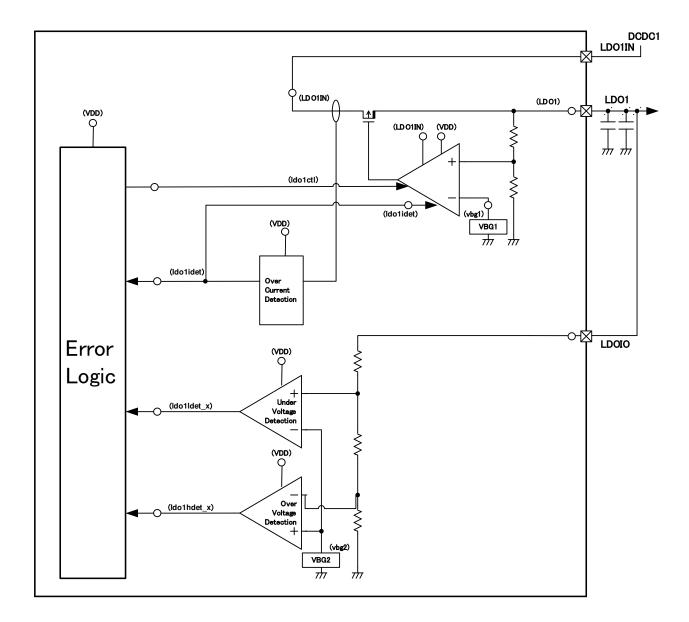

# 5-2. Series Power Supply

#### LDO<sub>1</sub>

- It is a series power supply incorporating output driver MOS.

- ➢ 6V output from DCDC1 convertor must be used as input voltage.

- > Output voltage is 5V±0.1V, and output current 400mA (max).

- > It incorporates functions of overcurrent detection and high/low voltage detection. (Set current consumption considering allowable dissipation and heat generation.)

- > It incorporates phase compensating capacitor.

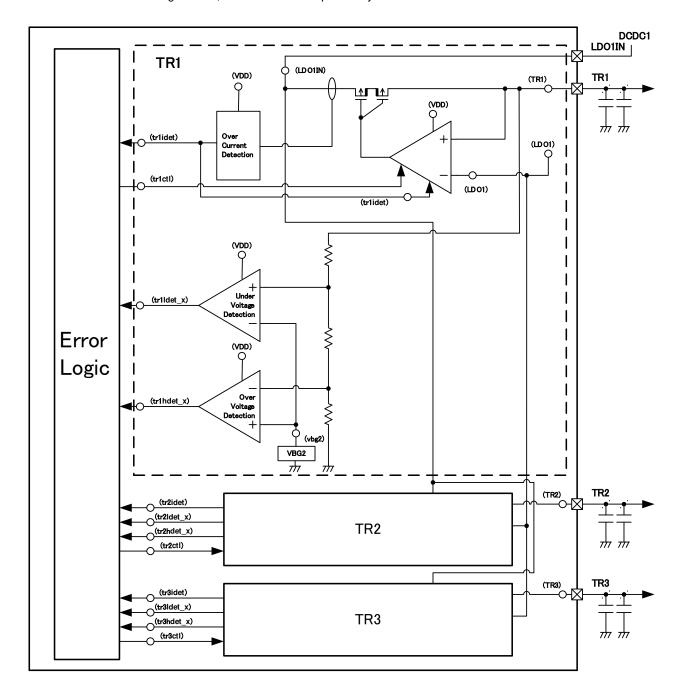

# TR1, TR2, TR3

- It is a tracker power supply incorporating output driver MOS.

- Output voltage is linked with LDO1.

- > Output current of TR1, TR2 or TR3 is 100mA (max).

- It incorporates functions of overcurrent detection (100mA (min) for TR1, TR2 and TR3 respectively) and high/low voltage detection (TR1, TR2, and TR3). (Set current consumption considering allowable dissipation and heat generation.)

- It enables turning off TR1, TR2 and TR3 independently via SPI communication.

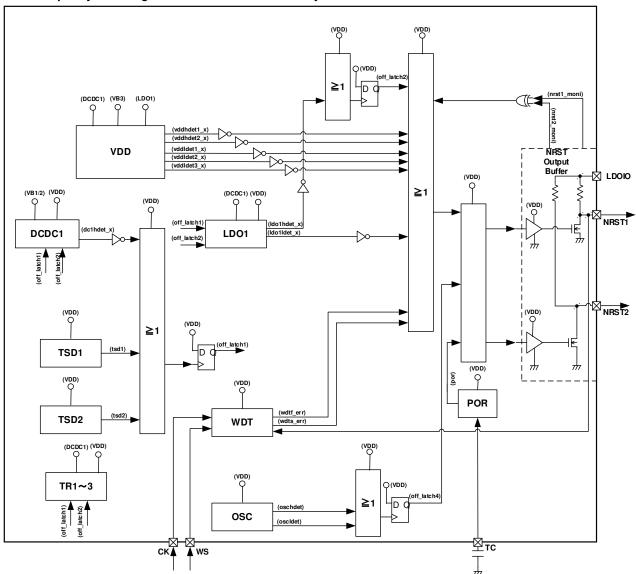

# 5-3. Abnormality Detection Function

It incorporates abnormality detection function as follows.

#### Reset output system diagram at the time of abnormality detection

#### Power supply operational matrix (Initial value as register setting)

- \* Relaunch of power supply input VB1,VB2 and VB3 or relaunch by IGN\_IN/CAN\_IN/MCU\_IN control is required to release off-latch (mode).

- \* "During start-up" is defined as the period until low voltage detection of each power supply is released, and "after start-up (in operation)" as the subsequent period.

- \* During off-latch (mode) or turning off, output voltage is discharged with a discharge resistor and turned off.

- \* If restart is requested during discharging, start-up operation is executed even with discharging.

#### ■ During operation (Initial value as register setting)

| Abnormality detection     | Power supply | VDD                 | DCDC1                            | LDO1                                                      | TR1 to 3                                       | NRST1/2 | NDIAG      |

|---------------------------|--------------|---------------------|----------------------------------|-----------------------------------------------------------|------------------------------------------------|---------|------------|

|                           | DCDC1        | Operation continued | Overcurrent detection off- latch | Operation continued* 1                                    | Operation continued * 1                        | L*4     | L<br>Latch |

| Overcurrent detection     | LDO1         | Operation continued | Operation continued              | Overcurrent limitation Operation continued (voltage drop) | Operation continued* 2                         | L* 4    | L<br>Latch |

|                           | TR1 to 3     | Operation continued | Operation continued              | Operation continued                                       | Overcurrent limitation Operation continued * 3 |         | L<br>Latch |

|                           | VDD          | High voltage<br>OFF | OFF                              | OFF                                                       | OFF                                            | L       | L<br>※5    |

| High voltage<br>detection | DCDC1        | Operation continued | High voltage<br>off-latch        | Off-latch                                                 | Off-latch                                      | L*4     | L<br>Latch |

| detection                 | LDO1         | Operation continued | Off-latch                        | High voltage off-latch                                    | Off-latch                                      | L       | L<br>Latch |

|                           | TR1 to 3     | Operation continued | Operation continued              | Operation continued                                       | High voltage<br>Operation<br>continued         | _       | L<br>Latch |

|                           | VB3          | Operation continued | OFF                              | OFF                                                       | OFF                                            | L*4     | L<br>Latch |

|                           | VDD          | Low voltage         | OFF                              | OFF                                                       | OFF                                            | L       | L          |

| Low voltage detection     | DCDC1        | Operation continued | Low voltage                      | Operation continued                                       | Operation continued                            | _       | _          |

|                           | LDO1         | Operation continued | Operation continued              | Low voltage                                               | Operation continued * 2                        | L       | L<br>Latch |

|                           | TR1 to 3     | Operation continued | Operation continued              | Operation continued                                       | Low voltage                                    | _       | L<br>Latch |

| Overheat detection        | _            | Operation continued | Off-latch                        | Off-latch                                                 | Off-latch                                      | L* 4    | L<br>Latch |

| Abnormal frequency        | _            | Operation continued | Off-latch                        | Off-latch                                                 | Off-latch                                      | L       | L<br>Latch |

<sup>\* 1:</sup> The operation continues, but the output is suspended because of DCDC1 off-latch (mode).

© 2015-2019 2019-12-10

<sup>\* 2:</sup> The operation continues, but voltage drops following LDO1 behavior.

<sup>\* 3:</sup> The operation continues, but output voltage drops in conjunction with current value.

<sup>\* 4:</sup> It becomes L if LDO1 detects low voltage.

<sup>\* 5:</sup> During operation If VDD high voltage is detected, low voltage detection is also accompanied by OFF operation, so it may look like a L latch.

■ During start-up (Initial value as register setting)

| Abnormality detection  | Power supply | VDD                 | DCDC1                                 | LDO1                                             | TR1 to 3                                         | NRST1/2 | NDIAG      |

|------------------------|--------------|---------------------|---------------------------------------|--------------------------------------------------|--------------------------------------------------|---------|------------|

|                        | DCDC1        | Normal start-<br>up | overcurrent<br>detection<br>off-latch | Start-up<br>failure                              | Start-up<br>failure                              | L* 1    | L<br>Latch |

|                        | LDO1         | Normal start-<br>up | Normal start-<br>up                   | Overcurrent<br>limitation<br>Normal start-<br>up | Normal start-<br>up                              | _       | L<br>Latch |

| Overcurrent detection  | LDO1         | Normal start-<br>up | Normal start-<br>up                   | Overcurrent<br>limitation<br>Start-up<br>failure | Start-up<br>failure                              | L* 1    | L<br>Latch |

|                        | TR1 to 3     | Normal start-<br>up | Normal start-<br>up                   | Normal start-<br>up                              | Overcurrent<br>limitation<br>Normal start-<br>up | 1       | L<br>Latch |

|                        | 111103       | Normal start-<br>up | Normal start-<br>up                   | Normal start-<br>up                              | Overcurrent<br>limitation<br>Start-up<br>failure | l       | L<br>Latch |

|                        | VDD          | High<br>voltage off | Start-up<br>failure                   | Start-up<br>failure                              | Start-up<br>failure                              | L       | L          |

|                        | DCDC1        | Normal start-<br>up | High<br>voltage off-<br>latch         | Start-up<br>failure                              | Start-up<br>failure                              | L* 1    | L<br>Latch |

| High voltage detection | LDO1         | Normal start-<br>up | Off-latch                             | High<br>voltage off-<br>latch                    | Off-latch                                        | L       | L<br>Latch |

|                        | TR1 to 3     | Normal start-<br>up | Normal start-<br>up                   | Normal start-<br>up                              | High<br>voltage<br>Normal start-<br>up           | ı       | L<br>Latch |

|                        | VB3          | Normal start-<br>up | Start-up<br>failure                   | Start-up<br>failure                              | Start-up<br>failure                              | L* 1    | L<br>Latch |

| 1                      | VDD          | Low voltage         | Start-up<br>failure                   | Start-up<br>failure                              | Start-up<br>failure                              | L       | L<br>Latch |

| Low voltage detection  | DCDC1        | Normal start-<br>up | Low voltage                           | Start-up<br>failure                              | Start-up<br>failure                              | _       | _          |

|                        | LDO1         | Normal start-<br>up | Normal start-<br>up                   | Low voltage                                      | Low voltage                                      | L       | L<br>Latch |

|                        | TR1 to 3     | Normal start-<br>up | Normal start-<br>up                   | Normal start-<br>up                              | Low voltage                                      | _       | L<br>Latch |

| Overheat detection     | _            | Normal start-<br>up | Start-up<br>failure                   | Start-up<br>failure                              | Start-up<br>failure                              | L * 1   | L<br>Latch |

| Abnormal frequency     | _            | Normal start-<br>up | Start-up<br>failure                   | Start-up<br>failure                              | Start-up<br>failure                              | L       | L<br>Latch |

<sup>\* 1:</sup> It becomes L if LDO1 detects low voltage.

# Voltage abnormality detection function of power supply output

It incorporates high voltage detection function for the output of DCDC1, LDO1, TR1 to 3 and VDD, and low voltage detection function for the output of VB3, LDO1, TR1 to 3 and VDD. Each detection result is input to error logic, which outputs NDIAG if any high voltage or low voltage is detected. NDIAG becomes H in normal status, while NDIAG becomes L latch at high voltage or low voltage detection.

If LDO1 or VDD detects low voltage, reset is output from NRST1 and NRST2 (NRST1 = NRST2 = L).

If VDD high voltage is detected, VDD, DCDC1, LDO1 and TR1 to 3 are turned off with reset outputting from NRST1 and NRST2 (NRST1 = NRST2 = L).

If DCDC1 detects high voltage, DCDC1, LDO1 and TR1 to 3 are latched off.

If LDO1 detects high voltage, DCDC1, LDO1 and TR1 to 3 are latched off with reset outputting from NRST1 and NRST2 (NRST1 = NRST2 = L).

List of operation at high voltage detection

| Monitoring function | SPI setting    | Setting<br>bit | Operation                                                                   | Initial<br>value | ABIST | Writing to register | NRST<br>1/2 | NDIAG      |

|---------------------|----------------|----------------|-----------------------------------------------------------------------------|------------------|-------|---------------------|-------------|------------|

|                     | Applicable     | 0              | NDIAG output only                                                           | _                | 0     | 0                   | _           | L<br>Latch |

| DCDC1               |                | 1              | NDIAG output<br>DCDC1, LDO1 and<br>TR1 to 3 off-latch                       | 0                | 0     | 0                   | _           | L<br>Latch |

|                     |                | 0              | NDIAG output only                                                           |                  | 0     | 0                   | _           | L<br>Latch |

| LDO1                | Applicable     | 1              | NDIAG and NRST1/2<br>output, DCDC1, LDO1<br>and TR1 to 3 off-latch          | 0                | 0     | 0                   | L           | L<br>Latch |

| TR1                 | Applicable     | 0              | NDIAG output<br>TR1 off-latch                                               |                  | 0     | 0                   | _           | L<br>Latch |

| INI                 |                | 1              | NDIAG output only                                                           | 0                | 0     | 0                   | _           | L<br>Latch |

| TR2                 | Applicable     | 0              | NDIAG output<br>TR2 off-latch                                               |                  | 0     | 0                   | _           | L<br>Latch |

| Inz                 | Applicable     | 1              | NDIAG output only                                                           | 0                | 0     | 0                   | _           | L<br>Latch |

| TR3                 | Applicable     | 0              | NDIAG output<br>TR3 off-latch                                               |                  | 0     | 0                   | _           | L<br>Latch |

| ins                 | Арріїсавіе     | 1              | NDIAG output only                                                           | 0                | 0     | 0                   | _           | L<br>Latch |

| VDD                 | Not applicable |                | NDIAG and NRST1/2<br>output, VDD, DCDC1,<br>LDO1 and TR1 to 3<br>turned off |                  |       |                     | L           | L          |

#### List of operation at low voltage detection

| Monitoring function | SPI setting    | Setting<br>bit | Operation                                                           | Initial<br>value | ABIST | Writing to<br>register | NRST<br>1/2 | NDIAG      |

|---------------------|----------------|----------------|---------------------------------------------------------------------|------------------|-------|------------------------|-------------|------------|

| VB3                 | Not applicable | _              | NDIAG output<br>DCDC1,LDO1 and TR1<br>to 3 turned off               | _                | 0     | 0                      | _           | L<br>Latch |

| LDO1                | Not applicable | _              | NDIAG and NRST1/2 output turned off                                 |                  | 0     | 0                      | L           | L<br>Latch |

| TR1                 | Not applicable | _              | DIAG output only                                                    |                  | 0     | 0                      |             | L<br>Latch |

| TR2                 | Not applicable | _              | DIAG output only                                                    |                  | 0     | 0                      | _           | L<br>Latch |

| TR3                 | Not applicable | _              | DIAG output only                                                    | _                | 0     | 0                      | _           | L<br>Latch |

| VDD                 | Not applicable | _              | NDIAG and NRST1/2<br>output, DCDC1, LDO1<br>and TR1 to 3 turned off |                  |       |                        | L           | L          |

#### Overcurrent abnormality detection operation

Overcurrent detection function is incorporated for the output of DCDC1, LDO1, TR1, TR2 and TR3. Each detection result is input to error logic, which outputs NDIAG if any overcurrent is detected. NDIAG becomes "H" in normal status, and NDIAG becomes "L latch" at overcurrent detection.

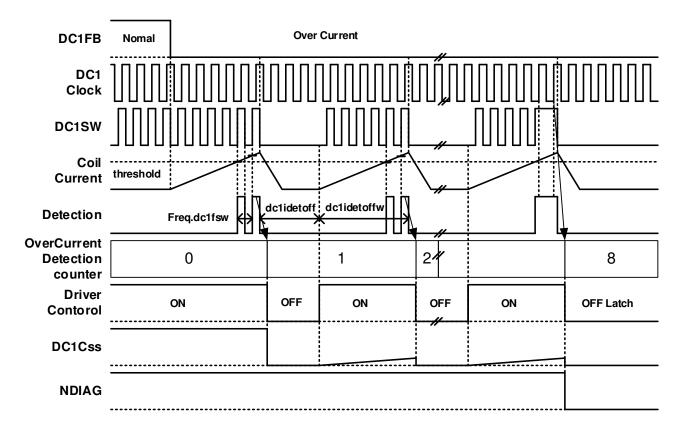

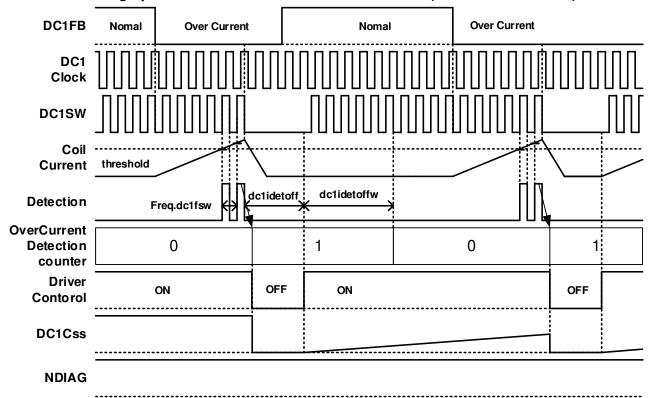

## **DCDC1** overcurrent operation

#### DCDC1 detection & control method

When overcurrent is detected for two pulse times at sampling frequency dc1fsw, output driver control is turned OFF. Even if this mode is repeated Ndc1idetoff (=8) times, if it is in the overcurrent state, DCDC1 power supply function is OFF Latch., it is to output information on abnormality detected to error logic and set NDIAG to L latch. At overcurrent detection, it is to output information on abnormality detected to error logic and set NDIAG to L latch.

After the Tdc1idetoff(typ.2ms) turn-off mode, overcurrent detection counter is reset if overcurrent is not detected in Tdc1idetoffw(maximum 2ms).

For details, refer to the following table and timing chart.

## ON/OFF switching operation at DCDC1 overcurrent detection (off-latch)

#### ON/OFF switching operation at DCDC1 overcurrent detection (with detection reset)

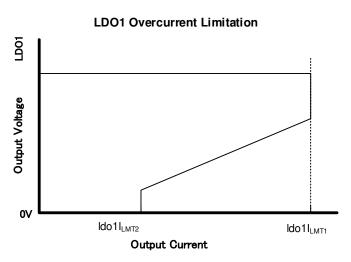

#### **LDO1** overcurrent operation

LDO1 incorporates a current limiter. The current limiter starts operating at overcurrent detection, and outputs a signal of limiter operation, information on abnormality detected, to error logic and set NDIAG to L latch. For details, refer to the table below.

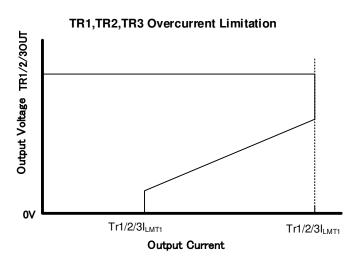

# TR1, TR2, TR3 overcurrent operation

TR1, TR2, TR3 incorporate a current limiter. The current limiter starts operating at overcurrent detection, and outputs a signal of limiter operation, information on abnormality detected, to error logic and set NDIAG to L latch. For details, refer to the table below.

List of operation of overcurrent detection values

| Monitoring function | SPI<br>setting | Setting<br>bit | Operation                 | Initial<br>value | ABIST | Writing to register | NDIAG   |

|---------------------|----------------|----------------|---------------------------|------------------|-------|---------------------|---------|

| 50504               | Applicable     | 0              | DCDC1 operation continued | -                | 0     | 0                   | L latch |

| DCDC1 overcurrent   |                | 1              | DCDC1 off-latch (8 times) | 0                | 0     | 0                   | L latch |

| LDO1 overcurrent    | Not applicable | _              | LDO1 current limiter      | -                | 0     | 0                   | L latch |

| TR1 overcurrent     | Not applicable | _              | TR1 current limiter       | -                | 0     | 0                   | L latch |

| TR2 overcurrent     | Not applicable | _              | TR2 current limiter       | -                | 0     | 0                   | L latch |

| TR3 overcurrent     | Not applicable | 1              | TR3 current limiter       | -                | 0     | 0                   | L latch |

<sup>\*</sup> Only at the time of starting until NRST1 is released(NRST1=H), TR1/2/3 overcurrent detection function does not start operation to write in register and NDIAG does not become L latch.

© 2015-2019 2019-12-10

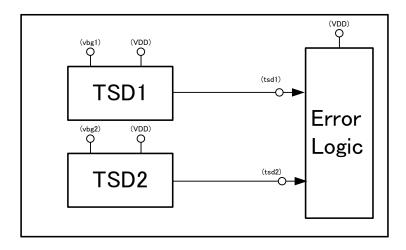

#### Overheat detection

This product incorporates an overheat detection function. It stops after latching off power supply circuits of DCDC1, LDO1 and TR1 to 3, if junction temperature Tj exceeds overheat detection temperature TSD1 or TSD2 = 170 °C (typ.) (Only at the time of overheat detection, processing to turn off DCDC1, LDO1 and TR1 to 3 is selectable by SPI setting.)

List of operation of overheat detection values

| Monitoring function | SPI<br>setting | Setting<br>bit | Operation                              | Initial<br>value | ABIST | Writing to register | NDIAG   |

|---------------------|----------------|----------------|----------------------------------------|------------------|-------|---------------------|---------|

| Overheat detection  | Applicable     | 0              | DCDC1,LDO1 and TR1 to 3 turned off     | _                | 0     | 0                   | L latch |

|                     |                | 1              | DCDC1, LDO1 and TR1 to 3 off-<br>latch | 0                | 0     | 0                   | L latch |

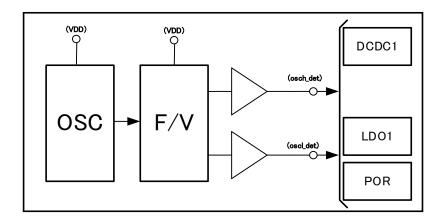

#### Oscillation frequency monitoring

- > F/V convertor and voltage comparator are to detect abnormality in high frequency and low frequency.

- ➤ If abnormal frequency is detected, it latches off DCDC1, LDO1 and TR1 to 3 simultaneously with NRST1/2 = L and NDIAG = L latch.

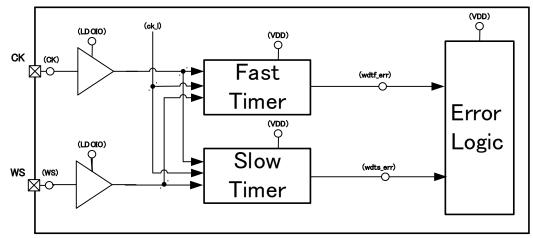

# 5-4. Watchdog Timer Watchdog timer

- ➤ It is a window type to detect both low speed and high speed abnormalities of watchdog clear pulse (CK input). If either of them is detected (\*1), reset signals of NRST1 and NRST2 = L, and NDIAG = L are output.

- Validity/invalidity of high speed abnormality detection is selectable via SPI communication.

- Validity/invalidity of watchdog timer is selectable by WS pin setting. (In the case of invalidity selected, NRST2 becomes L.)

- > Whether or not to latch NRST1 and NRST2 = L at watchdog error detection is selectable by register setting.

- > The number of times that NRST1 and NRST2 become L outputs due to the watchdog timer is counted. When this count reaches five times, NRST1 and NRST2 become L latches. However, when a clear pulse is input during counting, the count is cleared at that point.

- \*1 High speed abnormality detection is to be counted on a high speed detection counter. If the detection is counted 10 consecutive times with no normal input of clear pulse, reset signals of NRST1 and NRST2 = L, and NDIAG = L are output.

|                                                                                       | Condition for counting                                                 | Condition for WDT reset output                                                                          | Condition for<br>initializing counter<br>value                                                                                                                                            | Remarks                                               |

|---------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Watchdog timer<br>Counter                                                             | At valid WDT function                                                  | Low speed<br>abnormality detection                                                                      | Normal input of clear pulse or reset output or watchdog timer low speed abnormality detection or watchdog timer high speed abnormality detection or WS pin = H or at invalid WDT function | _                                                     |

| Watchdog timer<br>high speed detection<br>counter                                     | At valid WDT function<br>& WDT high speed<br>abnormality detection     | WDT high speed<br>abnormality detection<br>10 consecutive times of<br>detection                         | Reset output or normal<br>input of clear pulse or<br>WS pin =H or at invalid<br>WDT function                                                                                              | _                                                     |

| Watchdog timer reset counter  Watchdog reset detection attributable to watchdog timer |                                                                        | Reset output is latched with reset counter value = 5. (Reset output latch is not released with WS = H.) | Normal input of clear<br>pulse or WS pin = H or at<br>invalid WDT function                                                                                                                | Stopping counting at watchdog timer reset counter = 5 |

| CK counter                                                                            | At valid WDT function<br>(only the first time after<br>the validation) | typ. 256 ms count                                                                                       | Normal input of clear<br>pulse or WS pin = H                                                                                                                                              | _                                                     |

<sup>\*</sup> Valid WDT monitoring function: when clear pulse is input within start-up waiting time

Invalid WDT monitoring function: after Power-on reset (including recovery from low voltage)

In the case of WS pin = H

© 2015-2019 2019-12-10

# Watchdog timer function block

#### Watchdog timer start-up waiting time

WDT monitoring It will be started, when the clear pulse is input from the MCU within the watchdog timer start wait time (typ. 256 ms) from the time when the power on reset is released with this WS pin set to "L". However, if reset occurs 5 consecutive times with no input of clear pulse from MCU, it latches off.

If watchdog timer function is set invalid by WS pin setting, the start-up waiting time also becomes invalid.

- In the case of no clear pulse detected because of broken MCU during the start-up ⇒ reset

- At startup, if the MCU is broken and the low width (twl) of the clear pulse is short. ⇒ high speed detection after WDT monitoring has become valid ⇒ reset

#### **Condition for NRST2 release**

A MCU judges the operation normal and releases NRST2 if WDT clear signal is input within normal time (to be set in register) after WDT monitoring starts at clear pulse input within the start-up waiting time.

If watchdog timer function is set invalid by WS pin setting, NRST2 becomes L.

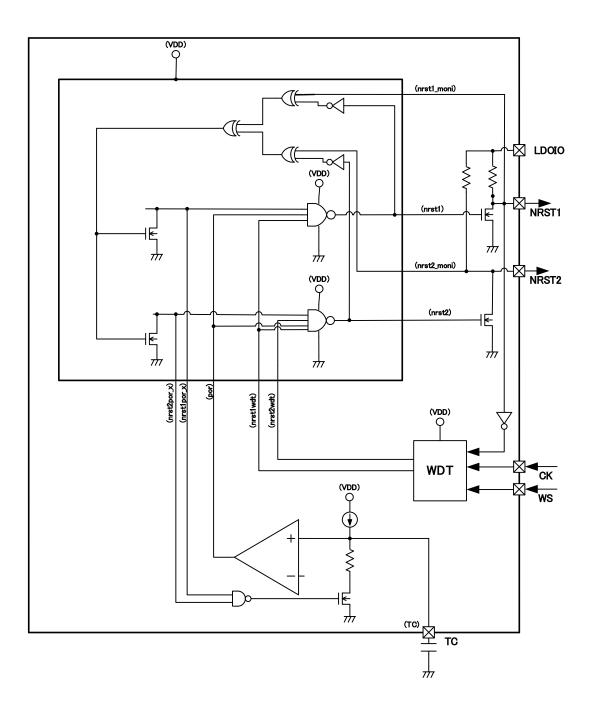

#### 5-5. Power-on Reset Function

#### Power-on reset

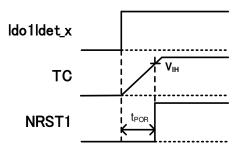

- LDO1 output voltage shows normal values (with low voltage detection released), Power-on reset timer function starts operating. After Power-on reset time, NRST1 becomes H and the reset is released.

- > Power-on reset time is changeable with capacitance of external capacitor (TC).

#### Reset output monitoring function

Reset output is constantly monitored. The output of NRST1 and NRST2 error logic is to be compared to the pin logic. If the latter differs from the former, reset output monitoring abnormality is detected with NRST1=NRST2=off, NDIAG=L latch.

© 2015-2019 2019-12-10

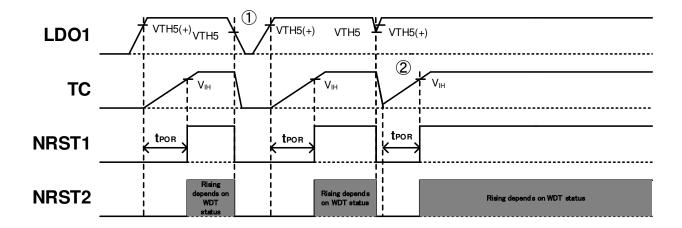

#### Reset timer timing chart

- ① NRST1/2 becomes L at LDO1 drop detection. NRST1 becomes H (NRST2 depending on WDT status) after Power-on reset time with LDO1 drop detection released.

- ② In the case of NRST1 = L, NRST1 becomes H after tPOR time even if LDO1 recovers instantly.

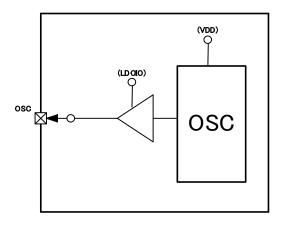

#### 5-6. Clock Generation Function

#### Oscillator circuit

- It is a C/R oscillator with built-in capacitor and resistor. Oscillation frequency is 8 MHz (typ.)

- It is used for DCDC convertor switching, and logic circuit clock.

- > The setting by SPI communication allows outputting divided clock from OSC pin.

- > It incorporates a detection circuit to output DIAG signal at the event of abnormal oscillation frequency.

- It incorporates a spread spectrum function. Whether to validate the function is selectable via SPI communication.

2019-12-10

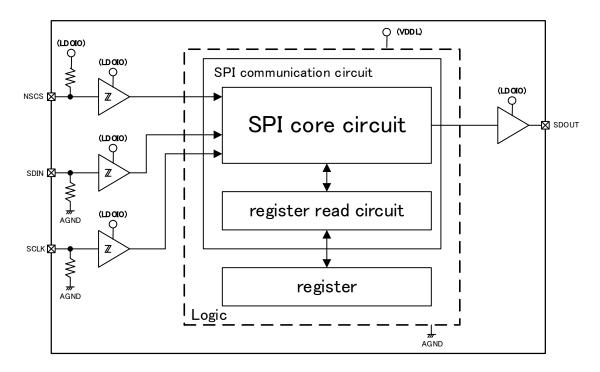

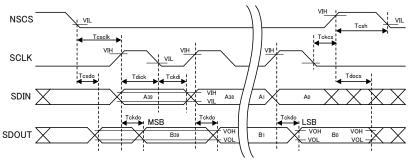

#### 5-7.SPI Communication

SPI communication circuit consists of SPI core circuit and register read circuit block.

NSCS becomes "L" only during communication, otherwise it is always "H".

SCLK is used to synchronize communication between IC and MCU. The MCU writes data in SDIN at rising edge of clock, and IC reads it at the next falling edge. IC writes data in SDOUT at rising edge of clock, and the MCU reads it at the next falling edge.

SDIN receives the data bit from the MCU in the order of MSB to LSB.

SDOUT sends the data bit to the MCU in the order of MSB to LSB. The output is in push-pull configuration, and will be high-impedance at the time of NSCS = "H".

The IC has NSCS pin with built-in pull-up resistor, and SCLK and SDIN pins with built-in pull-down resistors.

Fig. 5.8.a Block diagram for SPI communication circuit

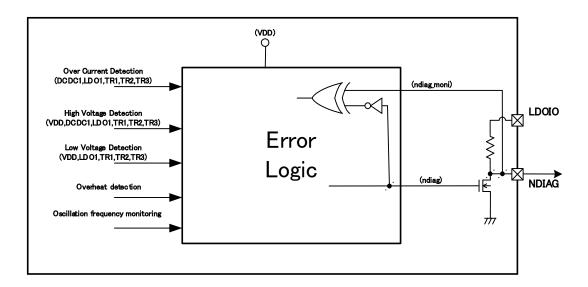

# 5-8. Error Logic

# **Error logic function**

- If power IC monitoring results are not acceptable, NDIAG = L latch is output. The abnormality data is written simultaneously in the register incorporated in SPI.

- The output of NDAIG error logic is to be compared to the pin logic constantly. If the latter differs from the former, NDAIG output monitoring abnormality is detected with NDAIG=L latch.

- If all the detected abnormalities become normal and abnormality data written in the register is cleared, the status returns to NDIAG = H.

Error logic circuit block diagram

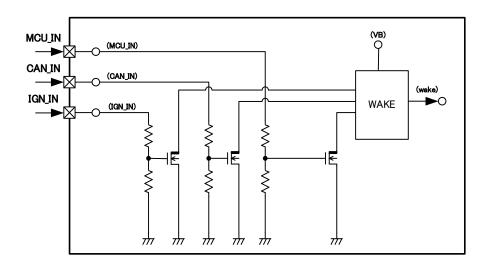

# 5-9. Wake-up Function

# Wake-up circuit

> This IC is waked up by inputting one of three inputs(CAN\_IN or IGN\_IN or MCU\_IN). The following shows the configuration.

#### Operation truth table

|        | Input             | Output           |      |  |

|--------|-------------------|------------------|------|--|

| CAN_IN | IGN_IN            | MCU_IN           | wake |  |

| "_"    | "L"               | "L"              | "L"  |  |

| "H"    | <b>"</b> *"       | " <del>*</del> " | "H"  |  |

| "*"    | "H"               | " <del>*</del> " | "H"  |  |

| "*"    | 6 <del>*</del> 17 | "H"              | "H"  |  |

※ "\*": No Care

# 6 Absolute maximum ratings (Ta = 25 °C)

| Item                  | Signal            | Pin                                                                    | Rating                                                                | Unit | Condition                                                                              |

|-----------------------|-------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------|------|----------------------------------------------------------------------------------------|

|                       |                   |                                                                        | -0.3 to 18                                                            |      | _                                                                                      |

|                       | V <sub>B</sub>    | VB1,VB2,VB3                                                            | 18 to 28(≤1h)                                                         | V    | _                                                                                      |

| Power<br>voltage      |                   |                                                                        | 28 to 40(≤1s)                                                         |      | _                                                                                      |

| vollago               | V <sub>LDO1</sub> | LDO1                                                                   | -0.3 to 6                                                             | ٧    | _                                                                                      |

|                       | V <sub>DD</sub>   | VDD                                                                    | -0.3 to 6                                                             | V    | _                                                                                      |

|                       |                   |                                                                        | -0.3 to 18                                                            |      | _                                                                                      |

|                       | $V_{\text{IN1}}$  | IGN_IN,CAN_IN,                                                         | 18 to 28(≤1h)                                                         | V    | _                                                                                      |

|                       |                   |                                                                        | 28 to 40(≤1s)                                                         |      | _                                                                                      |

|                       | V <sub>IN2</sub>  | MCU_IN                                                                 | -0.3 to 6                                                             | V    | _                                                                                      |

| Input                 | V <sub>IN3</sub>  | DC1FB,DC2IN,<br>LDO1IN                                                 | -0.3 to V <sub>B</sub> +0.3                                           | ٧    | V <sub>IN2</sub> ≤18<br>V <sub>IN2</sub> ≤28(≤1h)                                      |

| voltage               | V <sub>IN4</sub>  | LDOIO                                                                  | -0.3 to V <sub>LDO1IN</sub> +0.3                                      | V    | V <sub>IN4</sub> ≤6V                                                                   |

|                       | V <sub>IN5</sub>  | TC,WS<br>SDIN,SCLK,NSCS,CK                                             | -0.3 to V <sub>LDOIO</sub> +0.3                                       | ٧    | V <sub>IN5</sub> ≤6V                                                                   |

|                       | V <sub>IN6</sub>  | BSTOFF,DC1Css,<br>DC2Css,TEST1,TEST2,TEST3,TEST4,VDDL,<br>DC2FB,DC2FBs | -0.3 to V <sub>DD</sub> +0.3                                          | V    | V <sub>IN6</sub> ≤6V                                                                   |

|                       | V <sub>OUT1</sub> | DC1SW1, DC1SW2                                                         | -0.3 to V <sub>B</sub> +0.3                                           | ٧    | V <sub>out2</sub> ≤18<br>V <sub>out2</sub> ≤28(≤1h)<br>V <sub>out2</sub> ≤28 to 40(1s) |

| Output                | V <sub>OUT2</sub> | DC1G2, DC2SW                                                           | -0.3 to V <sub>B</sub> +0.3                                           | ٧    | V <sub>out2</sub> ≤18<br>V <sub>out2</sub> ≤28(≤1h)                                    |

| voltage               | V <sub>OUT3</sub> | NRST1,NRST2, NDIAG,<br>SDOUT, OSC                                      | -0.3 to V <sub>LDO1</sub> +0.3                                        | V    | V <sub>OUT3</sub> ≤6V                                                                  |

|                       | V <sub>OUT4</sub> | TR1, TR2, TR3                                                          | -2 to V <sub>B</sub> +0.3                                             | V    | V <sub>out4</sub> ≤18<br>V <sub>out4</sub> ≤28(≤1h)                                    |

|                       | I <sub>OUT1</sub> | DC1SW1, DC1SW2                                                         | dc1I <sub>DET</sub>                                                   |      | _                                                                                      |

| Outro                 | I <sub>OUT2</sub> | DC2SW                                                                  | _                                                                     |      | _                                                                                      |

| Output<br>current     | I <sub>OUT3</sub> | LDO1                                                                   | Ido1I <sub>LMT1</sub>                                                 | Α    | _                                                                                      |

|                       | I <sub>OUT4</sub> | TR1,TR2,TR3,                                                           | tr1I <sub>LMT1</sub> / tr2I <sub>LMT1</sub> /<br>tr3I <sub>LMT1</sub> |      | _                                                                                      |

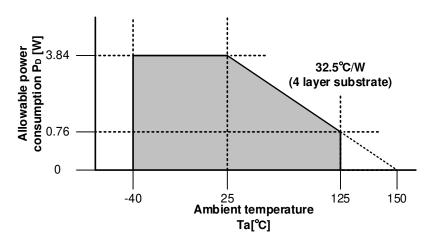

| Allowable dissipation |                   |                                                                        | Refer to Fig.6-1.                                                     | W    | _                                                                                      |

| Operating temperature | Topr              | _                                                                      | -40 to 125                                                            | °C   | _                                                                                      |

| Storage temperature   | Tstg              | -                                                                      | -55 to 150                                                            | °C   | _                                                                                      |

Note: Absolute maximum ratings are a set of ratings that must not be exceeded, for even a moment. Exceeding the absolute maximum ratings may cause IC breakdown, deterioration and/or damage, and consequently may damage other equipment than IC. Please keep the specified absolute maximum ratings unfailingly in any operating conditions for designing, and use the product within the specified operating ranges.

Substrate size 76.2×114.3×1.6 mm Soldering on substrate board: applicable Fig.6.1 Allowable dissipation

#### 7 Electrical characteristics

| Item                    | Signal              | Pin         | Measurement condition                                                                                           | Minimum | Standard | Maximum | Unit |  |  |  |  |

|-------------------------|---------------------|-------------|-----------------------------------------------------------------------------------------------------------------|---------|----------|---------|------|--|--|--|--|

| Overall characteristics |                     |             |                                                                                                                 |         |          |         |      |  |  |  |  |

| Stand-by current        | Icc- <sub>STB</sub> | VB1,VB2,VB3 | I <sub>VB1</sub> +I <sub>VB2</sub> +I <sub>VB3</sub> IGN_IN=CAN_IN=MCU_IN= 0V,VB1/2/3=12V,Ta=25°C               | _       | _        | 5       | μA   |  |  |  |  |

| Current consumption 1   | lcc1                | VB1,VB2,VB3 | VB1/2/3=12V,<br>I <sub>LDO1</sub> =300mA,<br>I <sub>TR1</sub> =100mA,I <sub>TR2</sub> =I <sub>TR3</sub> =40mA,  | _       |          | 350     | mA   |  |  |  |  |

| Current consumption 2   | lcc2                | VB1,VB2,VB3 | VB1/2/3=18V,<br>I <sub>LDO1</sub> =300mA,<br>I <sub>TR1</sub> =100mA,I <sub>TR2</sub> =I <sub>TR3</sub> =40mA,  | _       | _        | 240     | mA   |  |  |  |  |

| Current consumption 3   | lcc3                | VB1,VB2,VB3 | VB1/2/3=18V<br>I <sub>LDO1</sub> =50mA<br>I <sub>TR1</sub> =I <sub>TR2</sub> =I <sub>TR3</sub> =20mA            | _       | 1        | 90      | mA   |  |  |  |  |

| Current consumption 4   | Icc4                | VB1,VB2,VB3 | I <sub>LDO1</sub> =0mA<br>I <sub>TR1</sub> =I <sub>TR2</sub> =I <sub>TR3</sub> =0mA,<br>I <sub>DCDC2</sub> =0mA | _       | _        | 26      | mA   |  |  |  |  |

| Item                                           | Signal                   | Pin   | Measurement condition                                                          | Minimum               | Standard   | Maximum          | Unit  |

|------------------------------------------------|--------------------------|-------|--------------------------------------------------------------------------------|-----------------------|------------|------------------|-------|

| DCDC1 power supply                             |                          |       |                                                                                |                       | •          | •                | •     |

|                                                |                          |       | VB pin voltage<br>7.0V to:10 to 800mA                                          | 5.7                   | 6.0        | 6.3              |       |

|                                                |                          |       | VB pin voltage<br>6.2 to 7.0V: 10 to 500mA                                     | 5.7                   | _          | 7.0              |       |

| Output voltage                                 | $V_{DC1}$                |       | VB pin voltage<br>4.0V to 6.2V: 10 to 500mA<br>2.7V to 4.0V: 10 to 400mA       | 5.7                   | 6.0        | 6.3              | v     |

|                                                |                          | DC1FB | VB pin Voltage(Back mode)<br>7.0V to:10 to 800mA                               | 5.7                   | 6.0        | 6.3              |       |

|                                                |                          |       | VB pin Voltage(Back mode)<br>6.8V to 7V:10 to 800mA<br>6.0 to 6.8V:10 to 500mA | 5.7                   | _          | 7.0              |       |

|                                                |                          |       | VB3 pin voltage 7.0V to                                                        | 800                   | _          | _                |       |

|                                                |                          |       | VB3 pin voltage 4.0V to 7.0V                                                   | 500                   | _          | _                |       |

|                                                | ldc1                     |       | VB3 pin voltage 2.7V to 4.0V                                                   | 400                   | _          | _                | 4     |

| Output current                                 |                          |       | VB3 pin Voltage<br>(Back mode) 6.8V to                                         | 800                   | _          | _                | mA    |

|                                                |                          |       | VB3 pin Voltage<br>(Back mode) 6.0V to 6.8V                                    | 500                   | _          | _                |       |

| Switching frequency                            | $dc1f_{SW}$              | _     | _                                                                              | 340                   | 400        | 460              | kHz   |

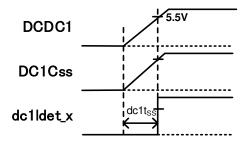

| Soft start time                                | dc1tss                   | _     | Refer to Fig.7.1.<br>V <sub>DC1</sub> : Time from 0→5.5V<br>DC1Css=0.01µF *    | 0.8                   | 1.6        | 2.4              | ms    |

| Overcurrent detection current                  | dc1I <sub>DET</sub>      | _     | _                                                                              | 1.5                   | 2.15       | 2.8              | Α     |

| Overcurrent detection off time                 | Tdc1 <sub>idetoff</sub>  | _     | _                                                                              | _                     | 2          | _                | ms    |

| Overcurrent detection off waiting time         | Tdc1 <sub>idetoffw</sub> | _     | _                                                                              | _                     | 2          | _                | ms    |

| Number of times of<br>overcurrent detected     | Ndc1 <sub>idetoff</sub>  | _     | _                                                                              | _                     | 8          | _                | times |

| H output voltage of                            |                          |       | lout=-20mA                                                                     | V <sub>DC1</sub> -0.5 | _          | V <sub>DC1</sub> |       |

| gate driver for boost mode                     | dc1V <sub>GH</sub>       | DC1G2 | lout=-20mA<br>(DCDC1 start & V <sub>DC1</sub> <5.3V)                           | 3.1                   | _          | V <sub>DC1</sub> | V     |

| L output voltage of gate driver for boost mode | dc1V <sub>GL</sub>       | 20.02 | lout=20mA                                                                      | _                     | _          | 0.5              | V     |

| LDO1 power supply                              |                          | 1001  | 1 45 400 55 4                                                                  | 1.0                   | F 0        | F 1              | V     |

| Output voltage  Load stability                 | V <sub>LDO1</sub>        | LDO1  | I <sub>LOAD1</sub> =1 to 400mA  VLDO1IN=6V                                     | 4.9<br>-1             | 5.0<br>0.2 | 5.1<br>1         | %     |

| Current limiter 1                              | Ido1I <sub>LMT1</sub>    | LDO1  | I <sub>LOAD1</sub> =1 to 400mA                                                 | 400                   |            | 800              | mA    |

|                                                |                          |       |                                                                                | 400                   | _          |                  |       |

| Current limiter 2 Output discharge             | Ido1I <sub>LMT2</sub>    | LDO1  | LDO1=0V                                                                        | _                     | _          | 100              | mA    |

| Output discharge resistance                    | R <sub>Ido1dis</sub>     | LDO1  | _                                                                              | 60                    | 130        | 220              | Ω     |

<sup>\*</sup> The standard value for soft start time is specified for Ics. Please note that fluctuations of capacitance of DC1Css pin's external capacitor are not considered.

Fig.7.1 Soft start time for DCDC1

| Item                      | Signal                | Pin         | Measurement condition                                                 | Minimum | Standard | Maximum | Unit |

|---------------------------|-----------------------|-------------|-----------------------------------------------------------------------|---------|----------|---------|------|

| TR1 power supply          |                       |             |                                                                       |         | •        |         | •    |

| Voltage difference        | V <sub>TR1-LDO1</sub> | TR1<br>LDO1 | I <sub>LDO1LOAD</sub> =1 to 400mA<br>I <sub>TR1LOAD</sub> =1 to 100mA | -20     | 0        | 20      | mV   |

| Current limiter 1         | tr1I <sub>LMT1</sub>  | TR1         | _                                                                     | 100     | _        | 300     | mA   |

| Current limiter 2         | tr1I <sub>LMT2</sub>  | TR1         | TR1=0V                                                                | _       | _        | 26      | mA   |

| Output pull-down resistor | tr1 <sub>RPD</sub>    | TR1         | _                                                                     | 5       | 10       | 20      | kΩ   |

| TR2 power supply          |                       |             |                                                                       |         |          |         |      |

| Voltage difference        | V <sub>TR2-LDO1</sub> | TR2<br>LDO1 | I <sub>LDO1LOAD</sub> =1 to 400mA<br>I <sub>TR2LOAD</sub> =1 to 100mA | -20     | 0        | 20      | mV   |

| Current limiter 1         | tr2I <sub>LMT1</sub>  | TR2         | _                                                                     | 100     | _        | 300     | mA   |

| Current limiter 2         | tr2I <sub>LMT2</sub>  | TR2         | TR2=0V                                                                | _       | _        | 26      | mA   |

| Output pull-down resistor | tr2 <sub>RPD</sub>    | TR2         | _                                                                     | 5       | 10       | 20      | kΩ   |

| TR3 power supply          |                       |             |                                                                       |         |          |         |      |

| Voltage difference        | V <sub>TR3-LDO1</sub> | TR3<br>LDO1 | I <sub>LDO1LOAD</sub> =1 to 400mA<br>I <sub>TR3LOAD</sub> =1 to 100mA | -20     | 0        | 20      | mV   |

| Current limiter 1         | tr3I <sub>LMT1</sub>  | TR3         | _                                                                     | 100     | _        | 300     | mA   |

| Current limiter 2         | tr3I <sub>LMT2</sub>  | TR3         | TR3=0V                                                                | _       | _        | 26      | mA   |

| Output pull-down resistor | tr3 <sub>RPD</sub>    | TR3         | _                                                                     | 5       | 10       | 20      | kΩ   |

| VDD power supply          |                       |             |                                                                       |         |          |         |      |

| Output voltage            | $V_{VDD}$             | VDD         | _                                                                     | 4.5     | 5.0      | 5.5     | V    |

| Start-up VB3 voltage      | Vstvb3                | VDD/VB3     | _                                                                     | _       | _        | 5.3     | V    |

| LDOIO                     |                       |             |                                                                       |         |          |         |      |

| LDOIO current             | I <sub>LDOIO</sub>    | LDOIO       | LDOIO connects LDO1                                                   | _       | _        | 7.2     | mA   |

| Item                               | Signal               | Pin       | Measurement condition                                     | Minimum                | Standard           | Maximum                | Unit     |

|------------------------------------|----------------------|-----------|-----------------------------------------------------------|------------------------|--------------------|------------------------|----------|

| Power-on reset                     |                      |           |                                                           |                        |                    |                        |          |

| Output voltage                     | V <sub>OL</sub>      |           | I <sub>OL</sub> =2mA                                      | _                      | 1                  | 0.3                    | ٧        |

| Output leak current                | I <sub>LEAK</sub>    | NRST1/2   | V <sub>OUT</sub> =LDOIO                                   | _                      | _                  | 5                      | μA       |

| Pull-up resistor                   | R <sub>RST</sub>     |           | _                                                         | 3.3                    | 4.7                | 6.1                    | kΩ       |

| Power-on reset                     | tpor                 | NRST1     | Refer to Fig.7.2.                                         | 320×C <sub>T</sub>     | 400×C <sub>T</sub> | 480×C⊤                 | ms       |

| L retaining voltage                | V <sub>RL</sub>      |           | Refer to Fig.7.3                                          | _                      | _                  | 1.2                    | V        |

| NRST 1/2 terminal                  | VAL                  |           | Time until NRST1/2 detects                                | 4                      | 8                  | 16                     | μs       |

| abnormality detection              | tfVTHNR              |           | logic abnormality after H / L                             |                        | J                  | 10                     | μο       |

| filter time                        | 1/2                  |           | output                                                    |                        |                    |                        |          |

| NRST 1/2 terminal                  |                      |           | •                                                         | _                      | 2.3                | 2.5                    | V        |

| abnormality                        | VhTHNR               | NRST1/2   | Detection threshold after                                 |                        |                    |                        |          |

| detection threshold                | 1/2                  | NITOT 1/2 | tfVTHNR1/2 at H output                                    |                        |                    |                        |          |

| High side                          |                      |           |                                                           |                        |                    |                        |          |

| NRST 1/2 terminal                  |                      |           |                                                           | 1.5                    | 1.8                | _                      | V        |

| abnormality                        | VTHNR1/2             |           | Detection threshold after                                 |                        |                    |                        |          |

| detection threshold                |                      |           | tfVTHNR1/2 at Low output                                  |                        |                    |                        |          |

| Low side                           | I <sub>IN</sub>      |           | _                                                         | -13                    | -10                | -7                     |          |

| Input current Discharge resistance | R <sub>DIS</sub>     | TC        |                                                           | 0.5                    | 1                  | 2                      | μA<br>kΩ |

| Threshold voltage                  | V <sub>IH</sub>      | 10        | _                                                         | 3.75                   | 4                  | 4.25                   | V        |

| Watchdog timer                     | V III                |           | 1                                                         | 0.70                   |                    | 0                      |          |

| Tratedeg time.                     |                      |           | (Watchdog timer time on low                               |                        |                    |                        |          |

| Watchdog – S                       | twp-s                |           | speed side) Register is set to                            | 5.0                    | 6.0                | 7.5                    | ms       |

|                                    |                      |           | initial value.                                            |                        |                    |                        |          |

|                                    |                      |           | (Maximum pre-configurable                                 |                        |                    |                        |          |

| Watchdog – S max                   | two-smax             |           | time for watchdog timer on                                | 40.0                   | 48.0               | 60.0                   | ms       |

|                                    |                      |           | low speed side)                                           |                        |                    |                        |          |

|                                    |                      |           | (Minimum pre-configurable                                 |                        |                    |                        |          |

| Watchdog – S min                   | t <sub>WD-Smin</sub> |           | time for watchdog timer on                                | 5.0                    | 6.0                | 7.5                    | ms       |

|                                    |                      |           | low speed side)                                           |                        |                    |                        |          |

| Watchdog – F                       | t                    |           | (Watchdog timer time on high speed side). Register is set | 0.41                   | 0.50               | 0.63                   | ms       |

| vvalcridog – i                     | t <sub>WD-F</sub>    |           | to initial value.                                         | 0.41                   | 0.50               | 0.00                   | 1113     |

|                                    |                      |           | (Maximum pre-configurable                                 |                        |                    |                        |          |

| Watchdog – F max                   | twp-Fmax             | CK        | time for watchdog timer on                                | 3.3                    | 4.0                | 5.0                    | ms       |

| 3                                  | -                    |           | high speed side)                                          |                        |                    |                        |          |

|                                    |                      |           | (Minimum pre-configurable                                 |                        |                    |                        |          |

| Watchdog – F min                   | two-Fmin             |           | time for watchdog timer on                                | 0.41                   | 0.50               | 0.63                   | ms       |

|                                    |                      |           | high speed side)                                          |                        |                    |                        |          |

| Watchdog                           | t <sub>wdr</sub>     |           | _                                                         | 111                    | 160                | 226                    | μs       |

| reset pulse width                  | - 1701               |           |                                                           |                        |                    |                        | F- 5     |

| Watchdog clock                     | t <sub>Wh</sub>      |           | Input detectable H width                                  | 1                      | _                  | _                      | μs       |

| pulse High width                   |                      |           |                                                           |                        |                    |                        |          |

| Watchdog clock pulse Low width     | twı                  |           | Input detectable L width                                  | 1                      | _                  | _                      | μs       |

| Watchdog timer                     |                      |           | Length of time between                                    |                        |                    |                        |          |

| waiting time for initial           | t <sub>wdst</sub>    |           | Power-on reset and initial                                | 213                    | 256                | 320                    | ms       |

| start-up                           | - wust               |           | watchdog clear pulse input                                |                        |                    |                        |          |

| •                                  | Iн                   | CK,       | V <sub>IN</sub> =V <sub>LDO1</sub>                        | 50                     | 100                | 200                    |          |

| Input current                      | I <sub>IL</sub>      | WS        | V <sub>IN</sub> =0V                                       | -5                     | _                  | 5                      | μA       |

| loout valtara                      | V <sub>IH</sub>      | CK,       | _                                                         | 0.75×V <sub>LDO1</sub> | _                  | _                      | .,       |

| Input voltage                      | VIL                  | ws        | I _                                                       | _                      | _                  | $0.25 \times V_{LDO1}$ | V        |

\* The standard value for Power-on reset is specified for Ics. Please note that fluctuations of C<sub>T</sub> [μF] are not considered. Minimum time at an instantaneous power failure is 264 x C<sub>T</sub> [ms].

Fig.7.2 Power-on reset

**%The L retaining voltage by VDD is a design guarantee.**

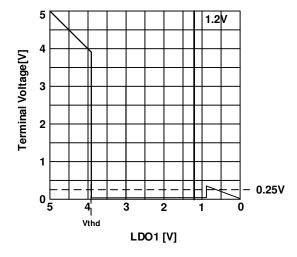

Fig.7.3 L retaining voltage

| Item                                                  | Signal     | Pin   | Measurement condition | Minimum | Standard | Maximum | Unit |

|-------------------------------------------------------|------------|-------|-----------------------|---------|----------|---------|------|

| Power supply voltage r                                | nonitoring |       |                       |         |          |         |      |

| DCDC1 high voltage detection                          | VhTH6      |       | Detected              | 8.7     | 9.0      | 9.3     |      |

| DCDC1 high voltage detection released                 | VhTH6(-)   |       | Released              | 8.6     | 8.9      | 9.2     | V    |

| DCDC1 high voltage<br>detection difference<br>voltage | dVhTH6     | DC1FB | VhTH6-VDC1            | 2.7     | 3.0      | 3.3     |      |

| DCDC1 high voltage detection filtering time           | tfVhTH     |       | _                     | 0.5     | 1.0      | 2.0     | ms   |

| LDO1 high voltage detection                           | VhTH5      |       | Detected              | 5.2     | 5.3      | 5.4     |      |

| LDO1 high voltage detection released                  | VhTH5(-)   |       | Released              | 5.1     | 5.2      | 5.3     | V    |

| LDO1 high voltage<br>detection difference<br>voltage  | dVhTH5     |       | VhTH5-VLDO1           | 0.2     | 0.3      | 0.4     |      |