## Unipolar 2-Phase Stepper Motor Driver ICs

## SLA7070MS Series Data Sheet

October, 2018 Rev.1.7

## **Table of Contents**

| 1.   | General Description                           |    |

|------|-----------------------------------------------|----|

| 2.   | Features and Benefits                         | 2  |

| 3.   | Part Numbers and Functional Characteristics   |    |

| 4.   | Specifications                                | 4  |

| 5.   | Power Derating Chart                          | 8  |

| 6.   | Package Outline Drawing.                      | 9  |

| 7.   | Functional Block Diagrams and Pin Assignments | 10 |

| 8.   | Application Example                           | 12 |

| 9.   | Truth Tables                                  |    |

| 10.  | Logic Input Pins                              | 14 |

| 11.  | Logic Input Timing                            | 15 |

| 12.  | Step Sequence Diagrams                        | 16 |

| 13.  | Individual Circuit Descriptions               | 22 |

| 14.  | Functional Descriptions                       | 24 |

| 15.  | Application Information                       | 31 |

| 16.  | Thermal Design Information                    | 36 |

| 17.  | Characteristics Data                          | 38 |

| Impo | ortant Notes                                  | 39 |

## 1. General Description

This document describes summary of the SLA7070MS series.

### 2. Features and Benefits

- (1) Main power supply voltages, V<sub>BB</sub>: 46 V (max.), 10 to 44 V normal operating range

- (2) Logic supply voltages, V<sub>DD</sub>: 3.0 to 5.5 V

- (3) Maximum output currents, I<sub>O(max)</sub>: 2.0 A, 3.0 A

- (4) Clock-in stepping control (built-in sequencer)

- (5) Full-, half-, and microstep products are available

- → Microstepping options are capable of full-, half-, quarter-, eighth-, and sixteenth-stepping

- (6) Built-in "sense resistor" detects motor current

- (7) All variants are pin-compatible for enhanced design flexibility

- (8) ZIP type 23-pin molded package (SLA package)

- (9) Self-excitation PWM current control with fixed OFF-time

- → For microstepping variants, OFF-time adjusted automatically by step reference current ratio (3 levels)

- (10) Built-in synchronous rectifying circuit reduces power dissipation at PWM-OFF

- (11) Synchronous PWM chopping function prevents motor noise in the Hold mode

- (12) The Sleep mode to reduce IC input current in stand-by state

- (13) Built-in protection circuitry against motor coil opens/shorts and thermal shutdown protection

- (14) The following are the product variants and optional features available:

- Blanking Time

- Full/Half step products:

Microstep product:

3.2 μs (standard), 5.2 μs (optional type B)

1.7 μs (standard), 3.2 μs (optional type B)

- Microstep product:Input Clock Edge

- Standard type: POS (positive) edge

- Optional type W: POS/NEG (positive and negative) edge

**NOTE:** The optional types listed above, "type B" and "type W", are abbreviated and referred to "B" and "W" as the letters for product branding codes, respectively. These terms and abbreviations are also used throughout this document. See also Section 6 for more details.

### 3. Part Numbers and Functional Characteristics

Table 3-1 provides the product variants available in the SLA7070MS series.

Table 3-1. Part Numbers and Functional Characteristics

|             | Functional Characteristics |           |            |               |  |  |  |

|-------------|----------------------------|-----------|------------|---------------|--|--|--|

|             |                            |           | Rated 0    | Current       |  |  |  |

|             | Seque                      | encer     | (Maximum S | etting Value) |  |  |  |

| Part Number | Full/Half Step             | Microstep | 2.0 A      | 3.0 A         |  |  |  |

| SLA7072MS   | X                          |           | X          |               |  |  |  |

| SLA7073MS   | X                          |           |            | X             |  |  |  |

| SLA7078MS   |                            | X         |            | X             |  |  |  |

In addition, the following functional options are available in the SLA7070MS series:

• Blanking Time

Full/Half step products: 3.2 μs (standard), 5.2 μs (optional type B)

Microstep product: 1.7 μs (standard), 3.2 μs (optional type B)

• Input Clock Edge

• Standard type: POS (positive) edge

• Optional type W: POS/NEG (positive and negative) edge

NOTE: The optional types listed above, "type B" and "type W", are abbreviated and referred to "B" and "W" as the letters for product branding codes, respectively. These terms and abbreviations are also used throughout this document. See also Section 6 for more details.

## 4. Specifications

Table 4-1. Absolute Maximum Ratings

Unless specifically noted, T<sub>A</sub> = 25 °C Symbol Characteristic Rating Unit Remarks ٧  $V_{\mathsf{M}}$ Load (Motor Supply) Voltage 46 Main Power Supply Voltage  $V_{BB}$ 46 ٧ ٧ 6 Power supply to DC Supply Voltage  $V_{DD}$ ٧ 7 ≤1 µs (5% duty) 2.0 Α SLA7072MS Control **Output Current**  $I_{O}$ current SLA7073MS 3.0 Α value SLA7078MS ٧ -0.3 to  $V_{DD} + 0.3$ Logic Input Voltage  $V_{IN}$ ٧ **REF Input Voltage**  $V_{\mathsf{REF}}$ -0.3 to  $V_{DD} + 0.3$ V Sense Voltage ±2  $V_{RS}$ Allowable Power Dissipation 4.7 W Without heatsink  $P_D$ Junction Temperature  $\mathsf{T}_\mathsf{J}$ 150 °C °C **Operating Ambient Temperature**  $\mathsf{T}_\mathsf{A}$ -20 to 85 °C Storage Temperature -30 to 150  $T_{sta}$

**NOTE:** Output current ratings may be limited by duty cycles, ambient temperatures, and heat sinking conditions. Do not exceed the maximum output currents and the maximum junction temperature (T<sub>J</sub>) given above, under any conditions of use.

Table 4-2. Recommended Operating Conditions

Unless specifically noted, T<sub>A</sub> = 25 °C

|                             | Standard Value |      |      |      |                                                                                                   |

|-----------------------------|----------------|------|------|------|---------------------------------------------------------------------------------------------------|

| Characteristic              | Symbol         | Min. | Max. | Unit | Remarks                                                                                           |

| Load (Motor Supply) Voltage | V <sub>M</sub> |      | 44   | V    |                                                                                                   |

| Main Power Supply Voltage   | $V_{BB}$       | 10   | 44   | V    |                                                                                                   |

| Logic Supply Voltage        | $V_{DD}$       | 3.0  | 5.5  | V    | Surge voltage at VDD pin<br>should be less than ±0.5<br>V to avoid malfunctioning<br>in operation |

| Case Temperature            | T <sub>C</sub> |      | 90   | °C   | Measured at Pin 12 (lead portion), without heatsink                                               |

**NOTE:** As the motor supply voltage,  $V_M$ , becomes higher, it also approaches the breakdown voltage of the OUTx pins (100 V min.); and breakdown will be more likely to happen. Even if one of the OUTx pins breaks down (due to surge noise or other factors), the SLA7070MS series will recognize it as abnormality (coil open) and will run appropriate protection functions. Therefore, a thorough evaluation is recommended.

Table 4-3. Electrical Characteristics 1

Unless specifically noted,  $T_A$  = 25 °C,  $V_{BB}$  = 24 V, and  $V_{DD}$  = 5 V

|                                                                    | <u> </u>           | Unies                     |           | iy noted, TA              | = 25 | $V_{BB} = 24 V$ , and $V_{DD} = 5 V$                         |

|--------------------------------------------------------------------|--------------------|---------------------------|-----------|---------------------------|------|--------------------------------------------------------------|

|                                                                    |                    | N 4" -                    | Rating    | N 4 -                     |      |                                                              |

| Characteristic                                                     | Symbol             | Min.                      | Тур.      | Max.                      | Unit | Conditions                                                   |

| Main Power Supply                                                  | I <sub>BB</sub>    |                           |           | 15                        | mA   | Normal mode                                                  |

| Current                                                            | I <sub>BBS</sub>   |                           |           | 100                       | μΑ   | Sleep1, Sleep2                                               |

| Logic Power Current                                                | I <sub>DD</sub>    |                           |           | 5                         | mA   |                                                              |

| MOSFET Breakdown<br>Voltage                                        | V <sub>DSS</sub>   | 100                       |           |                           | V    | $V_{BB} = 44V$ , $I_D = 1$ mA                                |

| Maximum Response<br>Frequency                                      | f <sub>clk</sub>   | 250                       | ,         |                           | kHz  | Clock duty cycle = 50%                                       |

| Logic Input Voltage                                                | $V_{IL}$           |                           |           | 0.25 ×<br>V <sub>DD</sub> | V    | Ś                                                            |

| Logio input voltage                                                | V <sub>IH</sub>    | 0.75 ×<br>V <sub>DD</sub> |           |                           | V    |                                                              |

| Logic Input Current                                                | I <sub>IL</sub>    |                           | ±1        |                           | μΑ   |                                                              |

| Logic input ourient                                                | I <sub>IH</sub>    |                           | ±1        |                           | μΑ   |                                                              |

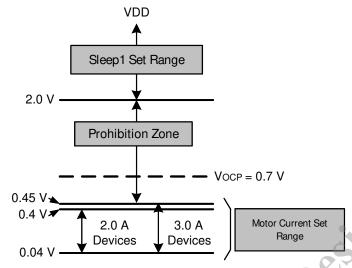

| REF Input Voltage                                                  | $V_{REF}$          | 0.04                      |           | <b>→</b>                  | V    | Table 4-5, Figure 4-1                                        |

| nui input voitage                                                  | $V_{REFS}$         | 2.0                       |           | V <sub>DD</sub>           | V    | Output OFF, Sleep11)                                         |

| REF Input Current                                                  | I <sub>REF</sub>   |                           | ±10       | Δ 🖸                       | μΑ   |                                                              |

| SENSE Detection<br>Voltage                                         | V <sub>SENSE</sub> | V <sub>REF</sub> – 0.03   | $V_{REF}$ | V <sub>REF</sub> + 0.03   | V    | V <sub>REF</sub> = 0 to 1.5 V,<br>Step reference ratio: 100% |

| Sleep-Enable Recovery<br>Time                                      | t <sub>SE</sub>    | 100                       | c. C      |                           | μs   | Sleep1, Sleep2                                               |

| Switching Time                                                     | t <sub>con</sub>   |                           | 2.0       |                           | μs   | Clock → Output ON                                            |

| Switching rine                                                     | t <sub>coff</sub>  |                           | 1.5       |                           | μs   | Clock → Output OFF                                           |

| Overcurrent Detection Voltage <sup>2)</sup>                        | V <sub>cor</sub>   | 0.65                      | 0.7       | 0.75                      | V    | Motor coils shorted                                          |

|                                                                    |                    |                           | 2.3       |                           | Α    | 1.0 A and 1.5 A devices                                      |

| Overcurrent Detection Current (V <sub>OCP</sub> / R <sub>S</sub> ) | Icop               |                           | 3.5       |                           | Α    | 2.0 A devices                                                |

| Outlett (AOCb / Lt8)                                               |                    |                           | 4.6       |                           | Α    | 3.0 A devices                                                |

| Load Disconnection Undetected Time                                 | t <sub>opp</sub>   |                           | 2         |                           | μs   | From PWM-OFF                                                 |

| Overheat Protection<br>Temperature                                 | T <sub>tsd</sub>   |                           | 140       |                           | °C   | Measured at back of device case (after heat has saturated)   |

| ***************************************                            | V <sub>FlagL</sub> |                           |           | 1.25                      | V    | I <sub>FlagL</sub> = 1.25 mA                                 |

| FLAG Output Voltage                                                | V <sub>FlegH</sub> | V <sub>DD</sub> –<br>1.25 |           |                           | V    | I <sub>FlagH</sub> = −1.25 mA                                |

| El AC Outout Current                                               | I <sub>FlagL</sub> |                           |           | 1.25                      | mA   |                                                              |

| FLAG Output Current                                                | I <sub>FlagH</sub> | -1.25                     |           |                           | mA   |                                                              |

| NOTE: II-lana anaic                                                | 11 ,               | 1                         |           |                           | 1    |                                                              |

NOTE: Unless specifically noted, negative current is defined as output current flow from a specified pin.

1) In a state of: IBBS, output OFF, and sequencer <u>enabled</u>.

2) Protection circuit operates when  $V_{SENSE} \ge V_{OCP}$ .

Table 4-4. Electrical Characteristics 2 (Varying with Step Sequence)

| (1) Full-/Half-step products: SLA7072MS, SLA7073MS  Unless specifically noted, $T_A = 25$ °C, $V_{BB} = 24$ V, and $V_{DD} = 5$ V |                  |        |      |      |       |                                         |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------|--------|------|------|-------|-----------------------------------------|

| Characteristic                                                                                                                    | Symbol           | Rating |      |      | Linit |                                         |

| Gnaracteristic                                                                                                                    |                  | Min.   | Тур. | Max. | Unit  | Conditions                              |

| Step Reference Current                                                                                                            | Mode F           |        | 100  |      | %     | $V_{REF} \approx V_{SENSE} = 100\%$     |

| Ratio                                                                                                                             | Mode 8           |        | 70   |      | %     | $V_{REF} = 0 \text{ to } 1.0 \text{ V}$ |

| Minimum PWM ON-Time                                                                                                               | 1                |        | 3.2  |      | μs    | Standard type<br>(w/o branding codes)   |

| WIIIIIIIIIIII F VVIVI OIN-TIITIE                                                                                                  | lon(min)         |        | 5.2  |      | μs    | Optional type B (w/ branding codes)     |

| PWM OFF-Time                                                                                                                      | t <sub>off</sub> |        | 12   |      | μs    |                                         |

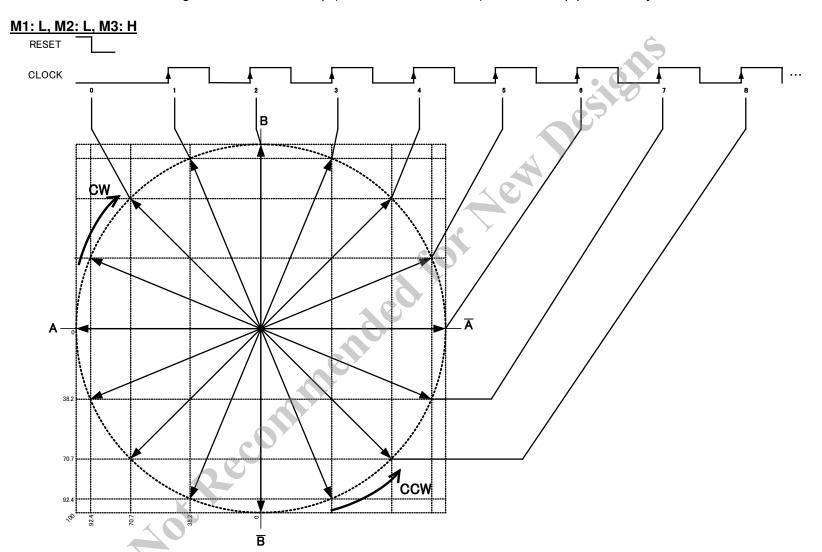

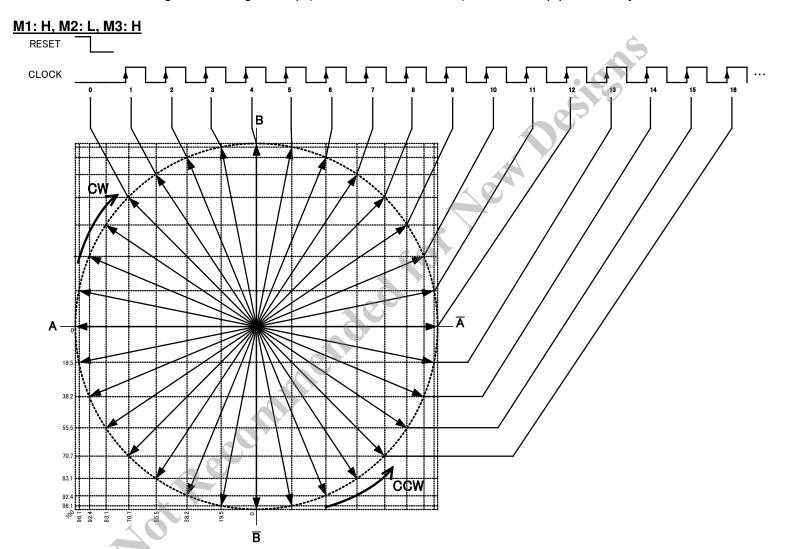

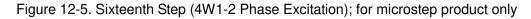

### (2) Microstep product: SLA7078MS

|                              | Unless specifically noted, T <sub>A</sub> = 25 °C, V <sub>BB</sub> = 24 V, and VDD = 5 V |                        |      |                                       |       |                                                                                 |  |  |

|------------------------------|------------------------------------------------------------------------------------------|------------------------|------|---------------------------------------|-------|---------------------------------------------------------------------------------|--|--|

| Characteristic               | Symbol                                                                                   | Rating                 |      |                                       | Unit  | Conditions                                                                      |  |  |

| Characteristic               | Symbol                                                                                   | Min.                   | Тур. | Max.                                  | Offit | Conditions                                                                      |  |  |

|                              | Mode F                                                                                   |                        | 100  |                                       | %     |                                                                                 |  |  |

|                              | Mode E                                                                                   |                        | 98.1 |                                       | %     |                                                                                 |  |  |

|                              | Mode D                                                                                   |                        | 95.7 |                                       | %     |                                                                                 |  |  |

|                              | Mode C                                                                                   |                        | 92.4 | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | %     |                                                                                 |  |  |

|                              | Mode B                                                                                   |                        | 88.2 |                                       | %     |                                                                                 |  |  |

|                              | Mode A                                                                                   |                        | 83.1 |                                       | %     |                                                                                 |  |  |

| Ctan Deference Comment       | Mode 9                                                                                   |                        | 77.3 |                                       | %     | \\\ ~\\\ 1000/                                                                  |  |  |

| Step Reference Current Ratio | Mode 8                                                                                   |                        | 70.7 |                                       | %     | $V_{REF} \approx V_{SENSE} = 100\%,$<br>$V_{REF} = 0 \text{ to } 1.0 \text{ V}$ |  |  |

| Tatio                        | Mode 7                                                                                   | 70                     | 63.4 |                                       | %     | TO THE POLOTION                                                                 |  |  |

|                              | Mode 6                                                                                   |                        | 55.5 |                                       | %     |                                                                                 |  |  |

|                              | Mode 5                                                                                   |                        | 47.1 |                                       | %     |                                                                                 |  |  |

|                              | Mode 4                                                                                   |                        | 38.2 |                                       | %     |                                                                                 |  |  |

|                              | Mode 3                                                                                   |                        | 29   |                                       | %     |                                                                                 |  |  |

|                              | Mode 2                                                                                   |                        | 19.5 |                                       | %     |                                                                                 |  |  |

|                              | Mode 1                                                                                   |                        | 9.8  |                                       | %     |                                                                                 |  |  |

|                              | $V_{MOL}$                                                                                |                        |      | 1.25                                  | V     | $I_{MOL} = 1.25 \text{ mA}$                                                     |  |  |

| MO Output Voltage            | V <sub>MOH</sub>                                                                         | V <sub>DD</sub> - 1.25 |      |                                       | V     | I <sub>MOH</sub> = −1.25 mA                                                     |  |  |

| MO Output Current            | I <sub>MOL</sub>                                                                         |                        |      | 1.25                                  | mA    |                                                                                 |  |  |

| WO Output Current            | I <sub>MOH</sub>                                                                         | -1.25                  |      |                                       | mA    |                                                                                 |  |  |

| Minimum PWM ON-Time          | <b>†</b>                                                                                 |                        | 1.7  |                                       | μs    | Standard type<br>(w/o branding codes)                                           |  |  |

| William F WWW ON-TIME        | t <sub>on(min)</sub>                                                                     |                        | 3.2  |                                       | μs    | Optional type B (w/ branding codes)                                             |  |  |

|                              | t <sub>off 1</sub>                                                                       |                        | 12   |                                       | μs    | Mode 8 to Mode F                                                                |  |  |

| PWM OFF-time                 | t <sub>off 2</sub>                                                                       |                        | 9    |                                       | μs    | Mode 4 to Mode 7                                                                |  |  |

|                              | t <sub>off 3</sub>                                                                       |                        | 7    |                                       | μs    | Mode 1 to Mode 3                                                                |  |  |

Table 4-5. Electrical Characteristics 3 (Varying with Output Current Range)

(1)  $I_0 = 2.0 \text{ A}$

Unless specifically noted,  $T_A = 25$  °C,  $V_{BB} = 24$  V, and  $V_{DD} = 5$  V

| Chiese epecinically herea, TA = 25 C, VBB = 21 V, and VDD = 0 |                     |        |       |       |       |                                |  |

|---------------------------------------------------------------|---------------------|--------|-------|-------|-------|--------------------------------|--|

| Characteristic                                                | Symbol              | Rating |       |       | Unit  | Conditions                     |  |

| Characteristic                                                | Symbol              | Min.   | Тур.  | Max.  | Ullit | Conditions                     |  |

| Output MOSFET ON-Voltage                                      | R <sub>DS(on)</sub> |        | 0.25  | 0.4   | Ω     | $I_D = 2.0 \text{ A}$          |  |

| Output MOSFET Body<br>Diodes Forward Voltage                  | V <sub>F</sub>      |        | 0.95  | 1.2   | V     | I <sub>F</sub> = 2.0 A         |  |

| Sense Resistor <sup>1)</sup>                                  | $R_{s}$             | 0.199  | 0.205 | 0.211 | Ω     | Tolerance: ±3%                 |  |

| REF Input Voltage                                             | $V_{REF}$           | 0.04   |       | 0.4   | V     | Within specified current limit |  |

<sup>&</sup>lt;sup>1)</sup> Includes approximately 5 m $\Omega$  circuit resistance in addition to the resistance of the built-in resistor itself.

(2)  $I_0 = 3.0 A$

Unless specifically noted, T<sub>A</sub> = 25 °C, V<sub>BB</sub> = 24 V, and V<sub>DD</sub> = 5 V

|                              |                     |        |       | ,         |      |                          |

|------------------------------|---------------------|--------|-------|-----------|------|--------------------------|

| Characteristic               | Symbol              | Rating |       |           | Unit | Conditions               |

| Characteristic               | Syllibol            | Min.   | Тур.  | Max.      | Unit | Conditions               |

| Output MOSFET                | R <sub>DS(on)</sub> |        | 0.18  | 0.24      | Ω    | I <sub>D</sub> = 3.0 A   |

| ON-Resistance                | 1 (DS(on)           |        | 0.10  |           | 32   | 10 = 0.070               |

| Output MOSFET Body           | $V_{F}$             |        | 0.95  | 2.1       | ٧    | I <sub>E</sub> = 3.0 A   |

| Diodes Forward Voltage       | <b>*</b> F          |        | 0.00  | \ <u></u> | ·    | 15 – 0.0 / (             |

| Sense Resistor <sup>1)</sup> | R <sub>s</sub>      | 0.150  | 0.155 | 0.160     | Ω    | Tolerance: ±3%           |

| REF Input Voltage            | $V_{REF}$           | 0.04   |       | 0.45      | V    | Within specified current |

| - Input voltage              | ▼ REF               | 0.04   |       | 0.70      | ٧    | limit                    |

<sup>&</sup>lt;sup>1)</sup> Includes approximately 5 m $\Omega$  circuit resistance in addition to the resistance of the built-in resistor itself.

Figure 4-1. Setting Range of Reference Voltage, V<sub>REF</sub>

**NOTE:** Extra attentions should be paid to the changeover between the motor current specification range and the Sleep1 set range.  $V_{\text{OCP}}$  falls on the "prohibition zone" threshold. If the changeover takes too long, OCP operation will start when  $V_{\text{SENSE}} > V_{\text{OCP}}$ .

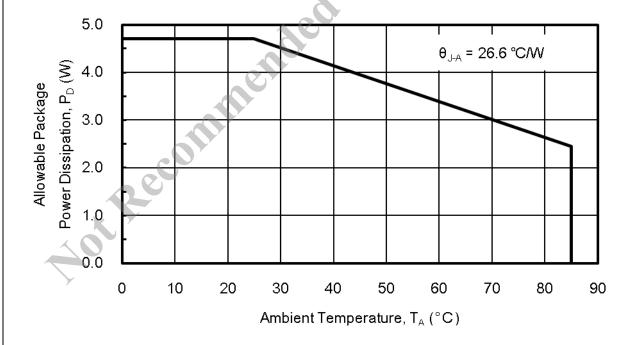

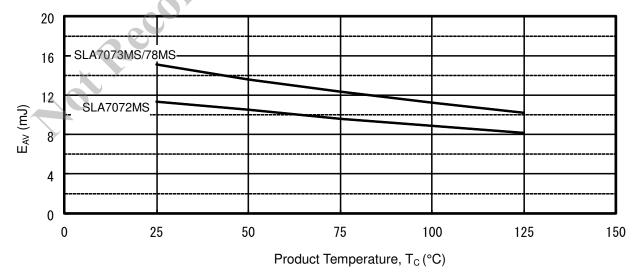

## 5. Power Derating Chart

Figure 5-1. Power Derating Chart

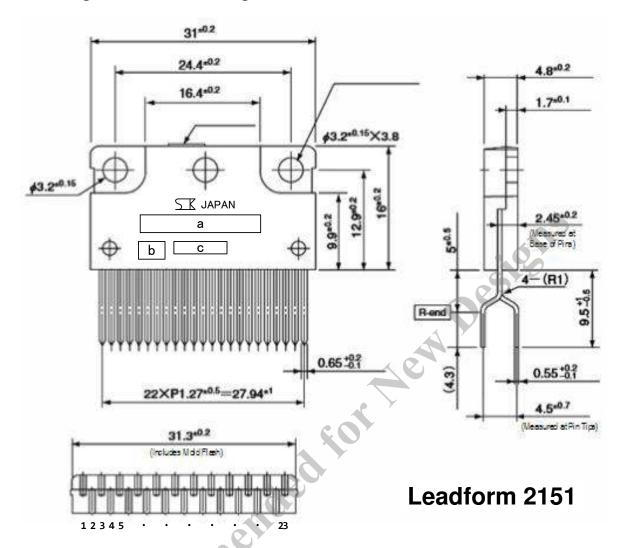

## 6. Package Outline Drawing

#### NOTES:

- Dimensions in millimeters

- Pin material: CuPin plating: Solder plating (Pb-free)

- Branding codes:

- a Part number 1: SLA707xMS

- The lowercase letter x represents a number of either of 2, 3, 7, or 8, according to the combination of rated currents and step sequencers. See also Table 3-1, which lists the part numbers and corresponding features.

- b Part number 2: W, B, or WB

- Only optional products have this area labeled with either of the letters listed above. W, B, and WB stand for optional type W (selectable clock inputs), type B (selectable blanking times), and type WB (a combined version of types W and B), respectively.

- Lot number: YMDD

- · Y is the last digit of the year of manufacture

- *M* is the month of the year (1 to 9, O, N, or D)

- DD is the day of the month (01 to 31)

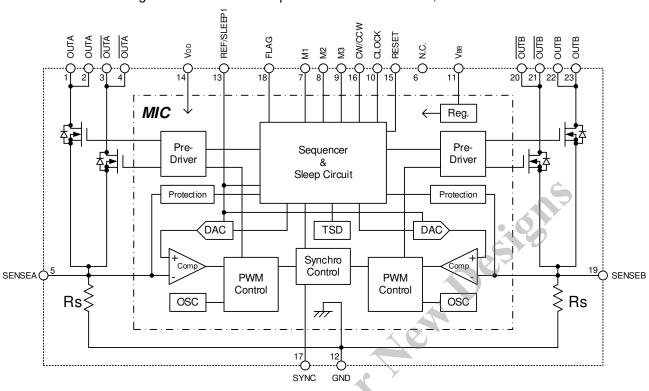

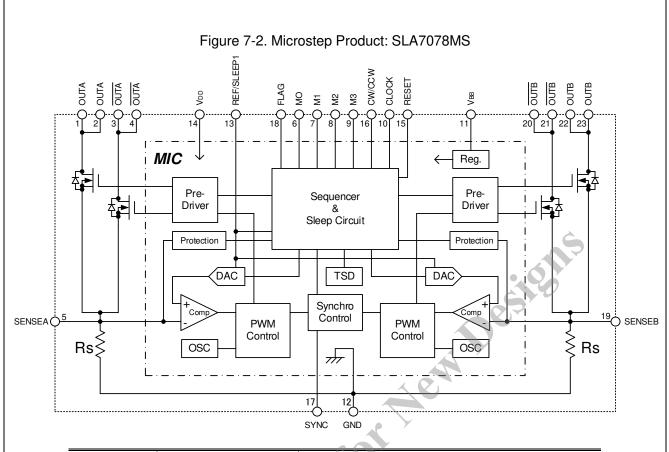

# 7. Functional Block Diagrams and Pin Assignments

Figure 7-1. Full-/Half-Step Products: SLA7072MS, SLA7073MS

| Pin No. | Symbol           | Function                                   |  |  |  |  |

|---------|------------------|--------------------------------------------|--|--|--|--|

| 1 2     | OUTA             | Phase A output                             |  |  |  |  |

| 3<br>4  | OUTA             | Phase A output                             |  |  |  |  |

| 5       | SENSEA           | Phase A current sensing                    |  |  |  |  |

| 6       | NC               | No connection                              |  |  |  |  |

| 7       | M1               |                                            |  |  |  |  |

| 8       | M2               | Input for excitation mode & Sleep2 setting |  |  |  |  |

| 9       | M3               |                                            |  |  |  |  |

| 10      | CLOCK            | Step clock input                           |  |  |  |  |

| 11      | $V_BB$           | Main power supply voltage (for motor)      |  |  |  |  |

| 12      | GND              | Ground                                     |  |  |  |  |

| 13      | REF/SLEEP1       | Input for control current / Sleep1 setting |  |  |  |  |

| 14      | $V_{	extsf{DD}}$ | Power supply to logic                      |  |  |  |  |

| 15      | RESET            | Reset input for internal logic             |  |  |  |  |

| 16      | CW/CCW           | Forward / reverse input                    |  |  |  |  |

| 17      | SYNC             | Synchronous PMW control switch input       |  |  |  |  |

| 18      | FLAG             | Output from protection circuit monitor     |  |  |  |  |

| 19      | SENSEB           | Phase B current sensing                    |  |  |  |  |

| 20      | OUTB             | Phase R output                             |  |  |  |  |

| 21      | OOID             | Phase B output                             |  |  |  |  |

| 22      | OUTB             | Phase B output                             |  |  |  |  |

| 23      | 0010             | Thase b output                             |  |  |  |  |

| Pin No. | Symbol     | Function                                      |  |  |  |

|---------|------------|-----------------------------------------------|--|--|--|

| 1       | OUTA       | Phase A output                                |  |  |  |

| 2       | <b>.</b>   | Naccon Carpar                                 |  |  |  |

| 3       | OUTA       | Phase A output                                |  |  |  |

| 4       | JOIN       | T hase 77 output                              |  |  |  |

| 5       | SENSEA     | Phase A current sensing                       |  |  |  |

| 6       | MO         | Output from 2-phase excitation status monitor |  |  |  |

| 7       | M1         |                                               |  |  |  |

| 8       | M2         | Input for excitation mode & Sleep2 setting    |  |  |  |

| 9       | M3         |                                               |  |  |  |

| 10      | CLOCK      | Step clock input                              |  |  |  |

| 11      | $V_{BB}$   | Main power supply voltage (for motor)         |  |  |  |

| 12      | GND        | Ground                                        |  |  |  |

| 13      | REF/SLEEP1 | Input for control current / Sleep1 setting    |  |  |  |

| 14      | $V_{DD}$   | Power supply to logic                         |  |  |  |

| 15      | RESET      | Reset input for internal logic                |  |  |  |

| 16      | CW/CCW     | Forward / reverse input                       |  |  |  |

| 17      | SYNC       | Synchronous PMW control switch input          |  |  |  |

| 18      | FLAG       | Output from protection circuit monitor for    |  |  |  |

| 10      | FLAG       | detecting coil opens/shorts                   |  |  |  |

| 19      | SENSEB     | Phase B current sensing                       |  |  |  |

| 20      | OUTB       | Dhoop D cutout                                |  |  |  |

| 21      | OUIB       | Phase B output                                |  |  |  |

| 22      | OUTD       | Phase B output                                |  |  |  |

| 23      | OUTB       |                                               |  |  |  |

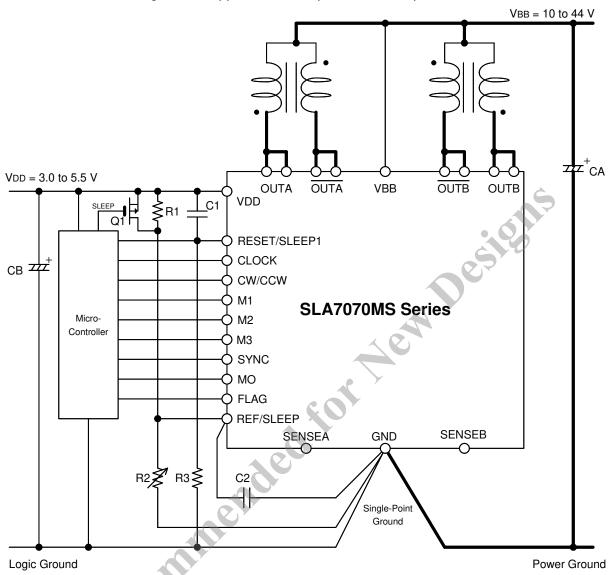

## 8. Application Example

Figure 8-1. Application Example for Microstep Product

Constants, for reference use only:

| $R1 = 10 \text{ k}\Omega$ | $C\dot{A} = 100 \mu\text{F} / 50 \text{V}$ |

|---------------------------|--------------------------------------------|

| $R2 = 1 k\Omega (VR)$     | $CB = 10 \mu F / 10 V$                     |

| $R3 = 10 \text{ k}\Omega$ | $C1 = 0.1 \mu\text{F}$                     |

|                           | $C2 = 0.1 \mu F$                           |

#### NOTES:

- Take precautions to avoid noise on the V<sub>DD</sub> line; noise levels greater than 0.5 V on the V<sub>DD</sub> line may cause device malfunction. Noise can be reduced by separating the logic ground and the power ground on a PCB from the GND pin (Pin 12).

- Unused logic input pins (CW/CCW, M1, M2, M3, RESET, and SYNC) <u>must be pulled up or down to VDD or ground.</u> If those unused pins are left open, the device may malfunction.

- Unused logic output pins (MO, FLAG) must be kept open.

#### 9. Truth Tables

#### (1) Common Input Pins

Table 9-1 shows the truth table for the input pins common to both full-/half-stepping and microstepping products available in the SLA7070MS series.

Table 9-1. Truth Table for Common Input Pins

|                      | 14510 0           | 1.11411 14510 101 001 | mion input i ino |                   |

|----------------------|-------------------|-----------------------|------------------|-------------------|

|                      |                   |                       |                  | Clock             |

|                      |                   |                       | POS Edge         | POS/NEG Edge      |

| Pin Name             | Low Level         | High Level            | (Standard)       | (Optional Type W) |

| RESET                | Normal operation  | Logic reset           |                  | _                 |

| CW/CCW               | Forward (CW)      | Reverse (CCW)         |                  |                   |

| M1                   |                   |                       |                  |                   |

| M2                   | Commutation (Slee | ep2 is not included)  |                  | <u> </u>          |

| M3 Commutation (Siee |                   | spz is not included)  |                  |                   |

| REF/SLEEP1           | Normal operation  | Sleep1 function       |                  |                   |

| SYNC                 | Non-sync PWM      | Cyna DWM control      |                  |                   |

| STNC                 | control           | Sync PWM control      |                  | _                 |

The Reset function is asynchronous. If an input on the RESET pin is high, the internal logic circuit is reset. At this point, if the REF/SLEEP1 pin stays low, outputs turn on at the starting point of excitation. Note that a signal on the RESET pin cannot control an output disable command.

Voltage across the REF/SLEEP1 pin controls PWM currents and the Sleep1 function.

- When  $V_{REF} \le 1.5$  V (low level), the REF/SLEEP1 pin functions as the reference voltage input for normal operation.

- When  $V_{REF} \geq 2.0$  V (high level), the REF/SLEEP1 pin disables all outputs. This is the Sleep1 mode that disables the internal linear circuitry and minimizes the main power supply current,  $I_{BB}$ . Although much of the internal circuitry is disabled, the logic circuit is still active. If an input signal on the CLOCK pin is asserted, the internal sequencer/translator circuit reacts and sets a step starting point for the next operation.

The Sleep2 function operates in the same way as the Sleep1 function does, except that the internal logic circuit enters the Hold mode. Therefore, in the Sleep2 mode, the internal sequencer/translator circuit is not activated even if a step command signal occurs on the CLOCK input pin.

The Sync function runs only at "2-phase excitation timing." If this function is used at other than the 2-phase excitation timing, an overall balance might collapse because PWM OFF-times and setting currents are different in each of phase A and phase B control scenario. (If this function is used at a point of 1-phase excitation, it does not react as the Sync function does. But there is no problem.) The 2-phase excitation timing is a point where the step reference current ratio of both phases A and B is either of Mode 8 or F.

### (2) Commutation/Sleep2 Function Setting

Table 9-2 provides the logic for the pins (M1, M2, and M3) which set commutation.

Table 9-2. Truth Table for Commutation/Sleep2 Functions

| Function (Pin Name) |    | Name) |                          |                              |

|---------------------|----|-------|--------------------------|------------------------------|

| M1                  | M2 | M3    | Full/Half Step           | Microstep                    |

| L                   | L  | L     | Full step (Mode 8 fixed) | Full step (Mode 8 fixed)     |

| Н                   | L  | L     | Full step (Mode F fixed) | Full step (Mode F fixed)     |

| L                   | Н  | L     | Half step (1-2 Phase)    | Half step (1-2 Phase)        |

| Н                   | Н  | L     | Half step (Mode F fixed) | Half step (Mode F fixed)     |

| L                   | L  | Н     |                          | Quarter step (W1-2 Phase)    |

| Н                   | L  | Н     | ClaanO function          | Eighth step (2W1-2 Phase)    |

| L                   | Н  | Н     | Sleep2 function          | Sixteenth step (4W1-2 Phase) |

| Н                   | Н  | Н     |                          | Sleep2 function              |

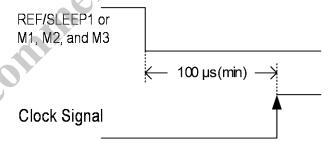

**NOTE:** The Sleep2 function disables outputs and reduces the driver supply current ( $I_{BB}$ ) in the same way as the Sleep1 function does. However, unlike the Sleep1 function, the logic circuitry is put into a "standby" state in the Sleep2 function. Therefore, the sequencer/translator is not activated even if a step command signal occurs on the CLOCK input pin. When awaking from the Sleep2 mode, a delay of  $100~\mu s$  or longer before sending a clock pulse is recommended.

#### (3) Monitor Output Pins

The SLA7070MS series provides two device status monitor outputs:

- MO pin (microstepping product only) Step sequence

- FLAG pin Protection feature operation

Table 9-3 shows the logic for the monitor output pins.

Table 9-3. Truth Table for Monitor Output Pins

| Pin Name | Low Level                            | High Level                   |

|----------|--------------------------------------|------------------------------|

| MO       | Other than 2-phase excitation timing | 2-phase excitation timing    |

| FLAG     | Normal operation                     | Protection circuit operation |

|          |                                      |                              |

**NOTE:** The outputs turn off at the point where the protection circuit starts operating. To release the protection state, cycle the logic supply voltage,  $V_{DD}$ .

## 10. Logic Input Pins

The low pass filter (LPF) incorporated with the logic input pins (CLOCK, RESET, CW/CCW, M1, M2, M3, and SYNC) improves noise rejection.

The logic inputs are CMOS input compatible; therefore, they are in a high impedance state. Note that the IC should be used at a fixed input level, either low or high.

If there is a possibility that signals from the microcontroller are in high impedance, add a pull-up/-down resistor. Since outputs from the logic input pins, which function as output ON/OFF controllers, may result in abnormal oscillation, leading to MOSFET breakdown as the worst-case scenario.

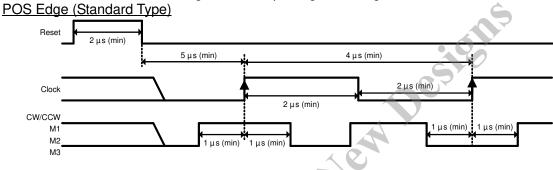

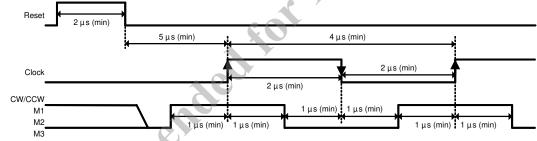

## 11. Logic Input Timing

#### (1) Clock Signal

a. A low-to-high transition (rising, or POS edge) or a low-to-high then high-to-low transition (rising and falling, or POS/NEG edge) on the CLOCK input signal advances the sequencer/translator. Clock pulse width should be set at 2 µs or longer in both positive and negative polarities. Therefore, clock response frequency is set to 250 kHz.

#### b. Clock Edge Timing

With regard to the input logic of the CW/CCW, M1, M2, and M3 pins, a 1 µs delay should occur both before and after a pulse edge, as setup and hold times (see Figure 11-1). The sequencer logic circuitry might malfunction if the logic polarity is changed during these setup and hold times.

Figure 11-1. Input Signal Timing

**NOTE:** When awaking from the Sleep1 or Sleep2 mode, a delay of  $\underline{100 \,\mu s}$  or  $\underline{longer}$  before sending a clock pulse is recommended.

### (2) Reset Signal

## a. Reset Signal Pulse Width

Reset pulse width is equivalent to the hold time of a high level input. It should be 2  $\mu s$  or longer, same as the clock pulse width.

#### b. Reset Release and Clock Input Timing

When the timing of a reset release (falling edge) and a clock edge is simultaneous, the internal logic might result in an unexpected operation. Therefore, a greater than 5  $\mu$ s delay is required between the falling edge of the RESET input signal and the next rising edge of the CLOCK input signal (see Figure 11-1).

#### (3) Logic Level Change

Logic level inputs on CW/CCW, M1, M2, and M3 set the translator step direction (CW/CCW) and step mode (M1, M2, and M3; see also Table 9-2, the commutation truth table). Changes to those inputs do not take effect until the rising edge of an input signal on the CLOCK pin. However, depending on the type and state of a motor, there may be errors in motor operation such as step-out. A thorough evaluation on the changes of sequence should be carried out.

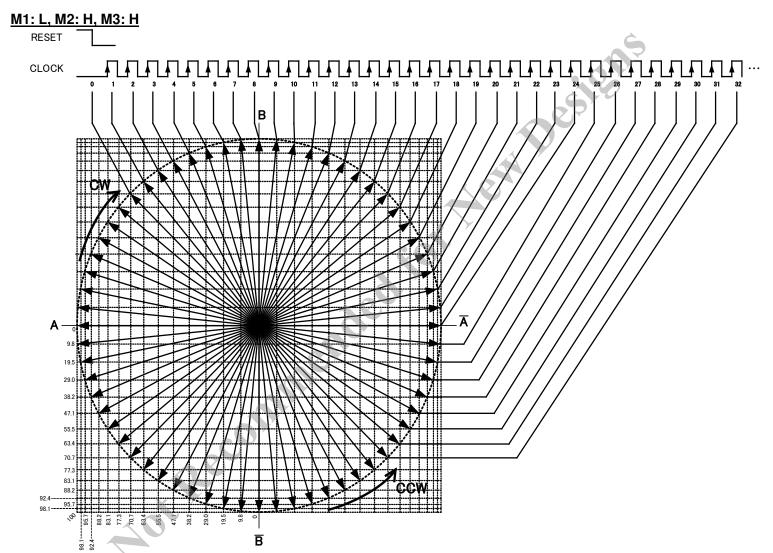

## 12. Step Sequence Diagrams

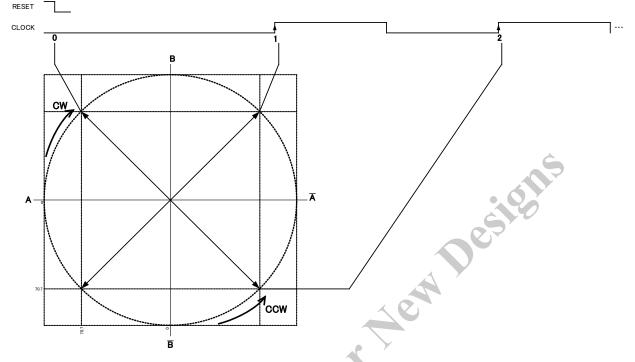

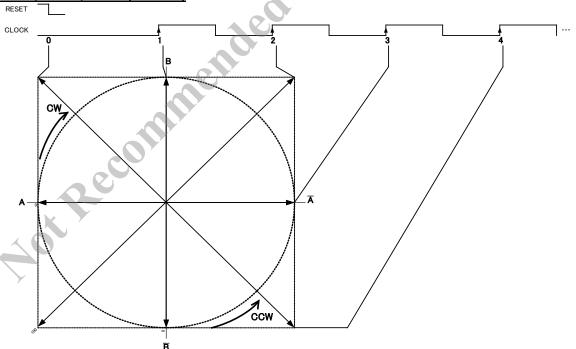

Figure 12-1. Full Step (2 Phase Excitation)

### M1: L, M2: L, M3: L (Mode 8)

### M1: H, M2: L, M3: L (Mode F)

Figure 12-2. Half Step (1-2 Phase Excitation)

### M1: L, M2: H, M3: L (1 Phase: Mode F / 2 Phase: Mode 8)

### M1: H, M2: H, M3: L (Mode F)

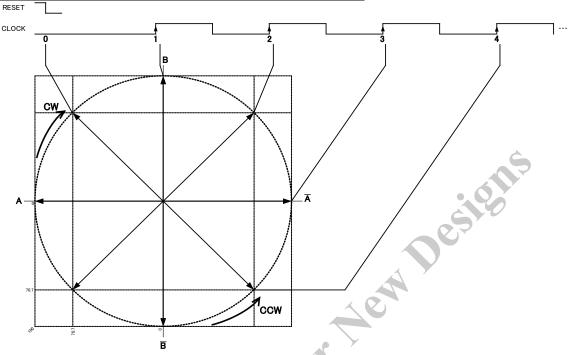

Figure 12-3. Quarter Step (W1-2 Phase Excitation); for microstep product only

Figure 12-4. Eighth Step (2W1-2 Phase Excitation); for microstep product only

#### **Excitation Change Sequence**

The change of excitation modes is determined by the settings of the excitation pins (M1, M2, and M3) before and after a step signal. Table 12-1 shows each excitation mode state setting.

Internal Sequence State1) W1-2 Phase PWM Mode PWM Mode 8 Mode 8/F 1/8 Step /16 Step ΧХ ΧХ В Α В D В В Ε В F В В В В CCW В В В В Α В 9 ΧХ ΧХ В 8 В В В Χ -/B /B 2 /B Χ /B /B /B 6 /B ΧХ 8 /B /B Α /B /B /B, /B 9 /B ΧХ ΧХ /B 8 /B 7 /B /B

Table 12-1. Excitation Mode States

/B /B /B

<sup>1)</sup> Each mode is defined accordingly to the SLA7070M series.

<sup>&</sup>lt;sup>2)</sup> **XX** indicates that sequence state is Mode 8; but step reference current ratio is Mode F. Mode F has a step reference current ratio of 100%, and a PWM OFF-time of 12 μs.

## 13. Individual Circuit Descriptions

#### (1) Monolithic IC (MIC)

#### Sequencer Logic

A single clock strategy is employed for step timing. An input on the CW/CCW pin determines the direction of motor rotation. Excitation mode is controlled by the combination of the M1, M2, and M3 input logic levels. See Section 9 for truth tables, and Section 11 for input timings.

#### • DAC (D-to-A Converter)

DACs that generate the reference voltage for controlling current. In microstep sequencing, the current at each step is set by the values of a sense resistor  $(R_S)$ , a reference voltage  $(V_{REF})$ , the output voltage of the DACs, controlled by the output of the sequencer/translator circuit. For the step reference current ratios, see the electrical characteristics tables given in Section 4.

#### · PWM Control

Circuits that allow self-excitation PWM current controlling with a fixed OFF-time are used in this series. Each built-in oscillator (OSC) determines an OFF-time and a blanking time for proper PWM operation. The operation mechanism of the PWM control circuitry is identical to that of the SLA7070M family. For more detailed functional descriptions, see Section 14.

#### · Synchronous Control

A synchronous chopping circuit that prevents occasional motor noise during a hold state which normally results from the asynchronous PWM operation of both motor phases. When the SYNC input pin is set to logic high, the circuit sends a timing signal that simultaneously turns off the chopping of phases A and B.

This function adopts the same operation mechanism applied to the SLA7070M series. Therefore, the use of the synchronous control during normal stepping is not recommended because, it produces less motor torque or may cause motor vibration due to staircase current.

The use of the synchronous control when the motor is not in operation is only allowed in 2-phase excitation timing, because the differences in current control values and PWM OFF-times between phases A and B exist at other excitation timings; otherwise, these two phases may not be synchronized or may be greatly disrupted in their current control values.

#### Regulator Circuit

An integrated regulator circuit is used for powering the output MOSFET gate drive circuit (pre-driver) and other internal linear circuits.

### Protection Circuit

Built-in protection circuits against motor coil opens or shorts are provided. This protection is activated by sensing the voltage across internal sense resistors, Rs. Therefore, an overcurrent condition cannot be detected which results from the OUTx pins or SENSEx pins, or both, shorting to GND. The protection against motor coil opens is available only during PWM operation; therefore, it does not work at constant voltage driving, when the motor is rotating at a high speed.

The operation of the protection circuit disables all outputs. To come out of the Protection mode, cycle the logic supply,  $V_{DD}$ . For more details, see the next section.

#### TSD Circuit

A TSD circuit that protects a driver by shifting an output to the Disable mode is incorporated. When the temperature of the product control IC (MIC) rises and becomes higher than its threshold, the circuit starts operating. To reset the function, perform the same steps as described in the Protection Circuit description.

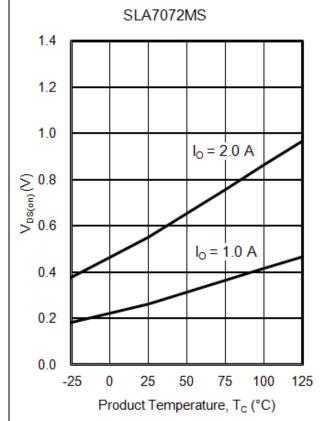

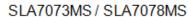

### (2) Output MOSFET Chip

The type of MOSFET chips to be mounted varies according to which of the two different output current ratings has been selected. For specifications, see Table 4-5.

| Rated Current (A) | Resistance<br>(ΩTyp.) |  |

|-------------------|-----------------------|--|

| 2.0               | 0.25                  |  |

| 3.0               | 0.18                  |  |

**NOTE:** Each resistance shown above includes approximately 5 m $\Omega$  circuit resistance in addition to the resistance of the built-in resistor itself.

#### (3) Sense Resistor

Sense resistors are incorporated in this series to detect motor current. The resistance of these varies according to which of the two different output current ratings has been selected. For specifications, see Table 4-5.

| Rated Current (A) | Resistance<br>(ΩTyp.) |  |

|-------------------|-----------------------|--|

| 2.0               | 0.205                 |  |

| 3.0               | 0.155                 |  |

NOTE: Each resistance shown above includes approximately 5 m $\Omega$  circuit resistance in addition to the resistance of the built-in resistor itself.

## 14. Functional Descriptions

- (1) PWM Current Control

- [1] Blanking Time

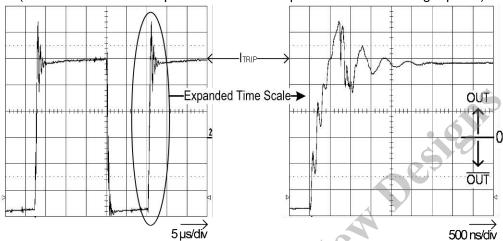

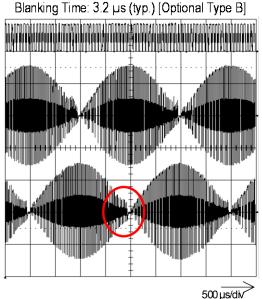

An actual operating waveform on the SENSEx pin when driving a motor is shown in Figure 14-1.

Figure 14-1. Operating Waveform on SENSEx Pin during PWM Chopping (Circled area of the left panel is shown in expanded scale in the right panel)

Immediately after a PWM turns off, ringing (or spike) noise on the SENSEx pin is observed for a period of a few microseconds. Ringing noise can be generated by various causes, such as capacitance between motor coils or inappropriate motor wiring.

Each pair of outputs is controlled by a fixed OFF-time PWM current-control circuit that limits the load current to a target value, I<sub>TRIP</sub>. Initially, an output is enabled and then currents flow through the motor winding and the current sense resistors. When the voltage across the current sense resistors equals the DAC output voltage, V<sub>TRIP</sub>, the current sense comparator resets a PWM latch. This turns off the driver for the fixed OFF-time, during which the load inductance causes the current to recirculate for the OFF-time period. Therefore, if the ringing noise on the current sense resistor(s) equals and surpasses V<sub>TRIP</sub>, the PWM turns off (i.e., a hunting phenomenon).

To prevent this phenomenon, a blanking time is set to override signals from the current sense comparator for a certain period immediately after the PWM turns on (Figure 14-2).

Figure 14-2. SENSEx Pin Waveform Pattern during PMW Control

PWM Pulse Width

ON

OFF (Fixed)

A

Blanking Time

Sanken Electric Co., Ltd.

### [2] Blanking Time and Hunting Phenomenon

Although current control can be improved by shortening a blanking time, the degree of margin to a ringing noise decreases simultaneously. For this reason, when a motor is driven by the device, a hunting phenomenon may occur. Figure 14-3 shows an example of the waveform pattern when the phenomenon occurs.

In order to overcome this problem, Sanken has released a new option, "type B", which offers a longer blanking time. Having the longer blanking time, the optional type B can improve problems such as torque reduction and huge motor noise that are occasionally found during the hunting phenomenon.

Figure 14-3. Example of SENSEx Pin Waveform during Hunting Phenomenon

### [3] Blanking Time Difference

Table 14-1 shows characteristic differences between two blanking times, shorter and longer blanking periods.

This comparison is based on the case where drive conditions, such as a motor, motor power supply voltage, REF input voltage, and circuit constant were kept the same while only the indicated parameters were changed.

Table 14-1. Characteristic Comparison of Difference in Blanking Time

| Table 11 1: Characteriotic Companion of Emercines in Elamining Time    |                    |         |  |  |  |

|------------------------------------------------------------------------|--------------------|---------|--|--|--|

| Parameter                                                              | Better Performance |         |  |  |  |

| Internal blanking time                                                 | Short              | Long    |  |  |  |

| Minimum PWM ON-time                                                    | Small ←            |         |  |  |  |

| Ringing noise suppression                                              |                    | → Large |  |  |  |

| Minimum coil current                                                   | Small <b>←</b>     |         |  |  |  |

| Coil current waveform distortion at a high rotation (mainly microstep) |                    | Large   |  |  |  |

Brief descriptions for each parameter are as follows:

Minimum PWM ON-time, toN(min)

This series has a blanking time that is effectively selected and fixed by the PWM control. Therefore, even if an application attempts to shorten its ON-time for limiting currents, it would not go below the fixed blanking time. Minimum PWM ON-time refers to the time when an output is on during this blanking time period, that is, when an output MOSFET is actually turned on. In other words, a blanking time determines a minimum ON-time ("Small" in Table 14-1).

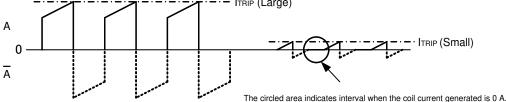

· Minimum Coil Current

This refers to the coil current when the PWM control is performed during a minimum PWM ON-time. In other words, the device with a shorter blanking time can reduce more coil current.

· Coil Current Waveform Distortion during High-Velocity Revolution

While a microstep drive is active, the I<sub>TRIP</sub> value changes to a predetermined value in accordance with a clock input. The I<sub>TRIP</sub> value (internal reference voltage splitting ratio) is then set up to be a sine wave. Because the PWM control of motor coil current is set according to the I<sub>TRIP</sub> value, (the envelope of) the motor coil current will also be controlled to be sine wave-like.

In fact, due to the inductance characteristic of the coil, the device requires some time to bring the coil current completely to a targeted value ( $I_{TRIP}$ ).

Roughly, the relationship between the convergence time  $(t_{conv})$ , a time until the coil current settles to its  $I_{TRIP}$  value, and the duty cycle  $(t_{clk})$  of an input clock pulse in any mode is

$$t_{CONV} < t_{clk}$$

,

where the coil current waveform amplitude serves as the limit for ITRIP.

When the current attempts to increase, the full limit of t<sub>conv</sub> is determined by power supply voltage and the time constant of the motor coil used. While the current attempts to decrease, the full limit is determined by the power supply voltage, the damping time constant of the motor coil used, and the minimum ON-time.

The duty cycle (t<sub>clk</sub>) is determined by the frequency of an input clock. It becomes smaller as the frequency of the input clock increases. When the frequency of the input clock is raised, because t<sub>clk</sub> becomes small, it is normal that the coil current cannot be raised to the I<sub>TRIP</sub> value within a single clock period. In this situation, the waveform amplitude of the coil current degenerates from the sine wave, referred to as "waveform distortion."

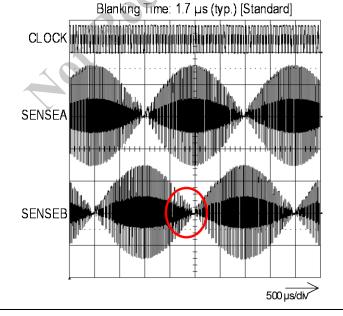

Figure 14-4 illustrates the comparison result of waveform distortions. Devices with different blanking times were compared under the operating conditions that power supply voltages, current preset values, motors, and so forth were kept the same.

As shown in the areas circled (blanking times) in the figure below, the amplitude envelope of the SENSEx pin waveform in the 1.7  $\mu s$  case, which is the same as the current waveform, has become sine wave-like whereas the waveform in the 3.2  $\mu s$  blanking time case has degenerated from an ideal sine wave.

The meaning of the team "Large" in Table 14-1 is as follows: if making a comparison under the same operating conditions, the device with a longer blanking time will result in less waveform distortion due to a lower clock frequency. But if the clock frequency is the same, waveform distortion will be larger due to a shorter blanking time. Even if such distortion is observed, it does not always mean that the motor characteristics will be negatively affected. Therefore, thorough evaluations should be carried out to make an informed decision.

Figure 14-4. Comparison of SENSEx Pin Waveforms during High-Speed Revolution

#### [4] PWM OFF-time

PWM OFF-time for the SLA7070MS series is controlled at a fixed time generated by the corresponding internal oscillator. It also is switched in three levels by step current reference ratios. (See Table 4-4 for more details.)

In addition, the SLA7070MS series provides a function that decreases power losses occurring when the PWM turns off. This function dissipates the back EMF stored in the motor coil at MOSFET turn-on, as well as at PWM turn-on (synchronous rectification operation).

Figure 14-5 explains differences between two back EMF generation mechanisms. Whereas the older version of our product series only performs ON/OFF operations using a MOSFET on the PWM-ON side, the SLA7070MS series can perform ON/OFF operations using a MOSFET on the PWM-OFF side.

To prevent simultaneous switching of the output MOSFETs at the synchronous rectification operation, the IC has a dead time of approximately 0.5 µs. During the dead time, the back EMF flows through the body diodes of the MOSFETs.

Figure 14-5. Difference in Back EMF Generation

Synchronous Rectification Operation

Voc

Virs

PWM ON

PWM OFF

PWM ON

FET Gate Signal

Virs

Sense Voltage

Virs

Sense Voltage

Virs

Virs

Sense Voltage

Virs

Virs

Virs

Virs

Sense Voltage

Virs

Virs

Virs

Virs

Virs

Sense Voltage

Virs

Sanken Electric Co., Ltd.

Back EMF flows through the body diode of MOFSET during dead time.

#### (2) Protection Functions

The SLA7070MS series includes a motor coil short protection circuit, a motor coil open protection circuit, and an overheat protection circuit. Detailed explanations of each protection circuit are provided below.

#### [1] Motor Coil Short Protection (Load Short) Circuit

This protection circuit, embedded in the SLA7070MS series, begins to operate when the device detects an increase in the sense resistor voltage,  $V_{RS}$ . The threshold voltage of this protection circuit,  $V_{OCP}$ , is set at approximately 0.7 V. Outputs are disabled at a time when this protection circuit starts, where  $V_{RS}$  exceeds  $V_{OCP}$ .

Coil Short Circuit

Value of the state of th

Figure 14-6. Motor Coil Short Protection Circuit Operation

#### **NOTES:**

- Overcurrent that flows without passing the sense resister is undetectable.

- To recover the circuit after the protection operates, V<sub>DD</sub> must be cycled and started up again.

#### [2] Motor Coil Open Protection Circuit (Patent acquired)

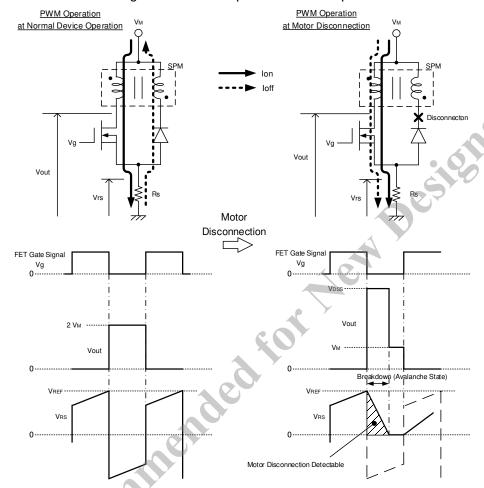

Driver destruction can occur when one output pin (motor coil) is disconnected in unipolar drive operation. This is because a MOSFET connected after disconnection will be in an avalanche breakdown state, where very high energy is added with back EMF when PWM is off. With the avalanche state, an output cancels the energy stored in the motor coil where the resisting pressure between the drain and source of the MOSFET is reached (i.e., the condition in which the breakdown occurred).

Although MOSFETs with a certain amount of an avalanche energy tolerance rating are used in the SLA7070MS series, the avalanche energy tolerance falls as a temperature increases.

Because high energy is added repeatedly whenever PWM operation disconnects the MOSFET, the temperature of the MOSFET rises; and when the applied energy exceeds the tolerance, the driver will be destroyed. Therefore, a circuit which detects this avalanche state and protects the driver is added in the SLA7070MS series.

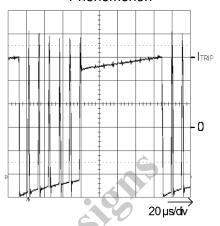

As explained above, when the motor coil is disconnected, accumulated voltage in the MOSFET causes a reverse current to flow during a PWM OFF-time. For this reason, VRS that is negative during a PWM OFF-time in normal operation becomes positive when the motor coil is disconnected. Thus, the disconnected motor is detectable by sensing that VRS in the PWM OFF-time is positive.

In order to avoid detection malfunctions, the SLA7070MS series actuates a dedicated protection function, the motor coil open protection circuit, when the motor disconnection state is detected three times continuously (see Figure 14-7).

Figure 14-7. Coil Open Protection Operation

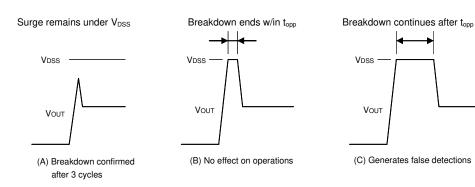

**NOTE:** In addition to requiring three breakdown cycles to confirm the open circuit condition, the SLA7070MS series provides a fixed delay, an overload disconnection undetected time  $(t_{opp})$ , before the protection is activated. This is to avoid false detections, which can be occurred by surge noise after PWM turn-off, causing an unwanted operation of the function even when the load is not actually disconnected. The figure below describes alternative  $t_{opp}$  scenarios. If a total period of breakdown time exceeds  $t_{opp}$ , the device shuts down the output. If this is the case, check the motor and wiring layout to reduce surge noise. Shortening the breakdown time will allow the protection circuit to function properly. (Variation among device variants and applications should be taken into consideration.) When there is no actual breakdown, normal operations will continue. One possible solution is adding a capacitor between the OUTx and GND pins, which could damp the surge noise sufficiently.

#### [3] Overheat Protection Circuit

When a product temperature rises and exceeds  $T_{tsd}$ , this protection circuit starts operating and sets all outputs to be disabled.

NOTE: This product series has multichip composition (one IC for control, four MOSFETs, and two chip resistors). Although main heat sources are the MOSFETs and chip resisters, the location which actually detects temperature is the control IC (MIC). Separated from these main heat sources, the control IC cannot detect a rapid temperature change. Accordingly, perform worst-case thermal evaluations, in which junction temperatures must not exceed a guaranteed value of 150°C, in your application design phase.

## 15. Application Information

### (1) Motor Current Ratio Setting

The motor current, Io, for the SLA7070MS series is determined by the values chosen for the external components, R1 and R2, and the current sense resistors,  $R_S$ , in the case of the sample application circuit shown in Figure 8-1. The formula to calculate Io is shown below:

$$Io = \frac{R2}{R1 + R2} \times V_{DD} / Rs.$$

(1)

The double-underlined term represents the reference voltage,  $V_{\text{REF}}$ .

If V<sub>REF</sub> is set below 0.1 V, the accuracy of IO setting is more likely to be degraded due to the variation between individual devices and/or the impedance of application trace layout.

The standard voltage for current ITRIP that the SLA7070MS series controls is partially divided by internal DACs:

$$I_{TRIP} = \frac{V_{REF}}{R_S} \times \text{ (Mode Proportion)}.$$

(2)

#### (2) Lower Limit of Control Current

The SLA7070MS series uses a self-oscillating PWM current-control topology in which an OFF-time is fixed. As energy stored in a motor coil is eliminated within the fixed PWM OFF-time, coil current flows intermittently, as shown in Figure 15-1. Thus, average current decreases as well as motor torque decreases. The point at which current starts flowing to the coil is considered as the lower limit of the control current,  $I_{O(min)}$ , where  $I_{OUT}$  is a target current level.

The lower limit of control current differs by application conditions of the motor or other factors, but it can be calculated from the following formula:

$$I_{O(\min)} = \frac{V_M}{R} \left( \frac{1}{\exp\left(-t_{OFF}/t_C\right)} - 1 \right), \quad \text{with } t_C = \frac{L_m}{R}, \text{ and }$$

$$R = R_m + R_{DS(on)} + R_S.$$

(3)

Where:

$V_M$  is the motor supply voltage,

RDS(on) is the MOS FET on-resistance,

R<sub>m</sub> is the motor winding resistance,

L<sub>m</sub> is the motor winding inductance,

toff is the PWM OFF-time, and

Rs is the current sense resistor.

Even if the control current value is set at less than its lower limit, there is no setting at which the IC fails to operate. However, the control current will worsen against its target current.

Figure 15-1. Model Waveform of Control Current Lower Limit

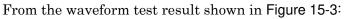

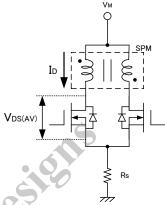

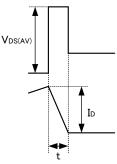

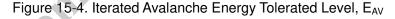

### (3) Avalanche Energy

In the unipolar topology of the SLA7070MS series, a surge voltage (ringing noise) that exceeds the MOSFET capacity to withstand might be applied to the IC. To prevent damage, the SLA7070MS series is designed with built-in MOSFETs having sufficient

avalanche resistance to withstand this surge voltage. Therefore, even if surge voltages occur, users will be able to use the IC without any problems.

However, in case the motor harness used is too long or the IC is used above its rated current or voltage, there is a possibility that an avalanche energy could be applied that exceeds Sanken design expectations. Thus, users must test the avalanche energy applied to the IC under actual application conditions.

The following procedure can be used to check the avalanche energy in an application. Figure 15-2 and Figure 15-3 show test points and waveform characteristics resultant, respectively.

$$\begin{split} V_{DS(AV)} &= 140 \text{ V}, \\ I_D &= 1 \text{ A, and} \\ t &= 0.5 \text{ } \mu s. \end{split}$$

The avalanche energy, E<sub>AV</sub>, then can be calculated using the following formula:

$$\begin{split} E_{\text{AV}} &\approx V_{\text{DS(AV)}} \times 1/2 \times I_{\text{D}} \times t \\ &= 140 \text{ (V)} \times 1/2 \times 1 \text{ (A)} \times 0.5 \times 10^{-6} \text{ (\mu s)} \\ &= 0.035 \text{ (mJ)}. \end{split} \tag{4}$$

By comparing the calculated E<sub>AV</sub> values with the graph shown in Figure 15-4, the application can be evaluated if it is safe for the IC by being within the avalanche energy-tolerated dose range of the MOFSETs.

Figure 15-2. Test Points

Figure 15-3. Waveform at Avalanche Breakdown

### (4) ON/OFF Sequence of Power Supply (V<sub>BB</sub> and V<sub>DD</sub>)

There is no restriction for the ON/OFF sequences of the main power supply,  $V_{BB}$ , and the logic supply,  $V_{DD}$ .

### (5) Motor Supply Voltage (V<sub>M</sub>) and Main Power Supply Voltage (V<sub>BB</sub>)

Because the SLA7070MS series has a structure that separates the contorl IC (MIC) and the power MOSFETs as shown in Figure 7-1, the motor supply and the main power supply are electrically separated. Therefore, it is possible to drive the IC with using different power supplies and different voltages for the motor supply and the main power supply.

### (6) Internal Logic Circuits

#### a. Reset for the Internal Sequencer

The sequencer/translator circuit embedded in this product series is initialized by the built-in power-on reset function, which is activated at a time when the logic supply (V<sub>DD</sub>) is applied. Therefore, the output immediately after power-on indicates a status that the power circuits are in the home state.

When the sequencer/translator must be reset after the motor has been operating, a signal must be input on the RESET pin. When external reset controlling is not necessary and the RESET pin is not used, the RESET pin must be pulled to logic low on an application circuit board.

#### b. Clock Input

The SLA7070MS series is designed to move one sequence increment at a time when a clock pulse edge is detected. And there are two different types of sequencer timings: positive-edge-triggered (standard type, active at a rising edge) and double-edge-triggered (optional type W, active at a rising edge and a falling edge).

When a clock input signal stops, the present excitation state enters the motor hold state. At this time, there is no difference to the IC if the clock input signal is at low level or high level.

### c. Chopping Synchronous Circuit

The SLA7070MS series has a chopping synchronous function to protect from abnormal noises that may occasionally occur during the motor Hold mode. This function can be operated by setting the SYNC pin at high level. However, if this function is used during motor rotation, control current does not stabilize; and that may result in reduced motor torque and/or increased vibration.

Note that the synchronous circuit should be disabled to control the motor current properly even when it is used in other than the 2-phase excitation state (Modes 8 and F) or the 1-phase excitation hold state.

In normal operation, an external microcomputer sends an input signal for switching. However, in applications where any input signals cannot be transmitted adequately due to a limited number of ports, the following method can be taken to use the function.

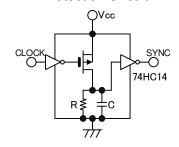

The schematic diagram in Figure 15-5 shows how the IC is designed so that a signal on the SYNC pin can be determined by an input signal on the CLOCK pin.

Figure 15-5. Clock Signal Shutoff Detection Circuit

Figure 15-6. Clock Signal Edge Detection Circuit

When the CLOCK pin receives a logic high signal, the internal capacitor, C, is charged, and the SYNC pin signal is set to logic low. However, if the input signal on the CLOCK pin cannot rise above a logic low level, the capacitor is discharged by the internal resistor, R, and the SYNC pin signal is set to logic high, causing the IC to shift to the synchronous mode. RC time constant in this circuit should be determined by the minimum clock frequency used.

When using a sequence that keeps an input signal on the CLOCK pin at logic high, an inverter circuit must be added.

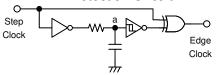

When the CLOCK pin signal is set at an undetermined level or when using a POS/NEG edge product (optional type W), an edge detection circuit (Figure 15-6) can be added to prepare a proper clock input signal, allowing correct processing by the circuit illustrated in Figure 15-5.

#### d. Output Disable Circuits (Sleep1 and Sleep2)

There are two methods to set the IC to a motor free-state (coast, with outputs disabled). One is to set the REF pin to more than 2 V (Sleep1). And the other is to set all the excitation mode setting pins (M1, M2, and M3) to high (Sleep2). In either way, the IC is put into the Sleep mode, which stops the main power supply and reduces circuit current.

The difference between the two methods is that the Sleep1 keeps the internal sequencer enabled, whereas the Sleep2 puts the internal sequencer into a hold state. That is to say, in the Sleep2 mode, the excitation sequence remains in the hold state even after a signal is input on the CLOCK pin.

When awaking to normal operation mode (motor rotation) from the Disable (Sleep1 or Sleep2) mode, set an appropriate delay time, i.e., a time period from cancellation of the Disable mode to an initial clock input edge. In doing so, consider not only a rise time for the IC, but also a rise time for the motor excitation current, which is important (Figure 15-7).

Figure 15-7. Timing Delay between Disable Mode Cancellation and the Next Clock Input

**NOTE:** In applications where POS/NEG edge (optional type W) products are used, the initial clock signal after the Disable mode cancellation can be a high-to-low transition.

#### e. REF/SLEEP1 Pin

The REF pin provides access to the following functions:

[1] Reference voltage setting for output current level setting:

Low level ( $V_{REF} \le 0.4$  to 0.45 V, depends on rated currents)

[2] Output Enable-Disable control input:

High level ( $V_{REF} \ge 2.0 \text{ V}$ )

These functions are further described in Section 9, and in the discussion of output disabling, above. Moreover, the threshold voltage to switch the output enable-disable signals is set to approximately 1.75 V.

To control the REF voltage, pay attention to the following points:

**Range A** – Control current value varies in accordance with  $V_{REF}$ , not only within the range specified in [1], but also within the range from [1] to the threshold voltage (typically 1.75 V). Therefore, power dissipation in the IC and the sense resistors must be given extra consideration. In addition, note that OCP operation may start depending on the reference voltage splitting ratio.

**Range B** — In this range, the voltage that switches output enable and disable exists. At enable, the same cautions apply as in  $Range\ A$ . For some cases, there are possibilities that an output status will become unstable as a result of iterations between enable and disable states.

### f. Logic Input Pins (CLOCK, RESET, CW/CCW, M1, M2, M3, and SYNC)

When a logic input pin (CLOCK, RESET, CW/CCW, M1, M2, M3, or SYNC) is not used, the pin must be tied to  $V_{DD}$  or GND. Do not leave any of these pins floating, because there is possibility of undefined effects on IC performance if they are left open.

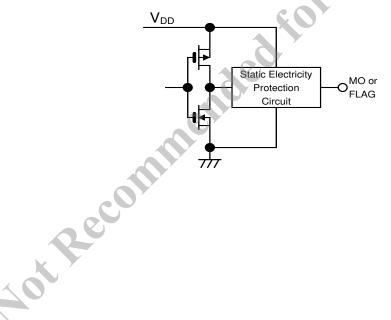

#### g. Monitor Output Pins (MO and FLAG)

The MO and FLAG pins are designed as monitor outputs. Moreover, the IC consists of <u>an inverter output</u> configuration, as shown in Figure 15-8. Therefore, let these pins open when they are not used.

Figure 15-8. MO/FLAG Pin General Internal Circuit Layout

## 16. Thermal Design Information

It is not practical to calculate the power dissipation of the SLA7070MS series accurately, because that would require factors that are variable during operation, such as time periods and excitation modes during motor rotation, input frequencies and sequences, and so forth.

Given this situation, it is preferable to perform approximate calculations at worst conditions. The following is a simplified formula for the calculation of power dissipation using extracted minimum necessary parameters:

$$P = I^2 \times (R_{DS(on)} + Rs) \times 2,$$

where:

P is the power dissipation in the IC,

I is the operation current ( $\approx I_0$ ),

RDS(on) is the on-resistance of the output MOSFET, and

Rs is the current sense resistance.

Based on the power dissipation in the IC calculated using the above formula, the expected increase in operating junction temperature,  $\Delta T_J$ , of the IC can be estimated using Figure 16-1. This result should be added to the worst-case ambient temperature when operating,  $T_{A(max)}$ . Based on the calculation, there is no problem unless  $T_{A(max)} + \Delta T_J > 150$  °C. However, final confirmation should be made by measuring the IC temperature during operation and then verifying power dissipation and junction temperature in the corresponding graph in Figure 16-1.

150 ncrease in Temperature, ∆T (°C)  $\Delta T_{I-A} = 26.6 \times P_D$ 125 100 75  $\Delta T_{C-A} = 21.3 \times P_D$ 50 25 0.5 0.0 1.0 5.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 Allowable Package Power Dissipation, PD (W)

Figure 16-1. Temperature Increase

When the IC is used with a heatsink mounted, product package thermal resistance,  $\theta_{J-A}$ , is a variable used in calculating  $\Delta T_{J-A}$ . The value of  $\theta_{J-A}$  is calculated from the following formula:

$$\theta_{\text{J-A}} \approx \theta_{\text{J-C}} + \theta_{\text{FIN}} = (\theta_{\text{J-A}} - \theta_{\text{C-A}}) + \theta_{\text{FIN}}$$

where  $\theta_{FIN}$  is the thermal resistance of the heatsink. Then,  $\Delta T_{J-A}$  can be calculated with using the value of  $\theta_{J-A}$ .

The following procedure should be used to measure product temperature and to estimate junction temperature in actual operation.

First, measure a temperature rise in the center of backside of mold resin used for the device ( $\Delta T_{C-A}$ ).

Second, estimate power dissipation (P) and junction temperature ( $T_J$ ) from the temperature rise with reference to Figure 16-1, the Temperature Increase graph. At this point, the device temperature rise ( $\Delta T_{C-A}$ ) and the junction temperature rise ( $T_J$ ) become almost equivalent in the following formula:

$\Delta T_{\rm J} \approx \Delta T_{\rm C-A} + P \times \theta_{\rm J-C}$ .

and Recommen

### **CAUTION**

The SLA7070MS series is designed as a multichip, consisting of four separate power elements (MOSFETs), one control IC (MIC), and two sense resistors. Moreover, because the monolithic IC cannot accurately detect the temperature of the built-in power elements, which are the primary sources of heat, the SLA7070MS series does not provide a protection function against overheating. For thermal protection, users must conduct sufficient thermal evaluations to ensure that the junction temperature of the IC does not exceed a guaranteed level of 150°C.