## Features

- 8-bit High Speed Single/ Dual/ Quad ADC Single Channel Mode: FSmax = 500 MSPS Dual Channel Mode: FSmax = 250 MSPS Quad Channel Mode: FSmax = 125 MSPS

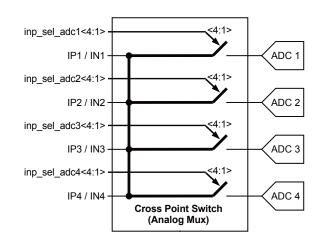

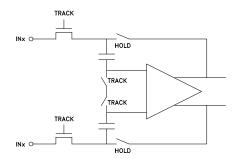

- Integrated Cross Point Switches (Mux Array)

- 1X to 50X Digital Gain. No Missing Codes up to 32X

- 1X Gain: 49.8 dB SNR. 10X Gain: 48 dB SNR

- Internal Low Jitter Programmable Clock Divider

- Ultra Low Power Dissipation 295 mW Including I/O at 500 MSPS and Reduced Bias

- 0.5 μs Start-up Time From Sleep, 15 μs From Power Down

- Internal Reference Circuitry with no External Components Required

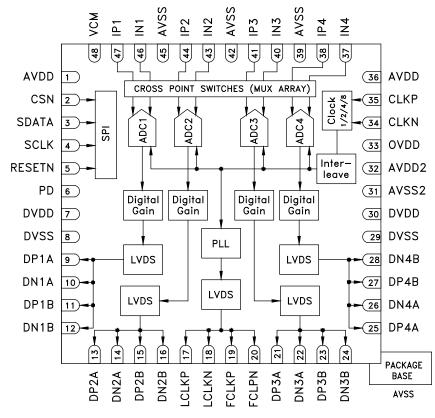

**Functional Diagram**

# HMCAD1510

## HIGH SPEED MULTI-MODE 8-BIT 30 то 500 MSPS A/D CONVERTER

- Coarse and Fine Gain Control

- Digital Fine Gain Adjustment for each ADC

- Internal Offset Correction

- 1.8V Supply Voltage

- 1.7 3.6V CMOS Logic on Control Interface Pins

- Serial LVDS/RSDS Output

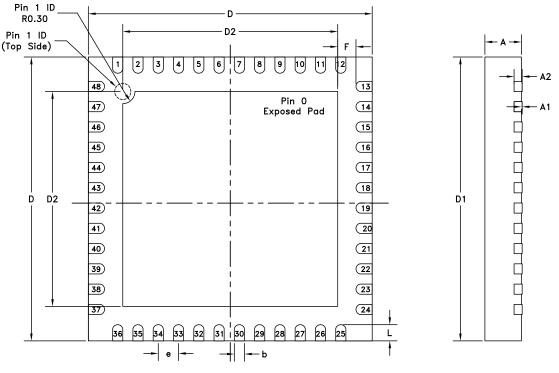

- 7 x 7 mm QFN 48 (LP7D) Package

## **Typical Applications**

- USB Powered Oscilloscopes

- Digital Oscilloscopes

- Satellite Receivers

## Pin compatible parts

HMCAD1510 is pin compatible with HMCAD1511 and HMCAD1520

#### Figure 1. Functional Block Diagram

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

For price, delivery, and to place orders: Analog Devices, Inc., One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 Phone: 781-329-4700 • Order online at www.analog.com Application Support: Phone: 1-800-ANALOG-D

0 - 1

# ROHS V

## HIGH SPEED MULTI-MODE 8-BIT 30 to 500 MSPS A/D CONVERTER

**HMCAD1510**

## **General Description**

The HMCAD1510 is a versatile high performance low power analog-to-digital converter (ADC), utilizing time-interleaving to increase sampling rate. Integrated Cross Point Switches activate the input selected by the user.

In single channel mode, one of the four inputs can be selected as a valid input to the single ADC channel. In dual channel mode, any two of the four inputs can be selected to each ADC channel. In quad channel mode, any input can be assigned to any ADC channel.

An internal, low jitter and programmable clock divider makes it possible to use a single clock source for all operational modes.

The HMCAD1510 is based on a proprietary structure, and employs internal reference circuitry, a serial control interface and serial LVDS/RSDS output data. Data and frame synchronization clocks are supplied for data capture at the receiver. Internal 1 to 50X digital coarse gain with ENOB > 7.5 up to 16X gain, allows digital implementation of oscilloscope gain settings. Internal digital fine gain can be set separately for each ADC to calibrate for gain errors.

Various modes and configuration settings can be applied to the ADC through the serial control interface (SPI). Each channel can be powered down independently and data format can be selected through this interface. A full chip idle mode can be set by a single external pin. Register settings determine the exact function of this pin.

HMCAD1510 is designed to easily interface with Field Programmable Gate Arrays (FPGAs) from several vendors.

## **Electrical Specifications**

#### **DC** Specifications

AVDD = 1.8V, DVDD = 1.8V, OVDD = 1.8V, FS = 125 MSPS, Quad Channel Mode, 50% clock duty cycle, -1 dBFS 70 MHz input signal, 1x/0 dB digital gain (fine and coarse), unless otherwise noted

| Parameter           | Description                                                             | Min                  | Тур                  | Max                  | Unit |

|---------------------|-------------------------------------------------------------------------|----------------------|----------------------|----------------------|------|

| DC accuracy         |                                                                         |                      |                      |                      |      |

| No missing codes    | sing codes                                                              |                      |                      |                      |      |

| Offset              | Offset error after internal digital offset correction                   |                      | 0.05                 |                      | LSB  |

| G <sub>abs</sub>    | Gain error                                                              |                      |                      | ±6                   | %FS  |

| G <sub>rei</sub>    | Gain matching between channels. ±3 sigma value at worst case conditions |                      | ±0.5                 |                      | %FS  |

| DNL                 | Differential non linearity                                              |                      | ±0.2                 |                      | LSB  |

| INL                 | Integral non linearity                                                  |                      | ±0.5                 |                      | LSB  |

| V <sub>CM,out</sub> | Common mode voltage output                                              |                      | V <sub>AVDD</sub> /2 |                      |      |

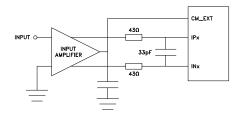

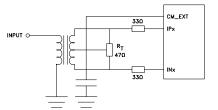

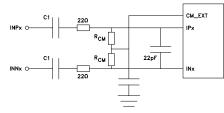

| Analog Input        |                                                                         |                      |                      |                      |      |

| V <sub>CM,in</sub>  | Analog input common mode voltage                                        | V <sub>CM</sub> -0.1 |                      | V <sub>CM</sub> +0.2 | V    |

| FSR                 | Differential input voltage full scale range                             |                      | 2                    |                      | Vpp  |

| C <sub>in,Q</sub>   | Differential input capacitance, Quad channel mode                       |                      | 5                    |                      | pF   |

| C <sub>in,D</sub>   | Differential input capacitance, Dual channel mode                       |                      | 7                    |                      | pF   |

| C <sub>in,S</sub>   | Differential input capacitance, Single channel mode                     |                      | 11                   |                      | pF   |

| Power Supply        |                                                                         |                      |                      |                      |      |

| V <sub>AVDD</sub>   | Analog Supply Voltage                                                   | 1.7                  | 1.8                  | 2                    | V    |

| V <sub>DVDD</sub>   | Digital and output driver supply voltage                                | 1.7                  | 1.8                  | 2                    | V    |

| V <sub>OVDD</sub>   | Digital CMOS Input Supply Voltage                                       | 1.7                  | 1.8                  | 3.6                  | V    |

| Temperature         | •                                                                       |                      |                      |                      |      |

| T <sub>A</sub>      | Operating free-air temperature                                          | -40                  |                      | 85                   | °C   |

|                     |                                                                         |                      |                      |                      |      |

A / D CONVERTERS - SMT

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

v03.0711

# ROHS V

## HIGH SPEED MULTI-MODE 8-BIT 30 TO 500 MSPS A/D CONVERTER

## AC Specifications

AVDD = 1.8V, DVDD = 1.8V, OVDD = 1.8V, 50% clock duty cycle, -1dBFS 70 MHz input signal, Gain = 1X, ADC current scaling -40%, RSDS output data levels unless otherwise noted

| Performance<br>SNR<br>SINAD <sub>incl</sub> | Signal to Noise Ratio, excluding interleaving spurs         Single Ch Mode , $F_s = 500$ MSPS         Single Ch Mode , $F_s = 500$ MSPS, Gain = 10X         Dual Ch Mode , $F_s = 250$ MSPS         Quad Ch Mode , $F_s = 125$ MSPS         Signal to Noise and Distortion Ratio, including interleaving spurs         Single Ch Mode , $F_s = 500$ MSPS         Dual Ch Mode , $F_s = 500$ MSPS         Dual Ch Mode , $F_s = 125$ MSPS         Dual Ch Mode , $F_s = 500$ MSPS         Dual Ch Mode , $F_s = 500$ MSPS         Dual Ch Mode , $F_s = 500$ MSPS | 48.5<br>48.5<br>48.5 | 49.9<br>48<br>49.8<br>49.7 | dBFS<br>dBFS<br>dBFS |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------|----------------------|

|                                             | Single Ch Mode , $F_s = 500$ MSPS         Single Ch Mode , $F_s = 500$ MSPS, Gain = 10X         Dual Ch Mode , $F_s = 250$ MSPS         Quad Ch Mode , $F_s = 125$ MSPS         Signal to Noise and Distortion Ratio, including interleaving spurs         Single Ch Mode , $F_s = 500$ MSPS         Dual Ch Mode , $F_s = 500$ MSPS                                                                                                     | 48.5                 | 48<br>49.8                 | dBFS                 |

| SINAD <sub>incl</sub>                       | Single Ch Mode , $F_s = 500$ MSPS, Gain = 10X         Dual Ch Mode , $F_s = 250$ MSPS         Quad Ch Mode , $F_s = 125$ MSPS         Signal to Noise and Distortion Ratio, including interleaving spurs         Single Ch Mode , $F_s = 500$ MSPS         Dual Ch Mode , $F_s = 500$ MSPS         Dual Ch Mode , $F_s = 500$ MSPS         Dual Ch Mode , $F_s = 250$ MSPS                                                                                                                                                                                       | 48.5                 | 48<br>49.8                 | dBFS                 |

| SINAD <sub>incl</sub>                       | Dual Ch Mode , $F_s = 250$ MSPS         Quad Ch Mode , $F_s = 125$ MSPS         Signal to Noise and Distortion Ratio, including interleaving spurs         Single Ch Mode , $F_s = 500$ MSPS         Dual Ch Mode , $F_s = 250$ MSPS                                                                                                                                                                                                                                                                                                                             |                      | 49.8                       |                      |

| SINAD <sub>incl</sub>                       | Quad Ch Mode , $F_s = 125$ MSPS         Signal to Noise and Distortion Ratio, including interleaving spurs         Single Ch Mode , $F_s = 500$ MSPS         Dual Ch Mode , $F_s = 250$ MSPS                                                                                                                                                                                                                                                                                                                                                                     |                      |                            | dBEG                 |

| SINAD <sub>incl</sub>                       | Signal to Noise and Distortion Ratio, including interleaving spurs<br>Single Ch Mode , F <sub>s</sub> = 500 MSPS<br>Dual Ch Mode , F <sub>s</sub> = 250 MSPS                                                                                                                                                                                                                                                                                                                                                                                                     | 48.5                 | 49.7                       |                      |

| SINAD <sub>incl</sub>                       | Single Ch Mode , $F_s = 500 \text{ MSPS}$<br>Dual Ch Mode , $F_s = 250 \text{ MSPS}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |                            | dBFS                 |

|                                             | Dual Ch Mode , F <sub>s</sub> = 250 MSPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |                            |                      |

|                                             | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      | 47                         | dBFS                 |

|                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      | 49.5                       | dBFS                 |

|                                             | Quad Ch Mode , $F_s = 125$ MSPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      | 49.6                       | dBFS                 |

| SINAD                                       | Signal to Noise and Distortion Ratio, excluding interleaving spurs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40                   | 40.4                       | 1050                 |

|                                             | Single Ch Mode , F <sub>s</sub> = 500 MSPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48                   | 49.4                       | dBFS                 |

|                                             | Single Ch Mode, $F_s = 500$ MSPS, Gain = 10X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40                   | 47.7                       | <br>dBFS             |

|                                             | Dual Ch Mode , F <sub>s</sub> = 250 MSPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 48                   | 49.5<br>49.6               | dBFS<br>dBFS         |

| SEDB                                        | Quad Ch Mode , F <sub>s</sub> = 125 MSPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40                   | 49.0                       |                      |

| SFDR                                        | Spurious Free Dynamic Range, including interleaving spurs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      | 40                         | <br>                 |

|                                             | Single Ch Mode , $F_s = 500$ MSPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      | 49                         | dBc                  |

|                                             | Dual Ch Mode , F <sub>s</sub> = 250 MSPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      | 59                         | dBc                  |

|                                             | Quad Ch Mode , F <sub>s</sub> = 125 MSPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      | 60                         | <br>dBc              |

| SFDR <sub>excl</sub>                        | Spurious Free Dynamic Range, excluding interleaving spurs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |                            |                      |

|                                             | Single Ch Mode , $F_s = 500 \text{ MSPS}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 56                   | 65                         | dBc                  |

|                                             | Single Ch Mode , F <sub>s</sub> = 500 MSPS, Gain = 10X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      | 65                         | dBc                  |

|                                             | Dual Ch Mode , $F_s = 250 \text{ MSPS}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 60                   | 69                         | dBc                  |

|                                             | Quad Ch Mode , F <sub>s</sub> = 125 MSPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 60                   | 69                         | dBc                  |

| HD2/3                                       | Worst of HD2/HD3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      |                            |                      |

|                                             | Single Ch Mode , $F_s = 500$ MSPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60                   | 67                         | dBc                  |

|                                             | Single Ch Mode , $F_s = 500$ MSPS, Gain = 10X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      | 65                         | dBc                  |

|                                             | Dual Ch Mode , $F_s = 250$ MSPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60                   | 70                         | dBc                  |

|                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60                   | 70                         | dBc                  |

|                                             | Quad Ch Mode , F <sub>s</sub> = 125 MSPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 00                   | 70                         | <br>UDC              |

| ENOB <sub>excl</sub>                        | Effective number of Bits, excluding interleaving spurs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |                            |                      |

|                                             | Single Ch Mode , F <sub>s</sub> = 500 MSPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      | 7.9                        | bits                 |

|                                             | Single Ch Mode , F <sub>s</sub> = 500 MSPS, Gain = 10X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      | 7.6                        | bits                 |

|                                             | Dual Ch Mode , F <sub>s</sub> = 250 MSPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      | 7.9                        | bits                 |

|                                             | Quad Ch Mode , F <sub>s</sub> = 125 MSPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      | 7.9                        | bits                 |

| X <sub>tik,2</sub>                          | CrossTalk Dual Ch Mode. Signal applied to 1 channel ( $F_{IN0}$ ). Measurement taken<br>on one channel with full scale at $F_{IN1}$ , $F_{IN1} = 71$ MHz, $F_{IN0} = 70$ MHz                                                                                                                                                                                                                                                                                                                                                                                     |                      | 65                         | dBc                  |

| X <sub>tik,4</sub>                          | CrossTalk Quad Ch Mode. Signal applied to 1 channel ( $F_{IN0}$ ). Measurement taken<br>on one channel with full scale at $F_{IN1}$ , $F_{IN1} = 71$ MHz, $F_{IN0} = 70$ MHz                                                                                                                                                                                                                                                                                                                                                                                     |                      | 70                         | dBc                  |

| X <sub>tlk,4</sub>                          | CrossTalk Quad Ch Mode. Signal applied to 1 channel (FIN0). Measurement taken on one channel with full scale at $F_{IN1}$ , $F_{IN1} = 71$ MHz, $F_{IN0} = 70$ MHz                                                                                                                                                                                                                                                                                                                                                                                               |                      | 70                         | dBc                  |

| Power Supply                                | Single Ch: $F_s = 500$ MSPS, Dual Ch: $F_s = 250$ MSPS, Quad Ch: $F_s = 125$ MSPS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |                            |                      |

| I <sub>AVDD</sub>                           | Analog Supply Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      | 99                         | mA                   |

|                                             | Digital and output driver Supply Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      | 65                         | mA                   |

| P <sub>AVDD</sub>                           | Analog Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      | 178                        | mW                   |

| P <sub>DVDD</sub>                           | Digital Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      | 117                        | mW                   |

| P <sub>TOT</sub>                            | Total Power Dissipation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                      | 295                        | mW                   |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

v03.0711

## HIGH SPEED MULTI-MODE 8-BIT 30 to 500 MSPS A/D CONVERTER

## AC Specifications

RoHS√

AVDD = 1.8V, DVDD = 1.8V, OVDD = 1.8V, 50% clock duty cycle, -1dBFS 70 MHz input signal, Gain = 1X, ADC current scaling -40%, RSDS output data levels unless otherwise noted

| Parameter              | Description                                                             | Min                | Тур | Max              | Unit |

|------------------------|-------------------------------------------------------------------------|--------------------|-----|------------------|------|

| P <sub>PD</sub>        | Power Down Mode dissipation                                             |                    | 15  |                  | μW   |

| P <sub>SLP</sub>       | Deep sleep Mode power dissipation                                       |                    | 49  |                  | mW   |

| P                      | Power dissipation with all channels in sleep channel mode (Light sleep) |                    | 67  |                  | mW   |

| P <sub>SLPCH_SAV</sub> |                                                                         |                    | 57  |                  | mW   |

| Analog Input           |                                                                         | ,                  |     |                  |      |

| F <sub>PBW</sub>       | Full Power Bandwidth                                                    |                    | 500 |                  | MHz  |

| Clock Inputs           |                                                                         | ,                  |     |                  |      |

| F <sub>smax</sub>      | Max. Conversion Rate in Modes: Single Ch<br>Dual Ch / Quad Ch           | 500 /<br>250 / 125 |     |                  | MSPS |

| F <sub>smin</sub>      | Min. Conversion Rate in Modes: Single Ch<br>Dual Ch / Quad Ch           |                    |     | 120 /<br>60 / 30 | MSPS |

## **Digital and Switching Specifications**

AVDD = 1.8V, DVDD = 1.8V, OVDD = 1.8V, RSDS output data levels, unless otherwise noted

| Parameter            | Description                                                                   |                        | Тур               | Мах                    | Unit   |

|----------------------|-------------------------------------------------------------------------------|------------------------|-------------------|------------------------|--------|

| Clock Inputs         |                                                                               |                        |                   |                        |        |

| DC                   | Duty Cycle                                                                    | 45                     |                   | 55                     | % high |

| Compliance           | LVDS supported up to 700 MHz                                                  | LVPECL,                | Sine wave, CM     | OS, LVDS               |        |

| V <sub>CK,sine</sub> | Differential input voltage swing, sine wave clock input                       | 1500                   |                   |                        | mVpp   |

| V <sub>CK,CMOS</sub> | Voltage input range CMOS (CLKN connected to ground)                           |                        | V <sub>OVDD</sub> |                        |        |

| V <sub>CM,CK</sub>   | Input common mode voltage. Keep voltages within ground and<br>voltage of OVDD | 0.3                    |                   | V <sub>OVDD</sub> -0.3 | V      |

| С <sub>ск</sub>      | Differential Input capacitance                                                |                        | 3                 |                        | pF     |

| Logic inputs (CM     | NOS)                                                                          |                        |                   |                        |        |

| V <sub>HI</sub>      | High Level Input Voltage. V <sub>OVDD</sub> ≥ 3.0V                            | 2                      |                   |                        | V      |

| V <sub>HI</sub>      | High Level Input Voltage. V <sub>OVDD</sub> = 1.7V - 3.0V                     | 0.8 ·V <sub>OVDD</sub> |                   |                        | V      |

| V                    | Low Level Input Voltage. V <sub>OVDD</sub> ≥ 3.0V                             | 0                      |                   | 0.8                    | V      |

| V                    | Low Level Input Voltage. V <sub>OVDD</sub> = 1.7V - 3.0V                      | 0                      |                   | 0.2 ·V <sub>OVDD</sub> | V      |

| I <sub>HI</sub>      | High Level Input leakage Current                                              |                        |                   | +/-10                  | μA     |

| I <sub>LI</sub>      | Low Level Input leakage Current                                               |                        |                   | +/-10                  | μA     |

| C <sub>i</sub>       | Input Capacitance                                                             |                        | 3                 |                        | pF     |

| Data Outputs         | ·                                                                             |                        |                   |                        |        |

| Compliance           |                                                                               |                        | LVDS / RSDS       |                        |        |

| V <sub>out</sub>     | Differential output voltage, LVDS                                             |                        | 350               |                        | mV     |

| V <sub>out</sub>     | Differential output voltage, RSDS                                             |                        | 150               |                        | mV     |

| V <sub>CM</sub>      | Output common mode voltage                                                    |                        | 1.2               |                        | V      |

| Output coding        | Default/optional                                                              | Offset                 | Binary/ 2's com   | plement                |        |

| Timing Characte      | ristics                                                                       |                        |                   |                        |        |

| t <sub>A</sub>       | Aperture delay                                                                |                        | 1.5               |                        | ns     |

| t                    | Aperture jitter, One bit set to '1' in jitter_ctrl<7:0>                       |                        | 160               |                        | fsrms  |

| T <sub>skew</sub>    | Timing skew between ADC channels                                              |                        | 2.5               |                        | psrms  |

ver, no rother ice. No Phone: 781-329-4700 • Order online at www.analog.com

Application Support: Phone: 1-800-ANALOG-D

v03.0711

#

## HIGH SPEED MULTI-MODE 8-BIT 30 то 500 MSPS A/D CONVERTER

## Digital and Switching Specifications

AVDD = 1.8V, DVDD = 1.8V, OVDD = 1.8V, RSDS output data levels, unless otherwise noted

| Parameter         | Description                                                                                                                | Min                      | Тур                      | Мах                      | Unit         |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|--------------|--|

| T <sub>su</sub>   | Start up time from Power Down Mode and Deep Sleep Mode to<br>Active Mode in µs. See section "Clock Frequency" for details. |                          | μs                       |                          |              |  |

| T                 | Start up time from Sleep Channel Mode to Active Mode                                                                       |                          |                          |                          | μs           |  |

| T                 | Out of range recovery time                                                                                                 |                          | 1                        |                          | clock cycles |  |

| TLATHSMQ          | Pipeline delay, Quad Channel Mode                                                                                          |                          | 32                       |                          | clock cycles |  |

| TLATHSMD          | Pipeline delay, Dual Channel Mode                                                                                          |                          | 64                       |                          |              |  |

| TLATHSMS          | Pipeline delay, Single Channel Mode                                                                                        |                          | 128                      |                          |              |  |

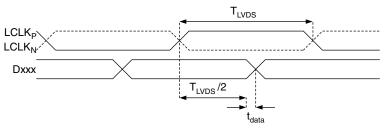

| LVDS Output Ti    | ming Characteristics                                                                                                       |                          |                          |                          |              |  |

| t <sub>data</sub> | LCLK to data delay time (excluding programmable phase shift)                                                               |                          | 50                       |                          | ps           |  |

| T <sub>PROP</sub> | Clock propagation delay.                                                                                                   | 6*T <sub>LVDS</sub> +2.2 | 7*T <sub>LVDS</sub> +3.5 | 7*T <sub>LVDS</sub> +5.0 | ns           |  |

|                   | LVDS bit-clock duty-cycle                                                                                                  | 45                       |                          | 55                       | % LCLK cycle |  |

|                   | Frame clock cycle-to-cycle jitter                                                                                          | 2.5                      |                          | % LCLK cycle             |              |  |

| T <sub>EDGE</sub> | Data rise- and fall time 20% to 80%                                                                                        | 0.7                      |                          |                          | ns           |  |

| T                 | Clock rise- and fall time 20% to 80%                                                                                       |                          | 0.7                      |                          | ns           |  |

## Table 1: Maximum Voltage Ratings

|                              |               | •              |

|------------------------------|---------------|----------------|

| Pin                          | Reference pin | Rating         |

| AVDD                         | AVSS          | -0.3V to +2.3V |

| DVDD                         | DVSS          | -0.3V to +2.3V |

| OVDD                         | AVSS          | -0.3V to +3.9V |

| AVSS / DVSS                  | DVSS / AVSS   | -0.3V to +0.3V |

| Analog inputs<br>and outputs | AVSS          | -0.3V to +2.3V |

| CLKx                         | AVSS          | -0.3V to +3.9V |

| LVDS outputs                 | DVSS          | -0.3V to +2.3V |

| Digital inputs               | DVSS          | -0.3V to +3.9V |

Applying voltages to the pins beyond those specified in Table 1 could cause permanent damage to the circuit.

| -40 to +85 °C  |

|----------------|

| -60 to +150 °C |

| 110 °C         |

| 29 °C/W        |

| J-STD-020      |

| Class 1C       |

| Class III      |

|                |

## ELECTROSTATIC SENSITIVE DEVICE OBSERVE HANDLING PRECAUTIONS

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

v03.0711

## HIGH SPEED MULTI-MODE 8-BIT 30 TO 500 MSPS A/D CONVERTER

## Pin Configuration and Description

#### Table 3: Pin descriptions

| Pin Name | Description                                                                                                                               | Pin Number | # Of Pins |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------|

| AVDD     | Analog power supply, 1.8V                                                                                                                 | 1, 36      | 2         |

| CSN      | Chip select enable. Active low                                                                                                            | 2          | 1         |

| SDATA    | Serial data input                                                                                                                         | 3          | 1         |

| SCLK     | Serial clock input                                                                                                                        | 4          | 1         |

| RESETN   | Reset SPI interface. Active low                                                                                                           | 5          | 1         |

| PD       | Power-down input. Activate after applying power in order to initialize the ADC correctly.<br>Alternatively use the SPI power down feature | 6          | 1         |

| DVDD     | Digital and I/O power supply, 1.8V                                                                                                        | 7, 30      | 2         |

| DVSS     | Digital ground                                                                                                                            | 8, 29      | 2         |

| DP1A     | LVDS channel 1A, positive output                                                                                                          | 9          | 1         |

| DN1A     | LVDS channel 1A, negative output                                                                                                          | 10         | 1         |

| DP1B     | LVDS channel 1B, positive output                                                                                                          | 11         | 1         |

| DN1B     | LVDS channel 1B, negative output                                                                                                          | 12         | 1         |

| DP2A     | LVDS channel 2A, positive output                                                                                                          | 13         | 1         |

| DN2A     | LVDS channel 2A, negative output                                                                                                          | 14         | 1         |

| DP2B     | LVDS channel 2B, positive output                                                                                                          | 15         | 1         |

| DN2B     | LVDS channel 2B, negative output                                                                                                          | 16         | 1         |

| LCLKP    | LVDS bit clock, positive output                                                                                                           | 17         | 1         |

| LCLKN    | LVDS bit clock, negative output                                                                                                           | 18         | 1         |

| FCLKP    | LVDS frame clock (1X), positive output                                                                                                    | 19         | 1         |

| FCLKN    | LVDS frame clock (1X), negative output                                                                                                    | 20         | 1         |

| DP3A     | LVDS channel 3A, positive output                                                                                                          | 21         | 1         |

| DN3A     | LVDS channel 3A, negative output                                                                                                          | 22         | 1         |

| DP3B     | LVDS channel 3B, positive output                                                                                                          | 23         | 1         |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

v03.0711

## HIGH SPEED MULTI-MODE 8-BIT 30 to 500 MSPS A/D CONVERTER

## Table 3: Pin descriptions

| Pin Name | Description                                   | Pin Number | # Of Pins |

|----------|-----------------------------------------------|------------|-----------|

| DN3B     | LVDS channel 3B, negative output              | 24         | 1         |

| DP4A     | LVDS channel 4A, positive output              | 25         | 1         |

| DN4A     | LVDS channel 4A, negative output              | 26         | 1         |

| DP4B     | LVDS channel 4B, positive output              | 27         | 1         |

| DN4B     | LVDS channel 4B, negative output              | 28         | 1         |

| AVSS2    | Analog ground domain 2                        | 31         | 1         |

| AVDD2    | Analog power supply domain 2, 1.8V            | 32         | 1         |

| OVDD     | Digital CMOS Inputs supply voltage            | 33         | 1         |

| CLKN     | Negative differential input clock.            | 34         | 1         |

| CLKP     | Positive differential input clock             | 35         | 1         |

| IN4      | Negative differential input signal, channel 4 | 37         | 1         |

| IP4      | Positive differential input signal, channel 4 | 38         | 1         |

| AVSS     | Analog ground                                 | 39, 42, 45 | 3         |

| IN3      | Negative differential input signal, channel 3 | 40         | 1         |

| IP3      | Positive differential input signal, channel 3 | 41         | 1         |

| IN2      | Negative differential input signal, channel 2 | 43         | 1         |

| IP2      | Positive differential input signal, channel 2 | 44         | 1         |

| IN1      | Negative differential input signal, channel 1 | 46         | 1         |

| IP1      | Positive differential input signal, channel 1 | 47         | 1         |

| VCM      | Common mode output pin, 0.5*AVDD              | 48         | 1         |

## Start up Initialization

As part of the HMCAD1510 power-on sequence both a reset and a power down cycle have to be applied to ensure correct start-up initialization. Make sure that the supply voltages are properly settled before the start up initialization is being performed. Reset can be done in one of two ways:

- 1. By applying a low-going pulse (minimum 20 ns) on the RESETN pin (asynchronous).

- 2. By using the serial interface to set the 'rst' bit high. Internal registers are reset to default values when this bit is set. The 'rst' bit is self-reset to zero. When using this method, do not apply any low-going pulse on the RESETN pin.

Power down cycling can be done in one of two ways:

- 1. By applying a high-going pulse (minimum 20 ns) on the PD pin (asynchronous).

- 2. By cycling the 'pd' bit in register 0Fhex to high (reg value '0200'hex) and then low (reg value '0000'hex).

## Serial Interface

The HMCAD1510 configuration registers can be accessed through a serial interface formed by the pins SDATA (serial interface data), SCLK (serial interface clock) and CSN (chip select, active low). The following occurs when CSN is set low:

- Serial data are shifted into the chip

- At every rising edge of SCLK, the value present at SDATA is latched

- SDATA is loaded into the register every 24th rising edge of SCLK

Multiples of 24-bit words data can be loaded within a single active CSN pulse. If more than 24 bits are loaded into SDATA during one active CSN pulse, only the first 24 bits are kept. The excess bits are ignored. Every 24-bit word is

HIGH SPEED MULTI-MODE 8-BIT 30 to 500 MSPS A/D CONVERTER

divided into two parts:

• The first eight bits form the register address

v03.0711

• The remaining 16 bits form the register data

Acceptable SCLK frequencies are from 20MHz down to a few hertz. Duty-cycle does not have to be tightly controlled.

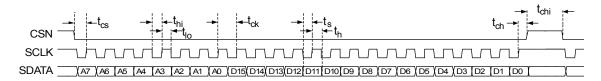

## **Timing Diagram**

Figure 3 shows the timing of the serial port interface. Table 4 explains the timing variables used in figure 3.

#### Figure 3: Serial Port Interface timing

#### Table 4: Serial Port Interface Timing Definitions

| Parameter       | Parameter Description           |    |    |  |  | Parameter Description |  |  |  |  |

|-----------------|---------------------------------|----|----|--|--|-----------------------|--|--|--|--|

| t <sub>cs</sub> | Setup time between CSN and SCLK | 8  | ns |  |  |                       |  |  |  |  |

| t <sub>ch</sub> | Hold time between CSN and SCLK  | 8  | ns |  |  |                       |  |  |  |  |

| t <sub>hi</sub> | SCLK high time                  | 20 | ns |  |  |                       |  |  |  |  |

| t <sub>io</sub> | SCLK low time                   | 20 | ns |  |  |                       |  |  |  |  |

| t <sub>ck</sub> | SCLK period                     | 50 | ns |  |  |                       |  |  |  |  |

| t <sub>s</sub>  | Data setup time                 | 5  | ns |  |  |                       |  |  |  |  |

| t <sub>h</sub>  | Data hold time                  | 5  | ns |  |  |                       |  |  |  |  |

v03.0711

## HIGH SPEED MULTI-MODE 8-BIT 30 to 500 MSPS A/D CONVERTER

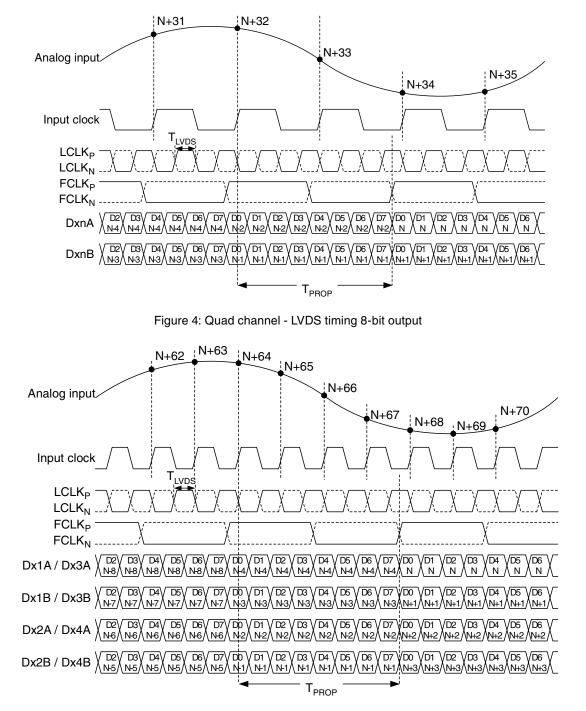

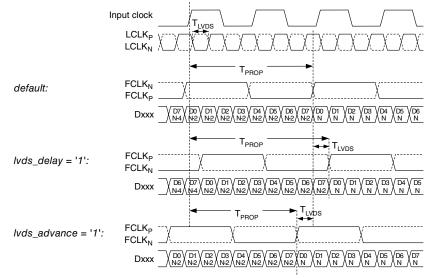

## Timing Diagrams

Figure 5: Dual channel - LVDS timing 8-bit output

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

v03.0711

## HIGH SPEED MULTI-MODE 8-BIT 30 to 500 MSPS A/D CONVERTER

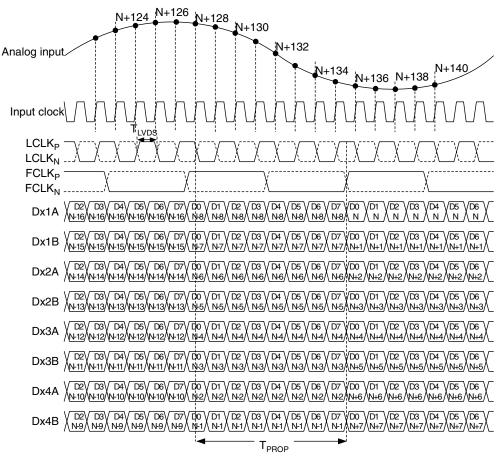

Figure 6: Single channel - LVDS timing 8-bit output

Figure 7: LVDS data timing

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

v03.0711

## HIGH SPEED MULTI-MODE 8-BIT 30 to 500 MSPS A/D CONVERTER

## **Register Map Summary**

#### Table 5: Register Map

| Name                  | Description                                                                            | Default                                     | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO | Hex<br>Address |

|-----------------------|----------------------------------------------------------------------------------------|---------------------------------------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|----------------|

| rst *                 | Self-clearing software reset.                                                          | Inactive                                    |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    | х  | 0x00           |

| sleep4_ch<br><4:1>    | Channel-specific sleep mode for a<br>Quad Channel setup.                               | Inactive                                    |     |     |     |     |     |     |    |    |    |    |    |    | x  | x  | x  | х  |                |

| sleep2_ch<br><2:1>    | Channel-specific sleep mode for a Dual<br>Channel setup.                               | Inactive                                    |     |     |     |     |     |     |    |    |    |    | х  | x  |    |    |    |    |                |

| sleep1_ch1            | Channel-specific sleep mode for a<br>Single Channel setup.                             | Inactive                                    |     |     |     |     |     |     |    |    |    | х  |    |    |    |    |    |    | 0x0F           |

| sleep                 | Go to sleep-mode.                                                                      | Inactive                                    |     |     |     |     |     |     |    | х  |    |    |    |    |    |    |    |    |                |

| pd                    | Go to power-down.                                                                      | Inactive                                    |     |     |     |     |     |     | х  |    |    |    |    |    |    |    |    |    |                |

| pd_pin_cfg<br><1:0>   | Configures the PD pin function.                                                        | PD pin configured<br>for power-down<br>mode |     |     |     |     | x   | x   |    |    |    |    |    |    |    |    |    |    |                |

| ilvds_lclk<br><2:0>   | LVDS current drive programmability for<br>LCLKP and LCLKN pins.                        | 3.5 mA drive                                |     |     |     |     |     |     |    |    |    |    |    |    |    | x  | x  | х  |                |

| ilvds_frame<br><2:0>  | LVDS current drive programmability for<br>FCLKP and FCLKN pins.                        | 3.5 mA drive                                |     |     |     |     |     |     |    |    |    | x  | х  | x  |    |    |    |    | 0x11           |

| ilvds_dat<br><2:0>    | LVDS current drive programmability for output data pins.                               | 3.5 mA drive                                |     |     |     |     |     | x   | x  | x  |    |    |    |    |    |    |    |    |                |

| en_lvds_<br>term      | Enables internal termination for LVDS buffers.                                         | Termination<br>disabled                     |     | x   |     |     |     |     |    |    |    |    |    |    |    |    |    |    |                |

| term_lclk<br><2:0>    | Programmable termination for LCLKN and LCLKP buffers.                                  | Termination<br>disabled                     |     | 1   |     |     |     |     |    |    |    |    |    |    |    | x  | x  | х  | 0x12           |

| term_frame<br><2:0>   | Programmable termination for FCLKN and FCLKP buffers.                                  | Termination<br>disabled                     |     | 1   |     |     |     |     |    |    |    | x  | х  | x  |    |    |    |    |                |

| term_dat<br><2:0>     | Programmable termination for output data buffers.                                      | Termination<br>disabled                     |     | 1   |     |     |     | x   | x  | x  |    |    |    |    |    |    |    |    |                |

| invert4_ch<br><4:1>   | Channel specific swapping of the<br>analog input signal for a Quad Channel<br>setup.   | IPx is positive input                       |     |     |     |     |     |     |    |    |    |    |    |    | x  | x  | x  | х  |                |

| invert2_ch<br><2:1>   | Channel specific swapping of the<br>analog input signal for a Dual Channel<br>setup.   | IPx is positive input                       |     |     |     |     |     |     |    |    |    |    | x  | x  |    |    |    |    | 0x24           |

| invert1_ch1           | Channel specific swapping of the<br>analog input signal for a Single<br>Channel setup. | IPx is positive input                       |     |     |     |     |     |     |    |    |    | x  |    |    |    |    |    |    |                |

| en_ramp               | Enables a repeating full-scale ramp<br>pattern on the outputs.                         | Inactive                                    |     |     |     |     |     |     |    |    |    | x  | 0  | 0  |    |    |    |    |                |

| dual_<br>custom_pat   | Enable the mode wherein the output toggles between two defined codes.                  | Inactive                                    |     |     |     |     |     |     |    |    |    | 0  | x  | 0  |    |    |    |    | 0x25           |

| single_<br>custom_pat | Enables the mode wherein the output is a constant specified code.                      | Inactive                                    |     |     |     |     |     |     |    |    |    | 0  | 0  | x  |    |    |    |    |                |

| bits_custom1<br><7:0> | Bits for the single custom pattern and for the first code of the dual custom pattern.  | 0x00                                        | x   | x   | x   | x   | x   | x   | x  | x  |    |    |    |    |    |    |    |    | 0x26           |

| bits_custom2<br><7:0> | Bits for the second code of the dual custom pattern.                                   | 0x00                                        | х   | x   | х   | х   | x   | x   | x  | x  |    |    |    |    |    |    |    |    | 0x27           |

| cgain4_ch1<br><3:0>   | Programmable coarse gain channel 1<br>in a Quad Channel setup.                         | 1x gain                                     |     |     |     |     |     |     |    |    |    |    |    |    | x  | х  | х  | х  |                |

| cgain4_ch2<br><3:0>   | Programmable coarse gain channel 2<br>in a Quad Channel setup.                         | 1x gain                                     |     |     |     |     |     |     |    |    | x  | x  | х  | x  |    |    |    |    | 0x2A           |

| cgain4_ch3<br><3:0>   | Programmable coarse gain channel 3<br>in a Quad Channel setup.                         | 1x gain                                     |     |     |     |     | x   | х   | x  | x  |    |    |    |    |    |    |    |    | UXZA           |

| cgain4_ch4<br><3:0>   | Programmable coarse gain channel 4<br>in a Quad Channel setup.                         | 1x gain                                     | х   | x   | x   | x   |     |     |    |    |    |    |    |    |    |    |    |    |                |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

v03.0711

## HIGH SPEED MULTI-MODE 8-BIT 30 TO 500 MSPS A/D CONVERTER

## Table 5: Register Map

| Name                       | Description                                                      | Default                   | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Hex<br>Address |

|----------------------------|------------------------------------------------------------------|---------------------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|----------------|

| cgain2_ch1<br><3:0>        | Programmable coarse gain channel 1<br>in a Dual Channel setup.   | 1x gain                   |     |     |     |     |     |     |    |    |    |    |    |    | x  | х  | х  | х  |                |

| cgain2_ch2<br><3:0>        | Programmable coarse gain channel 2<br>in a Dual Channel setup.   | 1x gain                   |     |     |     |     |     |     |    |    | x  | x  | x  | x  |    |    |    |    | 0x2B           |

| cgain1_ch1<br><3:0>        | Programmable coarse gain channel 1<br>in a Single Channel setup. | 1x gain                   |     |     |     |     | x   | x   | x  | x  |    |    |    |    |    |    |    |    |                |

| jitter_ctrl<br><7:0>       | Clock jitter adjustment.                                         | 160 fsrms                 |     |     |     |     |     |     |    |    | x  | x  | x  | x  | x  | х  | x  | х  | 0x30           |

| channel_<br>num <2:0> *    | Set number of channels: 1, 2 or 4 channels.                      | 4 channels                |     |     |     |     |     |     |    |    |    |    |    |    |    | х  | х  | x  | 0x31           |

| clk_divide<br><1:0>*       | Define clock divider factor: 1, 2, 4 or 8                        | Divide by 1               |     |     |     |     |     |     | x  | x  |    |    |    |    |    |    |    |    | 0,31           |

| coarse_<br>gain_cfg        | Configures the coarse gain setting                               | x-gain enabled            |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    | x  | 0x33           |

| fine_gain_en               | Enable use of fine gain.                                         | Disabled                  |     |     |     |     |     |     |    |    |    |    |    |    |    |    | х  |    |                |

| fgain_<br>branch1<br><6:0> | Programmable fine gain for branch1.                              | 0dB gain                  |     |     |     |     |     |     |    |    |    | x  | x  | x  | x  | х  | x  | x  | 0.424          |

| fgain_<br>branch2<br><6:0> | Programmable fine gain for branch 2.                             | 0dB gain                  |     | x   | x   | x   | x   | x   | x  | x  |    |    |    |    |    |    |    |    | 0x34           |

| fgain_<br>branch3<br><6:0> | Programmable fine gain for branch 3.                             | 0dB gain                  |     |     |     |     |     |     |    |    |    | x  | x  | x  | x  | х  | x  | x  | 0x35           |

| fgain_<br>branch4<br><6:0> | Programmable fine gain for branch 4.                             | 0dB gain                  |     | x   | x   | x   | x   | x   | x  | x  |    |    |    |    |    |    |    |    | 0,35           |

| fgain_<br>branch5<br><6:0> | Programmable fine gain for branch 5.                             | 0dB gain                  |     |     |     |     |     |     |    |    |    | x  | x  | x  | x  | х  | x  | x  | 0x36           |

| fgain_<br>branch6<br><6:0> | Programmable fine gain for branch 6.                             | 0dB gain                  |     | x   | x   | x   | x   | x   | x  | x  |    |    |    |    |    |    |    |    | 0x30           |

| fgain_<br>branch7<br><6:0> | Programmable fine gain for branch 7.                             | 0dB gain                  |     |     |     |     |     |     |    |    |    | x  | x  | x  | x  | х  | x  | x  | 0x37           |

| fgain_<br>branch8<br><6:0> | Programmable fine gain for branch 8.                             | 0dB gain                  |     | x   | x   | x   | x   | x   | x  | x  |    |    |    |    |    |    |    |    | 0x37           |

| inp_sel_adc1<br><4:0>      | Input select for adc 1.                                          | Signal input:<br>IP1/IN1  |     |     |     |     |     |     |    |    |    |    |    | x  | x  | х  | x  | 0  | 0x3A           |

| inp_sel_adc2<br><4:0>      | Input select for adc 2.                                          | Signal input: IP2/<br>IN2 |     |     |     | x   | x   | x   | x  | 0  |    |    |    |    |    |    |    |    | UX3A           |

| inp_sel_adc3<br><4:0>      | Input select for adc 3.                                          | Signal input: IP3/<br>IN3 |     |     |     |     |     |     |    |    |    |    |    | x  | x  | х  | x  | 0  | 0x3B           |

| inp_sel_<br>adc4<4:0>      | Input select for adc 4.                                          | Signal input: IP4/<br>IN4 |     |     |     | x   | x   | x   | x  | 0  |    |    |    |    |    |    |    |    |                |

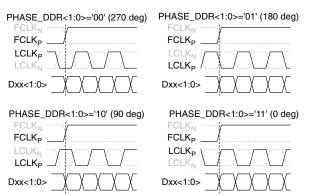

| phase_ddr<br><1:0>         | Controls the phase of the LCLK output relative to data.          | 90 degrees                |     |     |     |     |     |     |    |    |    | x  | x  |    |    |    |    |    | 0x42           |

| pat_deskew                 | Enable deskew pattern mode.                                      | Inactive                  |     |     |     |     |     |     |    |    |    |    |    |    |    |    | 0  | х  | 0x45           |

| pat_sync                   | Enable sync pattern mode.                                        | Inactive                  |     |     |     |     |     |     |    |    |    |    |    |    |    |    | х  | 0  | 0,10           |

| btc_mode                   | Binary two's complement format for<br>ADC output data.           | Straight offset<br>binary |     |     |     |     |     |     |    |    |    |    |    |    |    | х  |    |    | 0x46           |

| msb_first                  | Serialized ADC output data comes out with MSB first.             | LSB first                 |     |     |     |     |     |     |    |    |    |    |    |    | x  |    |    |    | 0.10           |