# EFR32MG24 Wireless SoC Family Data Sheet

The EFR32MG24 Wireless SoCs are ideal for mesh IoT wireless connectivity using Matter, OpenThread and Zigbee.

With key features like high performance 2.4 GHz RF, low current consumption, an Al/ML hardware accelerator and Secure Vault, IoT device makers can create smart, robust, and energy-efficient products that are secure from remote and local cyber-attacks. A Cortex®-M33 running up to 78 MHz and up to 1536 kB of Flash and 256 kB of RAM provides resources for demanding applications while leaving room for future growth.

Target applications include:

- · Smart Home Gateways and hubs, sensors, switches, door locks, smart plugs

- · Lighting LED bulbs, luminaires

- · Building Automation Gateways, sensors, switches, location services

- · AI/ML Predictive maintenance, glass break detection, wake-word detection

#### KEY FEATURES

- 32-bit ARM® Cortex®-M33 core with 78

MHz maximum operating frequency

- Up to 1536 kB of flash and 256 kB of RAM

- High performance radio with up to +19.5 dBm output power

- Energy efficient design with low active and sleep currents

- Secure Vault<sup>™</sup>

- · AI/ML Hardware Accelerator

# 1. Feature List

The EFR32MG24 highlighted features are listed below.

# Low Power Wireless System-on-Chip

- High Performance 32-bit 78 MHz ARM Cortex<sup>®</sup>-M33 with DSP instruction and floating-point unit for efficient signal processing

- Up to 1536 kB flash program memory

- Up to 256 kB RAM data memory

- 2.4 GHz radio operation

- Matrix Vector Processor for AI/ML acceleration

# Radio Performance

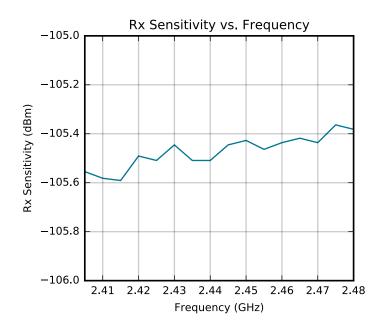

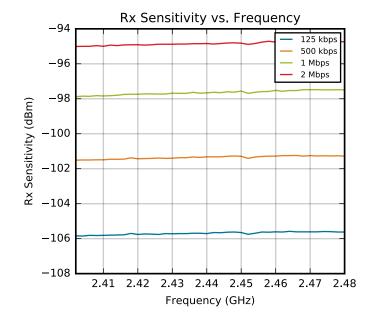

- -105.4 dBm sensitivity @ 250 kbps O-QPSK DSSS

- · -105.7 dBm sensitivity @ 125 kbps GFSK

- -97.6 dBm sensitivity @ 1 Mbps GFSK

- -94.8 dBm sensitivity @ 2 Mbps GFSK

- TX power up to 19.5 dBm

# Low System Energy Consumption

- 4.4 mA RX current (1 Mbps GFSK)

- 5.1 mA RX current (250 kbps O-QPSK DSSS)

- 5 mA TX current @ 0 dBm output power

- 19.1 mA TX current @ 10 dBm output power

- 156.8 mA TX current @ 19.5 dBm output power

- + 33.4  $\mu\text{A}/\text{MHz}$  in Active Mode (EM0) at 39.0 MHz

- 1.3 µA EM2 DeepSleep current (16 kB RAM retention and RTC running from LFRCO)

# Supported Modulation Format

- 2 (G)FSK with fully configurable shaping

- OQPSK DSSS

- (G)MSK

# Protocol Support

- Matter

- OpenThread

- Zigbee

- Bluetooth Low Energy (BLE 5.3)

- Bluetooth Mesh

- Proprietary 2.4 GHz

- Multiprotocol

- Direction finding using Angle-of-Arrival (AoA) and Angle-of-Departure (AoD)

- Secure Vault

- Hardware Cryptographic Acceleration for AES128/192/256, ChaCha20-Poly1305, SHA-1, SHA-2/256/384/512, ECDSA +ECDH(P-192, P-256, P-384, P-521), Ed25519 and Curve25519, J-PAKE, PBKDF2

- True Random Number Generator (TRNG)

- ARM® TrustZone®

- Secure Boot (Root of Trust Secure Loader)

- Secure Debug Unlock

- DPA Countermeasures

- Secure Key Management with PUF

- Anti-Tamper

- Secure Attestation

- Wide selection of MCU peripherals

- Analog to Digital Converter (IADC)

- 12-bit @ 1 Msps or 16-bit @ 76.9 ksps

- Select OPNs support High Speed Mode (up to 2 Msps) and High Accuracy Mode (up to 16 bits ENOB at 3.8 ksps)

- 2 × Analog Comparator (ACMP)

- 2 × Digital to Analog Converter (VDAC)

- Up to 32 General Purpose I/O pins with output state retention and asynchronous interrupts

- 8 Channel DMA Controller (LDMA)

- 16 Channel Peripheral Reflex System (PRS)

- 3 × 16-bit Timer/Counter with 3 Compare/Capture/PWM channels (TIMER2/3/4)

- 2 × 32-bit Timer/Counter with 3 Compare/Capture/PWM channels (TIMER0/1)

- 2 × 32-bit Real Time Counter (SYSRTC/BURTC)

- 24-bit Low Energy Timer for waveform generation (LETIM-ER)

- 16-bit Pulse Counter with asynchronous operation (PCNT)

- 2 × Watchdog Timer (WDOG)

- 1 × Universal Synchronous/Asynchronous Receiver/Transmitter (USART), supporting UART/SPI/SmartCard (ISO 7816)/IrDA/I<sup>2</sup>S

- 2 × Enhanced Universal Synchronous/Asynchronous Receiver/Transmitter (EUSART) supporting UART/SPI/DALI/ IrDA

- \*  $2 \times I^2C$  interface with SMBus support

- Low-Frequency RC Oscillator with precision mode to replace 32 kHz sleep crystal (LFRCO)

- Keypad scanner supporting up to 6x8 matrix (KEYSCAN)

- Die temperature sensor with +/-1.5 °C accuracy after singlepoint calibration

# Wide Operating Range

- 1.71 V to 3.8 V single power supply

- + -40 °C to 125 °C

- Packages

- QFN40 5 mm × 5 mm × 0.85 mm

- QFN48 6 mm × 6 mm × 0.85 mm

# 2. Ordering Information

| Table 2.1. | Ordering | Information |

|------------|----------|-------------|

|------------|----------|-------------|

| Ordering Code            | Max TX<br>Power | Flash<br>(kB) | RAM<br>(kB) | Secure<br>Vault | IADC High-<br>Speed /<br>High-Accu-<br>racy | Multi<br>Vector<br>Pro-<br>cessor | GPIO | Package / Pinout |

|--------------------------|-----------------|---------------|-------------|-----------------|---------------------------------------------|-----------------------------------|------|------------------|

| EFR32MG24B310F1536IM48-B | 10 dBm          | 1536          | 256         | High            | Yes                                         | Yes                               | 28   | QFN48 / ADC      |

| EFR32MG24B220F1536IM48-B | 19.5 dBm        | 1536          | 256         | High            | No                                          | Yes                               | 32   | QFN48 / Standard |

| EFR32MG24B210F1536IM48-B | 10 dBm          | 1536          | 256         | High            | No                                          | Yes                               | 32   | QFN48 / Standard |

| EFR32MG24B120F1536IM48-B | 19.5 dBm        | 1536          | 256         | High            | Yes                                         | No                                | 28   | QFN48 / ADC      |

| EFR32MG24B110F1536IM48-B | 10 dBm          | 1536          | 256         | High            | Yes                                         | No                                | 28   | QFN48 / ADC      |

| EFR32MG24B020F1536IM48-B | 19.5 dBm        | 1536          | 256         | High            | No                                          | No                                | 32   | QFN48 / Standard |

| EFR32MG24B020F1536IM40-B | 19.5 dBm        | 1536          | 256         | High            | No                                          | No                                | 26   | QFN40 / Standard |

| EFR32MG24B020F1024IM48-B | 19.5 dBm        | 1024          | 128         | High            | No                                          | No                                | 32   | QFN48 / Standard |

| EFR32MG24B010F1536IM48-B | 10 dBm          | 1536          | 256         | High            | No                                          | No                                | 32   | QFN48 / Standard |

| EFR32MG24B010F1536IM40-B | 10 dBm          | 1536          | 256         | High            | No                                          | No                                | 26   | QFN40 / Standard |

| EFR32MG24B010F1024IM48-B | 10 dBm          | 1024          | 128         | High            | No                                          | No                                | 32   | QFN48 / Standard |

| EFR32MG24A420F1536IM48-B | 19.5 dBm        | 1536          | 256         | Mid             | No                                          | No                                | 32   | QFN48 / Standard |

| EFR32MG24A420F1536IM40-B | 19.5 dBm        | 1536          | 256         | Mid             | No                                          | No                                | 26   | QFN40 / Standard |

| EFR32MG24A410F1536IM48-B | 10 dBm          | 1536          | 256         | Mid             | No                                          | No                                | 32   | QFN48 / Standard |

| EFR32MG24A410F1536IM40-B | 10 dBm          | 1536          | 256         | Mid             | No                                          | No                                | 26   | QFN40 / Standard |

| EFR32MG24A110F1024IM48-B | 10 dBm          | 1024          | 128         | Mid             | Yes                                         | No                                | 28   | QFN48 / ADC      |

| EFR32MG24A021F1024IM40-B | 19.5 dBm        | 1024          | 128         | Mid             | No                                          | No                                | 25   | QFN40 / HFCLKOUT |

| EFR32MG24A020F1536IM48-B | 19.5 dBm        | 1536          | 192         | Mid             | No                                          | No                                | 32   | QFN48 / Standard |

| EFR32MG24A020F1536IM40-B | 19.5 dBm        | 1536          | 192         | Mid             | No                                          | No                                | 26   | QFN40 / Standard |

| EFR32MG24A020F1024IM48-B | 19.5 dBm        | 1024          | 128         | Mid             | No                                          | No                                | 32   | QFN48 / Standard |

| EFR32MG24A020F1024IM40-B | 19.5 dBm        | 1024          | 128         | Mid             | No                                          | No                                | 26   | QFN40 / Standard |

| EFR32MG24A010F1536IM48-B | 10 dBm          | 1536          | 192         | Mid             | No                                          | No                                | 32   | QFN48 / Standard |

| EFR32MG24A010F1536IM40-B | 10 dBm          | 1536          | 192         | Mid             | No                                          | No                                | 26   | QFN40 / Standard |

| EFR32MG24A010F1024IM48-B | 10 dBm          | 1024          | 128         | Mid             | No                                          | No                                | 32   | QFN48 / Standard |

| EFR32MG24A010F1024IM40-B | 10 dBm          | 1024          | 128         | Mid             | No                                          | No                                | 26   | QFN40 / Standard |

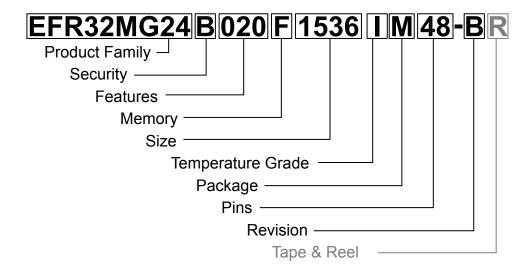

| Field                 | Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Family        | EFR32MG24: Mighty Gecko 24 Family                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Security              | <ul> <li>A: Secure Vault Mid</li> <li>B: Secure Vault High</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Features [f1][f2][f3] | <ul> <li>f1</li> <li>0: Base Configuration</li> <li>1: IADC High-Speed / High-Accuracy Available</li> <li>2: Matrix Vector Processor (MVP) Available</li> <li>3: IADC High-Speed / High-Accuracy and Matrix Vector Processor (MVP) Available</li> <li>4: 256K RAM and Secure Vault – Mid</li> <li>f2</li> <li>1: 10 dBm PA Transmit Power</li> <li>2: 19.5 dBm PA Transmit Power</li> <li>f3</li> <li>0: No feature enabled</li> <li>1: High Quality HFCLKOUT Pin Available</li> </ul> |

| Memory                | • F: Flash                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Size                  | Memory Size in kBytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Temperature Grade     | <ul> <li>G: -40 to +85 °C</li> <li>I: -40 to +125 °C</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Package               | • <b>M</b> : QFN                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Pins                  | Number of Package Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Revision              | • B: Revision B                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Tape & Reel           | • R: Tape & Reel (optional)                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Figure 2.1. Ordering Code Key

# **Table of Contents**

| 1. | Feature List                                                                                                      | . 2 | 2 |

|----|-------------------------------------------------------------------------------------------------------------------|-----|---|

| 2. | Ordering Information                                                                                              | . 3 | ; |

| 3. | System Overview                                                                                                   | . 9 | ) |

|    | 3.1 Introduction                                                                                                  | . 9 | ) |

|    | 3.2 Radio                                                                                                         | . 9 | ) |

|    | 3.2.1 Antenna Interface                                                                                           |     |   |

|    | 3.2.2 Fractional-N Frequency Synthesizer                                                                          |     |   |

|    | 3.2.3 Receiver Architecture                                                                                       |     |   |

|    | 3.2.4 Transmitter Architecture                                                                                    |     |   |

|    | 3.2.6 Data Buffering.                                                                                             |     |   |

|    | 3.2.7 Radio Controller (RAC).                                                                                     |     |   |

|    | 3.2.8 RF Signal Identifier                                                                                        |     |   |

|    | 3.3 General Purpose Input/Output (GPIO)                                                                           | .11 |   |

|    | 3.4 Keypad Scanner (KEYSCAN)                                                                                      |     |   |

|    | 3.5 Clocking                                                                                                      |     |   |

|    | 3.5.1 Clock Management Unit (CMU)                                                                                 |     |   |

|    | 3.5.2 Internal and External Oscillators.                                                                          |     |   |

|    | 3.6 Counters/Timers and PWM.                                                                                      |     |   |

|    | 3.6.1 Timer/Counter (TIMER)                                                                                       |     |   |

|    | 3.6.2 Low Energy Timer (LETIMER)                                                                                  |     |   |

|    | 3.6.3 System Real Time Clock with Capture (SYSRTC).                                                               |     |   |

|    | 3.6.4 Back-Up Real Time Counter (BURTC)                                                                           |     |   |

|    | 3.6.5 Watchdog Timer (WDOG).                                                                                      |     |   |

|    | 3.7 Communications and Other Digital Peripherals                                                                  |     |   |

|    | 3.7.1 Universal Synchronous/Asynchronous Receiver/Transmitter (USART).                                            |     |   |

|    | 3.7.2 Enhanced Universal Synchronous/Asynchronous Receiver/Transmitter (EUSART)                                   |     |   |

|    | 3.7.3 Inter-Integrated Circuit Interface (I <sup>2</sup> C)                                                       |     |   |

|    | 3.7.4 Peripheral Reflex System (PRS)                                                                              |     |   |

|    | 3.8 Secure Vault Features                                                                                         |     |   |

|    | 3.8.1       Secure Boot with Root of Trust and Secure Loader (RTSL)         3.8.2       Cryptographic Accelerator |     |   |

|    | 3.8.3 True Random Number Generator                                                                                |     |   |

|    | 3.8.4 Secure Debug with Lock/Unlock.                                                                              |     |   |

|    | 3.8.5 DPA Countermeasures.                                                                                        |     |   |

|    | 3.8.6 Secure Key Management with PUF                                                                              | .15 | 5 |

|    | 3.8.7 Anti-Tamper                                                                                                 |     |   |

|    | 3.8.8 Secure Attestation                                                                                          | .15 | 5 |

|    | 3.9 Analog                                                                                                        |     |   |

|    | 3.9.1 Analog to Digital Converter (IADC)                                                                          |     |   |

|    | 3.9.2 Analog Comparator (ACMP)                                                                                    |     |   |

|    | 3.9.3 Digital to Analog Converter (VDAC)                                                                          | .16 | j |

|    | 3.10 Power                                               |   |   |   | • | .17<br>.17<br>.17 |

|----|----------------------------------------------------------|---|---|---|---|-------------------|

|    | 3.11 Reset Management Unit (RMU)                         |   | • |   |   | .18               |

|    | 3.12 Core, Memory, and Accelerators                      |   |   |   |   |                   |

|    | 3.12.2 Memory System Controller (MSC)                    | • | • | • | • | .19<br>.19        |

|    | 3.12.4 Matrix Vector Processor (MVP)                     | • | • | • | • | .19               |

|    | 3.13 Memory Map                                          |   | • |   | • | .20               |

|    | 3.14 Configuration Summary                               |   |   |   |   | .21               |

| 4. | 4. Electrical Specifications                             |   |   |   |   | . 22              |

|    | 4.1 Electrical Characteristics                           |   |   |   |   | .22               |

|    | 4.2 Absolute Maximum Ratings.                            |   |   |   |   |                   |

|    | 4.3 General Operating Conditions                         |   |   |   |   | .24               |

|    | 4.4 DC-DC Converter                                      |   |   |   |   | .26               |

|    | 4.5 Thermal Characteristics                              |   |   |   |   | .28               |

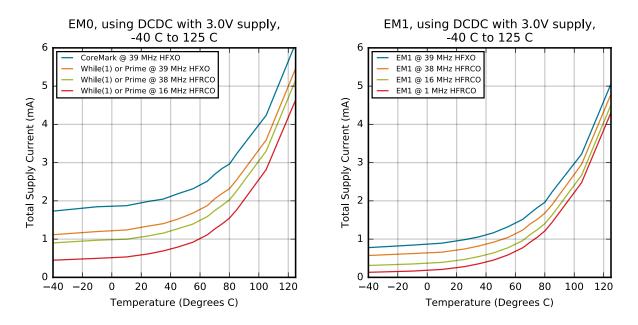

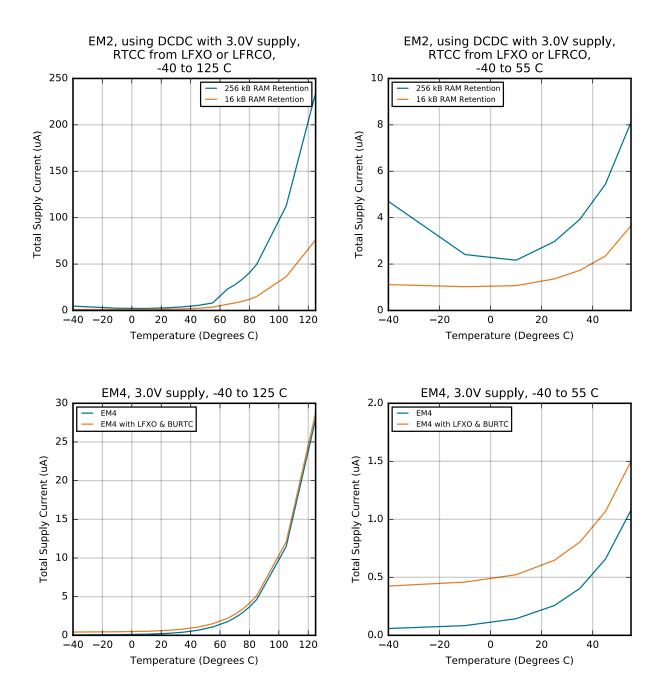

|    | 4.6 Current Consumption                                  |   |   |   |   | .29               |

|    | 4.6.1 MCU current consumption using DC-DC at 3.0 V input |   |   |   |   |                   |

|    | 4.6.2 Radio current consumption at 3.0V using DCDC       |   |   |   |   |                   |

|    | 4.6.4 Radio current consumption at 3.0V.                 |   |   |   |   |                   |

|    | 4.6.5 MCU current consumption at 1.8 V                   |   |   |   |   |                   |

|    | 4.6.6 Radio current consumption at 1.8V.                 |   |   |   |   | .42               |

|    | 4.7 Flash Characteristics                                |   |   |   |   | .44               |

|    | 4.8 Energy Mode Wake-up and Entry Times                  |   |   |   |   | .45               |

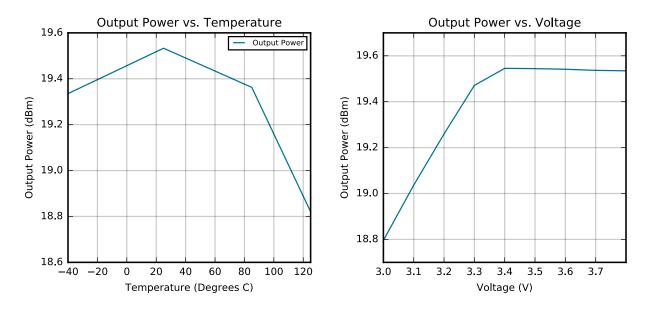

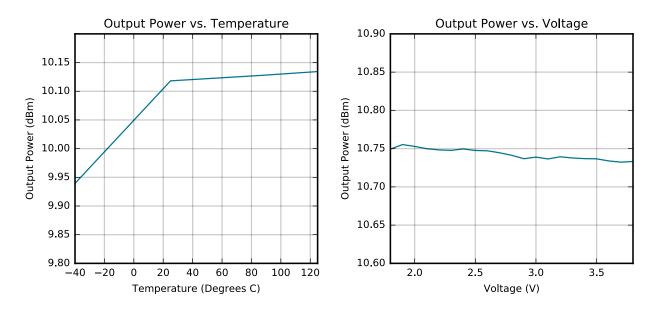

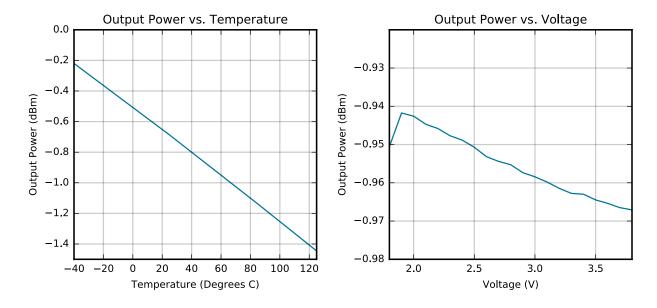

|    | 4.9 2.4 GHz RF Transceiver Characteristics               |   |   |   |   |                   |

|    | 4.9.1 RF Transmitter Characteristics                     |   |   |   |   |                   |

|    | 4.9.2 RF Receiver Characteristics                        |   |   |   |   |                   |

|    | 4.10 Oscillators                                         |   |   |   |   |                   |

|    | 4.10.2 Low Frequency Crystal Oscillator (LFXO)           |   |   |   |   |                   |

|    | 4.10.3 High Frequency RC Oscillator (HFRCO)              |   |   |   |   |                   |

|    | 4.10.4 Fast Start-Up RC Oscillator (FSRCO)               |   |   |   |   | .63               |

|    | 4.10.5 Precision Low Frequency RC Oscillator (LFRCO)     |   |   |   |   |                   |

|    | 4.10.6 Ultra Low Frequency RC Oscillator (ULFRCO)        |   |   |   |   |                   |

|    | 4.11 GPIO Pins (GPIO)                                    |   |   |   |   |                   |

|    | 4.12 Analog to Digital Converter (IADC)                  |   |   |   |   |                   |

|    | 4.13 Analog Comparator (ACMP)                            |   |   |   |   |                   |

|    | 4.14 Digital to Analog Converter (VDAC)                  |   |   |   |   | .75               |

|    | 4.15 Temperature Sensor                                       | .77 |

|----|---------------------------------------------------------------|-----|

|    | 4.16 Brown Out Detectors                                      | .78 |

|    | 4.16.1 DVDD BOD                                               |     |

|    | 4.16.2 Low-Energy DVDD BOD.                                   |     |

|    | 4.16.3 AVDD and IOVDD BODs                                    |     |

|    | 4.17 Pulse Counter (PCNT)                                     | .79 |

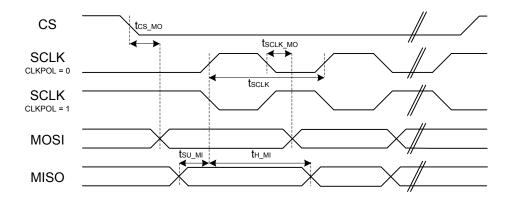

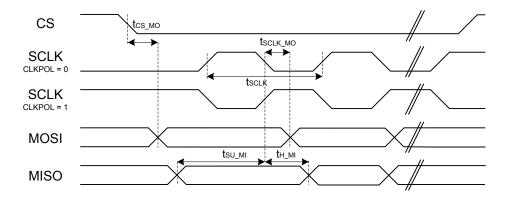

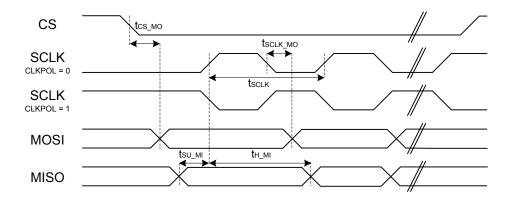

|    | 4.18 USART SPI Main Timing                                    |     |

|    | 4.18.1 USART SPI Main Timing, Voltage Scaling = VSCALE2       |     |

|    | 4.18.2 USART SPI Main Timing, Voltage Scaling = VSCALE1       |     |

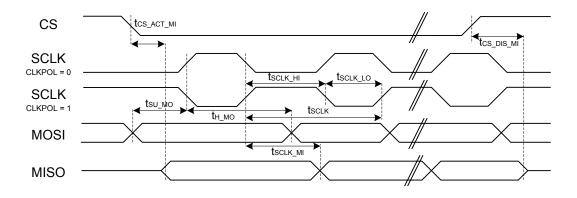

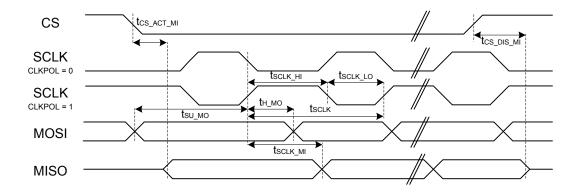

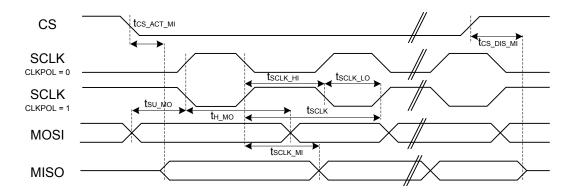

|    | 4.19 USART SPI Secondary Timing                               |     |

|    | 4.19.1 USART SPI Secondary Timing, Voltage Scaling = VSCALE2  |     |

|    | 4.19.2 USART SPI Secondary Timing, Voltage Scaling = VSCALE1  |     |

|    | 4.20 EUSART SPI Main Timing.                                  |     |

|    | 4.20.1 EUSART SPI Main Timing, Voltage Scaling = VSCALE2      |     |

|    |                                                               |     |

|    | 4.21 EUSART SPI Secondary Timing                              |     |

|    | 4.21.2 EUSART SPI Secondary Timing, Voltage Scaling = VSCALE2 |     |

|    | 4.21.3 EUSART SPI Secondary Timing, Voltage Scaling = VSCALE0 |     |

|    | 4.22 I2C Electrical Specifications                            |     |

|    | 4.22.1 I2C Standard-mode (Sm)                                 |     |

|    | 4.22.2 I2C Fast-mode (Fm)                                     |     |

|    | 4.22.3 I2C Fast-mode Plus (Fm+)                               | .90 |

|    | 4.23 Boot Timing                                              | .90 |

|    | 4.24 Crypto Operation Timing for SE Manager API               | .92 |

|    | 4.25 Crypto Operation Average Current for SE Manager API.     | .94 |

|    | 4.26 Matrix Vector Processor (MVP)                            |     |

|    | 4.27 Typical Performance Curves                               |     |

|    | 4.27.1 Supply Current                                         |     |

|    | 4.27.2 RF Characteristics                                     |     |

|    | 4.27.3 DC-DC Converter                                        | 102 |

|    | 4.27.4 IADC                                                   |     |

|    | 4.27.5 GPIO                                                   | 104 |

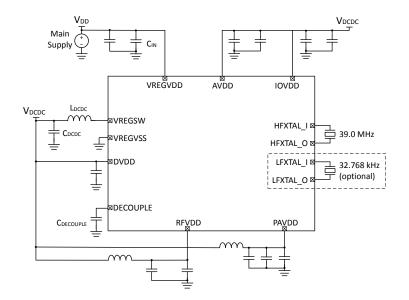

| 5. | Typical Connections                                           | 105 |

|    | 5.1 Power                                                     | 105 |

|    | 5.2 Other Connections                                         | 106 |

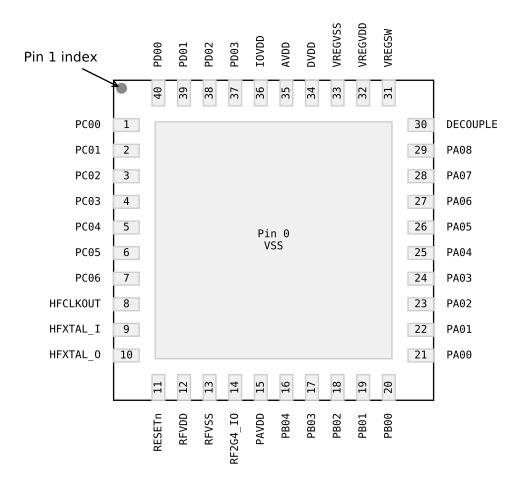

| 6. | Pin Definitions                                               | 107 |

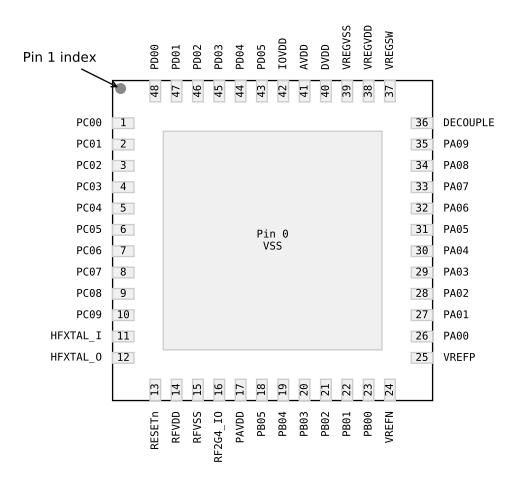

|    | 6.1 QFN48 / Standard Device Pinout                            | 107 |

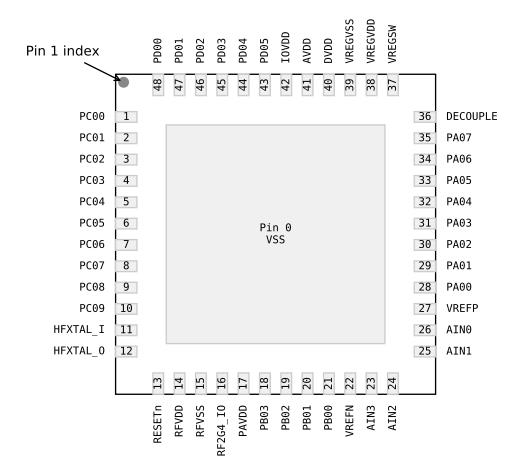

|    | 6.2 QFN48 / ADC Device Pinout                                 |     |

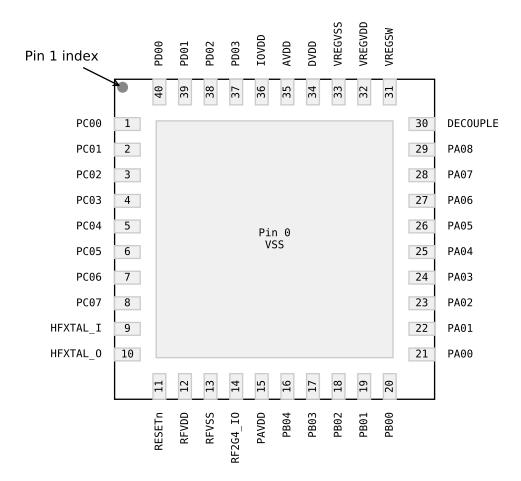

|    | 6.3 QFN40 / Standard Device Pinout                            |     |

|    | 6.4 QFN40 / HFCLKOUT Device Pinout                            |     |

|    | 6.5 Alternate Function Table.                                 |     |

|    | 6.6 Analog Peripheral Connectivity  | 16 |

|----|-------------------------------------|----|

|    | 6.7 Digital Peripheral Connectivity | 17 |

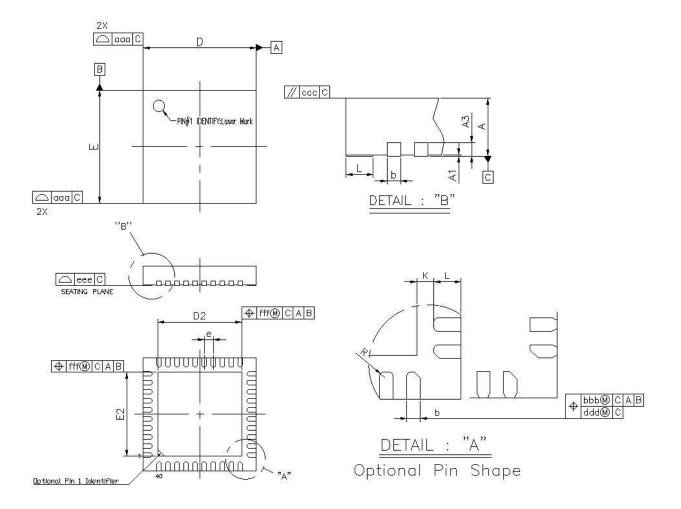

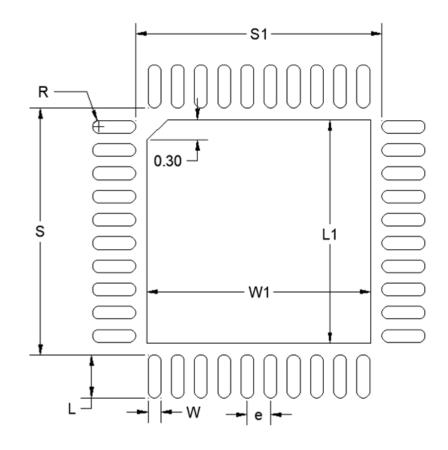

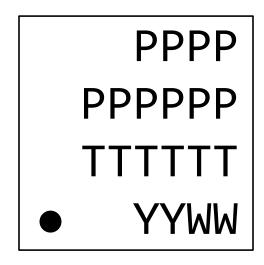

| 7. | QFN40 Package Specifications.       | 21 |

|    | 7.1 QFN40 Package Dimensions        | 21 |

|    | 7.2 QFN40 PCB Land Pattern          | 23 |

|    | 7.3 QFN40 Package Marking           | 24 |

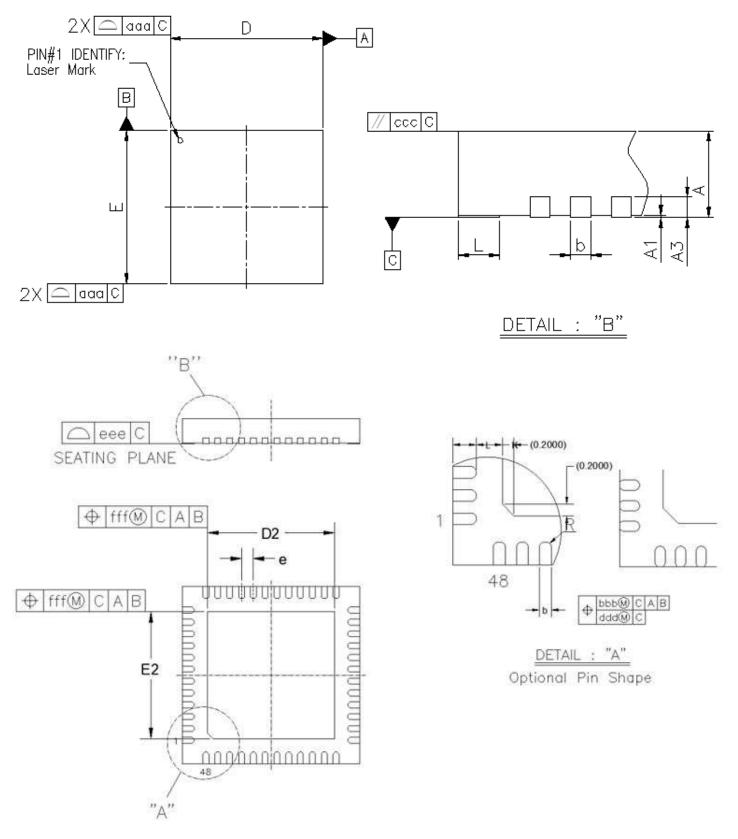

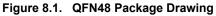

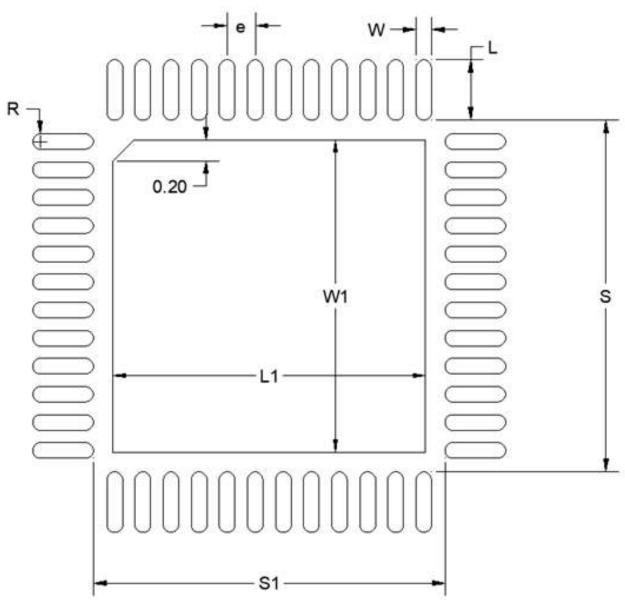

| 8. | QFN48 Package Specifications.       | 25 |

|    | 8.1 QFN48 Package Dimensions        | 25 |

|    | 8.2 QFN48 PCB Land Pattern          | 27 |

|    | 8.3 QFN48 Package Marking           | 28 |

| 9. | Revision History                    | 29 |

# 3. System Overview

#### 3.1 Introduction

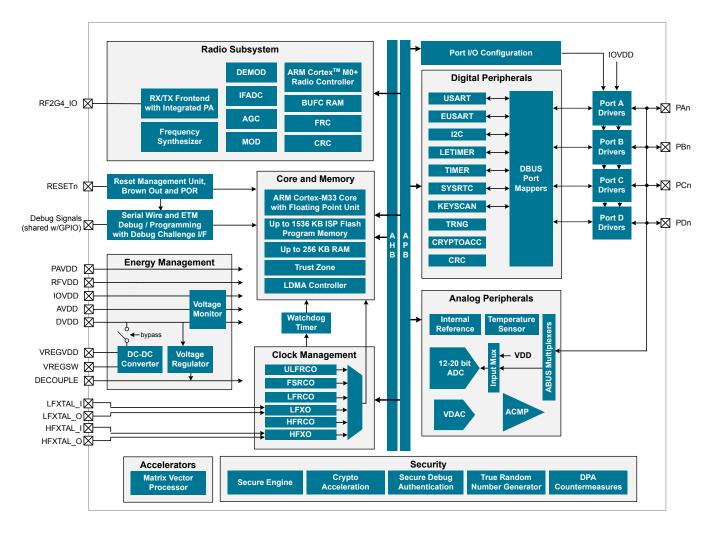

The EFR32 product family combines an energy-friendly MCU with a high performance radio transceiver. The devices are well suited for secure connected IoT multi-protocol devices requiring high performance and low energy consumption. This section gives a short introduction to the full radio and MCU system. The detailed functional description can be found in the EFR32xG24 Reference Manual.

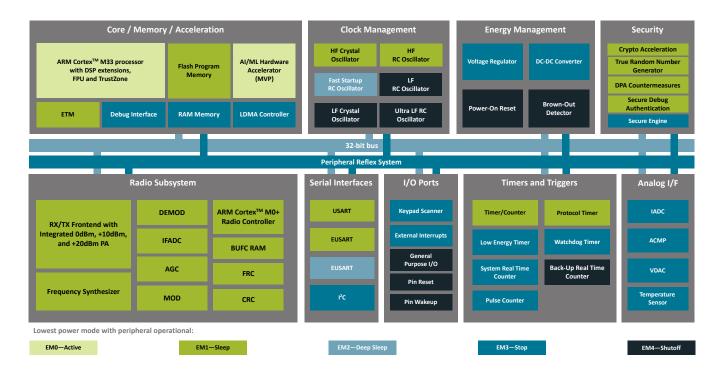

A block diagram of the EFR32MG24 family is shown in Figure 3.1 Detailed EFR32MG24 Block Diagram on page 9. The diagram shows a superset of features available on the family, which vary by OPN. For more information about specific device features, consult Ordering Information.

Figure 3.1. Detailed EFR32MG24 Block Diagram

#### 3.2 Radio

The EFR32MG24 Wireless SoC features a highly configurable radio transceiver supporting Zigbee, Bluetooth Low Energy and Bluetooth Mesh wireless protocols.

#### 3.2.1 Antenna Interface

The 2.4 GHz antenna interface consists of a single-ended pin (RF2G4\_IO). The external components for the antenna interface in typical applications are shown in the RF Matching Networks section.

#### 3.2.2 Fractional-N Frequency Synthesizer

The EFR32MG24 contains a high performance, low phase noise, fully integrated fractional-N frequency synthesizer. The synthesizer is used in receive mode to generate the LO frequency for the down-conversion mixer. It is also used in transmit mode to directly generate the modulated RF carrier.

The fractional-N architecture provides excellent phase noise performance, frequency resolution better than 100 Hz, and low energy consumption. The synthesizer's fast frequency settling allows for very short receiver and transmitter wake up times to reduce system energy consumption.

#### 3.2.3 Receiver Architecture

The EFR32MG24 uses a low-IF receiver architecture, consisting of a Low-Noise Amplifier (LNA) followed by an I/Q down-conversion mixer. The I/Q signals are further filtered and amplified before being sampled by the IF analog-to-digital converter (IFADC).

The IF frequency is configurable from 150 kHz to 1371 kHz. The IF can further be configured for high-side or low-side injection, providing flexibility with respect to known interferers at the image frequency.

The Automatic Gain Control (AGC) module adjusts the receiver gain to optimize performance and avoid saturation for excellent selectivity and blocking performance. The 2.4 GHz radio is calibrated at production to improve image rejection performance.

Demodulation is performed in the digital domain. The demodulator performs configurable decimation and channel filtering to allow receive bandwidths ranging from 0.1 to 2530 kHz. High carrier frequency and baud rate offsets are tolerated by active estimation and compensation. Advanced features supporting high quality communication under adverse conditions include forward error correction by block and convolutional coding as well as Direct Sequence Spread Spectrum (DSSS).

A Received Signal Strength Indicator (RSSI) is available for signal quality metrics, for level-based proximity detection, and for RF channel access by Collision Avoidance (CA) or Listen Before Talk (LBT) algorithms. An RSSI capture value is associated with each received frame and the dynamic RSSI measurement can be monitored throughout reception.

#### 3.2.4 Transmitter Architecture

The EFR32MG24 uses a direct-conversion transmitter architecture. For constant envelope modulation formats, the modulator controls phase and frequency modulation in the frequency synthesizer. Transmit symbols or chips are optionally shaped by a digital shaping filter. The shaping filter is fully configurable, including the BT product, and can be used to implement Gaussian or Raised Cosine shaping.

Carrier Sense Multiple Access - Collision Avoidance (CSMA-CA) or Listen Before Talk (LBT) algorithms can be automatically timed by the EFR32MG24. These algorithms are typically defined by regulatory standards to improve inter-operability in a given bandwidth between devices that otherwise lack synchronized RF channel access.

#### 3.2.5 Packet and State Trace

The EFR32MG24 Frame Controller has a packet and state trace unit that provides valuable information during the development phase. It features:

- Non-intrusive trace of transmit data, receive data and state information

- Data observability on a single-pin UART data output, or on a two-pin SPI data output

- · Configurable data output bitrate / baudrate

- Multiplexed transmitted data, received data and state / meta information in a single serial data stream

#### 3.2.6 Data Buffering

The EFR32MG24 features an advanced Radio Buffer Controller (BUFC) capable of handling up to 4 buffers of adjustable size from 64 bytes to 4096 bytes. Each buffer can be used for RX, TX or both. The buffer data is located in RAM, enabling zero-copy operations.

#### 3.2.7 Radio Controller (RAC)

The Radio Controller controls the top level state of the radio subsystem in the EFR32MG24. It performs the following tasks:

- Precisely-timed control of enabling and disabling of the receiver and transmitter circuitry

- · Run-time calibration of receiver, transmitter and frequency synthesizer

- Detailed frame transmission timing, including optional LBT or CSMA-CA

#### 3.2.8 RF Signal Identifier

When an IoT radio is placed next to a high duty-cycle co-located Wi-Fi radio transmission, IoT radios are blocked from receiving weak signals. The RF Signal Identifier feature available on EFR32MG24 devices enables the IoT radio to detect partial 802.15.4 or BLE/BT Mesh packets. When a partial packet is detected, the IoT radio can communicate this information to the corresponding Wi-Fi device (through serial interface or GPIO asserts), which can consequently halt transmission while the IoT radio waits for a packet retry to be received. This helps provide a higher success rate of receiving packets from other devices on the network, when co-located with an interfering Wi-Fi radio.

#### 3.3 General Purpose Input/Output (GPIO)

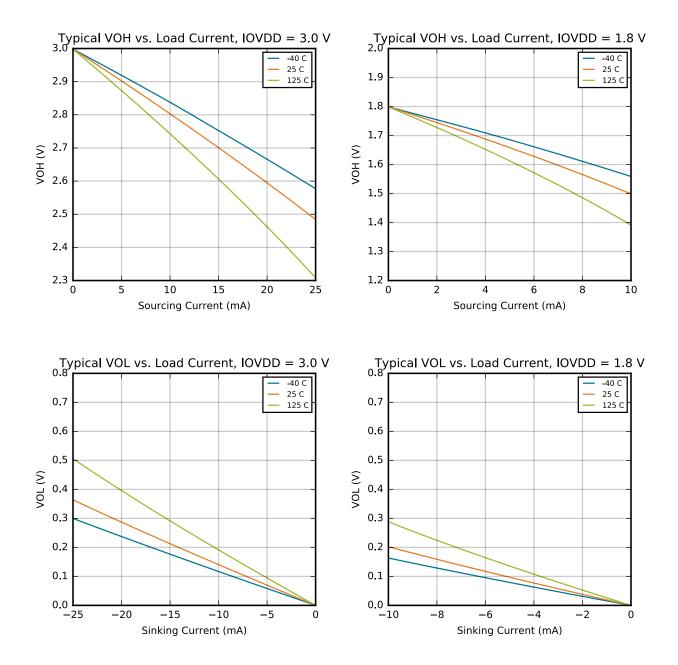

EFR32MG24 has up to 32 General Purpose Input/Output pins. Each GPIO pin can be individually configured as either an output or input. More advanced configurations including open-drain, open-source, and glitch-filtering can be configured for each individual GPIO pin. The GPIO pins can be overridden by peripheral connections, like SPI communication. Each peripheral connection can be routed to several GPIO pins on the device. The input value of a GPIO pin can be routed through the Peripheral Reflex System to other peripherals. The GPIO subsystem supports asynchronous external pin interrupts.

All of the pins on ports A and port B are EM2 capable. These pins may be used by Low-Energy peripherals in EM2/3 and may also be used as EM2/3 pin wake-ups. Pins on ports C and D are latched/retained in their current state when entering EM2 until EM2 exit upon which internal peripherals could once again drive those pads.

A few GPIOs also have EM4 wake functionality. These pins are listed in the Alternate Function Table.

#### 3.4 Keypad Scanner (KEYSCAN)

A low-energy keypad scanner (KEYSCAN) is included, which can scan up to a 6 x 8 matrix of keyboard switches. The KEYSCAN peripheral contains logic for debounce and settling time, allowing it to scan through the switch matrix autonomously in EM0 and EM1, and interrupt the processor when a key press is detected. A wake-on-keypress feature is also supported, allowing for the detection of any key press down to EM3.

#### 3.5 Clocking

#### 3.5.1 Clock Management Unit (CMU)

The Clock Management Unit controls oscillators and clocks in the EFR32MG24. Individual enabling and disabling of clocks to all peripheral modules is performed by the CMU. The CMU also controls enabling and configuration of the oscillators. A high degree of flexibility allows software to optimize energy consumption in any specific application by minimizing power dissipation in unused peripherals and oscillators.

#### 3.5.2 Internal and External Oscillators

The EFR32MG24 supports two crystal oscillators and fully integrates four RC oscillators, listed below.

- A high frequency crystal oscillator (HFXO) with integrated load capacitors, tunable in small steps, provides a precise timing reference for the MCU. The HFXO provides excellent RF clocking performance using a 39.0 MHz crystal. The HFXO can also support an external clock source such as a TCXO for applications that require an extremely accurate clock frequency over temperature.

- A 32.768 kHz crystal oscillator (LFXO) provides an accurate timing reference for low energy modes.

- An integrated high frequency RC oscillator (HFRCO) is available for the MCU system, when crystal accuracy is not required. The HFRCO employs fast start-up at minimal energy consumption combined with a wide frequency range, from 1 MHz to 78 MHz.

- · An integrated fast start-up RC oscillator (FSRCO) that runs at a fixed 20 MHz

- An integrated low frequency 32.768 kHz RC oscillator (LFRCO) for low power operation without an external crystal. Precision mode enables periodic recalibration against the 39.0 MHz HFXO crystal to improve accuracy to +/- 500 ppm, suitable for BLE sleep interval timing.

- An integrated ultra-low frequency 1 kHz RC oscillator (ULFRCO) is available to provide a timing reference at the lowest energy consumption in low energy modes.

#### 3.6 Counters/Timers and PWM

#### 3.6.1 Timer/Counter (TIMER)

TIMER peripherals keep track of timing, count events, generate PWM outputs and trigger timed actions in other peripherals through the Peripheral Reflex System (PRS). The core of each TIMER is a 16-bit or 32-bit counter with up to 3 compare/capture channels. Each channel is configurable in one of three modes. In capture mode, the counter state is stored in a buffer at a selected input event. In compare mode, the channel output reflects the comparison of the counter to a programmed threshold value. In PWM mode, the TIMER supports generation of pulse-width modulation (PWM) outputs of arbitrary waveforms defined by the sequence of values written to the compare registers. In addition some timers offer dead-time insertion.

See 3.14 Configuration Summary for information on the feature set of each timer.

#### 3.6.2 Low Energy Timer (LETIMER)

The unique LETIMER is a 24-bit timer that is available in energy mode EM0 Active, EM1 Sleep, EM2 Deep Sleep, and EM3 Stop. This allows it to be used for timing and output generation when most of the device is powered down, allowing simple tasks to be performed while the power consumption of the system is kept at an absolute minimum. The LETIMER can be used to output a variety of waveforms with minimal software intervention. The LETIMER is connected to the Peripheral Reflex System (PRS), and can be configured to start counting on compare matches from other peripherals such as the Real Time Clock.

#### 3.6.3 System Real Time Clock with Capture (SYSRTC)

The System Real Time Clock (SYSRTC) is a 32-bit counter providing timekeeping down to EM3. The SYSRTC can be clocked by any of the on-board low-frequency oscillators, and it is capable of providing system wake-up at user defined intervals.

#### 3.6.4 Back-Up Real Time Counter (BURTC)

The Back-Up Real Time Counter (BURTC) is a 32-bit counter providing timekeeping in all energy modes, including EM4. The BURTC can be clocked by any of the on-board low-frequency oscillators, and it is capable of providing system wake-up at user-defined intervals.

#### 3.6.5 Watchdog Timer (WDOG)

The watchdog timer can act both as an independent watchdog or as a watchdog synchronous with the CPU clock. It has windowed monitoring capabilities, and can generate a reset or different interrupts depending on the failure mode of the system. The watchdog can also monitor autonomous systems driven by the Peripheral Reflex System (PRS).

#### 3.7 Communications and Other Digital Peripherals

#### 3.7.1 Universal Synchronous/Asynchronous Receiver/Transmitter (USART)

The Universal Synchronous/Asynchronous Receiver/Transmitter is a flexible serial I/O module. It supports full duplex asynchronous UART communication with hardware flow control as well as RS-485, SPI, MicroWire and 3-wire. It can also interface with devices supporting:

- ISO7816 SmartCards

- IrDA

- 1<sup>2</sup>S

#### 3.7.2 Enhanced Universal Synchronous/Asynchronous Receiver/Transmitter (EUSART)

The Enhanced Universal Synchronous/Asynchronous Receiver/Transmitter supports full duplex asynchronous UART communication with hardware flow control, RS-485, and IrDA support. The EUSART also supports high-speed SPI. In EM0 and EM1 the EUSART provides a high-speed, buffered communication interface.

When routed to GPIO ports A or B, the EUSART0 may also be used in a low-energy mode and operate in EM2. A 32.768 kHz clock source allows full duplex UART communication up to 9600 baud. EUSART0 can also act as a SPI secondary device in EM2 and EM3, and wake the system when data is received from an external bus controller.

#### 3.7.3 Inter-Integrated Circuit Interface (I<sup>2</sup>C)

The I<sup>2</sup>C module provides an interface between the MCU and a serial I<sup>2</sup>C bus. It is capable of acting as a main or secondary interface and supports multi-drop buses. Standard-mode, fast-mode and fast-mode plus speeds are supported, allowing transmission rates from 10 kbit/s up to 1 Mbit/s. Bus arbitration and timeouts are also available, allowing implementation of an SMBus-compliant system. The interface provided to software by the I<sup>2</sup>C module allows precise timing control of the transmission process and highly automated transfers. Automatic recognition of addresses is provided in active and low energy modes. Note that not all instances of I<sup>2</sup>C are available in all energy modes.

#### 3.7.4 Peripheral Reflex System (PRS)

The Peripheral Reflex System provides a communication network between different peripheral modules without software involvement. Peripheral modules producing Reflex signals are called producers. The PRS routes Reflex signals from producers to consumer peripherals which in turn perform actions in response. Edge triggers and other functionality such as simple logic operations (AND, OR, NOT) can be applied by the PRS to the signals. The PRS allows peripherals to act autonomously without waking the MCU core, saving power.

#### 3.8 Secure Vault Features

A dedicated hardware secure engine containing its own CPU enables the Secure Vault functions. It isolates cryptographic functions and data from the host Cortex-M33 core, and provides several additional security features. The EFR32MG24 family includes devices with Secure Vault High and Secure Vault Mid capabilities, which are summarized in the table below.

| Feature                                                 | Secure Vault Mid                                                                                              | Secure Vault High                                                                                                      |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| True Random Number Generator (TRNG)                     | Yes                                                                                                           | Yes                                                                                                                    |

| Secure Boot with Root of Trust and Secure Loader (RTSL) | Yes                                                                                                           | Yes                                                                                                                    |

| Secure Debug with Lock/Unlock                           | Yes                                                                                                           | Yes                                                                                                                    |

| DPA Countermeasures                                     | Yes                                                                                                           | Yes                                                                                                                    |

| Anti-Tamper                                             |                                                                                                               | Yes                                                                                                                    |

| Secure Attestation                                      |                                                                                                               | Yes                                                                                                                    |

| Secure Key Management                                   |                                                                                                               | Yes                                                                                                                    |

| Symmetric Encryption                                    | <ul> <li>AES 128 / 192 / 256 bit</li> <li>ECB, CTR, CBC, CFB, CCM, GCM,<br/>CBC-MAC, and GMAC</li> </ul>      | <ul> <li>AES 128 / 192 / 256 bit</li> <li>ECB, CTR, CBC, CFB, CCM, GCM, CBC-MAC, and GMAC</li> <li>ChaCha20</li> </ul> |

| Public Key Encryption - ECDSA / ECDH /<br>EdDSA         | <ul> <li>p192 and p256</li> <li>Curve25519 (ECDH)<sup>1</sup></li> <li>Ed25519 (EdDSA)<sup>1</sup></li> </ul> | <ul> <li>p192, p256, p384 and p521</li> <li>Curve25519 (ECDH)</li> <li>Ed25519 (EdDSA)</li> </ul>                      |

| Key Derivation                                          | ECJ-PAKE p192 and p256                                                                                        | <ul> <li>ECJ-PAKE p192, p256, p384, and p521</li> <li>PBKDF2</li> <li>HKDF</li> </ul>                                  |

| Hashes                                                  | • SHA-1<br>• SHA-2/256                                                                                        | <ul> <li>SHA-1</li> <li>SHA-2 256, 384, and 512</li> <li>Poly1305</li> </ul>                                           |

#### **Table 3.1. Secure Vault Features**

#### Note:

1. These curves are supported in devices running SE v2.1.7 and higher

#### 3.8.1 Secure Boot with Root of Trust and Secure Loader (RTSL)

The Secure Boot with RTSL authenticates a chain of trusted firmware that begins from an immutable memory (ROM).

It prevents malware injection, prevents rollback, ensures that only authentic firmware is executed, and protects Over The Air updates.

For more information about this feature, see AN1218: Series 2 Secure Boot with RTSL.

#### 3.8.2 Cryptographic Accelerator

The Cryptographic Accelerator is an autonomous hardware accelerator with Differential Power Analysis (DPA) countermeasures to protect keys.

It supports AES encryption and decryption with 128/192/256-bit keys, ChaCha20 encryption, and Elliptic Curve Cryptography (ECC) to support public key operations, and hashes.

Supported block cipher modes of operation for AES include:

- ECB (Electronic Code Book)

- CTR (Counter Mode)

- CBC (Cipher Block Chaining)

- CFB (Cipher Feedback)

- GCM (Galois Counter Mode)

- CCM (Counter with CBC-MAC)

- CBC-MAC (Cipher Block Chaining Message Authentication Code)

- GMAC (Galois Message Authentication Code)

The Cryptographic Accelerator accelerates Elliptical Curve Cryptography and supports the NIST (National Institute of Standards and Technology) recommended curves including P-192, P-256, P-384, and P-521 for ECDH (Elliptic Curve Diffie-Hellman) key derivation, and ECDSA (Elliptic Curve Digital Signature Algorithm) sign and verify operations. Also supported is the non-NIST Curve25519 for ECDH and Ed25519 for EdDSA (Edwards-curve Digital Signature Algorithm) sign and verify operations.

Secure Vault also supports ECJ-PAKE (Elliptic Curve variant of Password Authenticated Key Exchange by Juggling) and PBKDF2 (Password-Based Key Derivation Function 2).

Supported hashes include SHA-1, SHA-2/256/384/512 and Poly1305.

This implementation provides a fast and energy efficient solution to state of the art cryptographic needs.

#### 3.8.3 True Random Number Generator

The True Random Number Generator module is a non-deterministic random number generator that harvests entropy from a thermal energy source. It includes start-up health tests for the entropy source as required by NIST SP800-90B and AIS-31 as well as online health tests required for NIST SP800-90C.

The TRNG is suitable for periodically generating entropy to seed an approved pseudo random number generator.

#### 3.8.4 Secure Debug with Lock/Unlock

For obvious security reasons, it is critical for a product to have its debug interface locked before being released in the field.

Secure Vault also provides a secure debug unlock function that allows authenticated access based on public key cryptography. This functionality is particularly useful for supporting failure analysis while maintaining confidentiality of IP and sensitive end-user data.

For more information about this feature, see AN1190: Series 2 Secure Debug.

#### 3.8.5 DPA Countermeasures

The AES and ECC accelerators have Differential Power Analysis (DPA) countermeasures support. This makes it very expensive from a time and effort standpoint to use DPA to recover secret keys.

#### 3.8.6 Secure Key Management with PUF

Key material in Secure Vault High products is protected by "key wrapping" with a standardized symmetric encryption mechanism. This method has the advantage of protecting a virtually unlimited number of keys, limited only by the storage that is accessible by the Cortex-M33, which includes off-chip storage as well. The symmetric key used for this wrapping and unwrapping must be highly secure because it can expose all other key materials in the system. The Secure Vault Key Management system uses a Physically Unclonable Function (PUF) to generate a persistent device-unique seed key on power up to dynamically generate this critical wrapping/unwrapping key which is only visible to the AES encryption engine and is not retained when the device loses power.

#### 3.8.7 Anti-Tamper

Secure Vault High devices provide internal tamper protection which monitors parameters such as voltage, temperature, and electromagnetic pulses as well as detecting tamper of the security sub-system itself. Additionally, 8 external configurable tamper pins support external tamper sources, such as enclosure tamper switches.

For each tamper event, the user is able to select the severity of the tamper response ranging from an interrupt, to a reset, to destroying the PUF reconstruction data which will make all protected key materials un-recoverable and effectively render the device inoperable. The tamper system also has an internal resettable event counter with programmable trigger threshold and refresh periods to mitigate false positive tamper events.

For more information about this feature, see AN1247: Anti-Tamper Protection Configuration and Use.

#### 3.8.8 Secure Attestation

Secure Vault High products support Secure Attestation, which begins with a secure identity that is created during the Silicon Labs manufacturing process. During device production, each device generates its own public/private keypair and securely stores the wrapped private key into immutable OTP memory and this key never leaves the device. The corresponding public key is extracted from the device and inserted into a binary DER-encoded X.509 device certificate, which is signed into a Silicon Labs CA chain and then programmed back into the chip into an immutable OTP memory.

The secure identity can be used to authenticate the chip at any time in the life of the product. The production certification chain can be requested remotely from the product. This certification chain can be used to verify that the device was authentically produced by Silicon Labs. The device unique public key is also bound to the device certificate in the certification chain. A challenge can be sent to the chip at any point in time to be signed by the device private key. The public key in the device certificate can then be used to verify the challenge response, proving that the device has access to the securely-stored private key, which prevents counterfeit products or impersonation attacks.

For more information about this feature, see AN1268: Authenticating Silicon Labs Devices Using Device Certificates.

#### 3.9 Analog

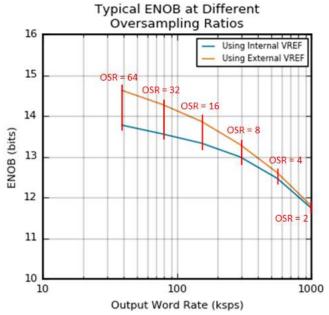

#### 3.9.1 Analog to Digital Converter (IADC)

The IADC is a hybrid architecture combining techniques from both SAR and Delta-Sigma style converters. Flexible controls allow finetuned performance and speed to meet the needs of a wide variety of applications. Hardware oversampling reduces system-level noise over multiple front-end samples. The IADC includes integrated voltage reference options. Inputs are selectable from a wide range of sources, including pins configurable as either single-ended or differential.

The IADC supports three operational modes:

- Normal Mode (all devices): Flexible speed and performance, 12-16 bits output resolution

- 11.7 bits ENOB performance at 1 Msps (OSR = 2)

- 14.3 bits ENOB performance at 76.9 ksps (OSR = 32)

- High Speed Mode (select devices): Doubles output speed of Normal mode with similar performance, 12-16 bits output resolution

- 11.7 bits ENOB performance at 2 Msps (OSR = 2)

- 14.3 bits ENOB performance at 153.8 ksps (OSR = 32)

- High Accuracy Mode (select devices): Optimized for low-rate, high performance applications, with 20 bit output resolution

- 16 bits ENOB performance at 3.8 ksps (OSR = 256)

- 15 bits ENOB performance at 15.3 ksps (OSR = 64)

#### 3.9.2 Analog Comparator (ACMP)

The Analog Comparator is used to compare the voltage of two analog inputs, with a digital output indicating which input voltage is higher. Inputs are selected from among internal references and external pins. The tradeoff between response time and current consumption is configurable by software. Two 6-bit reference dividers allow for a wide range of internally-programmable reference sources. The ACMP can also be used to monitor the supply voltage. An interrupt can be generated when the supply falls below or rises above the programmable threshold.

#### 3.9.3 Digital to Analog Converter (VDAC)

The Digital to Analog Converter (VDAC) can convert a digital value to an analog output voltage. The VDAC is a fully differential, 500 ksps, 12-bit converter. The VDAC may be used for a number of different applications such as sensor interfaces or sound output. The VDAC can generate high-resolution analog signals while the MCU is operating at low frequencies and with low total power consumption. Using DMA and a timer, the VDAC can be used to generate waveforms without any CPU intervention. The VDAC is available in all energy modes down to and including EM3.

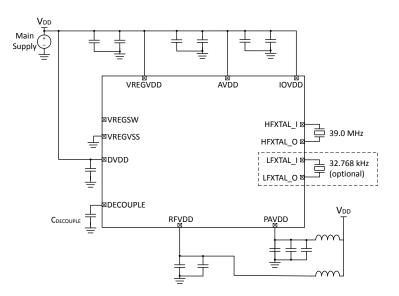

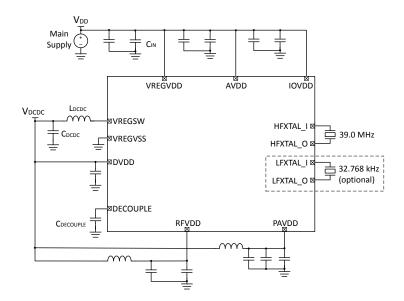

#### 3.10 Power

The EFR32MG24 has an Energy Management Unit (EMU) and efficient integrated regulators to generate internal supply voltages. Only a single external supply voltage is required, from which all internal voltages are created. An optional integrated DC-DC buck regulator can be utilized to further reduce the current consumption. The DC-DC regulator requires one external inductor and one external capacitor.

The EFR32MG24 device family includes support for internal supply voltage scaling, as well as two different power domains groups for peripherals. These enhancements allow for further supply current reductions and lower overall power consumption.

#### 3.10.1 Energy Management Unit (EMU)

The Energy Management Unit manages transitions of energy modes in the device. Each energy mode defines which peripherals and features are available and the amount of current the device consumes. The EMU can also be used to implement system-wide voltage scaling and turn off the power to unused RAM blocks to optimize the energy consumption in the target application. The DC-DC regulator operation is tightly integrated with the EMU.

#### 3.10.2 Voltage Scaling

The EFR32MG24 supports supply voltage scaling for the LDO powering DECOUPLE, with independent selections for EM0 / EM1 and EM2 / EM3. Voltage scaling helps to optimize the energy efficiency of the system by operating at lower voltages when possible. The EM0 / EM1 voltage scaling level defaults to VSCALE2, which allows the core to operate in active mode at full speed. The intermediate level, VSCALE1, allows operation in EM0 and EM1 at up to 40 MHz. The lowest level, VSCALE0, can be used to conserve power further in EM2 and EM3. The EMU will automatically switch the target voltage scaling level when transitioning between energy modes.

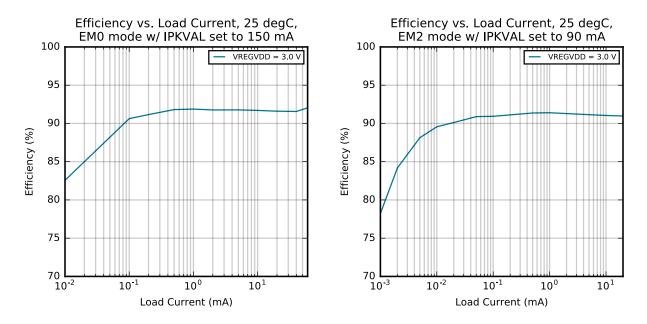

#### 3.10.3 DC-DC Converter

The DC-DC buck converter covers a wide range of load currents, providing high efficiency in energy modes EM0, EM1, EM2 and EM3. RF noise mitigation allows operation of the DC-DC converter without significantly degrading sensitivity of radio components. An on-chip supply-monitor signals when the supply voltage is low to allow bypass of the regulator via programmable software interrupt. It employs soft switching at boot and DCDC regulating-to-bypass transitions to limit the max supply slew-rate and mitigate inrush current.

#### 3.10.4 Power Domains

Peripherals may exist on one of several independent power domains which are powered down to minimize supply current when not in use. Power domains are managed automatically by the EMU.

The lowest-energy power domain is the "high-voltage" power domain (PDHV), which supports extremely low-energy infrastructure and peripherals. Circuits powered from PDHV are always on and available in all energy modes down to EM4.

The next power domain is the low power domain (PD0), which is further divided to power subsets of peripherals. All PD0 power domains are shut down in EM4. Circuits powered from PD0 power domains may be available in EM0, EM1, EM2, and EM3.

Low power domain A (PD0A) is the base power domain for EM2 and EM3 and will always remain on in EM0-EM3. It powers the most commonly-used EM2 and EM3-capable peripherals and infrastructure required to operate in EM2 and EM3. Auxiliary PD0 power domains (PD0B, PD0C, PD0D, PD0E) power additional EM2 and EM3-capable peripherals on demand. If any peripherals on one of the auxiliary power domains is enabled, that power domain will be active in EM2 and EM3. Otherwise, the auxiliary PD0 power domains will be shut down to reduce current.

Note: Power domain PD0E is also turned on when peripherals on PD0B, PD0C, or PD0D are used.

The active power domain (PD1) powers the rest of the device circuitry, including the CPU core and EM0 / EM1 peripherals. PD1 is always powered on in EM0 and EM1. PD1 is always shut down in EM2, EM3, and EM4.

Table 3.2 Peripheral Power Subdomains on page 18 shows the peripherals on the PDHV and PD0x domains. Any peripheral not listed is on PD1.

| Always On in EM2/EM3            |                        | Selectively On in EM2/3 |                                    |                   |         |  |  |

|---------------------------------|------------------------|-------------------------|------------------------------------|-------------------|---------|--|--|

| PDHV <sup>1</sup>               | PD0A                   | PD0B <sup>2</sup>       | PD0C <sup>2</sup>                  | PD0D <sup>2</sup> | PD0E    |  |  |

| LFRCO (Non-preci-<br>sion Mode) | SYSRTC                 | LETIMER0                | LFRCO (Precision Calibration Mode) | DEBUG             | GPIO    |  |  |

| LFXO                            | FSRCO                  | IADC0                   | HFRCOEM23                          | WDOG0/1           | KEYSCAN |  |  |

| BURTC                           |                        | PCNT0                   | HFXO                               | EUSART0           | PRS     |  |  |

| BURAM                           |                        | ACMP0/1                 |                                    | I2C0              |         |  |  |

| ULFRCO                          |                        | VDAC0/1                 |                                    |                   |         |  |  |

| Note:<br>1. Peripherals on P    | DHV are also available | in EM4.                 |                                    |                   | ,       |  |  |

#### Table 3.2. Peripheral Power Subdomains

2. If any of PD0B, PD0C, or PD0D are enabled, PD0E will also be automatically enabled.

#### 3.11 Reset Management Unit (RMU)

The RMU is responsible for handling reset of the EFR32MG24. A wide range of reset sources are available, including several power supply monitors, pin reset, software controlled reset, core lockup reset, and watchdog reset.

#### 3.12 Core, Memory, and Accelerators

#### 3.12.1 Processor Core

The ARM Cortex-M processor includes a 32-bit RISC processor integrating the following features and tasks in the system:

- ARM Cortex-M33 RISC processor achieving 1.50 Dhrystone MIPS/MHz

- ARM TrustZone security technology

- Embedded Trace Macrocell (ETM) for real-time trace and debug

- Up to 1536 kB flash program memory

- · Up to 256 kB RAM data memory

- · Configuration and event handling of all modules

- · 2-pin Serial-Wire debug interface

#### 3.12.2 Memory System Controller (MSC)

The Memory System Controller (MSC) is the program memory unit of the microcontroller. The flash memory is readable and writable from both the Cortex-M33 and LDMA. In addition to the main flash array where Program code is normally written the MSC also provides an Information block where additional information such as special user information or flash-lock bits are stored. There is also a readonly page in the information block containing system and device calibration data. Read and write operations are supported in energy modes EM0 Active and EM1 Sleep.

#### 3.12.3 Linked Direct Memory Access Controller (LDMA)

The Linked Direct Memory Access (LDMA) controller allows the system to perform memory operations independently of software. This reduces both energy consumption and software workload. The LDMA allows operations to be linked together and staged, enabling so-phisticated operations to be implemented.

#### 3.12.4 Matrix Vector Processor (MVP)

The Matrix Vector Processor (MVP) is designed to offload the major computationally intensive floating point operations, particularly matrixed complex floating point multiplications and additions. The MVP supports the acceleration of the key Angle-of-Arrival (AoA) MUSIC (MUltiple SIgnal Classification) algorithm computations, as well as other heavily floating-point computational problems such as Machine Learning (ML) or linear algebra.

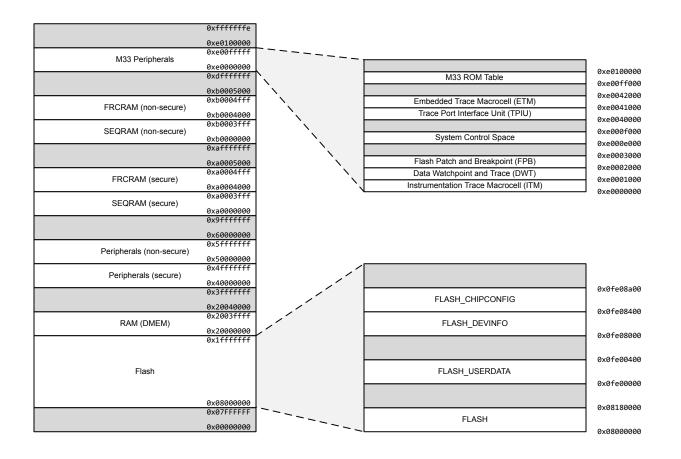

#### 3.13 Memory Map

The EFR32MG24 memory map is shown in the figures below. RAM and flash sizes are for the largest memory configuration.

Figure 3.2. EFR32MG24 Memory Map — Core Peripherals and Code Space

#### 3.14 Configuration Summary

The features of the EFR32MG24 are a subset of the feature set described in the device reference manual. The table below describes device specific implementation of the features. Remaining modules support full configuration. Refer to the Energy Modes table in the Reference Manual EMU Chapter for a more comprehensive list of energy mode support for all device peripherals.

#### Table 3.3. Configuration Summary

| Module   | Lowest Energy Mode                                                             | Configuration                   |

|----------|--------------------------------------------------------------------------------|---------------------------------|

| I2C0     | EM1 - Full functionality                                                       |                                 |

|          | EM2/3 <sup>1</sup> - Functionality limited to receive address recog-<br>nition |                                 |

| I2C1     | EM1 - Full functionality                                                       |                                 |

| LETIMER0 | EM2/3 <sup>1</sup>                                                             | 24-bit, 2-channels              |

| TIMER0   | EM1                                                                            | 32-bit, 3-channels, +DTI        |

| TIMER1   | EM1                                                                            | 32-bit, 3-channels, +DTI        |

| TIMER2   | EM1                                                                            | 16-bit, 3-channels, +DTI        |

| TIMER3   | EM1                                                                            | 16-bit, 3-channels, +DTI        |

| TIMER4   | EM1                                                                            | 16-bit, 3-channels, +DTI        |

| EUSART0  | EM1 - Full high-speed operation, all modes                                     | UART, SPI, IrDA, DALI           |

|          | EM2 <sup>1</sup> - Low-energy UART operation, 9600 Baud                        |                                 |

|          | EM2/3 <sup>1</sup> - Low-energy SPI secondary receiver                         |                                 |

| EUSART1  | EM1                                                                            | UART, SPI, IrDA, DALI           |

| USART0   | EM1                                                                            | UART, SPI, IrDA, I2S, SmartCard |

|          |                                                                                |                                 |

#### Note:

1. EM2 and EM3 operation is only supported for digital peripheral I/O on Port A and Port B. All GPIO ports support digital peripheral operation in EM0 and EM1.

# 4. Electrical Specifications

#### 4.1 Electrical Characteristics

All electrical parameters in all tables are specified under the following conditions, unless stated otherwise:

- Typical values are based on T<sub>A</sub>=25 °C and all supplies at 3.0 V, by production test and/or technology characterization.

- Radio performance numbers are measured in conducted mode, based on Silicon Laboratories reference designs using output power-specific external RF impedance-matching networks for interfacing to a 50 Ω antenna.

- Minimum and maximum values represent the worst conditions across supply voltage, process variation, and operating temperature, unless stated otherwise.

Due to on-chip circuitry (e.g., diodes), some EFR32MG24 power supply pins have a dependent relationship with one or more other power supply pins. These internal relationships between the external voltages applied to the various EFR32MG24 supply pins are defined below. Exceeding the below constraints can result in damage to the device and/or increased current draw.

- VREGVDD and DVDD

- In systems using the DCDC converter, DVDD (the buck converter output) should not be driven externally and VREGVDD (the buck converter input) must be greater than DVDD (VREGVDD ≥ DVDD)

- In systems not using the DCDC converter, DVDD must be shorted to VREGVDD on the PCB (VREGVDD = DVDD)

- AVDD, IOVDD: No dependency with each other or any other supply pin. Additional leakage may occur if DVDD remains unpowered with power applied to these supplies.

- DVDD ≥ DECOUPLE

- PAVDD ≥ RFVDD

#### 4.2 Absolute Maximum Ratings

Stresses beyond those listed below may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions beyond those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. For more information on the available quality and reliability data, see the Quality and Reliability Monitor Report at http://www.silabs.com/support/quality/pages/default.aspx.

#### Table 4.1. Absolute Maximum Ratings

| Parameter                              | Symbol               | Test Condition | Min  | Тур | Max                      | Unit   |

|----------------------------------------|----------------------|----------------|------|-----|--------------------------|--------|

| Storage temperature range              | T <sub>STG</sub>     |                | -50  | _   | +150                     | °C     |

| Voltage on any supply pin <sup>1</sup> | V <sub>DDMAX</sub>   |                | -0.3 |     | 3.8                      | V      |

| Junction temperature                   | T <sub>JMAX</sub>    | -I grade       | _    |     | +125                     | °C     |

| Voltage ramp rate on any supply pin    | Vddrampmax           |                | _    |     | 1.0                      | V / µs |

| Voltage on HFXO pins                   | V <sub>HFXOPIN</sub> |                | -0.3 | _   | 1.2                      | V      |

| DC voltage on any GPIO pin             | V <sub>DIGPIN</sub>  |                | -0.3 | _   | V <sub>IOVDD</sub> + 0.3 | V      |

| DC voltage on RESETn pin <sup>2</sup>  | V <sub>RESETn</sub>  |                | -0.3 | _   | 3.8                      | V      |

| DC voltage on RF pin<br>RF2G4_IO       | V <sub>MAX2G4</sub>  |                | -0.3 |     | 1.2                      | V      |

| Total current into VDD power lines     | I <sub>VDDMAX</sub>  | Source         | -    |     | 200                      | mA     |

| Total current into VSS ground lines    | I <sub>VSSMAX</sub>  | Sink           | -    |     | 200                      | mA     |

| Current per I/O pin                    | I <sub>IOMAX</sub>   | Sink           | _    |     | 50                       | mA     |

|                                        |                      | Source         | _    | —   | 50                       | mA     |

| Current for all I/O pins               | IIOALLMAX            | Sink           | _    | —   | 200                      | mA     |

|                                        |                      | Source         | _    |     | 200                      | mA     |

Note:

1. The maximum supply voltage on VREGVDD is limited under certain conditions when using the DC-DC. See the DC-DC specifications for more details.

2. The RESETn pin has a pull-up device to the DVDD supply. For minimum leakage, RESETn should not exceed the voltage at DVDD.

#### 4.3 General Operating Conditions

| Parameter                                        | Symbol                   | Test Condition                                                                             | Min  | Тур  | Max                | Unit |

|--------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------|------|------|--------------------|------|

| Operating ambient tempera-<br>ture range         | T <sub>A</sub>           | -I temperature grade <sup>1</sup>                                                          | -40  | _    | +125               | °C   |

| DVDD supply voltage                              | V <sub>DVDD</sub>        | EM0/1                                                                                      | 1.71 | 3.0  | 3.8                | V    |

|                                                  |                          | EM2/3/4 <sup>2</sup>                                                                       | 1.71 | 3.0  | 3.8                | V    |

| AVDD supply voltage                              | V <sub>AVDD</sub>        | AVDDBODEN=0 <sup>3</sup>                                                                   | 1.71 | 3.0  | 3.8                | V    |

| IOVDDx operating supply voltage (All IOVDD pins) | VIOVDDx                  | IOVDDxBODEN=0 <sup>3</sup>                                                                 | 1.71 | 3.0  | 3.8                | V    |

| RFVDD operating supply voltage                   | V <sub>RFVDD</sub>       |                                                                                            | 1.71 | 3.0  | V <sub>PAVDD</sub> | V    |

| VREGVDD operating supply                         | V <sub>VREGVDD</sub>     | DC-DC in regulation <sup>4</sup>                                                           | 2.2  | 3.0  | 3.8                | V    |

| voltage                                          |                          | DC-DC in bypass 60 mA load                                                                 | 1.8  | 3.0  | 3.8                | V    |

|                                                  |                          | DC-DC in bypass 120 mA load                                                                | 1.8  | 3.0  | 3.8                | V    |

|                                                  |                          | DC-DC not in use. DVDD exter-<br>nally shorted to VREGVDD                                  | 1.71 | 3.0  | 3.8                | V    |

| PAVDD operating supply voltage                   | V <sub>PAVDD</sub>       |                                                                                            | 1.71 | 3.0  | 3.8                | V    |

| DECOUPLE output capaci-<br>tor <sup>5</sup>      | C <sub>DECOUPLE</sub>    | $1.0 \ \mu\text{F} \pm 10\% \ \text{X8L}$ capacitor used for performance characterization. | 1.0  | _    | 2.75               | μF   |

| HCLK and SYSCLK frequen-                         | f <sub>HCLK</sub>        | VSCALE2, MODE = WS1                                                                        | _    | _    | 78                 | MHz  |

| су                                               |                          | VSCALE2, MODE = WS0                                                                        | _    | _    | 40                 | MHz  |

|                                                  |                          | VSCALE1, MODE = WS1                                                                        | _    | _    | 40                 | MHz  |

|                                                  |                          | VSCALE1, MODE = WS0                                                                        | _    | _    | 20                 | MHz  |

| PCLK frequency                                   | f <sub>PCLK</sub>        | VSCALE2 or VSCALE1                                                                         | _    | _    | 40                 | MHz  |

| EM01 Group A clock fre-                          | f <sub>EM01GRPACLK</sub> | VSCALE2                                                                                    | _    | _    | 78                 | MHz  |

| quency                                           |                          | VSCALE1                                                                                    | _    | _    | 40                 | MHz  |

| EM01 Group C clock fre-                          | f <sub>EM01GRPCCLK</sub> | VSCALE2                                                                                    | _    | _    | 78                 | MHz  |

| quency                                           |                          | VSCALE1                                                                                    | _    | _    | 40                 | MHz  |

| Radio HCLK frequency <sup>6</sup>                | f <sub>RHCLK</sub>       | VSCALE2 or VSCALE1                                                                         | _    | 39.0 | _                  | MHz  |