19-4375; Rev 1; 5/10

## **General Description**

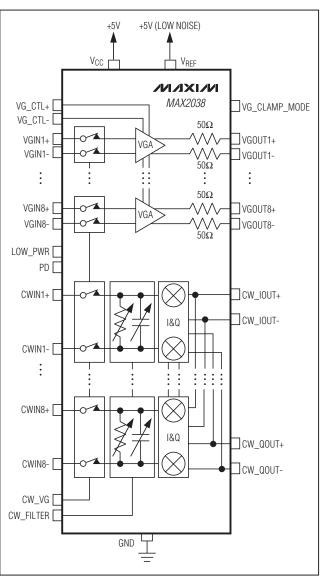

The MAX2038 8-channel variable-gain amplifier (VGA) and programmable octal mixer array is designed for high linearity, high dynamic range, and low noise performance targeting ultrasound imaging and Doppler applications. Each amplifier features differential inputs and outputs and a total gain range of 42dB (typ). In addition, the VGAs offer very low output-referred noise performance suitable for interfacing with 12-bit ADCs.

EVALUATION KIT AVAILABLE

The MAX2038 VGA is optimized for less than  $\pm 0.25$ dB absolute gain error to ensure minimal channel-to-channel ultrasound beamforming focus error. The device's differential outputs are designed to directly drive ultrasound ADCs through an external passive anti-aliasing filter. A switchable clamp is also provided at each amplifier's output to limit the output signals, thereby preventing ADC overdrive or saturation.

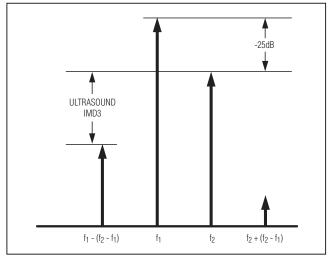

Dynamic performance of the device is optimized to reduce distortion to support second-harmonic imaging. The device achieves a second-harmonic distortion specification of -70dBc at V<sub>OUT</sub> = 1.5V<sub>P-P</sub> and f<sub>IN</sub> = 5MHz and an ultrasound-specific\*, two-tone, third-order intermodulation distortion specification of -52dBc at V<sub>OUT</sub> = 1.5V<sub>P-P</sub> and f<sub>IN</sub> = 5MHz.

The MAX2038 also integrates an octal quadrature mixer array and programmable LO phase generators for a complete CW beamforming solution. The LO phase selection for each channel can be programmed using a digital serial interface and a single high-frequency clock or the LOs for each complex mixer pair can be directly driven using separate 4 x LO clocks. The serial interface is designed to allow multiple devices to be easily daisy chained to minimize program interface wiring. The LO phase dividers can be programmed to allow 4, 8, or 16 quadrature phases. The input path of each CW mixer consists of a selectable lowpass filter for optimal CWD noise performance. The outputs of the mixers are summed into I and Q differential current outputs. The mixers and LO generators are designed to have exceptionally low noise performance of -155dBc/Hz at 1kHz offset from a 1.25MHz carrier.

The MAX2038 operates from a +5.0V power supply, consuming only 120mW/channel in VGA mode and 269mW/channel in normal power CW mode. A low-power CW mode is also available and consumes only 226mW/channel. The device is available in a lead-free 100-pin TQFP package (14mm x 14mm x 1mm) with an exposed pad. Electrical performance is guaranteed over a 0°C to +70°C temperature range.

### **Applications**

Ultrasound Imaging Sonar

##

## \_Features

- 8-Channel Configuration

- High Integration for Ultrasound Imaging Applications

- Pin Compatible with the MAX2037 Ultrasound VGA

### **VGA** Features

- Maximum Gain, Gain Range, and Output-Referred Noise Optimized for Interfacing with 12-Bit ADCs Maximum Gain of 29.5dB Total Gain Range of 42dB 22nV/\Hz Ultra-Low Output-Referred Noise at 5MHz

- ♦ ±0.25dB Absolute Gain Error

- ♦ 120mW Consumption per Channel

- Switchable Output VGA Clamp Eliminating ADC Overdrive

- Fully Differential VGA Outputs for Direct ADC Drive

- Variable Gain Range Achieves 42dB Dynamic Range

- -70dBc HD2 at VOUT = 1.5VP-P and fIN = 5MHz

- Two-Tone Ultrasound-Specific\* IMD3 of -52dBc at VOUT = 1.5Vp-p and fIN = 5MHz

### **CW Doppler Mixer Features**

- Low Mixer Noise of -155dBc/Hz at 1kHz Offset from 1.25MHz Carrier

- Serial-Programmable LO Phase Generator for 4, 8, 16 LO Quadrature Phase Resolution

- Optional Individual Channel 4 x fLO LO Input Drive Capability

- 269mW Power Consumption per Channel (Normal Power Mode) and 226mW Power Consumption per Channel (Low-Power Mode)

## **Ordering Information**

| PART          | TEMP RANGE   | PIN-PACKAGE  |  |  |

|---------------|--------------|--------------|--|--|

| MAX2038CCQ+D  | 0°C to +70°C | 100 TQFP-EP* |  |  |

| MAX2038CCQ+TD | 0°C to +70°C | 100 TQFP-EP* |  |  |

+Denotes a lead(Pb)-free/RoHS-compliant package. D = Dry packing.

T = Tape and reel.

\*EP = Exposed pad.

\*See the Ultrasound-Specific IMD3 Specification in the Applications Information section.

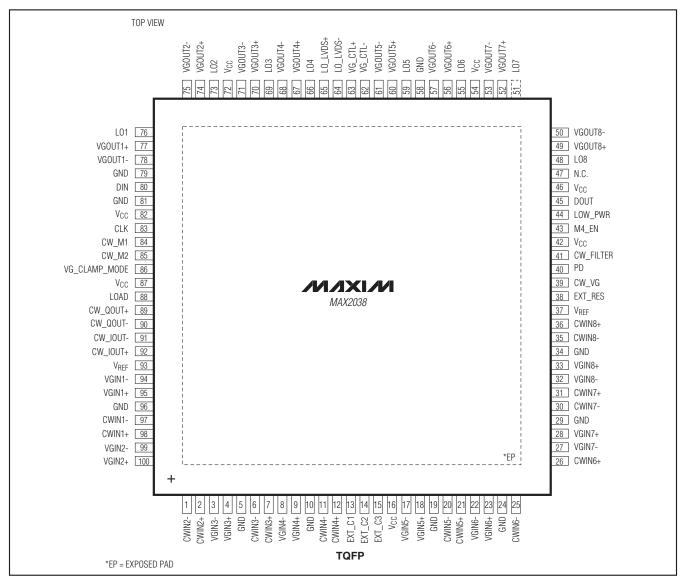

Pin Configuration appears at end of data sheet.

\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> , V <sub>REF</sub> to GND0.3V to +5.5V<br>Any Other Pins to GND0.3V to (V <sub>CC</sub> + 0.3V)<br>CW Mixer Output Voltage to GND (CW_IOUT+, CW_IOUT-, |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CW_QOUT+, CW_QOUT-)13V                                                                                                                                                 |  |

| VGA Differential Input Voltage (VGIN_+, VGIN)8.0VP-P<br>Analog Gain Control Differential Input Voltage                                                                 |  |

| (VG_CTL+, VG_CTL-)8.0VP-P<br>CW Mixer Differential Input Voltage                                                                                                       |  |

| (CWIN_+, CWIN)8.0VP-P                                                                                                                                                  |  |

| CW Mixer LVDS LO Differential Input Voltage           |  |

|-------------------------------------------------------|--|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |  |

| 100-Pin TQFP (derated 45.5mW/°C above +70°C)3636.4mW  |  |

| Dperating Temperature Range0°C to +70°C               |  |

| lunction Temperature+150°C                            |  |

| OJC (Note 1)+2°C/W                                    |  |

| OJA (Note 1)+22°C/W                                   |  |

| Storage Temperature Range40°C to +150°C               |  |

| _ead Temperature (soldering, 10s)+300°C               |  |

| Soldering Temperature (reflow)+260°C                  |  |

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to <u>www.maxim-ic.com/thermal-tutorial</u>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## DC ELECTRICAL CHARACTERISTICS-VGA MODE

(*Typical Application Circuit*, Figure 7. V<sub>CC</sub> = V<sub>REF</sub> = 4.75V to 5.25V, V<sub>CM</sub> = (3/5)V<sub>REF</sub>, T<sub>A</sub> = 0°C to +70°C, V<sub>GND</sub> = 0V, LOW\_PWR = 0, M4\_EN = 0, CW\_FILTER = 0 or 1, TEST\_MODE = 0, PD = 0, CW\_VG = 1, CW\_M1 = 0, CW\_M2 = 0, no RF signals applied, capacitance to GND at each of the VGA differential outputs is 60pF, differential capacitance across the VGA outputs is 10pF, R<sub>L</sub> = 1k $\Omega$ , CW mixer outputs pulled up to +11V through four separate ±0.1% 115 $\Omega$  resistors, all CW channels programmed off. Typical values are at V<sub>CC</sub> = V<sub>REF</sub> = 5V, T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 2)

| PARAMETER                                          | SYMBOL | CONDTION                   | MIN    | ТҮР  | MAX | UNITS |      |

|----------------------------------------------------|--------|----------------------------|--------|------|-----|-------|------|

| VGA MODE                                           |        | ·                          |        |      |     |       |      |

| Supply Voltage Range                               | Vcc    |                            |        | 4.75 | 5   | 5.25  | V    |

| V <sub>CC</sub> External Reference                 | VREF   | (Note 3)                   |        | 4.75 | 5   | 5.25  | V    |

| Total Power-Supply Current                         |        | Refers to VCC supply F     | PD = 0 |      | 204 | 231   | mA   |

| Total Tower-Supply Current                         |        | current plus VREF current  | PD = 1 |      | 27  | 33    | ША   |

| V <sub>CC</sub> Supply Current                     | IVCC   |                            |        |      | 192 | 216   | mA   |

| V <sub>REF</sub> Current                           | IREF   |                            |        |      | 12  | 15    | mA   |

| Current Consumption per<br>Amplifier Channel       |        | Refers to VCC supply curre | nt     |      | 24  | 27    | mA   |

| Differential Analog Control                        |        | Minimum gain               |        |      | +2  |       | \/   |

| Voltage Range                                      |        | Maximum gain               |        |      | -2  |       | VP-P |

| Differential Analog Control<br>Common-Mode Voltage | VCM    |                            |        | 2.85 | 3   | 3.15  | V    |

| Analog Control Input<br>Source/Sink Current        |        |                            |        |      | 4.5 | 5     | mA   |

| LOGIC INPUTS                                       |        |                            |        | ·    |     |       |      |

| CMOS Input High Voltage                            | VIH    |                            |        | 2.3  |     |       | V    |

| CMOS Input Low Voltage                             | VIL    |                            |        |      |     | 0.8   | V    |

## DC ELECTRICAL CHARACTERISTICS-CW MIXER MODE

(*Typical Application Circuit*, Figure 7.  $V_{CC} = V_{REF} = 4.75V$  to 5.25V,  $T_A = 0^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{GND} = 0V$ , LOW\_PWR = 0, M4\_EN = 0, CW\_FILTER = 0 or 1, TEST\_MODE = 0, PD = 0, CW\_VG = 0, CW\_M1 = 0, CW\_M2 = 0, no RF signals applied, capacitance to GND at each of the VGA differential outputs is 60pF, differential capacitance across the VGA outputs is 10pF, RL = 1k $\Omega$ , CW mixer outputs pulled up to +11V through four separate ±0.1% 115 $\Omega$  resistors. Typical values are at V<sub>CC</sub> = V<sub>REF</sub> = 5V, T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 2)

| PARAMETER SYMBOL CONDTIONS                                |                     | CONDTIONS                                                                                                                                                                                     | MIN | ТҮР          | МАХ  | UNITS             |

|-----------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------|------|-------------------|

| CW MIXER MODE                                             |                     | •                                                                                                                                                                                             |     |              |      |                   |

| Current in Full-Power Mode<br>5V V <sub>CC</sub> Supply   | ICC_FP              | Refers to V <sub>CC</sub> supply current (all 8 channels)                                                                                                                                     |     | 245          | 265  | mA                |

| Current in Full-Power Mode<br>11V V <sub>MIX</sub> Supply | I <sub>MIX_FP</sub> | Refers to $V_{MIX}$ supply current (all 8 channels)                                                                                                                                           |     | 106          | 120  | mA                |

| Current in Full-Power Mode<br>5V V <sub>REF</sub> Supply  | IREF_FP             | Refers to V <sub>REF</sub> supply current (all 8 channels)                                                                                                                                    |     | 17           | 21   | mA                |

| Power Dissipation in Full-Power<br>Mode                   | PDISS_FP            | Total power dissipation (all 8 channels including both 5V (V <sub>CC</sub> and V <sub>REF</sub> ) and 11V mixer pullup supply power dissipation in the device) (Note 4)                       |     | 2.15         | 2.41 | W                 |

| Current in Low-Power Mode<br>5V V <sub>CC</sub> Supply    | ICC_LP              | LOW_PWR = 1; refers to $V_{CC}$ supply current (all 8 channels)                                                                                                                               |     | 245          | 265  | mA                |

| Current in Low-Power Mode<br>11V V <sub>MIX</sub> Supply  | I <sub>MIX_LP</sub> | LOW_PWR = 1; refers to V <sub>MIX</sub> supply current (all 8 channels)                                                                                                                       |     | 53           | 60   | mA                |

| Current in Low-Power Mode<br>5V V <sub>REF</sub> Supply   | IREF_LP             | LOW_PWR = 1; refers to V <sub>REF</sub> supply current (all 8 channels)                                                                                                                       |     | 17           | 21   | mA                |

| Power Dissipation in Low-Power<br>Mode                    | PDISS_LP            | LOW_PWR = 1; total power dissipation<br>(all 8 channels including both 5V (V <sub>CC</sub> and<br>V <sub>REF</sub> ) and 11V mixer pullup supply power<br>dissipation in the device) (Note 4) |     | 1.81         | 2.06 | W                 |

| Mixer LVDS LO Input Common-<br>Mode Voltage               |                     | Modes 1 and 2 (Note 5)                                                                                                                                                                        |     | 1.25<br>±0.2 |      | V                 |

| LVDS LO Differential Input<br>Voltage                     |                     | Modes 1 and 2                                                                                                                                                                                 | 200 | 700          |      | mV <sub>P-P</sub> |

| LVDS LO Input<br>Common-Mode Current                      |                     | Per pin                                                                                                                                                                                       |     | 150          | 200  | μA                |

| LVDS LO Differential<br>Input Resistance                  |                     | Modes 1 and 2 (Note 6)                                                                                                                                                                        |     | 30           |      | kΩ                |

| Mixer IF Common-Mode Output<br>Current                    |                     | Common-mode current in each of the differential mixer outputs (Note 7)                                                                                                                        |     | 3.25         | 3.75 | mA                |

| DATA Output High Voltage                                  |                     | DOUT voltage when terminated in DIN<br>(daisy chain) (Note 8)                                                                                                                                 | 4.5 |              |      | V                 |

| DATA Output Low Voltage                                   |                     | DOUT voltage when terminated in DIN<br>(daisy chain) (Note 8)                                                                                                                                 |     |              | 0.5  | V                 |

## AC ELECTRICAL CHARACTERISTICS-VGA MODE

(*Typical Application Circuit*, Figure 7. V<sub>CC</sub> = V<sub>REF</sub> = 4.75V to 5.25V, V<sub>CM</sub> = (3/5)V<sub>REF</sub>, T<sub>A</sub> = 0°C to +70°C, V<sub>GND</sub> = 0V, LOW\_PWR = 0, M4\_EN = 0, CW\_FILTER = 1, TEST\_MODE = 0, PD = 0, CW\_VG = 1, CW\_M1 = 0, CW\_M2 = 0, VG\_CLAMP\_MODE = 1, f<sub>RF</sub> = f<sub>LO</sub>/16 = 5MHz, capacitance to GND at each of the VGA differential outputs is 60pF, differential capacitance across the VGA outputs is 10pF, R<sub>L</sub> = 1k $\Omega$ , CW mixer outputs pulled up to +11V through four separate ±0.1% 115 $\Omega$  resistors, differential mixer inputs are driven from a low impedance source. Typical values are at V<sub>CC</sub> = V<sub>REF</sub> = 5V, T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 2)

| PARAMETER                                 | SYMBOL  | CONDITIONS                                                                                                                                                     |                                                                     | MIN | ТҮР   | MAX  | UNITS                            |

|-------------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----|-------|------|----------------------------------|

| Mode Select Response Time                 |         | CW_VG set from log<br>(Note 9)                                                                                                                                 | gic 1 to 0 or from 0 to 1                                           |     | 2     |      | μs                               |

| VGA MODE                                  |         |                                                                                                                                                                |                                                                     |     |       |      |                                  |

| Full-Scale Bandwidth                      | f-1.3dB | 1.3dB $V_{OUT} = 1.5V_{P-P}$ ,<br>ain = 10dB $V_{OUT} = 1 k\Omega$<br>$V_{OUT} = 1.5V_{P-P}$ ,<br>at each single-ended<br>output is 60pF,<br>$R_L = 1 k\Omega$ |                                                                     |     | 18    |      | MHz                              |

|                                           |         |                                                                                                                                                                | No capacitive load $R_L = 1k\Omega$                                 |     | 29    |      |                                  |

| Small-Signal Bandwidth                    | f-1.3dB | $V_{OUT} = 1.5mV_{P-P}, 3$<br>gain = 10dB                                                                                                                      | 3dB bandwidth,                                                      |     | 30    |      | MHz                              |

| Differential Input Resistance             | RIN     |                                                                                                                                                                |                                                                     | 170 | 200   | 230  | Ω                                |

| Input Effective Capacitance               | CIN     | $f_{RF} = 10MHz$ , each                                                                                                                                        | input to ground                                                     |     | 15    |      | pF                               |

| Differential Output Resistance            | Rout    |                                                                                                                                                                |                                                                     |     | 100   |      | Ω                                |

| Maximum Gain                              |         |                                                                                                                                                                |                                                                     |     | +29.5 |      | dB                               |

| Minimum Gain                              |         |                                                                                                                                                                |                                                                     |     | -12.5 |      | dB                               |

| Gain Range                                |         |                                                                                                                                                                |                                                                     |     | 42    |      | dB                               |

| Absolute Gain Error                       |         | $T_A = +25^{\circ}C$ , full gai<br>V <sub>REF</sub> = 5V                                                                                                       | in range 0% to 100%,                                                |     | ±0.25 | ±1.5 | dB                               |

| VGA Gain Response Time                    |         | 40dB gain change                                                                                                                                               | to within 1dB final value                                           |     | 1     |      | μs                               |

| Input-Referred Noise                      |         | VG_CTL set for max<br>no input signal                                                                                                                          | kimum gain,                                                         |     | 2     |      | nV/√Hz                           |

|                                           |         |                                                                                                                                                                | No input signal                                                     |     | 22    |      |                                  |

| Output-Referred Noise                     |         | VG_CTL set for<br>+10dB of gain                                                                                                                                | V <sub>OUT</sub> = 1.5V <sub>P-P</sub> , 1kHz<br>offset             |     | 55    |      | nV/√Hz                           |

| Second Harmonic                           | HD2     | VG_CLAMP_MODE<br>+10dB of gain, f <sub>RF</sub> =                                                                                                              | = 1, VG_CTL set for<br>5MHz, V <sub>OUT</sub> = 1.5V <sub>P-P</sub> |     | -70   |      | dDo                              |

| Second Harmonic                           | HD2     | VG_CLAMP_MODE = 1, VG_CTL set for +10dB of gain, $f_{RF}$ = 10MHz, $V_{OUT}$ = 1.5VP-P                                                                         |                                                                     | -55 | -65   |      | dBc                              |

| Third-Order Intermodulation<br>Distortion | IMD3    | VG_CLT set for +10dB of gain, $f_{RF1} = 5MHz$ ,<br>$f_{RF2} = 5.01MHz$ , $V_{OUT} = 1.5V_{P-P}$ ,<br>$V_{REF} = 5V$ (Note 3)                                  |                                                                     | -40 | -52   |      | dBc                              |

| Channel-to-Channel Crosstalk              |         | V <sub>OUT</sub> = 1V <sub>P-P</sub> differ<br>VG_CTL set for +10                                                                                              |                                                                     | -80 |       | dB   |                                  |

| Maximum Output Voltage at<br>Clamp ON     |         |                                                                                                                                                                | $E = 0$ , VG_CTL set for<br>mV <sub>P-P</sub> differential input    |     | 2.4   |      | V <sub>P-P</sub><br>differential |

## AC ELECTRICAL CHARACTERISTICS-CW MIXER MODE

(*Typical Application Circuit*, Figure 7.  $V_{CC} = V_{REF} = 4.75V$  to 5.25V,  $T_A = 0^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{GND} = 0V$ ,  $LOW_PWR = 0$ ,  $M4_EN = 0$ ,  $CW_FILTER = 1$ , TEST\_MODE = 0, PD = 0,  $CW_VG = 0$ ,  $CW_M1 = 0$ ,  $CW_M2 = 0$ ,  $VG_CLAMP_MODE = 1$ ,  $f_{RF} = f_{LO}/16 = 5MHz$ , capacitance to GND at each of the VGA differential outputs is 60pF, differential capacitance across the VGA outputs is 10pF,  $R_L = 1k\Omega$ , CW mixer outputs pulled up to +11V through four separate ±0.1% 115 $\Omega$  resistors, differential mixer inputs are driven from a low impedance source. Typical values are at  $V_{CC} = V_{REF} = 5V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                                 | SYMBOL | CONDITIONS                                                                                                                                                          | MIN  | ТҮР  | МАХ | UNITS                            |  |

|-------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|----------------------------------|--|

| Maximum Output Voltage at<br>ClampOFF     |        | VG_CLAMP_MODE = 1, VG_CTL set for<br>+20dB of gain, 350mV <sub>P-P</sub> differential input                                                                         |      | 2.8  |     | V <sub>P-P</sub><br>differential |  |

| CW MIXER MODE                             |        |                                                                                                                                                                     |      |      |     |                                  |  |

| Mixer RF Frequency Range                  |        |                                                                                                                                                                     | 0.9  |      | 7.6 | MHz                              |  |

| Mixer LO Frequency Range                  |        |                                                                                                                                                                     | 1    |      | 7.5 | MHz                              |  |

| Mixer IF Frequency Range                  |        |                                                                                                                                                                     |      |      | 100 | kHz                              |  |

| Maximum Input Voltage Range               |        |                                                                                                                                                                     |      |      | 1.8 | V <sub>P-P</sub><br>differential |  |

| Differential Input Desistance             |        | CW_FILTER = 0                                                                                                                                                       |      | 633  |     |                                  |  |

| Differential Input Resistance             |        | CW_FILTER = 1                                                                                                                                                       |      | 1440 |     | Ω                                |  |

| Input-Referred Noise Voltage              |        | Mode 3, $f_{RF} = f_{LO}/4 = 1.25$ MHz, measured at a 1kHz offset frequency; clutter tone at 0.9V <sub>P-P</sub> differential measured at the mixer input           |      | 6    |     | nV/√Hz                           |  |

|                                           |        | Mode 3, RF terminated into $50\Omega$ ; f <sub>LO</sub> /4 = 1.25MHz, measured at 1kHz offset                                                                       |      | 4.6  |     |                                  |  |

| Third-Order Intermodulation<br>Distortion | IMD3   | Mode 1, $f_{RF1} = 5MHz$ at 0.9V <sub>P-P</sub> differential<br>input, Doppler tone $f_{RF2} = 5.01MHz$ at 25dBc<br>from clutter tone, $f_{LO}/16 = 5MHz$ (Note 10) |      | -50  |     | dBc                              |  |

| Mixer Output Voltage Compliance           |        | (Note 11)                                                                                                                                                           | 4.75 |      | 12  | V                                |  |

| Channel-to-Channel Phase<br>Matching      |        | Measured under zero beat conditions, $f_{RF} = 5MHz$ , $f_{LO}/16 = 5MHz$ (Note 12)                                                                                 |      | ±3.0 |     | Degrees                          |  |

| Channel-to-Channel Gain<br>Matching       |        | Measured under zero beat conditions, $f_{RF} = 5MHz$ , $f_{LO}/16 = 5MHz$ (Note 12)                                                                                 |      | ±2   |     | dB                               |  |

| Transponductance (Nate 12)                |        | CW_FILTER = 1 $f_{RF} = 1.1MHz$ , $1V_{P-P}$                                                                                                                        |      | 2.8  |     | ~~ <u>~</u>                      |  |

| Transconductance (Note 13)                |        | $CW_FILTER = 0$ differential, $f_{LO}/16 = 1MHz$                                                                                                                    |      | 2.8  |     | mS                               |  |

## AC ELECTRICAL CHARACTERISTICS-CW MIXER MODE (continued)

(*Typical Application Circuit*, Figure 7.  $V_{CC} = V_{REF} = 4.75V$  to 5.25V,  $T_A = 0^{\circ}C$  to  $+70^{\circ}C$ ,  $V_{GND} = 0V$ , LOW\_PWR = 0, M4\_EN = 0, CW\_FILTER = 1, TEST\_MODE = 0, PD = 0, CW\_VG = 0, CW\_M1 = 0, CW\_M2 = 0, VG\_CLAMP\_MODE = 1,  $f_{RF} = f_{LO}/16 = 5MHz$ , capacitance to GND at each of the VGA differential outputs is 60pF, differential capacitance across the VGA outputs is 10pF,  $R_L = 1k\Omega$ , CW mixer outputs pulled up to +11V through four separate ±0.1% 115 $\Omega$  resistors, differential mixer inputs are driven from a low impedance source. Typical values are at V<sub>CC</sub> = V<sub>REF</sub> = 5V,  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                                   | SYMBOL               | CONDITIONS | MIN | ТҮР | MAX | UNITS |  |  |  |

|---------------------------------------------|----------------------|------------|-----|-----|-----|-------|--|--|--|

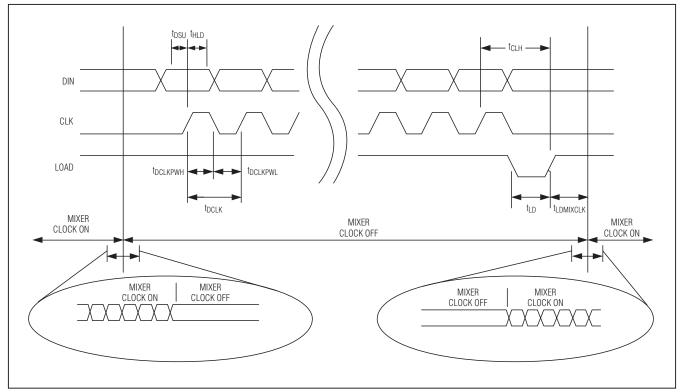

| SERIAL SHIFT REGISTER                       |                      |            |     |     |     |       |  |  |  |

| Serial Shift Register<br>Programming Rate   |                      |            |     |     | 10  | MHz   |  |  |  |

| Minimum Data Set-Up Time                    | tdsu                 |            |     | 30  |     | ns    |  |  |  |

| Minimum Data Hold Time                      | thld                 |            |     | 2   |     | ns    |  |  |  |

| Minimum Data Clock Time                     | <b>t</b> DCLK        |            |     | 100 |     | ns    |  |  |  |

| Minimum Data Clock Pulse Width<br>High      | <sup>t</sup> DCLKPWH |            |     | 30  |     | ns    |  |  |  |

| Minimum Data Clock Pulse Width<br>Low       | <sup>t</sup> DCLKPWL |            |     | 30  |     | ns    |  |  |  |

| Minimum Load Line                           | t <sub>LD</sub>      |            |     | 30  |     | ns    |  |  |  |

| Minimum Load Line High to<br>Mixer Clock On | <b>t</b> MIXCLK      |            |     | 30  |     | ns    |  |  |  |

| Minimum Data Clock to Load<br>Line High     | tCLH                 |            |     | 30  |     | ns    |  |  |  |

**Note 2:** Specifications at  $T_A = +25^{\circ}$ C and  $T_A = +70^{\circ}$ C are guaranteed by production test. Specifications at  $T_A = 0^{\circ}$ C are guaranteed by design and characterization.

**Note 3:** Noise performance of the device is dependent on the noise contribution from the supply to  $V_{REF}$ . Use a low-noise supply for  $V_{REF}$ .  $V_{CC}$  and  $V_{REF}$  can be connected together to share the same supply voltage if the supply for  $V_{CC}$  exhibits low noise.

Note 4: Total on-chip power dissipation is calculated as PDISS = V<sub>CC</sub> x I<sub>CC</sub> + V<sub>REF</sub> x I<sub>REF</sub> + [11V - (I<sub>MIX</sub>/4) x 115] x I<sub>MIX</sub>.

**Note 5:** Note that the LVDS CWD LO clocks are DC-coupled. This is to ensure immediate synchronization when the clock is first turned on. An AC-coupled LO is problematic in that the RC time constant associated with the coupling capacitors and the input impedance of the pin causes there to be a period of time (related to the RC time constant) when the DC level on the chip side of the capacitor is outside the acceptable common-mode range and the LO swing does not exceed both the logic thresholds required for proper operation. This problem associated with AC-coupling would cause an inability to ensure synchronization among beam-forming channels. The LVDS signal is terminated differentially with an external 100Ω resistor on the board.

**Note 6:** External  $100\Omega$  resistor terminates the LVDS differential signal path.

- **Note 7:** The mixer common-mode current (3.25mA/channel) is specified as the common-mode current in each of the differential mixer outputs (CW\_QOUT+, CW\_IOUT+, CW\_IOUT+, CW\_IOUT-).

- Note 8: Specification guaranteed only for DOUT driving DIN of the next device in a daisy-chain fashion.

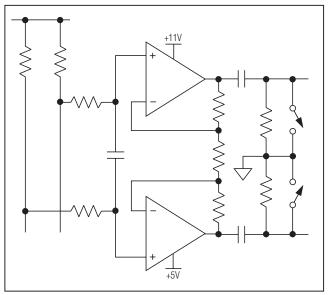

- **Note 9:** This response time does not include the CW output highpass filter. When switching to VGA mode, the CW outputs stop drawing current and the output voltage goes to the rail. If a highpass filter is used, the recovery time can be excessive and a switching network is recommended as shown in the *Applications Information* section.

- Note 10: See the Ultrasound-Specific IMD3 Specification in the Applications Information section.

- Note 11: Mixer output-voltage compliance is the range of acceptable voltages allowed on the CW mixer outputs.

- Note 12: Channel-to-channel gain-and-phase matching measured on 30 pieces during engineering characterization at room temperature. Each mixer is used as a phase detector and produces a DC voltage in the IQ plane. The phase is given by the angle of the vector drawn on that plane. Multiple channels from multiple parts are compared to each other to produce the phase variation.

- Note 13: Transconductance is defined as the quadrature summing of the CW differential output current at baseband divided by the mixer's input voltage.

AX2038

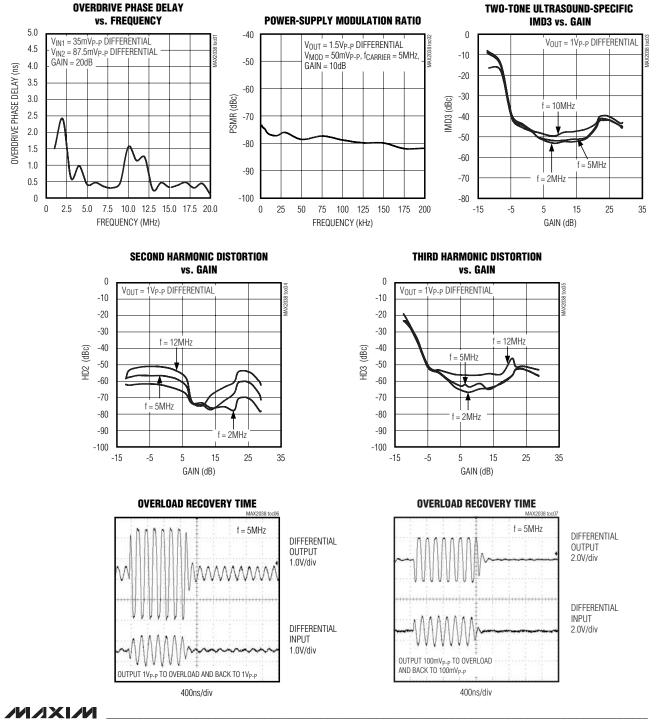

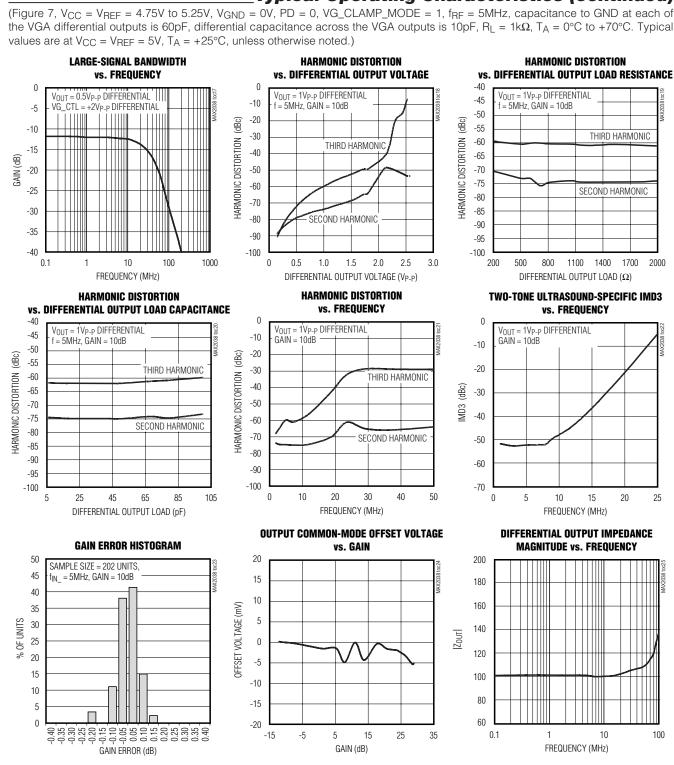

## **Typical Operating Characteristics**

(Figure 7, V<sub>CC</sub> = V<sub>REF</sub> = 4.75V to 5.25V, V<sub>GND</sub> = 0V, PD = 0V, VG\_CLAMP\_MODE = 1, f<sub>RF</sub> = 5MHz, capacitance to GND at each of the VGA differential outputs is 60pF, differential capacitance across the VGA outputs is 10pF,  $R_L = 1k\Omega$ ,  $T_A = 0^{\circ}C$  to +70°C. Typical values are at  $V_{CC} = V_{REF} = 5V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

MAX2038

values are at  $V_{CC} = V_{REF} = 5V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

# **MAX2038**

#### **CHANNEL-TO-CHANNEL CROSSTALK OUTPUT-REFERRED NOISE VOLTAGE CHANNEL-TO-CHANNEL CROSSTALK** vs. FREQUENCY vs. GAIN vs. GAIN 50 -60 -30 $V_{OUT} = 1V_{P-P}$ DIFFERENTIAL $V_{OUT} = 1.5V_{P-P}$ DIFFERENTIAL OUTPUT-REFERRED NOISE VOLTAGE (nV/VHz) f = 5MHzGAIN = 10dB, ADJACENT CHANNELS f = 10MHz, ADJACENT CHANNELS -40 -65 40 -70 -50 (gB) CROSSTALK (dB -75 -60 30 CROSSTALK -80 -70 20 -80 -85 -90 -90 10 -100 -95 -110 0 -100 -15 -5 5 15 25 35 -15 -5 5 15 25 35 1 10 100 FREQUENCY (MHz) GAIN (dB) GAIN (dB) GAIN vs. DIFFERENTIAL ANALOG LARGE-SIGNAL BANDWIDTH LARGE-SIGNAL BANDWIDTH CONTROL VOLTAGE (VG\_CTL) vs. FREQUENCY vs. FREQUENCY 35 40 30 $V_{OUT} = 1.5 V_{P-P} DIFFERENTIAL$ $V_{OUT} = 1.5V_{P-P}$ DIFFERENTIAL f = 5MHzVG CTL = $-2V_{P-P}$ DIFFERENTIAL $VG_CTL = -1V_{P-P} DIFFERENTIAL$ 35 25 25 Í Í HHH 20 30 15 25 15 GAIN (dB) GAIN (dB) GAIN (dB) 5 20 10 15 5 -5 10 0 -15 5 -5 0 -10 -25 2.5 1000 0.1 10 100 1000 -2.5 -1.5 -0.5 0.5 1.5 0.1 10 100 1 1 FREQUENCY (MHz) VG\_CTL (VP-P DIFFERENTIAL) FREQUENCY (MHz) LARGE-SIGNAL BANDWIDTH LARGE-SIGNAL BANDWIDTH LARGE-SIGNAL BANDWIDTH vs. FREQUENCY vs. FREQUENCY vs. FREQUENCY 20 10 5 $V_{OUT} = 1V_{P-P} DIFFERENTIAL$ $V_{OUT} = 1.5 V_{P-P} DIFFERENTIAL$ $V_{OUT} = 1.5 V_{P-P} DIFFERENTIAL$ $VG_CTL = +0.6V_{P-P}$ DIFFERENTIA $VG\_CTL = +1.5V_{P-P}$ $VG_CTL = +1.7V_{P-P} DIFFERENTIAL$ 15 5 0 10 0 -5 -5 -10 5 GAIN (dB) GAIN (dB) (gB) 0 -10 -15 GAIN ( -5 -15 -20 -10 -20 -25 -15 -25 -30 -30 -20 -35 0.1 10 100 1000 0.1 1 10 100 1000 0.1 10 1000 1 1 100 FREQUENCY (MHz) FREQUENCY (MHz) FREQUENCY (MHz)

(Figure 7, V<sub>CC</sub> = V<sub>REF</sub> = 4.75V to 5.25V, V<sub>GND</sub> = 0V, PD = 0, VG\_CLAMP\_MODE = 1,  $f_{RF}$  = 5MHz, capacitance to GND at each of the VGA differential outputs is 60pF, differential capacitance across the VGA outputs is 10pF,  $R_L$  = 1k $\Omega$ ,  $T_A$  = 0°C to +70°C. Typical

**Typical Operating Characteristics (continued)**

**Typical Operating Characteristics (continued)**

the VGA differential outputs is 60pF, differential capacitance across the VGA outputs is 10pF,  $R_L = 1k\Omega$ ,  $T_A = 0^{\circ}C$  to +70°C. Typical

**MAX2038**

## **Typical Operating Characteristics (continued)**

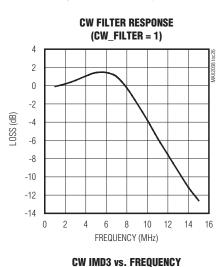

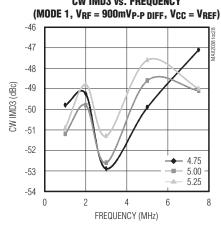

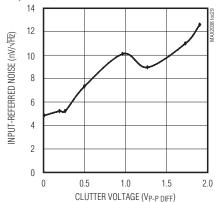

(Figure 7,  $V_{CC} = V_{REF} = 4.75V$  to 5.25V,  $V_{GND} = 0V$ , LOW\_PWR = 0, M4\_EN = 0, CW\_FILTER = 1, TEST\_MODE = 0, PD = 0, CW\_VG = 0, CW\_M1 = 0, CW\_M2 = 0, CW mixer outputs pulled up to 11V through four separate ±0.1% 115 $\Omega$  resistors, differential mixer inputs are driven from a low-impedance source.)

INPUT-REFERRED NOISE vs. CLUTTER VOLTAGE (MODE 4, F\_CLUTTER = 1.25MHz AT 1kHz OFFSET)

## \_\_Pin Description

| PIN                                            | NAME            | FUNCTION                                                                                                                                                            |

|------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                              | CWIN2-          | CW Mixer Channel 2 Inverting Differential Input                                                                                                                     |

| 2                                              | CWIN2+          | CW Mixer Channel 2 Noninverting Differential Input                                                                                                                  |

| 3                                              | VGIN3-          | VGA Channel 3 Inverting Differential Input                                                                                                                          |

| 4                                              | VGIN3+          | VGA Channel 3 Noninverting Differential Input                                                                                                                       |

| 5, 10, 19,<br>24, 29, 34,<br>58, 79,<br>81, 96 | GND             | Ground                                                                                                                                                              |

| 6                                              | CWIN3-          | CW Mixer Channel 3 Inverting Differential Input                                                                                                                     |

| 7                                              | CWIN3+          | CW Mixer Channel 3 Noninverting Differential Input                                                                                                                  |

| 8                                              | VGIN4-          | VGA Channel 4 Inverting Differential Input                                                                                                                          |

| 9                                              | VGIN4+          | VGA Channel 4 Noninverting Differential Input                                                                                                                       |

| 11                                             | CWIN4-          | CW Mixer Channel 4 Inverting Differential Input                                                                                                                     |

| 12                                             | CWIN4+          | CW Mixer Channel 4 Noninverting Differential Input                                                                                                                  |

| 13                                             | EXT_C1          | External Compensation. Connect a 4.7µF capacitor to ground as close as possible to the pin to bypass the internal biasing circuitry.                                |

| 14                                             | EXT_C2          | External Compensation. Connect a $4.7\mu$ F capacitor to ground as close as possible to the pin to bypass the internal biasing circuitry.                           |

| 15                                             | EXT_C3          | External Compensation. Connect a 4.7µF capacitor to ground as close as possible to the pin to bypass the internal biasing circuitry.                                |

| 16, 42, 46,<br>54, 72,<br>82, 87               | V <sub>CC</sub> | 5V Power Supply. Connect to an external +5V power supply. Bypass each V <sub>CC</sub> supply to ground with $0.1\mu$ F capacitors as close as possible to the pins. |

| 17                                             | VGIN5-          | VGA Channel 5 Inverting Differential Input                                                                                                                          |

| 18                                             | VGIN5+          | VGA Channel 5 Noninverting Differential Input                                                                                                                       |

| 20                                             | CWIN5-          | CW Mixer Channel 5 Inverting Differential Input                                                                                                                     |

| 21                                             | CWIN5+          | CW Mixer Channel 5 Noninverting Differential Input                                                                                                                  |

| 22                                             | VGIN6-          | VGA Channel 6 Inverting Differential Input                                                                                                                          |

| 23                                             | VGIN6+          | VGA Channel 6 Noninverting Differential Input                                                                                                                       |

| 25                                             | CWIN6-          | CW Mixer Channel 6 Inverting Differential Input                                                                                                                     |

| 26                                             | CWIN6+          | CW Mixer Channel 6 Noninverting Differential Input                                                                                                                  |

| 27                                             | VGIN7-          | VGA Channel 7 Inverting Differential Input                                                                                                                          |

| 28                                             | VGIN7+          | VGA Channel 7 Noninverting Differential Input                                                                                                                       |

| 30                                             | CWIN7-          | CW Mixer Channel 7 Inverting Differential Input                                                                                                                     |

| 31                                             | CWIN7+          | CW Mixer Channel 7 Noninverting Differential Input                                                                                                                  |

| 32                                             | VGIN8-          | VGA Channel 8 Inverting Differential Input                                                                                                                          |

| 33                                             | VGIN8+          | VGA Channel 8 Noninverting Differential Input                                                                                                                       |

| 35                                             | CWIN8-          | CW Mixer Channel 8 Inverting Differential Input                                                                                                                     |

| 36                                             | CWIN8+          | CW Mixer Channel 8 Noninverting Differential Input                                                                                                                  |

## \_\_\_\_\_Pin Description (continued)

| PIN    | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37, 93 | V <sub>REF</sub> | +5V Reference Supply. Connect to a low-noise power supply. Bypass to GND with a 0.1 $\mu$ F capacitor as close as possible to the pins. Note that noise performance of the device is dependent on the noise contribution from the supply to V <sub>REF</sub> . Use a low-noise supply for V <sub>REF</sub> . V <sub>CC</sub> and V <sub>REF</sub> can be connected together to share the same supply voltage if the supply for V <sub>CC</sub> exhibits low noise. |

| 38     | EXT_RES          | External Resistor. Connect a 0.1% 7.5k $\Omega$ resistor to ground as close as possible to the pin to set the bias for the internal biasing circuitry.                                                                                                                                                                                                                                                                                                             |

| 39     | CW_VG            | CW Mixer VGA Enable. Selects for VGA or CW mixer operation. Set CW_VG to a logic-high to enable the VGAs while the CW mixers are powered down. Set CW_VG to a logic-low to enable the CW mixers while the VGAs are powered down.                                                                                                                                                                                                                                   |

| 40     | PD               | Power-Down Switch. Drive PD high to set the device in power-down mode. Drive PD low for normal operation.                                                                                                                                                                                                                                                                                                                                                          |

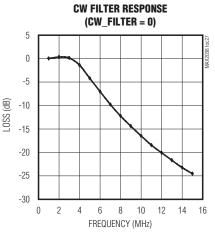

| 41     | CW_FILTER        | CW Filter Mode Corner Frequency Select. Selects in corner frequency of the internal lowpass filter for the CW path. Set CW_FILTER to a logic-high for a corner frequency of 9.5MHz. Set CW_FILTER to a logic-low for a corner frequency of 4.5MHz.                                                                                                                                                                                                                 |

| 43     | M4_EN            | Mode 4 Enable. Set M4_EN to a logic-high to override the serial port and activate all 8 channels of the CW path.                                                                                                                                                                                                                                                                                                                                                   |

| 44     | LOW_PWR          | Low-Power Enable. Set high to enable low-power CW mixer mode for the device.                                                                                                                                                                                                                                                                                                                                                                                       |

| 45     | DOUT             | Serial Port Data Output. Data output for ease of daisy-chaining CW channels for analog beamforming programming.                                                                                                                                                                                                                                                                                                                                                    |

| 47     | N.C.             | No Connect. Leave this pin unconnected (this pin is the TEST_MODE pin called out in the MAX2038 EV kit data sheet).                                                                                                                                                                                                                                                                                                                                                |

| 48     | LO8              | CW LO Input for Channel 8. LO clock input for modes 3 and 4.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 49     | VGOUT8+          | VGA Channel 8 Noninverting Differential Output                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 50     | VGOUT8-          | VGA Channel 8 Inverting Differential Output                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 51     | LO7              | CW LO Input for Channel 7. LO clock input for modes 3 and 4.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 52     | VGOUT7+          | VGA Channel 7 Noninverting Differential Output                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 53     | VGOUT7-          | VGA Channel 7 Inverting Differential Output                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 55     | LO6              | CW LO Input for Channel 6. LO clock input for modes 3 and 4.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 56     | VGOUT6+          | VGA Channel 6 Noninverting Differential Output                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 57     | VGOUT6-          | VGA Channel 6 Inverting Differential Output                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 59     | LO5              | CW LO Input for Channel 5. LO clock input for modes 3 and 4.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 60     | VGOUT5+          | VGA Channel 5 Noninverting Differential Output                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 61     | VGOUT5-          | VGA Channel 5 Inverting Differential Output                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 62     | VG_CTL-          | VGA Analog Gain Control Differential Input. Set the differential voltage to -2V for maximum gain                                                                                                                                                                                                                                                                                                                                                                   |

| 63     | VG_CTL+          | (+29.5dB), and to +2V for minimum gain (-12.5dB).                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 64     | LO_LVDS-         | CW LVDS LO Inverting Differential Input. LO clock inverting input for modes 1 and 2.                                                                                                                                                                                                                                                                                                                                                                               |

| 65     | LO_LVDS+         | CW LVDS LO Noninverting Differential Input. LO clock noninverting input for modes 1 and 2.                                                                                                                                                                                                                                                                                                                                                                         |

| 66     | LO4              | CW LO Input for Channel 4. LO clock input for modes 3 and 4.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 67     | VGOUT4+          | VGA Channel 4 Noninverting Differential Output                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 68     | VGOUT4-          | VGA Channel 4 Inverting Differential Output                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 69     | LO3              | CW LO Input for Channel 3. LO clock input for modes 3 and 4.                                                                                                                                                                                                                                                                                                                                                                                                       |

## Pin Description (continued)

| PIN | NAME              | FUNCTION                                                                                                                                                                                          |

|-----|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 70  | VGOUT3+           | VGA Channel 3 Noninverting Differential Output                                                                                                                                                    |

| 71  | VGOUT3-           | VGA Channel 3 Inverting Differential Output                                                                                                                                                       |

| 73  | LO2               | CW LO Input for Channel 2. LO clock input for modes 3 and 4.                                                                                                                                      |

| 74  | VGOUT2+           | VGA Channel 2 Noninverting Differential Output                                                                                                                                                    |

| 75  | VGOUT2-           | VGA Channel 2 Inverting Differential Output                                                                                                                                                       |

| 76  | LO1               | CW LO Input for Channel 1. LO clock input for modes 3 and 4.                                                                                                                                      |

| 77  | VGOUT1+           | VGA Channel 1 Noninverting Differential Output                                                                                                                                                    |

| 78  | VGOUT1-           | VGA Channel 1 Inverting Differential Output                                                                                                                                                       |

| 80  | DIN               | Serial Port Data Input. Data input to program the serial shift registers.                                                                                                                         |

| 83  | CLK               | Serial Port Data Clock. Clock input for programming the serial shift registers.                                                                                                                   |

| 84  | CW_M1             | CW Mode Select Input 1. Input for programming beamforming mode 1, 2, 3, or 4. See Table 1 for mode programming details.                                                                           |

| 85  | CW_M2             | CW Mode Select Input 2. Input for programming beamforming mode 1, 2, 3, or 4. See Table 1 for mode programming details.                                                                           |

| 86  | VG_CLAMP_<br>MODE | VGA Clamp Mode Enable. Drive VG_CLAMP_MODE low to enable VGA clamp mode. VGA output is clamped at typically 2.4V <sub>P-P</sub> differential. Drive VG_CLAMP_MODE high to disable VGA clamp mode. |

| 88  | LOAD              | Serial Port Load. Loads the data from the serial shift registers into the I/Q phase dividers. Pull LOAD bus from high to low and from low to high for programming the I/Q phase dividers.         |

| 89  | CW_QOUT+          | CW Mixer Noninverting Differential Quadrature Output. CW Mixer output for eight quadrature mixers combined.                                                                                       |

| 90  | CW_QOUT-          | CW Mixer Inverting Differential Quadrature Output. CW mixer output for eight quadrature mixers combined.                                                                                          |

| 91  | CW_IOUT-          | CW Mixer Inverting Differential In-Phase Output. CW mixer output for eight in-phase mixers combined.                                                                                              |

| 92  | CW_IOUT+          | CW Mixer Noninverting Differential In-Phase Output. CW Mixer output for eight in-phase mixers combined.                                                                                           |

| 94  | VGIN1-            | VGA Channel 1 Inverting Differential Input                                                                                                                                                        |

| 95  | VGIN1+            | VGA Channel 1 Noninverting Differential Input                                                                                                                                                     |

| 97  | CWIN1-            | CW Mixer Channel 1 Inverting Differential Input                                                                                                                                                   |

| 98  | CWIN1+            | CW Mixer Channel 1 Noninverting Differential Input                                                                                                                                                |

| 99  | VGIN2-            | VGA Channel 2 Inverting Differential Input                                                                                                                                                        |

| 100 | VGIN2+            | VGA Channel 2 Noninverting Differential Input                                                                                                                                                     |

|     | EP                | Exposed Pad. Internally connected to GND. Connect EP to a large PCB ground plane to maximize thermal performance.                                                                                 |

## **Detailed Description**

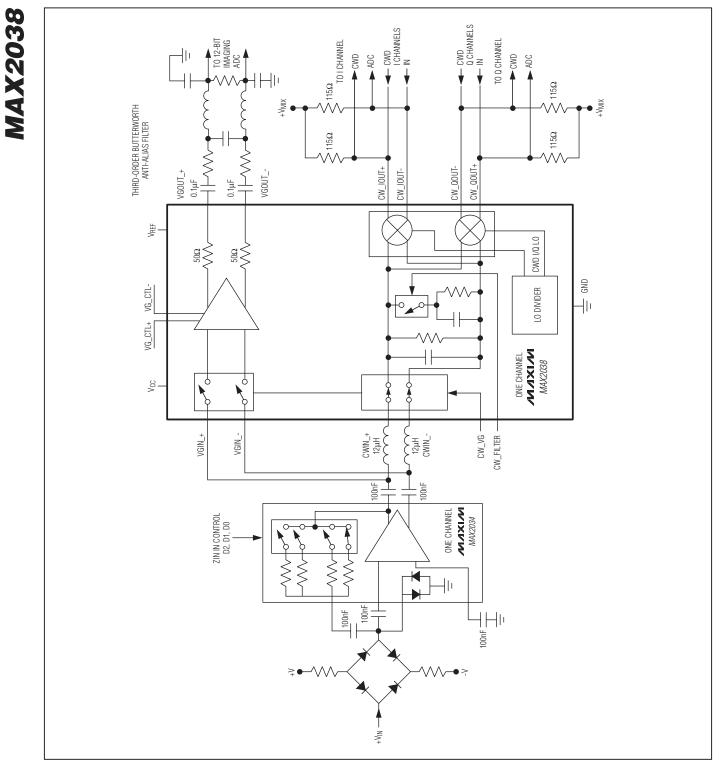

The MAX2038 is an 8-channel VGA integrated with a programmable octal quadrature mixer array designed for ultrasound imaging and Doppler applications. The device is optimized for efficient power consumption, high dynamic range, and for exceptionally low noise performance. The VGA path features differential inputs, analog variable gain control, differential outputs for direct ADC drive, and a selectable output voltage clamp to avoid ADC overdrive. The integrated octal quadrature mixer array includes serial programmable LO phase generators for CWD beamforming applications. The LO phase dividers can be programmed for 4, 8, or 16 guadrature phases. Lowpass filters are integrated at the input paths of each CW mixer. The outputs for the mixers are summed into single I/Q differential current outputs.

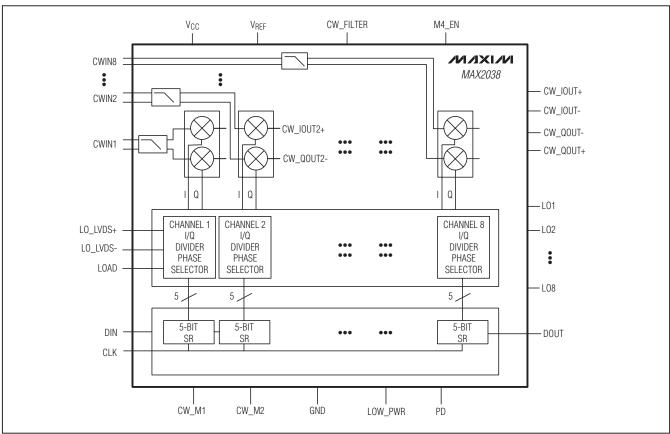

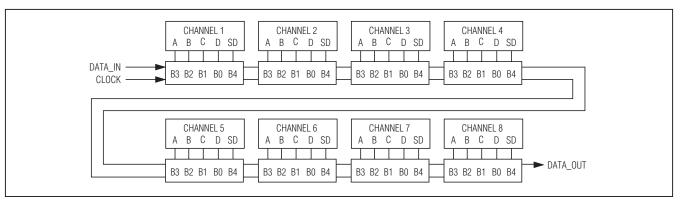

The MAX2038 also integrates an octal quadrature mixer array and programmable LO phase generators for a complete continuous wave (CW) Doppler beamforming solution. The LO phase selection for each channel is programmed using a digital serial interface and a single high-frequency clock, or the LOs for each complex mixer pair can be directly driven using separate 4 x LO clocks. The serial interface is designed to allow multiple devices to be easily daisy chained in order to minimize program interface wiring. The LO phase dividers can be programmed to allow 4, 8, or 16 quadrature phases. The input path of each CW mixer consists of a selectable lowpass filter for optimal CWD noise performance. The outputs of the mixers are summed into single I and Q differential current outputs. The mixers and LO generators are designed to have exceptionally low noise performance of -155dBc/Hz at 1kHz offset from a 1.25MHz carrier, measured with 900mVP-P differential clutter signal.

### Variable Gain Amplifier (VGA)

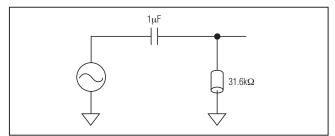

The MAX2038's VGAs are optimized for high linearity, high dynamic range, and low output-noise performance, making this component ideal for ultrasound imaging applications. The VGA paths also exhibit a channel-to-channel crosstalk of -80dB at 10MHz and an absolute gain error of less than ±0.25dB for minimal channel-to-channel focusing error in an ultrasound system. Each VGA path includes circuitry for adjusting analog gain, an output buffer with differential output ports (VGOUT\_+, VGOUT\_-) for driving ADCs, and differential input ports (VGIN\_+, VGIN\_-), which are ideal for directly interfacing to the MAX2034 quad LNA. See the *High-Level Wave Mixer and Programmable Beamformer Functional Diagram* for details.

## High-Level Wave Mixer and Programmable Beamformer \_\_\_\_\_Functional Diagram

The VGA has an adjustable gain range from -12.5dB to +29.5dB, achieving a total dynamic range of 42dB (typ). The VGA gain can be adjusted through the differential gain control inputs VG\_CTL+ and VG\_CTL-. Set the differential gain-control input voltage at +2V for minimum gain and -2V for maximum gain. The differential analog control common-mode voltage is 3V (typ).

### VGA Clamp

A clamp is provided to limit the VGA output signals to avoid overdriving the ADC or to prevent ADC saturation. Set VG\_CLAMP\_MODE low to clamp the VGA differential outputs at 2.4VP-P. Set the VG\_CLAMP\_MODE high to disable the clamp.

### **Power-Down**

The device can also be powered down with PD. Set PD to logic-high for power-down mode. In power-down mode, the device draws a total supply current of 27mA. Set PD to a logic-low for normal operation.

### **Overload Recovery**

The device is also optimized for quick overload recovery for operation under the large input-signal conditions that are typically found in ultrasound input buffer imaging applications. See the *Typical Operating Characteristics* for an illustration of the rapid recovery time from a transmit-related overload.

### **Octal Continuous Wave (CW) Mixer**

The MAX2038 CW mixers are designed using an active double-balanced topology. The mixers achieve high dynamic range and high linearity performance, with exceptionally low noise, which is ideal for ultrasound CWD signal reception. The octal quadrature mixer array provides noise performance of -155dBc/Hz at 1kHz from a 1.25MHz carrier, and a two-tone third-order ultrasound specific intermodulation product of typically -50dBc. See the *Ultrasound-Specific IMD3 Specification* in the *Applications Information* section.

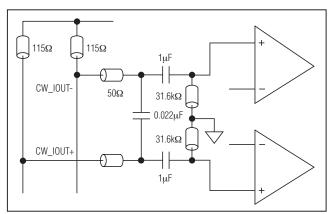

The octal array exhibits quadrature and in-phase differential current outputs (CW\_QOUT+, CW\_QOUT-, CW\_IOUT+, CW\_IOUT-) to produce the total CWD beamformed signal. The maximum differential current output is typically 3mAP-P and the mixer output-compliance voltage ranges from 4.75V to 12V.

## High-Level CW Mixer and Programmable \_\_\_\_\_Beamformer Functional Diagram

# **WAX2038**

### **CW Mixer Output Summation**

The outputs from the octal mixer array are summed internally to produce the total CWD summed beamformed signal. The octal array produces eight differential quadrature (Q) outputs and eight differential in-phase (I) outputs. All quadrature and in-phase outputs are summed into single I and Q differential current outputs (CW\_QOUT+, CW\_QOUT-, CW\_IOUT+, CW\_IOUT-).

### **LO Phase Select**

The LO phase dividers can be programmed through the shift registers to allow for 4, 8, or 16 quadrature phases for a complete CW beamforming solution.

### **CWD Beamforming Modes**

There are four separate modes of operating the CWD beamformer. See Table 1 for a summary of the different modes of operation. The mode of operation can be selected by the CW\_M1 and CW\_M2 logic inputs. Phase generation is controlled through the serial interface. See the *Serial Interface* section in the *Applications Information* section for details on how to program for different quadrature phases.

### Mode 1

For mode 1 operation, the LO\_LVDS input frequency is typically 16 x fLO. As the CWD LO frequency range is 1MHz to 7.5MHz, the input frequency ranges from 16MHz to 120MHz. This high LO clock frequency requires a differential LVDS input. The 16 x fLO input is then divided by 16 to produce 16 phases. These 16 phases are generated for each of the 8 channels and programmed for the selected phase by a serial shift register. Each channel has a corresponding 5-bit shift

register, which is used to program the output phase of the divide-by-16 circuit. The first 4 bits of the shift register are for programming the 16 phases, the fifth bit turns each channel on/off individually. For mode 1, set both CW\_M1 and CW\_M2 to a logic-low.

## Table 2. Mode 1 Logic Table (B4 = 0: Channel On/B4 = 1: Channel Off)

| MODE 1<br>CW_M1 = 0<br>CW_M2 = 0 | MSB  |      |      | LSB  | SHUTDOWN |

|----------------------------------|------|------|------|------|----------|

| PHASE                            | D    | С    | В    | Α    | SD       |

| (DEG)                            | (B0) | (B1) | (B2) | (B3) | (B4)     |

| 0                                | 0    | 0    | 0    | 0    | 0/1      |

| 22.5                             | 0    | 0    | 0    | 1    | 0/1      |

| 45                               | 0    | 0    | 1    | 0    | 0/1      |

| 67.5                             | 0    | 0    | 1    | 1    | 0/1      |

| 90                               | 0    | 1    | 0    | 0    | 0/1      |

| 112.5                            | 0    | 1    | 0    | 1    | 0/1      |

| 135                              | 0    | 1    | 1    | 0    | 0/1      |

| 157.5                            | 0    | 1    | 1    | 1    | 0/1      |

| 180                              | 1    | 0    | 0    | 0    | 0/1      |

| 202.5                            | 1    | 0    | 0    | 1    | 0/1      |

| 225                              | 1    | 0    | 1    | 0    | 0/1      |

| 247.5                            | 1    | 0    | 1    | 1    | 0/1      |

| 270                              | 1    | 1    | 0    | 0    | 0/1      |

| 292.5                            | 1    | 1    | 0    | 1    | 0/1      |

| 315                              | 1    | 1    | 1    | 0    | 0/1      |

| 337.5                            | 1    | 1    | 1    | 1    | 0/1      |

Table 1. Summary of CWD Beamforming Methods

| CW_M1 | CW_M2 | MODE | LO INPUT<br>FREQUENCY | CLOCK<br>INTERFACE | PHASE<br>RESOLUTION    | NO. OF<br>CLOCK<br>INPUTS<br>PER CHIP | PROGRAM<br>BY SERIAL<br>SHIFT<br>REGISTER<br>(SSR) | NO. OF<br>USEFUL<br>BITS IN<br>SSR | NO. OF<br>DON'T-<br>CARE BITS<br>IN SSR |

|-------|-------|------|-----------------------|--------------------|------------------------|---------------------------------------|----------------------------------------------------|------------------------------------|-----------------------------------------|

| 0     | 0     | 1    | 16 x                  | LVDS               | 16 phases              | 1                                     | Yes                                                | 4                                  | 0                                       |

| 0     | 1     | 2    | 8 x                   | LVDS               | 8 phases               | 1                                     | Yes                                                | 3                                  | 1 MSB                                   |

| 1     | 0     | 3    | 4 x                   | 3V CMOS            | 4 phases               | 8                                     | Yes                                                | 2                                  | 2 MSBs                                  |

| 1     | 1     | 4    | 4 x                   | 3V CMOS            | Quadrature<br>provided | 8                                     | No                                                 | N/A                                | N/A                                     |

N/A = Not applicable.

### Mode 2