# **Digital PWM System Controller**

Check for Samples: UCD9220

## **FEATURES**

- Fully Configurable Multi-Output and Multi-Phase Non-Isolated DC/DC PWM Controller

- Controls Up To Two Voltage Rails and Up To Four Phases

- Supports Switching Frequencies Up to 2MHz With 250 ps Duty-Cycle Resolution

- Up To 1mV Closed Loop Resolution

- Hardware-Accelerated, 3-Pole/3-Zero Compensator With Non-Linear Gain for Improved Transient Performance

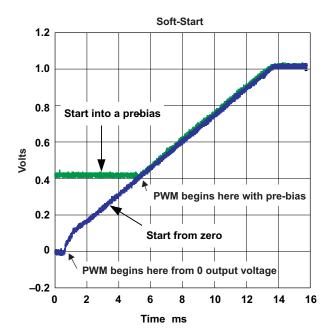

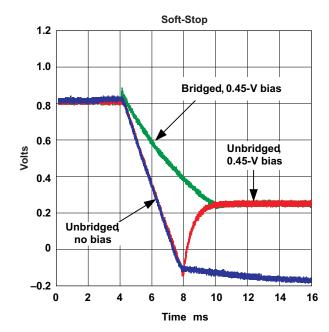

- Supports Multiple Soft-Start and Soft-Stop Configurations Including Prebias Start-up

- Supports Voltage Tracking, Margining and Sequencing

- Supports Current and Temperature Balancing for Multi-Phase Power Stages

- Supports Phase Adding/Shedding for Multi-Phase Power Stages

- Sync In /Out Pins Align DPWM Clocks Between Multiple UCD9220 Devices

- 12-Bit Digital Monitoring of Power Supply Parameters Including:

- Input Current and Voltage

- Output Current and Voltage

- Temperature at Each Power Stage

- Multiple Levels of Overcurrent Fault Protection:

- External Current Fault Inputs

- Analog Comparators Monitor Current Sense Voltage

- Current Digitally Monitored

- Over and Undervoltage Fault Protection

- Overtemperature Fault Protection

- Enhanced Nonvolatile Memory With Error Correction Code (ECC)

- Device Operates From a Single Supply With an Internal Regulator Controller That Allows Operation Over a Wide Supply Voltage Range

Fusion Digital Power, Auto-ID are trademarks of Texas Instruments.

Supported by Fusion Digital Power™

Designer, a Full Featured PC Based Design

Tool to Simulate, Configure, and Monitor

Power Supply Performance.

## **APPLICATIONS**

- Industrial/ATE

- Networking Equipment

- Telecommunications Equipment

- Servers

- Storage Systems

- FPGA, DSP and Memory Power

#### DESCRIPTION

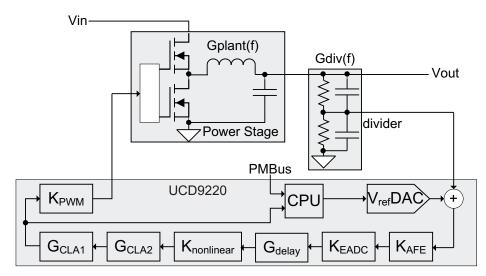

The UCD9220 is a multi-rail, multi-phase synchronous buck digital PWM controller designed for non-isolated DC/DC power applications. This device integrates dedicated circuitry for DC/DC loop management with flash memory and a serial interface to support configuration, monitoring and management.

The UCD9220 was designed to provide a wide variety of desirable features for non-isolated DC/DC converter applications while minimizing the total system component count by reducing external integrates circuits. The solution multi-loop management with sequencing, margining, tracking and intelligent phase management to optimize for system efficiency. Additionally, compensation and calibration are supported without the need to add external components.

To facilitate configuring the device, the Texas Instruments Fusion Digital Power™ Designer is provided. This PC based Graphical User Interface offers an intuitive interface to the device. This tool allows the design engineer to configure the system operating parameters for the application, store the configuration to on-chip non-volatile memory and observe both frequency domain and time domain simulations for each of the power stage outputs.

TI has also developed multiple complementary power stage solutions – from discrete drives in the UCD7k family to fully tested power train modules in the PTD family. These solutions have been developed to complement the UCD9k family of system power controllers.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TEXAS INSTRUMENTS

SLUS904 – MARCH 2009 www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

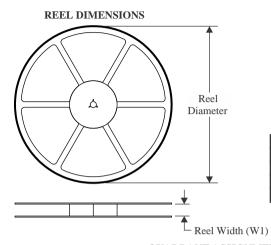

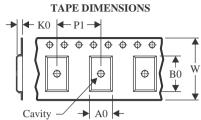

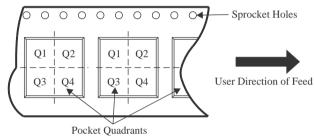

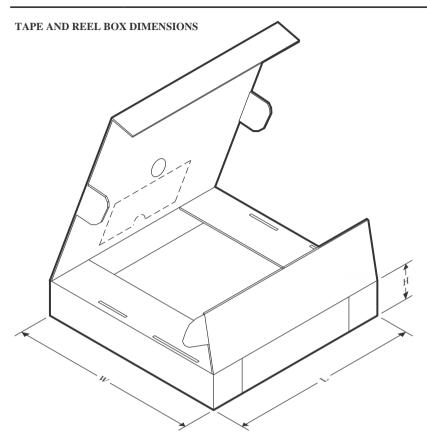

#### ORDERING INFORMATION(1)

| OPERATING TEMPERATURE RANGE, T <sub>A</sub> | ORDERABLE PART<br>NUMBER | PIN COUNT | SUPPLY       | PACKAGE | TOP SIDE MARKING |

|---------------------------------------------|--------------------------|-----------|--------------|---------|------------------|

| -40°C to 110°C                              | UCD9220RGZR              | 48-pin    | Reel of 2500 | QFN     | UCD9220          |

| -40°C to 110°C                              | UCD9220RGZT              | 48-pin    | Reel of 250  | QFN     | UCD9220          |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

#### **ELECTRICAL SPECIFICATIONS**

# ABSOLUTE MAXIMUM RATINGS(1)

|                                         | VALUE       | UNIT |

|-----------------------------------------|-------------|------|

| Voltage applied at V33D to DGND1        | -0.3 to 3.8 | V    |

| Voltage applied at V33A to AGND         | -0.3 to 3.8 | V    |

| Voltage applied to any pin (2)          | -0.3 to 3.8 | V    |

| Storage temperature (T <sub>STG</sub> ) | -40 to 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

Over operating free-air temperature range (unless otherwise noted).

|                               |                                             | MIN | NOM | MAX | UNIT |

|-------------------------------|---------------------------------------------|-----|-----|-----|------|

| V                             | Supply voltage during operation, V33D, V33A | 3   | 3.3 | 3.6 | V    |

| T <sub>A</sub> (1)            | Operating free-air temperature range        | -40 |     | 110 | °C   |

| T <sub>J</sub> <sup>(1)</sup> | Junction temperature                        |     |     | 125 | °C   |

(1) When operating, the UCD9220's typical power consumption causes a 15 °C temperature rise from ambient.

<sup>(2)</sup> All voltages referenced to GND.

# **ELECTRICAL CHARACTERISTICS**

|                          | PARAMETER                                           | TEST CONDITIONS                                                                                                        | MIN        | NOM   | MAX   | UNIT   |

|--------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------|-------|-------|--------|

| SUPPLY CURR              | ENT                                                 |                                                                                                                        | *          |       |       |        |

| I <sub>V33A</sub>        |                                                     | V <sub>33A</sub> = 3.3 V                                                                                               |            | 8     | 15    |        |

| I <sub>V33D</sub>        | Supply current                                      | V <sub>33D</sub> = 3.3 V                                                                                               |            | 42    | 55    | mA     |

| I <sub>V33D</sub>        | _ сарру сапси                                       | V <sub>33D</sub> = 3.3 V while storing configuration parameters in flash memory                                        |            | 52    | 65    | 1117 ( |

| INTERNAL REG             | GULATOR CONTROLLER INPUTS/OU                        | JTPUTS                                                                                                                 |            |       |       |        |

| V <sub>33</sub>          | 3.3-V linear regulator                              | Emitter of NPN transistor                                                                                              | 3.25       | 3.3   | 3.6   | V      |

| V <sub>33FB</sub>        | 3.3-V linear regulator feedback                     |                                                                                                                        |            | 4     | 4.6   | V      |

| I <sub>V33FB</sub>       | Series pass base drive                              | V <sub>IN</sub> = 12 V; current into the pin                                                                           |            | 10    |       | mA     |

| Beta                     | Series NPN pass device                              |                                                                                                                        | 40         |       |       |        |

| <b>EXTERNALLY</b>        | SUPPLIED 3.3 V POWER                                |                                                                                                                        |            |       |       |        |

| V <sub>33D</sub>         | Digital 3.3-V power                                 | T <sub>A</sub> = 25°C                                                                                                  | 3.13       |       | 3.6   | V      |

| V <sub>33A</sub>         | Analog 3.3-V power                                  | T <sub>A</sub> = 25°C                                                                                                  | 3.13       |       | 3.6   | V      |

|                          | IFIER INPUTS EAPn, EANn                             |                                                                                                                        |            |       |       |        |

| V <sub>CM</sub>          | Common mode voltage each pin                        |                                                                                                                        | -0.15      |       | 1.848 | V      |

| V <sub>DIFF</sub>        | Differential Voltage Range                          |                                                                                                                        | -0.25<br>6 |       | 1.998 | V      |

| V <sub>ERROR</sub>       | Internal error Voltage range                        | AFE_GAIN field of CLA_GAINS = 0 <sup>(1)</sup>                                                                         | -256       |       | 248   | mV     |

| EAP-EAN                  | Error voltage digital resolution                    | AFE_GAIN field of CLA_Gains = 3                                                                                        |            | 1     |       | mV     |

| R <sub>EA</sub>          | Input Impedance                                     | Ground reference                                                                                                       | 0.5        | 1.5   | 3     | МΩ     |

| I <sub>OFFSET</sub>      | Input offset current                                | 1 kΩ source impedance                                                                                                  | -5         |       | 5     | μA     |

| V <sub>REF</sub> DAC     |                                                     |                                                                                                                        |            |       |       |        |

| V <sub>REF</sub>         | Reference voltage setpoint                          |                                                                                                                        | 0          |       | 1.6   | V      |

| V <sub>REFRES</sub>      | Reference voltage resolution                        |                                                                                                                        |            | 1.56  |       | mV     |

| ANALOG INPU              | TS CS-1A, CS-1B, CS-2A, CS-3A, V <sub>in</sub>      | /I <sub>IN</sub> , Temperature, ADDR-0, ADDR-1, V <sub>track</sub> ,                                                   | ADCref     |       |       |        |

| I <sub>BIAS</sub>        | Bias current for PMBus Addr pins                    |                                                                                                                        | 9          |       | 11    | μA     |

| V <sub>ADDR_OPEN</sub>   | Voltage indicating open pin                         | ADDR-0, ADDR-1 open                                                                                                    | 2.226      |       |       | V      |

| V <sub>ADDR_SHORT</sub>  | Voltage indicating shorted pin                      | ADDR-0, ADDR-1 short to ground                                                                                         |            |       | 0.097 | V      |

| V <sub>ADC_RANGE</sub>   | Measurment range for voltage monitoring             | Inputs: V <sub>In</sub> /I <sub>IN</sub> , V <sub>track</sub> , V <sub>temperature</sub><br>CS-1A, CS-1B, CS-2A, CS-3A | 0          |       | 2.5   | V      |

| V <sub>OC_THRS</sub>     | Overcurrent comparator threshold voltage range      | Inputs: CS-1A, CS-1B, CS-2A, CS-3A                                                                                     | 0.032      |       | 2     | V      |

| V <sub>OC_RES</sub>      | Overcurrent comparator threshold voltage resolution | Inputs: CS-1A, CS-1B, CS-2A, CS-3A                                                                                     |            | 31.25 |       | mV     |

| ADCref                   | External Reference input                            |                                                                                                                        | 1.8        |       | V33A  | V      |

| Temp <sub>internal</sub> | Int. temperature sense accuracy                     | Over range from 0°C to 125°C                                                                                           | -5         |       | 5     | °C     |

| INL                      | ADC integral nonlinearity                           |                                                                                                                        | -2.5       |       | 2.5   | mV     |

| I <sub>lkg</sub>         | Input leakage current                               | 3V applied to pin                                                                                                      |            |       | 100   | nA     |

| R <sub>IN</sub>          | Input impedance                                     | Ground reference                                                                                                       | 8          |       |       | ΜΩ     |

| C <sub>IN</sub>          | Current Sense Input capacitance                     |                                                                                                                        |            |       | 10    | pF     |

<sup>(1)</sup> See the UCD92xx PMBus Command Reference for the description of the AFE\_GAIN field of CLA\_GAINS command.

SLUS904 – MARCH 2009 www.ti.com

# **ELECTRICAL CHARACTERISTICS (continued)**

|                         | PARAMETER                                    | TEST CONDITIONS                                                                                                                 | MIN                       | NOM | MAX                            | UNIT        |

|-------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----|--------------------------------|-------------|

| DIGITAL INPUT           | rs/outputs                                   |                                                                                                                                 |                           |     |                                |             |

| V <sub>OL</sub>         | Low-level output voltage                     | $I_{OL} = 6 \text{ mA}^{(2)}, V_{V33D} = 3 \text{ V}$                                                                           |                           |     | DGND1<br>+0.25                 | ٧           |

| V <sub>OH</sub>         | High-level output voltage                    | $I_{OH} = -6 \text{ mA}^{(3)}, V_{33D} = 3 \text{ V}$                                                                           | V <sub>33D</sub><br>-0.6V |     |                                | V           |

| V <sub>IH</sub>         | High-level input voltage                     | V <sub>33D</sub> = 3V                                                                                                           | 2.1                       |     | 3.6                            | ٧           |

| V <sub>IL</sub>         | Low-level input voltage                      | V <sub>33D</sub> = 3.5V                                                                                                         |                           |     | 1.1                            | ٧           |

| SYSTEM PERF             | ORMANCE                                      |                                                                                                                                 |                           |     |                                |             |

| $V_{Ref}$               | Setpoint Reference Accuracy                  | V <sub>ref</sub> commanded to be 1V, at 25°C<br>AFEgain = 4, 1V input to EAP/N measured<br>at output of the EADC <sup>(4)</sup> | -10                       |     | 10                             | mV          |

|                         | Setpoint Reference Accuracy over temperature | -40°C to 125°C                                                                                                                  | -20                       |     | 20                             | mV          |

| V <sub>DiffOffset</sub> | Differential offset between gain settings    | AFEgain = 4 compared to<br>AFEgain = 1, 2, or 8                                                                                 | -4                        |     | 4                              | mV          |

| t <sub>Delay</sub>      | Digital Compensator Delay <sup>(5)</sup>     |                                                                                                                                 | 240                       | ;   | 240 + 1<br>switching<br>period | ns          |

| F <sub>SW</sub>         | Switching Frequency                          |                                                                                                                                 | 15.26<br>0                |     | 2000                           | kHz         |

| Duty                    | Max and Min Duty Cycle                       | Configured via PMBus                                                                                                            | 0%                        |     | 100%                           |             |

| V <sub>33</sub> Slew    | V <sub>33</sub> slew rate                    | $V_{33}$ slew rate between 2.3 V and 2.9 V. $V_{33A} = V_{33D}$                                                                 | 0.25                      |     |                                | V/ms        |

| t <sub>retention</sub>  | Retention of configuration parameters        | T <sub>J</sub> = 25°C                                                                                                           | 100                       |     |                                | Years       |

| Write_Cycles            | Number of nonvolatile erase/write cycles     | T <sub>J</sub> = 25°C                                                                                                           | 20                        |     |                                | K<br>cycles |

- (2) The maximum I<sub>OL</sub>, for all outputs combined, should not exceed 12 mA to hold the maximum voltage drop specified.

- (3) The maximum I<sub>OH</sub>, for all outputs combined, should not exceed 48 mA to hold the maximum voltage drop specified.

- (4) With default device calibration. PMBus calibration can be used to improve the regulation tolerance.

- (5) Time from close of error ADC sample window to time when digitally calculated control effort (duty cycle) is available. This delay must be accounted for when calculating the system dynamic response. Includes EADC conversion time.

#### ADC MONITORING INTERVALS AND RESPONSE TIMES

The ADC operates in a continuous conversion sequence that measures each rail's output voltage, each power stage's output current, plus four other variables (one external temperature, Internal temperature, input voltage or current and tracking input voltage). The length of the sequence is determined by the number of output rails (NumRails) and total output power stages (NumPhases) configured for use. The time to complete the monitoring sampling sequence is give by the formula:

$$t_{ADC, SEQ} = t_{ADC} \times (NumRAILS + NumPHASE + 4)$$

(1)

|                      | PARAMETER              | TEST CONDITIONS                                                                  | MIN   | TYP  | MAX                           | UNIT |

|----------------------|------------------------|----------------------------------------------------------------------------------|-------|------|-------------------------------|------|

| t <sub>ADC</sub>     | ADC single-sample time |                                                                                  |       | 3.84 |                               | μs   |

| t <sub>ADC_SEQ</sub> | ADC sequencer interval | Min = 1 Rail + 1 Phase + 4 = 6 samples Max = 2 Rails + 4 Phases + 4 = 10 samples | 23.04 | :    | 38.4+1<br>switching<br>period | μs   |

The most recent ADC conversion results are periodically converted into the proper measurement units (volts, amperes, degrees), and each measurement is compared to its corresponding fault and warning limits. The monitoring operates asynchronously to the ADC, at intervals shown in the table below.

|                   | PARAMETER                          | TEST CONDITIONS | MIN | TYP                    | MAX | UNIT |

|-------------------|------------------------------------|-----------------|-----|------------------------|-----|------|

| t <sub>Vout</sub> | Output voltage monitoring interval |                 |     | 200                    |     | μs   |

| t <sub>lout</sub> | Output current monitoring interval |                 |     | $200 \times N_{Rails}$ |     | μs   |

| $t_{Vin}$         | Input voltage monitoring interval  |                 |     | 2                      |     | ms   |

| t <sub>lin</sub>  | Input current monitoring interval  |                 |     | 2                      |     | ms   |

| t <sub>TEMP</sub> | Temeprature monitoring interval    |                 | 25  | 25 x number of phases  | 100 | ms   |

| t <sub>lbal</sub> | Output current balancing interval  |                 |     | 2                      |     | ms   |

Because the ADC sequencer and the monitoring comparisons are asynchronous to each other, the response time to a fault condition depends on where the event occurs within the monitoring interval and within the ADC sequence interval. Once a fault condition is detected, some additional time is required to determine the correct action based on the FAULT\_RESPONSE code, and then to perform the appropriate response. The following table lists the worse-case fault response times.

|                                     | PARAMETER                                                                          | TEST CONDITIONS                                                                 | MAX TIME                                         | UNIT |

|-------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------|------|

| t <sub>OVF</sub> , t <sub>UVF</sub> | Over-voltage/under-voltage fault response time during normal operation             | Normal regulation, no PMBus activity, 4 stages enabled                          | 300                                              | μs   |

| t <sub>OVF</sub> , t <sub>UVF</sub> | Over-voltage/under-voltage fault response time, during data logging                | During data logging to nonvolatile memory <sup>(1)</sup>                        | 800                                              | μs   |

| t <sub>OVF</sub> , t <sub>UVF</sub> | Over-voltage/under-voltage fault response time, when tracking or sequencing enable | During tracking and soft-start ramp.                                            | 400                                              | μs   |

| t <sub>OCF</sub> , t <sub>UCF</sub> | Over-current/under-current fault response time during normal operation             | Normal regulation, no PMBus activity, 4 stages enabled 75% to 125% current step | 100 + (600 x N <sub>Rails</sub> ) <sup>(2)</sup> | μs   |

| t <sub>OCF</sub> , t <sub>UCF</sub> | Over-current/under-current fault response time, during data logging                | During data logging to nonvolatile memory 75% to 125% current step              | 600 + (600 x N <sub>Rails</sub> )                | μs   |

| t <sub>OCF</sub> , t <sub>UCF</sub> | Over-current/under-current fault response time, when tracking or sequencing enable | During tracking and soft start ramp<br>75% to 125% current step                 | 300 + (600 x N <sub>Rails</sub> )                | μs   |

| t <sub>OTF</sub>                    | Over-temperature fault response time                                               | Temperature rise of 10°C/sec,<br>OT threshold = 100°C                           | 5                                                | s    |

<sup>(1)</sup> During a STORE\_DEFAULT\_ALL command, which stores the entire configuration to nonvolatile memory, the fault detection latency can be up to 10 ms.

#### HARDWARE FAULT DETECTION LATENCY

The controller contains hardware fault detection circuits that are independent of the ADC monitoring sequencer.

|                  | PARAMETER                                                                                                                     | TEST CONDITIONS                           | MAX TIME              | UNIT             |

|------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------|------------------|

| t <sub>FLT</sub> | Time to disable DPWM output based on corresponding active FLT pin                                                             | High level on FLT pin                     | 15 + 3 x<br>NumPhases | μs               |

| t <sub>CLF</sub> | Time to disable the first DPWM output based on internal analog comparator fault                                               | Step change in CS voltage from 0V to 2.5V | 4                     | Switch<br>Cycles |

|                  | Time to disable all remaining DPWM and SRE outputs configured for the voltage rail after an internal analog comparator fault. | Step change in CS voltage from 0V to 2.5V | 10 + 3 x<br>NumPhases | μs               |

# PMBUS/SMBUS/I<sup>2</sup>C

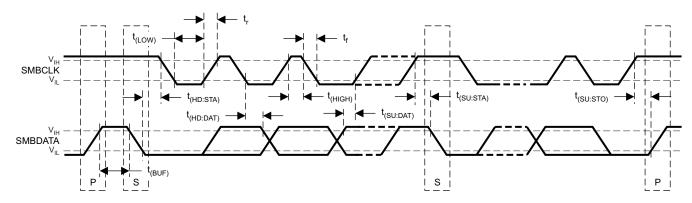

The timing characteristics and timing diagram for the communications interface that supports I<sup>2</sup>C, SMBus and PMBus are shown below.

<sup>(2)</sup> Because the current measurement is averaged with a smoothing filter, the response time to an Overcurrent condition depends on a combination of the time constant (τ) from Table 5, the recent measurement history, and how much the measured value exceeds the overcurrent limit.

# I<sup>2</sup>C/SMBus/PMBus Timing Characteristics

$T_A = -40$ °C to 85°C, 3V <  $V_{33D}$  < 3.6V, typical values at  $T_A = 25$ °C

|                         | PARAMETER                              | TEST CONDITIONS                 | MIN  | TYP | MAX  | UNIT |

|-------------------------|----------------------------------------|---------------------------------|------|-----|------|------|

| f <sub>SMB</sub>        | SMBus/PMBus operating frequency        | Slave mode; SMBC 50% duty cycle | 10   |     | 1000 | kHz  |

| f <sub>I2C</sub>        | IC operating frequency                 | Slave mode; SCL 50% duty cycle  | 10   |     | 1000 | kHz  |

| t <sub>(BUF)</sub>      | Bus free time between start and stop   |                                 | 4.7  |     |      | μs   |

| t <sub>(HD:STA)</sub>   | Hold time after (repeated) start       |                                 | 0.26 |     |      | μs   |

| t <sub>(SU:STA)</sub>   | Repeated start setup timed             |                                 | 0.26 |     |      | μs   |

| t <sub>(SU:STO)</sub>   | Stop setup time                        |                                 | 0.26 |     |      | μs   |

| t <sub>(HD:DAT)</sub>   | Data hold time                         | Receive mode                    | 0    |     |      | ns   |

| t <sub>(SU:DAT)</sub>   | Data setup time                        |                                 | 50   |     |      | ns   |

| t <sub>(TIMEOUT)</sub>  | Error signal/detect                    | See <sup>(1)</sup>              |      |     | 35   | μs   |

| t <sub>(LOW)</sub>      | Clock low period                       |                                 | 0.5  |     |      | μs   |

| t <sub>(HIGH)</sub>     | Clock high period                      | See (2)                         | 0.26 |     | 50   | μs   |

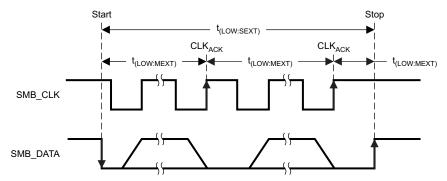

| t <sub>(LOW:SEXT)</sub> | Cumulative clock low slave extend time | See <sup>(3)</sup>              |      |     | 25   | μs   |

| t <sub>FALL</sub>       | Clock/data fall time                   | See <sup>(4)</sup>              |      |     | 120  | ns   |

| t <sub>RISE</sub>       | Clock/data rise time                   | See <sup>(5)</sup>              |      |     | 120  | ns   |

- The UCD9220 times out when any clock low exceeds  $t_{(TIMEOUT)}$ .  $t_{(HIGH)}$ , max, is the minimum bus idle time. SMBC = SMBD = 1 for t > 50 ms causes reset of any transaction involving UCD9220 that is in progress. This specification is valid when the NC\_SMB control bit remains in the default cleared state (CLK[0]=0).

- t(LOW-SEXT) is the cumulative time a slave device is allowed to extend the clock cycles in one message from initial start to the stop.

- Rise time  $t_{RISE} = V_{ILMAX} 0.15$ ) to  $(V_{ILMAX} + 0.15)$ Fall time  $t_{FALL} = 0.9 \ V_{33D}$  to  $(V_{ILMAX} 0.15)$ (4)

Figure 1. I<sup>2</sup>C/SMBus/PMBus Timing in Extended Mode Diagram

Submit Documentation Feedback

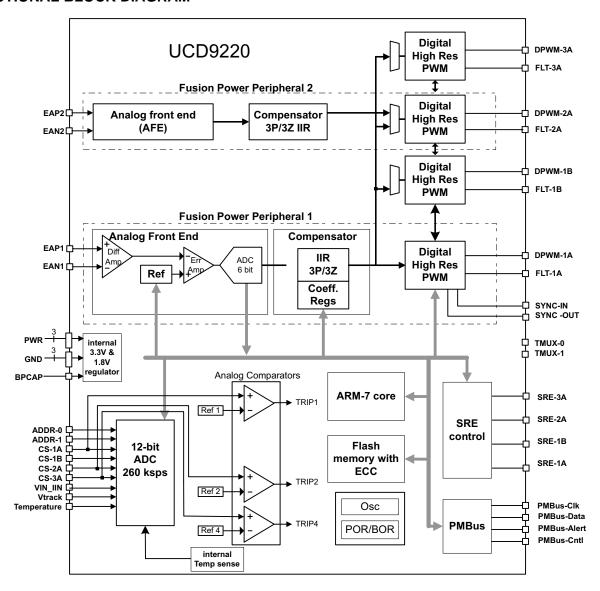

#### **FUNCTIONAL BLOCK DIAGRAM**

# TEXAS INSTRUMENTS

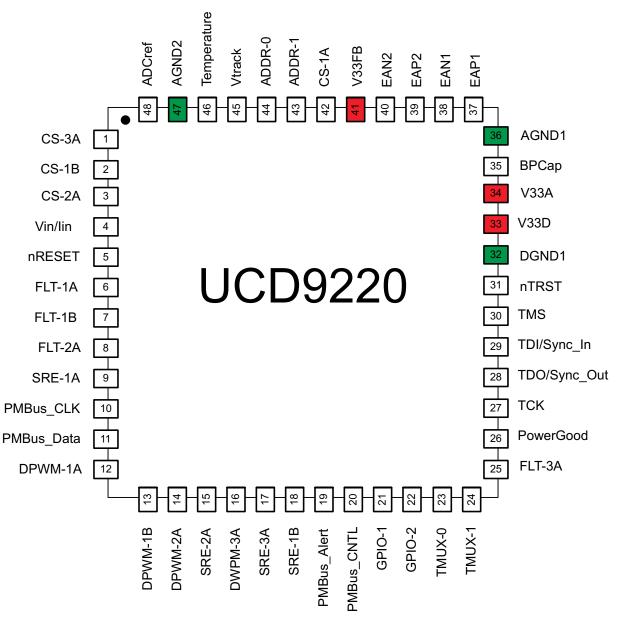

#### **PIN ASSIGNMENT**

Figure 2. UCD9220 Pin Assignment

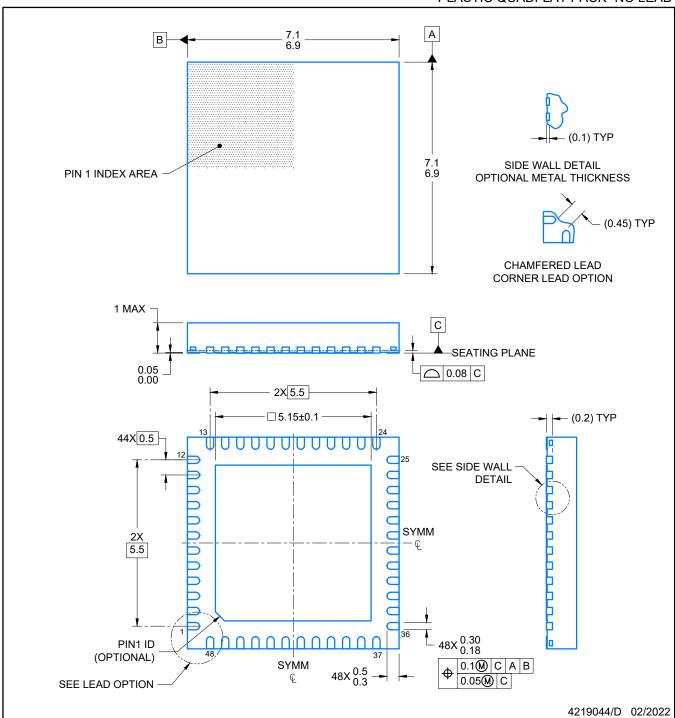

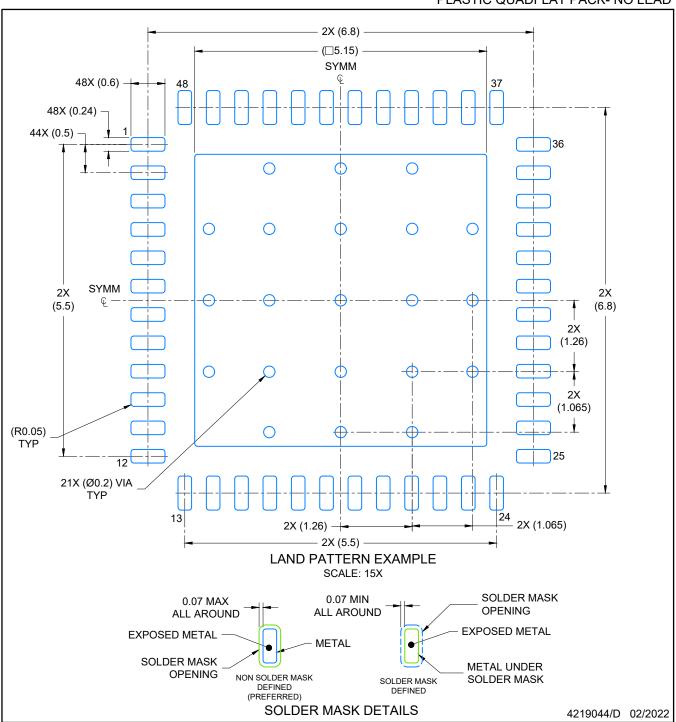

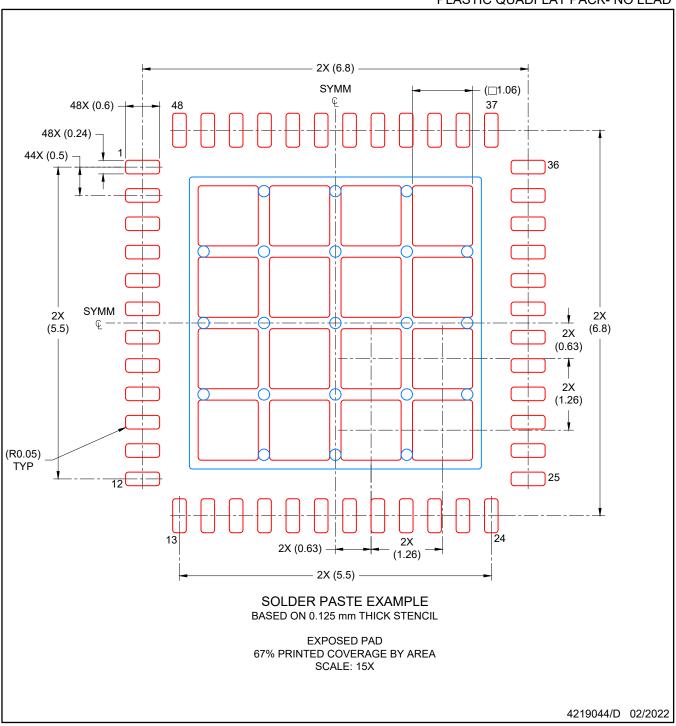

The UCD9220 is available in a plastic 48-pin QFN package (RGZ).

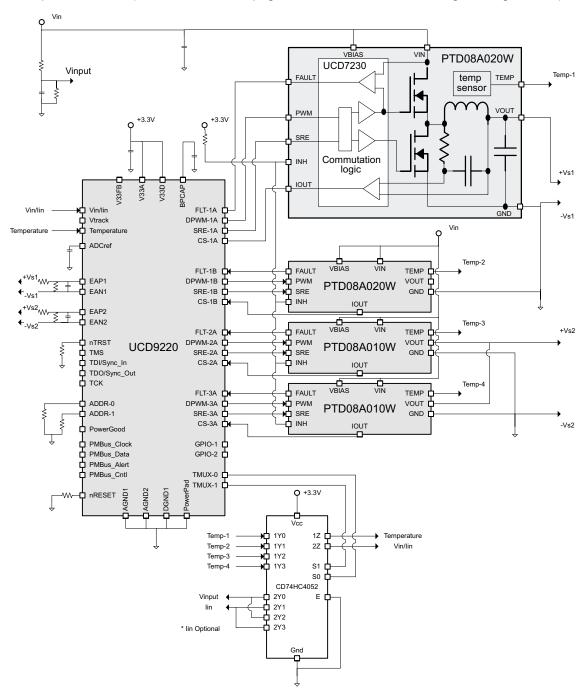

#### TYPICAL APPLICATION SCHEMATIC

Figure 3 shows the UCD9220 power supply controller as part of a system that provides the regulation of two independent power supplies. The loop for each power supply is created by the respective voltage outputs feeding into the differential voltage error ADC (EADC) inputs, and completed by DPWM outputs feeding into the gate drivers for each power stage (PTD modules in this example).

The ±V<sub>sense</sub>rail signals must be routed to the EAp/EAn input that matches the number of the lowest DPWM configured as part of the rail. (See more detail on page 19, "Flexible Rail/Power Stage Configuration".)

Figure 3. Typical Application Schematic

SLUS904 – MARCH 2009 www.ti.com

# **PIN DESCRIPTIONS**

|     | PIN                      |                  | FIN DESCRIPTIONS                                                                                                                          |

|-----|--------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME                     | 1/0              | DESCRIPTION                                                                                                                               |

| 1   | CS-3A                    | Input            | Power stage 3A current sense input and input to analog comparator 4                                                                       |

| 2   | CS-1B                    | Input            | Power stage 1B current sense input and input to analog comparator 2                                                                       |

| 3   | CS-2A                    | Input            | Power stage 2A current sense input and input to analog comparator 3                                                                       |

| 4   | $V_{in}/I_{in}$          | Input            | Input supply sense, alternates between V <sub>in</sub> and I <sub>in</sub>                                                                |

| 5   | nRESET                   | Input            | Active low device reset input pullup to 3.3V with a 10 kΩ resistor                                                                        |

| 6   | FLT-1A                   | Input            | External fault input 1A, active high                                                                                                      |

| 7   | FLT-1B                   | Input            | External fault input 1B, active high                                                                                                      |

| 8   | FLT-2A                   | Input            | External fault input 2A, active high                                                                                                      |

| 9   | SRE-1A                   | Output           | Synchronous rectifier enable 1A, active high                                                                                              |

| 10  | PMBus_Clk                | Input/Out<br>put | PMBus Clock pullup to 3.3V with a 10 K $\Omega$ resistor                                                                                  |

| 11  | PMBus_Data               | Input/Out<br>put | PMBus Data pullup to 3.3V with a 10 K $\Omega$ resistor                                                                                   |

| 12  | DPWM-1A                  | Output           | Digital Pulse Width Modulator output 1A                                                                                                   |

| 13  | DPWM-1B                  | Output           | Digital Pulse Width Modulator output 1B                                                                                                   |

| 14  | DPWM-2A                  | Output           | Digital Pulse Width Modulator output 2A                                                                                                   |

| 15  | SRE-2A                   | Output           | Synchronous rectifier enable 2A, active high                                                                                              |

| 16  | DPWM-3A                  | Output           | Digital Pulse Width Modulator output 3A                                                                                                   |

| 17  | SRE-3A                   | Output           | Synchronous rectifier enable 3A, active high                                                                                              |

| 18  | SRE-1B                   | Output           | Synchronous rectifier enable 1B, active high                                                                                              |

| 19  | PMBus_Alert              | Output           | PMBus Alert pullup to 3.3V with a 10 $K\Omega$ resistor                                                                                   |

| 20  | PMBus_Cntl               | Input            | PMBus Control pullup to 3.3V with a 10 $K\Omega$ resistor                                                                                 |

| 21  | GPIO-1                   | Input/Out<br>put | General Purpose Input/Output                                                                                                              |

| 22  | GPIO-2                   | Input/Out<br>put | General Purpose Input/Output                                                                                                              |

| 23  | TMUX-0                   | Input            | Temperature multiplexer select S0, V <sub>in</sub> /I <sub>in</sub> Select                                                                |

| 24  | TMUX-1                   | Input            | Temperature multiplexer select S1                                                                                                         |

| 25  | FLT-3A                   | Input            | External fault input 3A, active high                                                                                                      |

| 26  | PowerGood                | Input/Out<br>put | Power Good Indication                                                                                                                     |

| 27  | (JTAG) TCK               | Input            | JTAG Test Clock                                                                                                                           |

| 28  | (JTAG) TDO /<br>Sync_Out | Output           | JTAG Test data out (muxed with Sync_Out for synchronizing switching frequency across devices)                                             |

| 29  | (JTAG) TDI /<br>Sync_In  | Input            | JTAG Test data in (muxed with Sync_In for synchronizing switching frequency across devices) pull up to 3.3V with a 10 K $\Omega$ resistor |

| 30  | (JTAG) TMS               | Input/Out<br>put | JTAG Test mode select - tie to $V_{\rm 33D}$ with 10 k $\Omega$ resistor                                                                  |

| 31  | (JTAG) nTRST             | Input/Out<br>put | JTAG Test Reset - tie to ground with a 10 $\mathrm{K}\Omega$ resistor                                                                     |

| 32  | DGND1                    | Output           | Digital Ground                                                                                                                            |

| 33  | V33D                     | Input            | Digital core 3.3V supply                                                                                                                  |

| 34  | V33A                     | Input            | Analog 3.3V supply                                                                                                                        |

| 35  | BPCap                    | Input            | 1.8V bypass capacitor connection                                                                                                          |

| 36  | AGND1                    | Input            | Analog Ground                                                                                                                             |

| 37  | EAP1                     | Input            | Error analog, differential voltage. Positive channel #1 input                                                                             |

| 38  | EAN1                     | Input            | Error analog, differential voltage. Negative channel #1 input                                                                             |

| 39  | EAP2                     | Input            | Error analog, differential voltage. Positive channel #2 input                                                                             |

| 40  | EAN2                     | Input            | Error analog, differential voltage. Negative channel #2 input                                                                             |

Product Folder Links: UCD9220

Submit Documentation Feedback

# PIN DESCRIPTIONS (continued)

|          | PIN         | 1/0    | DECORIDATION                                                                      |

|----------|-------------|--------|-----------------------------------------------------------------------------------|

| NO.      | NAME        | I/O    | DESCRIPTION                                                                       |

| 41       | V33FB       | Output | Connection to the base of 3.3V linear regulator transistor (no connect if unused) |

| 42       | CS-1A       | Input  | Power stage 1A current sense input and input to analog comparator 1               |

| 43       | ADDR_1      | Input  | Address sense. Channel 1                                                          |

| 44       | ADDR_0      | Input  | Address sense. Channel 0                                                          |

| 45       | Vtrack      | Input  | Voltage Track Input                                                               |

| 46       | Temperature | Input  | Temperature Sense input                                                           |

| 47       | Agnd2       | Input  | Analog Ground                                                                     |

| 48       | ADCref      | Input  | ADC Decoupling Capacitor - Tie 0.1 µF cap to ground                               |

| PowerPad | Power Pad   | Input  | It is recommended that this pad be connected to analog ground                     |

#### **FUNCTIONAL OVERVIEW**

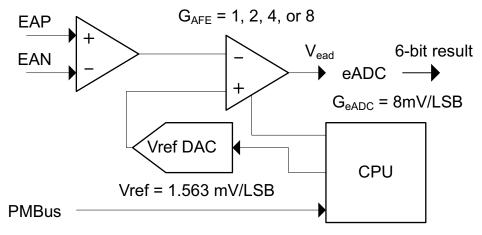

The UCD9220 contains two fusion power peripherals (FPP). Each FPP can be configured to regulate up to two DC/DC converter outputs. There are four PWM outputs that can be assigned to drive the coverter outputs. Each FPP can be configured to drive from one of the four power stages. Each FPP consists of:

- A differential input error voltage amplifier.

- A 10-bit DAC used to set the output regulation reference voltage.

- A fast ADC with programmable input gain to digitally measure the error voltage.

- A dedicated 3-pole/3-zero digital filter to compensate the error voltage.

- A digital PWM (DPWM) engine that generates the PWM pulse width based on the compensator output.

Each controller is configurable through a PMBus serial interface.

#### **PMBus Interface**

The PMBus is a serial interface specifically designed to support power management. It is based on the SMBus interface that is built on the I<sup>2</sup>C physical specification. The UCD9220 supports revision 1.1 of the PMBus standard. Wherever possible, standard PMBus commands are used to support the function of the device. For unique features of the UCD9220, MFR\_SPECIFIC commands are defined to configure or activate those features. These commands are defined in the UCD92xx PMBUS Command Reference.

The UCD9220 is PMBus compliant, in accordance with the "Compliance" section of the PMBus specification. The firmware is also compliant with the SMBus 1.1 specification, including support for the SMBus ALERT function. The hardware can support 100 kHz, 400 kHz, or 1 MHz PMBus operation.

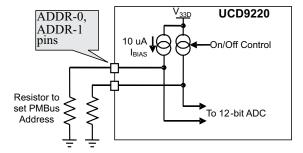

#### **Resistor Programmed PMBus Address Decode**

Two pins are allocated to decode the PMBus address. At power-up, the device applies a bias current to each address detect pin, and the voltage on that pin is captured by the internal 12-bit ADC. The PMBus address is calculated as follows:

PMBus Address =

$$12 \times bin(V_{AD01}) + bin(V_{AD00})$$

(2)

Where bin(V<sub>AD0x</sub>) is the address bin for one of 8 address as shown in Table 1.

Figure 4. PMBus Address Detection Method

The address bins are defined so that each bin is a constant ratio of the previous bin. This method maintains the width of each bin relative to the tolerance of the standard 1% resistors. The ratio betweens bins is 1.30.

Table 1. PMBus Address Bins

| PMBus ADDRESS | R <sub>PMBus</sub><br>PMBus RESISTANCE (kΩ) |

|---------------|---------------------------------------------|

| open          | -                                           |

| 11            | 210                                         |

| 10            | 158                                         |

| 9             | 115                                         |

| 8             | 84.5                                        |

Table 1. PMBus Address Bins (continued)

| PMBus ADDRESS | R <sub>PMBus</sub><br>PMBus RESISTANCE (kΩ) |

|---------------|---------------------------------------------|

| 7             | 63.4                                        |

| 6             | 47.5                                        |

| 5             | 36.5                                        |

| 4             | 27.4                                        |

| short         | _                                           |

A low impedance (short) on either address pin that produces a voltage below the minimum voltage causes the PMBus address to default to address 126. A high impedance (open) on either address pin that produces a voltage above the maximum voltage also causes the PMBus address to default to address 126.

The PMBus address can be set to any value ranging from 1 to 126, except address 12. Address 0 is not used because it is the SMBus General Call address; address 12 is reserved for the PMBus alert response. Also, it is recommended that address 11 not be used by this device or any other device that shares the PMBus with it, since it is used in manufacturing to program the device. Further, address 127 cannot be used by this device or any other device that shares the PMBus with it, since the address is reserved by this device for device manufacturing test.

Finally, it is recommended that address 126 not be used for any devices on the PMBus, since this is the address that the UCD9220 defaults to if the address lines are shorted to ground or left open. If any other UCD9220 has a short or open on its address lines, then its address would conflict with the (programmed) address 126.

If a short or open is detected on the PMBus address pin, then the UCD9220 assigns the address to 126 and enables the JTAG port. Note: if the JTAG port is enabled in this way then the JTAG pins are not available for sequencing.

**Table 2. PMBus Address Assignment Rules**

| ADDRESS | STATUS     | REASON                                                            |

|---------|------------|-------------------------------------------------------------------|

| 0       | Prohibited | SMBus general address call                                        |

| 1-10    | Avaliable  |                                                                   |

| 11      | Avoid      | Causes confilcts with other devices during program flash updates. |

| 12      | Prohibited | PMBus alert response protocol                                     |

| 13-125  | Avaliable  |                                                                   |

| 126     | Avoid      | Default value; may cause conflicts with other devices.            |

| 127     | Prohibited | Used by TI manufacturing for device tests.                        |

SLUS904 – MARCH 2009 www.ti.com

#### **JTAG Interface**

The JTAG interface can provide an alternate interface for programming the device. It is disabled by default in order to enable the sync, and power good status pins with which it is multiplexed. There are three conditions under which the JTAG interface is enabled:

- 1. When the ROM MODE PMBus command is issued.

- 2. On power-up if the Data Flash is blank. This allows JTAG to be used for writing the configuration parameters to a programmed device with no PMBus interaction.

- 3. When an invalid address is detected at power-up. By opening or shorting one of the address pins to ground, an invalid address can be generated that enables JTAG.

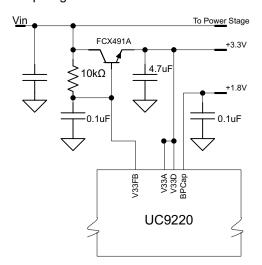

# **Bias Supply Generator (Series Regulator Controller)**

Internally, the circuits in the UCD92XX require 3.3V to operate. This can be provided using an existing 3.3V power supply or it can be generated from the power supply input voltage using an internal series regulator and an external transistor. The requirements for the external transistor are that it be an NPN device with a beta of at least 40. Figure 3 shows the typical application using the external series pass transistor. The base of the transistor is driven by a  $10k\Omega$  resistor to Vin and a transconduction amplifier whose output is on the V33FB pin. The NPN emitter becomes the 3.3 V supply for the chip and requires bypass capacitors of 0.1 µF and 4.7µF.

A transconductance amplifier sinks current into the V33FB pin, in order to regulate the amount of current allowed into the base of the transistor, which regulates the collector current, which determines the emitter voltage (3.3 V). The resistor value should be sized low enough to give efficient base drive at minimum input voltage, yet large enough to not exceed the maximum current sink capability of the V33FV pin at maximum input voltage. Higher beta transistors help in increasing the minimum resistance value, as less base current is needed to sufficiently drive the higher beta transistor. A resistor value of 10 K $\Omega$  works well for most applications that use the FCX491A BJT.

Some circuits in the device require 1.8V that is generated internally from the 3.3V supply. This voltage requires a 0.1 to 1 µF bypass capacitor from BPCap to ground.

Figure 5. 3.3V Regulator Circuit

#### **Power On Reset**

The UCD9220 has an integrated power-on reset (POR) circuit that monitors the supply voltage. At power-up, the POR circuit detects the V33D rise. When V33D is greater than  $V_{IH}$ , the device initiates and internal startup sequence. At the end of the startup sequence, the device begins normal operation, as defined by the downloaded device PMBus configuration.

#### **External Reset**

The device can be forced into the reset state by an external circuit connected to the nRESET pin. A logic low voltage on this pin holds the device in reset. To avoid an erroneous trigger caused by noise, a 10 k $\Omega$  pull up resistor to 3.3V is recommended.

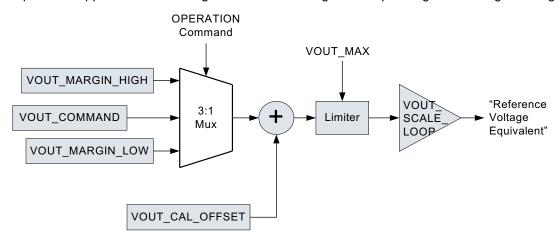

# **Output Voltage Adjustment**

The nominal output voltage is programmed by a combination of PMBus commands: VOUT\_COMMAND, VOUT\_CAL\_OFFSET, and VOUT\_MAX. Their relationship is shown in Figure 6. Output voltage margining is configured by the VOUT\_MARGIN\_HIGH and VOUT\_MARGIN\_LOW commands. The OPERATION command selects between the nominal output voltage and either of the margin voltages. The OPERATION command also includes an option to suppress certain voltage faults and warnings while operating at the margin settings.

Figure 6. PMBus Voltage Adjustment Methods

For a complete description of the commands supported by the UCD9220 see the UCD92xx PMBUS Command Reference. Each of these commands can also be issued from the Texas Instruments Fusion Digital Power™ Designer program. This Graphical User Interface (GUI) PC program issues the appropriate commands to configure the UCD9220 device.

#### Calibration

To optimize the operation of the UCD9220, PMBus commands are supplied to enable fine calibration of output voltage, output current, and temperature measurements. The supported commands and related calibration formulas may be found in the UCD92xx PMBUS Command Reference.

# **Analog Front End (AFE)**

Figure 7. Analog Front End Block Diagram

SLUS904 - MARCH 2009 www.ti.com

The UCD9220 senses the power supply output voltage differentially through the EAP and EAN pins. The error amplifier utilizes a switched capacitor topology that provides a wide common mode range for the output voltage sense signals. The fully differential nature of the error amplifier also ensures low offset performance.

The output voltage is sampled at a programmable time (set by the EADC SAMPLE TRIGGER PMBus command). When the differential input voltage is sampled, the voltage is captured in internal capacitors and then transferred to the error amplifier where the value is subtracted from the set-point reference which is generated by the 10-bit Vref DAC as shown in Figure 7. The resulting error voltage is then amplified by a programmable gain circuit before the error voltage is converted to a digital value by the flash ADC. This programmable gain is configured through the PMBus and affects the dynamic range and resolution of the sensed error voltage as shown in Table 3.

| AFE GAIN | AFE_GAIN for PMBus COMMAND | EFFECTIVE ADC<br>RESOLUTION (mV) | DIGITAL ERROR<br>VOLTAGE DYNAMIC<br>RANGE (mV) |  |  |

|----------|----------------------------|----------------------------------|------------------------------------------------|--|--|

| 1        | 0                          | 8                                | -256 to 248                                    |  |  |

| 2        | 1                          | 4                                | -128 to 124                                    |  |  |

| 4        | 2                          | 2                                | -64 to 62                                      |  |  |

| 8        | 3                          | 1                                | -32 to 31                                      |  |  |

**Table 3. Analog Front End Resolution**

The AFE variable gain is one of the compensation coefficients that are stored when the device is configured by issuing the CLA GAINS PMBus command. Compensator coefficients are arranged in several banks: one bank for start/stop ramp or tracking, one bank for normal regulation mode and one bank for light load mode. This allows the user to trade-off resolution and dynamic range for each operational mode.

The EADC, which samples the error voltage, has high accuracy, high resolution, and a fast conversion time. However, its range is limited as shown in Table 3. If the output voltage is different from the reference by more than this, the EADC reports a saturated value at -32 LSBs or 31 LSBs. The UCD9220 overcomes this limitation by adjusting the Vref DAC up or down in order to bring the error voltage out of saturation. In this way, the effective range of the ADC is extended. When the EADC saturates, the Vref DAC is slewed at a rate of 0.156 V/ms, referred to the EA differential inputs.

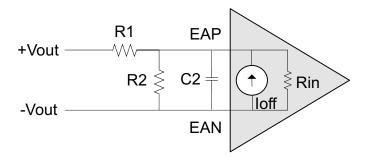

The differential feedback error voltage  $V_{EA} = V_{EAP} - V_{EAN}$ . For brief instances,  $V_{EA}$  may go as high as the maximum value of  $V_{DIFF}$ ; however, the steady-state commanded voltage must be less than the maximum value of V<sub>ref</sub>, which is lower. An attenuator network using resistors R1 and R2 should be used to ensure that V<sub>EA</sub> does not exceed the maximum value of V<sub>DIFF</sub> when operating at the commanded voltage level.

Figure 8. Input Offset Equivalent Circuit

To obtain the best possible accuracy, the input resistance and offset current on the device should be considered when calculating the gain of a voltage divider between the output voltage and the EA sense inputs of the UCD9220. The input resistance and input offset current are specified in the parametric tables in this datasheet.  $V_{EA} = V_{EAP} - V_{EAN}$  in the equation below.

$$V_{EA} = \frac{R_2}{R_1 + R_2 + \left(\frac{R_1 R_2}{R_{IN}}\right)} V_{OUT} + \frac{R_1 R_2}{R_1 + R_2 + \left(\frac{R_1 R_2}{R_{IN}}\right)} I_{OFF}$$

(3)

Product Folder Links: UCD9220

Submit Documentation Feedback

The effect of the offset current can be reduced by making the resistance of the divider network low. R1 should be between  $1k\Omega$  and  $5k\Omega$ . Then R2, the lower divider resistor, can be calculated as:

$$R_2 = \frac{R_1 V_{EA}}{V_{OUT} - \left(1 + \frac{R_1}{R_{IN}}\right) V_{EA} \pm R_1 I_{OFF}}$$

(4)

# **EAP/EAN Voltage Sense Filtering**

Conditioning should be provided on the EAP and EAN signals. Figure 8 shows a divider network between the output voltage and the voltage sense input to the controller. The resistor divider is used to bring the output voltage within the dynamic range of the controller. When no attenuation is needed, R2 can be left open and the signal conditioned by the low-pass filter formed by R1 and C2.

As with any power supply system, maximize the accuracy of the output voltage by sensing the voltage directly across an output capacitor, and route the positive and negative differential sense signals as a balanced pair of traces or as a twisted pair cable back to the controller. Put the divider network close to the controller. This ensures that there is a low impedance driving the differential voltage sense signal from the voltage rail output back to the controller. The resistance of the divider network is a trade-off between power loss and minimizing interference susceptibility. A parallel resistance of 1k to  $4k\Omega$  is a good compromise.

$$R_1 = \frac{R_P}{K} \quad R_2 = \frac{R_P}{1 - K} \quad \text{where} \quad K = \frac{V_{EA}}{V_{OUT}} \quad \text{and} \quad R_P = \frac{R_1 R_2}{R_1 + R_2}$$

(5)

It is recommended that a capacitor be placed across the lower resistor of the divider network. This acts as an additional pole in the compensation and as an anti-alias filter for the EADC. To be effective as an anti-alias filter, the corner frequency should be 35% to 40% of the switching frequency. Then the capacitor is calculated as:

$$C_2 = \frac{1}{2\pi \times 0.35 \times F_{SW} \times R_P} \tag{6}$$

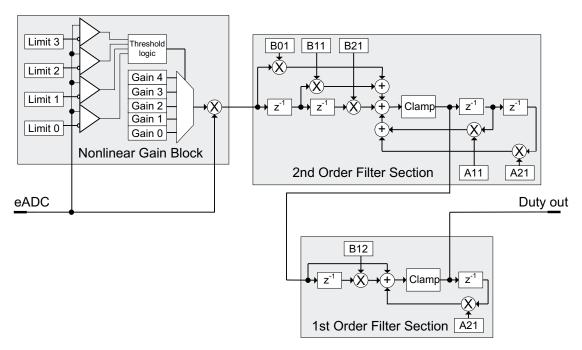

# **Digital Compensator**

Each voltage rail controller in the UCD9220 includes a digital compensator. The compensator consists of a nonlinear gain stage, followed by a digital filter consisting of a second order infinite impulse response (IIR) filter section cascaded with a first order IIR filter section.

The Texas Instruments Fusion Digital Power™ Designer development tool can be used to assist in defining the compensator coefficients. The design tool allows the compensator to be described in terms of the pole frequencies, zero frequencies and gain desired for the control loop. In addition, the Fusion Digital Power™ Designer can be used to characterize the power stage so that the compensator coefficients can be chosen based on the total loop gain for each feedback system. The coefficients of the filter sections are generated through modeling the power stage and load.

Additionally, the UCD9220 has three banks of filter coefficients: Bank-0 is used during the soft start/stop ramp or tracking; Bank-1 is used while in regulation mode; and Bank-2 is used when the measured output current is below the configured light load threshold.

SLUS904 – MARCH 2009 www.ti.com

Figure 9. Digital Compensator

The nonlinear gain block allows a different gain to be applied to the system when the error voltage deviates from zero. Typically Limit 0 and Limit 1 would be configured with negative values between –1 and –32 and Limit 2 and Limit 3 would be configured with positive values between 1 and 31. However, the gain thresholds do not have to be symmetrical. For example, the four limit registers could all be set to positive values causing the Gain 0 value to set the gain for all negative errors and a nonlinear gain profile would be applied to only positive error voltages.

The cascaded 1st order filter section is used to generate the third zero and third pole.

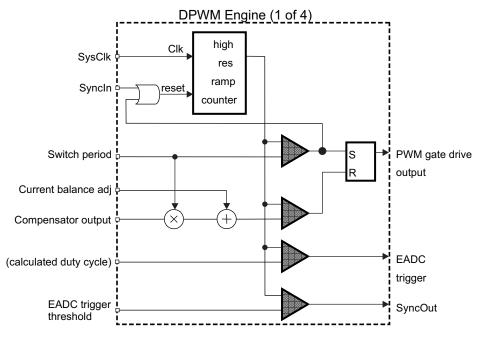

#### **DPWM Engine**

The output of the compensator feeds the high resolution DPWM engine. The DPWM engine produces the pulse width modulated gate drive output from the device. In operation, the compensator calculates the necessary duty cycle as a digital number representing a percentage from 0 to 100%. The duty cycle value is multiplied by the configured period to generate a comparator threshold value. This threshold is compared against the high speed switching period counter to generate the desired DPWM pulse width. This is shown in Figure 10.

Each DPWM engine can be synchronized to another DPWM engine or to an external sync signal via the SYNC\_IN and SYNC\_OUT pins. Configuration of the synchronization function is done through a MFR\_SPECIFIC PMBus command. See the DPWM Synchronization section for more details.

Submit Documentation Feedback

Figure 10. DPWM Engine

# Flexible Rail/Power Stage Configuration

The UCD9220 can control one to two voltage rails, each of which can comprise a programmable number of power stages (up to a maximum of four). The following table shows all possible rail / power stage configurations. Configuration is made through the PHASE\_INFO command which is described in detail in the UCD92xx PMBus Command Reference.

Table 4. Power Stage Configurations<sup>(1)</sup>

| NUMBER OF STAGES<br>RAIL #1 : RAIL #2 | RAIL #1 POWER STAGES       | RAIL #2 POWER STAGES |  |  |  |  |

|---------------------------------------|----------------------------|----------------------|--|--|--|--|

| 4:0                                   | 1A, 1B, 2A, 3A             | (none)               |  |  |  |  |

| 3:0                                   | 1A, 1B, 2A                 | (none)               |  |  |  |  |

| 2:0                                   | 1A, 1B                     | (none)               |  |  |  |  |

| 1:0                                   | 1A                         | (none)               |  |  |  |  |

| 3:1                                   | 1A, 1B, 3A                 | 2A                   |  |  |  |  |

| 2:1                                   | 1A, 1B                     | 2A                   |  |  |  |  |

| 1:1                                   | 1A                         | 2A                   |  |  |  |  |

| 2:2                                   | 1A, 1B                     | 2A, 3A               |  |  |  |  |

| 1:2                                   | 1A                         | 2A, 3A               |  |  |  |  |

| 1:3                                   | Invalid (use               | 3 : 1 instead)       |  |  |  |  |

| 0:4                                   | Invalid (use               | e 4: 0 instead)      |  |  |  |  |

| 0:3                                   | Invalid (use 3:0 instead)  |                      |  |  |  |  |

| 0:2                                   | Invalid (use 2: 0 instead) |                      |  |  |  |  |

| 0 : 1                                 | Invalid (use               | 1:0 instead)         |  |  |  |  |

<sup>(1)</sup> Phases should be selected in the order listed. For a two single phase rail configuration, power stage selections should be 1A and 2A.

#### **DPWM Phase Distribution**

When two rails are configured, the UCD9220 offsets (in time) the phase of the 1st power stage assigned to each rail in order to minimize input current ripple. The constant time used for this offset is:

$$t_{rail-rail\ spread} = \frac{3}{13} t_{SW}$$

(7)

Where t<sub>SW</sub> is the period of the rail with the fastest switching frequency.

The ratio 3/13 is chosen because it is close to 1/4, but it is a prime ratio. This should ensure that any configuration of rails and power stages should not have the leading edge of the DPWM signal aligned.

The PHASE\_INFO PMBus command is also used to configure the number of power stages driving each voltage rail. When multiple power stages are configured to drive a voltage rail, the UCD9220 automatically distributes the phase of each DPWM output to minimize ripple. This is accomplished by setting the rising edge of each DPWM pulse to be separated by:

$$t_{phase-phase spread} = \frac{t_{SW}}{N_{Phases}}$$

(8)

Where t<sub>SW</sub> is the switching period and N<sub>Phases</sub> is the number of power stages driving a voltage rail.

# **DPWM Synchronization**

DPWM synchronization provides a method to link the timing between rails on two distinct devices at the switching rate; i.e., two rails on different devices can be configured to run at the same frequency and sync forcing them not to drift from each other. (Note that within a single device, because all rails are driven off a common clock there is no need for an internal sync because rails will not drift.)

The PMBus SYNC\_IN\_OUT command sets which rails (if any) should follow the sync input, and which rail (if any) should drive the sync output.

For rails that are following the sync input, the DPWM ramp timer for that output is reset when the sync input goes high. This allows the slave device to sync to inputs that are either faster or slower than it is. On the fast side, there is no limit to how much faster the input is compared to the defined frequency of the rail; when the pulse comes in, the timer is reset and the frequencies are locked. This is the standard mode of operation - setting the slave to run slower, and letting the sync speed it up.

If the slave rail is running fast, the sync pulse resets the counter after the DPWM output has already been turned on. Resetting the counter at this point results in a larger duty cycle for that period. Because the system is closed loop; however, the controller reacts by decreasing the commanded control effort, with the result being a regulated rail synchronized to a slower master. Synchronizing to the slower master does have a limit however. If the master is slow enough that the DPWM output has sufficient time to output the entire command pulse before the sync input arrives, the result is a double pulse. This is likely an undesirable mode of operation.

The Sync Input and Output Configuration Word set by the PMBus command consists of two bytes. The upper byte (sync\_out) controls which rail drives the sync output signal (0=DWPM1, 1=DPWM2, 2=DPWM3, 3=DPWM4. Any other value disables sync\_out). The lower byte (sync\_in) determines which rail(s) respond to the sync input signal (each bit represents one rail - note that multiple rails can be synchronized to the input). The DPWM period is aligned to the sync input. For more information, see the UCD92xx PMBUS Command Reference.

Note that once a rail is synchronized to an external source, the rail-to-rail spacing that attempts to minimize input current ripple are lost. Rail-to-rail spacing can only be restored by power cycling or issuing a SOFT\_RESET command.

#### Phase Shedding at Light Current Load

By issuing LIGHT\_LOAD\_LIMIT\_LOW, LIGHT\_LOAD\_LIMIT\_HIGH, and LIGHT\_LOAD\_CONFIG commands, the UCD9220 can be configured to shed (disable) power stages when at light load. When this feature is enabled, the device disables the configured number of power stages when the average current drops below the specified LIGHT\_LOAD\_LIMIT\_LOW. In addition, a separate set of compensation coefficients can be loaded into the digital compensator when entering a light load condition.

#### **Phase Adding at Normal Current Load**

After shedding phases, if the current load is increased past the LIGHT\_LOAD\_LIMIT\_HIGH threshold, all phases are re-enabled. If the compensator was configured for light load, the normal load coefficients are restored as well. See the UCD92xx PMBUS Command Reference for more information.

# **Current Sense Input Filtering**

Each power stage current is monitored by the device at the CS pins. There are 3 "A" channel pins and 1 "B" channel pin. The B channels monitors the current with a 12-bit ADC and samples each current sense voltage in turn. The A channels monitor the current with the same12-bit ADC and also monitor the current with a digitally programmable analog comparator.

Because the current sense signal is digitally sampled, it should be conditioned with an RC network acting as an anti-alias filter. Since the sample rate for the CS inputs is  $1/t_{lout}$ , a good cutoff frequency for the RC network is from 2 kHz to 3 kHz.

# **Output Current Measurement**

Pins CS-1A, CS-1B, CS-2A, and CS-3A are used to measure either output current or inductor current in each of the controlled power stages. PMBus commands IOUT\_CAL\_GAIN and IOUT\_CAL\_OFFSET are used to calibrate each measurement. See the UCD92xx PMBus Command Reference for specifics on configuring this voltage to current conversion.

When the measured current is outside the range of either the over-current or under-current fault threshold, a current fault is declared and the UCD9220 performs the PMBus configured fault recovery. ADC current measurements are digitally averaged before they are compared against the current fault threshold. The output current is measured at a rate of one output rail per t<sub>lout</sub> microseconds. The current measurements are then passed through a digital smoothing filter to reduce noise on the signal and prevent false errors. The output of the smoothing filter asymptotically approaches the input value with a time constant that is approximately 3.5 times the sampling interval.

**OUTPUT CURRENT SAMPLING NUMBER OF OUTPUT RAILS** FILTER TIME CONSTANTS (ms) INTERVALS (µs) 1 200 0.7 1.4 2 400 3 600 2.1 4 800 2.8

**Table 5. Output Current Filter Times Constants**

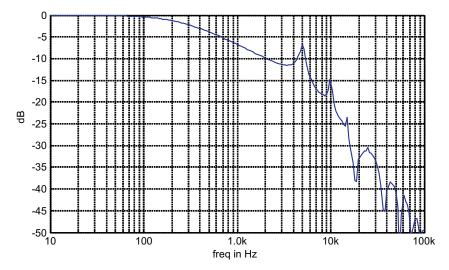

For example, with a single rail, the filter has the transfer function characteristics (Figure 11) that shows the signal magnitude at the output of the averaging filter due to a sine wave input for a range of frequencies. This plot includes an RC analog low pass network, with a corner frequency of 3 kHz, on the current sense inputs.

This averaged current measurement is used for output current fault detection; see Over-current Detection below.

In response to a PMBus request for a current reading, the device returns an average current value. When the UCD9220 is configured to drive a multi-phase power converter, the device adds the average current measurement for each of the power stages tied to a power rail.

Figure 11. Averaging Filter for Current Monitoring

# **Output Current Balancing**

When the UCD9220 is configured to drive multiple power stage circuits from one compensator, current balancing is implemented by adjusting each gate drive output pulse width to correct for current imbalance between the connected power stage sections. The UCD9220 balances the current by monitoring the current at the CS analog input for each power stage and then adding a current balance adjustment value to the DPWM ramp threshold value for each power stage.

When there is more than one power stage connected to the voltage rail, the device continually determines which stage has the highest measured current and which stage has the lowest measured current. To balance the currents while maintaining a constant total current, the adjustment value for the power stage with the lowest current is increased by the same amount as the adjustment value for the power stage with the highest current is decreased. A slight modification to this algorithm is made to keep the adjustment values positive in order to ensure that a positive DPWM duty cycle is commanded under all conditions.

#### **Over-Current Detection**

Several mechanisms are provided to sense output current fault conditions. This allows for the design of power systems with multiple layers of protection.

- 1. An integrated gate driver such as the UCD7230 can be used to generate the FLT signal. The UCD7230 monitors the voltage drop across the high side FET and if it exceeds a resistor/voltage programmed threshold, the UCD7230 activates its fault output. The FLT input can be disabled by reconfiguring the FLT pin to be a sequencing pin in the GUI. A logic high signal on the FLT input causes a hardware interrupt to the internal CPU. The CPU then determines which DPWM outputs are configured to be associated with the voltage rail that contained the fault and disables those DPWM and SRE outputs. This process takes about 14 microseconds.

- 2. Inputs CS-1A, CS-1B, CS-2A and CS-3A each drive an internal analog comparator. These comparators can be used to detect the voltage output of a current sense circuit. Each comparator has a separate PMBus configurable threshold. This threshold is set by issuing the FAST\_OC\_FAULT\_LIMIT command. Though the command is specified in amperes, the hardware threshold is programmed with a value between 31mV and 2V in 64 steps. The relationship between the amperes to sensed volts is configured using the IOUT\_CAL\_GAIN command. When the current sense voltage exceeds the configured threshold the corresponding DPWM and SRE outputs are driven low on the voltage rail with the fault.

3. Each Current Sense input to the UCD9220 is also monitored by the 12-bit ADC. Each measured value is scaled using the IOUT\_CAL\_GAIN and IOUT\_CAL\_OFFSET commands. The currents for each power stage configured as part of a voltage rail are summed and compared to the OC limit set by the IOUT\_OC\_FAULT\_LIMIT command. The action taken when a fault is detected is defined by the IOUT\_OC\_FAULT\_RESPONSE command.

Because the current measurement is averaged with a smoothing filter, the response time to an Over-current condition depends on a combination of the time constant  $(\tau)$  from Table 5, the recent measurement history, and how much the measured value exceeds the over-current limit. When the current steps from a current  $(I_1)$  that is less than the limit to a higher current  $(I_2)$  that is greater than the limit, the output of the smoothing filter is:

$$I_{\text{smoothed}}(t) = I_1 + \left(I_2 - I_1\right) \left(1 - e^{\frac{-t}{\tau}}\right)$$

(9)

At the point when  $I_{smoothed}$  exceeds the limit, the smoothing filter lags time,  $t_{lag}$  is:

$$t_{lag} = \tau \ln \left( \frac{I_2 - I_1}{I_2 - I_{limit}} \right)$$

(10)

The worst case response time to an over-current condition is the sum of the sampling interval (see Table 5) and the smoothing filter lag,  $t_{laq}$  from the equation above.

#### **Current Foldback Mode**

When the measured output current exceeds the value specified by the IOUT\_OC\_FAULT\_LIMIT command, the UCD9220 attempts to continue to operate by reducing the output voltage in order to maintain the output current at the value set by IOUT\_OC\_FAULT\_LIMIT. This continues indefinitely as long as the output voltage remains above the minimum value specified by IOUT\_OC\_LV\_FAULT\_LIMIT. If the output voltage is pulled down to less than that value, the device responds as programmed by the IOUT\_OC\_LV\_FAULT\_RESPONSE command.

# **Input Voltage and Current Monitoring**

The Vin/lin pin on the UCD9220 monitors the input voltage and current. To measure both input voltage and input current, an external multiplexer is required, see Figure 3. If measurement of only the input voltage, and not input current, is desired, then a multiplexer is not needed. The multiplexer is switched between voltage and current using the TMUX-0 signal. (This signal is the LSB of the temperature mux select signals, so the TMUX-0 signal is connected both to the temperature multiplexer as well as the voltage/current multiplexer). When TMUX-0 is low, the  $V_{in}/I_{in}$  pin will be sampled for  $I_{in}$ . The  $I_{in}/I_{in}$  pin is monitored using the internal 12-bit ADC which has a dynamic range of 0 to 2.5V. The fault thresholds for the input voltage are set using the VIN\_OV\_FAULT\_LIMIT and VIN\_UV\_FAULT\_LIMIT commands. The scaling for Vin is set using the VIN\_SCALE\_MONITOR command, and the scaling for lin is set using the IIN SCALE MONITOR command.

#### **Temperature Monitoring**

Both the internal device temperature and up to four external temperatures are monitored by the UCD9220. The controller supports multiple PMBus commands related to temperature, including READ\_TEMPERATURE\_1, which reads the internal temperature, READ\_TEMPERATURE\_2, which reads the external power stage temperatures, OT\_FAULT\_LIMIT, which sets the over temperature fault limit, and OT\_FAULT\_RESPONSE, which defines the action to take when the configured limit is exceeded.

If more than one external temperature is to be measured, the UCD9220 provides analog multiplexer select pins (TMUX0-1) to allow up to 4 external temperatures to be measured. The output of the multiplexer is routed to the Temperature pin. The controller cycles through each of the power stage temperature measurement signals. The signal from the external temperature sensor is expected to be a linear voltage proportional to temperature. The PMBus commands TEMPERATURE\_CAL\_GAIN and TEMPERATURE\_CAL\_OFFSET are used to scale the measured temperature-dependent voltage to °C.

The inputs to the multiplexer are mapped in the order that the outputs are assigned in the PHASE\_INFO PMBus command. For example, if only one power stage is wired to each DPWM, the two temperature signals should be wired to the first two multiplexer inputs.

SLUS904 – MARCH 2009 www.ti.com

The UCD9220 monitors temperature using the 12-bit monitor ADC, sampling each temperature in turn with a 800 ms sample period. These measurements are smoothed by a digital filter, similar to that used to smooth the output current measurements. The filter has a time constant 15.5 times the sample interval, or 12.4 s (15.5  $\times$  800 ms = 12.4 seconds). This filtering reduces the probability of false fault detections.