#### **Radiation Tolerant 8-Channel Source Driver**

#### **Description**

The AAHS298B is part of Microsemi's new family of Radiation Tolerant products aimed at the aerospace and defense markets. The AAHS298B is a Radiation-Tolerant source driver with eight non-inverting channels, with internal thermal shutdown.

Capable of providing an interface from TTL, 5V or 12V logic systems to relays, motors, solenoids, and other loads, this device adds the additional benefit of an internal thermal shutdown and output transient protection/clamp diodes with sustaining voltages to 75V.

Each output is capable of sourcing 700mA with a withstand voltage of 75V over the full military temperature range. The thermal shutdown is intended to protect against over-current and soft-start occurrences.

The AAHS298B is offered in 20-pin ceramic SOIC package with formed and flat leads. The AAHS298B has demonstrated tolerance to 100kRad (Si) total dose (min), 50kRad (Si) ELDRS (min), as well as immunity to latch-up and SEE tolerance.

#### **Features**

- 700mA Output Source Current

- Zero Quiescent Off Current

- Full Channel Isolation to Prevent Fault Propagation

- Internal Ground Clamp Diodes

- 75V Output Breakdown Voltage

- TTL, 5V and 12V Logic Compatible

- Internal Thermal Shutdown

- Radiation tolerant to 100kRad(Si) Total Dose, 50kRad (Si) ELDRS

- -55°C to +125°C Temperature Range

- Available in 20-pin Ceramic SOIC with formed and flat Leads

- QML listed with SMD 5962-15231

#### **Applications**

- Relay/Solenoid Drivers

- Lamp/LED Drivers

- Stepper and/or Servo Motor Drivers

#### **Product Highlight**

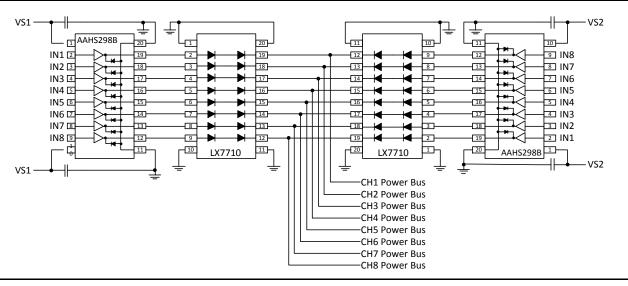

Figure 1 · Redundant Switchable Power Bus

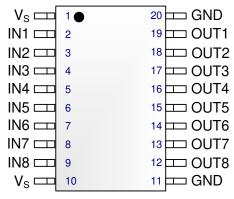

# Pin Configuration and Pinout

S20 PACKAGE

# **Ordering Information**

| Ambient<br>Temperature | Туре     | Package                | Part Number Flow                           |            | Packaging<br>Type |  |

|------------------------|----------|------------------------|--------------------------------------------|------------|-------------------|--|

| -55°C to               | Hermetic | CSOIC 20L<br>Flat Lead | AAHS298B-07-4020A-V<br>SMD 5962-1523101VYC | QML-V      |                   |  |

| 125°C                  |          |                        | AAHS298B-06-4020A-Q<br>SMD 5962-1523101QYC | QML- Q     | Tray              |  |

| -55°C to               | Hermetic | Hermetic CSOIC 20L     | AAHS298B-S-S20B-S<br>SMD 5962-1523101VXC   | QML-V      |                   |  |

| 125°C                  |          |                        | AAHS298B-S-S20B-B<br>SMD 5962-1523101QXC   | QML- Q     |                   |  |

| 0°C to 70°C            |          |                        | AAHS298B-S-S20B-ENGR                       | Commercial |                   |  |

## Pin Description

| Pin Number | Pin Designator | Description                                                                                                                                                                                                  |  |  |

|------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1, 10      | Supply Voltage | Input Supply Voltage, both pins should be externally connected on the F to improve the internal current distribution and allow the device to safely provide the maximum 2800mA of continuous supply current. |  |  |

| 2-9        | IN[1:8]        | 8 Logic Inputs, TTL, CMOS & High Voltage (12V) compatible. With all inputs low the device is in sleep mode.                                                                                                  |  |  |

| 11, 20     | GND            | Ground, both pins should be externally connected externally on the PCB to improve the internal current distribution and improve forward voltage of the flyback clamping diodes.                              |  |  |

| 12-19      | OUT[1:8]       | 700mA Source Outputs.                                                                                                                                                                                        |  |  |

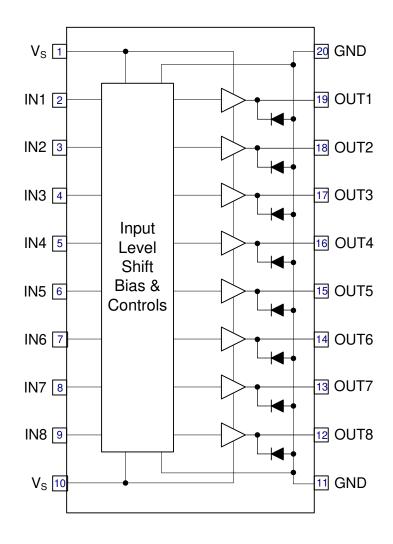

# **Block Diagram**

Figure 2 · AAHS298B Simplified Block Diagram

### **Absolute Maximum Ratings**

| Parameter                                                           | Value        | Units |

|---------------------------------------------------------------------|--------------|-------|

| Supply Voltage (VS, Max voltage between VS and GND)                 | -0.5 to 75   | V     |

| Digital Inputs (IN[1:8], Max voltage between INPUT & GND)           | -0.5 to 15   | V     |

| Output Voltage (OUT[1:8], Maximum voltage between OUT[1:8] and GND) | 75           | V     |

| Single Output Continuous Current (OUT[1:8])                         | -700         | mA    |

| Single Output Peak Current (OUT[1:8], ≤ 1 second)                   | -1200        | mA    |

| Multiple Output Simultaneously Continuous Current (OUT[1:8])        | -2800        | mA    |

| ESD (all pins, HBM)                                                 | 2000         | V     |

| Operating Junction Range                                            | -55 to 150   | °C    |

| Storage Temperature Range                                           | -65 to 150   | °C    |

| Lead Temperature (Soldering, 10 Seconds)                            | 300          | °C    |

| Peak Package Solder Reflow Temp. (40 sec. max. exp.)                | 260 (+0, -5) | °C    |

| Lead Temperature. (Soldering 10 seconds)                            | 300          | °C    |

Exceeding these ratings could cause damage to the device. All voltages are with respect to GND. Currents are positive into, negative out of specified terminal. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" are not implied. Exposure to "Absolute Maximum Ratings" for extended periods may affect device reliability.

#### **Thermal Data**

| Parameter                                          | Value | Units |  |  |

|----------------------------------------------------|-------|-------|--|--|

| S20 Package:                                       |       |       |  |  |

| Thermal Resistance-Junction to Case, $\theta_{JC}$ | 2.24  | °C/W  |  |  |

Note: The  $\theta_{JC}$  number is for conduction only to the ceramic base of the package. It assumes that the ceramic base has a thermal epoxy underneath the ceramic package to exhaust the heat from the package into the PCB, or other mounting surface.

### **Electrical Characteristics**

Unless otherwise stated the following specifications apply over operating ambient temperature of -55 $^{\circ}$ C < Temp < 125 $^{\circ}$ C, V<sub>S</sub> = 50V, 100kRad (Si) TID (min), 50kRad (Si) ELDRS (min)

| 0                    | B                                     | Total Constitution                         | Test   |     |     |     |       |

|----------------------|---------------------------------------|--------------------------------------------|--------|-----|-----|-----|-------|

| Symbol               | Parameter                             | Test Condition                             | Setup  | Min | Тур | Max | Units |

| Operation            | ng Supply Current                     |                                            |        |     |     |     |       |

| I <sub>SLEEP</sub>   | Standby Supply Current                | IN[1:8] = 0.0V, No Output Load             | 1      |     | 1   | 20  | μΑ    |

| I <sub>VS2.5</sub>   | Active Supply Current                 | IN[1:8] = 2.5V, No Output Load             | _oad 2 |     | 5   | 25  | mA    |

| I <sub>VS5</sub>     | Active Supply Current                 | IN[1:8] = 5.0V, No Output Load             |        |     | 7   | 25  | IIIA  |

| AC Cha               | racteristics                          |                                            |        |     |     |     |       |

| t <sub>on</sub>      | Output Turn On Delay<br>Time          |                                            |        |     |     | 2   |       |

| t <sub>off</sub>     | Output Turn Off Delay<br>Time         | Load = $470\Omega$ , $100pF$ , $V_S = 45V$ |        |     |     | 10  |       |

| t <sub>R</sub>       | Output Rise Time (10% to 90%)         | $V_{IL} = 0.8; V_{IH} = 2.5V$              |        |     |     | 2   | μs    |

| t <sub>F</sub>       | Output Fall Time (90% to 10%)         |                                            |        |     |     | 10  |       |

| DC Cha               | racteristics                          |                                            |        |     |     |     |       |

| Vs                   | Supply Voltage Range                  |                                            |        | 10  |     | 50  | ٧     |

| THSD <sub>TRIP</sub> | Thermal Shutdown Trip<br>Temperature  |                                            |        | 135 | 155 | 175 | 9     |

| THSD <sub>RST</sub>  | Thermal Shutdown Reset<br>Temperature | Restarts at 125°C                          |        | 125 |     |     | ōС    |

| $V_{IH}$             | Input High Level                      |                                            |        | 2.5 |     |     |       |

| V <sub>IL</sub>      | Input Low Level                       |                                            | 3      |     |     | 0.8 |       |

| VCE <sub>SAT</sub>   | Output Saturation at 350mA            |                                            |        |     | 1.7 | 2.2 | V     |

| VCE <sub>SAT</sub>   | Output Saturation at 500mA            | IN[1:8] = 2.5V                             |        |     | 1.8 | 2.3 |       |

| VCE <sub>SAT</sub>   | Output Saturation at 700mA            |                                            |        |     | 2.1 | 2.7 |       |

| I <sub>IH</sub>      | Input High Leakage                    | IN[1:8] = 5.0V                             | _      |     | 60  | 100 |       |

| I <sub>IL</sub>      | Input Low Leakage                     | IN[1:8] = 0.0V                             | 5      |     | 0.1 | 10  | μΑ    |

| l <sub>OL</sub>      | Output Low Leakage                    | Output OFF, VOUTX = 0.0V                   | 6      |     | 2   | 50  |       |

|                      | Clamp Diode Forward<br>Voltage        | I <sub>F</sub> = 200mA                     | 7      |     |     | 2.5 |       |

| $V_{F}$              |                                       | I <sub>F</sub> = 700mA                     |        |     |     | 3.0 | V     |

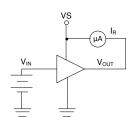

| I <sub>R</sub>       | Clamp Diode Leakage<br>Current        | V <sub>R</sub> = 50V                       | 8      |     |     | 50  | μΑ    |

## **Parameter Test Configurations**

(See test setup numbers in Electrical Characteristics Table)

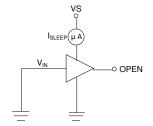

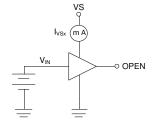

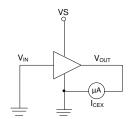

Test Setup 1 Standby Supply Current

Test Setup 2 Active Supply Current

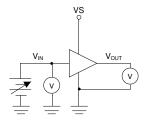

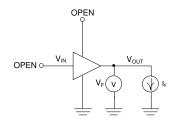

Test Setup 3 Input Threshold Voltage

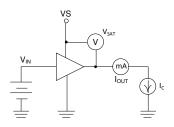

Test Setup 4  $V_{CE(sat)}$  Test Circuit

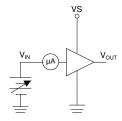

Test Setup 5 Input Bias Current

Test Setup 6 Output Leakage Current

Test Setup 7 Clamp Diode Forward Voltage

Test Setup 8 Clamp Diode Leakage Current

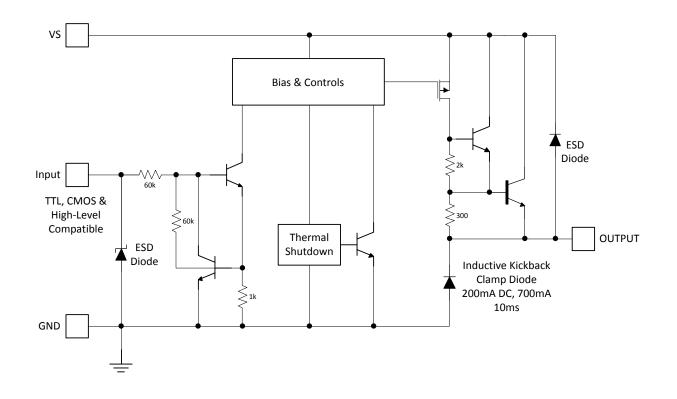

### Single Channel Block Diagram

Figure 3 · AAHS298B Single Channel Simplified Block Diagram

### **Application Information**

#### **VS Pins**

The AAHS298B has two VS (Input Supply) pins (pins 1, 10). The maximum 2800mA total supply current limit for the AAHS298B comes from the supply bond wires current capability, these bond wires will fuse open around 2A each. By externally connecting these two pins on the printed-circuit board the utilization of two pins one at each end of the package improves the internal current distribution. With only one VS pin connected, the saturation voltage would progressively increase from the near to the far channel due to internal IR losses in the die metallization, and the part will not be capable of the full 2800mA, only 1400mA.

#### **IN Pins**

The IN (Inputs) pins are compatible with TTL (5V), CMOS (3V) & High-Level (12V) logic levels and not only turn on their respective output but also provide bias to the device activating for instance the thermal shutdown circuitry. Conversely if all IN pins are low the device is off with no quiescent current, and the device is in sleep mode.

#### **OUT Pins**

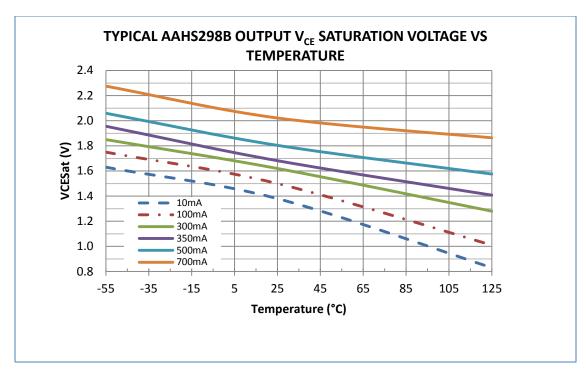

The OUT (Output) pins are switched high-side drivers designed to output 700mA continuous current with a typical saturation voltage drop of 2.1V. See figure 4 for the typical saturation voltages with changes in output current and temperature. At the rated maximum continuous operating current which is 700mA, the saturation voltage still has a negative temperature coefficient as indicated in the chart. This is advantageous since it reduces the power dissipation when the device operates at elevated temperatures.

Above 700mA the saturation increases more rapidly and due to the design of the output transistors the output current self-limits itself around 1.4A, but could reach the bond-wire fusing current of 2A on a "dead" short-circuit condition in a matter of milliseconds. This is a protection feature designed to isolate a shorted output under overstress while allowing the remaining outputs to function normally. The 700mA per channel current was therefore determined to be around 50% of the drive maximum capability of the output transistors.

#### **Thermal Shutdown**

The thermal shut-down circuitry is located in the center of the die between channels 4 & 5. The die being relatively thick, and the silicon being a good conductor of heat, the temperature gradient at the surface of the die, say between channel #1 and #4 cannot exceed a few degrees centigrade.

When all channels are dissipating power, the Junction to Case Thermal Resistance is less than 3°C/W when measured between the junctions at the surface of the silicon and the bottom of the ceramic package. The Junction to Case thermal resistance for one channel only is less than 20°C/W.

When the package is mounted with a heat pad under it on a PCB equipped with an integral heat-sink, the Junction to PCB thermal resistance could be of the order of 10°C/W, and in this condition which we have verified, it is almost impossible for the thermal shut-down circuitry to trip.

On the contrary, if the part is simply mounted on the PCB with no heat sinking we have been able to make the thermal shutdown trip with the PCB at room temperature with 4 channels ON at full load (2800mA total creating approximately 6W of power dissipation).

There is a time constant associated with the thermal shut-down circuitry which measures in seconds and this is why we cannot rely on it to protect the part against "dead" short-circuits during which the current could exceed 2A and blow the bond wire in 10 to 20mS.

#### **Clamp Diodes**

Each output channel includes an integrated clamp diode to protect against possible inductive kick-backs. These diodes are rated for 200mA DC current at a maximum of 2.5V, and can withstand 700mA for about 10ms. Like the VS pins by externally connecting the two GND pins together on the printed-circuit board the utilization of both pins one at each end of the package improves the internal current distribution and losses.

It is very important to recirculate any flyback current close to the source to minimize noise issues. When using the AAHS298B's built-in output transient suppression diodes for this purpose the PCB layout or wiring should insure that the digital input side and output power sides do not share ground paths, and the conductors and/or traces are sized accordingly. When the proximity of the inductive load is some distance from the driver then an additional 'freewheel diode', or snubber circuit may be required to minimize noise and clamp voltage excursions. If using the internal diode causes other complications (delay times, etc.) a varistor or transorb may be used instead. Keeping the power and digital grounds separate and only connecting them at the one star ground point should minimize and ground loop or bounce issues.

### **Characteristic Curves**

Figure 4  $\cdot$  Typical Output  $V_{\text{CE}}$  vs Saturation Voltage

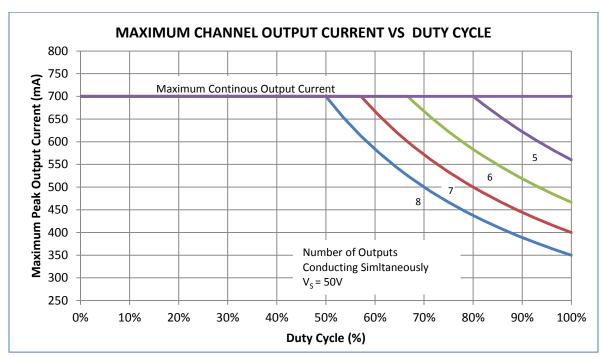

Figure 5 · Maximum Channel Output vs Duty Cycle (≤ 4 channels may be operated continuously at maximum current within package power limitations)

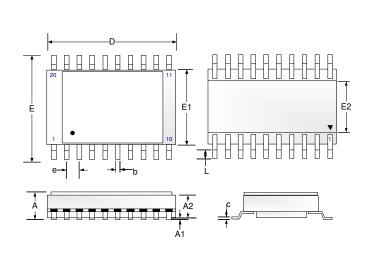

## Package Outline Dimensions

Controlling dimensions are in inches, metric equivalents are shown for general information.

| Dim   | MILLIME ERS |       | INCHES    |       |  |

|-------|-------------|-------|-----------|-------|--|

| DIIII | MIN         | MAX   | MIN       | MAX   |  |

| Α     | 2.28        | 2.92  | 0.090     | 0.115 |  |

| A1    |             | 0.38  |           | 0.015 |  |

| A2    | 1.78        | 2.41  | 0.070     | 0.095 |  |

| b     | 0.36        | 0.48  | .0140     | .0190 |  |

| С     | 0.15        | 0.25  | 0.006     | 0.010 |  |

| D     | 12.45       | 13.08 | 0.490     | 0.515 |  |

| Е     | 10.16       | 11.18 | 0.400     | 0.440 |  |

| E1    | 7.24        | 7.62  | 0.285     | 0.300 |  |

| E2    | 4.70 BSC    |       | 0.185 BSC |       |  |

| е     | 1.27 BSC    |       | 0.050     | ) BSC |  |

| L     | 0.50        | 0.76  | 0.020     | 0.030 |  |

Figure 6 · S20 20-Lead Ceramic SOIC Package Dimensions

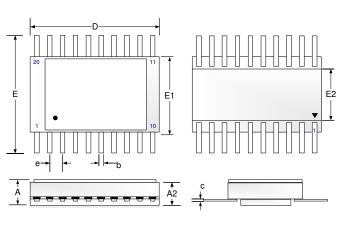

| Dim | MILLIMETERS |       | INCHES    |       |

|-----|-------------|-------|-----------|-------|

|     | MIN         | MAX   | MIN       | MAX   |

| Α   | 2.03        | 2.67  | 0.080     | 0.105 |

| A2  | 1.78        | 2.41  | 0.070     | 0.095 |

| b   | 0.36        | 0.48  | .0140     | .0190 |

| С   | 0.15        | 0.25  | 0.006     | 0.010 |

| D   | 12.45       | 13.08 | 0.490     | 0.515 |

| Е   | 21.00       | 24.00 | 0.827     | 0.945 |

| E1  | 7.24        | 7.62  | 0.285     | 0.300 |

| E2  | 4.70 BSC    |       | 0.185 BSC |       |

| е   | 1.27 BSC    |       | 0.050     | D BSC |

Figure 7  $\cdot$  S20 20-Lead Ceramic SOIC Package with Flat Leads Dimensions

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

E-mail: sales.support@microsemi.com

© 2017 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,400 employees globally. Learn more at www.microsemi.com.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.