Click here to ask an associate for production status of specific part numbers.

### 4.5V to 60V, Synchronous Step-Down Supercapacitor Charger Controller

#### **General Description**

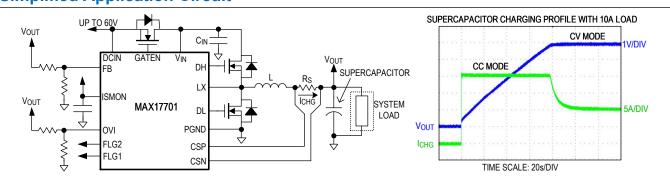

The Himalaya series of voltage regulator ICs, power modules, and chargers enable cooler, smaller, and simpler power supply solutions. The MAX17701 is a high efficiency, high voltage, Himalaya synchronous, step-down, supercapacitor charger controller designed to operate over an input-voltage range of a 4.5V to 60V. The MAX17701 operates over a -40°C to +125°C industrial temperature range and charges a supercapacitor with a  $\pm 4\%$  accurate constant current. After the supercapacitor is charged, the device regulates the no-load output voltage with  $\pm 1\%$  accuracy. The output voltage is programmable from 1.25V up to ( $V_{DCIN}$  - 2.1V).

The MAX17701 supercapacitor charger controller is designed to provide a holistic application solution requiring backup energy storage with a precise charging capability. The device uses an external nMOSFET to provide input supply-side short-circuit protection; thus, preventing supercapacitor discharge.

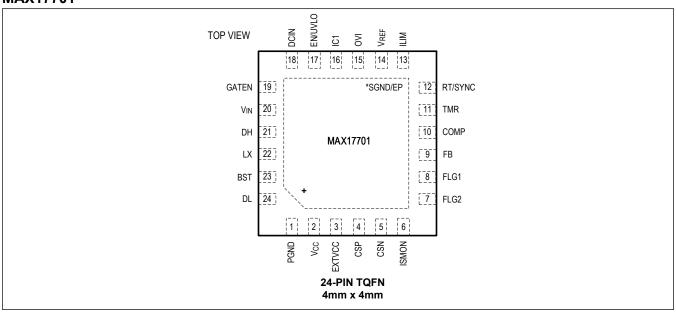

The MAX17701 provides a safety timer (TMR) feature to set the maximum allowed constant current (CC) mode charging time. The device features an uncommitted comparator, which can be used to detect an output overvoltage event (OVI) and prevent the supercapacitor from overcharging. The MAX17701 is available in a 24-pin 4mm x 4mm TQFN package with an exposed pad.

#### **Applications**

- Peak Power Delivery and Energy Storage

- Backup Power for Industrial Safety

- Ride-Through Last-Gasp Supplies

- Portable Medical Equipment

- Building and Home Automation Backup Power

#### **Benefits and Features**

- Optimized Feature Set for Supercapacitor Charging

- ±4% Charging Current Regulation Accuracy

- ±6% Charging Current Monitor Accuracy (ISMON)

- ±1% Voltage Regulation Accuracy

- Programmable CC Mode Charging Current (ILIM)

- Wide 4.5V to 60V Input-Voltage Range

- Adjustable Output-Voltage Range from 1.25V Up To (V<sub>DCIN</sub> - 2.1V)

- 125kHz to 2.2MHz Adjustable Frequency with External Clock Synchronization (RT/SYNC)

- Reliable Operation in Adverse Environmental Conditions

- Input Short-Circuit Protection (GATEN)

- Safety Timer Feature (TMR)

- Output Overvoltage Protection (OVI)

- Cycle-by-Cycle Overcurrent Limit

- Programmable EN/UVLO Threshold

- Status Output Monitoring Using Open-Drain Outputs (FLG1 and FLG2)

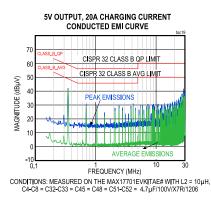

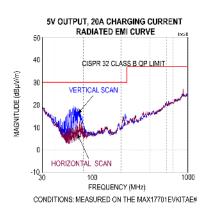

- Complies with CISPR 32 (EN55032) Class B Conducted and Radiated Emissions

- Overtemperature Protection

- Wide -40°C to +125°C Ambient Operating Temperature Range/ -40°C to +150°C Junction Temperature Range

#### **Simplified Application Circuit**

Ordering Information appears at end of data sheet.

19-100772; Rev 6; 6/22

#### **TABLE OF CONTENTS**

| General Description                                                          |    |

|------------------------------------------------------------------------------|----|

| Applications                                                                 |    |

| Benefits and Features                                                        |    |

| Simplified Application Circuit                                               |    |

| Absolute Maximum Ratings                                                     | 6  |

| Package Information                                                          | 6  |

| 24 PIN TQFN                                                                  | 6  |

| Electrical Characteristics                                                   | 6  |

| Typical Operating Characteristics                                            |    |

| Pin Configuration                                                            |    |

| MAX17701                                                                     |    |

| Pin Description                                                              |    |

| Functional Diagrams                                                          |    |

| MAX17701 Block Diagram                                                       |    |

| Detailed Description                                                         |    |

| Power-Up/-Down Sequence                                                      |    |

| Input Short-Circuit Protection (GATEN)                                       |    |

| Charger Operation                                                            | 21 |

| Charger Timers (TMR)                                                         |    |

| Charger Status Outputs (FLG1, FLG2)                                          |    |

| Hardware Faults                                                              | 23 |

| Linear Regulator (V <sub>CC</sub> and EXTVCC)                                | 23 |

| Reference Voltage (V <sub>REF</sub> )                                        | 23 |

| Setting the Switching Frequency and External Clock Synchronization (RT/SYNC) | 23 |

| Peak Current-Limit                                                           | 24 |

| Charging Current Monitoring (ISMON)                                          | 24 |

| Thermal-Shutdown Protection                                                  | 24 |

| Applications Information                                                     |    |

| Inductor Selection                                                           |    |

| Output Capacitor Selection                                                   |    |

| Input Capacitor Selection                                                    |    |

| Operating Input-Voltage Range                                                | 26 |

| CC Mode Charging Current Setting (ILIM)                                      | 27 |

| Setting the Input Undervoltage-Lockout Level (EN/UVLO)                       | 28 |

| Current Regulation Loop Compensation (COMP)                                  | 29 |

| Setting the Output Voltage and Voltage Regulation Loop (FB)                  |    |

| Output Overvoltage Protection (OVI)                                          |    |

| Bootstrap Capacitor Selection                                                |    |

| Bootstrap Diode Selection                                                    |    |

### 4.5V to 60V, Synchronous Step-Down Supercapacitor Charger Controller

# TABLE OF CONTENTS (CONTINUED)Input Short-Circuit Protection External nMOSFET Selection31Step-Down Converter nMOSFET Selection31Device Power Dissipation32PCB Layout Guidelines32Typical Application Circuit3320A Supercapacitor Charger33Ordering Information35

# 4.5V to 60V, Synchronous Step-Down Supercapacitor Charger Controller

#### LIST OF FIGURES

| LIST OF FIGURES                                                      |    |

|----------------------------------------------------------------------|----|

| Figure 1. Average Current Mode Control Loop                          |    |

| Figure 2. Charger Power-Up/-Down Sequence                            | 19 |

| Figure 3. Input Short-Circuit Protection and Recovery Timing Diagram | 20 |

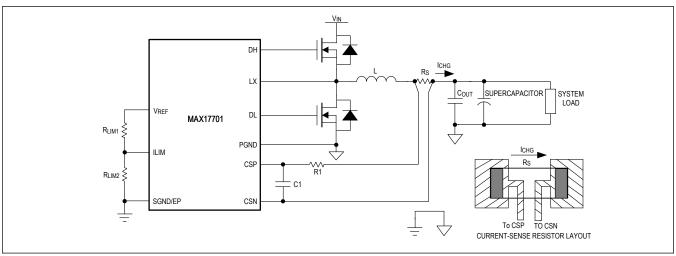

| Figure 4. Current-Sense Circuit                                      | 28 |

| Figure 5. Setting Input-Undervoltage Lockout                         | 28 |

| Figure 6. Setting the Supercapacitor Overvoltage Level               | 30 |

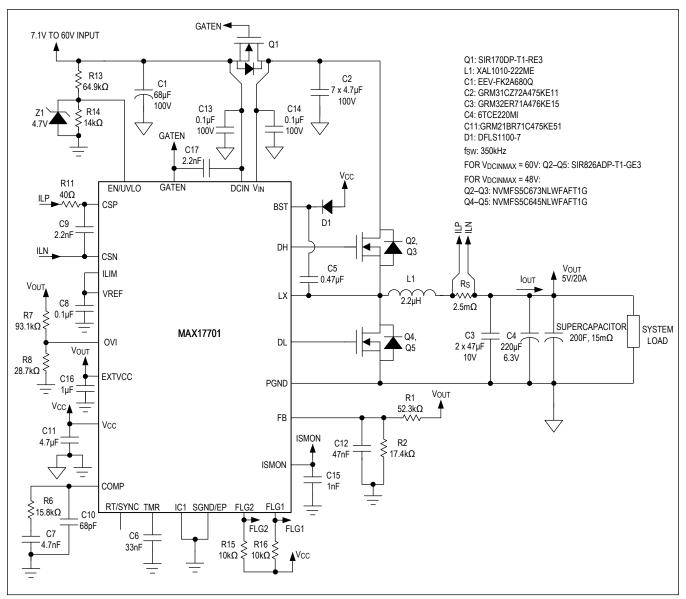

| Figure 7. 5V/20A Supercapacitor Charger                              | 33 |

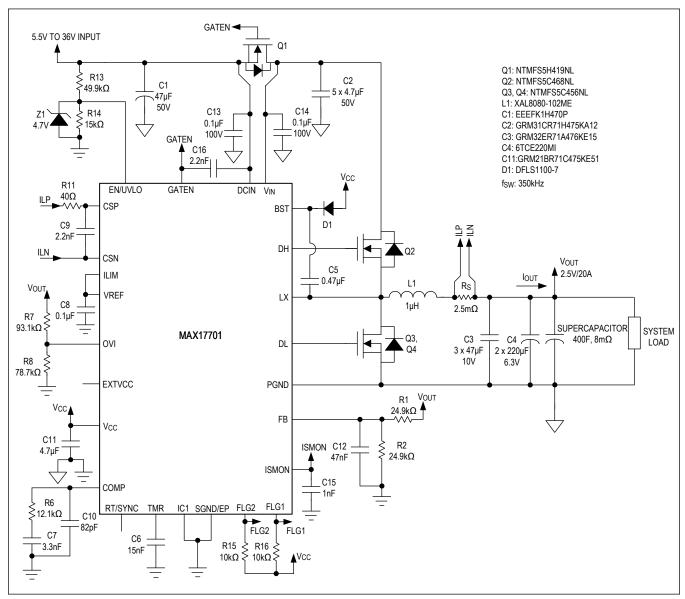

| Figure 8. 2.5V/20A Supercapacitor Charger                            | 34 |

# 4.5V to 60V, Synchronous Step-Down Supercapacitor Charger Controller

| LIST OF TABLES                          |    |

|-----------------------------------------|----|

| Fable 1. Status Output Indications      | 22 |

| Fable 2. Protection Under System Faults | 23 |

#### **Absolute Maximum Ratings**

| V <sub>IN</sub> to SGND/EP0.3V to +65V                             |

|--------------------------------------------------------------------|

| DCIN to SGND/EP0.3V to min(+65V, V <sub>IN</sub> + 0.6V)           |

| GATEN to SGND/EP max(-0.3V, DCIN - 0.3V) to (DCIN + 6V)            |

| GATEN to DCIN0.3V to +6V                                           |

| V <sub>CC</sub> to SGND/EP0.3V to min(+6V, V <sub>IN</sub> + 0.3V) |

| CSN, CSP to SGND/EP0.3V to (V <sub>IN</sub> + 0.6V)                |

| CSP to CSN0.3V to +0.3V                                            |

| $V_{REF}$ , TMR, ILIM to SGND/EP0.3V to ( $V_{CC}$ + 0.3V)         |

| COMP, ISMON, RT/SYNC to SGND/EP0.3V to (V <sub>CC</sub> + 0.3V)    |

| OVI, FB to SGND/EP0.3V to +6V                                      |

| FLG1, FLG2, EN/UVLO to SGND/EP0.3V to +6V                          |

| LX to PGND0.3V to +65V                                             |

| BST to LX0.3V to +6V                                               |

| BST to PGND                          | 0.3V to +70V                     |

|--------------------------------------|----------------------------------|

| DL to PGND                           | 0.3V to (V <sub>CC</sub> + 0.3V) |

| DH to LX                             | 0.3V to (BST + 0.3V)             |

| EXTVCC to SGND/EP                    | 0.3V to +26V                     |

| PGND, IC1 to SGND/EP                 | 0.3V to +0.3V                    |

| Continuous Power Dissipation (TA =   |                                  |

| 27.85mW/°C above +70°C))             | 2222mW                           |

| Operating Temperature Range (Note 1) | )40°C to +125°C                  |

| Junction Temperature                 | +150°C                           |

| Storage Temperature Range            |                                  |

| Lead Temperature (soldering, 10s)    | +300°C                           |

| Soldering Temperature (reflow)       | +260°C                           |

**Note 1:** Junction temperature greater than +125°C degrades operating lifetimes.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Information**

#### 24 PIN TQFN

| Package Code                           | T2444+5C         |  |  |  |

|----------------------------------------|------------------|--|--|--|

| Outline Number                         | <u>21-100405</u> |  |  |  |

| Land Pattern Number                    | <u>90-100139</u> |  |  |  |

| Thermal Resistance, Four-Layer Board:  |                  |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 36°C/W           |  |  |  |

| Junction to Case $(\theta_{JC})$       | 3°C/W            |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{IN} = V_{DCIN} = 24V, C_{VIN} = 4.7\mu\text{F}, C_{DCIN} = 100n\text{F}, C_{VCC} = 4.7\mu\text{F}, C_{VREF} = 100n\text{F}, C_{BST} = 470n\text{F}, V_{EXTVCC} = V_{SGND/EP} = V_{PGND} = V_{FB} = V_{OVI} = V_{IC1} = 0V, V_{EN/UVLO} = V_{LX} = V_{TMR} = V_{ILIM} = V_{CSN} = V_{CSP} = 2.5V, V_{BST} \text{ to } V_{LX} = 5V, RT/SYNC = DH = DL = GATEN = COMP = FLG1 = FLG2 = ISMON = Unconnected, T_A= -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted.}$  Typical values are at  $T_{A}$  = +25°C. All voltages are referenced to SGND/EP, unless otherwise noted.) (Note 2)

| PARAMETER                     | SYMBOL             | CONDITIONS                                                           | MIN | TYP | MAX | UNITS |  |

|-------------------------------|--------------------|----------------------------------------------------------------------|-----|-----|-----|-------|--|

| POWER SUPPLY                  |                    |                                                                      |     |     |     |       |  |

| DCIN Voltage Range            |                    | DCIN connected to V <sub>IN</sub> , External nMOSFET not used        |     |     | 60  | V     |  |

|                               |                    | External nMOSFET used                                                | 5.5 |     | 60  |       |  |

| V <sub>IN</sub> Voltage Range |                    |                                                                      | 4.5 |     | 60  | V     |  |

| Input Quiescent Current       | I <sub>QNS</sub>   | (V <sub>IN</sub> - V <sub>CSN</sub> ) > 2.1V, V <sub>FB</sub> = 1.5V | 1.4 | 2.1 | 2.8 | mA    |  |

| Input Switching Current       | I <sub>QS</sub>    |                                                                      | 1.7 | 2.5 | 3.5 | mA    |  |

| Shutdown Supply<br>Current    | I <sub>IN-SH</sub> | V <sub>EN/UVLO</sub> = 0V (Shutdown mode)                            |     | 7   | 18  | μA    |  |

#### **Electrical Characteristics (continued)**

$(V_{IN} = V_{DCIN} = 24V, C_{VIN} = 4.7 \mu F, C_{DCIN} = 100 nF, C_{VCC} = 4.7 \mu F, C_{VREF} = 100 nF, C_{BST} = 470 nF, V_{EXTVCC} = V_{SGND/EP} = V_{PGND} = V_{PS} = V_{OVI} = V_{IC1} = 0V, V_{EN/UVLO} = V_{LX} = V_{TMR} = V_{ILIM} = V_{CSN} = V_{CSP} = 2.5 V, V_{BST} \text{ to } V_{LX} = 5 V, RT/SYNC = DH = DL = GATEN = COMP = FLG1 = FLG2 = ISMON = Unconnected, T_A = -40°C to +125°C, unless otherwise noted. Typical values are at T_A = +25°C. All voltages are referenced to SGND/EP, unless otherwise noted.) (Note 2)$

| PARAMETER                               | SYMBOL               | CONDITIONS                                                                                          | MIN                      | TYP    | MAX                      | UNITS |  |

|-----------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------|--------------------------|--------|--------------------------|-------|--|

| ENABLE/UVLO (EN/UVLO)                   |                      |                                                                                                     |                          |        |                          |       |  |

| EN/UVLO Rising<br>Threshold             | V <sub>EN_TH_R</sub> | V <sub>EN/UVLO</sub> rising                                                                         | 1.22                     | 1.25   | 1.27                     | V     |  |

| EN/UVLO Falling<br>Threshold            | V <sub>EN_TH_F</sub> |                                                                                                     | 1.07                     | 1.09   | 1.11                     | V     |  |

| EN/UVLO Bias Current                    | I <sub>EN-BIAS</sub> | V <sub>EN/UVLO</sub> = 0.5V                                                                         | 1.4                      | 3.0    | 6.5                      | μA    |  |

| EN/UVLO True                            | V <sub>ENT</sub>     | V <sub>EN/UVLO</sub> rising                                                                         | 0.4                      | 0.7    | 1.1                      | V     |  |

| Shutdown Threshold                      | VENI                 | Hysteresis                                                                                          |                          | 60     |                          | mV    |  |

| V <sub>CC</sub> REGULATORS (INT         | -LDO AND EXT         | -LDO)                                                                                               |                          |        |                          |       |  |

|                                         |                      | 6V < V <sub>IN</sub> < 60V, I <sub>VCC</sub> = 1mA (V <sub>CC</sub> supplied from INT-LDO)          | 5.00                     | 5.15   | 5.30                     |       |  |

| V <sub>CC</sub> Output Voltage          | V <sub>CC</sub>      | $V_{IN}$ = 24V, $I_{VCC}$ = 0mA to 75mA, ( $V_{CC}$ supplied from INT-LDO)                          | 4.95                     | 5.10   | 5.25                     | V     |  |

| VCC Output Voltage                      | <b>v</b> CC          | 6V < V <sub>EXTVCC</sub> < 24V, I <sub>VCC</sub> = 1mA (V <sub>CC</sub> supplied from EXT-LDO)      | 5.00                     | 5.15   | 5.30                     | V     |  |

|                                         |                      | V <sub>EXTVCC</sub> = 12V, I <sub>VCC</sub> = 0mA to 75 mA, (V <sub>CC</sub> supplied from EXT-LDO) | 4.95                     | 5.10   | 5.25                     |       |  |

| V <sub>CC</sub> Output Current<br>Limit |                      | $V_{IN}$ = 8.5V, $V_{CC}$ = 4V ( $V_{CC}$ supplied from INT-LDO)                                    | 80                       | 110    | 135                      | mA    |  |

|                                         | IVCC_LIMIT           | V <sub>EXTVCC</sub> = 8.5V, V <sub>CC</sub> = 4V (V <sub>CC</sub> supplied from EXT-LDO)            | 80                       | 110    | 135                      |       |  |

| V <sub>CC</sub> Dropout Voltage         | .,                   | V <sub>IN</sub> = 4.5V, I <sub>VCC</sub> = 75mA (V <sub>CC</sub> supplied from IN-LDO)              |                          | 370    | 750                      |       |  |

|                                         | V <sub>CC-DO</sub>   | V <sub>EXTVCC</sub> = 4.9V, I <sub>VCC</sub> = 75mA (V <sub>CC</sub> supplied from EXT-LDO)         |                          | 185    | 350                      | mV    |  |

| V <sub>CC</sub> Undervoltage            | V <sub>CC-UVR</sub>  | V <sub>CC</sub> rising                                                                              | 4.14                     | 4.20   | 4.26                     | .,,   |  |

| Threshold                               | V <sub>CC-UVF</sub>  | V <sub>CC</sub> falling                                                                             | 3.74                     | 3.80   | 3.86                     | V     |  |

| EXTVCC Voltage Range                    |                      |                                                                                                     | 4.8                      |        | 24.0                     | V     |  |

| EXTVCC Switchover                       |                      | V <sub>EXTVCC</sub> rising                                                                          | 4.63                     | 4.70   | 4.77                     | V     |  |

| Voltage                                 |                      | Hysteresis                                                                                          |                          | 0.24   |                          | V     |  |

| OSCILLATOR (RT/SYNC                     | )                    |                                                                                                     |                          |        |                          |       |  |

|                                         |                      | $R_{RT/SYNC} = 350 \text{ k}\Omega$                                                                 | 118.75                   | 125.00 | 131.25                   |       |  |

| Switching Frequency                     | f <sub>SW</sub>      | R <sub>RT/SYNC</sub> = Unconnected 332                                                              | 332.5                    | 350.0  | 367.5                    | kHz   |  |

| Switching Frequency                     | 1200                 | $R_{RT/SYNC} = 110k\Omega$                                                                          | 380                      | 400    | 420                      | KHZ   |  |

|                                         |                      | $R_{RT/SYNC} = 19k\Omega$                                                                           | 2090                     | 2200   | 2310                     |       |  |

| Synchronization<br>Frequency Range      | fSYNC                |                                                                                                     | 0.9 x<br>f <sub>SW</sub> |        | 1.1 x<br>f <sub>SW</sub> | kHz   |  |

| External Clock<br>Amplitude             |                      | C <sub>COUPLING</sub> = 10pF                                                                        | 3                        |        |                          | V     |  |

| SYNC High Pulse-Width                   |                      |                                                                                                     | 100                      |        |                          | ns    |  |

| SYNC Low Pulse-Width                    |                      |                                                                                                     | 100                      |        |                          | ns    |  |

#### **Electrical Characteristics (continued)**

$(V_{IN} = V_{DCIN} = 24V, C_{VIN} = 4.7 \mu F, C_{DCIN} = 100 nF, C_{VCC} = 4.7 \mu F, C_{VREF} = 100 nF, C_{BST} = 470 nF, V_{EXTVCC} = V_{SGND/EP} = V_{PGND} = V_{PS} = V_{OVI} = V_{IC1} = 0V, V_{EN/UVLO} = V_{LX} = V_{TMR} = V_{ILIM} = V_{CSN} = V_{CSP} = 2.5 V, V_{BST} \text{ to } V_{LX} = 5 V, RT/SYNC = DH = DL = GATEN = COMP = FLG1 = FLG2 = ISMON = Unconnected, T_A = -40°C to +125°C, unless otherwise noted. Typical values are at T_A = +25°C. All voltages are referenced to SGND/EP, unless otherwise noted.) (Note 2)$

| PARAMETER                               | SYMBOL               | CONDITIONS                                                                       | MIN   | TYP   | MAX                   | UNITS |  |

|-----------------------------------------|----------------------|----------------------------------------------------------------------------------|-------|-------|-----------------------|-------|--|

| SYNC Input-Leakage<br>Current           | ISYNC_LKG            | V <sub>RT/SYNC</sub> = 2.5V, T <sub>A</sub> = +25°C -100 +100                    |       | +100  | nA                    |       |  |

| GATE DRIVER                             | •                    |                                                                                  |       |       |                       |       |  |

| DH to BST On-<br>Resistance             |                      | Source 100mA                                                                     | 0.8   | 1.2   | 2.1                   | Ω     |  |

| DH to LX On-Resistance                  |                      | Sink 100mA                                                                       | 0.3   | 0.6   | 1.0                   | Ω     |  |

| DL to V <sub>CC</sub> On-<br>Resistance |                      | Source 100mA                                                                     | 0.8   | 1.2   | 2.1                   | Ω     |  |

| DL to PGND On-<br>Resistance            |                      | Sink 100mA                                                                       | 0.3   | 0.6   | 1.0                   | Ω     |  |

| DH Minimum Controlled<br>On Time        | tmin_on_dh           |                                                                                  | 60    | 80    | 100                   | ns    |  |

| DL Minimum<br>Guaranteed On Time        | tmin_on_dl           |                                                                                  | 60    | 80    | 100                   | ns    |  |

| Dead Time                               | t <sub>DT_HL</sub>   | DH falling to DL rising, C <sub>DH-LX</sub> = 6nF,<br>C <sub>DL-PGND</sub> = 6nF |       | 30    |                       | - ns  |  |

|                                         | t <sub>DT_LH</sub>   | DL falling to DH rising, C <sub>DH-LX</sub> = 6nF,<br>C <sub>DL-PGND</sub> = 6nF |       | 30    |                       |       |  |

| DH Transition Time                      | tHR                  | DH rising, C <sub>DH-LX</sub> = 6nF                                              |       | 25    |                       | ns    |  |

| t <sub>HF</sub>                         |                      | DH falling, C <sub>DH-LX</sub> = 6nF                                             |       | 11    |                       | 115   |  |

| DL Transition Time                      | t <sub>LR</sub>      | DL rising, C <sub>DL-PGND</sub> = 6nF                                            |       | 25    |                       | ns    |  |

| DE Hansilion Time                       | t <sub>LF</sub>      | DL falling, C <sub>DL-PGND</sub> = 6nF                                           | 11    |       | lis                   |       |  |

| REFERENCE VOLTAGE                       | (VREF)               |                                                                                  |       |       |                       |       |  |

| V <sub>REF</sub> Output Voltage         | V <sub>REF</sub>     | I <sub>VREF</sub> = 0 to 1mA                                                     | 2.465 | 2.500 | 2.535                 | V     |  |

| Reference Current Limit                 | I <sub>REF_LIM</sub> | V <sub>REF</sub> = 2.45V                                                         | 1.2   | 1.8   | 2.7                   | mA    |  |

| CURRENT SENSE (CSP,                     | CSN, ILIM)           |                                                                                  |       |       |                       |       |  |

| CSP, CSN Common<br>Mode Voltage Range   |                      |                                                                                  | 0     |       | (V <sub>IN</sub> - 2) | V     |  |

| CSP to CSN Input<br>Operating Voltage   | V <sub>DIFF_CS</sub> | V <sub>DIFF_CS</sub> = (V <sub>CSP</sub> - V <sub>CSN</sub> )                    | -10   |       | +100                  | mV    |  |

|                                         |                      | V <sub>ILIM</sub> = 1.5V                                                         | 48    | 50    | 52                    |       |  |

| CSP to CSN Regulation                   | V                    | V <sub>ILIM</sub> = 0.75V                                                        | 23    | 25    | 27                    | mV    |  |

| Voltage Accuracy                        | V <sub>CSREG</sub>   | V <sub>ILIM</sub> = 0.15V                                                        | 3     | 5     | 7                     |       |  |

|                                         |                      | V <sub>ILIM</sub> = V <sub>REF</sub>                                             | 48    | 50    | 52                    |       |  |

| CSP Pin Current                         |                      | CSP source                                                                       |       | 200   | 1400                  | nA    |  |

#### **Electrical Characteristics (continued)**

$(V_{IN} = V_{DCIN} = 24V, C_{VIN} = 4.7 \mu F, C_{DCIN} = 100 nF, C_{VCC} = 4.7 \mu F, C_{VREF} = 100 nF, C_{BST} = 470 nF, V_{EXTVCC} = V_{SGND/EP} = V_{PGND} = V_{PS} = V_{OVI} = V_{IC1} = 0V, V_{EN/UVLO} = V_{LX} = V_{TMR} = V_{ILIM} = V_{CSN} = V_{CSP} = 2.5 V, V_{BST} \text{ to } V_{LX} = 5 V, RT/SYNC = DH = DL = GATEN = COMP = FLG1 = FLG2 = ISMON = Unconnected, T_A = -40°C to +125°C, unless otherwise noted. Typical values are at T_A = +25°C. All voltages are referenced to SGND/EP, unless otherwise noted.) (Note 2)$

| PARAMETER                                             | SYMBOL                                       | COND                                                            | ITIONS                                                                | MIN   | TYP   | MAX   | UNITS |

|-------------------------------------------------------|----------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------|-------|-------|-------|-------|

|                                                       |                                              | V <sub>EN/UVLO</sub> = 0V, CS                                   | N sink                                                                |       | 1.3   | 2.3   |       |

| CSN Pin Current                                       |                                              | Charger on, V <sub>ILIM</sub> = 0.15V to 1.5V                   | I <sub>CHG</sub> > I <sub>CHGMAX</sub> /10, CSN source                | 250   | 400   | 550   | μΑ    |

|                                                       |                                              | (see Note 3)                                                    | I <sub>CHG</sub> <<br>I <sub>CHGMAX</sub> /10, CSN<br>sink            | 470   | 700   | 1000  |       |

| Current Loop Error<br>Amplifier<br>Transconductance   | 9mi                                          | $(V_{CSP} - V_{CSN}) = V_{CSN}$                                 | SNEG ±25mV                                                            | 275   | 480   | 685   | μS    |

| ILIM Input-Leakage<br>Current                         |                                              | V <sub>ILIM</sub> = 1.5V, T <sub>A</sub> = +                    | 25°C                                                                  | -100  |       | +100  | nA    |

| CSN Undervoltage-                                     | V                                            | (V <sub>IN</sub> - V <sub>CSN</sub> ), rising                   |                                                                       | 1.97  | 2.04  | 2.10  | V     |

| Lockout Threshold                                     | V <sub>CMUVLO</sub>                          | (V <sub>IN</sub> - V <sub>CSN</sub> ), falling                  |                                                                       | 1.88  | 1.95  | 2.02  | ] V   |

| Overcurrent Threshold                                 | Vaannus                                      | V <sub>CSPEAK</sub> = (V <sub>CSP</sub> -                       | V <sub>CSN</sub> ), V <sub>ILIM</sub> = 1.5V                          | 70    | 75    | 80    | mV    |

| Overcurrent Threshold                                 | V <sub>CSPEAK</sub>                          | Hysteresis                                                      |                                                                       |       | 10    |       | IIIV  |

| Zero Cross Threshold                                  | $V_{ZX}$                                     | (V <sub>CSP</sub> - V <sub>CSN</sub> ) falling                  | 9                                                                     | 3     | 4.5   | 6     | mV    |

| PWM Ramp Amplitude                                    | $V_{RAMP}$                                   | f <sub>SW</sub> = 125kHz to 2.2                                 | MHz                                                                   | 1.37  | 1.44  | 1.51  | V     |

| VOLTAGE REGULATION                                    | AMPLIFIER (F                                 | В)                                                              |                                                                       |       |       |       |       |

| FB Reference Voltage                                  | $V_{FB\_REG}$                                |                                                                 |                                                                       | 1.237 | 1.250 | 1.263 | V     |

| FB Input-Leakage<br>Current                           |                                              | V <sub>FB</sub> = 1.3V, T <sub>A</sub> = +2                     | V <sub>FB</sub> = 1.3V, T <sub>A</sub> = +25°C                        |       |       | +100  | nA    |

| Voltage Loop Error<br>Amplifier Gain                  | $G_V$                                        |                                                                 |                                                                       | 1.15  | 1.30  | 1.42  | mV/mV |

| INPUT SHORT-CIRCUIT                                   | PROTECTION (                                 | GATEN)                                                          |                                                                       |       |       |       |       |

| External nMOSFET<br>Gate Drive Voltage                | (V <sub>GATEN</sub> -<br>V <sub>DCIN</sub> ) |                                                                 |                                                                       | 4.65  | 5.0   | 5.5   | V     |

| GATEN Drive Current                                   | I <sub>GATEN</sub>                           |                                                                 |                                                                       | 17    | 20    | 23    | μA    |

| GATEN Active Pulldown Resistance                      | R <sub>GATEN_</sub> A                        | I <sub>GATEN</sub> = 100mA                                      |                                                                       |       | 1.1   | 2.1   | Ω     |

| GATEN Passive<br>Pulldown Resistance                  | R <sub>GATEN_P</sub>                         | V <sub>EN/UVLO</sub> = 0V                                       |                                                                       |       | 400   | 800   | Ω     |

| GATEN-DCIN Threshold                                  | V <sub>GATEN_OK</sub>                        |                                                                 |                                                                       | 3.20  | 3.55  | 3.90  | V     |

| GATEN OK Delay                                        | t <sub>GATEN_OK</sub>                        |                                                                 |                                                                       |       | 15    |       | ms    |

| External nMOSFET                                      |                                              | (V <sub>DCIN</sub> - V <sub>IN</sub> ) falling                  |                                                                       | -111  | -93   | -75   |       |

| Reverse-Blocking<br>Threshold                         | V <sub>REV</sub>                             | Hysteresis                                                      |                                                                       |       | 20    |       | mV    |

| External nMOSFET<br>Reverse-Blocking<br>Response Time |                                              | C <sub>GATEN-DCIN</sub> = 10n<br>93mV) to (V <sub>GATEN</sub> - | F, V <sub>DCIN</sub> < (V <sub>IN</sub> -<br>V <sub>DCIN</sub> ) < 2V |       | 100   | 180   | ns    |

| V <sub>IN</sub> to DCIN Reverse                       |                                              | V <sub>DCIN</sub> = 0V, V <sub>IN</sub> =                       | V <sub>EN/UVLO</sub> = 0V                                             |       | 170   | 260   | μΑ    |

| Leakage Current                                       |                                              | 60V                                                             |                                                                       |       | 230   | 350   |       |

#### **Electrical Characteristics (continued)**

$(V_{IN} = V_{DCIN} = 24V, C_{VIN} = 4.7 \mu F, C_{DCIN} = 100 nF, C_{VCC} = 4.7 \mu F, C_{VREF} = 100 nF, C_{BST} = 470 nF, V_{EXTVCC} = V_{SGND/EP} = V_{PGND} = V_{FB} = V_{OVI} = V_{IC1} = 0V, V_{EN/UVLO} = V_{LX} = V_{TMR} = V_{ILIM} = V_{CSN} = V_{CSP} = 2.5V, V_{BST} \text{ to } V_{LX} = 5V, RT/SYNC = DH = DL = GATEN = COMP = FLG1 = FLG2 = ISMON = Unconnected, T_A = -40°C to +125°C, unless otherwise noted. Typical values are at T_A = +25°C. All voltages are referenced to SGND/EP, unless otherwise noted.) (Note 2)$

| PARAMETER                             | SYMBOL                | CONDITIONS                                                           | MIN   | TYP    | MAX   | UNITS               |  |

|---------------------------------------|-----------------------|----------------------------------------------------------------------|-------|--------|-------|---------------------|--|

| CHARGER FUNCTIONS                     |                       |                                                                      |       |        |       |                     |  |

| Constant Voltage (CV)                 | V                     | V <sub>ILIM</sub> = 1.5V, V <sub>FB</sub> rising                     | 97.15 | 97.50  | 97.85 | % of                |  |

| Mode FB Threshold                     | V <sub>FB_CV</sub>    | Hysteresis                                                           |       | 0.3    |       | V <sub>FB_REG</sub> |  |

| Overvoltage Comparator                | Vo. # 711             | V <sub>OVI</sub> rising                                              | 1.245 | 1.260  | 1.275 | V                   |  |

| Threshold (OVI)                       | V <sub>OVI_TH</sub>   | V <sub>OVI</sub> falling                                             | 1.235 | 1.250  | 1.265 | V                   |  |

| ISMON Output-Voltage                  |                       | $(V_{CSP} - V_{CSN}) = 50 \text{mV}$                                 | 1.41  | 1.50   | 1.59  | V                   |  |

| Accuracy                              |                       | $(V_{CSP} - V_{CSN}) = 10 \text{mV}$                                 | 0.21  | 0.30   | 0.39  | V                   |  |

| ISMON Output<br>Resistance            |                       |                                                                      |       | 90     |       | kΩ                  |  |

| ISMON Output<br>Bandwidth             |                       |                                                                      |       | 100    |       | kHz                 |  |

| CHARGER TIMER (TMR)                   |                       |                                                                      |       |        |       |                     |  |

| Charger Startup Delay                 | t                     | C <sub>TMR</sub> = 33nF, TMR enabled                                 |       | 27     |       | ms                  |  |

| Charger Startup Delay                 | t <sub>CH_START</sub> | TMR disabled                                                         |       | 26     |       | 1115                |  |

| TMR Oscillator Upper Threshold        | V <sub>TMR_H</sub>    |                                                                      | 1.47  | 1.50   | 1.53  | V                   |  |

| TMR Oscillator Lower Threshold        | V <sub>TMR_L</sub>    |                                                                      | 0.94  | 0.96   | 0.98  | V                   |  |

| TMR Source/Sink<br>Current            | I <sub>TMR</sub>      |                                                                      | 8.9   | 10     | 10.9  | μA                  |  |

| TMR Disable Threshold                 | V <sub>TMR_DIS</sub>  | V <sub>TMR</sub> > V <sub>TMR_DIS</sub> (powerup check only)         | 1.9   | 2.0    | 2.1   | V                   |  |

| TMR Short to SGND/EP Fault Threshold  | V <sub>TMR_GND</sub>  | V <sub>TMR</sub> < V <sub>TMR_GND</sub> (powerup check only)         | 80    | 100    | 120   | mV                  |  |

| Constant Current (CC)<br>Mode Timeout | <sup>t</sup> FCHG     |                                                                      |       | 32767  |       | TMR<br>CYCLES       |  |

| TMR Fault Blanking<br>Timeout         | tBLANK_OFF            |                                                                      |       | 131071 |       | TMR<br>CYCLES       |  |

| CHARGER STATUS OUT                    | PUTS (FLG1, F         | LG2)                                                                 |       |        |       | •                   |  |

| FLG1/FLG2 Pulldown<br>Voltage         |                       | I <sub>FLG1</sub> , I <sub>FLG2</sub> = 10mA                         |       |        | 500   | mV                  |  |

| FLG1/FLG2 Leakage<br>Current          |                       | V <sub>FLG1</sub> , V <sub>FLG2</sub> = 5.5V, T <sub>A</sub> = +25°C | -100  |        | +100  | nA                  |  |

| IC THERMAL PROTECTI                   | ON                    |                                                                      |       |        |       |                     |  |

| Thermal Shutdown                      |                       | Temperature rising                                                   |       | 160    |       | °C                  |  |

| Threshold                             |                       | Hysteresis                                                           |       | 10     |       |                     |  |

**Note 2:** Electrical specifications are production tested at T<sub>A</sub> = +25°C. Specifications over the entire operating temperature range are guaranteed by design and characterization.

Note 3: CC mode charging current setting is calculated using this equation:

$$I_{\text{CHGMAX}} = \frac{V_{\text{CSREG}}}{R_{\text{S}}}$$

where R<sub>S</sub> is the current sense resistor.

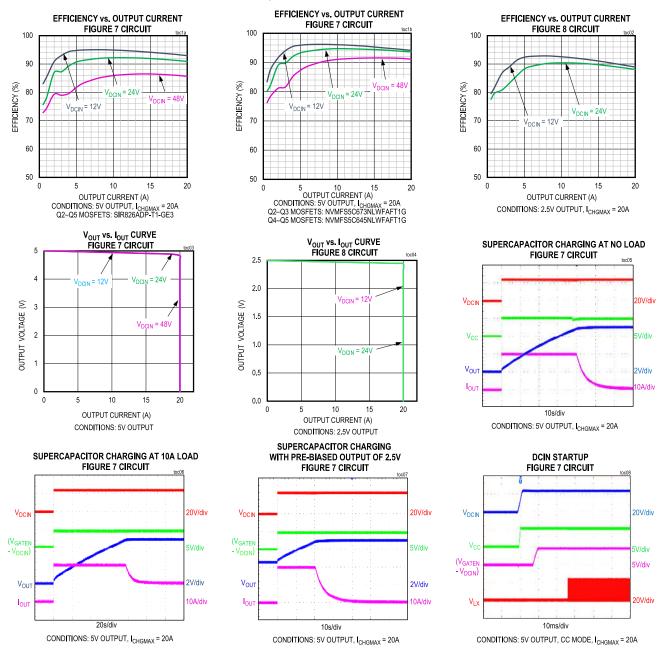

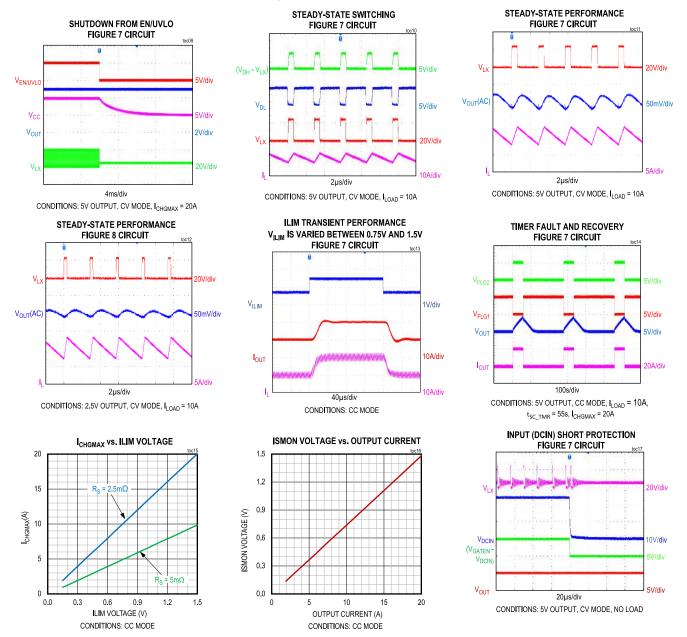

#### **Typical Operating Characteristics**

$(V_{DCIN} = 24V, V_{SGND/EP} = V_{PGND} = 0V, RT/SYNC = unconnected (f_{SW} = 350kHz), T_A = +25^{\circ}C$ , unless otherwise noted. All voltages are referenced to SGND/EP, unless otherwise noted.)

#### **Typical Operating Characteristics (continued)**

$(V_{DCIN} = 24V, V_{SGND/EP} = V_{PGND} = 0V, RT/SYNC = unconnected (f_{SW} = 350kHz), T_A = +25^{\circ}C$ , unless otherwise noted. All voltages are referenced to SGND/EP, unless otherwise noted.)

#### **Typical Operating Characteristics (continued)**

$(V_{DCIN} = 24V, V_{SGND/EP} = V_{PGND} = 0V, RT/SYNC = unconnected (f_{SW} = 350kHz), T_A = +25^{\circ}C$ , unless otherwise noted. All voltages are referenced to SGND/EP, unless otherwise noted.)

#### **Pin Configuration**

#### **MAX17701**

#### **Pin Description**

| PIN  | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                    |

|------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | PGND             | Power Ground. Connect to the return terminal of a V <sub>CC</sub> bypass capacitor placed close to IC, and the source terminal of external low-side nMOSFET. Refer to the MAX17701 EV kit data sheet for a PCB layout example.                                                                                                                              |

| 2    | V <sub>CC</sub>  | Internal LDO Output. Connect a minimum of $4.7\mu\text{F}/0805$ , low-ESR ceramic capacitor between V <sub>CC</sub> and PGND. V <sub>CC</sub> supports the IC internal control circuitry and gate drive current for external nMOSFETs.                                                                                                                      |

| 3    | EXTVCC           | External Power-Supply Input for EXT-LDO. To power internal circuitry from an external supply, apply a voltage between 4.8V and 24V to the EXTVCC pin. Connect a minimum of 1µF/0603, low-ESR ceramic capacitor between EXTVCC and SGND/EP. Leave EXTVCC open when not used.                                                                                 |

| 4    | CSP              | Inverting Input of the Current Loop Error Amplifier. The CSP and CSN pins measure the voltage across the current sense resistor R <sub>S</sub> (see Figure 4).                                                                                                                                                                                              |

| 5    | CSN              | Non-Inverting Input of the Current Loop Error Amplifier. Connect CSN to the node connecting the output capacitor and current sense resistor $R_S$ . Use Kelvin connections and route the CSP and CSN traces as a differential pair (see Figure 4).                                                                                                          |

| 6    | ISMON            | Output of Charging Current Monitor. Bypass ISMON with a 1nF low-ESR ceramic capacitor to SGND/EP. The voltage on this pin is 30 times the voltage drop across the current sense resistor R <sub>S</sub> .                                                                                                                                                   |

| 7, 8 | FLG2, FLG1       | Open-Drain Status Output Pins. Connect a $10k\Omega$ pullup resistor each from $V_{CC}$ to the FLG1 and FLG2 pins. See the <u>Charger Status Outputs (FLG1, FLG2)</u> section for more details.                                                                                                                                                             |

| 9    | FB               | Feedback Input. Connect FB to the center node of a resistor-divider from the positive terminal of supercapacitor to SGND/EP to set the output voltage. See the <u>Setting the Output Voltage and Voltage Regulation Loop (FB)</u> section for more details.                                                                                                 |

| 10   | СОМР             | Current Loop Error Amplifier Output. Connect a compensation network at this pin to stabilize the inner current loop. See the <i>Current Regulation Loop Compensation (COMP)</i> section for more details.                                                                                                                                                   |

| 11   | TMR              | Supercapacitor Safety Timer Setting Pin. A capacitor from TMR to SGND/EP sets the charging time in CC mode. Place the timer capacitor close to the TMR pin. Connect TMR to V <sub>REF</sub> to disable the timer function. See the <u>Charger Timers (TMR)</u> section for more details.                                                                    |

| 12   | RT/SYNC          | Switching Frequency Programming/Synchronization Input. Connect a resistor from RT/SYNC to SGND/EP to set the switching frequency between 125kHz to 2.2MHz. Leave RT/SYNC open for the default 350kHz frequency. See the <a href="Setting the Switching Frequency and External ClockSynchronization">Synchronization (RT/SYNC)</a> section for more details. |

| 13   | ILIM             | CC Mode Charging Current Programming Input. Connect ILIM to the center node of a resistor divider between V <sub>REF</sub> and SGND/EP to set the CC mode charging current. Connect to V <sub>REF</sub> for default CC mode charging current setting. See the <u>CC Mode Charging Current Setting (ILIM)</u> section for more details.                      |

| 14   | V <sub>REF</sub> | 2.5V Reference Output. Bypass $V_{REF}$ with a 0.1 $\mu$ F low-ESR ceramic capacitor to SGND/EP. See the <u>Reference Voltage (<math>V_{REF}</math>)</u> section for more details.                                                                                                                                                                          |

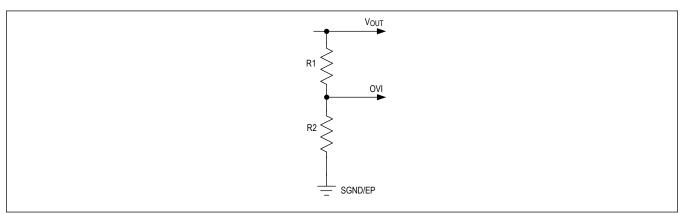

| 15   | OVI              | Overvoltage Detection Input. Connect OVI to the center node of a resistor divider from the output voltage node to SGND/EP. If $V_{OVI}$ exceeds $V_{OVI\_TH}$ , charging is stopped and the charger enters into the latched fault.                                                                                                                          |

| 16   | IC1              | Internal Connection. Connect to SGND/EP                                                                                                                                                                                                                                                                                                                     |

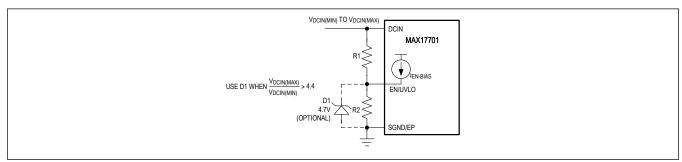

| 17   | EN/UVLO          | Enable/Undervoltage Lockout Input. Connect to the center node of a resistor divider between DCIN and SGND/EP to set the input voltage at which the device turns on. Connect to SGND/EP to shutdown the device. See the <u>Setting the Input Undervoltage-Lockout Level (EN/UVLO)</u> section for more details.                                              |

#### **Pin Description (continued)**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 18  | DCIN            | Input Supply Voltage Sense Pin. Bypass DCIN with a $0.1\mu F$ ceramic capacitor to PGND. The DCIN and $V_{IN}$ pins measure the voltage across external nMOSFET. Use Kelvin connections and route the $V_{IN}$ and DCIN traces as differential pair. Refer to the MAX17701 EV kit data sheet for the recommended PCB layout and routing. If input short-circuit protection feature is not used, connect DCIN to $V_{IN}$ close to IC. |  |

| 19  | GATEN           | Gate Drive Output for External nMOSFET. Bypass GATEN with a 2.2nF low-ESR ceramic capacitor to DCIN. GATEN controls the gate of an external nMOSFET connected between DCIN and V <sub>IN</sub> to prevent supercapacitor discharge when DCIN is shorted to PGND. See the <u>Input Short Circuit Protection (GATEN)</u> section for more details.                                                                                      |  |

| 20  | V <sub>IN</sub> | MAX17701 IC Supply Pin. Bypass V <sub>IN</sub> to PGND with a 0.1μF ceramic capacitor. Refer to the MAX17701 EV kit data sheet for the recommended PCB layout and routing.                                                                                                                                                                                                                                                            |  |

| 21  | DH              | High Side nMOSFET Gate Driver Output. Connect to the gate of a high-side nMOSFET.                                                                                                                                                                                                                                                                                                                                                     |  |

| 22  | LX              | Switching Node Connection Input. Connect to the switching node of the converter.                                                                                                                                                                                                                                                                                                                                                      |  |

| 23  | BST             | Bootstrap Capacitor Connection Input. Connect a 0.1µF (min) capacitor between the BST and LX pins. Connect a Schottky diode from V <sub>CC</sub> to the BST pin. See the <u>Bootstrap Capacitor Selection</u> and <u>Bootstrap Diode Selection</u> sections for more details.                                                                                                                                                         |  |

| 24  | DL              | Low-Side nMOSFET Gate Driver Output. Connect to the gate of a low-side nMOSFET.                                                                                                                                                                                                                                                                                                                                                       |  |

| _   | SGND/EP         | Signal Ground, Exposed Pad. Refer to the MAX17701 EV kit data sheet recommended method for the PCB layout, routing, and thermal vias.                                                                                                                                                                                                                                                                                                 |  |

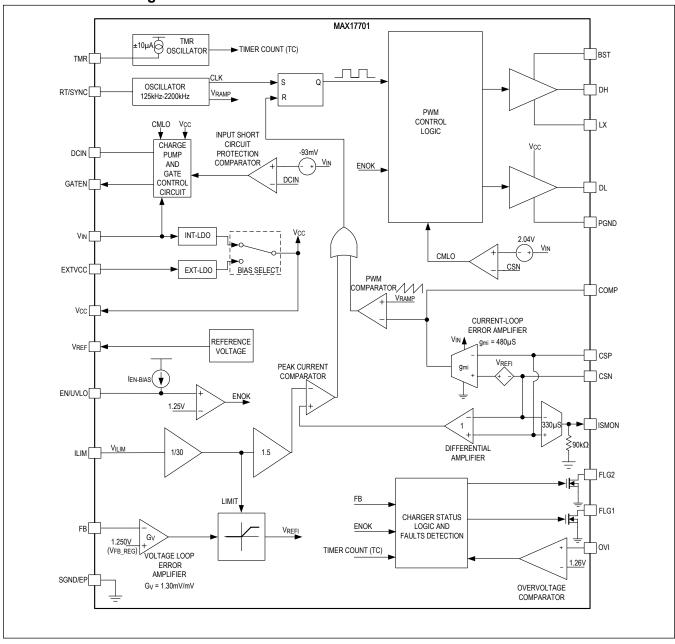

#### **Functional Diagrams**

#### MAX17701 Block Diagram

#### **Detailed Description**

The MAX17701 is a 4.5V to 60V, synchronous, step-down, supercapacitor charger controller designed to operate over a -40°C to +125°C temperature range. It charges a supercapacitor with constant charging current with up to ±4% accuracy. After the supercapacitor is charged, the device regulates the no load output voltage with ±1% accuracy. The MAX17701 supports a wide output-voltage range of 1.25V to (V<sub>DCIN</sub> - 2.1V).

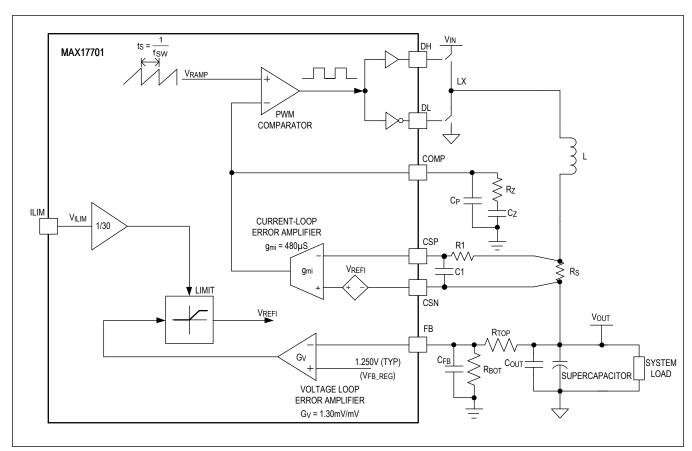

The MAX17701 features a constant frequency, average current-mode control architecture shown in Figure 1. An internal current loop consists of a transconductance amplifier  $g_{mi}$  that senses the inductor current flowing through current sense resistor  $R_S$  as a voltage drop across the CSP and CSN pins. The current sense voltage is compared with a current loop reference voltage ( $V_{REFI}$ ), which is set by the outer voltage loop error amplifier ( $G_V$ ) and limited by the voltage programmed at the ILIM pin ( $V_{ILIM}$ ). The voltage at the COMP pin is compared with a 1.44V (typ) ramp using a PWM comparator to set the duty cycle of the converter. The required compensation to stabilize the current loop is applied at the COMP pin using  $R_Z$ ,  $C_Z$ , and  $C_P$ . Under steady-state conditions, the inner current loop forces the voltage drop across  $R_S$  equal to  $V_{RFFI}$ .

The output voltage is monitored by the voltage error amplifier  $G_V$  with a resistor divider ( $R_{TOP}$ ,  $R_{BOT}$ ) connected across the positive and negative supercapacitor terminals with the center node connected to the FB pin. The voltage at the FB pin ( $V_{FB}$ ) is compared with the FB reference voltage ( $V_{FB\_REG}$ ). The voltage loop error amplifier sets the current loop

reference voltage (V<sub>REFI</sub>). V<sub>REFI</sub> is limited to

$$\frac{V_{\text{ILIM}}}{30}$$

until  $V_{\text{FB}} \le \left[V_{\text{FB\_REG}} - \frac{V_{\text{ILIM}}}{30 \times G_V}\right]$ . This results in a constant current

through R<sub>S</sub>. When the output voltage rises, such that  $V_{FB} > \left[V_{FB\_REG} - \frac{V_{ILIM}}{30 \times G_V}\right]$ ,  $V_{REFI}$ ; hence, the output load current

$(I_{LOAD})$  proportionately reduces. The steady-state FB regulation voltage, and consequently the output voltage depend on the load  $(I_{LOAD})$  connected across the supercapacitor, as given by the following equation:

$$V_{\text{OUT\_LOAD}} = \left[V_{\text{FB\_REG}} - \frac{I_{\text{LOAD}} \times R_{\text{S}}}{G_{V}}\right] \times \left[\frac{R_{\text{TOP}} + R_{\text{BOT}}}{R_{\text{BOT}}}\right]$$

where,

V<sub>FB</sub> <sub>REG</sub> = FB reference voltage

V<sub>OUT LOAD</sub> = Steady-state output voltage for a given load current

I<sub>I OAD</sub> = Output load current of the charger

R<sub>TOP</sub>, R<sub>BOT</sub> = Output voltage feedback voltage divider resistors

$G_V$  = Voltage loop error amplifier gain (1.30mV/mV)

The MAX17701 provides input short-circuit protection, and prevents supercapacitor discharging for input supply-side short-circuit events by means of an external nMOSFET. A safety timer (TMR) sets the maximum allowed CC mode charging time to improve system safety. The device features an uncommitted comparator, which can be used to detect an output overvoltage (OVI), which improves the safety of load circuitry, and prevents the supercapacitor from overcharging.

The switching frequency of the device can be programmed from 125kHz to 2.2 MHz using a resistor at the RT/SYNC pin. The RT/SYNC also provides an external clock synchronization feature. Input undervoltage lockout is implemented using the EN/UVLO pin. Two open-drain status outputs (FLG1 and FLG2) indicate the supercapacitor charger status. The system current can be monitored using the ISMON pin.

Figure 1. Average Current Mode Control Loop

#### Power-Up/-Down Sequence

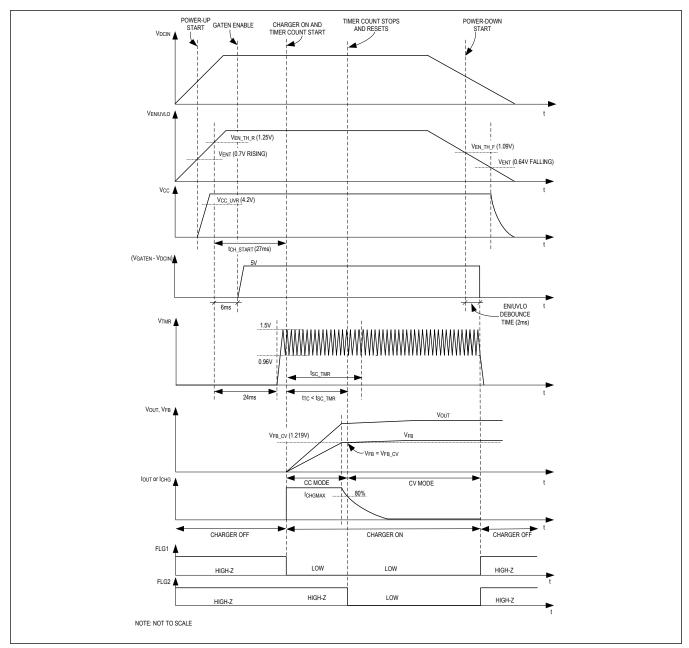

Figure 2 shows the MAX17701 power-up/-down sequence when DCIN voltage is applied/removed. When DCIN voltage reaches a level such that  $V_{EN/UVLO}$  is around 0.7V ( $V_{ENT}$ ) the INT-LDO regulator is enabled and  $V_{CC}$  rises. When  $V_{CC}$  rises above 4.2V ( $V_{CC-UVR}$ ) and  $V_{EN/UVLO}$  rises above 1.25V ( $V_{EN\_TH\_R}$ ), the MAX17701 initiates EN/UVLO debounce and checks for hardware faults. If there are no hardware faults (see the *Hardware Faults* section) detected at power-up, the MAX17701 enables internal blocks during charger startup delay time  $t_{CH\_START}$ . After this delay, the charger initiates LX switching and enters CC mode. In CC mode, the current is regulated at the CC mode charging current setting ( $t_{CHGMAX}$ ). The safety timer counts the charging time in CC mode and if the output voltage reaches constant voltage mode ( $t_{CHS}$ ) via visibility timer setting ( $t_{CLSTMR}$ ), the charger enters constant voltage (CV) mode and continues to operate.

When  $V_{EN/UVLO}$  falls below 1.09V ( $V_{EN\_TH\_F}$ ), the MAX17701 initiates a shutdown sequence with a debounce time of 2ms (typ). If the input voltage decreases such that ( $V_{IN}$  -  $V_{CSN}$ ) falls below the current loop error amplifier undervoltage lockout falling threshold 1.95V ( $V_{CMUVLO}$ ), the MAX17701 initiates a shutdown sequence immediately. The converter stops switching, and GATEN is pulled down with 1.1 $\Omega$  ( $R_{GATEN\_A}$ ) to DCIN to turn off the external nMOSFET. The COMP is pulled low after a debounce time of 100 $\mu$ s (typ).

If  $V_{EN/UVLO}$  falls below 0.64V ( $V_{ENT}$ ), the MAX17701 initiates a shutdown sequence with a debounce time of 10µs (typ). During this shutdown sequence, the MAX17701 pulls down the GATEN with 1.1 $\Omega$  ( $R_{GATEN\_A}$ ) to DCIN to turn off the external nMOSFET. See the <u>Setting the Input Undervoltage-Lockout Level (EN/UVLO)</u> section for more details.

Figure 2. Charger Power-Up/-Down Sequence

#### Input Short-Circuit Protection (GATEN)

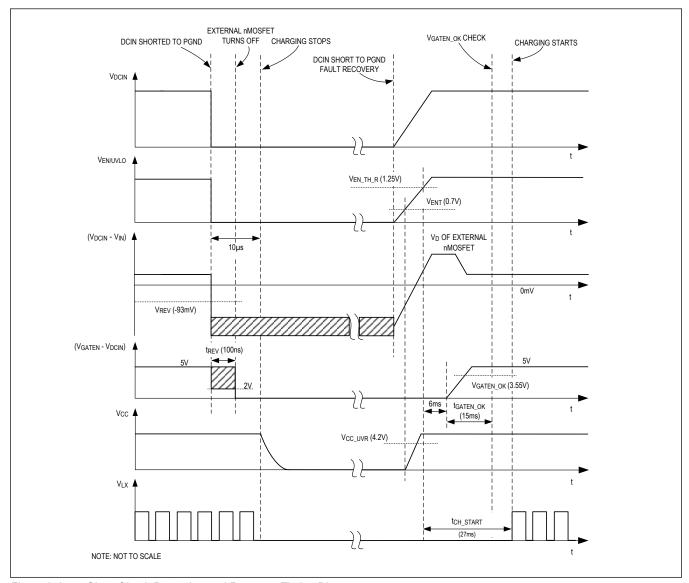

The MAX17701 provides gate drive output (GATEN) that drives a logic-level gate threshold external nMOSFET, which turns off and prevents supercapacitor discharging for input supply short-circuit events. The GATEN is pulled up with 20µA ( $I_{GATEN}$ ) when  $V_{IN}$  is 2.04V ( $V_{CMUVLO}$ ) above  $V_{CSN}$ . If  $V_{GATEN}$  does not reach 3.55V ( $V_{GATEN\_OK}$ ) within 15ms ( $I_{GATEN\_OK}$ ), MAX17701 enters latched hardware fault.

Figure 3 depicts the MAX17701 behavior when DCIN is shorted to PGND. When VDCIN is 93mV (VREV) below VIN,

GATEN is pulled down with  $1.1\Omega$  (R<sub>GATEN A</sub>) and the external nMOSFET is turned off within 100ns (typ). When V<sub>EN/UVLO</sub> goes below 0.64V (V<sub>ENT</sub>), the MAX17701 shuts down with 10 $\mu$ s (typ) debounce time. When DCIN-to-PGND short is removed, the power-up sequence is initiated (see the <u>Power-Up/Down Sequence</u> section).

Measure the differential voltage between the source and drain terminals of the input short-circuit protection external nMOSFET using a Kelvin connection. Shield DCIN,  $V_{\text{IN}}$  and GATEN signal traces using static ground plane on either side of the traces and on the adjacent layers of PCB. Place the 0.1µF decoupling capacitors on DCIN and  $V_{\text{IN}}$  pins close to MAX17701. The MAX17701 EV kit depicts the recommended layout and routing of DCIN,  $V_{\text{IN}}$  and GATEN traces.

When the input short-circuit protection is not used, connect a 2.2nF capacitor between GATEN and DCIN, and short DCIN to  $V_{\text{IN}}$ .

Figure 3. Input Short-Circuit Protection and Recovery Timing Diagram

### 4.5V to 60V, Synchronous Step-Down Supercapacitor Charger Controller

#### **Charger Operation**

MAX17701 offers constant current (CC) mode and constant voltage (CV) mode for charging a supercapacitor. In CC mode, the charging current is regulated to the CC mode charging current ( $I_{CHGMAX}$ ) proportional to  $V_{ILIM}$ . The safety timer starts counting when the device enters CC mode. When  $V_{FB}$  goes above 1.219V ( $V_{FB\_CV}$ ) within the CC mode timeout period ( $t_{SC\_TMR}$ ), the charger enters CV mode and the safety timer stops counting (see <u>Charger Timers (TMR)</u> section). The safety timer count resets when the device enters CV mode. In CV mode, the device continues to charge the supercapacitor until  $V_{FB}$  reaches 1.250V ( $V_{FB\_REG}$ ). The charger regulates  $V_{FB}$  at  $V_{FB\_REG}$  at no load. When  $V_{FB}$  drops below 1.215V ( $V_{FB\_CV}$ ), the charger exits CV mode, enters CC mode, and the timer count restarts.

#### **Charger Timers (TMR)**

The MAX17701 offers a programmable timer feature to provide additional safety to the supercapacitor and the connected load. Connect a capacitor from TMR to SGND/EP to enable the timer feature. Connect TMR to  $V_{REF}$  to disable the timer feature. The timer counts the charging time in CC mode. If  $V_{FB}$  does not reach 1.219V ( $V_{FB}$  CV) within CC mode timeout period ( $t_{SC}$  TMR), the charger turns off. The charger restarts after 4 times  $t_{SC}$  TMR. The MAX17701 supports 470pF to  $t_{SC}$  to  $t_{SC}$  TMR, translating into a CC mode timeout period range of 1.5 second to 9 hours.

The safety timer is programmed based on maximum supercapacitor value ( $C_{SUP}$ ), output voltage ( $V_{OUT}$ ), and CC mode charging current setting ( $I_{CHGMAX}$ ). Refer to the <u>CC Mode Charging Current Setting ( $I_{LIM}$ )</u> section.

Choose the required safety timer period using the following equation:

$$t_{\text{SC\_TMR}} \ge \frac{c_{\text{SUP}} \times v_{\text{OUT}}}{l_{\text{CHGMAX}} - l_{\text{LOAD}}}$$

where I<sub>LOAD</sub> is the system load during the supercapacitor charging period

Select  $I_{CHGMAX} \ge 1.5 \times I_{LOAD}$  to ensure the charger enters CV mode

Use the following equation to calculate  $C_{TMR}$  for the required  $t_{SC\ TMR}$ :

where

t<sub>SC TMR</sub> = Desired safety timer timeout setting in seconds

C<sub>TMR</sub> = TMR capacitor in Farad

t<sub>FCHG</sub> = Number of TMR cycles in CC mode (32767)

$V_{TMR}$  H = TMR oscillator upper threshold (1.5V)

V<sub>TMR I</sub> = TMR oscillator lower threshold (0.96V)

$I_{TMR} = TMR$  pin source/sink current (10µA)

#### **Charger Status Outputs (FLG1, FLG2)**

The MAX17701 features two open-drain status output pins (FLG1 and FLG2) to indicate the status of the charger. <u>Table</u> 1 shows the status flag summary.

**Table 1. Status Output Indications**

| CHARGER STATUS FLG (FLG2 and FLG1) | FLG2 FLG1                          |                                    | CHARGER STATUS                            |  |

|------------------------------------|------------------------------------|------------------------------------|-------------------------------------------|--|

| 11                                 | Open drain in Hi-<br>Impedance (1) | Open drain in Hi-<br>Impedance (1) | Charger Off                               |  |

| 10                                 | Open drain in Hi-<br>Impedance (1) | Open drain pulls low (0) CC Mode   |                                           |  |

| 00                                 | Open drain pulls low (0)           | Open drain pulls low (0)           | CV Mode                                   |  |

| 01                                 | Open drain pulls low (0)           | Open drain in Hi-<br>Impedance (1) | Hardware Fault or Safety Timer<br>Timeout |  |

#### **Hardware Faults**

The MAX17701 features hardware fault checks at power-up and during normal operation. <u>Table 2</u> provides various fault detection features available and their behaviors in MAX17701.

**Table 2. Protection Under System Faults**

| FAULT CONDITION                                                       | FAULT MONITOR STATE                 | FAULT BEHAVIOR                                                        |  |

|-----------------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------|--|

| RT/SYNC to SGND/EP short                                              |                                     |                                                                       |  |

| GATEN to DCIN short                                                   |                                     |                                                                       |  |

| TMR pin left unconnected                                              |                                     |                                                                       |  |

| TMR to SGND/EP short                                                  | Power-up check                      |                                                                       |  |

| V <sub>REF</sub> to SGND/EP short                                     |                                     |                                                                       |  |

| Output overvoltage (V <sub>OVI</sub> > V <sub>OVI_TH</sub> )          |                                     | Latched fault, need to recycle power or EN/UVLO to restart the device |  |

| (V <sub>GATEN</sub> - V <sub>DCIN</sub> ) <<br>V <sub>GATEN_</sub> OK |                                     |                                                                       |  |

| $V_{REF}$ < 1.95V or $V_{REF}$ > 3.05V                                | Continuous, during normal operation |                                                                       |  |

| Output overvoltage (V <sub>OVI</sub> > V <sub>OVI_TH</sub> )          | 555.44.611                          |                                                                       |  |

#### Linear Regulator (V<sub>CC</sub> and EXTVCC)

The MAX17701 integrates two internal low-dropout (LDO) linear regulators INT-LDO and EXT-LDO that power  $V_{CC}$ .  $V_{CC}$  powers gate drivers and internal control circuitry. INT-LDO is powered from  $V_{IN}$  and turns on when  $V_{EN/UVLO} > V_{ENT}$  (0.7V). EXT-LDO is powered from EXTVCC. At any time, only one of these two linear regulators operates, depending on the EXTVCC voltage. If  $V_{EXTVCC} > 4.7V$  (typ) then  $V_{CC}$  is powered from EXT-LDO. If  $V_{EXTVCC} < 4.46V$ (typ), then  $V_{CC}$  is powered from INT-LDO. Powering  $V_{CC}$  from EXTVCC reduces on-chip dissipation and increases efficiency at higher input voltages. Connect EXTVCC to  $V_{OUT}$  for applications with  $V_{OUT} \ge 4.8V$ . The maximum voltage limit on EXTVCC is 24V. Bypass EXTVCC with a 1µF ceramic capacitor to SGND/EP. Leave EXTVCC open when not used. Bypass  $V_{CC}$  to PGND with at least a  $4.7\mu$ F/0805, low-ESR ceramic capacitor.

#### Reference Voltage (V<sub>REF</sub>)

The MAX17701 provides a 2.5V reference voltage on the  $V_{REF}$  pin with  $\pm 1.4\%$  accuracy.  $V_{REF}$  can be used to program  $V_{ILIM}$  to set the CC mode charging current ( $I_{CHGMAX}$ ). Connect a minimum 0.1 $\mu$ F low-ESR ceramic capacitor between  $V_{REF}$  and SGND/EP. See the <u>CC Mode Charging Current Setting (ILIM)</u> section for more details.

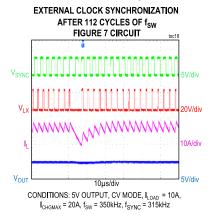

#### Setting the Switching Frequency and External Clock Synchronization (RT/SYNC)

The switching frequency of the device can be programmed from 125kHz to 2.2MHz by using a resistor ( $R_{RT/SYNC}$ ) connected from the RT/SYNC pin to SGND/EP.  $R_{RT/SYNC}$  can be calculated using the following equation:

$$R_{RT/SYNC} = \frac{44830}{f_{SW}} - 1.205$$

Where  $R_{RT/SYNC}$  is in  $k\Omega$  and  $f_{SW}$  is in kHz. Leave the RT/SYNC pin unconnected to operate the device at 350kHz default switching frequency.

The MAX17701 can be synchronized to an external clock coupled to the RT/SYNC pin through a 10pF ceramic capacitor. The external clock is detected after checking the rising edge for 112 cycles of the internal clock (set by RT/SYNC). If the external clock frequency is within the allowed SYNC frequency range (±10% of nominal internal clock frequency), the device stops switching for 2 switching time periods and then restarts with an external clock. When the external clock is removed, the device stops switching for 10 switching time periods and then restarts with an internal clock.

The minimum external clock pulse-width should be greater than 100ns. The off-time duration of the external clock should be at least 100ns.

#### **Peak Current-Limit**

The MAX17701 provides a cycle-by-cycle overcurrent protection by limiting the peak current-sense voltage ( $V_{CSP} - V_{CSN}$ ) across the current sense pins. When an overcurrent event (( $V_{CSP} - V_{CSN}$ ) >  $V_{CSPEAK}$ ) is detected, the overcurrent comparator in the MAX17701 terminates the DH pulse and limits the peak current. The overcurrent fault is not latched.

#### **Charging Current Monitoring (ISMON)**

The output charge current can be monitored by observing the voltage at the ISMON pin. Connect a 1nF ceramic capacitor on ISMON to filter out the switching frequency component in the ISMON voltage. The charging current is given by the following equation:

$$I_{\text{CHG}} = \frac{V_{\text{ISMON}}}{30 \times R_{S}}$$

where,

I<sub>CHG</sub> = Charging current

V<sub>ISMON</sub> = Voltage at the ISMON pin

R<sub>S</sub> = Current-sense resistance

#### **Thermal-Shutdown Protection**

Thermal-shutdown protection limits junction temperature of the device. When the junction temperature of the device exceeds +160°C, an on-chip thermal sensor shuts down the device, allowing the device to cool. The device turns on after the junction temperature reduces by 10°C. Carefully evaluate the total power dissipation to avoid unwanted triggering of the thermal shutdown during normal operation (see the <u>Device Power Dissipation</u> section).

#### **Applications Information**

#### **Inductor Selection**

Three key inductor parameters must be specified for operation with the device: inductance value (L), DC resistance ( $R_{DCR}$ ), and inductor saturation current ( $I_{SAT}$ ).

The required inductance is calculated based on the inductor current ripple ratio (LIR), i.e., ratio of peak-to-peak ripple current ( $\Delta I_{\rm I}$ ) to CC mode charging current (ICHGMAX). A good compromise between size and loss is an LIR of 0.3.

The inductance value (L) is given by the higher value of the two calculated inductances:

L1 =

$$\frac{V_{OUT} \times (1-D)}{LIR \times I_{CHGMAX} \times f_{SW}}$$

L2 =

$$\frac{V_{OUT}}{600000 \times I_{CHGMAX}}$$

where:

V<sub>OUT</sub> = Desired voltage across supercapacitor

I<sub>CHGMAX</sub> = CC mode charging current

D = Duty cycle of the converter,  $V_{OUT}/V_{IN}$

V<sub>IN</sub> = Nominal input voltage

f<sub>SW</sub> = Switching frequency in Hz

Select an inductor that is nearest to the calculated value. The inductor RMS-current rating should be more than the CC mode charging current. Select a low-loss inductor with acceptable dimensions and the lowest possible DC resistance. The saturation current rating ( $I_{SAT}$ ) of the inductor must be high enough to ensure that saturation can occur only above the overcurrent threshold corresponding to  $V_{CSPEAK}$ .

#### **Output Capacitor Selection**

Supercapacitors have significant equivalent series resistance (ESR<sub>SUP</sub>). The switching ripple component of charger output current flows into this ESR<sub>SUP</sub> and results in a large output-voltage ripple. To reduce the voltage ripple across the supercapacitor, additional X7R ceramic capacitors and/or low-ESR POSCAP capacitors can be used at the output of the charger.

X7R ceramic output capacitors are preferred due to their stability over temperature in industrial applications. For higher values of output capacitance, low-ESR POSCAP capacitors can be used in parallel with ceramic capacitors.

Calculate the required output capacitance (C<sub>OUT</sub>) based on the following equation:

$$C_{OUT} = \frac{25 \times I_{CHGMAX}}{f_{SW} \times V_{OUT}}$$

where:

I<sub>CHGMAX</sub> = CC mode charging current setting

f<sub>SW</sub> = Switching frequency in Hz

V<sub>OUT</sub> = Desired voltage across the supercapacitor

Derating of ceramic capacitors with DC-bias voltage must be considered while selecting the capacitors, using the manufacturer data sheet. The selected output capacitor  $C_{OUT\_SEL}$  and its equivalent series resistance (ESR<sub>COUT</sub>) affect the output-voltage ripple ( $\Delta V_{OUT}$ ). Estimate the resultant  $\Delta V_{OUT}$  using the following equation:

$$\Delta \mathsf{V}_{OUT} \approx \Delta I_L \times \left( \mathsf{ESR}_{\mathsf{COUT}} + \frac{1}{8 \times f_{\mathsf{SW}} \times C_{\mathsf{OUT\_SEL}}} \right)$$

where  $\Delta I_L$  is the inductor peak-to-peak ripple current.

In applications with a long cable between the charger output and the supercapacitor, to dampen the oscillations caused by the interaction of the cable inductance with the low ESR output capacitors of the charger circuit, an electrolytic capacitor with appropriate ESR (equivalent series resistance) may be used. Choose an electrolytic capacitor equal to 1.5 times the value of C<sub>OUT\_SEL</sub>. Select an electrolytic capacitor with an equivalent series resistance (ESR<sub>ELCO</sub>) as calculated below:

$$ESR_{ELCO} = \sqrt{\frac{L_{CABLE}}{C_{OUT}}}$$

where L<sub>CABLE</sub> is the output cable inductance.

#### **Input Capacitor Selection**

The input filter capacitor reduces peak currents drawn from the power source and reduces noise and voltage ripple on the input caused by the switching converter. Calculate the required input capacitance at  $V_{IN}$  ( $C_{VIN}$ ) using the following equation:

$$C_{VIN} = \frac{I_{CHGMAX} \times D \times (1 - D)}{\eta \times f_{SW} \times \Delta V_{IN}}$$

where:

$$D = \frac{V_{OUT}}{V_{IN}}$$

is the duty ratio of the converter

f<sub>SW</sub> = Switching frequency in Hz

$\Delta V_{IN}$  = Allowable input-voltage ripple

$\eta$  = Efficiency of the converter

I<sub>CHGMAX</sub> = CC mode charging current

Choose  $\Delta V_{IN} \le 0.5 V$  to minimize voltage ripple across the external nMOSFET and to provide robust operation during input short-circuit events.

The input capacitor RMS current (I<sub>RMS</sub>) is calculated using the following equation:

$$I_{\text{RMS}} = I_{\text{CHGMAX}} \times \frac{\sqrt{V_{\text{OUT}} \times [V_{\text{IN}} - V_{\text{OUT}}]}}{V_{\text{IN}}}$$

Choose low-ESR ceramic input capacitors that exhibit less than a +10°C temperature rise at I<sub>RMS</sub> for optimal long-term reliability. X7R capacitors are recommended in industrial applications for their temperature stability. Derating of ceramic capacitors with DC-bias voltage must be considered while selecting the capacitors using the manufacturer data sheet.

Choose an electrolytic capacitor at DCIN in order to prevent the DCIN voltage from being less than -0.3V during input short events. An electrolytic capacitor also provides the damping for potential oscillations caused by inductance of the longer input power path and input ceramic capacitor ( $C_{VIN}$ ). Additionally, if required, add a Schottky diode at DCIN in parallel with the electrolytic capacitor.