# THREE AND FOUR CELL LITHIUM-ION OR LITHIUM-POLYMER BATTERY PROTECTION AFE

### **FEATURES**

- 2-, 3-, or 4-Cell Series Protection Control

- Can Directly Interface With the bq2084 Gas

Gauges

- Provides Individual Cell Voltages and Battery Voltage to Battery Management Host

- Integrated Cell Balancing Drive

- I<sup>2</sup>C Compatible User Interface Allows Access to Battery Information

- Programmable Threshold and Delay for Over Load and Short Circuit During Charge and Discharge

- System Alert Interrupt Output

- Host Control Can Initiate Sleep Power Mode

and Ship Mode

- Integrated 3.3-V, 25-mA LDO

- Supply Voltage Range From 4.5 V to 25 V

- Low Supply Current of 60-µA Typical

## APPLICATIONS

- Notebook PCs

- Medical and Test Equipment

- Portable Instrumentation

## DESCRIPTION

The bq29312 is a 2-, 3-, or 4-cell lithium-ion battery pack protection analog front end (AFE) IC that incorporates a 3.3-V, 25-mA low-dropout regulator (LDO). The bq29312 also integrates an  $I^2C$  compatible interface to extract battery parameters such as cell voltages and control output status. Other parameters such as current protection thresholds and delays can be programmed into the bq29312 to increase the flexibility of the battery management system.

The bq29312 provides safety protection for overcharge, overload, short-circuit, overvoltage, and undervoltage conditions in conjunction with the battery management host. In overload and short-circuit conditions, the bq29312 turns the FET drive off autonomously dependant on the internal configuration setting.

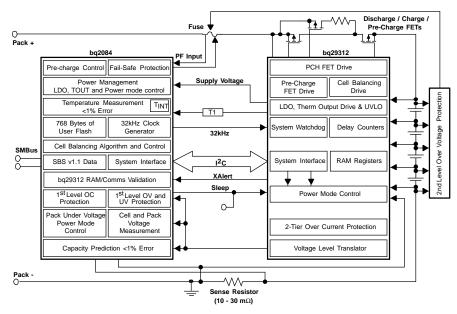

SYSTEM PARTITIONING DIAGRAM

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

A

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## **DESCRIPTION (Continued)**

The communications interface allows the host to observe and control the current status of the bq29312. It enables cell balancing, enters different power modes, sets overload levels, sets the overload blanking delay time, sets short-circuit threshold levels for charge and discharge, and sets the short-circuit blanking delay time.

Cell balancing of each cell is performed via a cell bypass path, which is enabled via the internal control register accessible via the  $I^2C$  compatible interface. The maximum bypass current is set via an external series resistor and internal FET on resistance (typical 400  $\Omega$ ).

#### **ORDERING INFORMATION**

| <b>-</b>       | PACKAGED <sup>(1)</sup> |

|----------------|-------------------------|

| I <sub>A</sub> | TSSOP (PW)              |

| –25°C to 85°C  | bq29312PW<br>bq29312PWR |

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

### PACKAGE DISSIPATION RATINGS

| PACKAGE | POWER RATING          | DERATING FACTOR             | POWER RATING          |                       |  |

|---------|-----------------------|-----------------------------|-----------------------|-----------------------|--|

| PACKAGE | T <sub>A</sub> ≤ 25°C | ABOVE $T_A \le 25^{\circ}C$ | T <sub>A</sub> ≤ 70°C | T <sub>A</sub> = 85°C |  |

| PW      | 874 mW                | 6.99 W/°C                   | 559 mW                | 454 mW                |  |

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted<sup>(1)(2)</sup>

|                  |                                    |                                                | bq29312                |  |

|------------------|------------------------------------|------------------------------------------------|------------------------|--|

| $V_{SS}$         | Supply voltage range               | PACK, BAT                                      | –0.3 V to 34 V         |  |

|                  |                                    | VC1, VC2, VC3, VC4                             | –0.3 V to 34 V         |  |

|                  |                                    | SR1, SR2                                       | -1.0 V to 1.0 V        |  |

|                  |                                    | VC5                                            | –1.0 V to 4.0 V        |  |

| VI               | Input voltage range                | VC1 to VC2, VC2 to VC3, VC3 to VC4, VC4 to VC5 | –0.3 to 8.5 V          |  |

|                  |                                    | WDI, SLEEP, SCLK, SDATA                        | –0.3 to 8.5 V          |  |

|                  |                                    | ZVCHG                                          | –0.3 V to 34 V         |  |

|                  |                                    | DSG, CHG                                       | –0.3 V to BAT          |  |

| V                |                                    | OD                                             | –0.3 V to 34 V         |  |

| Vo               | Output voltage range               | PMS                                            | -0.3 V to PACK - 0.2 V |  |

|                  |                                    | TOUT, SCLK, SDATA, CELL, XALERT                | –0.3 to 7 V            |  |

|                  | Current for cell balancing         | Current for cell balancing                     |                        |  |

|                  | Continuous total power dissipation | Continuous total power dissipation             |                        |  |

| T <sub>stg</sub> | Storage temperature range          |                                                | –65°C to 150°C         |  |

| -                | Lead temperature (soldering, 1     | Lead temperature (soldering, 10 sec)           |                        |  |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to ground of this device except VCn - VC(n + 1), where n = 1, 2, 3, 4 cell voltage.

### **RECOMMENDED OPERATING CONDITIONS**

|                                                |                                               |                                 | MIN                     | NOM    | MAX          | UNIT |

|------------------------------------------------|-----------------------------------------------|---------------------------------|-------------------------|--------|--------------|------|

|                                                | Supply Voltage (BAT or PACK)                  |                                 | 4.5 <sup>(1)</sup>      |        | 25           | V    |

| V <sub>I(STARTUP)</sub>                        | Start-up voltage (PACK)                       |                                 | 5.0                     |        |              | V    |

|                                                |                                               | VC1, VC2, VC3, VC4              | 0                       |        | BAT          |      |

|                                                |                                               | SR1, SR2                        | -0.5                    |        | 0.5          |      |

| M                                              | Input voltage range                           | VC5                             | -0.5                    |        | 3.0          | v    |

| vI                                             | input voltage range                           | VCn – VC(n+1), (n = 1, 2, 3, 4) | 0                       |        | 5.0          | v    |

| VI<br>VIH<br>VIL<br>VIH<br>VIL<br>VO<br>O<br>O |                                               | PMS                             | 0                       | F      | ACK          |      |

|                                                |                                               | SLEEP                           | 0                       |        | REG          |      |

| V <sub>IH</sub>                                |                                               |                                 | 0.8×REG                 |        | REG          | V    |

| V <sub>IL</sub>                                | Logic level input voltage                     | SCLK, SDATA, WDI                | 0                       |        | 0.2 ×<br>REG |      |

| V <sub>IH</sub>                                | DMC la sia la val                             | PMS                             | V <sub>PACK</sub> - 0.2 | N      | PACK         | V    |

| V <sub>IL</sub>                                | PMS logic level                               | PMS                             | 0                       |        | 0.2          |      |

|                                                | PMS pull up/pull down resistance              | RPMS                            | 100                     |        | 1000         | kΩ   |

| Vo                                             | Output voltage                                | OD                              |                         |        | 25           | V    |

| I <sub>O</sub>                                 | Output current                                | XALERT, SDATA                   |                         |        | 200          | μA   |

|                                                |                                               | CELL                            |                         |        | ±10          | μA   |

| l <sub>l</sub>                                 | Input current,External 3.3 V REG<br>capacitor | SLEEP                           | -0.5                    |        | 1.0          | μA   |

|                                                | oupuonon                                      | C <sub>(REG)</sub>              | 4.7                     |        |              | μF   |

| V <sub>IH</sub><br>VIL<br>VIL<br>VIL<br>O<br>O | Extend CELL output filter                     | R <sub>(CELL)</sub>             |                         | 100    |              | Ω    |

|                                                | Extend CELL output filter                     | C <sub>(CELL)</sub>             |                         | 100    |              | nF   |

|                                                |                                               | OD                              |                         |        | 1            | mA   |

| IOL                                            | Input frequency                               | WDI                             | :                       | 32.768 |              | kHz  |

|                                                | WDI high time                                 |                                 | 2                       |        | 28           | μs   |

| T <sub>A</sub>                                 | Operating temperature                         |                                 | -25                     |        | 85           | °C   |

(1) V<sub>(PACK)</sub> supply voltage must rise above start-up voltage on power up to enable the internal regulator which drives REG and TOUT as required. Once V<sub>(PACK)</sub> is above the start-up voltage, it can fall down to the minimum supply voltage and still meet the specifications of the bq29312.

#### **ELECTRICAL CHARACTERISTICS**

$T_{A}$  = 25°C,  $C_{(REG)}$  = 4.7  $\mu F,~BAT$  = 14 V (unless otherwise noted)

| PARAMETER                     |                                                          | TEST CONDITIONS                                                                                                                                                                                  |                                       |       | TYP         | MAX   | UNIT |

|-------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------|-------------|-------|------|

| SUPPLY CU                     | RRENT                                                    |                                                                                                                                                                                                  |                                       |       |             |       |      |

| I <sub>CC1</sub>              | Supply current 1                                         | No load at REG, TOUT, XALERT, SCLK, and SDATA.<br>ZVCHG = off ,VMEN = on, WDI no clock,                                                                                                          | T 0500 to 0500                        |       | 60          | 90    | μA   |

|                               |                                                          | Select VC5 = VC4 = 0 V                                                                                                                                                                           | $T_A = -25^{\circ}C$ to $85^{\circ}C$ |       |             | 100   |      |

| I <sub>CC2</sub>              | Supply current 2<br>(Depends of VM<br>topology selected) | No load at REG, TOUT, XALERT, SCLK, and SDATA.<br>ZVCHG = off, VMEN = off, WDI no clock                                                                                                          | $T_A = -25^{\circ}C$ to $85^{\circ}C$ |       | 25          | 50    | μA   |

| I <sub>(SLEEP)</sub>          | Sleep current                                            | No load at REG, TOUT, XALERT, SCLK, and<br>SDATA.CHG, DSG and ZVCHG = off, REG = on,<br>VMEN = off, WDI no clock, SLEEP = REG or OPEN                                                            | $T_A = -25^{\circ}C$ to $85^{\circ}C$ |       | 20          | 40    | μA   |

| I <sub>(SHIP)</sub>           | Ship current                                             | $ \begin{array}{l} \mbox{REG, CHG, DSG and ZVCHG = off, REG = off,} \\ \mbox{VMEN = off, WDI no clock, VPACK= 0 V} \end{array}  T_{A} = -25^{\circ}\mbox{C to } 85^{\circ}\mbox{C} \end{array} $ |                                       |       | 0.1         | 1.0   | μA   |

| 3.3 V LDO                     |                                                          |                                                                                                                                                                                                  |                                       |       |             |       |      |

|                               |                                                          | 8.0 V < BAT or PACK $\leq$ 25 V, I <sub>O</sub> $\leq$ 25 mA                                                                                                                                     |                                       | -4%   | 3.3         | 2%    |      |

|                               | Regulator output                                         | 6.5 V < BAT or PACK $\leq$ 8 V, I <sub>O</sub> $\leq$ 25 mA                                                                                                                                      | T 0500 to 0500                        | -9%   | 3.3         | 2%    | V    |

| V <sub>(REG)</sub>            | voltage                                                  | 5.4 V $\leq$ BATor PACK $\leq$ 6.5 V, I <sub>O</sub> $\leq$ 16 mA                                                                                                                                | $T_A = -25^{\circ}C$ to $85^{\circ}C$ | -9%   | 3.3         | 2%    | V    |

|                               |                                                          | 4.5 V $\leq$ BAT or PACK $\leq$ 25 V, I_O $\leq$ 2 mA                                                                                                                                            |                                       | -2%   | 3.3         | 2%    | V    |

| $\Delta V_{(EGTEMP)}$         | Regulator output<br>change with<br>temperature           | 5.4 V $\leq$ BAT $\leq$ 25 V, I <sub>O</sub> = 2 mA,                                                                                                                                             | $T_A = -25^{\circ}C$ to $85^{\circ}C$ |       | ±0.2%       |       |      |

| $\Delta V_{(\text{REGLINE})}$ | Line regulation                                          | 5.4 V $\leq$ BAT or PACK $\leq$ 25 V, I <sub>O</sub> = 2 mA                                                                                                                                      |                                       |       | 3           | 10    | mV   |

| A)/                           | Lood together                                            | $BAT = 14 \ V, \ 0.2 \ mA \leq I_O \leq 2 \ mA$                                                                                                                                                  |                                       |       | 7           | 15    | mV   |

| $\Delta V_{(REGLOAD)}$        | Load regulation                                          | $BAT = 14 \ V, \ 0.2 \ mA \leq I_O \leq 25 \ mA$                                                                                                                                                 |                                       |       | 40          | 100   | mv   |

| 1                             | Current limit                                            | BAT = 14 V, REG = 3.0 V                                                                                                                                                                          |                                       |       |             | 100   | mA   |

| I <sub>MAX</sub>              |                                                          | BAT = 14 V, REG = 0 V                                                                                                                                                                            |                                       | 12    |             | 50    | ma   |

| CELL VOLT                     | AGE MONITOR                                              |                                                                                                                                                                                                  |                                       |       |             |       |      |

| V                             | CELL output                                              | $V_{(Cn)} - V_{(Cn~+~1)}$ = 0 V, 8.0 V $\leq$ BAT or PACK $\leq$ 25 V                                                                                                                            |                                       |       | 0.975       |       | V    |

| V <sub>(CELL OUT)</sub>       |                                                          | $V_{(Cn)}-V_{(Cn~+~1)}$ = 4.5 V, 8.0 V $\leq$ BAT or PACK $\leq$ 25 V                                                                                                                            |                                       |       | 0.3         |       | ~    |

| REF                           | CELL output                                              | Mode <sup>(1)</sup> , 8.0 V $\leq$ BAT or PACK $\leq$ 25 V                                                                                                                                       |                                       | -1%   | 0.975       | 1%    | V    |

| PACK                          | CELL output                                              | Mode <sup>(2)</sup>                                                                                                                                                                              |                                       | -5%   | PACK/<br>25 | 5%    | V    |

| к                             |                                                          | K = (CELL output (VC5 = 0.0 V, VC4 = 4.5 V)<br>- CELL output (VC5 = VC4 = 0.0 V)/ 4.5                                                                                                            |                                       | 0.147 | 0.150       | 0.153 |      |

| r.                            | CELL scale factor                                        | K = (CELL output (VC2 = 13.5 V, VC1 = 18.0 V)<br>– CELL output (VC2 = VC1 = 13.5 V)/ 4.5                                                                                                         |                                       |       | 0.150       | 0.153 |      |

| VICR                          | CELL output offset<br>error                              | CELL output (VC2 = 17.0 V, VC1 = 17.0 V)<br>CELL output (VC2 = VC1 = 0.0 V)                                                                                                                      |                                       |       | -1          |       | mV   |

| R <sub>(BAL)</sub>            | Cell balance internal resistance                         | $rds_{(ON)}$ for internal FET switch at V <sub>DS</sub> = 2.0 V                                                                                                                                  |                                       | 200   | 400         | 800   | Ω    |

|                               |                                                          | II.                                                                                                                                                                                              |                                       |       |             |       |      |

(1) Register Address =0x04, b2(CAL0) = b3(CAL1) = 1, Register Address = 0x03, b0(VMEN) = 1

(2) Register Address = 0x03, b1(PACKOUT) = 1, b0( VMEN) = 1

## **ELECTRICAL CHARACTERISTICS (Continued)**

$T_A = 25^{\circ}C$ ,  $C_{(REG)} = 4.7 \ \mu\text{F}$ , BAT = 14 V (unless otherwise noted)

| PARAMETER TEST CONDITION |                                                      |                                                                                                                            | IDITION                               | MIN  | NOM | MAX  | UNIT |

|--------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------|-----|------|------|

| OVER LO                  | AD (OL) AND SHORT CIRCUIT (SC) DETECT                | ION                                                                                                                        |                                       |      |     |      |      |

| V <sub>OL</sub>          | OL detection threshold range, typical <sup>(1)</sup> |                                                                                                                            |                                       | -50  |     | -205 | mV   |

| $\Delta V_{OL}$          | OL detection threshold program step                  |                                                                                                                            |                                       |      | 5   |      | mV   |

| V <sub>HYS(OL)</sub>     | OL detection threshold hysteresis                    |                                                                                                                            |                                       | 7    | 10  | 13   | mV   |

|                          |                                                      | Charge                                                                                                                     |                                       | 100  |     | 475  |      |

| V <sub>(SC)</sub>        | SC detection threshold range, typical <sup>(2)</sup> | Discharge                                                                                                                  |                                       | -100 |     | -475 | mV   |

|                          |                                                      | Charge                                                                                                                     |                                       |      | 25  |      |      |

| $\Delta V_{(SC)}$        | SC detection threshold program step                  | Discharge                                                                                                                  |                                       |      | -25 |      | mV   |

| V <sub>HYS(SC)</sub>     | SC detection threshold hysteresis                    | Charge and Discharge                                                                                                       |                                       | 40   | 50  | 60   | mV   |

|                          |                                                      |                                                                                                                            | V <sub>OL</sub> = 50 mV (min)         | 40   | 50  | 60   |      |

| V <sub>(OL_acr)</sub>    | OL detection threshold accuracy <sup>(1)</sup>       | Discharge                                                                                                                  | V <sub>OL</sub> = 100 mV              | 90   | 100 | 110  | mV   |

|                          |                                                      |                                                                                                                            | V <sub>OL</sub> = 205 mV (max)        | 184  | 205 | 226  |      |

|                          | SC detection threshold accuracy <sup>(2)</sup>       |                                                                                                                            | V <sub>SC</sub> = 100 mV (min)        | 80   | 100 | 120  | mV   |

| V <sub>(SC_acr)</sub>    |                                                      | Charge and Discharge                                                                                                       | V <sub>SC</sub> = 200 mV              | 180  | 200 | 220  |      |

|                          |                                                      |                                                                                                                            | V <sub>SC</sub> = 475 mV (max)        | 426  | 475 | 523  |      |

| FET DRIV                 | E CIRCUIT                                            |                                                                                                                            |                                       |      |     |      |      |

|                          | (FETON)                                              |                                                                                                                            | BAT= 20 V                             | 12   | 15  | 18   |      |

| V(FETON)                 |                                                      | $\begin{array}{c} V_{(\text{FETONC})} = V_{(\text{PACK})} - V_{(\text{CHG})} \\ \text{VGS connect 1 } M\Omega \end{array}$ | PACK = 20 V                           | 12   | 15  | 18   | V    |

| V <sub>(ZCHG)</sub>      | ZVCHG clamp voltage                                  |                                                                                                                            | PACK= 4.5 V                           | 3.3  | 3.5 | 3.7  | V    |

|                          | Output voltage, charge and discharge FETs            | V <sub>(FETOFF)</sub> = V <sub>(PACK)</sub> - V <sub>(DSG)</sub>                                                           | PACK= 16 V                            |      |     | 0.2  | N    |

| V <sub>(FETOFF)</sub>    | off                                                  | V <sub>(FETOFF</sub> )=V <sub>(BAT)</sub> -V <sub>(CHG)</sub>                                                              | BAT = 16 V                            | -    |     | 0.2  | V    |

|                          | Diag time                                            |                                                                                                                            | V <sub>DSG</sub> :10%–90%             |      | 40  | 200  |      |

| t <sub>r</sub>           | Rise time                                            | C <sub>L</sub> = 4700 pF                                                                                                   | V <sub>CHG</sub> :10%–90%             |      | 40  | 200  | μs   |

|                          | Fall time                                            | C <sub>1</sub> = 4700 pF                                                                                                   | V <sub>DSG</sub> :90%–10%             |      | 40  | 200  |      |

| t <sub>f</sub>           | Fail ume                                             | $G_{L} = 4700 \text{ pr}$                                                                                                  | V <sub>CHG</sub> :90%–10%             |      | 40  | 200  | μs   |

| THERMIS                  | TOR DRIVE                                            |                                                                                                                            | <b>i</b>                              |      |     |      |      |

| r <sub>DS(on)</sub>      | TOUT pass-element series resistance                  | $I_{O}$ = -1 mA at TOUT pin, rds_{(ON)} = (V_{REG} - V_{O} (TOUT))/1 mA, T_{A} = -25°C to 85°C                             |                                       |      | 50  | 100  | Ω    |

| LOGIC                    |                                                      |                                                                                                                            |                                       |      |     |      |      |

| D                        |                                                      | XALERT                                                                                                                     | $T_A = -25^{\circ}C$ to $85^{\circ}C$ | 60   | 100 | 200  | ko   |

| R <sub>(PUP)</sub>       | Internal pullup resistance                           | SDATA, SCLK,                                                                                                               | $T_A = -25^{\circ}C$ to $85^{\circ}C$ | 6    | 10  | 20   | kΩ   |

|                          |                                                      | XALERT, $I_0 = 200 \ \mu A$ ,                                                                                              | $T_A = -25^{\circ}C$ to $85^{\circ}C$ |      |     | 0.2  |      |

| V <sub>OL</sub>          | Logic level output voltage                           | SDATA, Ι <sub>Ο</sub> = 50 μΑ,                                                                                             | $T_A = -25^{\circ}C$ to $85^{\circ}C$ |      |     | 0.4  | V    |

|                          |                                                      | $OD I_O = 1 mA$ ,                                                                                                          | $T_A = -25^{\circ}C$ to $85^{\circ}C$ |      |     | 0.6  |      |

(1) See OL register for setting detection threshold

(2) See SC register for setting detection threshold

SLUS546E-MARCH 2003-REVISED MARCH 2005

#### **AC ELECTRICAL CHARACTERISTICS**

$T_{_{A}}=25^{\circ}C,\ C_{_{(REG)}}=4.7\ \mu\text{F},\ \text{BAT}$  = 14 V (unless otherwise noted)

|                       | PARAMETER                | TEST CONDITION | MIN | NOM | MAX  | UNIT |

|-----------------------|--------------------------|----------------|-----|-----|------|------|

| t <sub>(WDTINT)</sub> | WDT start-up detect time |                | 250 | 700 | 2000 | ms   |

| t <sub>(WDWT)</sub>   | WDT detect time          |                |     | 100 |      | μs   |

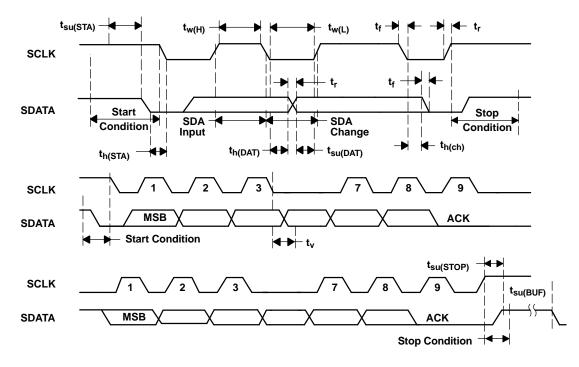

## AC TIMING SPECIFICATIONS (I<sup>2</sup>C COMPATIBLE SERIAL INTERFACE)

|                       | PARAMETER                                                            | MIN | MAX  | UNIT |

|-----------------------|----------------------------------------------------------------------|-----|------|------|

| t <sub>r</sub>        | SCLK SDATA rise time                                                 |     | 1000 | ns   |

| t <sub>f</sub>        | SCLK SDAT fall time                                                  |     | 300  | ns   |

| t <sub>w(H)</sub>     | SCLK pulse width high                                                | 4.0 |      | μs   |

| t <sub>w(L)</sub>     | SCLK pulse width low                                                 | 4.7 |      | μs   |

| t <sub>su(STA)</sub>  | Setup time for START condition                                       | 4.7 |      | μs   |

| t <sub>h(STA)</sub>   | START condition hold time after which first clock pulse is generated | 4.0 |      | μs   |

| t <sub>su(DAT)</sub>  | Data setup time                                                      | 250 |      | ns   |

| t <sub>h(DAT)</sub>   | Data hold time                                                       | 0   |      | μs   |

| t <sub>su(STOP)</sub> | Setup time for STOP condition                                        | 4.0 |      | μs   |

| t <sub>su(BUF)</sub>  | Time the bus must be free before new transmission can start          | 4.7 |      | μs   |

| t <sub>V</sub>        | Clock low to data out valid                                          |     | 900  | ns   |

| t <sub>h(CH)</sub>    | Data out hold time after clock low                                   | 0   |      | ns   |

| f <sub>SCL</sub>      | Clock frequency                                                      | 0   | 100  | kHz  |

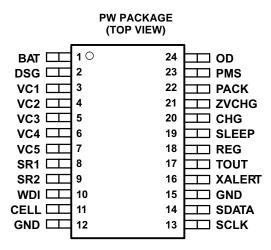

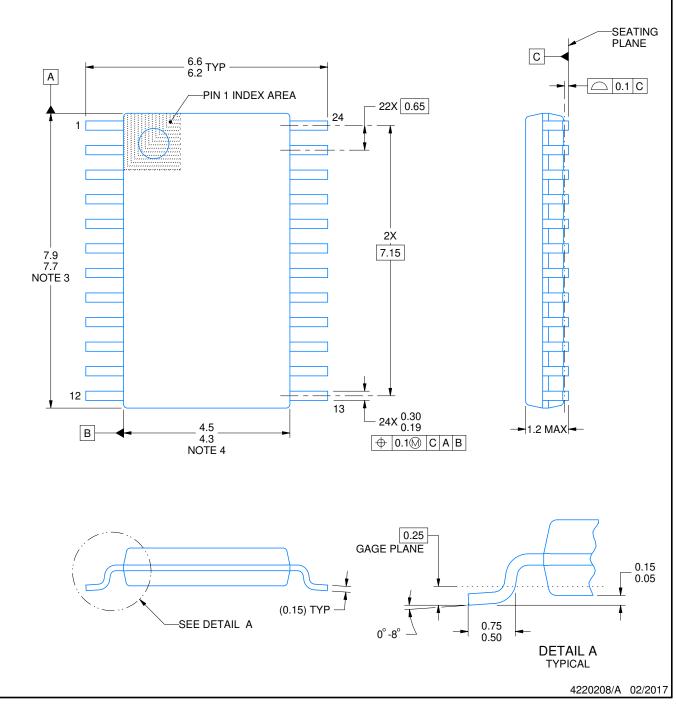

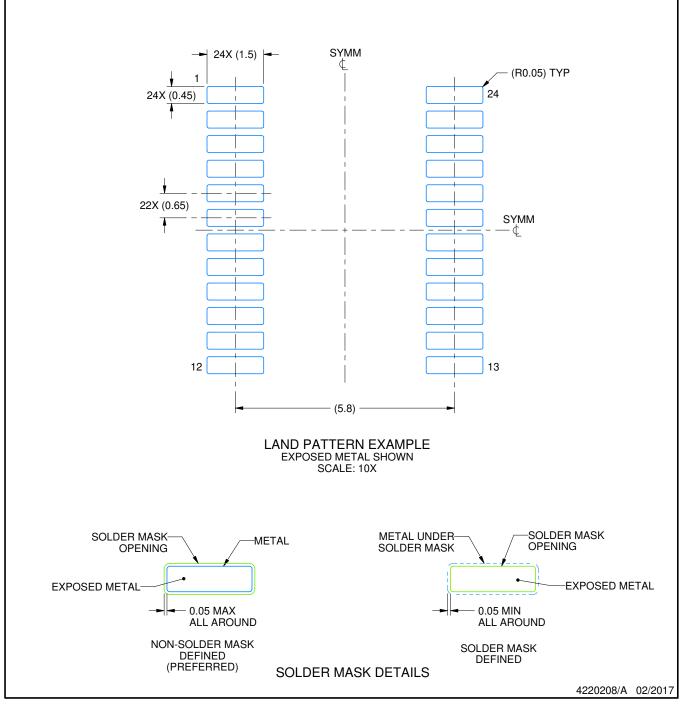

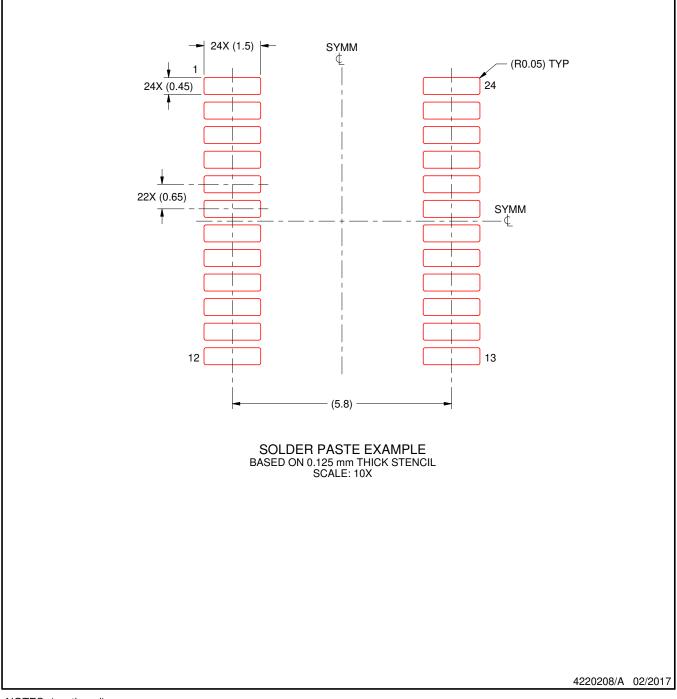

#### **PIN ASSIGNMENTS**

#### **Terminal Functions**

| TERM   | IINAL | DESCRIPTION                                                                                                                                                             |  |  |  |

|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME   | NO.   | DESCRIPTION                                                                                                                                                             |  |  |  |

| BAT    | 1     | Diode protected BAT+ terminal and primary power source.                                                                                                                 |  |  |  |

| DSG    | 2     | Push-pull output discharge FET gate drive                                                                                                                               |  |  |  |

| VC1    | 3     | Sense voltage input terminal for most positive cell and balance current input for most positive cell.                                                                   |  |  |  |

| VC2    | 4     | Sense voltage input terminal for second most positive cell, balance current input for second most positive cell and return balance current for most positive cell.      |  |  |  |

| VC3    | 5     | Sense voltage input terminal for third most positive cell, balance current input for third most positive cell and return balance current for second most positive cell. |  |  |  |

| VC4    | 6     | Sense voltage input terminal for least positive cell, balance current input for least positive cell and return balance current for third most positive cell.            |  |  |  |

| VC5    | 7     | Sense voltage input terminal for most negative cell, return balance current for least positive cell.                                                                    |  |  |  |

| SR1    | 8     | Current sense positive terminal when charging relative to SR2                                                                                                           |  |  |  |

| SR2    | 9     | Current sense negative terminal when discharging relative to SR2 current sense terminal                                                                                 |  |  |  |

| WDI    | 10    | Digital input that provides the timing clock for the OC and SC delays and also acts as the watchdog clock.                                                              |  |  |  |

| CELL   | 11    | Output of scaled value of the measured cell voltage.                                                                                                                    |  |  |  |

| GND    | 12    | Analog ground pin and negative pack terminal                                                                                                                            |  |  |  |

| SCLK   | 13    | Open-drain bidirectional serial interface clock with internal 10 k $\Omega$ pull-up to V <sub>(REG)</sub> .                                                             |  |  |  |

| SDATA  | 14    | Open-drain bidirectional serial interface data with internal 10 k $\Omega$ pull-up to V <sub>(REG)</sub> .                                                              |  |  |  |

| GND    | 15    | Connect to GND                                                                                                                                                          |  |  |  |

| XALERT | 16    | Open-drain output used to indicate status register changes. With internal 100 k $\Omega$ pull-up to V_{(REG)}                                                           |  |  |  |

| TOUT   | 17    | Provides thermistor bias current                                                                                                                                        |  |  |  |

| REG    | 18    | Integrated 3.3-V regulator output                                                                                                                                       |  |  |  |

| SLEEP  | 19    | This pin is pulled up to $V_{(REG)}$ internally, open or H level makes Sleep mode                                                                                       |  |  |  |

| CHG    | 20    | Push-pull output charge FET gate drive                                                                                                                                  |  |  |  |

| ZVCHG  | 21    | The ZVCHG FET drive is connected here                                                                                                                                   |  |  |  |

| PACK   | 22    | PACK positive terminal and alternative power source                                                                                                                     |  |  |  |

| PMS    | 23    | 0-V charge configuration select pin, CHG terminal ON/OFF is determined by this pin.                                                                                     |  |  |  |

| OD     | 24    | NCH FET open drain output                                                                                                                                               |  |  |  |

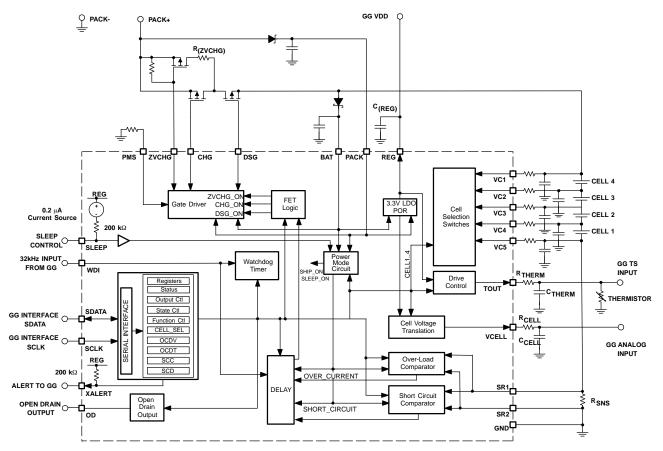

FUNCTIONAL BLOCK DIAGRAM

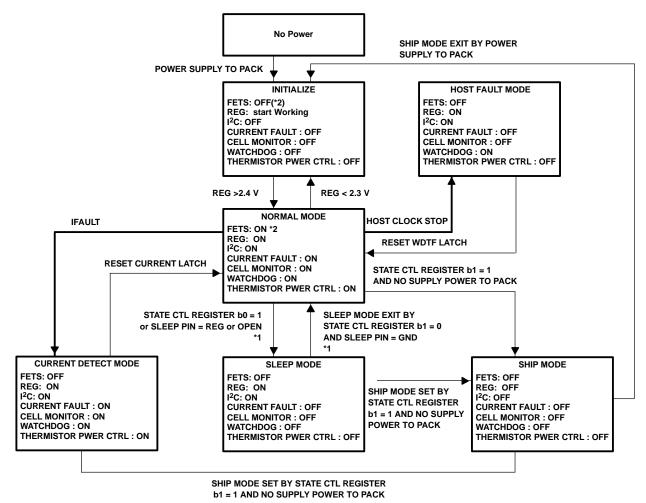

STATE DIAGRAM

Interrupt Request When

Enrering These States

\*1: Interrupt Request is Granted When Only External Sleep Pin Changes

\*2: When PMS connect to Pack, Default State of CHG FET is ON.

### FUNCTIONAL DESCRIPTION

#### Low-Dropout Regulator (REG)

The inputs for this regulator can be derived from the battery cell stack (BAT) or the pack positive terminal (PACK). The output is typically 3.3 V with the minimum output capacitance for stable operation is 4.7 µF and is also internally current limited. During normal operation, the regulator limits output current to typically 50 mA.

#### Initialization

The bq29312 internal control circuit is powered by the REG voltage, which it also monitors. When the voltage at REG falls below 2.3 V, the internal circuit turns off the FETs and disables all controllable functions, including the REG and TOUT outputs. REG does not start up unless a voltage above  $V_{(STARTUP)}$  is supplied to the PACK terminal. After the regulator has started, based on PACK voltage, it keeps operating through the BAT input, even if the PACK voltage is removed. If the BAT input is below the minimum operating range, then the bq29312 does not operate if the supply to the PACK input is removed. After start up, when the REG voltage is above 2.4 V, the bq29312 is in Normal mode.

The initial state of the CHG output depends on the PMS input. If PMS = PACK then CHG = ON however, if PMS = GND then CHG = OFF.

#### **Overload Detection**

The overload detection is used to detect abnormal currents in the discharge direction. This feature is used to protect the pass FETs, cells and any other inline components from excessive current conditions. The detection circuit also incorporates a blanking delay before driving the control for the pass FETs to the OFF state. The overload sense voltage is set in the OLV register, and delay time is set in the OLT register. The overload threshold can be programmed from 50 mV to 205 mV in 5-mV steps with the default being 50 mV and hysteresis of 10 mV.

#### **Short-Circuit Detection**

The short current circuit detection is used to detect abnormal current in either the charge or discharge direction. This safety feature is used to protect the pass FETs, cells, and any other inline components from excessive current conditions. The detection circuit also incorporates a blanking delay before driving the control for the pass FETs to the OFF state. The short- circuit thresholds and delay time are set in the SCC and SCD registers respectively where SCC is for charging and SCD is for discharge. The short-circuit threshold can be programmed from 100 mV to 475 mV in 25-mV steps with the default being 100 mV and hysteresis of 50 mV.

#### **Overload and Short-Circuit Delay**

The overload delay (default =1 ms) allows the system to momentarily accept a high current condition without disconnecting the supply to the load. The delay time can be increased via the OLT register, which can be programmed for a range of 1 ms to 31 ms with steps of 2 ms.

The short-circuit delay (default = 0  $\mu$ s) is programmable in the SCC and SCD registers. This register can be programmed from 0  $\mu$ s to 915  $\mu$ s with steps of 61  $\mu$ s.

#### **Overload and Short-Circuit Response**

When an overload or short-circuit fault is detected, the FETs are turned off. The STATUS (b0...b2) register reports the details of short-circuit (charge), short-circuit (discharge), and overload. The respective STATUS (b0...b2) bits are set to 1 and the XALERT output is triggered. This condition is latched until the CONTROL (b0) is set and then reset. If a FET is turned on via resetting CONTROL (b0) and the error condition is still present on the system, then the device reenters the protection response state.

#### Cell Voltage

The cell voltage is translated to allow a system host to measure individual series elements of the battery. The series element voltage is translated to a GND-based voltage equal to  $0.15 \pm 0.002$  of the series element voltage. This provides a range from 0 V to 4.5 V. The translation output is inversely proportional to the input using the following equation.

Where,  $V_{(CELL OUT)} = -K \times V_{(CELL IN)} + 0.975$  (V)

Programming CELL\_SEL (b1, b0) selects the individual series element. The CELL\_SEL (b3, b2) selects the voltage monitor mode, cell monitor, offset etc.

### Calibration of Cell Voltage Monitor Amplifier Gain

The cell voltage monitor amplifier has an offset and to increase accuracy this can be calibrated.

There are a couple of method by calibration circumstance.

The following procedure shows how to measure and calculate the offset and gain as one of example.

Step 1

- Set CAL1=1, CAL0=1, CELL1=0, CELL0=0, VMEN=1

- $V_{REF}$  is trimmed to 0.975 V within ±1%, measuring  $V_{REF}$  eliminates its error.

- Measure internal reference voltage V<sub>REF</sub> from VCELL directly.

- VREF=measured reference voltage

- Step 2

- Set CAL1=0, CAL0=0, CELL1=0, CELL0=0, VMEN=1

- The output voltage includes the offset and represented by:

$V_{O(4-5)} = V_{REF} + (1 + K) \times V_{OS} (V)$

Where K = CELL Scaling Factor

- V<sub>OS</sub> = Offset voltage at input of the internal operational-amplifier

- Step 3

- Set CAL1=1, CAL0=0, CELL1=0, CELL0=0, VMEN=1

- Measuring scaled REF voltage through VCELL amp.

- The output voltage includes the scale factor error and offset and is represented by:

$V_{(OUTR)} = V_{REF} + (1 + K) \times V_{OS} - K \times V_{REF} (V)$

- Step 4

- Calculate  $(V_{O(4-5)} V_{(OUTR})/V_{REF}$

- The result is the actual scaling factor,  $K_{(ACT)}$  and is represented by:

$K_{(ACT)} = (V_{O(4-5)} - V_{(OUTR)})/V_{REF} = (V_{REF} + (1 + K) \times V_{OS}) - (V_{REF} + (1 + K) \times V_{OS} - K \times V_{REF})/V_{REF} = K \times V_{REF}/V_{REF} = K$

- Step 5

- Calculate the actual offset value where:

$V_{OS(ACT)} = (V_{O(4-5)} - V_{REF})/(1 + K_{(ACT)})$

- Step 6

- Calibrated cell voltage is calculated by:

$VCn - VC(n+1) = \{V_{REF} + (1 + K_{(ACT)}) \times V_{OS(ACT)} - V_{(CELLOUT)}\}/K_{(ACT)} - \{V_{O(4-5)} - V_{(CELLOUT)}\}/K_{(ACT)}$

For improved measurement accuracy, V<sub>OS(ACT)</sub> for each cell voltage should be measured.

- Set CAL1=0, CAL0=0, CELL1=0, CELL0=1, VMEN=1

- Set CAL1=0, CAL0=0, CELL1=1, CELL0=0, VMEN=1

- Set CAL1=0, CAL0=0, CELL1=1, CELL0=1, VMEN=1

Measuring  $V_{O(3\text{-}4)}$  ,  $V_{O(2\text{-}3),}$   $V_{O(1\text{-}2),}$

- $VC4 VC5 = \{V_{O(4-5)} V(_{CELLOUT})\}/K_{(ACT)}$

- $VC3 VC4 = \{V_{O(3-4)} V_{(CELLOUT)}\}/K_{(ACT)}$

- $VC2 VC3 = \{V_{O(2-3)} V_{(CELLOUT)}\} / K_{(ACT)}$

- $VC1 VC2 = \{V_{O(1-2)} V_{(CELLOUT)}\}/K_{(ACT)}$

#### **Cell Balance Control**

The cell balance control allows a small bypass path to be controlled for any one series element. The purpose of this bypass path is to reduce the current into any one cell during charging to bring the series elements to the same voltage. Series resistors placed between the input pins and the positive series element nodes control the bypass current value. Individual series element selection is made using bits 4 through 7 of the CELL\_SEL register.

#### Thermistor Drive Circuit (TOUT)

The TOUT pin can be enabled to drive a thermistor from REG. The typical thermistor resistance is 10 k $\Omega$  at 25°C. The default-state is OFF to conserve power. The maximum output impedance is 100  $\Omega$ . TOUT is enabled in FUNCTION CTL Register (bit 5).

#### **Open Drain Drive Circuit (OD)**

The open drain output has 1-mA current source drive with a maximum output voltage of 25 V. The OD output is enabled or disabled by OUTPUT CTL Register (bit 4) and has a default state of OFF.

### XALERT (XALERT)

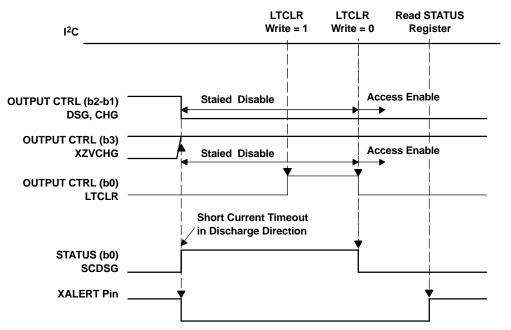

XALERT is driven low when an OL or SC current fault is detected, if the SLEEP pin changes state or a watchdog fault occurs. To clear XALERT, toggle (from 0, set to 1 then reset to 0) OUTPUT CTL (bit 0), then read the STATUS register.

#### Latch Clear (LTCLR)

When a current limit fault or watch dog timer fault occurs, the state is latched. To clear these faults, toggle (from 0, set 1 then reset to 0) LTCLR in the OUTPUT CTL register (bit 0).

Figure 1 is the LTCLR and XALERT clear example after sensing short-circuit.

#### Figure 1. LTCLR and XALERT Clear Example After Sensing Short LTCLR and XALER Clear Example

## 2-, 3-, or 4-Cell Configuration

In a 3-cell configuration, VC1 is shorted to VC2. In a 2-cell configuration, VC1 and VC2 are shorted to VC3.

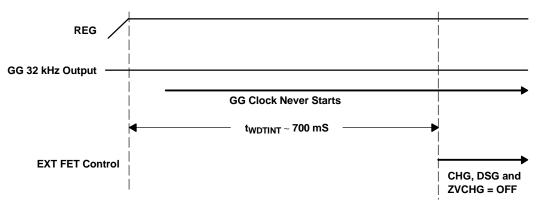

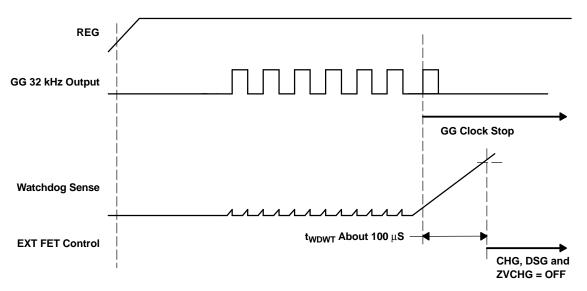

#### Watchdog Input (WDI)

The WDI input is required as a time base for delay timing when determining overload and short-circuit delay periods and is used as part of the system watchdog.

Initially the watchdog monitors the hosts oscillator start up, if there is no response from the host within 700 ms of the bq29312 reaching its minimum operating voltage, then the bq29312 turns both CHG, DSG and ZVCHG FETs OFF.

Once the watchdog has been started during this wake up period, it monitors the host for an oscillation stop condition, which is defined as a period of 100  $\mu$ s (typ) where no clock input is received. If an oscillator stop condition is identified, then the watchdog turns the CHG, DSG and ZVCHG FETs OFF. When the host clock oscillation is started, WDF is released, but the flag is latched until LTCLR is toggled.

Figure 3. Watchdog Timing Chart—WDI Fault After Startup

### DSG and CHG FET Driver Control

The bq29312 drives the DSG, CHG, and ZVCHG FET off if an OL or SC safety threshold is breached depending on the current direction. The host can force any FET on or off only if the bq29312 integrated protection control allows. The DSG and CHG FET drive gate-to-drain voltage is clamped to 15 V (typ).

The default-state of the CHG and DSG FET drive is off, when PMS = GND. A host can control the FET drive by programming OUTPUT CTL (b3...b1) where b1 is used to control the discharge FET, b2 is used to control the charge FET and b3 is used to control the ZVCHG FET. These controls are only valid when not in the initialized state. The CHG drive FET can be powered by PACK and the DSG FET can be powered by BAT.

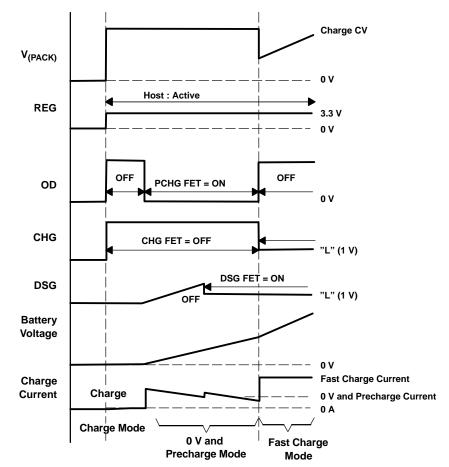

#### Precharge and 0 V Charging—Theory of Operation

The bq29312 supports both a charger that has a precharge mode and one that does not. The bq29312 also supports charging even when the battery falls to 0 V. Detail is described in the application section.

#### SLEEP Control Input (SLEEP)

The SLEEP input is pulled-up internally to REG. When SLEEP is pulled to REG, the bq29312 enters the SLEEP mode. The SLEEP mode disables all the FET outputs and the OL, SC and watchdog faults are also disabled. The RAM configuration is still valid on exit of the SLEEP mode. The host can force the bq29312 into SLEEP mode via register control also.

| ITENA                       |          | SLEEP                                       |                                                                                                    |

|-----------------------------|----------|---------------------------------------------|----------------------------------------------------------------------------------------------------|

| ITEM                        | FUNCTION | I <sup>2</sup> C READ/WRITE                 | EXIT SLEEP                                                                                         |

| I <sup>2</sup> C Read/Write | Active   |                                             |                                                                                                    |

| REG Output                  | Active   |                                             |                                                                                                    |

| External pin control:       |          |                                             |                                                                                                    |

| CHG, DSG, ZVCHG, TOUT, OD   |          |                                             |                                                                                                    |

| OC and SC protection:       |          |                                             |                                                                                                    |

| SCD, SCC and OCD            |          | Write is available,<br>but read is disabled | Last pre-sleep entry configuration is valid.(If change configuration, latest write data is valid.) |

| CELL Translation            | Disabled | but read is disabled                        |                                                                                                    |

| PACKOUT, VMEN               |          |                                             |                                                                                                    |

| Cell Balancing:             |          |                                             |                                                                                                    |

| CB[3:0]                     |          |                                             |                                                                                                    |

| Watchdog: WDDIS             |          |                                             |                                                                                                    |

#### Table 1. SLEEP Control Input

#### **Power Modes**

The bq29312 has three power modes, Normal, Sleep, and Ship. The following table outlines the operational functions during these power modes.

| POWER<br>MODE | TO ENTER POWER MODE                                             | TO EXIT POWER<br>MODE  | MODE DESCRIPTION                                                                                                                                                      |

|---------------|-----------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Normal        | SLEEP = GND and<br>STATE CTL( b0) = 0 and<br>STATE CTL( b1) = 0 |                        | The battery is in normal operation with protection, power management and battery monitoring functions available and operating.                                        |

|               |                                                                 |                        | The supply current of this mode varies as the host can enable and disable various power management features.                                                          |

| Sleep         | {SLEEP = REG (floating) or                                      | SLEEP = GND and        | All functions stop except LDO and I <sup>2</sup> C interface.                                                                                                         |

|               | STATE CTL( $b0$ ) = 1 } and<br>STATE CTL( $b1$ ) = 0            |                        | On entry to this mode, all registers are masked off keeping their state.                                                                                              |

|               |                                                                 |                        | The host controller can change the RAM registers via the I <sup>2</sup> C interface, but reading data is disabled until exit of Sleep mode.                           |

| Ship          | STATE CTL( b1) = 1<br>And supply at the PACK pin is<br>removed  | Supply voltage to PACK | The bq29312 is completely shut down as in the sleep mode. In addition the REG output is disabled, I <sup>2</sup> C interface is powered down and memory is not valid. |

#### Table 2. Power Modes

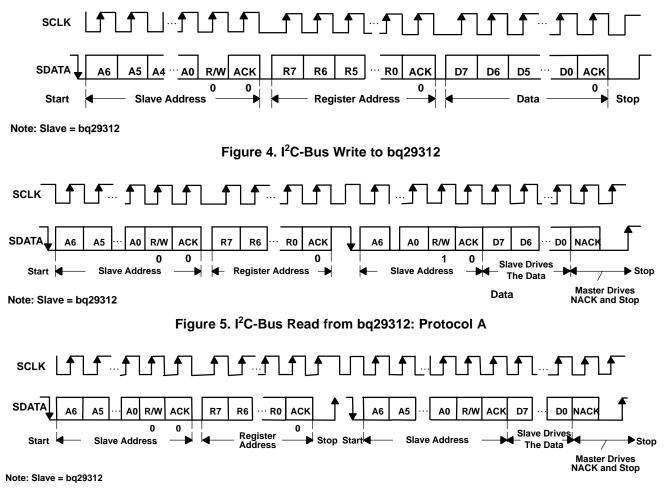

#### Communications

The I<sup>2</sup>C compatible serial communications provides read and write access to the bq29312 data area. The data is clocked via separate data (SDATA) and clock (SCLK) pins. The bq29312 acts as a slave device and does not generate clock pulses. Communication to the bq29312 is provided from GPIO pins or an I<sup>2</sup>C supporting port of a host system controller. The slave address for the bq29312 is 7 bits and the value is 0100 000 (0x20).

|                      | (MSB) I <sup>2</sup> C ADDRESS +R/W BIT |   |                                       |   |   |   | (LSB) |   |

|----------------------|-----------------------------------------|---|---------------------------------------|---|---|---|-------|---|

|                      | (MSB)                                   |   | I <sup>2</sup> C ADDRESS (0x20) (LSB) |   |   |   |       |   |

| Write <sup>(1)</sup> | 0                                       | 1 | 0                                     | 0 | 0 | 0 | 0     | 0 |

| Read                 | 0                                       | I | 0                                     | 0 | 0 | 0 | 0     | 1 |

(1) Bit 0: 0 = write, 1= read

The bq29312 does not have the following functions compatible with the I<sup>2</sup>C specification.

- The bq29312 is always regarded as a slave.

- The bq29312 does not return a NACK for an invalid register address.

- The bq29312 does not support the general code of the I<sup>2</sup>C specification, and therefore does not return an ACK.

- The bq29312 does not support the address auto increment, which allows continuous reading and writing.

- The bq29312 allows data to written or read from the same location without resending the location address.

### **Register Map**

The bq29312 has 9 addressable registers. These registers provide status, control, and configuration information for the battery protection system.

| NAME         | ADDR | TYPE | DESCRIPTION                                                                                 |

|--------------|------|------|---------------------------------------------------------------------------------------------|

| STATUS       | 0x00 | R    | Status register                                                                             |

| OUTPUT CTL   | 0x01 | R/W  | Output pin control from system host                                                         |

| STATE CTL    | 0x02 | R/W  | State control                                                                               |

| FUNCTION CTL | 0x03 | R/W  | Function control                                                                            |

| CELL _SEL    | 0x04 | R/W  | Battery cell select for cell translation and balance bypass and select mode for calibration |

| OLV          | 0x05 | R/W  | Overload threshold voltage                                                                  |

| OLT          | 0x06 | R/W  | Overload delay time                                                                         |

| SCC          | 0x07 | R/W  | Short-circuit current threshold voltage and delay for charge                                |

| SCD          | 0x08 | R/W  | Short-circuit current threshold voltage and delay for discharge                             |

#### Table 3. Addressable Registers

### STATUS : Status register

|   | STATUS REGISTER (0x00) |        |          |     |    |       |       |  |  |  |  |

|---|------------------------|--------|----------|-----|----|-------|-------|--|--|--|--|

| 7 | 6                      | 5      | 4        | 3   | 2  | 1     | 0     |  |  |  |  |

| 0 | 0                      | ZVCLMP | SLEEPDET | WDF | OL | SCCHG | SCDSG |  |  |  |  |

The STATUS register provides information about the current state of the bq29312. Reading the STATUS register clears the XALERT pin.

STATUS b0 (SCDSG): This bit indicates a short-circuit in the discharge direction.

0 = Current below the short-circuit threshold in the discharge direction (default).

1 = Current greater than or equal to the short-circuit threshold in the discharge direction.

STATUS b1 (SCCHG): This bit indicates a short-circuit in the charge direction.

0 = Current below the short-circuit threshold in the charge direction (default).

1 = Current greater than or equal to the short-circuit threshold in the charge direction.

STATUS b2 (OL): This bit indicates an overload condition.

0 = Current less than or equal to the overload threshold (default).

1 = Current greater than overload threshold.

STATUS b3 (WDF): This bit indicates a watchdog fault condition has occurred.

0 = 32 kHz oscillation is normal (default).

1 = 32 kHz oscillation stopped or not started and the watchdog has timed out.

STATUS b4 (SLEEPDET): This bit indicates the bq29312 is SLEEP mode.

0 = bq29312 is not SLEEP mode (default).

1 = bq29312 is SLEEP mode.

STATUS b5 (ZVCLMP): This bit indicates ZVCHG output is clamped.

0 = ZVCHG pin is not clamped (default).

1 = ZVCHG pin is clamped.

#### **OUTPUT CTL: Output Control Register**

|   | OUTPUT CTL REGISTER (0x01) |   |    |        |     |     |       |  |  |  |  |

|---|----------------------------|---|----|--------|-----|-----|-------|--|--|--|--|

| 7 | 6                          | 5 | 4  | 3      | 2   | 1   | 0     |  |  |  |  |

| 0 | 0                          | 0 | OD | XZVCHG | CHG | DSG | LTCLR |  |  |  |  |

The OUTPUT CTL register controls the outputs of the bq29312 and can be used to clear certain states.

OUTPUT CTL b0 (LTCLR): When a current limit fault or watchdog timer fault is latched, this bit releases the fault latch when toggled from 0 to 1 and back to 0 (default =0).

0 = (default)

0->1 ->0 clears the fault latches

OUTPUT CTL b1 (DSG): This bit controls the external discharge FET.

0 = discharge FET is off and is controlled by the system host (default).

1 = discharge FET is on and the bq29312 is in normal operating mode.

OUTPUT CTL b2 (CHG): This bit controls the external charge FET.

#### PMS=GND

0 = charge FET is off and is controlled by the system host (default).

1 = charge FET is on and the bq29312 is in normal operating mode.

PMS=PACK

0 = charge FET is off and is controlled by the system host.

1 = charge FET is on and the bq29312 is in normal operating mode (default).

OUTPUT CTL b3 (XZVCHG): This bit controls the external ZVCHG FET.

0 = ZVCHG FET is on and is controlled by the system host (default).

1 = ZVCHG FET is off and the bq29312 is in normal operating mode.

OUTPUT CTL b4 (OD): This bit enables or disables the OD output.

0 = OD is high impedance (default).

1 = OD output is active (GND).

#### STATE CTL: State Control Register

|                 | STATE CTL REGISTER (0x02) |   |   |   |       |      |       |  |  |  |  |

|-----------------|---------------------------|---|---|---|-------|------|-------|--|--|--|--|

| 7 6 5 4 3 2 1 0 |                           |   |   |   |       |      |       |  |  |  |  |

| 0               | 0                         | 0 | 0 | 0 | WDDIS | SHIP | SLEEP |  |  |  |  |

The STATE CTL register controls the state of the bq29312.

STATE CTL b0 (SLEEP): This bit is used to enter the sleep power mode.

0 = bq29312 exits sleep mode (default).

1 = bq29312 enters the sleep mode.

STATE CTL b1 (SHIP): This bit is used to enter the ship power mode when pack supply voltage is not applied.

0 = bq29312 in normal mode (default).

1 = bq29312 enters ship mode when pack voltage is removed.

STATE CTL b2 (WDDIS): This bit is used to enable or disable the watchdog timer function.

0 = enable clock monitoring (default).

1 = disable clock monitoring.

NOTE: Use caution when setting the WDDIS. For example, when the 32-kHz input fails, the overload and short-circuit delay timers no longer function because they use the same WDI input. If the WDI input clock stops, these current protections do not function. WDF should be enabled at any time for maximum safety. If the watchdog function is disabled, the CHG and DSG FETs should be turned off.

## **FUNCTION CTL: Function Control Register**

|   | FUNCTION CTL REGISTER (0x03) |      |      |      |     |         |      |  |  |  |  |

|---|------------------------------|------|------|------|-----|---------|------|--|--|--|--|

| 7 | 6                            | 5    | 4    | 3    | 2   | 1       | 0    |  |  |  |  |

| 0 | 0                            | TOUT | XSCD | SSCC | XOL | PACKOUT | VMEN |  |  |  |  |

The FUNCTION CTL register enables and disables functons of the bq29312.

FUNCTION CTL b0 (VMEN): This bit enables or disables the cell and battery voltage monitoring function.

0 = disable voltage monitoring (default). CELL output is pulled down to GND level.

1 = enable voltage monitoring.

FUNCTION CTL b1 (PACKOUT): This bit is used to translate the PACK input to the CELL pin when VMEN=1 The pack voltage is divided by 25 and is presented on CELL regardless of the CELL\_SEL register settings.

0 = disable PACK OUT (default).

1 = enable PACK OUT.

FUNCTION CTL b2 (XOL): This bit enables or disables the over current sense function.

0 = enable over load sense (default).

1 = disable over load sense.

FUNCTION CTL b3 (XSCC): This bit enables or disables the short current sense function of charging.

0 = enable short-circuit current sense in charge direction (default).

1 = disable short-circuit current sense in charge direction.

FUNCTION CTL b4 (XSCD): This bit enables or disables the short current sense function of discharge.

0 = enable short-circuit current sense in discharge direction (default).

1 = disable short-circuit current sense in discharge direction.

FUNCTION CTL b5 (TOUT): This bit controls the power to the thermistor.

0 = thermistor power is off (default).

1 = thermistor power is on.

SLUS546E-MARCH 2003-REVISED MARCH 2005

#### CELL SEL: Cell Select Register

|     | CELL_SEL REGISTER (0x04) |     |     |      |      |       |       |  |  |  |  |

|-----|--------------------------|-----|-----|------|------|-------|-------|--|--|--|--|

| 7   | 6                        | 5   | 4   | 3    | 2    | 1     | 0     |  |  |  |  |

| CB3 | CB2                      | CB1 | CB0 | CAL1 | CAL0 | CELL1 | CELL0 |  |  |  |  |

This register determines cell selection for voltage measurement and translation, cell balancing and the operational mode of the cell voltage monitoring.

CELL\_SEL b0-b1 (CELL0-CELL1): These two bits select the series cell for voltage measurement translation.

| CELL1 | CELL0 | SELECTED CELL                            |

|-------|-------|------------------------------------------|

| 0     | 0     | VC4–VC5, Bottom series element (Default) |

| 0     | 1     | VC4–VC3, Second lowest series element    |

| 1     | 0     | VC3–VC2, Second highest series element   |

| 1     | 1     | VC1–VC2, Top series element              |

CELL\_SEL b2-b3 (CAL1, CAL0): These bits determine the mode of the voltage monitor block.

| CAL1 | CAL0 | SELECTED MODE                                                                                |

|------|------|----------------------------------------------------------------------------------------------|

| 0    | 0    | Cell translation for selected cell (default)                                                 |

| 0    | 1    | Offset measurement for selected cell                                                         |

| 1    | 0    | Monitor the V <sub>REF</sub> value for gain calibration                                      |

| 1    | 1    | Monitor the $V_{REF}$ directly value for gain calibration, bypassing the translation circuit |

CELL\_SEL b4-b7 (CB0-CB3): These 4 bits select the series cell for cell balance bypass path.

CELL SEL b4 (CB0): This bit enables or disables the bottom series cell balance charge bypass path

0 = disable bottom series cell balance charge bypass path (default).

1 = enable bottom series cell balance charge bypass path.

CELL SEL b5 (CB1): This bit enables or disables the second lowest series cell balance charge bypass path. 0 = disable series cell balance charge bypass path (default).

1 = enable series cell balance charge bypass path.

CELL SEL b6 (CB2): This bit enables or disables the second highest cell balance charge bypass path.

- 0 = disable series cell balance charge bypass path (default).

- 1 = enable series cell balance charge bypass path.

CELL SEL b7 (CB3): This bit enables or disables the highest series cell balance charge bypass path.

0 = disable series cell balance charge bypass path (default).

1 = enable series cell balance charge bypass path.

## **OLV: Overload Voltage Threshold Register**

|   | OLV REGISTER (0x05) |   |      |      |      |      |      |  |  |  |  |

|---|---------------------|---|------|------|------|------|------|--|--|--|--|

| 7 | 6                   | 5 | 4    | 3    | 2    | 1    | 0    |  |  |  |  |

| 0 | 0                   | 0 | OLV4 | OLV3 | OLV2 | OLV1 | OLV0 |  |  |  |  |

OLV (b4-b0): These five bits select the value of the over load threshold with a default of 00000.

| OLV (b4–b0) configuration bits with corresponding voltage threshold |

|---------------------------------------------------------------------|

|---------------------------------------------------------------------|

| 00000 | 0.050 V | 01000 | 0.090 V | 10000 | 0.130 V | 11000 | 0.170 V |

|-------|---------|-------|---------|-------|---------|-------|---------|

| 00001 | 0.055 V | 01001 | 0.095 V | 10001 | 0.135 V | 11001 | 0.175 V |

| 00010 | 0.060 V | 01010 | 0.100 V | 10010 | 0.140 V | 11010 | 0.180 V |

| 00011 | 0.065 V | 01011 | 0.105 V | 10011 | 0.145 V | 11011 | 0.185 V |

| 00100 | 0.070 V | 01100 | 0.110 V | 10100 | 0.150 V | 11100 | 0.190 V |

| 00101 | 0.075 V | 01101 | 0.115 V | 10101 | 0.155 V | 11101 | 0.195 V |

| 00110 | 0.080 V | 01110 | 0.120 V | 10110 | 0.160 V | 11110 | 0.200 V |

| 00111 | 0.085 V | 01111 | 0.125 V | 10111 | 0.165 V | 11111 | 0.205 V |

#### **OLT: Overload Blanking Delay Time Register**

|   | OLT REGISTER (0x06) |   |   |      |      |      |      |  |  |  |  |  |

|---|---------------------|---|---|------|------|------|------|--|--|--|--|--|

| 7 | 6                   | 5 | 4 | 3    | 2    | 1    | 0    |  |  |  |  |  |

| 0 | 0                   | 0 | 0 | OLT3 | OLT2 | OLT1 | OLT0 |  |  |  |  |  |

OLT(b3-b0): These four bits select the value of the delay time for overload with a default of 0000.

OLT(b3-b0) configuration bits with corresponding delay time

| 0000 | 1 ms | 0100 | 9 ms  | 1000 | 17 ms | 1100 | 25 ms |

|------|------|------|-------|------|-------|------|-------|

| 0001 | 3 ms | 0101 | 11 ms | 1001 | 19 ms | 1101 | 27 ms |

| 0010 | 5 ms | 0110 | 13 ms | 1010 | 21 ms | 1110 | 29 ms |

| 0011 | 7 ms | 0111 | 15 ms | 1011 | 23 ms | 1111 | 31 ms |

### SCC: Short Circuit in Charge Configuration Register

| SCC REGISTER (0x07) |                                                 |  |  |  |  |  |  |  |  |  |

|---------------------|-------------------------------------------------|--|--|--|--|--|--|--|--|--|

| 7 6 5 4 3 2 1 0     |                                                 |  |  |  |  |  |  |  |  |  |

| SCCT3               | SCCT3 SCCT2 SCCT1 SCCT0 SCCV3 SCCV2 SCCV1 SCCV0 |  |  |  |  |  |  |  |  |  |

This register selects the short-circuit threshold voltage and delay for charge.

SCC(b3-b0) : These bits select the value of the short-circuit voltage threshold with 0000 as the default.

SCC(b3–b0) with corresponding SC threshold voltage

| 0000 | 0.100 V | 0100 | 0.200 V | 1000 | 0.300 V | 1100 | 0.400 V |

|------|---------|------|---------|------|---------|------|---------|

| 0001 | 0.125 V | 0101 | 0.225 V | 1001 | 0.325 V | 1101 | 0.425 V |

| 0010 | 0.150 V | 0110 | 0.250 V | 1010 | 0.350 V | 1110 | 0.450 V |

| 0011 | 0.175 V | 0111 | 0.275 V | 1011 | 0.375 V | 1111 | 0.475 V |

SCC(b7-b4): These bits select the value of the short-circuit delay time. Exceeding the short-circuit voltage threshold for longer than this period will turn off the corresponding CHG, DSG, and ZVCHG output. 0000 is the default.

| SCC(b7-b4 | ) with | corresponding | g SC dela | ly time |

|-----------|--------|---------------|-----------|---------|

|-----------|--------|---------------|-----------|---------|

| 0000 | 0 µs   | 0100 | 244 µs | 1000 | 488 µs | 1100 | 732 µs |

|------|--------|------|--------|------|--------|------|--------|

| 0001 | 61 µs  | 0101 | 305 µs | 1001 | 549 µs | 1101 | 793 µs |

| 0010 | 122 µs | 0110 | 366 µs | 1010 | 610 µs | 1110 | 854 μs |

| 0011 | 183 µs | 0111 | 427 µs | 1011 | 671 µs | 1111 | 915 µs |

### SCD: Short Circuit in Discharge Configuration Register

| SCD REGISTER (0x08)                             |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------|--|--|--|--|--|--|--|--|--|

| 7 6 5 4 3 2 1 0                                 |  |  |  |  |  |  |  |  |  |

| SCDT3 SCDT2 SCDT1 SCDT0 SCDV3 SCDV2 SCDV1 SCDV0 |  |  |  |  |  |  |  |  |  |

This register selects the short-circuit threshold voltage and delay for discharge.

SCD(b3-b0) with corresponding SC threshold voltage with 0000 as the default.

SCD(b3-b0): These bits select the value of the short-circuit voltage threshold

| 0000 | 0.10 V  | 0100 | 0.20 V  | 1000 | 0.30 V  | 1100 | 0.40 V  |

|------|---------|------|---------|------|---------|------|---------|

| 0001 | 0.125 V | 0101 | 0.225 V | 1001 | 0.325 V | 1101 | 0.425 V |

| 0010 | 0.150 V | 0110 | 0.250 V | 1010 | 0.350 V | 1110 | 0.450 V |

| 0011 | 0.175 V | 0111 | 0.275 V | 1011 | 0.375 V | 1111 | 0.475 V |

SCD(b7–b4): These bits select the value of the short-circuit delay time. Exceeding the short-circuit voltage threshold for longer than this period will turn off the corresponding CHG, DSG, and ZVCHG output as has 0000 as the default.

SCD(b7-b4) with corresponding SC delay time

| 0000 | 0 µs   | 0100 | 244 µs | 1000 | 488 µs | 1100 | 732 µs |

|------|--------|------|--------|------|--------|------|--------|

| 0001 | 61 µs  | 0101 | 305 µs | 1001 | 549 µs | 1101 | 793 µs |

| 0010 | 122 µs | 0110 | 366 µs | 1010 | 610 µs | 1110 | 854 µs |

| 0011 | 183 µs | 0111 | 427 µs | 1011 | 671 µs | 1111 | 915 µs |

### **APPLICATION INFORMATION**

#### Precharge and 0-V Charging—Theory of Operation

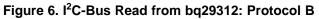

In order to charge, the charge FET (CHG-FET) must be turned on to create a current path. When the  $V_{(BAT)}$  is 0 V and CHG-FET = ON, the  $V_{(PACK)}$  is as low as the battery voltage. In this case, the supply voltage for the device is too low to operate. There are 3 possible configurations for this function and the bq29312 can be easily configured according to the application needs. The 3 modes are 0-V Charge FET Mode, Common FET Mode and Precharge FET Mode.

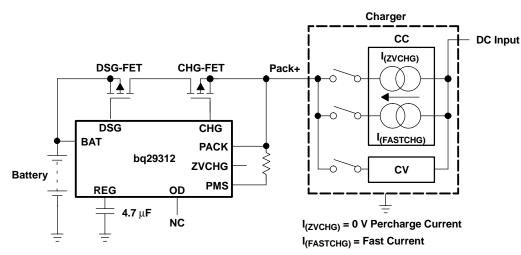

- 1. 0-V Charge FET Mode Dedicates a precharge current path using an additional FET (ZVCHG-FET) to sustain the PACK+ voltage level. The host charger is expected to provide a precharge function.

- 2. Common FET Mode Does not use a dedicated precharge FET. The charge FET (CHG-FET) is assured to be set to ON state as default. The charger is expected to provide a precharge function.

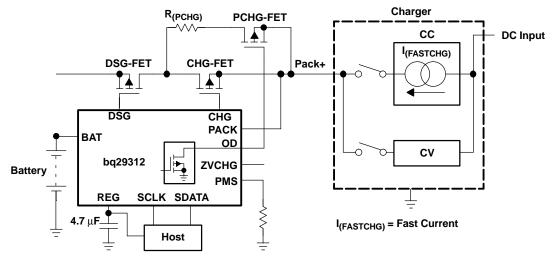

- Precharge FET Mode Dedicates a precharge current path using an additional open drain (OD) pin drive FET (PCHG-FET) FET to sustain the PACK+ voltage level. The charger does not provide any precharge function.

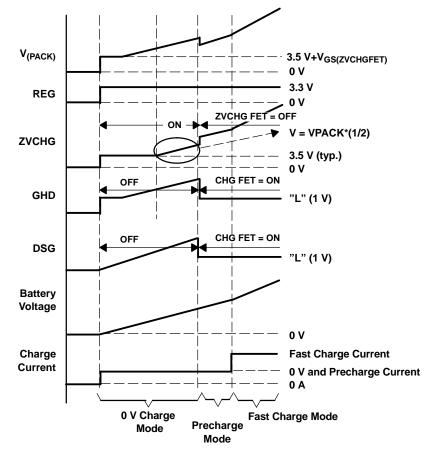

#### 0-V Charge FET Mode

In this mode, a dedicated precharge current path using an additional FET (ZVCHG-FET) is required to sustain a suitable PACK+ voltage level. The charger is expected to provide the precharge function in this mode where the precharge current level is suitable to charge cells below a set level, typically below 3 V per cell. When the lowest cell voltage rises above this level, then a fast charging current is applied by the charger.

The circuit diagram for this method is shown in Figure 7, showing how the additional FET is added in parallel with the charge FET (CHG-FET).

Figure 7. 0-V Charge FET Mode Circuit

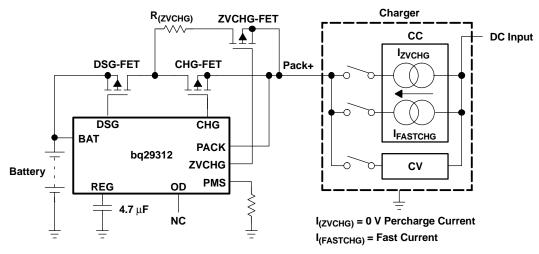

In order to pass 0 V or precharge current an appropriate gate-source voltage  $V_{(GS)}$ , for ZVCHG-FET must be applied. Here,  $V_{(PACK)}$  can be expressed in terms of  $V_{(GS)}$  as follows:

$V_{(PACK)} = V_{(ZVCHG)} + V_{(GS)}(ZVCHG-FET gate - source voltage)$

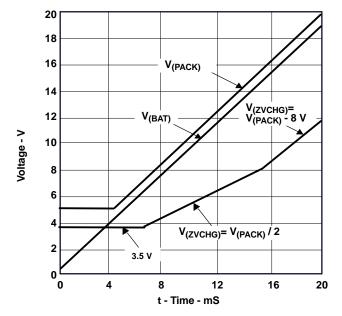

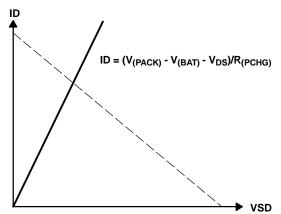

Figure 8. Drain Current vs Drain-Source Voltage Characteristics

In the bq29312, the initial state is for CHG-FET = OFF and ZVCHG-FET = ON with the V<sub>(ZVCHG)</sub> clamped at 3.5 V initially. Then the charger applies a constant current and raises V<sub>(PACK)</sub> high enough to pass the precharge current, point A. For example, if the V<sub>(GS)</sub> is 2 V at this point, V<sub>(PACK)</sub> is 3.5 V + 2 V = 5.5 V. Also, the ZVCHG-FET is used in its MOS saturation region at this point so that V<sub>(DS)</sub> is expressed as follows:

$V_{(PACK)} = V_{(BAT)} + V_F + V_{DS(ZVCHG-FET)}$