Dear customer

LAPIS Semiconductor Co., Ltd. ("LAPIS Semiconductor"), on the 1<sup>st</sup> day of October, 2020, implemented the incorporation-type company split (shinsetsu-bunkatsu) in which LAPIS established a new company, LAPIS Technology Co., Ltd. ("LAPIS Technology") and LAPIS Technology succeeded LAPIS Semiconductor's LSI business.

Therefore, all references to "LAPIS Semiconductor Co., Ltd.", "LAPIS Semiconductor" and/or "LAPIS" in this document shall be replaced with "LAPIS Technology Co., Ltd."

Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

LAPIS Technology Co., Ltd.

October 1, 2020

# **ML9475**

1/3 or 1/4 Duty, 40-Output LCD Driver

#### **GENERAL DESCRIPTION**

The ML9475 is an LCD driver for dynamic display. It has a function to switch between 1/3 and 1/4 duty. When 1/4 duty is selected, an LCD of up to 160 segments can be driven directly; when 1/3 duty is selected, an LCD of up to 120 segments can be driven directly.

#### **FEATURES**

• Logic power supply voltage : 2.7 to 3.6 V, 4.5 to 5.5 V

Driver power supply voltage

Operating temperature

3.5 to 5.5 V

-40 to +105°C

• 40 segment outputs

1/4 duty : Up to 160 segments can be displayed. 1/3 duty : Up to 120 segments can be displayed.

• Serially interfaces with the CPU using the three signal lines of LOAD, DATA\_IN, and CLOCK

• Built-in RC oscillator circuit for LCD AC drive (the CLKSEL pin allows selecting an external clock input)

• Built-in voltage-dividing resistor for bias voltage generation

• Package : 56-pin plastic QFP (QFP56-P-910-0.65-2K)

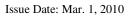

# **BLOCK DIAGRAM**

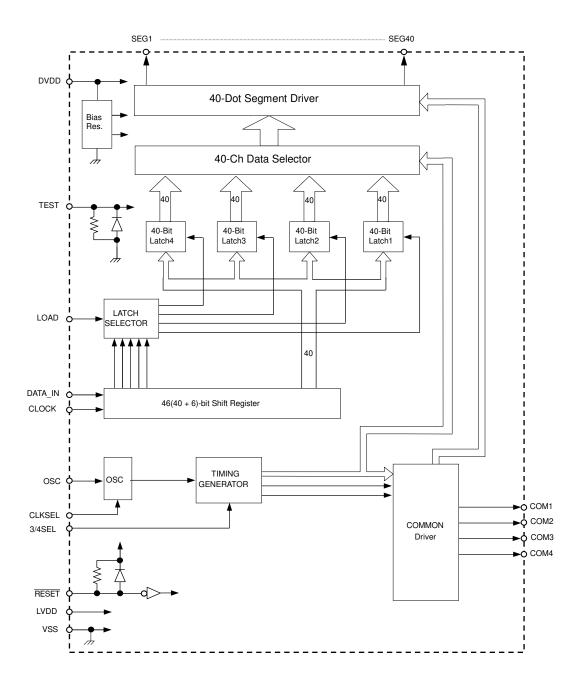

# PIN CONFIGURATION (TOP VIEW)

56-Pin Plastic QFP

# PIN DESCRIPTION

| Symbol                       | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

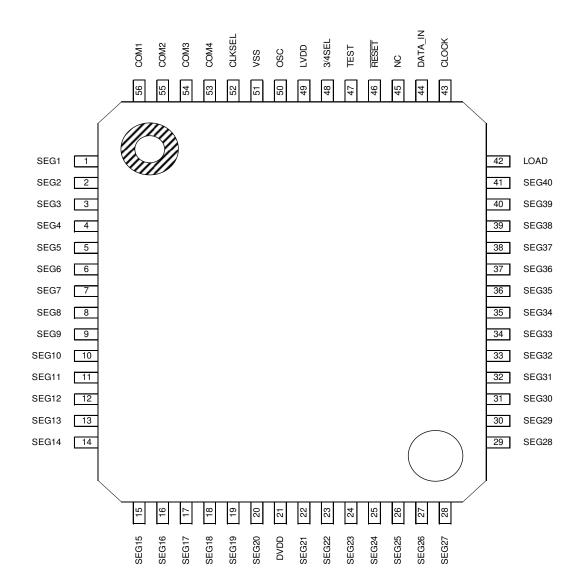

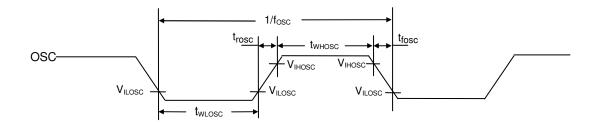

| OSC                          | I/O | Pin for oscillation. Has a Schmitt circuit built in. An oscillator circuit can be configured by connecting one external resistor and one external capacitor. Since an oscillator circuit is susceptible to external noise, make the wiring between this pin and external components as short as possible. An external clock input can be selected by CLKSEL. The relationship between oscillation frequency $f_{OSC}$ and frame frequency $f_{FRM}$ is: $f_{FRM} = f_{OSC}/24^{(*1)}$ |

| DATA_IN                      | I   | Serial data input pin. Has a Schmitt circuit built in. The LCD display is turned on when the input data signal is at a "H" level and turned off when the input data signal is at a "L" level.                                                                                                                                                                                                                                                                                         |

| CLOCK                        | I   | Shift clock input pin. Has a Schmitt circuit built in.  Data to the DATA_IN pin is shifted in sync with the rising edges of the shift clock pulses.                                                                                                                                                                                                                                                                                                                                   |

| LOAD                         | I   | Load pulse input pin. Has a Schmitt circuit built in. Used to transfer serially input data to the display latch or write commands.                                                                                                                                                                                                                                                                                                                                                    |

| TEST                         | ı   | IC test pin. Has a pull-down resistor built in. Leave this pin open or connect it to VSS when not used.                                                                                                                                                                                                                                                                                                                                                                               |

| CLKSEL                       | ı   | OSC pin input switching pin.  When using the built-in oscillator circuit, set this pin to a "L" level; when inputting an external clock, set this pin to a "H" level. While this pin is at a "H" level, the oscillator circuit connected is disabled.                                                                                                                                                                                                                                 |

| 3/4SEL                       | ı   | 1/3- or 1/4-duty switching input pin. When "H" level is input, 1/3 duty is selected and when "L" level is input, 1/4 duty is selected.                                                                                                                                                                                                                                                                                                                                                |

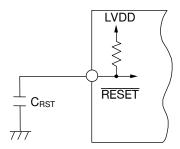

| RESET                        | I   | Reset signal input pin for initializing the IC. Has a Schmitt circuit built in. This pin is enabled by setting it to "L" level. This pin has a built-in pull-up resistor. Normally, this pin, when connected with an external capacitor, performs power-on reset. (*2)                                                                                                                                                                                                                |

| COM1<br>COM2<br>COM3<br>COM4 | 0   | Output pins for LCD display. Connect to the common pins of the LCD panel.  - When 1/3 duty is selected: Common signals are outputted through the COM1, COM2, and COM3 pins. Leave the COM4 pin open.  - When 1/4 duty is selected: Common signals are outputted through the COM1, COM2, COM3, and COM4 pins.                                                                                                                                                                          |

| SEG1 to SEG40                | 0   | Output pins for LCD display. Connect to the segment pins of the LCD panel. For the relationship between each output of these pins and data, see the section on "Data Structure."                                                                                                                                                                                                                                                                                                      |

| LVDD                         | _   | Logic power supply pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DVDD                         | _   | LCD driver power supply pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VSS                          | _   | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

# \*1: Oscillator circuit configuration

# \*2: Reset circuit configuration

#### ABSOLUTE MAXIMUM RATINGS

| Parameter            | Symbol           | Condition  | Rating           | Unit |

|----------------------|------------------|------------|------------------|------|

| Power supply voltage | LVDD, DVDD       | Ta = 25°C  | -0.3 to +6.5     | V    |

| Input voltage        | Vı               | Ta = 25°C  | -0.3 to LVDD+0.3 | V    |

| Power dissipation    | P <sub>D</sub>   | Ta ≤ 105°C | 350              | mW   |

| Output current       | I <sub>O</sub>   | Ta = 25°C  | -2.0 to +2.0     | mA   |

| Storage temperature  | T <sub>STG</sub> | _          | -55 to +150      | °C   |

#### RECOMMENDED OPERATING CONDITIONS

| Parameter                  | Symbol | Condition | Range                  | Unit |

|----------------------------|--------|-----------|------------------------|------|

| Logic power supply voltage | LVDD   | VSS= 0 V  | 2.7 to 3.6, 4.5 to 5.5 | V    |

| LCD drive voltage          | DVDD   | VSS= 0 V  | 3.5 to 5.5             | V    |

| CLOCK frequency            | fcp    | _         | 0.01 to 2              | MHz  |

| Operating temperature      | Ta     | _         | -40 to +105            | °C   |

Recommended setting range for external parts (for oscillator circuit)

(LVDD = 4.5 to 5.5 V)

| Parameter            | Symbol           | Condition | Min. | Max.  | Unit |

|----------------------|------------------|-----------|------|-------|------|

| Oscillator resistor  | Ro               | _         | 20   | 82    | kΩ   |

| Oscillator capacitor | Co               | _         | 0.01 | 0.047 | μF   |

| Frame frequency      | f <sub>FRM</sub> | _         | 14.6 | 451.0 | Hz   |

The relationship between external oscillator resistor value, external oscillator capacitor value, and frame frequency is as follows:

$fFRM = f_{OSC} / 24$

$f_{OSC} = 1 \ / \ (device \ coefficient \times external \ oscillator \ resistor \ value \ R_O \times external \ oscillator \ capacitor \ value \ C_O)$  Device coefficient =  $0.6 \pm 23\%$

(LVDD = 2.7 to 3.6 V)

| Parameter            | Symbol           | Condition | Min. | Max.  | Unit |

|----------------------|------------------|-----------|------|-------|------|

| Oscillator resistor  | Ro               | _         | 20   | 82    | kΩ   |

| Oscillator capacitor | Co               | _         | 0.01 | 0.047 | μF   |

| Frame frequency      | f <sub>FRM</sub> | _         | 14.6 | 451.0 | Hz   |

The relationship between external oscillator resistor value, external oscillator capacitor value, and frame frequency is as follows:

$fFRM = f_{OSC} / 24$

$f_{OSC} = 1 \ / \ (device \ coefficient \times external \ oscillator \ resistor \ value \ R_O \times external \ oscillator \ capacitor \ value \ C_O)$  Device coefficient =  $0.6 \pm 23\%$

### **ELECTRICAL CHARACTERISTICS**

#### **DC Characteristics**

$(LVDD = 2.7 \text{ to } 3.6 \text{ V}, 4.5 \text{ to } 5.5 \text{ V}, DVDD = 3.5 \text{ to } 5.5, Ta = -40 \text{ to } +105^{\circ}C)$

|                       | •                  | (LVDD = 2.7)         | 10 3.6 V, 4.5 10 5.5   | V, DVDD = 3.5 10 | 5.5, ra = | = <del>40 (0 + 103 C)</del> |  |

|-----------------------|--------------------|----------------------|------------------------|------------------|-----------|-----------------------------|--|

| Parameter             | Symbol             | Condition            | Min.                   | Max.             | Unit      | Applicable pin              |  |

|                       | V                  | LVDD = 4.5 to 5.5V   | 0.8LVDD                |                  |           | *1                          |  |

|                       | $V_{IH}$           | LVDD = 2.7 to 3.6V   | 0.85LVDD               |                  |           | "1                          |  |

| «1 l» ·               |                    | LVDD = 4.5 to 5.5V   |                        | 1./55            | .,        |                             |  |

| "H" input voltage     | ١.,                | CLKSEL = "H"         | 0.8LVDD                | LVDD             | V         |                             |  |

|                       | V <sub>IHOSC</sub> | LVDD = 2.7 to 3.6V   | 0.051.1/55             |                  |           | OSC                         |  |

|                       |                    | CLKSEL = "H"         | 0.85LVDD               |                  |           |                             |  |

|                       | .,                 | LVDD = 4.5 to 5.5V   |                        | 0.2LVDD          |           | **                          |  |

|                       | $V_{IL}$           | LVDD = 2.7 to 3.6V   |                        | 0.15LVDD         |           | *1                          |  |

|                       |                    | LVDD = 4.5 to 5.5V   | _                      |                  |           |                             |  |

| "L" input voltage     | .,                 | CLKSEL = "H"         | 0                      | 0.2LVDD          | V         |                             |  |

|                       | V <sub>ILOSC</sub> | LVDD = 2.7 to 3.6V   |                        |                  |           | OSC                         |  |

|                       |                    | CLKSEL = "H"         |                        | 0.15LVDD         |           |                             |  |

|                       | I <sub>IH1</sub>   | $V_I = LVDD$         | _                      | 1                | μA        | *2                          |  |

| "H" input current     |                    | $V_I = LVDD$         |                        | _                |           | 000                         |  |

|                       | I <sub>IHOSC</sub> | CLKSEL = "H"         | _                      | 1                | μΑ        | OSC                         |  |

|                       | I <sub>IL1</sub>   | $V_I = 0V$           | -1                     | _                | μΑ        | *2                          |  |

|                       | I <sub>IL2</sub>   | LVDD = 5V            | 0.000                  | 0.045            | mA        |                             |  |

|                       |                    | $V_I = 0V$           | -0.009                 | -0.045           |           | RESET                       |  |

| "L" input current     |                    | LVDD = 3V            | -0.004                 | -0.030           | mA        | NESET                       |  |

|                       |                    | $V_I = 0V$           | -0.004                 |                  |           |                             |  |

|                       |                    | $V_I = 0V$           | -1                     |                  |           | OSC                         |  |

|                       | I <sub>ILOSC</sub> | CLKSEL = "H"         | -1                     | _                | μΑ        | 030                         |  |

|                       | V <sub>OS0</sub>   | DVDD = 4.5V          | DVDD = 4.5V DVDD - 0.8 |                  | V         |                             |  |

|                       |                    | $I_0 = -10 \mu A$    | DVDD = 0.6             | _                | V         |                             |  |

|                       | V <sub>OS1</sub>   | DVDD = 4.5V          | 2/3DVDD - 0.8          | 2/3DVDD + 0.8    | ٧         |                             |  |

| Segment output        |                    | $I_O = \pm 10 \mu A$ | 2/30 000 - 0.8         | 2/30 000 + 0.8   | V         | SEG1 to                     |  |

| voltage               | V <sub>OS2</sub>   | DVDD = 4.5V          | 1/3DVDD - 0.8          | 1/3DVDD + 0.8    | V         | SEG40                       |  |

|                       | V OS2              | $I_O = \pm 10 \mu A$ | 1/30 000 - 0.0         | 1/30 000 + 0.0   | ٧         |                             |  |

|                       | V <sub>OS3</sub>   | DVDD = 4.5V          |                        | 0.8              | ٧         |                             |  |

|                       | V OS3              | $I_0 = 10 \mu A$     | _                      | 0.0              | ٧         |                             |  |

|                       | V <sub>OC0</sub>   | DVDD = 4.5V          | DVDD - 0.77            |                  | V         |                             |  |

| Common output voltage | A OC0              | $I_0 = -10 \mu A$    |                        | _                | V         |                             |  |

|                       | V <sub>OC1</sub>   | DVDD = 4.5V          | 2/3DVDD -              | 2/3DVDD+0.77     | V         |                             |  |

|                       | <b>V</b> OC1       | $I_O = \pm 10 \mu A$ | 0.77                   | 2/300 000 000 17 | V         | COM1 to<br>COM4             |  |

|                       | V <sub>OC2</sub>   | DVDD = 4.5V          | 1/3DVDD —              | 1/3DVDD+0.77     | V         |                             |  |

|                       | <b>V</b> OG2       | $I_O = \pm 10 \mu A$ | 0.77                   | 1/300 000 000 17 | ٧         |                             |  |

|                       | V <sub>OC3</sub>   | DVDD = 4.5V          | _                      | 0.77             | V         |                             |  |

|                       |                    | $I_O = 10 \mu A$     |                        | 0.77             | •         |                             |  |

| Dynamic supply        | $I_{DVDD+}I_{L}$   | *3                   | _                      | 0.5              | mA        | LVDD,                       |  |

| current               | VDD                | J                    | _                      | 0.5              | шл        | DVDD                        |  |

<sup>\*1</sup> CLOCK, LOAD, DATA\_IN, RESET, 3/4SEL, and CLKSEL

<sup>\*2</sup> CLOCK, LOAD, DATA\_IN, 3/4SEL, and CLKSEL

<sup>\*3</sup>  $C_0 = 0.022 \,\mu\text{F}, \, R_0 = 33 \,\text{k}\Omega, \, \text{no load}$

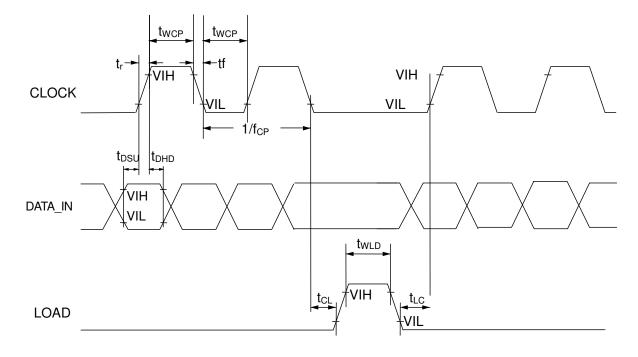

# **Switching Characteristics (Serial Interface)**

$(LVDD = 2.7 \text{ to } 3.6 \text{ V}, 4.5 \text{ to } 5.5 \text{ V}, DVDD = 3.5 \text{ to } 5.5 \text{ V}, Ta = -40 \text{ to } +105^{\circ}C)$

| Parameter               | Symbol                          | Condition    | Min. | Max. | Unit |

|-------------------------|---------------------------------|--------------|------|------|------|

| Clock frequency         | f <sub>CP</sub>                 | _            | 0.01 | 2.0  | MHz  |

| Clock pulse width       | twcp                            | _            | 70   | _    | ns   |

| Rise time, Fall time *4 | t <sub>r</sub> , t <sub>f</sub> | _            | _    | 3    | μS   |

| Data setup time         | t <sub>DSU</sub>                | _            | 50   | _    | ns   |

| Data hold time          | t <sub>DHD</sub>                | _            | 50   | _    | ns   |

| Load pulse width        | t <sub>WLD</sub>                | _            | 100  | _    | ns   |

| Clock to load time      | t <sub>CL</sub>                 | <del>_</del> | 100  | _    | ns   |

| Load to clock time      | t <sub>LC</sub>                 | _            | 100  | _    | ns   |

# \*4 Applied to CLOCK pin

# **Switching Characteristics (External Clock Input to OSC)**

$(LVDD = 2.7 \text{ to } 3.6 \text{ V}, 4.5 \text{ to } 5.5 \text{ V}, DVDD = 3.5 \text{ to } 5.5 \text{ V}, Ta = -40 \text{ to } +105^{\circ}C)$

| Parameter                   | Symbol Condition     |              | Min. | Max. | Unit |

|-----------------------------|----------------------|--------------|------|------|------|

| OSC input frequency         | f <sub>osc</sub>     | CLKSEL = "H" | 0.5  | 10   | kHz  |

| OSC rise time, fall time *5 | $t_{rosc}, t_{fOSC}$ | CLKSEL = "H" | _    | 1    | μS   |

| OSC "H" period              | t <sub>whosc</sub>   | CLKSEL = "H" | 4    | _    | μS   |

| OSC "L" period              | twLosc               | CLKSEL = "H" | 4    | _    | μS   |

# \*5 Applied to OSC pin

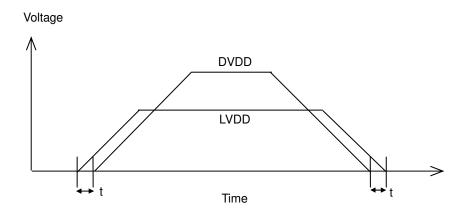

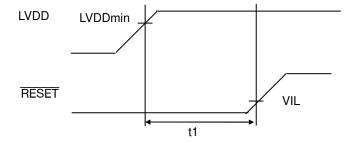

#### **POWER-ON/OFF TIMING**

If LVDD is in the range of 0 V to LVDDmin, make sure that LVDD  $\geq$  DVDD and t  $\geq$  0[ns] are satisfied. When performing power-on reset with a capacitor connected to the  $\overline{RESET}$  pin, be careful about the relationship between the capacitance value and the rise time of the power supply.

#### **INITIALIZATION TIMING**

Drive the  $\overline{RESET}$  pin Low and hold it Low under the condition "t1  $\geq$  0[ns]" until LVDD reaches LVDDmin.

The value of the current of the pull-up resistor is specified for  $\overline{RESET}$  pin.

The customer needs to select an external capacitor that meets the timing requirements shown above.

#### **FUNCTIONAL DESCRIPTION**

#### **Description of Operation**

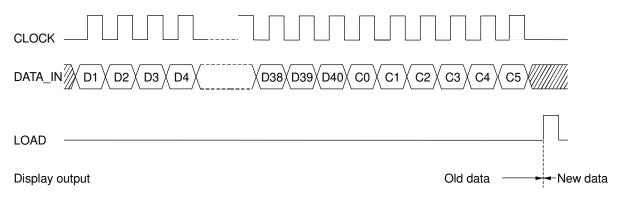

#### • Display data input

As described in the section on "Data Structure," display data consists of a data field, which corresponds to the LCD segments ON and OFF, and a command field, which indicates the input of display data.

Set a value in each of bits C0 and C1 in the command field according to the common output that corresponds to the display data, and set a display data input command in the remaining four bits.

Data that has been input to the DATA\_IN pin is loaded into the shift register on the rising edges of the CLOCK pulses, transferred to the display data latch during the "H" level period of the LOAD pulse, and then output via the segment driver.

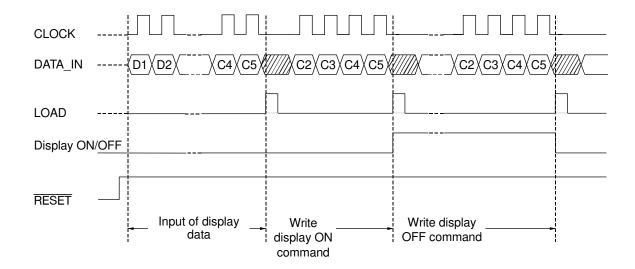

#### • Display ON, display OFF

Display goes off when power-on reset is executed; therefore, to turn display on, write the display ON command (F5).

The display OFF command (F4) is a command that makes all segments go off. By writing the display OFF command, the segments go off irrespective of display data.

The display ON command (F5) is a command that clears a display off state. By writing the display ON command, display goes back to the previous state.

### **List of Commands**

| Command name | C5 | C4 | C3 | C2 | C1 | C0              | Description                              |

|--------------|----|----|----|----|----|-----------------|------------------------------------------|

| F0           | 0  | 0  | 0  | 0  | ×  | ×               | Disabled                                 |

| F0'          | 0  | 0  | 0  | 1  | ×  | ×               | Disabled                                 |

| F1           | 0  | 0  | 1  | 0  | 0  | 0               | Display data input (corresponds to COM1) |

|              |    |    |    |    |    | 1               | Display data input (corresponds to COM2) |

|              |    |    |    |    | 1  | 0               | Display data input (corresponds to COM3) |

|              |    |    |    |    |    | 1               | Display data input (corresponds to COM4) |

| F2           | 0  | 1  | 0  | ×  | ×  | ×               | Disabled                                 |

| F3           | 0  | 1  | 1  | 0  | 0  | 0               | Disabled                                 |

|              |    |    |    |    |    | 1 Disabled      |                                          |

|              |    |    |    |    | 1  | 0 Disabled      |                                          |

|              |    |    |    |    |    | 1               | Disabled                                 |

| F3'          | 0  | 1  | 1  | 1  | ×  | ×               | Disabled                                 |

| F4           | 1  | 0  | 1  | 0  | ×  | × × Display OFF |                                          |

| F5           | 1  | 0  | 1  | 1  | ×  | × × Display ON  |                                          |

| F6           | 1  | 1  | 0  | ×  | ×  | ×               | Disabled                                 |

| F7           | 1  | 0  | 0  | ×  | ×  | ×               | Disabled                                 |

| F8           | 1  | 1  | 1  | ×  | ×  | ×               | Disabled                                 |

#### ×: Don't care

If a "Disabled" command is executed, no transfer is carried out from the shift register to the latch; however, data within the shift register will be rewritten. To transfer correct data to the latch, it is necessary to transfer data again using the F1 command.

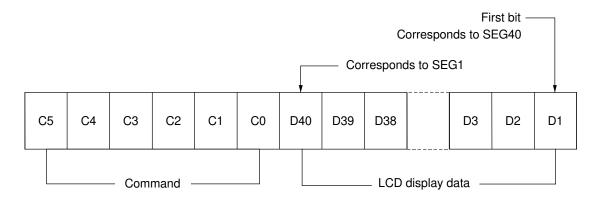

#### **Data Structure**

[Input data]

- Note 1: The setting of command F4 or F5 becomes enabled by inputting only the four bits of C2 to C5. (No need to input D1 to D40, C0, or C1.)

- Note 2: If any dummy bits are required because of the transfer bit count, add them before the first bit.

- Note 3: Command execution depends on the value of bits C5 to C0 stored immediately before LOAD goes to a "H" level.

# **Common and Segment Output Waveforms**

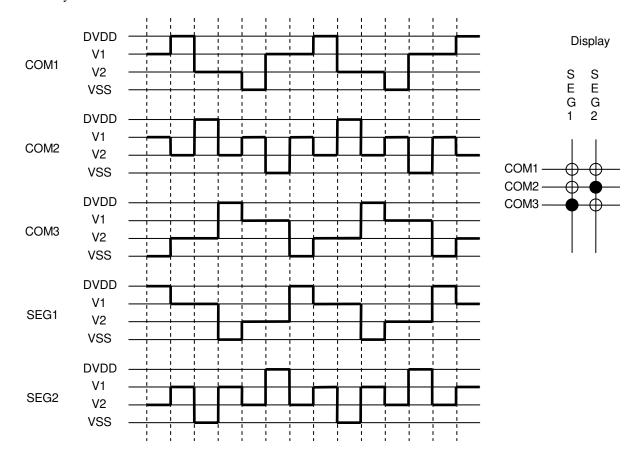

### • 1/3 duty

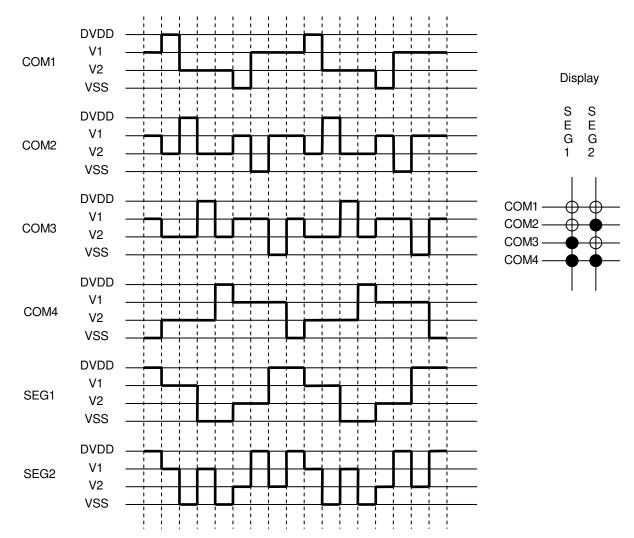

### • 1/4 duty

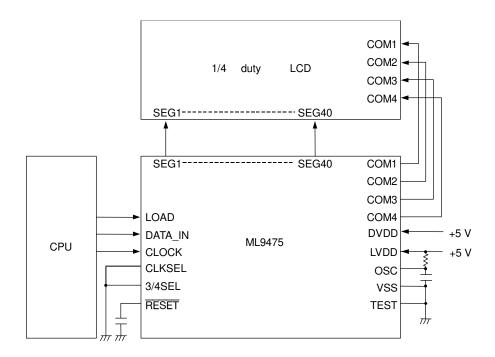

# APPLICATION CIRCUIT

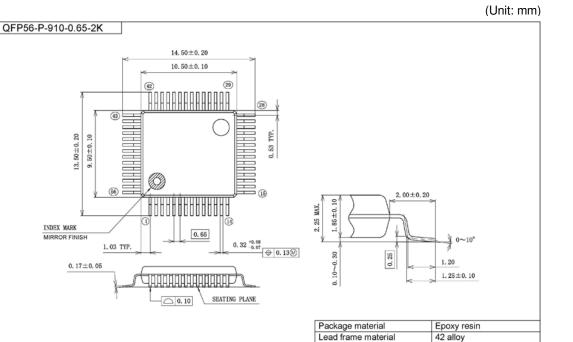

#### PACKAGE DIMENSIONS

Lead finish

Pin treatment Package weight (g)

Rev. No./Last Revised

Sn-2Bi (Bi 2% typ.) Solder plating (≥5µm)

0.43 TYP.

1/Sep. 25, 2007

Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact ROHM's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

# **REVISION HISTORY**

|              |              | F                   | Page               |                 |

|--------------|--------------|---------------------|--------------------|-----------------|

| Document No. | Date         | Previous<br>Edition | Current<br>Edition | Description     |

| FEDL9475-01  | Mar. 1, 2010 | _                   | -                  | Final edition 1 |

#### **NOTICE**

No copying or reproduction of this document, in part or in whole, is permitted without the consent of LAPIS Semiconductor Co., Ltd.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing LAPIS Semiconductor's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from LAPIS Semiconductor upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, LAPIS Semiconductor shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. LAPIS Semiconductor does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by LAPIS Semiconductor and other parties. LAPIS Semiconductor shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While LAPIS Semiconductor always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. LAPIS Semiconductor shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). LAPIS Semiconductor shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Copyright 2010 - 2011 LAPIS Semiconductor Co., Ltd.