### **General Description**

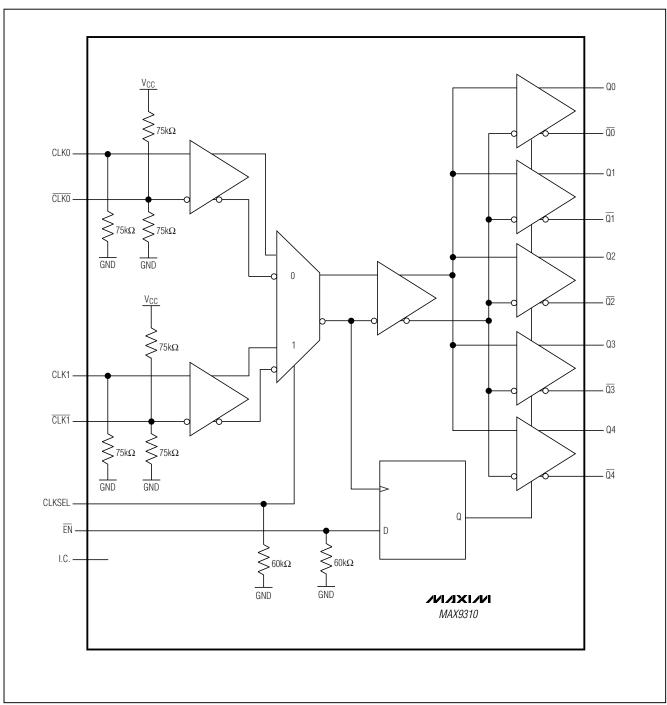

The MAX9310 is a fast, low-skew 1:5 differential driver with selectable LVPECL/HSTL inputs and LVDS outputs, designed for clock distribution applications. This device features an ultra-low propagation delay of 345ps with 45.5mA of supply current.

The MAX9310 operates from a 2.375V to 2.625V power supply for use in 2.5V systems. A 2:1 input multiplexer is used to select one of two differential inputs. The input selection is controlled through the CLKSEL pin. This device also features a synchronous enable function.

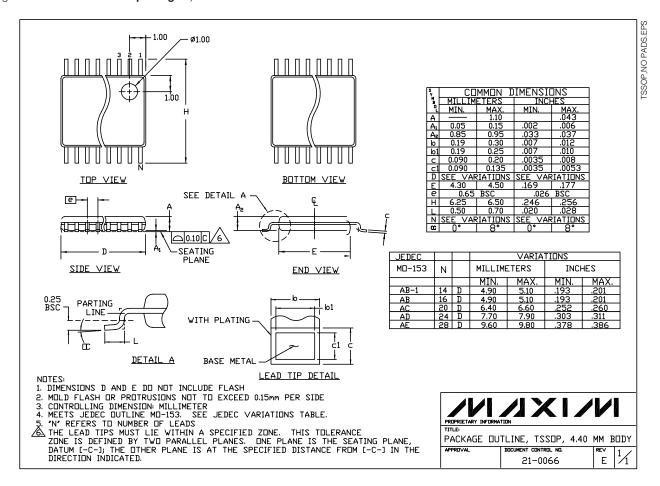

The MAX9310 is offered in a space-saving 20-pin TSSOP package and operates over the extended temperature range from -40°C to +85°C.

### **Applications**

Data and Clock Drivers and Buffers Central-Office Backplane Clock Distribution **DSLAM Base Stations** ATF

## **Features**

- ♦ Guaranteed 1.0GHz Operating Frequency

- ♦ 8ps Output-to-Output Skew

- ♦ 345ps Propagation Delay

- ♦ Accepts LVPECL and Differential HSTL Inputs

- ♦ Synchronous Output Enable/Disable

- **♦ Two Selectable Differential Inputs**

- ♦ 2.375V to 2.625V Supply Voltage

- ♦ ESD Protection: ±2kV (Human Body Model)

- ♦ Input Bias Resistors Drive Output Low for Open Inputs

### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX9310EUP | -40°C to +85°C | 20 TSSOP    |

Functional diagram appears at end of data sheet.

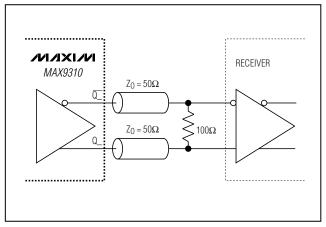

### **Typical Application Circuit**

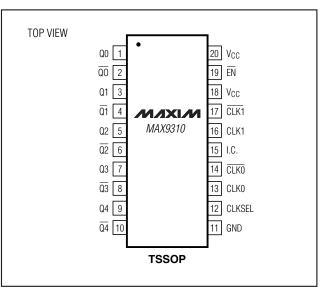

## Pin Configuration

NIXIN

Maxim Integrated Products 1

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND0.3V to +4.1V                                                                     |

|---------------------------------------------------------------------------------------------------------|

| $\overline{\text{EN}}$ , CLKSEL, CLK_, $\overline{\text{CLK}}$ , to GND0.3V to (V <sub>CC</sub> + 0.3V) |

| CLK_ to $\overline{\text{CLK}}$                                                                         |

| Continuous Output Current24mA                                                                           |

| Surge Output Current50mA                                                                                |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                                                   |

| Single-Layer PC Board                                                                                   |

| 20-Pin TSSOP (derate 7.69mW/°C above +70°C)615mW                                                        |

| Multilayer PC Board                                                                                     |

| 20-Pin TSSOP (derate 11mW/°C above +70°C)879mW                                                          |

| Junction-to-Ambient Thermal Resistance in Still Air                                                     |

| Single-Layer PC Board                                                                                   |

| 20-Pin TSSOP+130°C/W                                                                                    |

| Multilayer PC Board<br>20-Pin TSSOP<br>Junction-to-Ambient Thermal Resistance with | ·              |

|------------------------------------------------------------------------------------|----------------|

| Airflow Single-Layer PC board                                                      |                |

| 20-Pin TSSOP                                                                       | +96°C/W        |

| Junction-to-Case Thermal Resistance                                                |                |

| 20-Pin TSSOP                                                                       | +20°C/W        |

| Operating Temperature Range                                                        | 40°C to +85°C  |

| Junction Temperature                                                               | +150°C         |

| Storage Temperature Range                                                          | 65°C to +150°C |

| ESD Protection                                                                     |                |

| Human Body Model (inputs and outputs)                                              | ±2kV           |

| Lead Temperature (soldering, 10s)                                                  |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS

$(V_{CC}$  - GND = 2.375V to 2.625V, outputs terminated with 100 $\Omega$  ±1%, unless otherwise noted. Typical values are at  $V_{CC}$  - GND = 2.5V,  $V_{IHD} = V_{CC}$  - 1.0V,  $V_{ILD} = V_{CC}$  - 1.5V, unless otherwise noted.) (Notes 1, 2, and 3)

| DADAMETED                          | OVMDOL                            | CONDITIONS                                           |                         | -40°C |                            |                         | +25°C |                            | +85°C                   |     |                            |       |

|------------------------------------|-----------------------------------|------------------------------------------------------|-------------------------|-------|----------------------------|-------------------------|-------|----------------------------|-------------------------|-----|----------------------------|-------|

| PARAMETER                          | SYMBOL                            | CONDITIONS                                           | MIN                     | TYP   | MAX                        | MIN                     | TYP   | MAX                        | MIN                     | TYP | MAX                        | UNITS |

| SINGLE-ENDED                       | INPUTS (C                         | LKSEL, EN)                                           |                         |       |                            |                         |       |                            |                         |     |                            |       |

| Input High<br>Voltage              | VIH                               |                                                      | V <sub>CC</sub> - 1.165 |       | V <sub>CC</sub> - 0.88     | V <sub>CC</sub> - 1.165 |       | V <sub>CC</sub> - 0.88     | V <sub>CC</sub> - 1.165 |     | V <sub>CC</sub> - 0.88     | V     |

| Input Low<br>Voltage               | VIL                               |                                                      | V <sub>CC</sub> - 1.81  |       | V <sub>CC</sub> -<br>1.475 | V <sub>CC</sub> - 1.81  |       | V <sub>CC</sub> -<br>1.475 | V <sub>CC</sub> - 1.81  |     | V <sub>CC</sub> -<br>1.475 | V     |

| Input Current                      | I <sub>IN</sub>                   | VIH(MAX),<br>VIL(MAX)                                | -150                    |       | +50                        | -150                    |       | +50                        | -150                    |     | +50                        | μА    |

| DIFFERENTIAL I                     | DIFFERENTIAL INPUTS (CLK_, CLK_)  |                                                      |                         |       |                            |                         |       |                            |                         |     |                            |       |

| Differential Input<br>High Voltage | V <sub>IHD</sub>                  | Figure 1                                             | 1.2                     |       | Vcc                        | 1.2                     |       | V <sub>C</sub> C           | 1.2                     |     | V <sub>C</sub> C           | V     |

| Differential Input<br>Low Voltage  | V <sub>ILD</sub>                  | Figure 1                                             | GND                     |       | V <sub>CC</sub> - 0.095    | GND                     |       | V <sub>CC</sub> - 0.095    | GND                     |     | V <sub>CC</sub> - 0.095    | V     |

| Differential Input<br>Voltage      | V <sub>ID</sub>                   | V <sub>IHD</sub> - V <sub>ILD</sub>                  | 0.095                   |       | Vcc                        | 0.095                   |       | Vcc                        | 0.095                   |     | Vcc                        | V     |

| Input Current                      | I <sub>IH</sub> , I <sub>IL</sub> | CLK_, or CLK_ = V <sub>IHD</sub> or V <sub>ILD</sub> | -60                     |       | +50                        | -60                     |       | +50                        | -60                     |     | +60                        | μА    |

| OUTPUTS (Q_, G                     | OUTPUTS (Q_, \overline{Q_})       |                                                      |                         |       |                            |                         |       |                            |                         |     |                            |       |

| Output High<br>Voltage             | VoH                               | Figure 1                                             |                         |       | 1.6                        |                         |       | 1.6                        |                         |     | 1.6                        | V     |

| Output Low<br>Voltage              | VoL                               | Figure 1                                             | 0.9                     |       |                            | 0.9                     |       |                            | 0.9                     |     |                            | V     |

| Differential<br>Output Voltage     | V <sub>OD</sub>                   | V <sub>OH</sub> - V <sub>OL</sub> ,<br>Figure 1      | 250                     | 350   | 450                        | 250                     | 350   | 450                        | 250                     | 350 | 450                        | mV    |

### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC}$  - GND = 2.375V to 2.625V, outputs terminated with 100 $\Omega$  ±1%, unless otherwise noted. Typical values are at  $V_{CC}$  - GND = 2.5V,  $V_{IHD}$  =  $V_{CC}$  - 1.0V,  $V_{ILD}$  =  $V_{CC}$  - 1.5V, unless otherwise noted.) (Notes 1, 2, and 3)

| DADAMETED                                                              | SYMBOL            | CONDITIONS              |       | -40°C |       | +25°C |      |       | +85°C |      |       | UNITS |

|------------------------------------------------------------------------|-------------------|-------------------------|-------|-------|-------|-------|------|-------|-------|------|-------|-------|

| PARAMETER                                                              | SYMBOL            | CONDITIONS              | MIN   | TYP   | MAX   | MIN   | TYP  | MAX   | MIN   | TYP  | MAX   | UNITS |

| Change in V <sub>OD</sub><br>Between<br>Complementary<br>Output States | ΔV <sub>OD</sub>  |                         |       |       | 40    |       |      | 40    |       |      | 40    | mV    |

| Output Offset<br>Voltage                                               | Vos               |                         | 1.125 | 1.25  | 1.375 | 1.125 | 1.25 | 1.375 | 1.125 | 1.25 | 1.375 | mV    |

| Change in V <sub>OS</sub> Between Complementary Output States          | ΔV <sub>OCM</sub> |                         |       |       | 25    |       |      | 25    |       |      | 25    | mV    |

| Output Short-                                                          |                   | Q_ shorted to Q_        |       |       | 12    |       |      | 12    |       |      | 12    |       |

| Circuit Current                                                        | losc              | Q_ or Q_ shorted to GND |       |       | 28    |       |      | 28    |       |      | 28    | mA    |

| POWER SUPPLY                                                           | 1                 |                         |       |       |       |       |      |       |       |      |       |       |

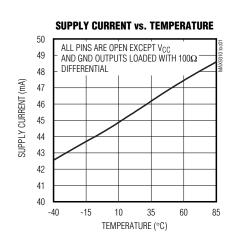

| Power-Supply<br>Current                                                | Icc               | (Note 4)                |       | 42    | 75    |       | 45.5 | 75    |       | 48.5 | 75    | mA    |

### **AC ELECTRICAL CHARACTERISTICS**

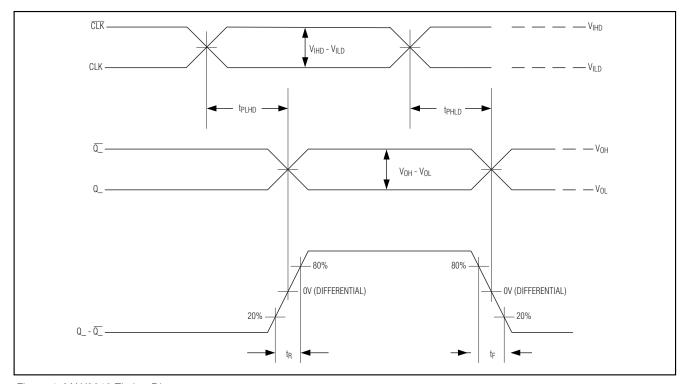

$(V_{CC}$  - GND = 2.375V to 2.625V, outputs terminated with 100 $\Omega$  ±1%,  $f_{IN} \le$  1.0GHz, input transition time = 125ps (20% to 80%),  $V_{IHD}$  -  $V_{ILD}$  = 0.15V to  $V_{CC}$ , unless otherwise noted. Typical values are at  $V_{CC}$  - GND = 2.5V,  $V_{IHD}$  =  $V_{CC}$  - 1.0V,  $V_{ILD}$  =  $V_{CC}$  - 1.5V, unless otherwise noted.) (Notes 1 and 5)

| PARAMETER                              | SYMBOL           | CONDITIONS                                                                 |     | -40°C |     |     | +25°C |     |     | +85°C |     | UNITS       |

|----------------------------------------|------------------|----------------------------------------------------------------------------|-----|-------|-----|-----|-------|-----|-----|-------|-----|-------------|

| PARAMETER                              | STIVIBUL         | CONDITIONS                                                                 | MIN | TYP   | MAX | MIN | TYP   | MAX | MIN | TYP   | MAX | UNITS       |

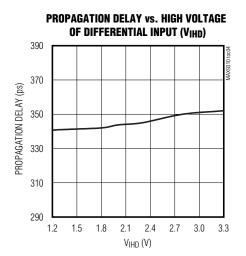

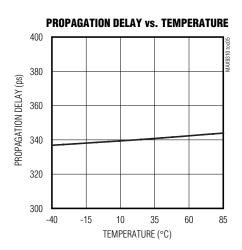

| Propagation Delay CLK_, CLK_ to Q_, Q_ | tphL,<br>tpLH    | Figure 1                                                                   | 250 | 335   | 600 | 250 | 345   | 600 | 250 | 345   | 600 | ps          |

| Output-to-<br>Output Skew              | tskoo            | (Note 6)                                                                   |     | 10    | 25  |     | 8     | 25  |     | 5     | 25  | ps          |

| Part-to-Part<br>Skew                   | tskpp            | (Note 7)                                                                   |     |       | 145 |     |       | 145 |     |       | 145 | ps          |

| Added Random<br>Jitter                 | t <sub>RJ</sub>  | f <sub>IN</sub> = 1.0GHz,<br>clock pattern<br>(Note 8)                     |     | 0.4   | 1.0 |     | 0.4   | 1.0 |     | 0.4   | 1.0 | ps<br>(RMS) |

| Added<br>Deterministic<br>Jitter       | t <sub>D</sub> J | f <sub>IN</sub> = 1.0Gsps,<br>2 <sup>23</sup> - 1 PRBS<br>pattern (Note 8) |     | 41    | 52  |     | 41    | 52  |     | 41    | 52  | ps<br>(P-P) |

### **AC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC}$  - GND = 2.375V to 2.625V, outputs terminated with 100 $\Omega$  ±1%,  $f_{IN} \le$  1.0GHz, input transition time = 125ps (20% to 80%),  $V_{IHD}$  -  $V_{ILD}$  = 0.15V to  $V_{CC}$ , unless otherwise noted. Typical values are at  $V_{CC}$  - GND = 2.5V,  $V_{IHD}$  =  $V_{CC}$  - 1.0V,  $V_{ILD}$  =  $V_{CC}$  - 1.5V, unless otherwise noted.) (Notes 1 and 5)

| PARAMETER                                | SYMBOL            | CAMBOI                  | CVMBOL | CVMBOL | CVMBOL | CVMBOL | CVMPOL | CVMPOL | CVMPOL | CVMBOL | CVMPOL | CVMDOL | CONDITIONS |  | -40°C |  |  | +25°C |  |  | +85°C |  | UNITS |

|------------------------------------------|-------------------|-------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|--|-------|--|--|-------|--|--|-------|--|-------|

| PANAMETER                                |                   | COMPLITIONS             | MIN    | TYP    | MAX    | MIN    | TYP    | MAX    | MIN    | TYP    | MAX    | UNITS  |            |  |       |  |  |       |  |  |       |  |       |

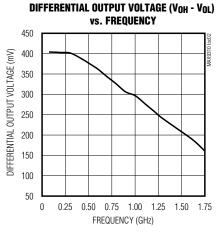

| Operating<br>Frequency                   | fMAX              | V <sub>OD</sub> ≥ 250mV | 1.0    |        |        | 1.0    |        |        | 1.0    |        |        | GHz    |            |  |       |  |  |       |  |  |       |  |       |

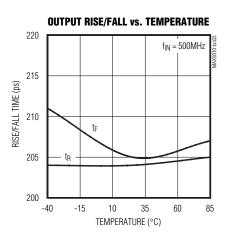

| Differential<br>Output Rise/Fall<br>Time | t <sub>R/tF</sub> | 20% to 80%,<br>Figure 1 | 140    | 205    | 300    | 140    | 205    | 300    | 140    | 205    | 300    | ps     |            |  |       |  |  |       |  |  |       |  |       |

- Note 1: Measurements are made with the device in thermal equilibrium.

- Note 2: Current into a pin is defined as positive. Current out of a pin is defined as negative.

- **Note 3:** DC parameters are production tested at +25°C. DC limits are guaranteed by design and characterized over the full operating temperature range.

- **Note 4:** All pins are open except  $V_{CC}$  and GND, all outputs are loaded with  $100\Omega$  differentially.

- Note 5: Guaranteed by design and characterization. Limits are set to ±6 sigma.

- **Note 6:** Measured between outputs of the same part at the signal crossing points for a same-edge transition.

- **Note 7:** Measured between outputs of different parts at the signal crossing points under identical conditions for a same-edge transition.

- Note 8: Device jitter added to the input signal.

### Typical Operating Characteristics

$(V_{CC}$  - GND = 2.5V, outputs terminated with 100 $\Omega$  ±1%,  $f_{IN}$  = 1.0GHz, input transition time = 125ps (20% to 80%),  $V_{IHD}$  =  $V_{CC}$  - 1.0V,  $V_{ILD}$  =  $V_{CC}$  - 1.5V, unless otherwise noted.)

### **Typical Operating Characteristics (continued)**

$(V_{CC}$  - GND = 2.5V, outputs terminated with 100 $\Omega$  ±1%,  $f_{IN}$  = 1.0GHz, input transition time = 125ps (20% to 80%),  $V_{IHD}$  =  $V_{CC}$  - 1.0V,  $V_{ILD}$  =  $V_{CC}$  - 1.5V, unless otherwise noted.)

### **Pin Description**

| PIN | NAME   | FUNCTION                                                                                                                                                                                |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Q0     | Noninverting Differential Output 0. Typically terminated with $100\Omega$ to $\overline{Q0}$ .                                                                                          |

| 2   | Q0     | Inverting Differential Output 0. Typically terminated with $100\Omega$ to Q0.                                                                                                           |

| 3   | Q1     | Noninverting Differential Output 1. Typically terminated with $100\Omega$ to $\overline{Q1}$ .                                                                                          |

| 4   | Q1     | Inverting Differential Output 1. Typically terminated with $100\Omega$ to Q1.                                                                                                           |

| 5   | Q2     | Noninverting Differential Output 2. Typically terminated with $100\Omega$ to $\overline{\Omega 2}$ .                                                                                    |

| 6   | Q2     | Inverting Differential Output 2. Typically terminated with $100\Omega$ to Q2.                                                                                                           |

| 7   | Q3     | Noninverting Differential Output 3. Typically terminated with $100\Omega$ to $\overline{\text{Q3}}$ .                                                                                   |

| 8   | Q3     | Inverting Differential Output 3. Typically terminated with $100\Omega$ to Q3.                                                                                                           |

| 9   | Q4     | Noninverting Differential Output 4. Typically terminated with $100\Omega$ to $\overline{Q4}$ .                                                                                          |

| 10  | Q4     | Inverting Differential Output 4. Typically terminated with $100\Omega$ to Q4.                                                                                                           |

| 11  | GND    | Ground                                                                                                                                                                                  |

| 12  | CLKSEL | Clock Select Input. Drive low to select the CLK0, $\overline{\text{CLK0}}$ input. Drive high to select the CLK1, $\overline{\text{CLK1}}$ input. Internal 60k $\Omega$ pulldown to GND. |

| 13  | CLK0   | Noninverting Differential Clock Input 0. Internal 75kΩ pulldown to GND.                                                                                                                 |

| 14  | CLK0   | Inverting Differential Clock Input 0. Internal 75k $\Omega$ pullup to V <sub>CC</sub> and 75k $\Omega$ pulldown to GND.                                                                 |

| 15  | I.C.   | Internally Connect. Do not connect externally.                                                                                                                                          |

| 16  | CLK1   | Noninverting Differential Input 1. Internal 75k $\Omega$ pulldown to GND.                                                                                                               |

| 17  | CLK1   | Inverting Differential Input 1. Internal 75k $\Omega$ pullup to V <sub>CC</sub> and 75k $\Omega$ pulldown to GND.                                                                       |

### **Pin Description (continued)**

| PIN    | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                             |

|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18, 20 | Vcc  | Positive Supply Voltage. Bypass each $V_{CC}$ to GND with $0.1\mu F$ and $0.01\mu F$ ceramic capacitors. Place the capacitors as close to the device as possible with the smaller value capacitor closest to the device.                                                                                                                             |

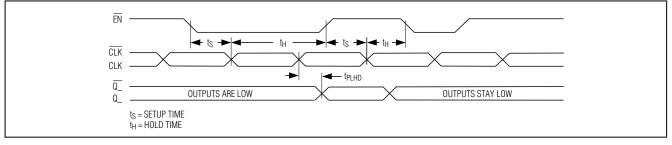

| 19     | ĒN   | Output Enable Input. Outputs are synchronously enabled on the falling edge of the selected clock input when $\overline{\text{EN}}$ is low. Outputs are synchronously driven to a differential low state on the falling edge of the selected clock input when $\overline{\text{EN}}$ is high. Internal $60\text{k}\Omega$ pulldown to GND (Figure 2). |

Figure 1. MAX9310 Timing Diagram

Figure 2. MAX9310 EN Timing Diagram

### **Detailed Description**

The MAX9310 is a low-skew 1:5 differential driver with two selectable LVPECL inputs and LVDS outputs, designed for clock distribution applications. The selected clock accepts a differential input signal and reproduces it on five separate differential LVDS outputs. The inputs are biased with internal resistors such that the output is differential low when inputs are open. The output drivers are guaranteed to operate at frequencies up to 1.0GHz with LVDS output levels conforming to the EIA/TIA-644 standard.

The MAX9310 is designed for 2.375V to 2.625V operation in systems with a nominal 2.5V supply.

### **Differential LVPECL Input**

The MAX9310 has two input differential pairs that accept differential LVPECL/HSTL inputs. Each differential input pair has to be independently terminated. A select pin (CLKSEL) is used to activate the desired input. The maximum magnitude of the differential signal applied to the input is VCC. Specifications for the high and low voltages of a differential input (VIHD and VILD) and the differential input voltage (VIHD - VILD) apply simultaneously.

#### Synchronous Enable

The MAX9310 is synchronously enabled and disabled with outputs in a differential low state to eliminate shortened clock pulses.  $\overline{EN}$  is connected to the input of an edge-triggered D flip-flop. After power-up, drive  $\overline{EN}$  low and toggle the selected clock input to enable the outputs. The outputs are enabled on the falling edge of the selected clock input after  $\overline{EN}$  goes low. The outputs are set to a differential low state on the falling edge of the selected clock input after  $\overline{EN}$  goes high (Figure 2).

#### **Input Bias Resistors**

Internal biasing resistors ensure a (differential) output low condition in the event that the inputs are not connected. The inverting input  $(\overline{CLK}_-)$  is biased with a  $75k\Omega$  pulldown to GND and a  $75k\Omega$  pullup to VCC. The noninverting input (CLK\_) is biased with a  $75k\Omega$  pulldown to GND.

#### **Differential LVDS Output**

The LVDS outputs must be terminated with  $100\Omega$  across Q\_ and  $\overline{Q}$ , as shown in the *Typical Application Circuit*. The outputs are short-circuit protected.

### **Applications Information**

### Supply Bypassing

Bypass each VCC to GND with high-frequency surface-mount ceramic  $0.1\mu\text{F}$  and  $0.01\mu\text{F}$  capacitors in parallel as close to the device as possible, with the  $0.01\mu\text{F}$  capacitor closest to the device. Use multiple parallel vias to minimize parasitic inductance and reduce power-supply bounce with high-current transients.

### **Controlled-Impedance Traces**

Input and output trace characteristics affect the performance of the MAX9310. Connect high-frequency input and output signals to  $50\Omega$  characteristic impedance traces. Minimize the number of vias to prevent impedance discontinuities. Reduce reflections by maintaining the  $50\Omega$  characteristic impedance through cables and connectors. Reduce skew within a differential pair by matching the electrical length of the traces.

### Output Termination

Terminate the outputs with  $100\Omega$  across Q\_ and  $\overline{Q}$ , as shown in the *Typical Application Circuit*.

### **Chip Information**

TRANSISTOR COUNT: 716 PROCESS: Bipolar

## \_Functional Diagram

8 \_\_\_\_\_\_ MIXI/N

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.