### AT25EU0041A

4-Mbit, Ultra-Low Energy Serial Flash Memory

#### **Features**

- Voltage Range: 1.65 V − 3.6 V

- 4-Mbit Flash Memory

- Serial Peripheral Interface (SPI) compatible

- · Supports SPI modes 0 and 3

- Supports single input/output operations (1,1,1)

- Supports dual input and dual output operations (1,1,2), (1,2,2), (0,2,2)

- Supports quad input and quad output operations (1,1,4), (1,4,4), (0,4,4)

- 108 MHz Maximum Operating Frequency

- Program

- Serial-input Page Program up to 256 bytes

- Dual-Input Page Program up to 256 bytes

- Quad-Input Page Program up to 256 bytes

- · Program Suspend and Resume

- Erase

- Page erase (256-byte)

- Block erase (4/32/64 kbyte)

- · Full Chip erase

- · Erase Suspend and Resume

- Program/Erase Speed

- · Page Program time: 2 ms typical

- Page Erase time: 8 ms typical

- Block Erase time: 8 ms typical

- · Chip Erase time: 8 ms typical

- Flexible Architecture: 4/32/64 kbyte blocks

- Software-controlled Reset

- Software/Hardware Write Protection

- · 3x512-Byte Security Registers with OTP Lock

- Enable/Disable protection with WP Pin

- Write protect all/portion of memory via software protect

- · Top or Bottom Block selection

- Low Power Consumption

- 1.1 mA active read current (typical)

- 100 nA Deep Power-Down (DPD) current (typical)

- Temperature Range: -40 °C to +85 °C

- Cycling Endurance/Data Retention

- 10k program and erase cycles

- · 20-year data retention

- Industry standard green (Pb/Halide-free/RoHS Compliant) Package Options

- 8-lead SOIC (150-mil)

- 8-pad 2 x 3 x 0.6 mm UDFN

## **Contents**

| Features                                          | 1  |

|---------------------------------------------------|----|

| Figures                                           | 3  |

| Tables                                            | 4  |

| 1. Product Overview                               | 5  |

| 2. Package Types and Pinouts                      |    |

| 2.1 Pin Configuration - SOP 150-mil               |    |

| 2.2 Pad Configuration - UDFN 2X3 MM               | 6  |

| 3. Block Addresses                                |    |

| 4. Functional and Operational Description         | 9  |

| 4.1 Dual SPI Commands                             |    |

| 4.2 Quad SPI Commands                             |    |

| 4.3 Supply Voltage                                |    |

| 4.4 Active Power and Standby Power Modes          | 10 |

| 4.5 Hold Condition                                |    |

| 4.6 Software Reset                                | 10 |

| 5. Status and Configuration Registers             | 11 |

| 5.1 Status Register 1                             | 11 |

| 5.2 Status Register 2                             | 12 |

| 5.3 Status Register Protection                    |    |

| 5.4 Status Register Memory Protection             | 14 |

| 6. Command Set                                    |    |

| 6.1 Configuration and Status Commands             | 18 |

| 6.2 Read Commands                                 |    |

| 6.3 ID and Power Commands                         |    |

| 6.4 Program / Erase and Security Commands         |    |

| 7. Electrical Characteristics                     |    |

| 7.1 Absolute Maximum Ratings                      |    |

| 7.2 Operating Ranges                              |    |

| 7.3 Power-Up / Power-Down Timing and Requirements |    |

| 7.4 DC Characteristics                            |    |

| 7.5 AC Measurement conditions                     |    |

| 7.6 AC Characteristics                            |    |

| 7.7 Serial Output Timing                          |    |

| 7.8 Serial Input Timing                           |    |

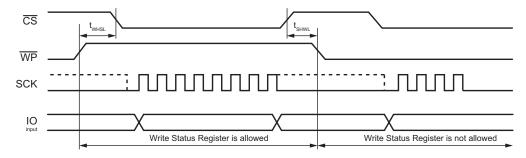

| 7.9 HOLD Timing<br>7.10 WP Timing                 |    |

|                                                   |    |

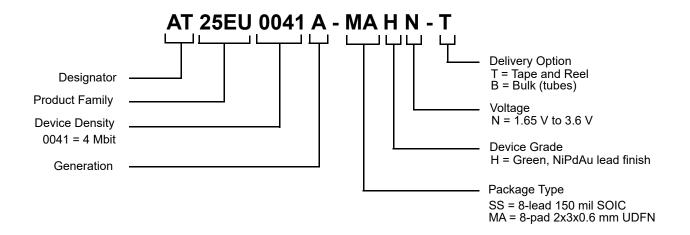

| 8. Ordering Information                           |    |

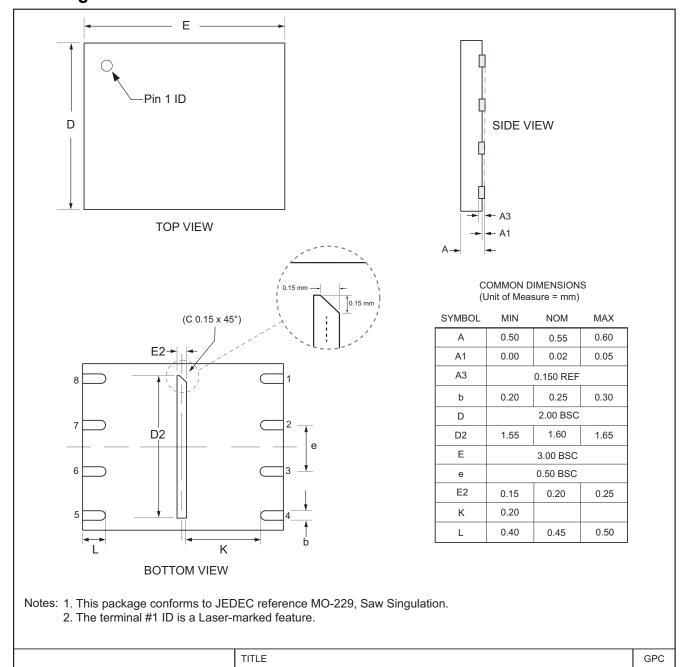

| 9. Packaging Information                          |    |

| 9.1 Eight-Pin SOIC 150-mil                        |    |

| 9.2 Eight-Pad 2 x 3 x 0.6 mm UDFN                 |    |

| 10 Revision History                               | 60 |

# **Figures**

| Figure 1. AT25EU0041A Logic Diagram                                         | 5  |

|-----------------------------------------------------------------------------|----|

| Figure 2. AT25EU0041A Pin Assignments, Eight-pin SOP 150-mil (Top View)     | 6  |

| Figure 3. AT25EU0041A Pad Assignments, Eight-pad UDFN 2x3 mm (Top View)     | 6  |

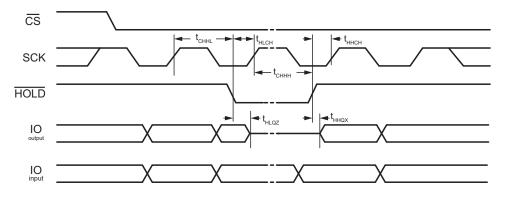

| Figure 4. Hold Condition Activation                                         |    |

| Figure 5. Write Enable Command for SPI Mode                                 |    |

| Figure 6. Write Enable for Volatile Status Register (50h)                   | 18 |

| Figure 7. Write Disable Command, SPI Mode                                   | 19 |

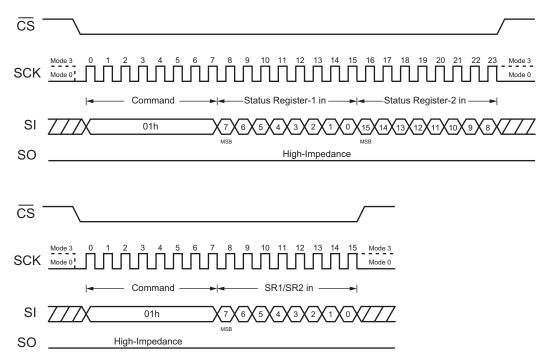

| Figure 8. Read Status Register Command                                      |    |

| Figure 9. Active Status Interrupt Command                                   |    |

| Figure 10. Write Status Register Command                                    | 21 |

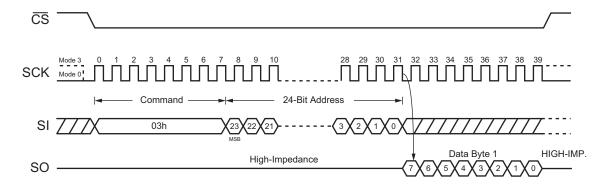

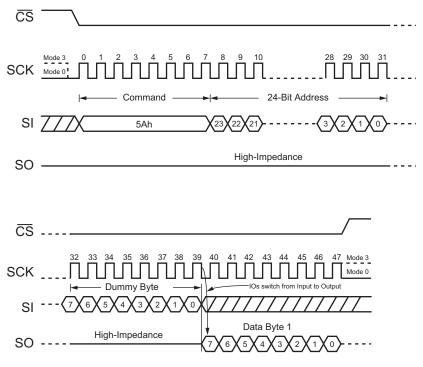

| Figure 11. Read Data Command                                                |    |

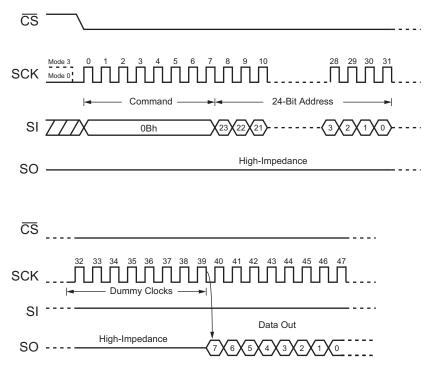

| Figure 12. Fast Read Command                                                |    |

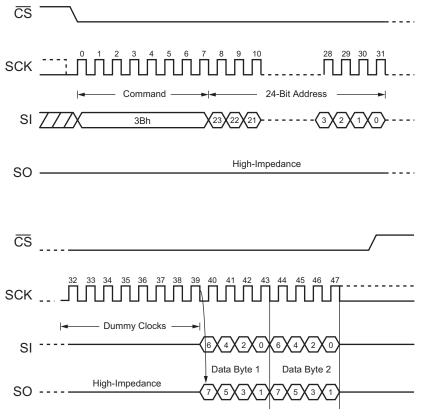

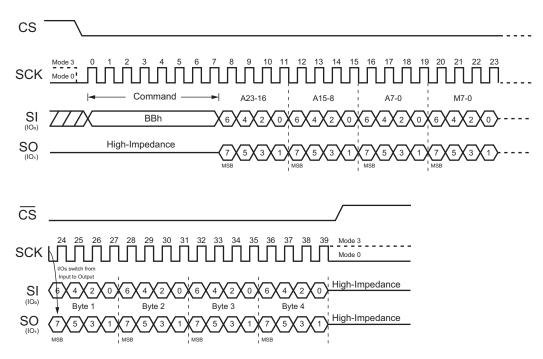

| Figure 13. Fast Read Dual Output Command                                    |    |

| Figure 14. Fast Read Dual I/O Command (Initial command or previous M5-4≠10) |    |

| Figure 15. Fast Read Dual I/O Command (Previous command M5-4=10)            |    |

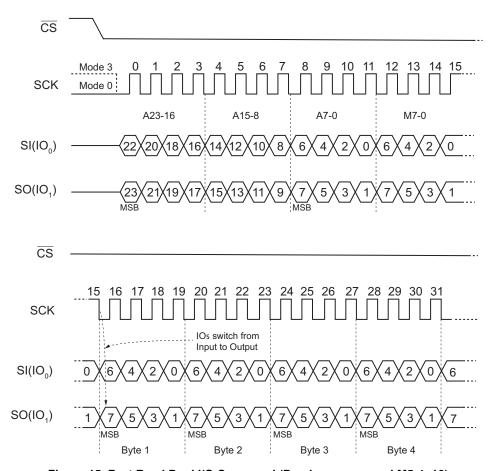

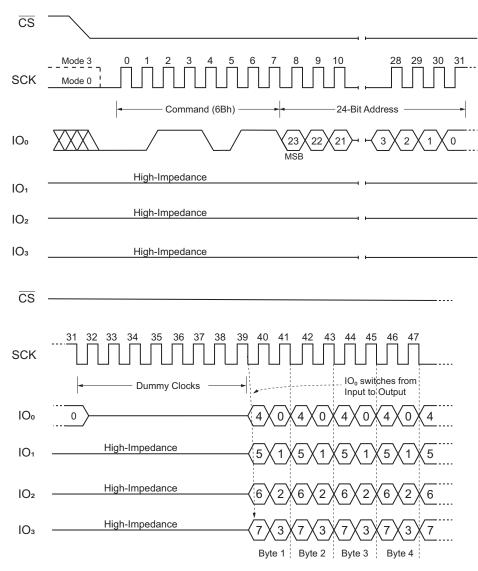

| Figure 16. Fast Read Quad Output Command                                    |    |

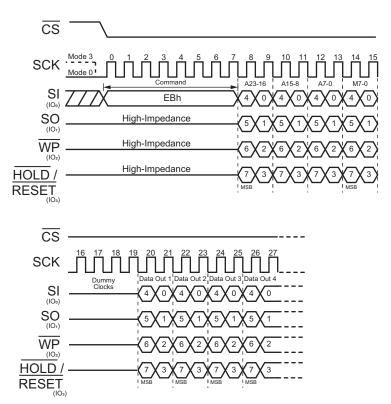

| Figure 17. Fast Read Quad I/O Command (Initial command or previous M5-4≠10) |    |

| Figure 18. Fast Read Quad I/O Command (Previous command set M5-4=10)        |    |

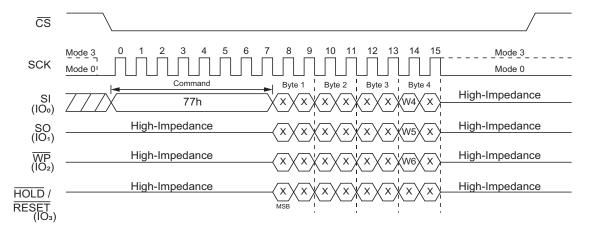

| Figure 19. Set Burst with Wrap Command                                      | 30 |

| Figure 20. Release Power-Down Command                                       |    |

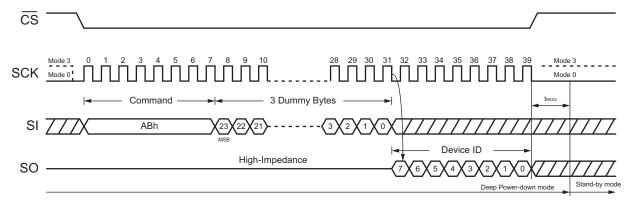

| Figure 21. Release Power-Down / Device ID Command                           |    |

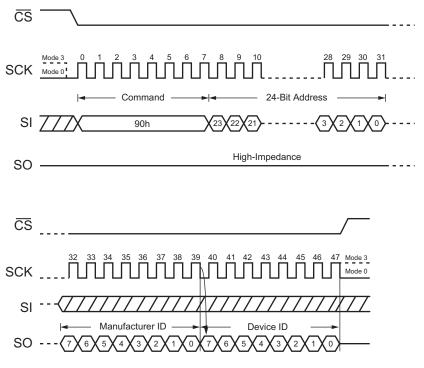

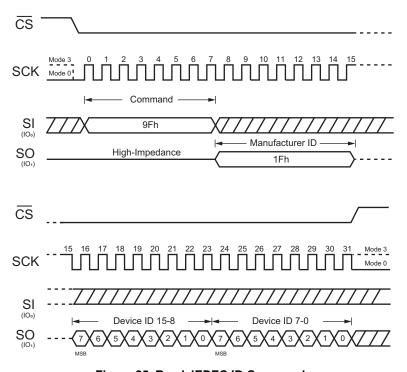

| Figure 22. Read Manufacturer / Device ID Command                            | 32 |

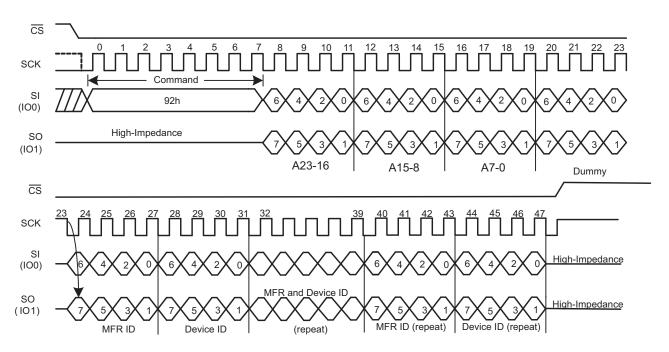

| Figure 23. Dual I/O Read Manufacture ID/ Device ID Timing                   | 33 |

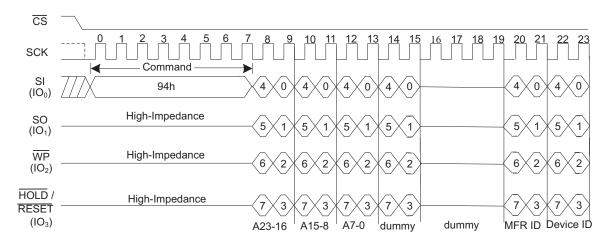

| Figure 24. Quad I/O Read Manufacture ID / Device ID Sequence Diagram        | 34 |

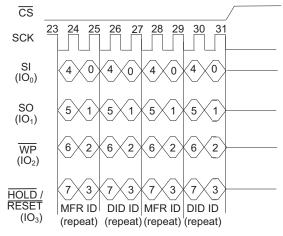

| Figure 25. Read JEDEC ID Command                                            | 35 |

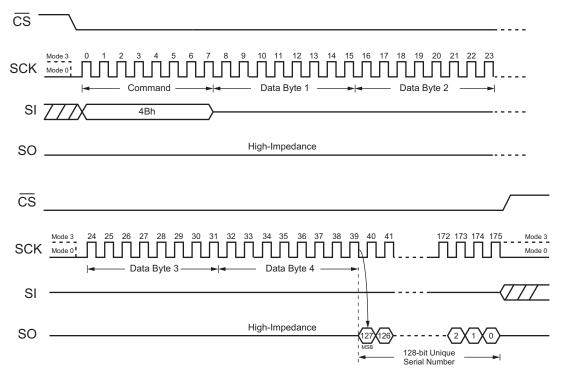

| Figure 26. Read Unique ID Sequence Diagram                                  |    |

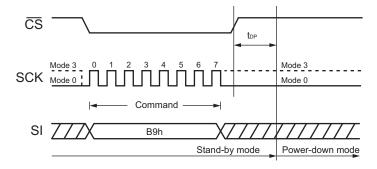

| Figure 27. Deep Power-Down Command                                          |    |

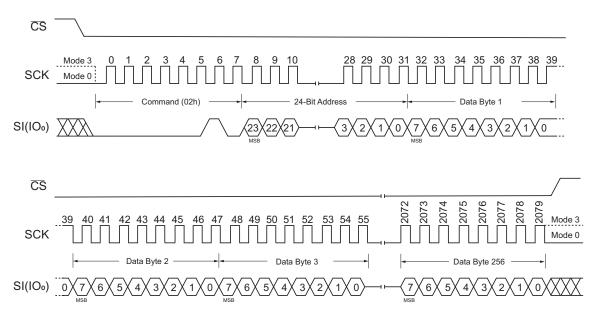

| Figure 28. Page Program Command                                             | 38 |

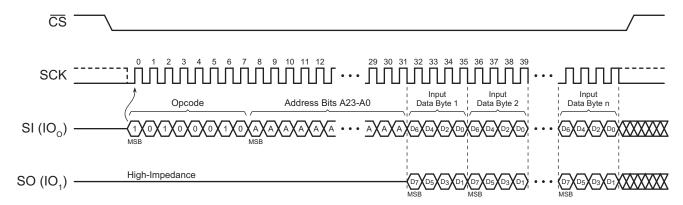

| Figure 29. Dual Page Program Command                                        | 39 |

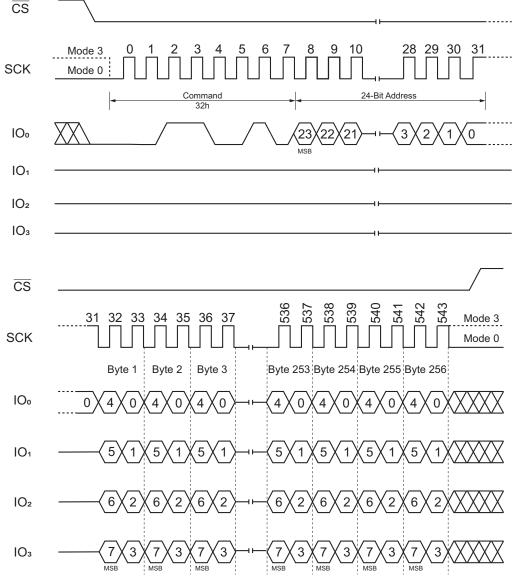

| Figure 30. Quad Input Page Program Command                                  | 40 |

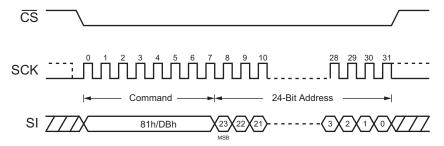

| Figure 31. Page Erase Command                                               | 41 |

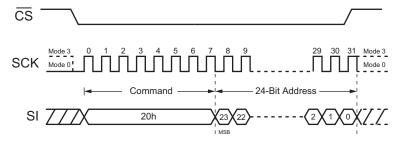

| Figure 32. 4 kB Block Erase Command                                         | 41 |

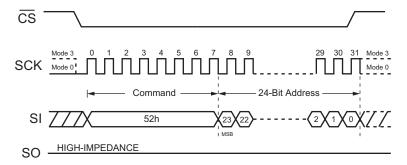

| Figure 33. 32 kB Block Erase Command                                        | 42 |

| Figure 34. 64 kB Block Erase Command                                        | 42 |

| Figure 35. Chip Erase Command                                               | 43 |

| Figure 36. Program/Erase Suspend Command                                    | 44 |

| Figure 37. Program/Erase Resume Command                                     | 46 |

| Figure 38. Erase Security Register Command                                  | 47 |

| Figure 39. Program Security Register Command                                | 48 |

| Figure 40. Read Security Command                                            | 49 |

| Figure 41. Enable Reset and Reset Command Sequence                          | 50 |

| Figure 42. Read Serial Flash Discoverable Parameter Command                 | 50 |

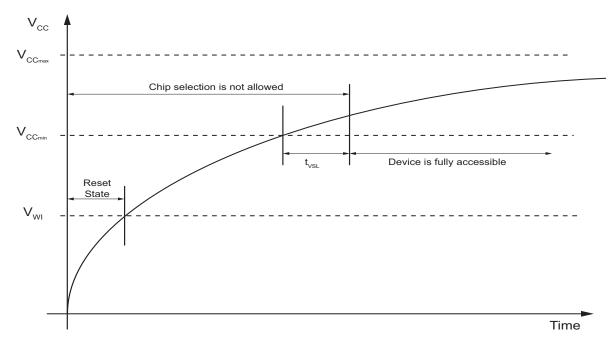

| Figure 43. Power-Up Timing and Voltage Levels                               |    |

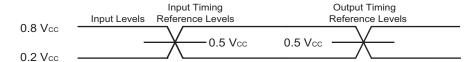

| Figure 44. AC Measurement I/O Waveform                                      |    |

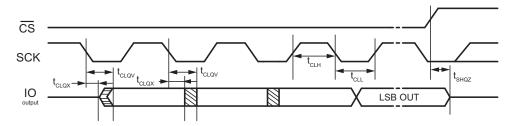

| Figure 45. Serial Output Timing                                             | 56 |

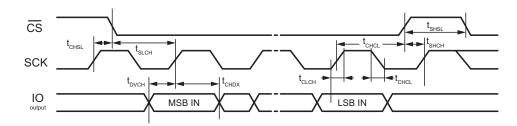

| Figure 46. Serial Input Timing                                              | 56 |

| Figure 47. HOLD Timing                                                      |    |

| Figure 48. WP Timing                                                        | 56 |

### AT25EU0041A Datasheet

### **Tables**

| Table 1. Pin Descriptions                                                                           | 6  |

|-----------------------------------------------------------------------------------------------------|----|

| Table 2. Block Addresses for the AT25EU0041A                                                        | 8  |

| Table 3. Status Register 1 Format                                                                   | 11 |

| Table 4. Status Register 2 Format                                                                   | 12 |

| Table 5. Status Register Protect Table                                                              | 13 |

| Table 6: Memory Array with CMP = 0                                                                  | 14 |

| Table 7. Memory Array with CMP = 1                                                                  | 15 |

| Table 8. Command Set Table 1                                                                        | 16 |

| Table 9. Wrap-Around Length Based on Wrap Bits                                                      | 30 |

| Table 10. AT25EU0041A ID Definition Table                                                           | 30 |

| Table 11. Readable Area of Memory While a Program or Erase Operation is Suspended                   | 43 |

| Table 12. Acceptable Commands During Program/Erase Suspend After t <sub>PSL</sub> /t <sub>ESL</sub> | 44 |

| Table 13. Acceptable Commands During Suspend (t <sub>PSL</sub> /t <sub>ESL</sub> Not Required)      | 44 |

| Table 14. Erase Security Coding                                                                     |    |

| Table 15. Program Security Register Coding                                                          | 48 |

| Table 16. Read Security Register Coding                                                             | 49 |

| Table 17. Absolute Maximum Ratings                                                                  | 51 |

| Table 18. Operating Ranges                                                                          | 51 |

| Table 19. Timing Requirements for Power-Up/Down                                                     |    |

| Table 20. DC Electrical Characteristics for 1.65 V to 3.6 V                                         |    |

| Table 21. DC Electrical Characteristics for 2.3 V to 3.6 V                                          | 53 |

| Table 22. AC Measurement Conditions                                                                 |    |

| Table 23. AC Electrical Characteristics for 1.65 V to 3.6 V                                         |    |

| Table 24. AC Electrical Characteristics for 2.3 V to 3.6 V                                          | 55 |

| Table 25 Ordering Codes                                                                             | 57 |

### 1. Product Overview

The AT25EU0041A is a new family of 4-Mbit Serial Peripheral Interface (SPI) Flash memory devices designed for ultra-low energy consumption. It is designed for battery powered system applications on the edge of the IoT network that are quite sensitive to the energy consumption of non-volatile memory devices. It can be used either for storing program code that is shadowed from Flash memory into embedded, or as external RAM for executing program code directly from the Nor Flash memory.

The AT25EU0041A achieves the ultra-low energy consumption by using a flexible erase architecture and short erase times with very low power for all operations such as read, program, and erase. The short erase times are constant and independent of the size of the memory block being erased. It also supports the page-erase feature, which allows erasing a block as small as 256 bytes. The page-erase feature makes write operations much more efficient.

The AT25EU0041A provides flexibility by supporting a wide  $V_{CC}$  voltage range (1.65 V – 3.6 V). The device supports the JEDEC standard manufacturer and device ID, as well as a 128-bit Unique Serial Number.

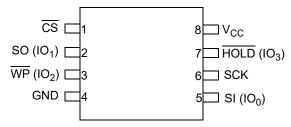

Figure 1 shows the logic diagram of the AT25EU0041A device.

Figure 1. AT25EU0041A Logic Diagram

# 2. Package Types and Pinouts

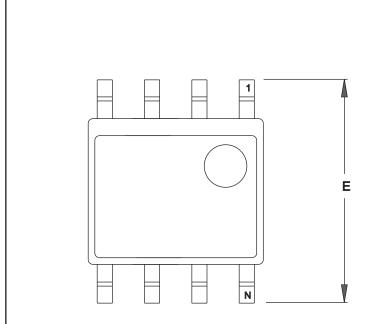

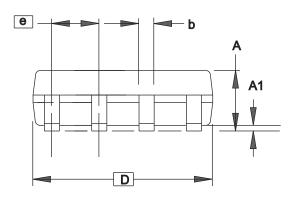

## 2.1 Pin Configuration - SOP 150-mil

Figure 2. AT25EU0041A Pin Assignments, Eight-pin SOP 150-mil (Top View)

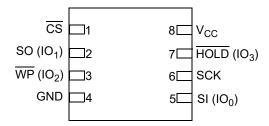

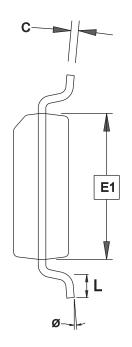

## 2.2 Pad Configuration - UDFN 2X3 MM

Figure 3. AT25EU0041A Pad Assignments, Eight-pad UDFN 2x3 mm (Top View)

During all operations,  $V_{CC}$  must be held stable and within the specified valid range:  $V_{CC}$  (min) to  $V_{CC}$  (max).

All of the input and output signals must be held high or low (according to voltages of  $V_{IH}$ ,  $V_{OH}$ ,  $V_{IL}$ , or  $V_{OL}$ ; see Section 7.6, AC Characteristics).

**Table 1. Pin Descriptions**

| Symbol        | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Asserted<br>State | Туре  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|

| <del>CS</del> | CHIP SELECT  Asserting the $\overline{CS}$ pin selects the device. When the $\overline{CS}$ pin is deasserted, the device is deselected and normally be placed in standby mode (all input signals are ignored, and all output signals are high impedance).  Unless an internal Program, Erase, or Write Status Registers embedded operation is in progress, the device is in the Standby Power mode. Driving the $\overline{CS}$ input to low enables the device, placing it in the Active Power mode. After power-up, a falling edge on $\overline{CS}$ is required before the start of any command.  A high-to-low transition on the $\overline{CS}$ pin is required to start an operation; a low-to-high transition is required to end an operation. When ending an internally self-timed operation, such as a program or erase cycle, the device does not enter the standby mode until the operation is complete.  To ensure correct power-up sequencing, it is recommended to add a 10k Ohm pull-up resistor from $\overline{CS}$ to $V_{CC}$ . This ensures $\overline{CS}$ ramps together with $V_{CC}$ during power-up. | Low               | Input |

| SCK           | SERIAL CLOCK This pin provides a clock to the device. Command, address, and input data present on the SI pin is latched in on the rising edge of SCK, while output data on the SO pin is clocked out on the falling edge of SCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                 | Input |

### **Table 1. Pin Descriptions**

| Symbol                     | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Asserted<br>State | Туре         |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------|

| SI (IO <sub>0</sub> )      | SERIAL INPUT  The SI pin is used for all data input, including command and address sequences. Data on the SI pin is latched in on the rising edge of SCK.  Data present on the SI pin is ignored whenever the device is deselected (CS is deasserted).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                 | Input/Output |

| SO (IO <sub>1</sub> )      | SERIAL OUTPUT: Data on the SO pin is clocked out on the falling edge of SCK.  The SO pin is in a high-impedance state whenever the device is deselected (CS is deasserted).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                 | Input/Output |

| WP (IO <sub>2</sub> )      | WRITE PROTECT / $IO_2$ This pin is used either for write-protection, in which case it is referred to as $\overline{WP}$ , or as one of the quad-SPI I/O pins, in which case it is referred to as $IO_2$ .  When the Quad Enable (QE) bit of Status Register 2 is 0, and the SRP1 and SRP0 bits are 0 and 1, respectively, the pin can be used for write-protection. It then can be asserted (driven low) to protect the Status Registers from modification.  When the QE bit of Status Register 2 is 1, quad-SPI communication is enabled, and the pin is used as I/O pin $IO_2$ in any command that makes use of quad-SPI. In this setting, do not use the pin for write-protection.  The $\overline{WP}$ pin is internally pulled high and can be left floating if not used.                                                                                                                                                  | -                 | Input/Output |

| HOLD<br>(IO <sub>3</sub> ) | HOLD / IO <sub>3</sub> This pin is used either for pausing communication, in which case it is referred to as HOLD, or as one of the quad-SPI I/O pins, in which case it is referred to as IO <sub>3</sub> .  When the Quad Enable (QE) bit of Status Register 2 is 0, this pin is used as a HOLD pin. When the QE bit of Status Register 2 is 1, quad-SPI communication is enabled, and the pin is used as I/O pin IO <sub>3</sub> in any command that makes use of quad-SPI. In this setting, do not use the pin for pausing communication.  The HOLD pin is used to pause a SPI sequence without resetting the clocking sequence. To enable the HOLD mode, CS must be low. The HOLD mode effect is on with the falling edge of the HOLD signal with SCK being low. The HOLD mode ends on the rising edge of the HOLD signal with SCK being low.  The HOLD pin is internally pulled high and can be left floating if not used. | -                 | Input/Output |

| V <sub>CC</sub>            | <b>DEVICE POWER SUPPLY</b> The $V_{CC}$ pin supplies the source voltage to the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                 | Power        |

| GND                        | GROUND  The ground reference for the power supply. Connect GND to the system ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                 | Power        |

# 3. Block Addresses

Table 2. Block Addresses for the AT25EU0041A

| 64-kbyte Block            | 32-kbyte Block            | 4-kbyte Block        | Address Range           |

|---------------------------|---------------------------|----------------------|-------------------------|

|                           |                           | 4 kbytes (Block 127) | 07F000h - 07FFFFh       |

|                           |                           | 4 kbytes (B126)      | 07E000h - 07EFFFh       |

|                           |                           | 4 kbytes (B125)      | 07D000h - 07DFFFh       |

|                           | 32 kbytes                 | 4 kbytes (B124)      | 07C000h - 07CFFFh       |

|                           | (block 15)                | 4 kbytes (B123)      | 07B000h - 07BFFFh       |

|                           |                           | 4 kbytes (B122)      | 07A000h - 07AFFFh       |

|                           |                           | 4 kbytes (B121)      | 079000h - 079FFFh       |

| 64 kbytes                 |                           | 4 kbytes (B120)      | 078000h - 078FFFh       |

| (block 7)                 |                           | 4 kbytes (B119)      | 077000h - 077FFFh       |

|                           |                           | 4 kbytes (B118)      | 076000h - 076FFFh       |

|                           |                           | 4 kbytes (B117)      | 075000h - 075FFFh       |

|                           | 32 kbytes                 | 4 kbytes (B116)      | 074000h - 074FFFh       |

|                           | (block 14)                | 4 kbytes (B115)      | 073000h - 073FFFh       |

|                           |                           | 4 kbytes (B114)      | 072000h - 072FFFh       |

|                           |                           | 4 kbytes (B113)      | 071000h - 071FFFh       |

|                           |                           | 4 kbytes (B112)      | 070000h - 070FFFh       |

| 64 kbytes (block 6)       | 32 kbytes (block 13)      | 4 kbytes (B111)      | 06F000h - 06FFFFh       |

| to<br>64 kbytes (block 1) | to<br>32 kbytes (block 2) | to<br>4 kbytes (B16) | to<br>010000h - 010FFFh |

|                           |                           | 4 kbytes (B15)       | 00F000h - 00FFFFh       |

|                           |                           | 4 kbytes (B14)       | 00E000h - 00EFFFh       |

|                           |                           | 4 kbytes (B13)       | 00D000h - 00DFFFh       |

|                           | 32 kbytes                 | 4 kbytes (B12)       | 00C000h - 00CFFFh       |

|                           | (block 1)                 | 4 kbytes (B11)       | 00B000h - 00BFFFh       |

|                           |                           | 4 kbytes (B10)       | 00A000h - 00AFFFh       |

|                           |                           | 4 kbytes (B9)        | 009000h - 009FFFh       |

| 64 kbytes                 |                           | 4 kbytes (B8)        | 008000h - 008FFFh       |

| (block 0)                 |                           | 4 kbytes (B7)        | 007000h - 007FFFh       |

|                           |                           | 4 kbytes (B6)        | 006000h - 006FFFh       |

|                           |                           | 4 kbytes (B5)        | 005000h - 005FFFh       |

|                           | 32 kbytes                 | 4 kbytes (B4)        | 004000h - 004FFFh       |

|                           | (block 0)                 | 4 kbytes (B3)        | 003000h - 003FFFh       |

|                           |                           | 4 kbytes (B2)        | 002000h - 002FFFh       |

|                           |                           | 4 kbytes (B1)        | 001000h - 001FFFh       |

|                           |                           | 4 kbytes (B0)        | 000000h - 000FFFh       |

# 4. Functional and Operational Description

The AT25EU0041A features a serial peripheral interface on a four-signals bus: SCK,  $\overline{\text{CS}}$ , SI, and SO. Both SPI bus mode 0 and 3 are supported.

The SPI mode has input bits (including commands, addresses, data, M7~M0, W6~W4, etc.) latched on the rising edge of SCK, as well as output bits transferred out on the falling edge of SCK.

#### 4.1 Dual SPI Commands

The AT25EU0041A supports Dual SPI operation. when using the Dual Output Fast Read (3Bh) or Dual I/O Fast read (BBh) commands. These commands allow data to be transferred to, and from, the device at two times the rate of the standard SPI. When using the Dual SPI command, the SI and SO pins become bidirectional I/O pins IO<sub>0</sub> and IO<sub>1</sub>, respectively.

#### 4.2 Quad SPI Commands

The AT25EU0041A supports Quad SPI operation when using the Quad Output Fast Read (6Bh) or Quad I/O Fast Read (EBh) commands. These commands allow the data to be transferred to, and from, the device at four times the rate of standard SPI. When using the Quad SPI command, the SI and SO pins become bidirectional I/O pins, and the WP and HOLD pins become IO<sub>2</sub> and IO<sub>3</sub>, respectively. Quad SPI commands require the non-volatile Quad Enable bit (QE) in Status Register 2 to be set to 1.

### 4.3 Supply Voltage

### 4.3.1 Operating Supply Voltage

Before selecting the memory and issuing commands to it, a valid and stable  $V_{CC}$  voltage within the specified  $[V_{CC}(min), V_{CC}(max)]$  range must be applied (see operating ranges). To secure a stable DC supply voltage, it is recommended to decouple the  $V_{CC}$  line with a suitable capacitor (usually of the order of 100 nF to 1  $\mu$ F) close to the  $V_{CC}/V_{SS}$  package pins. This voltage must remain stable and valid until the end of the transmission of the command; for a Write command, it must be stable until the completion of the internal write cycle.

### 4.3.2 Power-up Conditions

When the power supply is turned on,  $V_{CC}$  rises continuously from  $V_{SS}$  to  $V_{CC}$ . During this time, the  $\overline{CS}$  line is not allowed to float; it must follow the  $V_{CC}$  voltage. Thus, it is recommended to connect the  $\overline{CS}$  line to  $V_{CC}$  through a suitable pull-up resistor. Also, the  $\overline{CS}$  input offers a built-in safety feature: the  $\overline{CS}$  input is edge sensitive and level sensitive: after power-up, the device does not become selected until a falling edge has first been detected on  $\overline{CS}$ . This ensures that  $\overline{CS}$  must have been high before going low to start the first operation.

#### 4.3.3 Device Reset

To prevent inadvertent Write operations during power-up (continuous rise of  $V_{CC}$ ), a power-on reset (POR) circuit is included. At power-up, the device does not respond to any command until  $V_{CC}$  has reached the power-on reset threshold voltage (this threshold is lower than the minimum  $V_{CC}$  operating voltage defined in Power-up Timing). When  $V_{CC}$  has passed the POR threshold, the device is reset.

#### 4.3.4 Power-Down

At power-down (continuous decrease in  $V_{CC}$ ), as soon as  $V_{CC}$  drops from the normal operating voltage to below the power-on reset threshold voltage ( $V_{WI}$ ), the device stops responding to any command sent to it. During power-down, the device must be deselected ( $\overline{CS}$  must be allowed to follow the voltage applied on  $V_{CC}$ ) and in Standby power mode (there must be no internal Write cycle in progress).

### 4.4 Active Power and Standby Power Modes

When  $\overline{CS}$  is low, the device is selected, and in the Active Power mode. The device consumes  $I_{CC}$ . When  $\overline{CS}$  is high, the device is deselected. If a Write cycle is not currently in progress, the device then goes in to the Standby Power mode, and the device consumption drops to  $I_{CC1}$ .

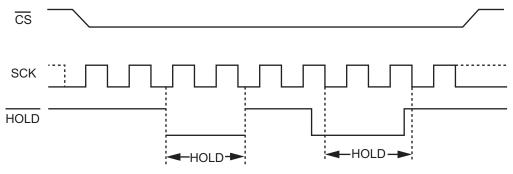

### 4.5 Hold Condition

When QE=0, HOLD=0, the HOLD signal is used to pause any serial communications with the device without resetting the clocking sequence, but does not stop the in-progress operation of write status register, programming, or erasing. During the Hold condition, the Serial Data Output (SO) is high impedance, and Serial Data Input (SI) and SCK are don't care. To enter the Hold condition, the device must be selected, with CS low. Normally, the device is kept selected for the whole duration of the Hold condition. Deselecting the device while it is in the Hold condition, has the effect of resetting the state of the device, and this mechanism can be used if it is required to reset any processes that had been in progress. The Hold condition starts when the HOLD signal is driven low at the same time as SCK already being low (Figure 4). The Hold condition ends when the HOLD signal is driven high at the same time as Serial Clock (SCK) is low. Figure 4 also shows what happens if the rising and falling edges are not timed to coincide with SCK being low.

Figure 4. Hold Condition Activation

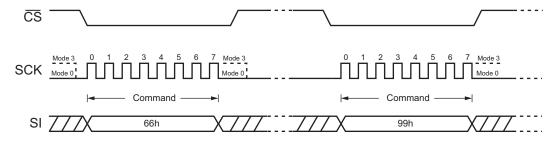

#### 4.6 Software Reset

The AT25EU0041A can be reset to the initial power-on state by a software reset sequence. This sequence must include two consecutive commands: Enable Reset (66h) and Reset (99h). If the command sequence is accepted, the device takes approximately 300  $\mu$ s (t<sub>RST</sub>) to reset. No command is accepted during the reset period.

# 5. Status and Configuration Registers

# 5.1 Status Register 1

Table 3 shows the bit assignments for Status Register 1.

Table 3. Status Register 1 Format

| Bit # | Acronym | Name                            | Туре | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|---------|---------------------------------|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | SRP0    | Status<br>Register<br>Protect 0 | R/W  | 0       | The Status Register Protect 0 bit is a non-volatile bit that, along with the SRP1 and WP bits, controls the method of write protection: software protection, hardware protection, power supply lock-down, or one time programmable protection. See Table 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6:2   | BP4-BP0 | Block<br>Protect Size           | R/W  | 0       | The Block Protect (BP4, BP3, BP2, BP1, BP0) bits are non-volatile. They define the size of the area to be software-protected against Program and Erase commands. These bits are written with the Write Status Register command. When the Block Protect (BP4, BP3, BP2, BP1, BP0) bits are set to 1, the relevant memory (as defined in Table 6 and Table 7) becomes protected against Page Program, Page Erase, and Block Erase commands. The Block Protect (BP4, BP3, BP2, BP1, BP0) bits can be written provided that the Hardware Protected mode has not been set. The Chip Erase command is executed if the Block Protect (BP2, BP1, and BP0) bits are 0 and CMP=0, or the Block Protect (BP2, BP1 and BP0) bits are 1 and CMP=1. |

| 1     | WEL     | Write<br>Enable                 | R    | n/a     | The Write Enable Latch bit indicates the status of the internal Write Enable Latch. When WEL is 1, the internal Write Enable Latch is set, when WEL is 0, the internal Write Enable Latch is reset, and no Write Status Register, Program or Erase command is accepted.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0     | WIP     | Write-in-<br>Progress           | R    | n/a     | The Write in Progress (WIP) bit indicates if the memory is busy programming erasing, or writing to the status register. When set to 1 (the Status Register is being programmed, erased, or written to; when 0, the device is not programming, erasing, writing to the status register.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

# 5.2 Status Register 2

Table 4 shows the bit assignments for Status Register 2.

Table 4. Status Register 2 Format

| Bit # | Acronym  | Name                                   | Type | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|-------|----------|----------------------------------------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7     | SUS      | Suspend<br>Status                      | R    | n/a     | The SUS bit is a read-only bit in Status Register 2 that is set to 1 after executing a Program/Erase Suspend (75h) command. The SUS bit is cleared to 0 by a Program/Erase Resume (7Ah) command, Software Reset (66h/99h) command, or power-down, power-up cycle.                                                                                                                                                                                  |  |  |  |  |  |  |

| 6     | СМР      | Complement<br>Protect                  | R/W  | 0       | The Complement Protect bit is a non-volatile read/write bit in the status register that is used in conjunction with the BP4, BP3, BP2, BP1, and BP0 bits to provide more flexibility for the array protection. See the Table 5 for details.                                                                                                                                                                                                        |  |  |  |  |  |  |

| 5:3   | LB3-LB1  | Write-Protect<br>and Control<br>Status | R    | 0       | The LB bits are non-volatile One-Time Program (OTP) bits in the Status Register (S13-S11) that provide the write protect control and status to the Security Registers. The default state of LB is 0 (the security registers are unlocked). LB can be set to 1 individually using the Write Register command. LB is One-Time Programmable; once it is set to 1, the Security Registers becomes read-only permanently (LB3-1 corresponds to S13-11). |  |  |  |  |  |  |

| 2     | Reserved |                                        | R    | n/a     | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 1     | QE       | Quad Enable                            | n/a  | 0       | This is a non-volatile read/write bit that allows Quad SPI operation. When 0, the $\overline{WP}$ and $\overline{HOLD}$ pins are enabled. When set to 1, the quad $IO_2$ and $IO_3$ pins are enabled. Never set the QE pin to 1 during standard SPI or dual SPI operation if the $\overline{WP}$ and $\overline{HOLD}$ pins are connected directly to the power supply or ground.                                                                  |  |  |  |  |  |  |

| 0     | SRP1     | Status<br>Register<br>Protect 1        | R/W  | 0       | The Status Register Protect 1 is a non-volatile Read/Write bit that, along with the SRP0 and WP bits, controls the method of write protection: software protection, hardware protection, power supply lock-down, or one time programmable protection. See Table 5.                                                                                                                                                                                 |  |  |  |  |  |  |

# 5.3 Status Register Protection

Note that the default value is set by the manufacturer during wafer sort; it is marked as default in Table 5.

**Table 5. Status Register Protect Table**

| SRP1 | SRP0 | WP | Status Register                                                              | Description                                                                                        |  |  |

|------|------|----|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|

| 0    | 0    | Х  | Software Protected                                                           | The Status Register can be written to after a Write Enable command, WEL=1 (default).               |  |  |

| 0    | 1    | 0  | 0 Hardware Protected WP = 0, the Status Register is locked and cannot be wri |                                                                                                    |  |  |

| 0    | 1    | 1  | Hardware Unprotected                                                         | WP = 1, the Status Register is unlocked and can be written to after a Write Enable command, WEL=1. |  |  |

| 1    | 0    | Х  | Power Supply Lock-Down <sup>1</sup>                                          | Status Register is protected and cannot be written to until the next power-down, power-up cycle.   |  |  |

| 1    | 1    | х  | One-Time Program                                                             | Status Register is permanently protected and cannot be written to.                                 |  |  |

<sup>1.</sup> When SRP1, SRP0= (1, 0), a power-down, power-up cycle changes SRP1, SRP0 to (0, 0) state.

<sup>2.</sup> The One-Time Program feature is available upon special order. Contact Renesas Electronics for details.

# 5.4 Status Register Memory Protection

### 5.4.1 Protection Tables

Table 6: Memory Array with CMP = 0

| Statu | ıs Regis | ter Pro | tection   | Bits <sup>1</sup> | Memory Content <sup>2</sup> |                 |                      |                   |  |  |  |

|-------|----------|---------|-----------|-------------------|-----------------------------|-----------------|----------------------|-------------------|--|--|--|

| BP4   | ВР3      | BP2     | 2 BP1 BP0 |                   | Protected<br>Block(s)       | Address Range   | Protected<br>Density | Protected Portion |  |  |  |

| Χ     | Х        | 0       | 0         | 0                 | None                        | None            | None                 | None              |  |  |  |

| 0     | 0        | 0       | 0         | 1                 | 7                           | 070000h-07FFFFh | 64 kB                | Upper 1/8         |  |  |  |

| 0     | 0        | 0       | 1         | 0                 | 6 and 7                     | 060000h-07FFFFh | 128 kB               | Upper 1/4         |  |  |  |

| 0     | 0        | 0       | 1         | 1                 | 4 to 7                      | 040000h-07FFFFh | 256 kB               | Upper 1/2         |  |  |  |

| 0     | 1        | 0       | 0         | 1                 | 0                           | 000000h-00FFFFh | 64 kB                | Lower 1/8         |  |  |  |

| 0     | 1        | 0       | 1         | 0                 | 0 to 1                      | 000000h-01FFFFh | 128 kB               | Lower 1/4         |  |  |  |

| 0     | 1        | 0       | 1         | 1                 | 0 to 3                      | 000000h-03FFFFh | 256 kB               | Lower 1/2         |  |  |  |

| 0     | Х        | 1       | Х         | Х                 | 0 to 7                      | 000000h-07FFFFh | 512 kB               | All               |  |  |  |

| 1     | 0        | 0       | 0         | 1                 | 7                           | 07F000h-07FFFFh | 4 kB                 | Upper 1/128       |  |  |  |

| 1     | 0        | 0       | 1         | 0                 | 7                           | 07E000h-07FFFFh | 8 kB                 | Upper 1/64        |  |  |  |

| 1     | 0        | 0       | 1         | 1                 | 7                           | 07C000h-07FFFFh | 16 kB                | Upper 1/32        |  |  |  |

| 1     | 0        | 1       | 0         | Х                 | 7                           | 078000h-07FFFFh | 32 kB                | Upper 1/16        |  |  |  |

| 1     | 0        | 1       | 1         | 0                 | 7                           | 078000h-07FFFFh | 32 kB                | Upper 1/16        |  |  |  |

| 1     | 1        | 0       | 0         | 1                 | 0                           | 000000h-000FFFh | 4 kB                 | Lower 1/128       |  |  |  |

| 1     | 1        | 0       | 1         | 0                 | 0                           | 000000h-001FFFh | 8 kB                 | Lower 1/64        |  |  |  |

| 1     | 1        | 0       | 1         | 1                 | 0                           | 000000h-003FFFh | 16 kB                | Lower 1/32        |  |  |  |

| 1     | 1        | 1       | 0         | Х                 | 0                           | 000000h-007FFFh | 32 kB                | Lower 1/16        |  |  |  |

| 1     | 1        | 1       | 1         | 0                 | 0                           | 000000h-007FFFh | 32 kB                | Lower 1/16        |  |  |  |

| 1     | Х        | 1       | 1         | 1                 | 0 to 7                      | 000000h-07FFFFh | 512 kB               | All               |  |  |  |

<sup>1.</sup> X = don't care

<sup>2.</sup> If any Erase or Program command specifies a memory region that contains a protected data portion, that command is ignored.

Table 7. Memory Array with CMP = 1

|                | Pro | otection E | Bits |     | Memory Content <sup>2</sup> |                 |                      |                   |  |

|----------------|-----|------------|------|-----|-----------------------------|-----------------|----------------------|-------------------|--|

| BP4            | ВР3 | BP2        | BP1  | BP0 | Protected<br>Block(s)       | Address Range   | Protected<br>Density | Protected Portion |  |

| X <sup>1</sup> | Х   | 0          | 0    | 0   | 0 to 7                      | 000000h-07FFFFh | 512 kB               | All               |  |

| 0              | 0   | 0          | 0    | 1   | 0 to 6                      | 000000h-06FFFFh | 448 kB               | Lower 7/8         |  |

| 0              | 0   | 0          | 1    | 0   | 0 and 5                     | 000000h-05FFFFh | 384 kB               | Lower 3/4         |  |

| 0              | 0   | 0          | 1    | 1   | 0 to 3                      | 000000h-03FFFFh | 256 kB               | Lower 1/2         |  |

| 0              | 1   | 0          | 0    | 1   | 1 to 7                      | 010000h-07FFFFh | 448 kB               | Upper 7/8         |  |

| 0              | 1   | 0          | 1    | 0   | 2 to 7                      | 020000h-07FFFFh | 384 kB               | Upper 3/4         |  |

| 0              | 1   | 0          | 1    | 1   | 4 to 7                      | 040000h-07FFFFh | 256 kB               | Upper 1/2         |  |

| 0              | Х   | 1          | Х    | Х   | None                        | None None       |                      | None              |  |

| 1              | 0   | 0          | 0    | 1   | 0 to 7                      | 000000h-07EFFFh | 508 kB               | Lower 127/128     |  |

| 1              | 0   | 0          | 1    | 0   | 0 to 7                      | 000000h-07DFFFh | 504 kB               | Lower 63/64       |  |

| 1              | 0   | 0          | 1    | 1   | 0 to 7                      | 000000h-07BFFFh | 496 kB               | Lower 31/32       |  |

| 1              | 0   | 1          | 0    | Х   | 0 to 7                      | 000000h-077FFFh | 480 kB               | Lower 15/16       |  |

| 1              | 0   | 1          | 1    | 0   | 0 to 7                      | 000000h-077FFFh | 480 kB               | Lower 15/16       |  |

| 1              | 1   | 0          | 0    | 1   | 0 to 7                      | 001000h-07FFFFh | 508 kB               | Upper 127/128     |  |

| 1              | 1   | 0          | 1    | 0   | 0 to 7                      | 002000h-07FFFFh | 504 kB               | Upper 63/64       |  |

| 1              | 1   | 0          | 1    | 1   | 0 to 7                      | 004000h-07FFFFh | 496 kB               | Upper 31/32       |  |

| 1              | 1   | 1          | 0    | Х   | 0 to 7                      | 008000h-07FFFFh | 480 kB               | Upper 15/16       |  |

| 1              | 1   | 1          | 1    | 0   | 0 to 7                      | 008000h-07FFFFh | 480 kB               | Upper 15/16       |  |

| 1              | Х   | 1          | 1    | 1   | None                        | None            | None                 | None              |  |

<sup>1.</sup> X = don't care.

<sup>2.</sup> If any Erase or Program command specifies a memory region that contains protected data portion, this command is ignored.

### 6. Command Set

All commands, addresses, and data are transferred into and out of the device, beginning with the most significant bit on the first rising edge of SCK after  $\overline{CS}$  is driven low. Then, the one-byte opcode must be transferred into the device on SI, most significant bit first, each bit being latched on a rising edge of SCK.

Every command sequence starts with a one-byte opcode. Depending on the command, this might be followed by address bytes. See Table 8.

For the Read, Fast Read, Read Status Register 1, Read Status Register 2 or Release from Deep Power-Down, or Read Device ID command, the transferred-in command sequence is followed by a data out sequence. CS can be driven high after any bit of the data-out sequence is being transferred out.

For the Page Program, Page Erase, Block Erase, Chip Erase, Write Status Register, Write Enable, Write Disable or Deep Power-Down command,  $\overline{CS}$  must be driven high exactly at a byte boundary; otherwise, the command is rejected. ( $\overline{CS}$  must drive high when the number of clock pulses after  $\overline{CS}$  being driven low is an exact multiple of eight.) For Page Program, if at any time the input byte is not a full byte, nothing happens, and WEL is not reset.

Table 8. Command Set Table 1

| Table 6. Command Set Table                  |         |                              |                             |                      |                      |                      |              |  |  |  |  |

|---------------------------------------------|---------|------------------------------|-----------------------------|----------------------|----------------------|----------------------|--------------|--|--|--|--|

| <b>Command Name</b>                         | Byte 1  | Byte 2                       | Byte 3                      | Byte 4               | Byte 5               | Byte 6               | n- Bytes     |  |  |  |  |

| Read                                        | ·       |                              |                             |                      |                      |                      |              |  |  |  |  |

| Normal Read Data                            | 03h     | A23-A16                      | A15-A8                      | A7-A0                | (D7-D0)              | (Next Byte)          | (continuous) |  |  |  |  |

| Fast Read                                   | 0Bh     | A23-A16                      | A15-A8                      | A7-A0                | Dummy                | (D7-D0)              | (continuous) |  |  |  |  |

| Dual Output Fast Read                       | 3Bh     | A23-A16                      | A15-A8                      | A7-A0                | Dummy                | (D7-D0) <sup>2</sup> | (continuous) |  |  |  |  |

| Quad Output Fast Read                       | 6Bh     | A23-A16                      | A15-A8                      | A7-A0                | Dummy                | (D7-D0) <sup>3</sup> | (continuous) |  |  |  |  |

| Dual I/O Fast Read                          | BBh     | A23-A8 <sup>4</sup>          | A7-A0<br>M7-M0 <sup>4</sup> | (D7-D0)              |                      |                      | (continuous) |  |  |  |  |

| Quad I/O Fast Read                          | EBh     | A23-A0<br>M7-M0 <sup>5</sup> | Dummy                       | (D7-D0) <sup>6</sup> |                      |                      | (continuous) |  |  |  |  |

| Set Burst with Wrap                         | 77h     | W6-W4                        |                             |                      |                      |                      |              |  |  |  |  |

| Program/Erase and Suspe                     | end     |                              |                             | ·                    | 1                    | 1                    |              |  |  |  |  |

| Page Program                                | 02h     | A23-A16                      | A15-A8                      | A7-A0                | (D7-D0) <sup>7</sup> | (Next Byte)          |              |  |  |  |  |

| Dual Page Program                           | A2h     | A23-A16                      | A15-A8                      | A7-A0                | (D7-D0) <sup>7</sup> | (Next Byte)          |              |  |  |  |  |

| Quad Page Program                           | 32h     | A23-A16                      | A15-A8                      | A7-A0                | (D7-D0) <sup>7</sup> | (Next Byte)          |              |  |  |  |  |

| Page Erase                                  | 81h/DBh | A23-A16                      | A15-A8                      | A7-A0                | (D7-D0) <sup>7</sup> | (Next Byte)          |              |  |  |  |  |

| Block Erase (4 kB)                          | 20h     | A23-A16                      | A15-A8                      | A7-A0                | (D7-D0) <sup>7</sup> | (Next Byte)          |              |  |  |  |  |

| Block Erase (32 kB)                         | 52h     | A23-A16                      | A15-A8                      | A7-A0                |                      |                      |              |  |  |  |  |

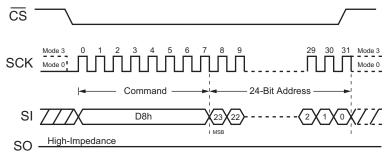

| Block Erase (64 kB)                         | D8h     | A23-A16                      | A15-A8                      | A7-A0                |                      |                      |              |  |  |  |  |

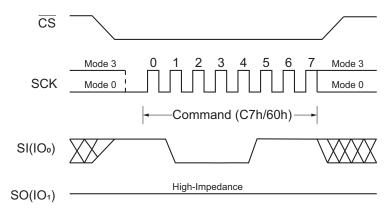

| Chip Erase                                  | C7h/60h |                              |                             |                      |                      |                      |              |  |  |  |  |

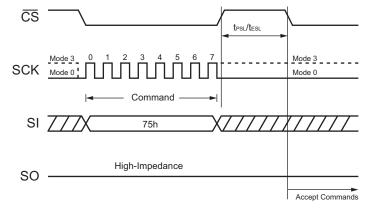

| Program/Erase Suspend                       | 75h     |                              |                             |                      |                      |                      |              |  |  |  |  |

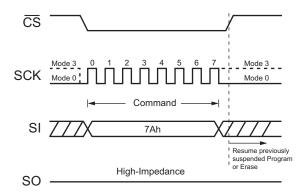

| Program/Erase Resume                        | 7Ah     |                              |                             |                      |                      |                      |              |  |  |  |  |

| Security                                    |         |                              |                             | ·                    | 1                    | 1                    |              |  |  |  |  |

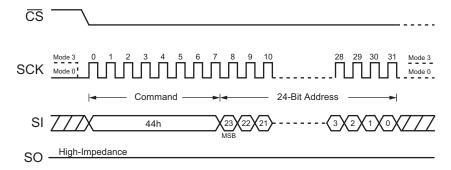

| Erase Security Registers                    | 44h     | A23-A16 <sup>8</sup>         | A15-A8 <sup>8</sup>         | A7-A0 <sup>8</sup>   |                      |                      |              |  |  |  |  |

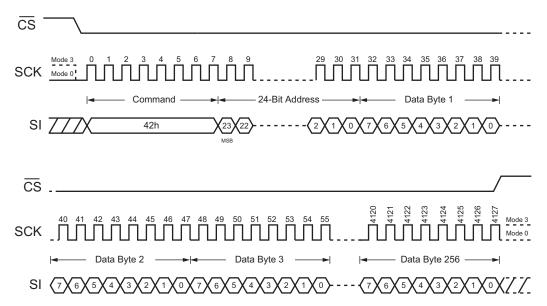

| Program Security<br>Registers               | 42h     | A23-A16 <sup>8</sup>         | A15-A8 <sup>8</sup>         | A7-A0 <sup>8</sup>   | D7-D0                | Next Byte            |              |  |  |  |  |

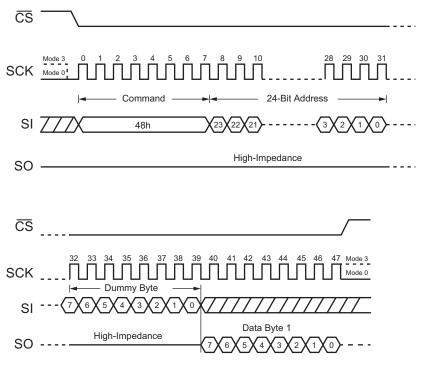

| Read Security Registers                     | 48h     | A23-A16 <sup>8</sup>         | A15-A8 <sup>8</sup>         | A7-A0 <sup>8</sup>   | Dummy                | D7-D0                |              |  |  |  |  |

| Read Serial Flash<br>Discoverable Parameter | 5Ah     | A23-A16                      | A15-A8                      | A7-A0                | Dummy                | (D7-D0)              | (continuous) |  |  |  |  |

| Configuration                               | -       |                              | 1                           |                      | 1                    | •                    |              |  |  |  |  |

| Write Enable                                | 06h     |                              |                             |                      |                      |                      |              |  |  |  |  |

| Volatile SR Write Enable                    | 50h     |                              |                             |                      |                      |                      |              |  |  |  |  |

| Write Disable                               | 04h     |                              |                             |                      |                      |                      |              |  |  |  |  |

| Table 8. | Command | Set Table 1 | (Cont.) |

|----------|---------|-------------|---------|

|----------|---------|-------------|---------|

| Command Name             | Byte 1 | Byte 2                         | Byte 3                          | Byte 4                 | Byte 5                  | Byte 6                                             | n- Bytes     |

|--------------------------|--------|--------------------------------|---------------------------------|------------------------|-------------------------|----------------------------------------------------|--------------|

| Status Register          | 1      | 1                              | I                               | L                      | 1                       | 1                                                  |              |

| Read Status Register 1   | 05h    | (S7-S0) <sup>9</sup>           |                                 |                        |                         |                                                    | (continuous) |

| Write Status Register 10 | 01h    | S7-S0                          | S15-S8                          |                        |                         |                                                    |              |

| Read Status Register 2   | 35h    | (S15-S8) <sup>9</sup>          |                                 |                        |                         |                                                    | (continuous) |

| Active Status Interrupt  | 25h    |                                |                                 |                        |                         |                                                    |              |

| ID and Power             | •      |                                |                                 |                        |                         |                                                    |              |

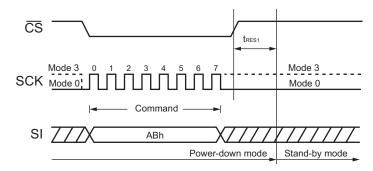

| Deep Power-down          | B9h    |                                |                                 |                        |                         |                                                    |              |

| Release Power-down / ID  | ABh    | Dummy                          | Dummy                           | Dummy                  | ID7-ID0                 |                                                    | (continuous) |

| Release Power-down       | ABH    |                                |                                 |                        |                         |                                                    |              |

| Manufacturer/Device ID   | 90h    | Dummy                          | Dummy                           | 00/01h                 | (MF7-MF0)/<br>(ID7-ID0) | (ID7-ID0) <sup>9</sup> /<br>(MF7-MF0) <sup>9</sup> | (continuous) |

| Mftr./Device ID Dual IO  | 92h    | A23-A8 <sup>4</sup>            | A7-A0 <sup>4</sup><br>(M7-M0)   | (M7-M0)<br>(D7-D0)     |                         |                                                    | (continuous) |

| Mftr./Device ID Quad IO  | 94h    | A23-A0<br>(M7-M0) <sup>5</sup> | (M7-M0)<br>(D7-D0) <sup>6</sup> |                        |                         |                                                    | (continuous) |

| Read JEDEC ID            | 9Fh    | (MF7-MF0)                      | (ID15-ID8)                      | (ID7-ID0) <sup>9</sup> |                         |                                                    | (continuous) |

| Read Unique ID Number    | 4Bh    | Dummy                          | Dummy                           | Dummy                  | Dummy                   | (ID127-ID0)                                        |              |

| Other Commands           |        |                                | 1                               | 1                      |                         | ,                                                  |              |

| Enable Reset             | 66h    |                                |                                 |                        |                         |                                                    |              |

| Reset Device             | 99h    |                                |                                 |                        |                         |                                                    |              |

- 1. Data bytes are transferred with Most Significant Bit first. Byte fields with data in parenthesis ( ) indicate data output from the device.

- 2. Dual SPI data output format:

- $IO_0 = (D6, D4, D2, D0)$

- $IO_1 = (D7, D5, D3, D1)$

- 3. Quad SPI data output format:

- $IO_0 = (D4, D0, ....)$

- $IO_1 = (D5, D1, ....)$

- IO<sub>2</sub> = (D6, D2, .....)

- $IO_3 = (D7, D3, ....)$

- 4. Dual SPI address input format:

- IO<sub>0</sub> = A22, A20, A18, A16, A14, A12, A10, A8, A6, A4, A2, A0, M6, M4, M2, M0

- IO<sub>1</sub> = A23, A21, A19, A17, A15, A13, A11, A9, A7, A5, A3, A1, M7, M5, M3, M1

- 5. Quad SPI address input format:

- $IO_0$  = A20, A16, A12, A8, A4, A0, M4, M0

- IO<sub>1</sub> = A21, A17, A13, A9, A5, A1, M5, M1

- IO<sub>2</sub> = A22, A18, A14, A10, A6, A2, M6, M2

- $IO_3 = A23$ , A19, A15, A11, A7, A3, M7, M3

- 6. Fast Read Quad I/O data output format:

- $IO_0 = (x, x, x, x, D4, D0, D4, D0)$

- $IO_1 = (x, x, x, x, D5, D1, D5, D1)$

- $IO_2 = (x, x, x, x, D6, D2, D6, D2)$

- $IO_3^- = (x, x, x, x, D7, D3, D7, D3)$

- 7. At least one byte of data input is required for Page Program, Dual Page Program, Quad Page Program and Program Security Registers, up to 256 bytes of data input. If more than 256 bytes of data are sent to the device, the addressing wraps to the beginning of the page and overwrites previously sent data.

- 8. Security Register Address:

- Security Register 1 A23-16 = 00h A15-9 = 0001000 A8-0 = byte address Security Register 2 A23-16 = 00h A15-9 = 0010000 A8-0 = byte address

- 9. The Status Register contents and Device ID repeat continuously until  $\overline{\text{CS}}$  terminates the command.

- 10. Write Status Register (01h) can also be used to write Status Register 1 and 2, see Table 6.1.6.

### 6.1 Configuration and Status Commands

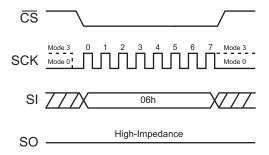

### 6.1.1 Write Enable (06h)

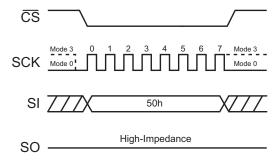

The Write Enable command sets the Write Enable Latch (WEL) bit in the Status Register to 1. The WEL bit must be set before every Page Program, Page Erase, Block Erase, Chip Erase, Write Status Register, and Erase/Program Security Registers command. The Write Enable command is entered by driving  $\overline{CS}$  low, transferring the opcode 06h into the Data Input (SI) pin on the rising edge of SCK, and then driving  $\overline{CS}$  high.

Figure 5. Write Enable Command for SPI Mode

#### 6.1.2 Write Enable for Volatile Status Register (50h)

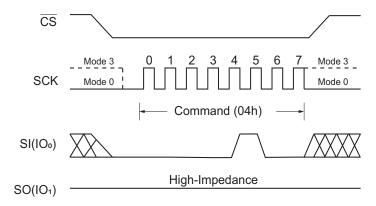

The non-volatile Status Register bits described in Section 5 can also be written to as volatile bits. This gives more flexibility to change the system configuration and memory protection schemes quickly without waiting for the typical non-volatile bit write cycles or affecting the endurance of the Status Register non-volatile bits. To write the volatile values into the Status Register bits, the Write Enable for Volatile Status Register (50h) command must be issued before a Write Status Register (01h) command. The Write Enable for Volatile Status Register command does not set the Write Enable Latch (WEL) bit; it is only valid for the Write Status Register command to change the volatile Status Register bit values.

Figure 6. Write Enable for Volatile Status Register (50h)

### 6.1.3 Write Disable (04h)

The Write Disable command resets the Write Enable Latch (WEL) bit in the Status Register to 0. The Write Disable command is entered by driving  $\overline{\text{CS}}$  low, transferring the opcode 04h onto the SI pin, and then driving  $\overline{\text{CS}}$  high. Note that the WEL bit is automatically reset after power-up and upon completion of the Write Status Register, Erase/Program Security Registers, Page Program, Page Erase, Block Erase, Chip Erase, and Reset command.

Figure 7. Write Disable Command, SPI Mode

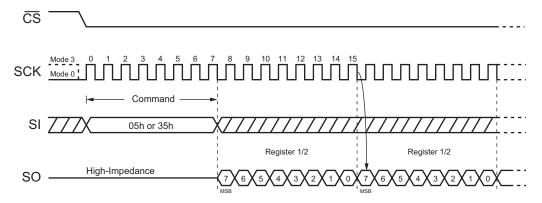

### 6.1.4 Read Status Register 1 (05h), Status Register 2 (35h)

The Read Status Register commands allow the eight-bit Status Registers to be read. The command is entered by driving  $\overline{\text{CS}}$  low and transferring the opcode 05h for Status Register 1, 35h for Status Register 2 onto the SI pin on the rising edge of SCK. The status register bits are then transferred out on the SO pin at the falling edge of SCK, with most significant bit (MSB) first, as shown in Figure 8. See Section 5 for Status Register descriptions. The Read Status Register command can be used at any time, even while a Program, Erase or Write Status Register cycle is in progress. This allows the RDY/BSY status bit to be checked to determine when the cycle is complete and if the device can accept another command. The Status Register can be read continuously, as shown in Figure 8. The command is completed by driving  $\overline{\text{CS}}$  high.

Figure 8. Read Status Register Command

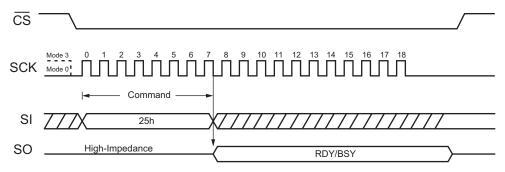

### 6.1.5 Active Status Interrupt (25h)

The Active Status Interrupt improves the ability to determine if the device is busy or not. It is not necessary to continuously read the Status Register; it is sufficient to monitor the value of the SO line. If the SO line is connected to an interrupt line on the host controller, the host controller can be in sleep mode until the SO line indicates that the device is ready for the next command. The RDY/BSY bit can be read at any time, including during an internally self-timed program or erase operation. To enable the Active Status Interrupt command, the  $\overline{\text{CS}}$  pin must first be asserted, and the opcode of 25h must be clocked into the device. The value of the SI line after the opcode being clocked in is of no significance to the operation. The value of RDY/BSY is then output on the SO line, and is continuously updated by the device for as long as the  $\overline{\text{CS}}$  pin remains asserted. Additional clocks on the SCK pin are not required. That is, whether the additional clock on the SCK pin exists is independent of the correct output of the value of RDY/BSY. (Figure 9 shows a case where additional clocks exist.) If the RDY/BSY bit changes from 1 to 0 while the  $\overline{\text{CS}}$  pin is asserted, the SO line changes from 1 to 0. (The RDY/BSY bit cannot change from 0 to 1 during an operation; so, if the SO line already is 0, it does not change.) Deasserting the  $\overline{\text{CS}}$  pin terminates the Active Status Interrupt operation and puts the SO pin into a high-impedance state. The sequence of issuing the ASI command is:  $\overline{\text{CS}}$  goes low  $\rightarrow$  sending ASI opcode  $\rightarrow$  RDY/BSY data out on SO.

Figure 9. Active Status Interrupt Command

### 6.1.6 Write Status Register (01h)

The Write Status Register command allows the Status Registers to be written. Status Register 1 can be written by the Write Status Register 01h command; Status Register 2 be written by the Write Status Register 01h command. When the Write Status Register command 01h writes one byte data, it is written to Status Register 1. When the Write Status Register command 01h writes two bytes of data, the first byte data is written to Status Register 1, and the second byte data is written to Status Register 2. The writable Status Register bits include: SRP0, BP[4:0] in Status Register 1. All other Status Register bit locations are read-only and are not affected by the Write Status Register command. LB[3:1] are non-volatile OTP bits; once set to 1, they cannot be cleared to 0.

The Write Status Register (WRSR) command allows new values to be written to the Status Register. Before it can be accepted, a Write Enable (WREN) or Write Enable For Volatile SR command must previously have been executed After the Write Enable (WREN) command has been decoded and executed, the device sets the Write Enable Latch (WEL).

The Write Status Register command has no effect on S15 (SUS), S1 (WEL), and S0 (RDY/BSY) of the Status Register.  $\overline{CS}$  must be driven high after the 8 or 16 bits of data have been latched in. If not, the Write Status Register (WRSR) command is not executed. As soon as  $\overline{CS}$  is driven high, the self-timed Write Status Register cycle (whose duration is  $t_W$ ) is initiated. While the Write Status Register cycle is in progress, the Status Register can still be read to check the value of the Write In Progress (RDY/BSY) bit. The RDY/BSY bit is 1 during the self-timed Write Status Register cycle; it is 0 when it is completed. When the cycle is completed, the Write Enable Latch (WEL) is reset.

The Write Status Register command lets the user change the values of the Block Protect (BP4, BP3, BP2, BP1, and BP0) bits, to define the size of the area that is to be treated as read-only, as defined in Table 6 and Table 7. The Write Status Register (WRSR) command also lets the user set or reset the Status Register Protect (SRP1 and SRP0) bits in accordance with the Write Protect (WP) signal. The Status Register Protect (SRP1 and SRP0) bits

and Write Protect (WP) signal allow the device to be put in the Hardware Protected Mode. The Write Status Register command is not executed once the Hardware Protected Mode is entered.

The sequence of issuing WRSR command is:  $\overline{CS}$  goes low  $\rightarrow$  sending WRSR opcode  $\rightarrow$  Status Register data on  $SI \rightarrow \overline{CS}$  goes high.

The  $\overline{\text{CS}}$  must go high exactly at the 8-bit or 16-bit data boundary; otherwise, the command is rejected. The self-timed Write Status Register cycle time ( $t_W$ ) is initiated as soon as  $\overline{\text{CS}}$  goes high. The Ready/Busy (RDY/BSY) bit can be checked during the Write Status Register cycle is in progress. The RDY/BSY is set 1 during the  $t_W$  timing, and is set to 0 when the Write Status Register Cycle is completed and the Write Enable Latch (WEL) bit is reset.

Figure 10. Write Status Register Command

#### 6.2 Read Commands

### 6.2.1 Normal Read Data (03h)

The Read Data command allows one or more data bytes to be sequentially read from the memory. The command is initiated by driving the  $\overline{\text{CS}}$  pin low, then transferring the opcode 03h, followed by a 24-bit address (A23-A0), onto the SI pin. The code and address bits are latched on the rising edge of the SCK pin. After the address is received, the data byte of the addressed memory location is transferred out on the SO pin at the falling edge of SCK, with most significant bit (MSB) first. The address is automatically incremented to the next higher address after each byte of data is transferred out, allowing for a continuous stream of data. This means that the entire memory can be accessed with a single command as long as the clock continues. The command is completed by driving  $\overline{\text{CS}}$  high. The Read Data command sequence is shown in Figure 11. If a Read Data command is issued while an Erase, Program, or other Write cycle is in progress (RDY/BSY=1), the command is ignored and has no effect on the current cycle. The Read Data command allows a clock frequency up to a maximum of  $f_R$  (see Section 7.6, AC Characteristics).

Figure 11. Read Data Command

### 6.2.2 Fast Read (0Bh)

The Fast Read command is similar to the Read Data command except that it can operate at the highest possible frequency of  $f_{\mathbb{C}}$  (see Section 7.6, AC Characteristics). In standard SPI mode, this is done by adding eight dummy clocks after the 24-bit address, as shown in Figure 12. The dummy clocks allow the devices internal circuits additional time for setting up the initial address. During the dummy clocks the data value on the SO pin is a don't care.

Figure 12. Fast Read Command

### 6.2.3 Fast Read Dual Output (3Bh)

The Dual-Output Read Array command is similar to the standard Read Array command. Unlike the standard Read Array command, the Dual-Output Read Array command allows two bits of data to be clocked out of the device on every clock cycle, rather than just one.