#### 1 TMS320DM642 Video/Imaging Fixed-Point Digital Signal Processor

#### 1.1 Features

- High-Performance Digital Media Processor

- 2-, 1.67-, 1.39-ns Instruction Cycle Time

- 500-, 600-, 720-MHz Clock Rate

- Eight 32-Bit Instructions/Cycle

- 4000, 4800, 5760 MIPS

- Fully Software-Compatible With C64x™

- VelociTI.2<sup>™</sup> Extensions to VelociTI<sup>™</sup> Advanced Very-Long-Instruction-Word (VLIW) TMS320C64x<sup>™</sup> DSP Core

- Eight Highly Independent Functional Units With VelociTI.2™ Extensions:

- Six ALUs (32-/40-Bit), Each Supports Single 32-Bit, Dual 16-Bit, or Quad 8-Bit Arithmetic per Clock Cycle

- Two Multipliers Support Four 16 x 16-Bit Multiplies (32-Bit Results) per Clock Cycle or Eight 8 x 8-Bit Multiplies (16-Bit Results) per Clock Cycle

- Load-Store Architecture With Non-Aligned Support

- 64 32-Bit General-Purpose Registers

- Instruction Packing Reduces Code Size

- All Instructions Conditional

- Instruction Set Features

- Byte-Addressable (8-/16-/32-/64-Bit Data)

- 8-Bit Overflow Protection

- Bit-Field Extract, Set, Clear

- Normalization, Saturation, Bit-Counting

- VelociTI.2™ Increased Orthogonality

- L1/L2 Memory Architecture

- 128K-Bit (16K-Byte) L1P Program Cache (Direct Mapped)

- 128K-Bit (16K-Byte) L1D Data Cache (2-Way Set-Associative)

- 2M-Bit (256K-Byte) L2 Unified Mapped RAM/Cache (Flexible RAM/Cache Allocation)

- Endianess: Little Endian, Big Endian

- 64-Bit External Memory Interface (EMIF)

- Glueless Interface to Asynchronous Memories (SRAM and EPROM) and Synchronous Memories (SDRAM, SBSRAM, ZBT SRAM, and FIFO)

- 1024M-Byte Total Addressable External Memory Space

- Enhanced Direct-Memory-Access (EDMA)

Controller (64 Independent Channels)

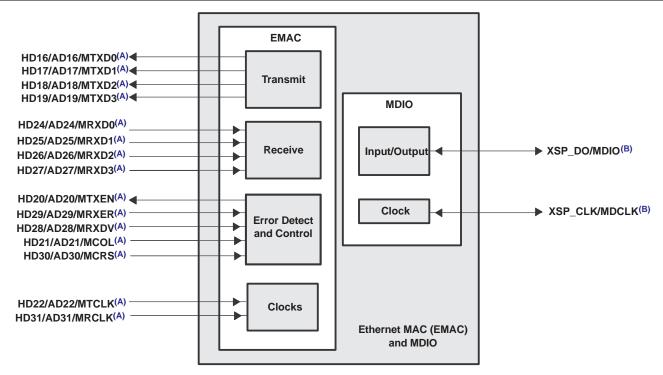

- 10/100 Mb/s Ethernet MAC (EMAC)

- IEEE 802.3 Compliant

- Media Independent Interface (MII)

- 8 Independent Transmit (TX) Channels and 1 Receive (RX) Channel

- Management Data Input/Output (MDIO)

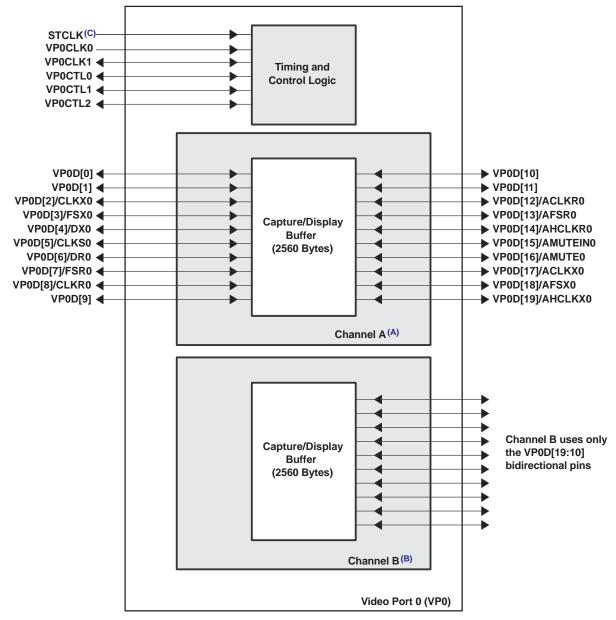

- Three Configurable Video Ports

- Providing a Glueless I/F to Common Video Decoder and Encoder Devices

- Supports Multiple Resolutions/Video Stds

- VCXO Interpolated Control Port (VIC)

- Supports Audio/Video Synchronization

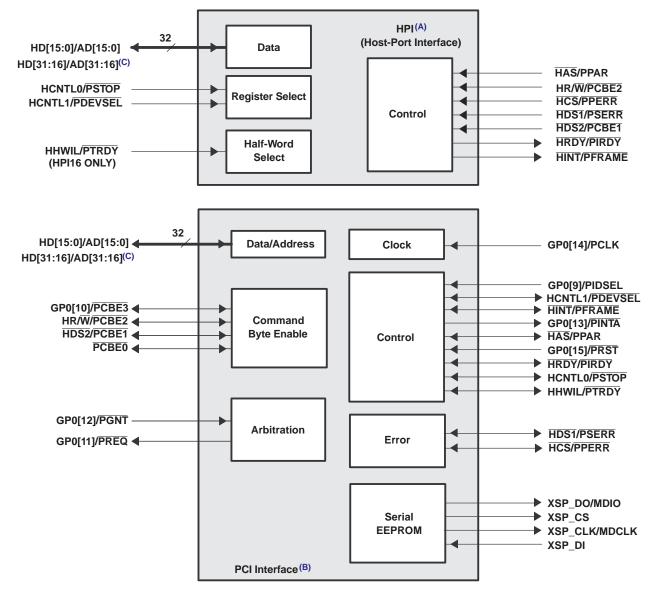

- Host-Port Interface (HPI) [32-/16-Bit]

- 32-Bit/66-MHz, 3.3-V Peripheral Component Interconnect (PCI) Master/Slave Interface Conforms to PCI Specification 2.2

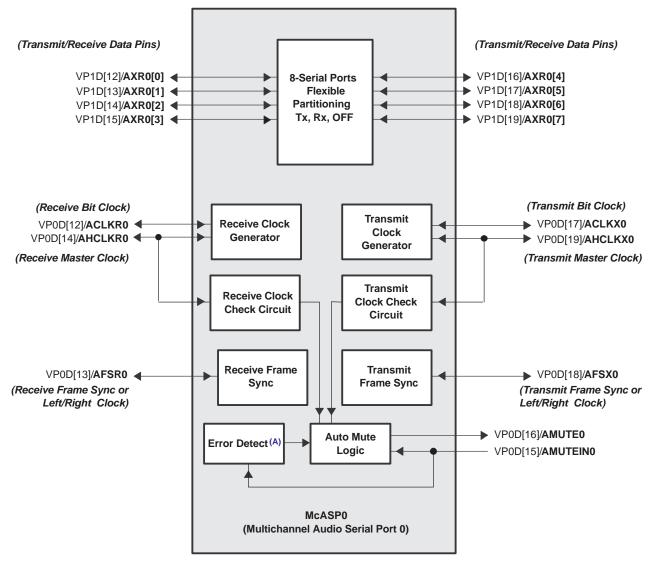

- Multichannel Audio Serial Port (McASP)

- Eight Serial Data Pins

- Wide Variety of I<sup>2</sup>S and Similar Bit Stream Format

- Integrated Digital Audio I/F Transmitter Supports S/PDIF, IEC60958-1, AES-3, CP-430 Formats

- Inter-Integrated Circuit (I<sup>2</sup>C Bus™)

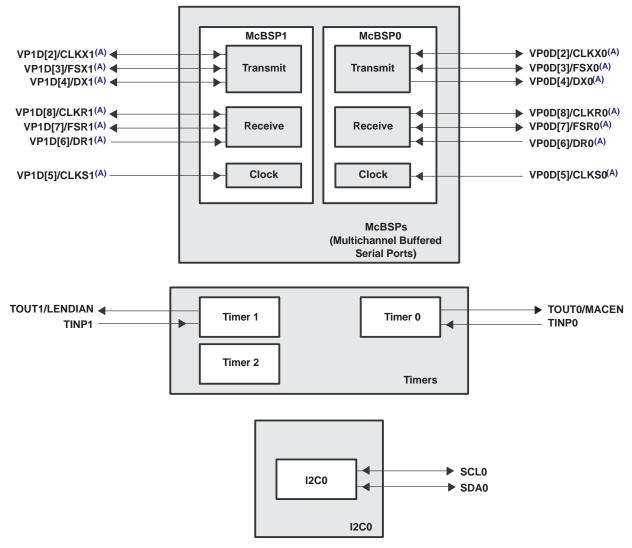

- Two Multichannel Buffered Serial Ports

- Three 32-Bit General-Purpose Timers

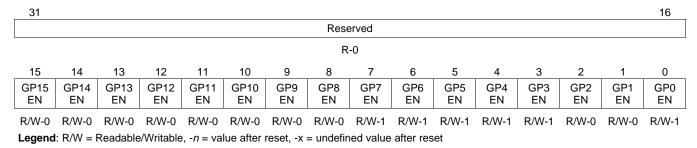

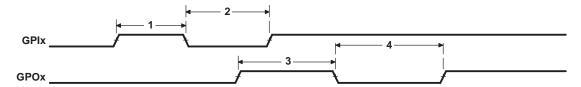

- Sixteen General-Purpose I/O (GPIO) Pins

- Flexible PLL Clock Generator

- IEEE-1149.1 (JTAG) Boundary-Scan-Compatible

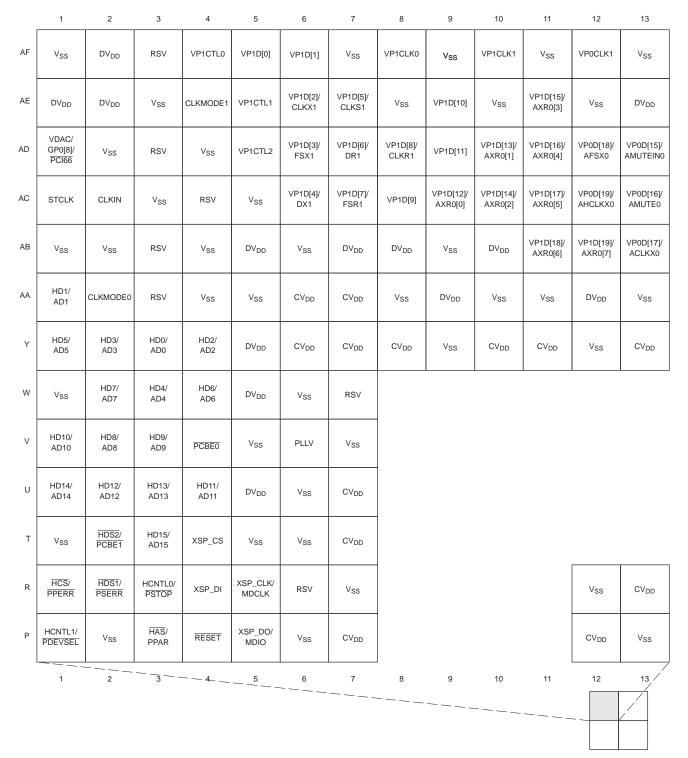

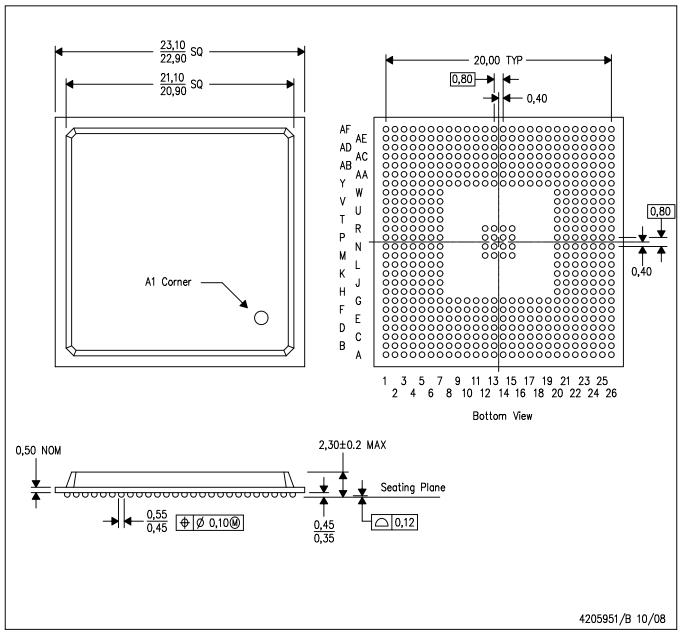

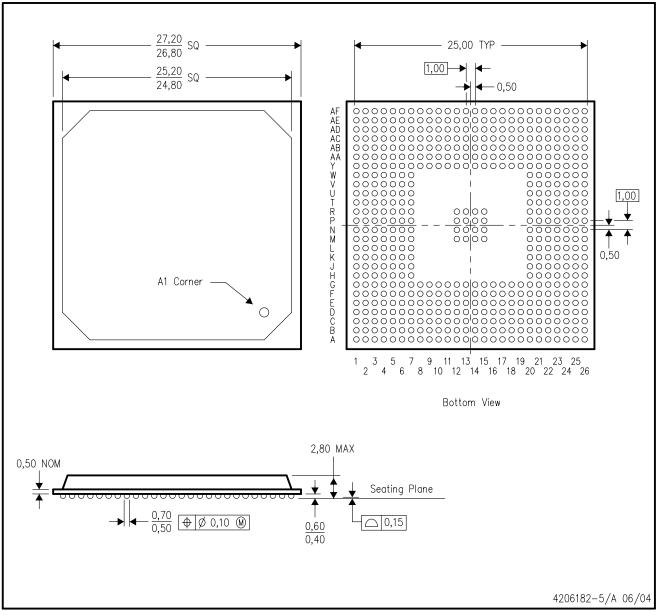

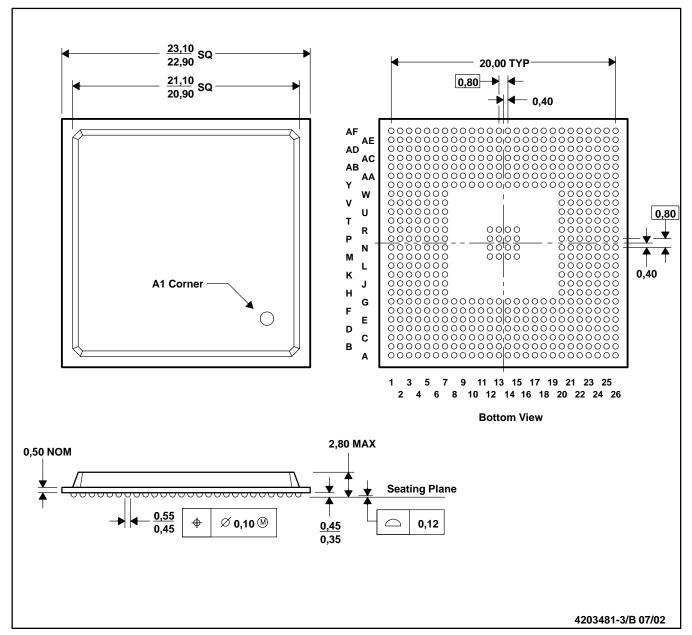

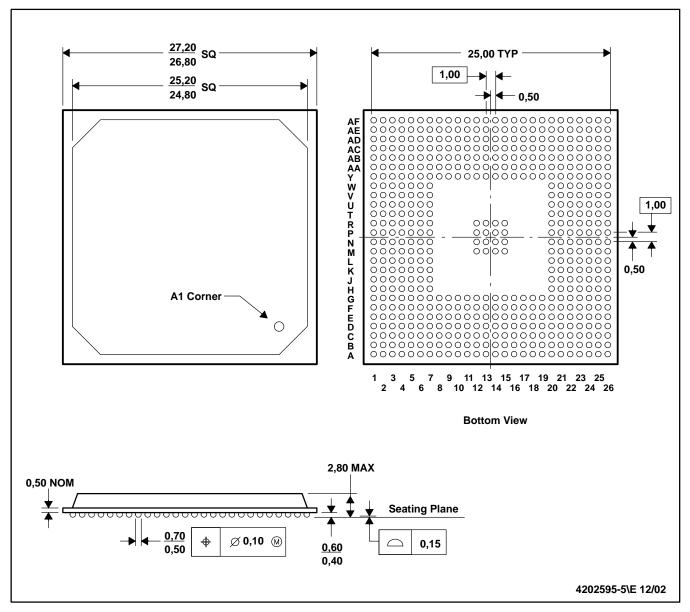

- 548-Pin Ball Grid Array (BGA) Package (GDK and ZDK Suffixes), 0.8-mm Ball Pitch

- 548-Pin Ball Grid Array (BGA) Package (GNZ and ZNZ Suffixes), 1.0-mm Ball Pitch

- 0.13-µm/6-Level Cu Metal Process (CMOS)

- 3.3-V I/O, 1.2-V Internal (-500)

- 3.3-V I/O, 1.4-V Internal (A-500, A-600, -600, -720)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this document.

Windows is a registered trademark of Microsoft Corporation. I<sup>2</sup>C Bus is a trademark of Philips Electronics N.V..

# TMS320DM642 Video/Imaging Fixed-Point Digital Signal Processor

SPRS200L-JULY 2002-REVISED JANUARY 2007

#### 1.2 Description

The TMS320C64x<sup>™</sup> DSPs (including the TMS320DM642 device) are the highest-performance fixed-point DSP generation in the TMS320C6000<sup>™</sup> DSP platform. The TMS320DM642 (DM642) device is based on the second-generation high-performance, advanced VelociTI<sup>™</sup> very-long-instruction-word (VLIW) architecture (VelociTI.2<sup>™</sup>) developed by Texas Instruments (TI), making these DSPs an excellent choice for digital media applications. The C64x<sup>™</sup> is a code-compatible member of the C6000<sup>™</sup> DSP platform.

With performance of up to 5760 million instructions per second (MIPS) at a clock rate of 720 MHz, the DM642 device offers cost-effective solutions to high-performance DSP programming challenges. The DM642 DSP possesses the operational flexibility of high-speed controllers and the numerical capability of array processors. The C64x<sup>™</sup> DSP core processor has 64 general-purpose registers of 32-bit word length and eight highly independent functional units—two multipliers for a 32-bit result and six arithmetic logic units (ALUs)—with VelociTI.2<sup>™</sup> extensions. The VelociTI.2<sup>™</sup> extensions in the eight functional units include new instructions to accelerate the performance in video and imaging applications and extend the parallelism of the VelociTI<sup>™</sup> architecture. The DM642 can produce four 16-bit multiply-accumulates (MACs) per cycle for a total of 2880 million MACs per second (MMACS), or eight 8-bit MACs per cycle for a total of 5760 MMACS. The DM642 DSP also has application-specific hardware logic, on-chip memory, and additional on-chip peripherals similar to the other C6000<sup>™</sup> DSP platform devices.

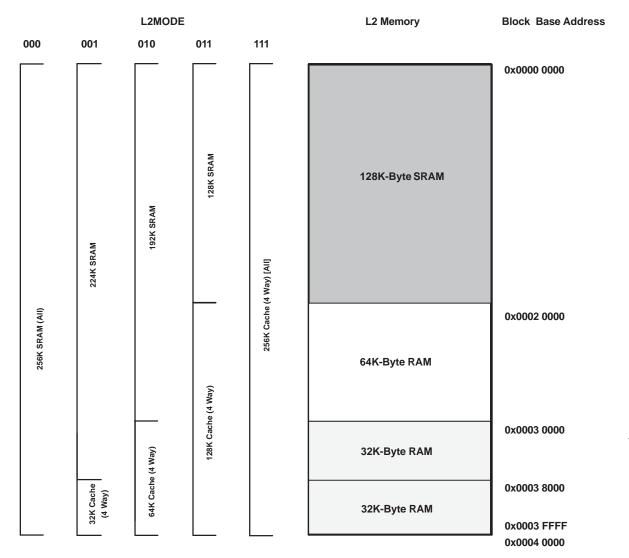

The DM642 uses a two-level cache-based architecture and has a powerful and diverse set of peripherals. The Level 1 program cache (L1P) is a 128-Kbit direct mapped cache and the Level 1 data cache (L1D) is a 128-Kbit 2-way set-associative cache. The Level 2 memory/cache (L2) consists of an 2-Mbit memory space that is shared between program and data space. L2 memory can be configured as mapped memory, cache, or combinations of the two. The peripheral set includes: three configurable video ports; a 10/100 Mb/s Ethernet MAC (EMAC); a management data input/output (MDIO) module; a VCXO interpolated control port (VIC); one multichannel buffered audio serial port (McASPO); an inter-integrated circuit (I2C) Bus module; two multichannel buffered serial ports (McBSPs); three 32-bit general-purpose timers; a user-configurable 16-bit or 32-bit host-port interface (HPI16/HPI32); a peripheral component interconnect (PCI); a 16-pin general-purpose input/output port (GPO) with programmable interrupt/event generation modes; and a 64-bit glueless external memory interface (EMIFA), which is capable of interfacing to synchronous and asynchronous memories and peripherals.

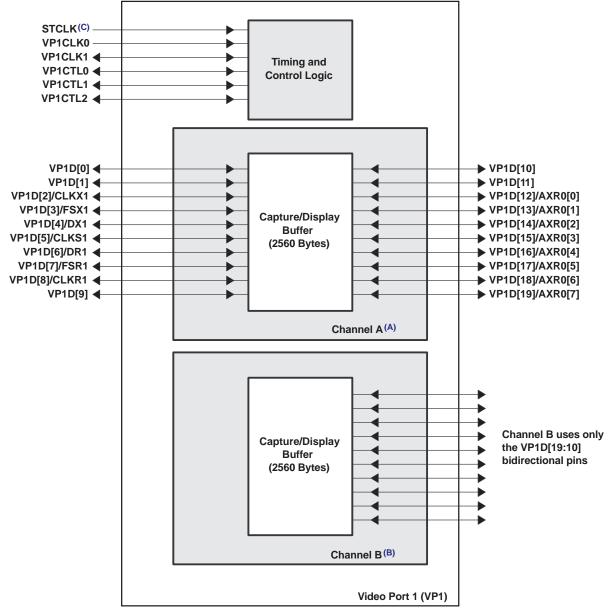

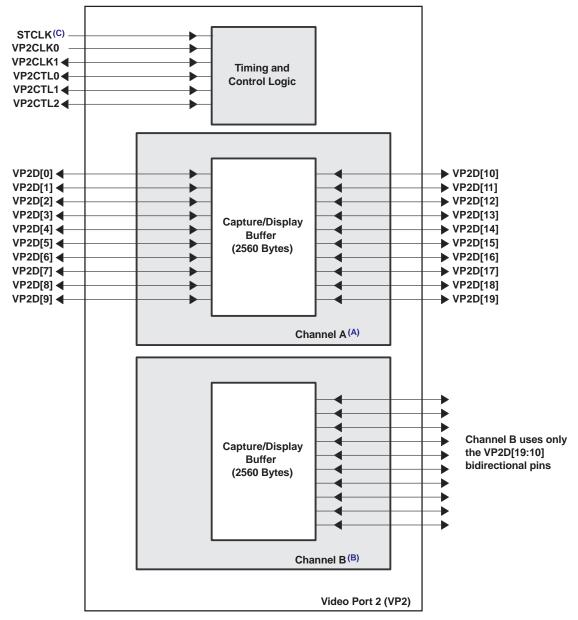

The DM642 device has three configurable video port peripherals (VP0, VP1, and VP2). These video port peripherals provide a glueless interface to common video decoder and encoder devices. The DM642 video port peripherals support multiple resolutions and video standards (e.g., CCIR601, ITU-BT.656, BT.1120, SMPTE 125M, 260M, 274M, and 296M).

These three video port peripherals are configurable and can support either video capture and/or video display modes. Each video port consists of two channels — A and B with a 5120-byte capture/display buffer that is splittable between the two channels.

For more details on the Video Port peripherals, see the *TMS320C64x DSP Video Port/VCXO Interpolated Control (VIC) Port Reference Guide* (literature number SPRU629).

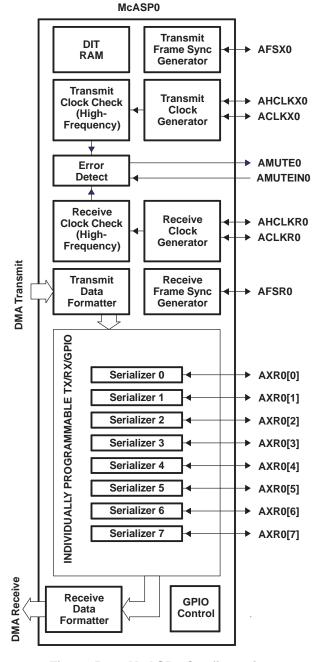

The McASP0 port supports one transmit and one receive clock zone, with eight serial data pins which can be individually allocated to any of the two zones. The serial port supports time-division multiplexing on each pin from 2 to 32 time slots. The DM642 has sufficient bandwidth to support all 8 serial data pins transmitting a 192-kHz stereo signal. Serial data in each zone may be transmitted and received on multiple serial data pins simultaneously and formatted in a multitude of variations on the Philips Inter-IC Sound (I<sup>2</sup>S) format.

In addition, the McASP0 transmitter may be programmed to output multiple S/PDIF, IEC60958, AES-3, CP-430 encoded data channels simultaneously, with a single RAM containing the full implementation of user data and channel status fields.

McASP0 also provides extensive error-checking and recovery features, such as the bad clock detection circuit for each high-frequency master clock which verifies that the master clock is within a programmed frequency range.

#### TMS320DM642 Video/Imaging Fixed-Point Digital Signal Processor

SPRS200L-JULY 2002-REVISED JANUARY 2007

The VCXO interpolated control (VIC) port provides digital-to-analog conversion with resolution from 9-bits to up to 16-bits. The output of the VIC is a single bit interpolated D/A output. For more details on the VIC port, see the *TMS320C64x DSP Video Port/VCXO Interpolated Control (VIC) Port Reference Guide* (literature number SPRU629).

The ethernet media access controller (EMAC) provides an efficient interface between the DM642 DSP core processor and the network. The DM642 EMAC support both 10Base-T and 100Base-TX, or 10 Mbits/second (Mbps) and 100 Mbps in either half- or full-duplex, with hardware flow control and quality of service (QOS) support. The DM642 EMAC makes use of a custom interface to the DSP core that allows efficient data transmission and reception. For more details on the EMAC, see the TMS320C6000 DSP Ethernet Media Access Controller (EMAC) / Management Data Input/Output (MDIO) Module Reference Guide (literature number SPRU628).

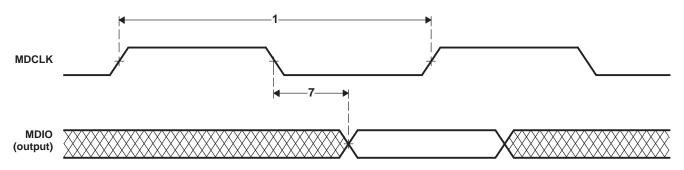

The management data input/output (MDIO) module continuously polls all 32 MDIO addresses in order to enumerate all PHY devices in the system. Once a PHY candidate has been selected by the DSP, the MDIO module transparently monitors its link state by reading the PHY status register. Link change events are stored in the MDIO module and can optionally interrupt the DSP, allowing the DSP to poll the link status of the device without continuously performing costly MDIO accesses. For more details on the MDIO, see the *TMS320C6000 DSP Ethernet Media Access Controller (EMAC) / Management Data Input/Output (MDIO) Module Reference Guide* (literature number SPRU628).

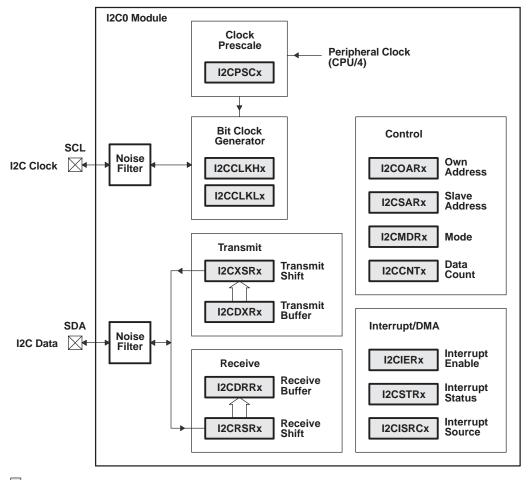

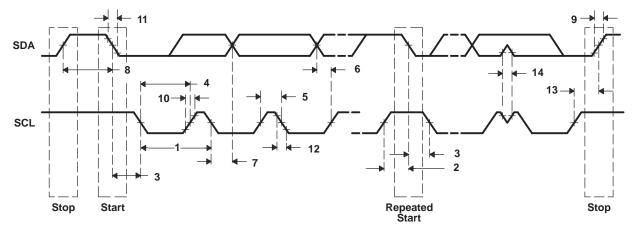

The I2C0 port on the TMS320DM642 allows the DSP to easily control peripheral devices and communicate with a host processor. In addition, the standard multichannel buffered serial port (McBSP) may be used to communicate with serial peripheral interface (SPI) mode peripheral devices.

The DM642 has a complete set of development tools which includes: a new C compiler, an assembly optimizer to simplify programming and scheduling, and a Windows<sup>®</sup> debugger interface for visibility into source code execution.

#### 1.2.1 Device Compatibility

The DM642 device is a code-compatible member of the C6000™ DSP platform.

The C64x<sup>™</sup> DSP generation of devices has a diverse and powerful set of peripherals.

For more detailed information on the device compatibility and similarities/differences among the DM642 and other C64x<sup>™</sup> devices, see the *TMS320DM642 Technical Overview* (literature number SPRU615).

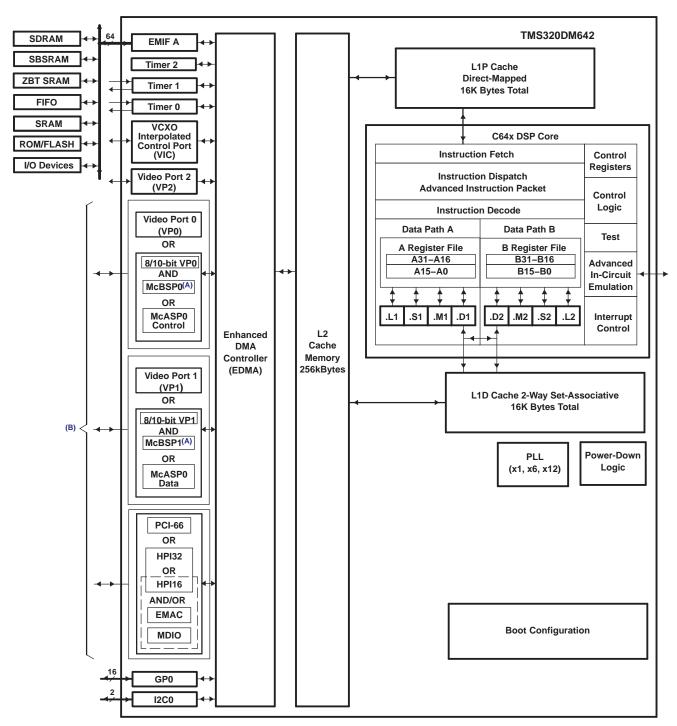

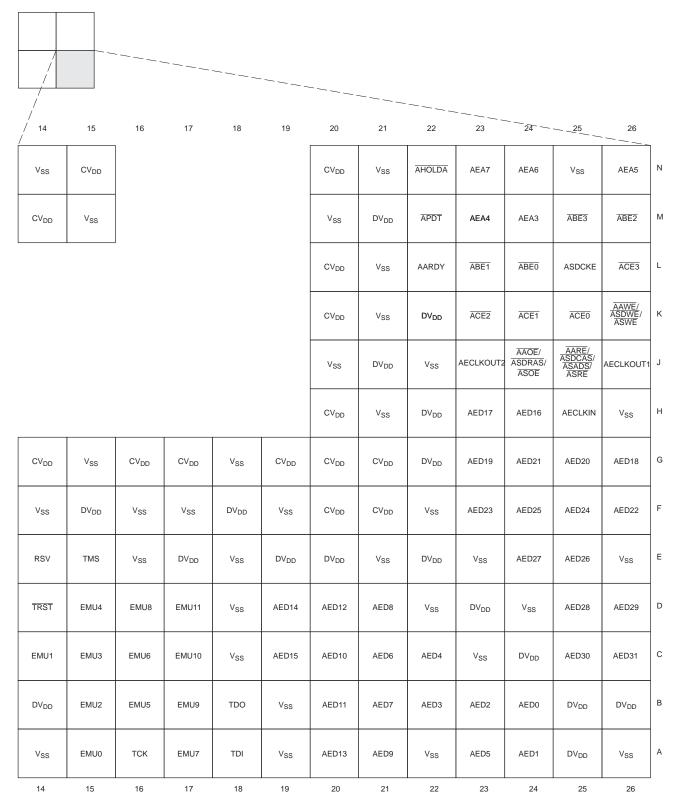

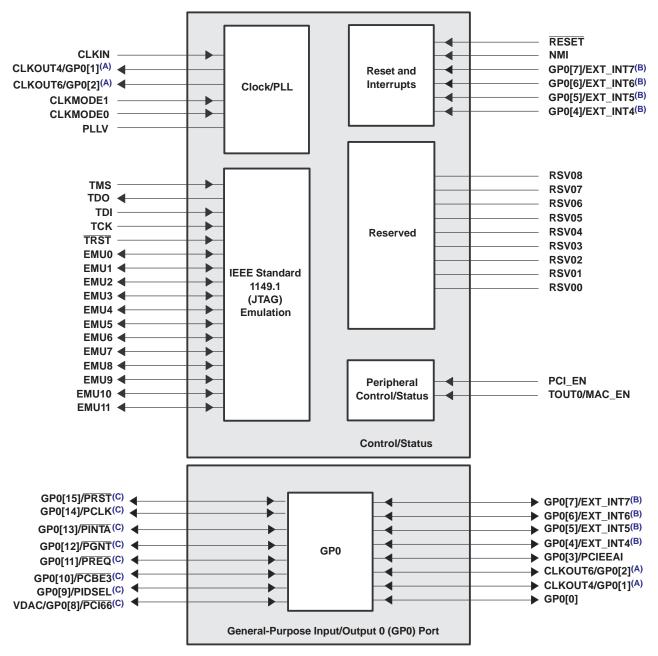

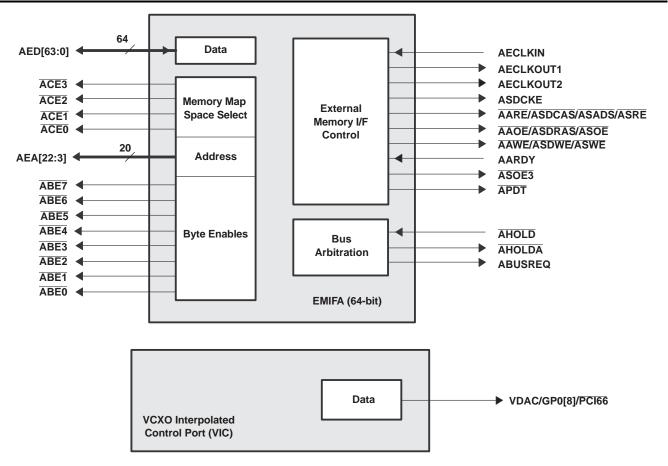

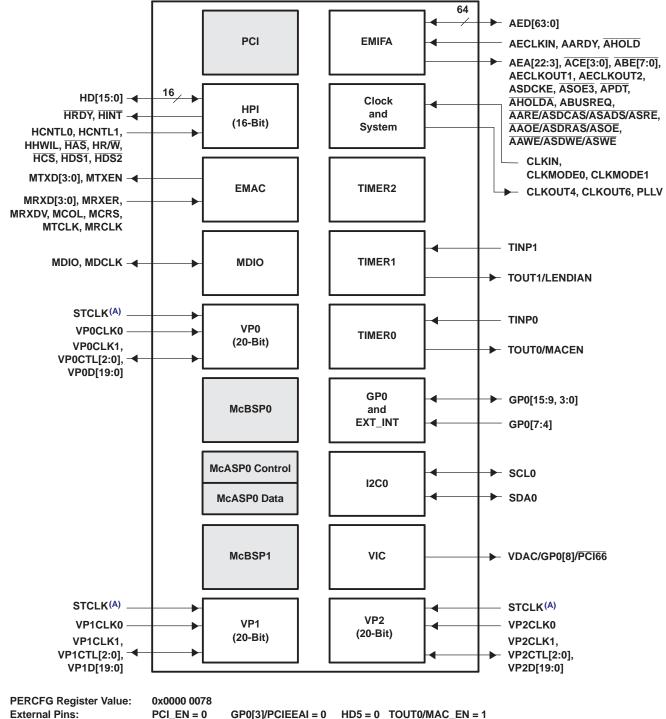

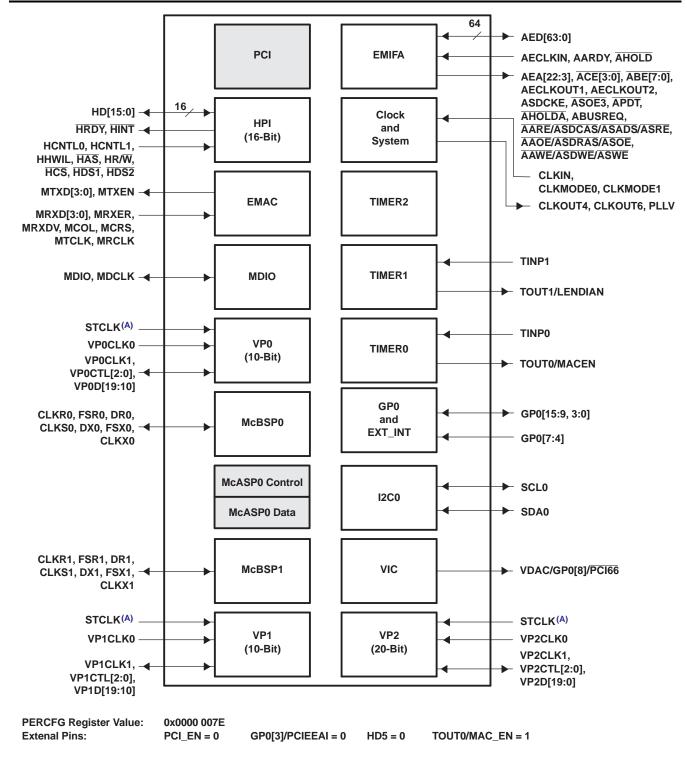

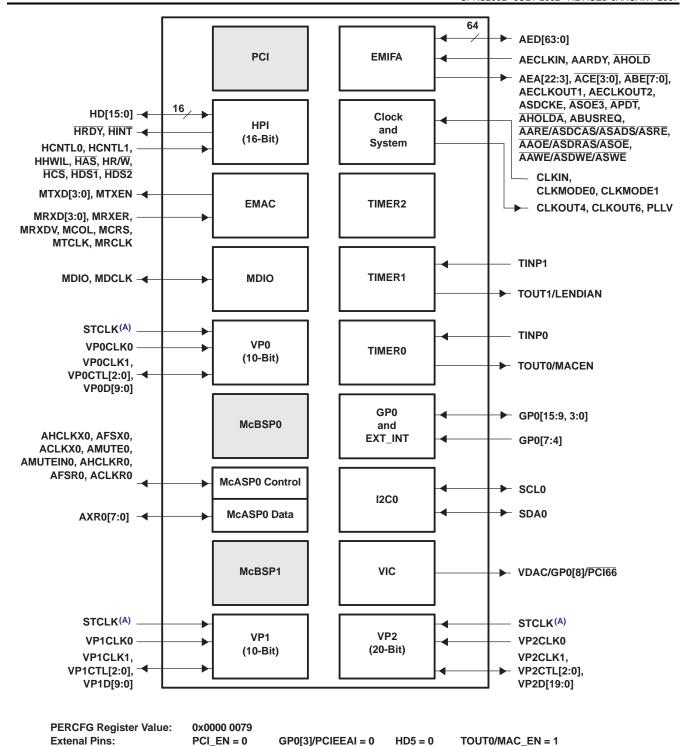

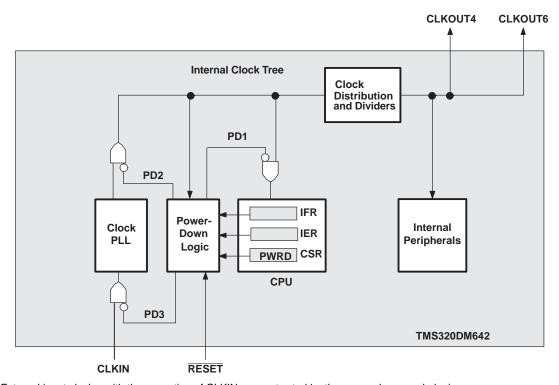

# 1.3 Functional Block Diagram

Figure 1-1 shows the functional block diagram of the DM642 device.

- A. McBSPs: Framing Chips H.100, MVIP, SCSA, T1, E1; AC97 Devices; SPI Devices; Codecs

- B. The Video Port 0 (VP0) peripheral is muxed with the McBSP0 peripheral and the McASP0 control pins. The Video Port 1 (VP1) peripheral is muxed with the McBSP1 peripheral and the McASP0 data pins. The PCI peripheral is muxed with the HPI(32/16), EMAC, and MDIO peripherals. For more details on the multiplexed pins of these peripherals, see the Device Configurations section of this data sheet.

Figure 1-1. Functional Block Diagram

# TMS320DM642 Video/Imaging Fixed-Point Digital Signal Processor SPRS200L-JULY 2002-REVISED JANUARY 2007

### Contents

| 1 |       | 320DM642 Video/Imaging Fixed-Point Digital al Processor                                    | 1         | 5   |       | 42 Peripheral Information and Electrical ifications | . <u>73</u> |

|---|-------|--------------------------------------------------------------------------------------------|-----------|-----|-------|-----------------------------------------------------|-------------|

|   | 1.1   | Features                                                                                   | 1         |     | 5.1   | Parameter Information                               | . <u>73</u> |

|   | 1.2   | Description                                                                                | 2         |     | 5.2   | Recommended Clock and Control Signal Transition     | n           |

|   | 1.2.1 | Device Compatibility                                                                       | 3         |     |       | Behavior                                            | . <u>75</u> |

|   | 1.3   | Functional Block Diagram                                                                   | 4         |     | 5.3   | Power Supplies                                      | . <u>75</u> |

| 2 | Devi  | ce Overview                                                                                | <u>6</u>  |     | 5.4   | Enhanced Direct Memory Access (EDMA)                |             |

|   | 2.1   | Device Characteristics                                                                     | 6         |     |       | Controller                                          | _           |

|   | 2.2   | CPU (DSP Core) Description                                                                 | 7         |     | 5.5   | Interrupts                                          |             |

|   | 2.3   | Memory Map Summary                                                                         | _         |     | 5.6   | Reset                                               |             |

|   | 2.4   | Bootmode                                                                                   |           |     | 5.7   | Clock PLL                                           | • <u>88</u> |

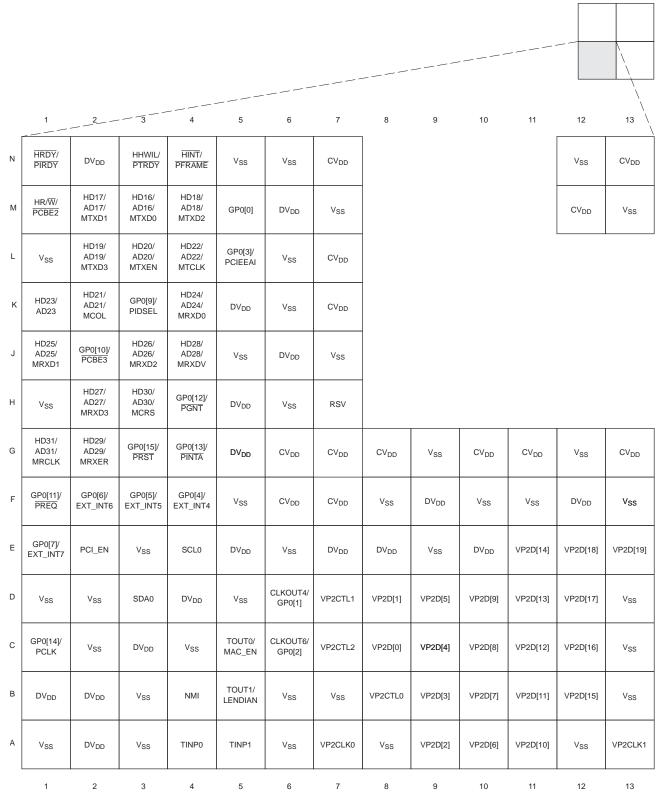

|   | 2.5   | Pin Assignments                                                                            |           |     | 5.8   | External Memory Interface (EMIF)                    | . <u>94</u> |

|   | _     | -                                                                                          |           |     | 5.9   | Multichannel Audio Serial Port (McASP0)             |             |

| _ | 2.6   | Development                                                                                |           |     |       | Peripheral                                          | <u>110</u>  |

| 3 |       | ce Configurations5                                                                         |           |     | 5.10  | Inter-Integrated Circuit (I2C)                      | <u>118</u>  |

|   | 3.1   | Configurations at Reset                                                                    | 54        |     | 5.11  | Host-Port Interface (HPI)                           | <u>123</u>  |

|   | 3.2   | Configurations After Reset                                                                 | <u>56</u> |     | 5.12  | Peripheral Component Interconnect (PCI)             | <u>129</u>  |

|   | 3.3   | Peripheral Configuration Lock                                                              | <u>59</u> |     | 5.13  | Multichannel Buffered Serial Port (McBSP)           | <u>133</u>  |

|   | 3.4   | Device Status Register Description                                                         | 61        |     | 5.14  | Video Port                                          | <u>142</u>  |

|   | 3.5   | Multiplexed Pin Configurations                                                             | <u>63</u> |     | 5.15  | VCXO Interpolated Control (VIC)                     | <u>150</u>  |

|   | 3.6   | Debugging Considerations                                                                   | <u>65</u> |     | 5.16  | Ethernet Media Access Controller (EMAC)             | 152         |

|   | 3.7   | Configuration Examples                                                                     | <u>66</u> |     | 5.17  | Management Data Input/Output (MDIO)                 | <u>158</u>  |

| 4 | Devi  | ce Operating Conditions 7                                                                  | <u>70</u> |     | 5.18  | Timer                                               | 160         |

|   | 4.1   | Absolute Maximum Ratings Over Operating Case                                               |           |     | 5.19  | General-Purpose Input/Output (GPIO)                 | 162         |

|   |       | Temperature Range (Unless Otherwise Noted)                                                 | 70        |     | 5.20  | JTAG                                                |             |

|   | 4.0   | ,                                                                                          |           | Rev | ision | History                                             | 167         |

|   | 4.2   | Recommended Operating Conditions                                                           | <u>70</u> | 6   |       | nanical Data                                        |             |

|   | 4.3   | Electrical Characteristics Over Recommended<br>Ranges of Supply Voltage and Operating Case |           | •   | 6.1   | Thermal Data                                        |             |

|   |       | Temperature (Unless Otherwise Noted)                                                       | 71        |     | 6.2   | Packaging Information                               |             |

|   |       | (                                                                                          |           |     | 0.2   | rackaging information                               | 109         |

#### 2 Device Overview

#### 2.1 Device Characteristics

Table 2-1 provides an overview of the DM642 DSP. The table shows significant features of the DM642 device, including the capacity of on-chip RAM, the peripherals, the CPU frequency, and the package type with pin count.

Table 2-1. Characteristics of the DM642 Processor

| I                                                       | HARDWARE FEATURES                                                       | DM642                                                                                                                                                                                                                                                                                                              |  |  |

|---------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                         | EMIFA (64-bit bus width)<br>(clock source = AECLKIN)                    | 1                                                                                                                                                                                                                                                                                                                  |  |  |

|                                                         | EDMA (64 independent channels)                                          | 1                                                                                                                                                                                                                                                                                                                  |  |  |

|                                                         | McASP0 (uses Peripheral Clock [AUXCLK])                                 | 1                                                                                                                                                                                                                                                                                                                  |  |  |

|                                                         | I2C0 (uses Peripheral Clock)                                            | 1                                                                                                                                                                                                                                                                                                                  |  |  |

|                                                         | HPI (32- or 16-bit user selectable)                                     | 1 (HPI16 or HPI32)                                                                                                                                                                                                                                                                                                 |  |  |

| Peripherals  Not all peripherals pins are               | PCI (32-bit), 66-MHz/33-MHz<br>[DeviceID Register value 0x9065]         | 1                                                                                                                                                                                                                                                                                                                  |  |  |

| available at the same time<br>(For more detail, see the | McBSPs<br>(internal clock source = CPU/4 clock frequency)               | 2                                                                                                                                                                                                                                                                                                                  |  |  |

| Device Configuration section).                          | Configurable Video Ports (VP0, VP1, VP2)                                | 3                                                                                                                                                                                                                                                                                                                  |  |  |

| ,                                                       | 10/100 Ethernet MAC (EMAC)                                              | 1                                                                                                                                                                                                                                                                                                                  |  |  |

|                                                         | Management Data Input/Output (MDIO)                                     | 1                                                                                                                                                                                                                                                                                                                  |  |  |

|                                                         | VCXO Interpolated Control Port (VIC)                                    | 1                                                                                                                                                                                                                                                                                                                  |  |  |

|                                                         | 32-Bit Timers<br>(internal clock source = CPU/8 clock frequency)        | 3                                                                                                                                                                                                                                                                                                                  |  |  |

|                                                         | General-Purpose Input/Output Port (GP0)                                 | 16                                                                                                                                                                                                                                                                                                                 |  |  |

|                                                         | Size (Bytes)                                                            | 288K                                                                                                                                                                                                                                                                                                               |  |  |

| On-Chip Memory                                          | Organization                                                            | 16K-Byte (16KB) L1 Program (L1P) Cache<br>16KB L1 Data (L1D) Cache<br>256KB Unified Mapped RAM/Cache (L2)                                                                                                                                                                                                          |  |  |

| CPU ID + CPU Rev ID                                     | Control Status Register (CSR.[31:16])                                   | 0x0C01                                                                                                                                                                                                                                                                                                             |  |  |

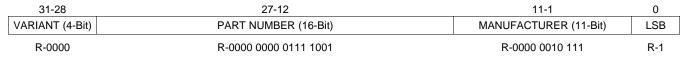

| JTAG BSDL_ID                                            | JTAGID register (address location: 0x01B3F008)                          | 0x0007902F                                                                                                                                                                                                                                                                                                         |  |  |

| Frequency                                               | MHz                                                                     | 500, 600, 720                                                                                                                                                                                                                                                                                                      |  |  |

| Cycle Time                                              | ns                                                                      | 2 ns (DM642-500) and (DM642 <b>A</b> -500)<br>[500 MHz CPU, 100 MHz EMIF <sup>(1)</sup> , 33 MHz PCI port]<br>1.67 ns (DM642-600) and (DM642 <b>A</b> -600)<br>[600 MHz CPU, 133 MHz EMIF <sup>(1)</sup> , 66 MHz PCI port]<br>1.39 ns (DM642-720)<br>[720 MHz CPU, 133 MHz EMIF <sup>(1)</sup> , 66 MHz PCI port] |  |  |

| Voltage                                                 | Core (V)                                                                | 1.2 V (-500)<br>1.4 V ( <b>A</b> -500, <b>A</b> -600, -600, -720)                                                                                                                                                                                                                                                  |  |  |

|                                                         | I/O (V)                                                                 | 3.3 V                                                                                                                                                                                                                                                                                                              |  |  |

| PLL Options                                             | CLKIN frequency multiplier                                              | Bypass (x1), x6, x12                                                                                                                                                                                                                                                                                               |  |  |

| BGA Package                                             | 23 x 23 mm                                                              | 548-Pin BGA (GDK and ZDK)                                                                                                                                                                                                                                                                                          |  |  |

| DOA I ackage                                            | 27 x 27 mm                                                              | 548-Pin BGA (GNZ and ZNZ)                                                                                                                                                                                                                                                                                          |  |  |

| Process Technology                                      | μm                                                                      | 0.13 μm                                                                                                                                                                                                                                                                                                            |  |  |

| Product Status <sup>(2)</sup>                           | Product Preview (PP), Advance Information (AI), or Production Data (PD) | PD                                                                                                                                                                                                                                                                                                                 |  |  |

<sup>(1)</sup> On this DM64x<sup>™</sup> device, the rated EMIF speed affects only the SDRAM interface on the EMIF. For more detailed information, see the EMIF device speed portion of this data sheet.

<sup>(2)</sup> PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

#### SPRS200L-JULY 2002-REVISED JANUARY 2007

### 2.2 CPU (DSP Core) Description

The CPU fetches VelociTI™ advanced very-long instruction words (VLIWs) (256 bits wide) to supply up to eight 32-bit instructions to the eight functional units during every clock cycle. The VelociTI™ VLIW architecture features controls by which all eight units do not have to be supplied with instructions if they are not ready to execute. The first bit of every 32-bit instruction determines if the next instruction belongs to the same execute packet as the previous instruction, or whether it should be executed in the following clock as a part of the next execute packet. Fetch packets are always 256 bits wide; however, the execute packets can vary in size. The variable-length execute packets are a key memory-saving feature, distinguishing the C64x CPUs from other VLIW architectures. The C64x™ VelociTI.2™ extensions add enhancements to the TMS320C62x™ DSP VelociTI™ architecture. These enhancements include:

- Register file enhancements

- Data path extensions

- Quad 8-bit and dual 16-bit extensions with data flow enhancements

- Additional functional unit hardware

- Increased orthogonality of the instruction set

- Additional instructions that reduce code size and increase register flexibility

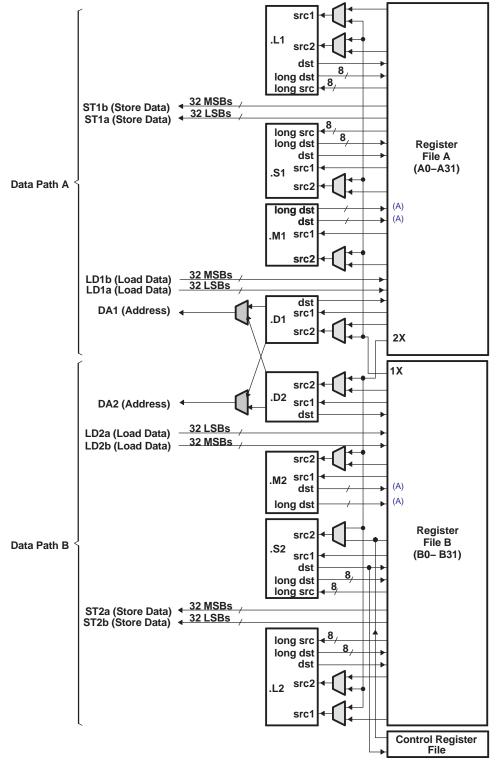

The CPU features two sets of functional units. Each set contains four units and a register file. One set contains functional units .L1, .S1, .M1, and .D1; the other set contains units .D2, .M2, .S2, and .L2. The two register files each contain 32 32-bit registers for a total of 64 general-purpose registers. In addition to supporting the packed 16-bit and 32-/40-bit fixed-point data types found in the C62x<sup>™</sup> VelociTI<sup>™</sup> VLIW architecture, the C64x™ register files also support packed 8-bit data and 64-bit fixed-point data types. The two sets of functional units, along with two register files, compose sides A and B of the CPU [see the functional block and CPU (DSP core) diagram, and Figure 2-1]. The four functional units on each side of the CPU can freely share the 32 registers belonging to that side. Additionally, each side features a "data cross path"—a single data bus connected to all the registers on the other side, by which the two sets of functional units can access data from the register files on the opposite side. The C64x CPU pipelines data-cross-path accesses over multiple clock cycles. This allows the same register to be used as a data-cross-path operand by multiple functional units in the same execute packet. All functional units in the C64x CPU can access operands via the data cross path. Register access by functional units on the same side of the CPU as the register file can service all the units in a single clock cycle. On the C64x CPU, a delay clock is introduced whenever an instruction attempts to read a register via a data cross path if that register was updated in the previous clock cycle.

In addition to the  $C62x^{TM}$  DSP fixed-point instructions, the  $C64x^{TM}$  DSP includes a comprehensive collection of quad 8-bit and dual 16-bit instruction set extensions. These VelociTI.2<sup>TM</sup> extensions allow the C64x CPU to operate directly on packed data to streamline data flow and increase instruction set efficiency. This is a key factor for video and imaging applications.

Another key feature of the C64x CPU is the load/store architecture, where all instructions operate on registers (as opposed to data in memory). Two sets of data-addressing units (.D1 and .D2) are responsible for all data transfers between the register files and the memory. The data address driven by the .D units allows data addresses generated from one register file to be used to load or store data to or from the other register file. The C64x .D units can load and store bytes (8 bits), half-words (16 bits), and words (32 bits) with a single instruction. And with the new data path extensions, the C64x .D unit can load and store doublewords (64 bits) with a single instruction. Furthermore, the non-aligned load and store instructions allow the .D units to access words and doublewords on any byte boundary. The C64x CPU supports a variety of indirect addressing modes using either linear- or circular-addressing with 5- or 15-bit offsets. All instructions are conditional, and most can access any one of the 64 registers. Some registers, however, are singled out to support specific addressing modes or to hold the condition for conditional instructions (if the condition is not automatically "true").

## TMS320DM642 Video/Imaging Fixed-Point Digital Signal Processor

SPRS200L-JULY 2002-REVISED JANUARY 2007

The two .M functional units perform all multiplication operations. Each of the C64x .M units can perform two 16  $\times$  16-bit multiplies or four 8  $\times$  8-bit multiplies per clock cycle. The .M unit can also perform 16  $\times$  32-bit multiply operations, dual 16  $\times$  16-bit multiplies with add/subtract operations, and quad 8  $\times$  8-bit multiplies with add operations. In addition to standard multiplies, the C64x .M units include bit-count, rotate, Galois field multiplies, and bidirectional variable shift hardware.

The two .S and .L functional units perform a general set of arithmetic, logical, and branch functions with results available every clock cycle. The arithmetic and logical functions on the C64x CPU include single 32-bit, dual 16-bit, and quad 8-bit operations.

The processing flow begins when a 256-bit-wide instruction fetch packet is fetched from a program memory. The 32-bit instructions destined for the individual functional units are "linked" together by "1" bits in the least significant bit (LSB) position of the instructions. The instructions that are "chained" together for simultaneous execution (up to eight in total) compose an execute packet. A "0" in the LSB of an instruction breaks the chain, effectively placing the instructions that follow it in the next execute packet. A C64x<sup>TM</sup> DSP device enhancement now allows execute packets to cross fetch-packet boundaries. In the TMS320C62x<sup>™</sup>/TMS320C67x<sup>™</sup> DSP devices, if an execute packet crosses the fetch-packet boundary (256 bits wide), the assembler places it in the next fetch packet, while the remainder of the current fetch packet is padded with NOP instructions. In the C64x<sup>™</sup> DSP device, the execute boundary restrictions have been removed, thereby, eliminating all of the NOPs added to pad the fetch packet, and thus, decreasing the overall code size. The number of execute packets within a fetch packet can vary from one to eight. Execute packets are dispatched to their respective functional units at the rate of one per clock cycle and the next 256-bit fetch packet is not fetched until all the execute packets from the current fetch packet have been dispatched. After decoding, the instructions simultaneously drive all active functional units for a maximum execution rate of eight instructions every clock cycle. While most results are stored in 32-bit registers, they can be subsequently moved to memory as bytes, half-words, or doublewords. All load and store instructions are byte-, half-word-, word-, or doubleword-addressable.

For more details on the C64x CPU functional units enhancements, see the following documents:

- TMS320C6000 CPU and Instruction Set Reference Guide (literature number SPRU189)

- TMS320C64x Technical Overview (literature number SPRU395)

A. For the .M functional units, the long dst is 32 MSBs and the dst is 32 LSBs.

Figure 2-1. TMS320C64x<sup>™</sup> CPU (DSP Core) Data Paths

## 2.2.1 CPU Core Registers

Table 2-2. L2 Cache Registers (C64x)

| HEX ADDRESS RANGE     | ACRONYM           | REGISTER NAME                                  | COMMENTS |

|-----------------------|-------------------|------------------------------------------------|----------|

| 0184 0000             | CCFG              | Cache configuration register                   |          |

| 0184 0004 - 0184 0FFC | _                 | Reserved                                       |          |

| 0184 1000             | EDMAWEIGHT        | L2 EDMA access control register                |          |

| 0184 1004 – 0184 1FFC | _                 | Reserved                                       |          |

| 0184 2000             | L2ALLOC0          | L2 allocation register 0                       |          |

| 0184 2004             | L2ALLOC1          | L2 allocation register 1                       |          |

| 0184 2008             | L2ALLOC2          | L2 allocation register 2                       |          |

| 0184 200C             | L2ALLOC3          | L2 allocation register 3                       |          |

| 0184 2010 - 0184 3FFC | _                 | Reserved                                       |          |

| 0184 4000             | L2WBAR            | L2 writeback base address register             |          |

| 0184 4004             | L2WWC             | L2 writeback word count register               |          |

| 0184 4010             | L2WIBAR           | L2 writeback invalidate base address register  |          |

| 0184 4014             | L2WIWC            | L2 writeback invalidate word count register    |          |

| 0184 4018             | L2IBAR            | L2 invalidate base address register            |          |

| 0184 401C             | L2IWC             | L2 invalidate word count register              |          |

| 0184 4020             | L1PIBAR           | L1P invalidate base address register           |          |

| 0184 4024             | L1PIWC            | L1P invalidate word count register             |          |

| 0184 4030             | L1DWIBAR          | L1D writeback invalidate base address register |          |

| 0184 4034             | L1DWIWC           | L1D writeback invalidate word count register   |          |

| 0184 4038 – 0184 4044 | _                 | Reserved                                       |          |

| 0184 4048             | L1DIBAR           | L1D invalidate base address register           |          |

| 0184 404C             | L1DIWC            | L1D invalidate word count register             |          |

| 0184 4050 - 0184 4FFC | _                 | Reserved                                       |          |

| 0184 5000             | L2WB              | L2 writeback all register                      |          |

| 0184 5004             | L2WBINV           | L2 writeback invalidate all register           |          |

| 0184 5008 - 0184 7FFC | _                 | Reserved                                       |          |

| 0184 8000 – 0184 81FC | MAR0 to<br>MAR127 | Reserved                                       |          |

| 0184 8200             | MAR128            | Controls EMIFA CE0 range 8000 0000 – 80FF FFFF |          |

| 0184 8204             | MAR129            | Controls EMIFA CE0 range 8100 0000 – 81FF FFFF |          |

| 0184 8208             | MAR130            | Controls EMIFA CE0 range 8200 0000 – 82FF FFFF |          |

| 0184 820C             | MAR131            | Controls EMIFA CE0 range 8300 0000 – 83FF FFFF |          |

| 0184 8210             | MAR132            | Controls EMIFA CE0 range 8400 0000 – 84FF FFFF |          |

| 0184 8214             | MAR133            | Controls EMIFA CE0 range 8500 0000 – 85FF FFFF |          |

| 0184 8218             | MAR134            | Controls EMIFA CE0 range 8600 0000 – 86FF FFFF |          |

| 0184 821C             | MAR135            | Controls EMIFA CE0 range 8700 0000 – 87FF FFFF |          |

| 0184 8220             | MAR136            | Controls EMIFA CE0 range 8800 0000 – 88FF FFFF |          |

| 0184 8224             | MAR137            | Controls EMIFA CE0 range 8900 0000 – 89FF FFFF |          |

| 0184 8228             | MAR138            | Controls EMIFA CE0 range 8A00 0000 – 8AFF FFFF |          |

| 0184 822C             | MAR139            | Controls EMIFA CE0 range 8B00 0000 – 8BFF FFFF |          |

| 0184 8230             | MAR140            | Controls EMIFA CE0 range 8C00 0000 – 8CFF FFFF |          |

| 0184 8234             | MAR141            | Controls EMIFA CE0 range 8D00 0000 – 8DFF FFFF |          |

| 0184 8238             | MAR142            | Controls EMIFA CE0 range 8E00 0000 – 8EFF FFFF |          |

| 0184 823C             | MAR143            | Controls EMIFA CE0 range 8F00 0000 – 8FFF FFFF |          |

| 0184 8240             | MAR144            | Controls EMIFA CE1 range 9000 0000 – 90FF FFFF |          |

# TMS320DM642 Video/Imaging Fixed-Point Digital Signal Processor SPRS200L-JULY 2002-REVISED JANUARY 2007

## Table 2-2. L2 Cache Registers (C64x) (continued)

| HEX ADDRESS RANGE | ACRONYM | REGISTER NAME                                  | COMMENTS |

|-------------------|---------|------------------------------------------------|----------|

| 0184 8244         | MAR145  | Controls EMIFA CE1 range 9100 0000 – 91FF FFFF |          |

| 0184 8248         | MAR146  | Controls EMIFA CE1 range 9200 0000 – 92FF FFFF |          |

| 0184 824C         | MAR147  | Controls EMIFA CE1 range 9300 0000 – 93FF FFFF |          |

| 0184 8250         | MAR148  | Controls EMIFA CE1 range 9400 0000 – 94FF FFFF |          |

| 0184 8254         | MAR149  | Controls EMIFA CE1 range 9500 0000 – 95FF FFFF |          |

| 0184 8258         | MAR150  | Controls EMIFA CE1 range 9600 0000 – 96FF FFFF |          |

| 0184 825C         | MAR151  | Controls EMIFA CE1 range 9700 0000 – 97FF FFFF |          |

| 0184 8260         | MAR152  | Controls EMIFA CE1 range 9800 0000 – 98FF FFFF |          |

| 0184 8264         | MAR153  | Controls EMIFA CE1 range 9900 0000 – 99FF FFFF |          |

| 0184 8268         | MAR154  | Controls EMIFA CE1 range 9A00 0000 – 9AFF FFFF |          |

| 0184 826C         | MAR155  | Controls EMIFA CE1 range 9B00 0000 – 9BFF FFFF |          |

| 0184 8270         | MAR156  | Controls EMIFA CE1 range 9C00 0000 – 9CFF FFFF |          |

| 0184 8274         | MAR157  | Controls EMIFA CE1 range 9D00 0000 – 9DFF FFFF |          |

| 0184 8278         | MAR158  | Controls EMIFA CE1 range 9E00 0000 – 9EFF FFFF |          |

| 0184 827C         | MAR159  | Controls EMIFA CE1 range 9F00 0000 – 9FFF FFFF |          |

| 0184 8280         | MAR160  | Controls EMIFA CE2 range A000 0000 – A0FF FFFF |          |

| 0184 8284         | MAR161  | Controls EMIFA CE2 range A100 0000 – A1FF FFFF |          |

| 0184 8288         | MAR162  | Controls EMIFA CE2 range A200 0000 – A2FF FFFF |          |

| 0184 828C         | MAR163  | Controls EMIFA CE2 range A300 0000 – A3FF FFFF |          |

| 0184 8290         | MAR164  | Controls EMIFA CE2 range A400 0000 – A4FF FFFF |          |

| 0184 8294         | MAR165  | Controls EMIFA CE2 range A500 0000 – A5FF FFFF |          |

| 0184 8298         | MAR166  | Controls EMIFA CE2 range A600 0000 – A6FF FFFF |          |

| 0184 829C         | MAR167  | Controls EMIFA CE2 range A700 0000 – A7FF FFFF |          |

| 0184 82A0         | MAR168  | Controls EMIFA CE2 range A800 0000 – A8FF FFFF |          |

| 0184 82A4         | MAR169  | Controls EMIFA CE2 range A900 0000 – A9FF FFFF |          |

| 0184 82A8         | MAR170  | Controls EMIFA CE2 range AA00 0000 – AAFF FFFF |          |

| 0184 82AC         | MAR171  | Controls EMIFA CE2 range AB00 0000 – ABFF FFFF |          |

| 0184 82B0         | MAR172  | Controls EMIFA CE2 range AC00 0000 – ACFF FFFF |          |

| 0184 82B4         | MAR173  | Controls EMIFA CE2 range AD00 0000 – ADFF FFFF |          |

| 0184 82B8         | MAR174  | Controls EMIFA CE2 range AE00 0000 – AEFF FFFF |          |

| 0184 82BC         | MAR175  | Controls EMIFA CE2 range AF00 0000 – AFFF FFFF |          |

| 0184 82C0         | MAR176  | Controls EMIFA CE3 range B000 0000 – B0FF FFFF |          |

| 0184 82C4         | MAR177  | Controls EMIFA CE3 range B100 0000 – B1FF FFFF |          |

| 0184 82C8         | MAR178  | Controls EMIFA CE3 range B200 0000 – B2FF FFFF |          |

| 0184 82CC         | MAR179  | Controls EMIFA CE3 range B300 0000 – B3FF FFFF |          |

| 0184 82D0         | MAR180  | Controls EMIFA CE3 range B400 0000 – B4FF FFFF |          |

| 0184 82D4         | MAR181  | Controls EMIFA CE3 range B500 0000 – B5FF FFFF |          |

| 0184 82D8         | MAR182  | Controls EMIFA CE3 range B600 0000 – B6FF FFFF |          |

| 0184 82DC         | MAR183  | Controls EMIFA CE3 range B700 0000 – B7FF FFFF |          |

| 0184 82E0         | MAR184  | Controls EMIFA CE3 range B800 0000 – B8FF FFFF |          |

| 0184 82E4         | MAR185  | Controls EMIFA CE3 range B900 0000 – B9FF FFFF |          |

| 0184 82E8         | MAR186  | Controls EMIFA CE3 range BA00 0000 – BAFF FFFF |          |

| 0184 82EC         | MAR187  | Controls EMIFA CE3 range BB00 0000 – BBFF FFFF |          |

| 0184 82F0         | MAR188  | Controls EMIFA CE3 range BC00 0000 – BCFF FFFF |          |

| 0184 82F4         | MAR189  | Controls EMIFA CE3 range BD00 0000 – BDFF FFFF |          |

| 0184 82F8         | MAR190  | Controls EMIFA CE3 range BE00 0000 – BEFF FFFF |          |

| 0184 82FC         | MAR191  | Controls EMIFA CE3 range BF00 0000 – BFFF FFFF |          |

# TMS320DM642 Video/Imaging Fixed-Point Digital Signal Processor

### Table 2-2. L2 Cache Registers (C64x) (continued)

| HEX ADDRESS RANGE     | ACRONYM             | REGISTER NAME | COMMENTS |

|-----------------------|---------------------|---------------|----------|

| 0184 8300 - 0184 83FC | MAR192 to<br>MAR255 | Reserved      |          |

| 0184 8400 - 0187 FFFF | -                   | Reserved      |          |

#### 2.3 Memory Map Summary

Table 2-3 shows the memory map address ranges of the DM642 device. Internal memory is always located at address 0 and can be used as both program and data memory. The external memory address ranges in the DM642 device begin at the hex address location 0x8000 0000 for EMIFA.

Table 2-3. TMS320DM642 Memory Map Summary

| EWRAP Registers         2K         01C8 3000 - 01C8 37FF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MEMORY BLOCK DESCRIPTION                      | BLOCK SIZE<br>(BYTES) | HEX ADDRESS RANGE     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------|-----------------------|

| Reserved         23M         0010 0000 - 017F FFFF           External Memory Interface A (EMIFA) Registers         256K         0180 0000 - 0183 FFFF           L2 Registers         256K         0184 0000 - 0187 FFFF           HPI Registers         256K         0188 0000 - 0188 FFFF           McBSP 1 Registers         256K         0190 0000 - 0193 FFFF           McBSP 1 Registers         256K         0190 0000 - 0197 FFFF           Timer 1 Registers         256K         0194 0000 - 0197 FFFF           Timer 1 Registers         256K         0198 0000 - 0198 FFFF           Interrupt Selector Registers         256K         0190 0000 - 0198 FFFF           Interrupt Selector Registers         256K         0190 0000 - 0198 FFFF           Interrupt Selector Registers         256K         0190 0000 - 0198 FFFF           Interrupt Selector Registers         256K         0190 0000 - 0188 FFFF           Reserved         512K         01A4 0000 - 0184 FFFF           Timer 2 Registers         256K         01A0 0000 - 0184 FFFF           Device Configuration Registers         256K         01B0 0000 - 0183 FFFF           Device Configuration Registers         4K         0183 F000 - 0183 FFFF           Device Configuration Registers         16K         0184 0000 - 0184 FFFF                                                                                 | Internal RAM (L2)                             | 256K                  | 0000 0000 – 0003 FFFF |

| External Memory Interface A (EMIFA) Registers         256K         0180 0000 – 0183 FFFF           L2 Registers         256K         0184 0000 – 0187 FFFF           HPI Registers         256K         0184 0000 – 0188 FFFF           McBSP O Registers         256K         0180 0000 – 0188 FFFF           McBSP 1 Registers         256K         0190 0000 – 0193 FFFF           Timer O Registers         256K         0190 0000 – 0198 FFFF           Timer 1 Registers         256K         0190 0000 – 0198 FFFF           Interrupt Selector Registers         256K         0190 0000 – 0198 FFFF           Interrupt Selector Registers         256K         0190 0000 – 0198 FFFF           EDMA RAM and EDMA Registers         256K         01A0 0000 – 01AF FFFF           EDMA RAM and EDMA Registers         256K         01A0 0000 – 01AF FFFF           Timer 2 Registers         256K         01A0 0000 – 01AF FFFF           Timer 2 Registers         256K         01AC 0000 – 01AF FFFF           Timer 2 Registers         256K         01A0 0000 – 01B3 FFFF           Timer 2 Registers         256K         01B0 0000 – 01B3 FFFF           Timer 2 Registers         256K         01B0 0000 – 01B3 FFFF           Timer 2 Registers         256K         01B4 0000 – 01B4 FFFF           L2CO Da                                                                                  | Reserved                                      | 768K                  | 0004 0000 – 000F FFFF |

| 12 Registers   256K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Reserved                                      | 23M                   | 0010 0000 – 017F FFFF |

| HPI Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | External Memory Interface A (EMIFA) Registers | 256K                  | 0180 0000 – 0183 FFFF |

| McBSP 0 Registers         256K         018C 0000 – 018F FFFF           McBSP 1 Registers         256K         0190 0000 – 0193 FFFF           Timer 0 Registers         256K         0194 0000 – 0197 FFFF           Timer 1 Registers         256K         0198 0000 – 0197 FFFF           Interrupt Selector Registers         256K         0190 0000 – 019F FFFF           EDMA RAM and EDMA Registers         256K         01A0 0000 – 01A3 FFFF           EDMA RAM and EDMA Registers         256K         01A0 0000 – 01A3 FFFF           EDMA RAM and EDMA Registers         256K         01A0 0000 – 01A3 FFFF           EDMA RAM and EDMA Registers         256K         01A0 0000 – 01A3 FFFF           Timer 2 Registers         256K         01A0 0000 – 01A3 FFFF           Timer 2 Registers         256K         01A0 0000 – 01A3 FFFF           Timer 2 Registers         256K         01B0 0000 – 01B3 FFFF           Device Configuration Registers         4K         01B3 FF000 – 01B3 FFFF           Device Configuration Registers         4K         01B3 FFF           Device Configuration Registers         16K         01B4 0000 – 01B4 FFFF           Reserved         32K         01B4 0000 – 01B4 FFFF           McASPO Control Registers         16K         01B4 0000 – 01B7 FFFF <td< td=""><td>L2 Registers</td><td>256K</td><td>0184 0000 – 0187 FFFF</td></td<>          | L2 Registers                                  | 256K                  | 0184 0000 – 0187 FFFF |

| MCBSP 1 Registers         256K         0190 0000 – 0193 FFFF           Timer 0 Registers         256K         0194 0000 – 0197 FFFF           Timer 1 Registers         256K         0198 0000 – 0198 FFFF           Interrupt Selector Registers         256K         0190 0000 – 0198 FFFF           EDMA RAM and EDMA Registers         256K         01A0 0000 – 01A3 FFFF           EDMA RAM and EDMA Registers         256K         01A0 0000 – 01A3 FFFF           EBMA RAM and EDMA Registers         256K         01A0 0000 – 01A3 FFFF           EDMA RAM and EDMA Registers         256K         01A0 0000 – 01A3 FFFF           EBMA RAM and EDMA Registers         256K         01A0 0000 – 01A3 FFFF           Timer 2 Registers         256K         01A0 0000 – 01A3 FFFF           CPO Registers         256K         01B0 0000 – 01B3 FFFF           Device Configuration Registers         4K         01B3 0000 – 01B3 FFFF           Device Configuration Registers         4K         01B3 0000 – 01B3 FFFF           12CO Data and Control Registers         16K         01B4 0000 – 01B4 FFFF           12CO Data and Control Registers         16K         01B4 0000 – 01B4 FFFF           Reserved         192K         01B5 0000 – 01B7 FFFF           PCD Registers         256K         01B0 0000 – 01B7 FFFF <td>HPI Registers</td> <td>256K</td> <td>0188 0000 – 018B FFFF</td> | HPI Registers                                 | 256K                  | 0188 0000 – 018B FFFF |

| Timer 0 Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | McBSP 0 Registers                             | 256K                  | 018C 0000 – 018F FFFF |

| Timer 1 Registers         256K         0198 0000 - 0198 FFFF           Interrupt Selector Registers         256K         019C 0000 - 019F FFFF           EDMA RAM and EDMA Registers         256K         01A0 0000 - 01A3 FFFF           Reserved         512K         01A4 0000 - 01A8 FFFF           Timer 2 Registers         256K         01AC 0000 - 01AF FFFF           GPO Registers         256K         01AC 0000 - 01B3 FFFF           Device Configuration Registers         4K         01B3 0000 - 01B3 FFFF           Device Configuration Registers         4K         01B3 0000 - 01B3 FFFF           Device Configuration Registers         4K         01B4 0000 - 01B3 FFFF           Reserved         32K         01B4 0000 - 01B4 FFFF           Reserved         32K         01B4 0000 - 01B4 FFFF           McASPO Control Registers         16K         01B4 0000 - 01B7 FFFF           Reserved         192K         01B5 0000 - 01B7 FFFF           Emulation         256K         01B8 0000 - 01B7 FFFF           Emulation         256K         01B8 0000 - 01B7 FFFF           Emulation         256K         01B8 0000 - 01B7 FFFF           PCI Registers         256K         01B0 0000 - 01C3 FFFF           VPO Control         16K         01C4 0000 - 01C4 FFFF                                                                                                           | McBSP 1 Registers                             | 256K                  | 0190 0000 – 0193 FFFF |

| Interrupt Selector Registers   256K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Timer 0 Registers                             | 256K                  | 0194 0000 – 0197 FFFF |

| EDMA RAM and EDMA Registers   256K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Timer 1 Registers                             | 256K                  | 0198 0000 – 019B FFFF |

| Sizk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Interrupt Selector Registers                  | 256K                  | 019C 0000 - 019F FFFF |

| Timer 2 Registers         256K         01AC 0000 – 01AF FFFF           GP0 Registers         256K – 4K         01B0 0000 – 01B3 FFFF           Device Configuration Registers         4K         01B3 F000 – 01B3 FFFF           12C0 Data and Control Registers         16K         01B4 0000 – 01B4 FFFF           Reserved         32K         01B4 4000 – 01B4 FFFF           McASP0 Control Registers         16K         01B4 C000 – 01B4 FFFF           McASP0 Control Registers         16K         01B4 0000 – 01B4 FFFF           Reserved         192K         01B5 0000 – 01B7 FFFF           Reserved         256K         01B8 0000 – 01BF FFFF           Emulation         256K         01B6 0000 – 01BF FFFF           PCI Registers         256K         01B0 0000 – 01C3 FFFF           VPO Control         16K         01C4 0000 – 01C3 FFFF           VPO Control         16K         01C4 0000 – 01C4 FFFF           VP1 Control         16K         01C4 4000 – 01C4 FFFF           VP2 Control         16K         01C4 4000 – 01C4 FFFF           VP2 Control         16K         01C4 2000 – 01C4 FFFF           VP2 Control         16K         01C4 2000 – 01C4 FFFF           VP2 Control         16K         01C4 8000 – 01C4 FFFF           EMSes                                                                                                                              | EDMA RAM and EDMA Registers                   | 256K                  | 01A0 0000 - 01A3 FFFF |

| GP0 Registers         256K - 4K         01B0 0000 - 01B3 EFFF           Device Configuration Registers         4K         01B3 F000 - 01B3 FFFF           12CO Data and Control Registers         16K         01B4 0000 - 01B4 SFFF           Reserved         32K         01B4 4000 - 01B4 BFFF           McASP0 Control Registers         16K         01B4 C000 - 01B4 FFFF           Reserved         192K         01B5 0000 - 01B7 FFFF           Reserved         256K         01B8 0000 - 01B8 FFFF           Emulation         256K         01BC 0000 - 01B3 FFFF           PCI Registers         256K         01BC 0000 - 01B3 FFFF           VPO Control         16K         01C0 0000 - 01C4 FFFF           VPO Control         16K         01C4 0000 - 01C4 3FFF           VP1 Control         16K         01C4 4000 - 01C4 3FFF           VP2 Control         16K         01C4 4000 - 01C4 7FFF           VP2 Control         16K         01C4 4000 - 01C4 7FFF           VP2 Control         16K         01C4 2000 - 01C4 FFFF           VP2 Control         16K         01C4 2000 - 01C4 FFFF           VP2 Control         16K         01C4 2000 - 01C4 FFFF           VP2 Control         4K         01C8 3000 - 01C8 0FFF           EMAC Control                                                                                                                                            | Reserved                                      | 512K                  | 01A4 0000 – 01AB FFFF |

| Device Configuration Registers         4K         01B3 F000 – 01B3 FFFF           I2C0 Data and Control Registers         16K         01B4 0000 – 01B4 FFFF           Reserved         32K         01B4 4000 – 01B4 FFFF           McASPO Control Registers         16K         01B4 C000 – 01B7 FFFF           Reserved         192K         01B5 0000 – 01B7 FFFF           Reserved         256K         01B8 0000 – 01B8 FFFF           Emulation         256K         01BC 0000 – 01B7 FFFF           Emulation         256K         01BC 0000 – 01B7 FFFF           PCI Registers         256K         01BC 0000 – 01B7 FFFF           VPO Control         16K         01C4 0000 – 01C3 FFFF           VPO Control         16K         01C4 0000 – 01C4 FFFF           VP1 Control         16K         01C4 4000 – 01C4 FFFF           VP2 Control         16K         01C4 8000 – 01C4 FFFF           VP2 Control         16K         01C4 8000 – 01C4 FFFF           VP2 Control         16K         01C4 8000 – 01C7 FFFF           Reserved         192K <td>Timer 2 Registers</td> <td>256K</td> <td>01AC 0000 - 01AF FFFF</td>                                                                   | Timer 2 Registers                             | 256K                  | 01AC 0000 - 01AF FFFF |

| 12C0 Data and Control Registers   16K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | GP0 Registers                                 | 256K – 4K             | 01B0 0000 - 01B3 EFFF |

| 12C0 Data and Control Registers   16K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Device Configuration Registers                | 4K                    | 01B3 F000 – 01B3 FFFF |

| Reserved       32K       01B4 4000 – 01B4 BFFF         McASP0 Control Registers       16K       01B4 C000 – 01B4 FFFF         Reserved       192K       01B5 0000 – 01B7 FFFF         Reserved       256K       01B8 0000 – 01BF FFFF         Emulation       256K       01BC 0000 – 01BF FFFF         PCI Registers       256K       01C0 0000 – 01C3 FFFF         VPO Control       16K       01C4 0000 – 01C4 3FFF         VP1 Control       16K       01C4 4000 – 01C4 7FFF         VP2 Control       16K       01C4 4000 – 01C4 FFFF         VP2 Control       16K       01C4 0000 – 01C4 FFFF         VP2 Control       16K       01C4 0000 – 01C4 FFFF         VP2 Control       16K       01C4 0000 – 01C4 FFFF         VP3 Control       16K       01C4 0000 – 01C4 FFFF         Reserved       192K       01C5 0000 – 01C7 FFFF         EMAC Control       4K       01C8 0000 – 01C8 0FFF         EMAC Wrapper       8K       01C8 1000 – 01C8 2FFF         EWRAP Registers       2K       01C8 3000 – 01C8 3FFF         MDIO Control Registers       2K       01C8 3000 – 01C8 3FFF         Reserved       3.5M       01C8 4000 – 01C8 2FFF FFFF         MCBSP 0 Data       64M       3000 000                                                                                                                                                                                                    |                                               | 16K                   | 01B4 0000 - 01B4 3FFF |

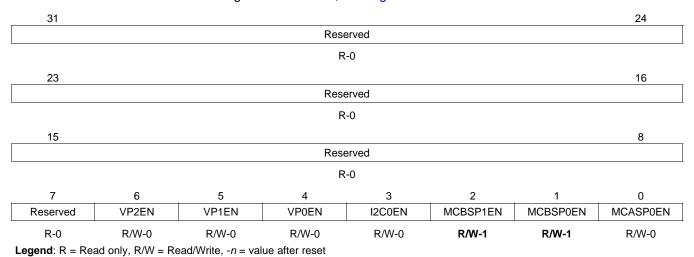

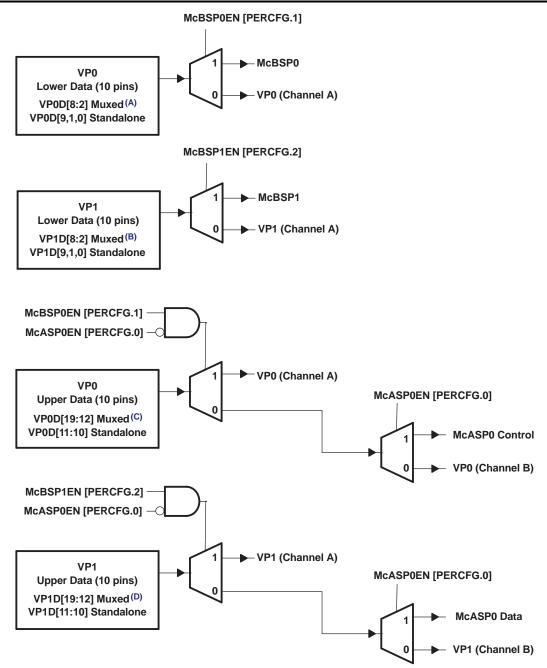

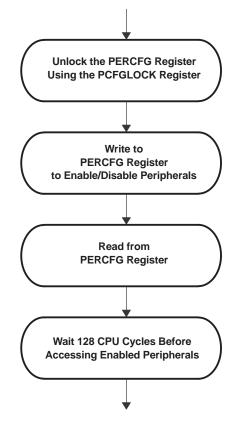

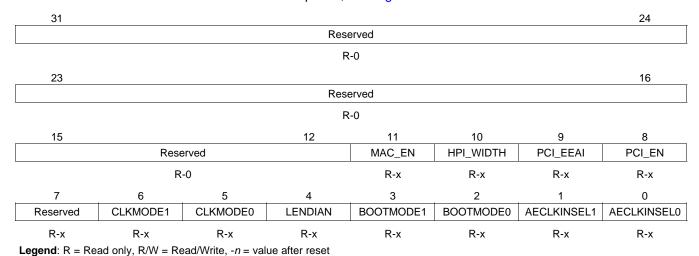

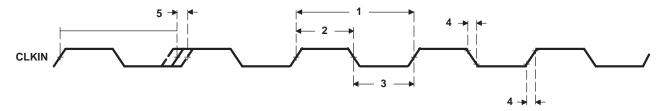

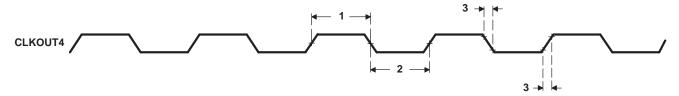

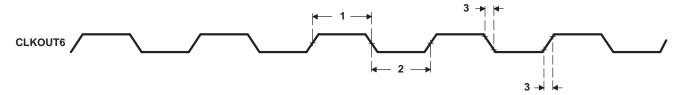

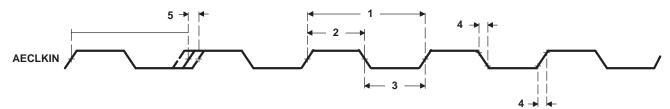

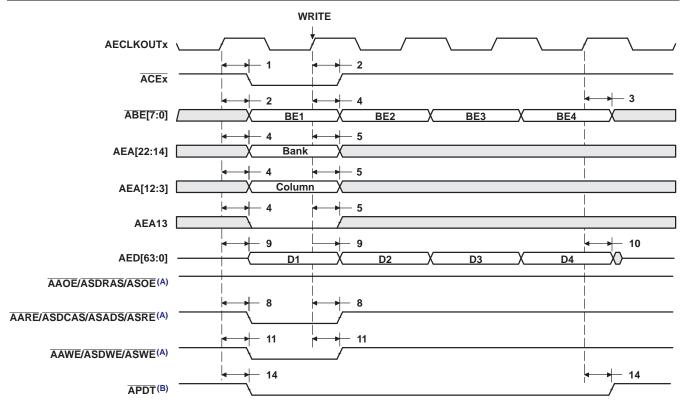

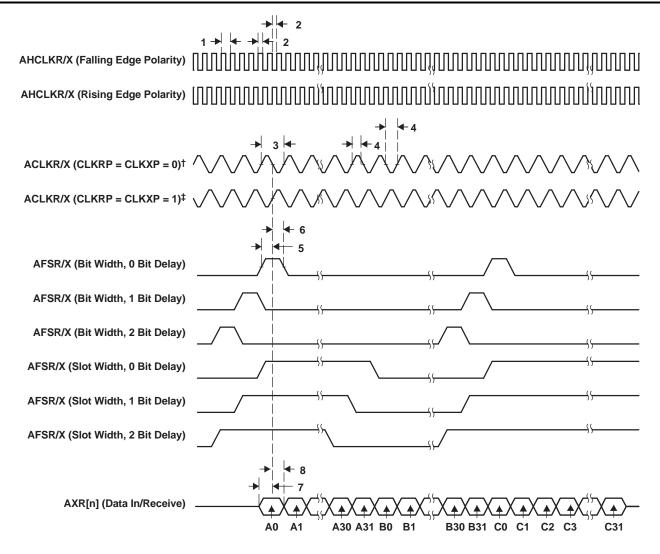

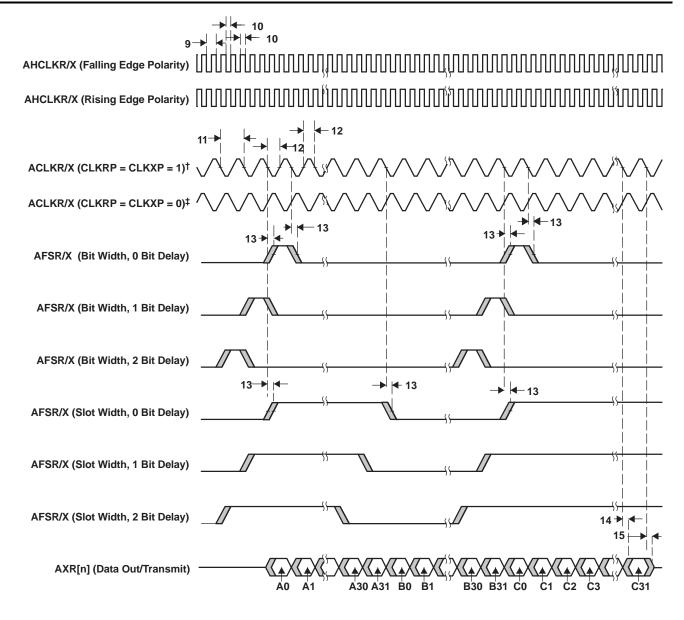

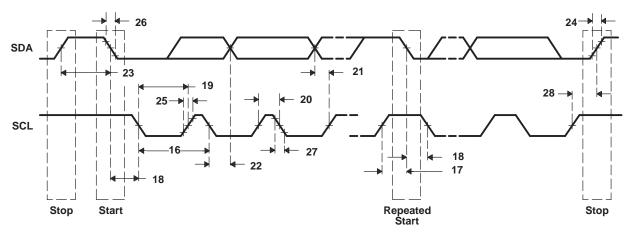

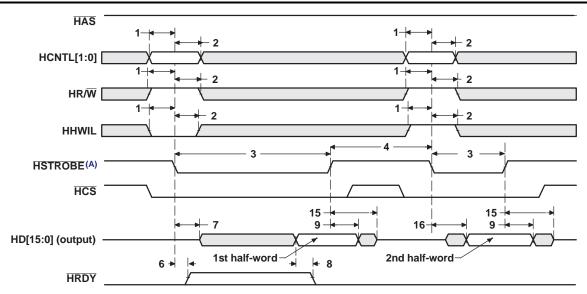

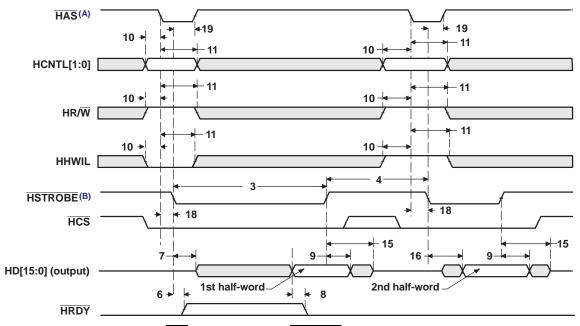

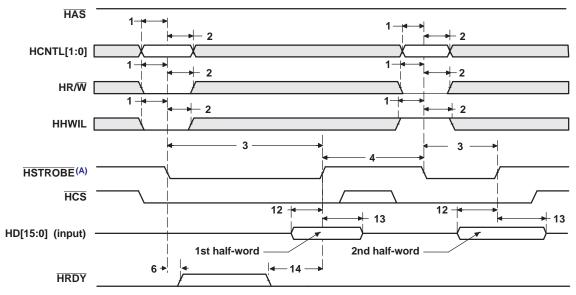

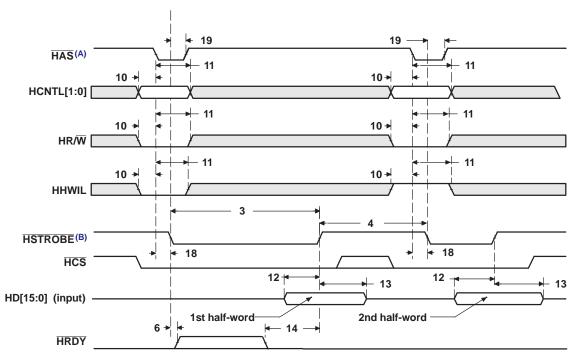

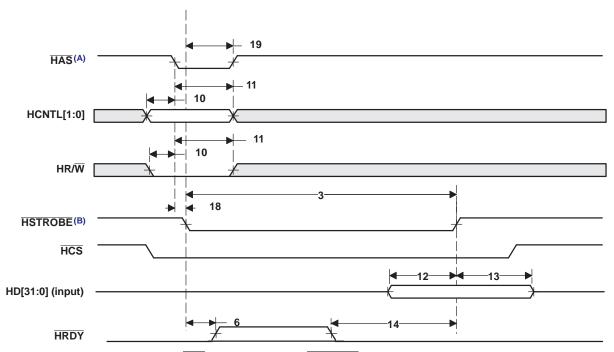

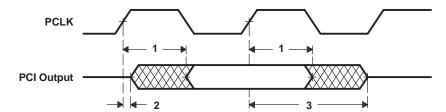

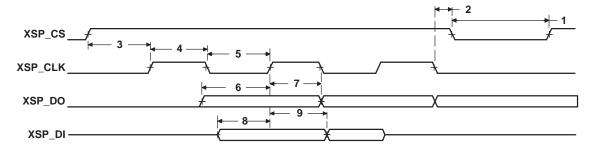

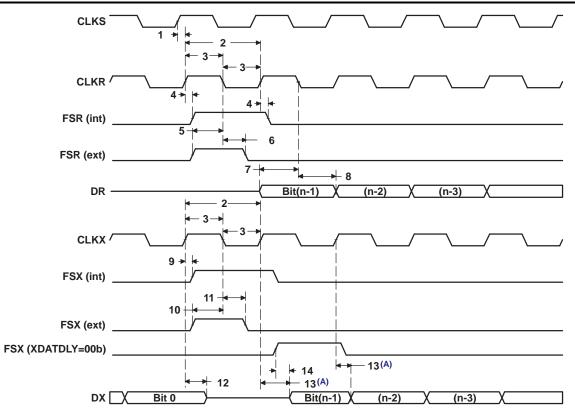

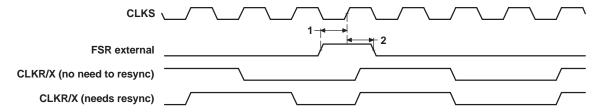

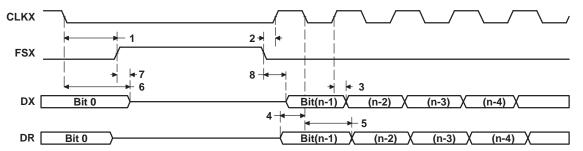

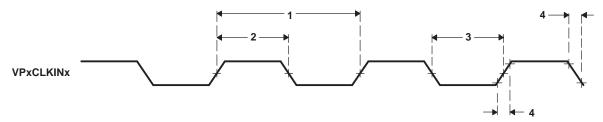

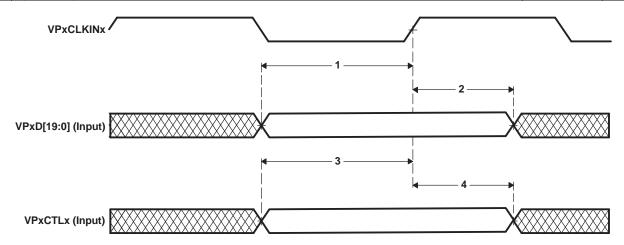

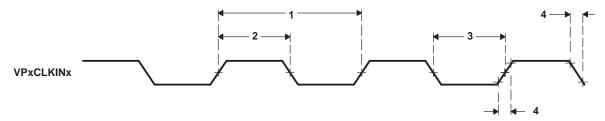

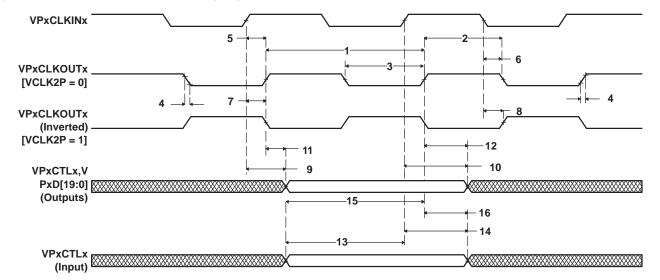

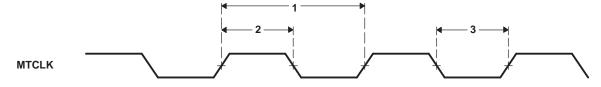

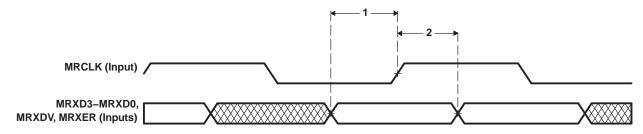

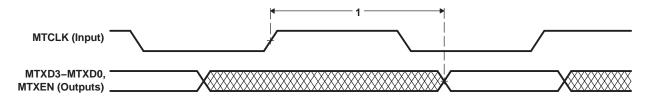

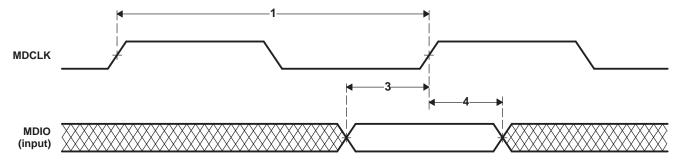

| Reserved         192K         0185 0000 – 0187 FFFF           Reserved         256K         0188 0000 – 018B FFFF           Emulation         256K         01BC 0000 – 01BF FFFF           PCI Registers         256K         01C0 0000 – 01C3 FFFF           VPO Control         16K         01C4 0000 – 01C4 3FFF           VP1 Control         16K         01C4 4000 – 01C4 7FFF           VP2 Control         16K         01C4 8000 – 01C4 BFFF           VIC Control         16K         01C4 0000 – 01C4 FFFF           Reserved         192K         01C5 0000 – 01C7 FFFF           EMAC Control         4K         01C8 0000 – 01C8 0FFF           EMAC Wrapper         8K         01C8 1000 – 01C8 2FFF           EWRAP Registers         2K         01C8 3000 – 01C8 37FF           MDIO Control Registers         2K         01C8 3000 – 01C8 3FFF           Reserved         3.5M         01C8 4000 – 01FF FFFF           QDMA Registers         52         0200 0000 – 0200 0033           Reserved         736M – 52         0200 0004 – 2FFF FFFF           McBSP 0 Data         64M         3000 0000 – 3FFF FFFF           McBSP 1 Data         64M         3400 0000 – 3FFF FFFF           McASPO Data         1M         3C00 0000 – 3C0F                                                                                                                                                |                                               | 32K                   | 01B4 4000 – 01B4 BFFF |