# TMC389–DATASHEET

Energy saving high resolution microstepping three phase stepper driver with step and direction interface and external power stage

TRINAMIC<sup>®</sup> Motion Control GmbH & Co. KG Hamburg, GERMANY

www.trinamic.com

## 1 Features

The TMC389 is an energy efficient three phase stepper motor driver for high resolution microstepping applications. It integrates a low resonance three phase chopper for quiet motor operation. Its step and direction interface allows simple use. An SPI™ management interface allows for parameterization and diagnostics. The TMC389 directly drives 3 external N/P channel dual MOSFETs for motor currents up to 8A and up to 60V. Protection and diagnostic features further reduce system cost and increase reliability.

#### Highlights

- Up to 171 microsteps (256 sine wave steps) using step/direction interface or 20 Bit SPI™ interface

- High precision sensorless motor load measurement stallGuard2

- Energy efficiency and coolness by automatic load dependant motor current regulation coolStep™: Save up to 75% of energy!

- Internal microstep extrapolation allows 256 wave step smoothness with low frequency step input

- Dual edge step option allows half step frequency requirement, e.g. for opto-couplers

- Up to 8A Motor current using external N&P channel MOSFET pairs

- Synchronous rectification reduces transistor heating

- 9V to 60V operating voltage (peak)

- 3.3V or 5V interface

- QFN32 package for extremely small solution with superior thermal performance

- EMV optimized current controlled gate drivers up to 45mA gate current

- Overcurrent, short to GND and overtemperature protection and diagnostics integrated

#### Applications

- Precision three phase stepper motor drives

- Stage lighting

- Medical applications

- Optical applications

- Robotics

#### Motor type

• 3 phase Stepper

# 2 Table of contents

| 1  | ۱ FEATURES 1 |                                                                                                                                        |    |  |  |  |  |

|----|--------------|----------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

| 2  | T/           | ABLE OF CONTENTS                                                                                                                       | 2  |  |  |  |  |

|    | 2.1          | DISCLAIMER                                                                                                                             | 3  |  |  |  |  |

| 3  | PI           | RINCIPLE OF OPERATION                                                                                                                  | 4  |  |  |  |  |

|    | 3.1          | Moving the motor                                                                                                                       | 4  |  |  |  |  |

|    | 3.           | 1.1 Step and direction control                                                                                                         |    |  |  |  |  |

|    | -            | 1.2 SPI control                                                                                                                        |    |  |  |  |  |

|    | 3.2          | Chopped motor coil driver<br>Energy efficient driver with load feedback                                                                |    |  |  |  |  |

|    | 3.3          |                                                                                                                                        |    |  |  |  |  |

| 4  | Ρ.           | INNING                                                                                                                                 |    |  |  |  |  |

|    | 4.1          | ТМС389-LА                                                                                                                              |    |  |  |  |  |

|    | 4.2          | Package codes<br>Dimensional drawings                                                                                                  |    |  |  |  |  |

|    | 4.3<br>4.    | 3.1 QFN32 dimensions                                                                                                                   |    |  |  |  |  |

| _  | •            | LOCK DIAGRAM                                                                                                                           |    |  |  |  |  |

| 5  |              |                                                                                                                                        |    |  |  |  |  |

|    | 5.1          | PIN DESCRIPTION OF TMC389-LA                                                                                                           |    |  |  |  |  |

| 6  | S            | PI™ MODE SHIFT REGISTER                                                                                                                | 10 |  |  |  |  |

|    | 6.1          | Overview (write)                                                                                                                       |    |  |  |  |  |

|    | 6.2          | OVERVIEW (READ)                                                                                                                        |    |  |  |  |  |

|    | 6.3          | DRIVER CONTROL REGISTER BIT ASSIGNMENT                                                                                                 |    |  |  |  |  |

|    |              | <ul> <li>Driver control register bit assignment in SPI mode</li> <li>Driver control register bit assignment in StepDir mode</li> </ul> |    |  |  |  |  |

|    | 6.4          | CONFIGURATION REGISTER BIT ASSIGNMENT                                                                                                  |    |  |  |  |  |

|    | 6.5          | BIT ASSIGNMENT FOR READ                                                                                                                |    |  |  |  |  |

|    | 6.6          | SPI™ TIMING                                                                                                                            | 17 |  |  |  |  |

| 7  | S            | TEP AND DIRECTION INTERFACE                                                                                                            | 18 |  |  |  |  |

|    | 7.1          | Timing                                                                                                                                 | 18 |  |  |  |  |

|    | 7.2          | INTERNAL MICROSTEP TABLE                                                                                                               |    |  |  |  |  |

|    | 7.3          | SWITCHING BETWEEN DIFFERENT MICROSTEP RESOLUTIONS                                                                                      |    |  |  |  |  |

|    | 7.4          | STEP RATE MULTIPLIER AND STAND STILL DETECTION                                                                                         | 19 |  |  |  |  |

| 8  | C            | URRENT SETTING                                                                                                                         | 21 |  |  |  |  |

|    | 8.1          | CONSIDERATIONS ON THE CURRENT SENSE RESISTORS AND LAYOUT                                                                               | 21 |  |  |  |  |

| 9  | C            | HOPPER OPERATION OF THE MOTOR COILS                                                                                                    | 23 |  |  |  |  |

|    | 9.1          | SPREADCYCLE CHOPPER                                                                                                                    | 24 |  |  |  |  |

| 1( | )            | MOSFET DRIVER STAGE                                                                                                                    | 26 |  |  |  |  |

|    | 10.1         | PRINCIPLE OF OPERATION                                                                                                                 | 26 |  |  |  |  |

|    | 10.1         | -                                                                                                                                      |    |  |  |  |  |

|    | 10.3         | ENN INPUT                                                                                                                              | 26 |  |  |  |  |

|    | 10.4         | SLOPE CONTROL IN TMC389                                                                                                                | 27 |  |  |  |  |

| 1: | L            | DIAGNOSTICS AND PROTECTION                                                                                                             | 28 |  |  |  |  |

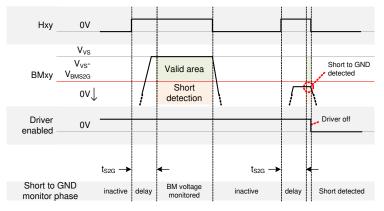

|    | 11.1         | SHORT TO GND DETECTION                                                                                                                 | 28 |  |  |  |  |

|    | 11.2         |                                                                                                                                        |    |  |  |  |  |

|    | 11.3         |                                                                                                                                        |    |  |  |  |  |

|    | 11.4         | UNDERVOLTAGE DETECTION                                                                                                                 | 30 |  |  |  |  |

| 12  | STA         | .LLGUARD₂™ SENSORLESS LOAD MEASUREMENT                                                                       |    |

|-----|-------------|--------------------------------------------------------------------------------------------------------------|----|

| 12. | _           | TUNING THE STALLGUARD2™ THRESHOLD SGT                                                                        |    |

| -   | 12.1.1      | Variable velocity operation<br>Accuracy and reproducibility of stallGuard2™ measurement                      |    |

| 12. | 12.1.2<br>~ | Accuracy and reproducibility of stallGuard2™ measurement<br>STALLGUARD2™ MEASUREMENT FREQUENCY AND FILTERING |    |

| 12. |             | DETECTING A MOTOR STALL.                                                                                     |    |

| 12. | -           | LIMITS OF STALLGUARD2 <sup>™</sup> OPERATION                                                                 | -  |

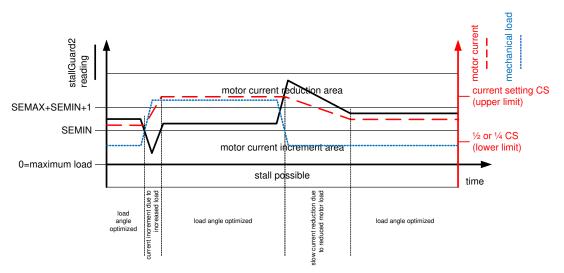

| 13  | CO(         | DLSTEP™ SMART ENERGY OPERATION                                                                               | 34 |

| 13. | .1          | COOLSTEP™ SMART ENERGY CURRENT REGULATOR                                                                     |    |

| -   | 13.1.1      | Adaptation to the load situation                                                                             |    |

| 2   | 13.1.2      |                                                                                                              |    |

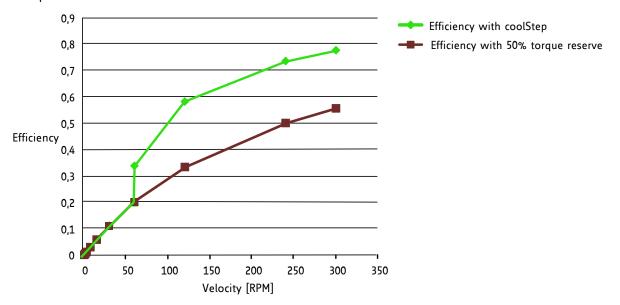

| 13. | .2          | USER BENEFITS, SAVE ENERGY, REDUCE POWER AND COOLING INFRASTRUCTURE                                          | 36 |

| 14  | POV         | NER SUPPLY SEQUENCING                                                                                        | 37 |

| 15  | CLO         | CK OSCILLATOR AND CLOCK INPUT                                                                                | 38 |

| 15. | .1          | CONSIDERATIONS ON THE FREQUENCY                                                                              | 38 |

| 16  | ABS         | OLUTE MAXIMUM RATINGS                                                                                        | 39 |

| 17  | ELE         | CTRICAL CHARACTERISTICS                                                                                      | 39 |

| 17. | .1          | Operational Range                                                                                            | 39 |

| 17. | .2          | DC CHARACTERISTICS AND TIMING CHARACTERISTICS                                                                | 40 |

| 17. | 3           | ESD SENSITIVE DEVICE                                                                                         |    |

| 17. | 4           | MOSFET EXAMPLES                                                                                              | 45 |

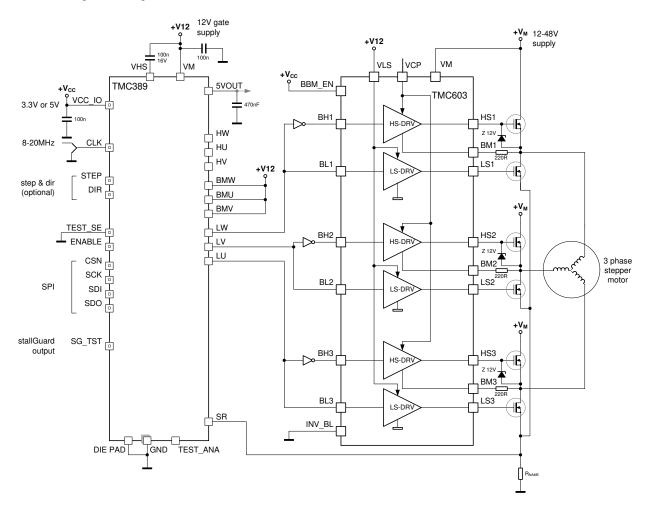

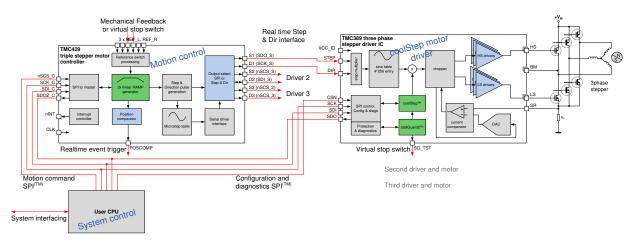

| 18  | USI         | NG AN EXTERNAL POWER STAGE FOR HIGHER VOLTAGE OR CURRENT                                                     | 46 |

| 19  | GET         | TING STARTED                                                                                                 | 47 |

| 19. | .1          | INITIALIZATION OF THE DRIVER.                                                                                | 47 |

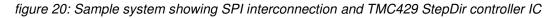

| 19. | .2          | SENDING SPI DATA FROM A CPU                                                                                  | 47 |

| 20  | TAB         | BLE OF FIGURES                                                                                               | 48 |

| 21  | REV         | ISION HISTORY                                                                                                | 48 |

| 21. | .1          | DOCUMENTATION REVISION                                                                                       | 48 |

#### 2.1 Disclaimer

TRINAMIC Motion Control GmbH & Co. KG does not authorize or warrant any of its products for use in life support systems, without the specific written consent of TRINAMIC Motion Control GmbH & Co. KG. Life support systems are equipment intended to support or sustain life, and whose failure to perform, when properly used in accordance with instructions provided, can be reasonably expected to result in personal injury or death.

Information given in this data sheet is believed to be accurate and reliable. However no responsibility is assumed for the consequences of its use nor for any infringement of patents or other rights of third parties which may result from its use.

Specifications are subject to change without notice.

™: All trademarks used are property of their respective owners.

## 3 Principle of operation

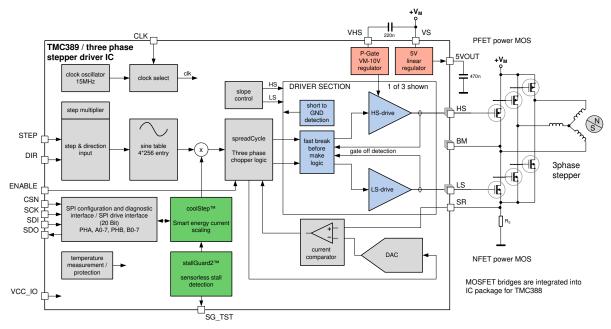

figure 1: Basic application block diagram

#### 3.1 Moving the motor

#### 3.1.1 Step and direction control

The TMC389 is a chopped stepper motor driver with integrated sequencer and SPI interface. It provides two possibilities to control the motor: The motor can be controlled by applying pulses on the step and direction interface, following an initialization phase which uses the SPI interface to parameterize the driver for the application. Control and diagnostic registers give the flexibility to react to changing operation conditions and to modify the behavior of the chip when it receives a step impulse. An internal microstep table supplies sine and cosine values which control the motor current for each step. Each step impulse advances the step pointer in the tables and hence leads to the IC executing the next microstep.

#### 3.1.2 SPI control

A second mode of operation uses the SPI interface, only. The motor coil currents can be controlled via the SPI interface, while taking advantage of all other control and diagnostic functions. This mode is more flexible, as the microstep waves can be specially adapted to the motor to give the best fit for smoothest operation. It requires slightly more CPU overhead to look up the driver tables and to send out new current values for both coils. The SPI update rate corresponds to the step rate at low velocities. At highest velocities the update rate can be limited to a few 10kHz or some 100kHz, depending on the processor power, or alternatively to an update rate corresponding to a fullstep.

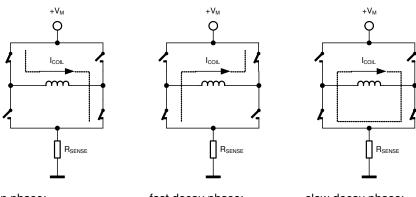

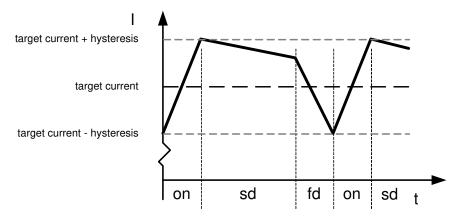

#### 3.2 Chopped motor coil driver

The driver use a cycle by cycle chopper mode: The motor current becomes regulated by comparing the motor current to a set value for each chopper cycle. This constant off time chopper scheme allows highest dynamic. The spreadCycle chopper scheme automatically integrates a fast decay cycle and guarantees smooth zero crossing performance. In an optional operation mode, fast decay length per cycle can be selected by the user. In this classic constant off time mode, zero crossing can be optimized by setting a programmable current offset.

#### 3.3 Energy efficient driver with load feedback

The TMC389 integrates a high resolution load measurement stallGuard2<sup>™</sup>, which allows sensing the mechanical load on the motor. This gives more information on the drive allowing functions like sensorless homing. Its coolStep<sup>™</sup> feature uses load measurement information to reduce the motor current to the minimum motor current required in the actual load situation. This saves lots of energy and keeps components cool, making the drive an efficient and precise solution.

# 4 Pinning

### 4.1 TMC389-LA

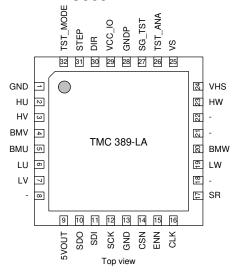

figure 2: TMC389 pinning

#### 4.2 Package codes

| Туре                     | Package      | Temperature range | Code/marking |

|--------------------------|--------------|-------------------|--------------|

| TMC389                   | QFN32 (ROHS) | -40°C +125°C      | TMC389-LA    |

| TMC389<br>eng.<br>sample | QFN32 (ROHS) | -40°C +125°C      | TMC389-ES    |

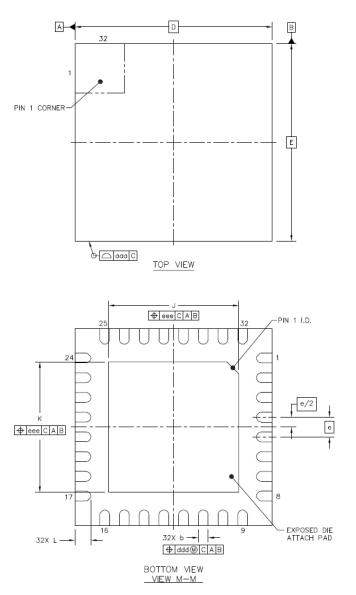

# **4.3 Dimensional drawings** For drawings, see next page.

Attention: Drawings not to scale.

#### 4.3.1 QFN32 dimensions

| Parameter              | Ref | Min  | Nom   | Max  |

|------------------------|-----|------|-------|------|

| total thickness        | А   | 0.80 | 0.85  | 0.90 |

| stand off              | A1  | 0.00 | 0.035 | 0.05 |

| mold thickness         | A2  | -    | 0.65  | 0.67 |

| lead frame thickness   | A3  |      | 0.203 |      |

| lead width             | b   | 0.2  | 0.25  | 0.3  |

| body size X            | D   |      | 5.0   |      |

| body size Y            | Е   |      | 5.0   |      |

| lead pitch             | е   |      | 0.5   |      |

| exposed die pad size X | J   | 3.2  | 3.3   | 3.4  |

| exposed die pad size Y | K   | 3.2  | 3.3   | 3.4  |

| lead length            | L   | 0.35 | 0.4   | 0.45 |

| package edge tolerance | aaa |      |       | 0.1  |

| mold flatness          | bbb |      |       | 0.1  |

| coplanarity            | CCC |      |       | 0.08 |

| lead offset            | ddd |      |       | 0.1  |

| exposed pad offset     | eee |      |       | 0.1  |

All dimensions are in mm.

figure 3: QFN32 5x5 dimensions

## 5 Block diagram

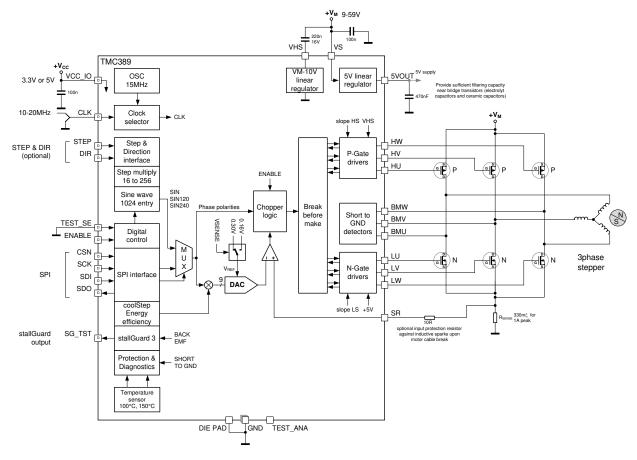

figure 4: TMC389 block and application schematic

The application schematic shows the basic building blocks of the IC and the connections to the power bridge transistors, as well as the power supply. The connection of the digital interface lines to the microcontroller and / or a motion controller is specific to the system architecture and the micro-controller type. Do not leave any input floating over extended periods of time, as there are no pull up or pull down resistors integrated. The choice of power MOSFETs for the TMC389 depends on the desired motor current and supply voltage. Please refer chapter 17.4. For even higher motor current capability, external MOSFET drivers can be added using full N channel bridges.

# 5.1 Pin description of TMC389-LA

| Pin               | Number         | Туре   | Function                                                                                                                                                                                                                                                                                                                                                                                          |  |

|-------------------|----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GND               | 1, 13          |        | Digital and analog low power GND                                                                                                                                                                                                                                                                                                                                                                  |  |

| HU<br>HV<br>HW    | 2,<br>3,<br>23 | O (VS) | High side P-channel driver output. Becomes driven to VHS to switch on MOSFET.                                                                                                                                                                                                                                                                                                                     |  |

| BMV<br>BMU<br>BMW | 4<br>5<br>20   | I (VS) | Sensing input for bridge outputs. Used for short to GND protection.<br>May be tied to VS if unused.                                                                                                                                                                                                                                                                                               |  |

| LU<br>LV<br>LW    | 6<br>7<br>19   | O 5V   | Low side MOSFET driver output. Becomes driven to 5VOUT to switch on MOSFET.                                                                                                                                                                                                                                                                                                                       |  |

| SR                | 17             | AI     | Sense resistor input of chopper driver.                                                                                                                                                                                                                                                                                                                                                           |  |

| 5VOUT             | 9              |        | Output of internal 5V linear regulator. This voltage is used to supply the low side drivers and internal analog circuitry. An external capacitor to GND close to the pin is required. Place the capacitor near to pin 9 and pin 13. 470nF ceramic are sufficient for most applications, an additional tantalum capacitor ( $10\mu$ F or more) improves performance with high gate charge MOSFETs. |  |

| SDO               | 10             | DO VIO | Data output of SPI interface (Tristate)                                                                                                                                                                                                                                                                                                                                                           |  |

| SDI               | 11             | DI VIO | Data input of SPI interface<br>(Scan test input in test mode)                                                                                                                                                                                                                                                                                                                                     |  |

| SCK               | 12             | DI VIO | Serial clock input of SPI interface<br>(Scan test shift enable input in test mode)                                                                                                                                                                                                                                                                                                                |  |

| CSN               | 14             | DI VIO | Chip select input of SPI interface                                                                                                                                                                                                                                                                                                                                                                |  |

| ENN               | 15             | DI VIO | Enable not input for drivers. Switches off all MOSFETs.                                                                                                                                                                                                                                                                                                                                           |  |

| CLK               | 16             | DI VIO | Clock input for all internal operations. Tie low to use internal oscillator. A high signal disables the internal oscillator until power down.                                                                                                                                                                                                                                                     |  |

| VHS               | 24             |        | High side supply voltage (motor supply voltage - 10V)                                                                                                                                                                                                                                                                                                                                             |  |

| VS                | 25             |        | Motor supply voltage                                                                                                                                                                                                                                                                                                                                                                              |  |

| TST_ANA           | 26             | AO VIO | Analog mode test output. Leave open or tie to GND for normal operation.                                                                                                                                                                                                                                                                                                                           |  |

| SG_TST            | 27             | DO VIO | stallGuard2™ output. Signals motor stall (high active).                                                                                                                                                                                                                                                                                                                                           |  |

| GNDP              | 28             |        | Power GND for MOSFET drivers. Connect directly to GND                                                                                                                                                                                                                                                                                                                                             |  |

| VCC_IO            | 29             |        | Input / output supply voltage VIO for all digital pins. Tie to digital logic supply voltage. Allows operation in 3.3V and 5V systems.                                                                                                                                                                                                                                                             |  |

| DIR               | 30             | DI VIO | Direction input. Is sampled upon detection of a step to determine stepping direction. An internal glitch filter for 60ns is provided.                                                                                                                                                                                                                                                             |  |

| STEP              | 31             | DI VIO | Step input. An internal glitch filter for 60ns is provided.                                                                                                                                                                                                                                                                                                                                       |  |

| TST_MODE          | 32             | DI VIO | Test mode input. Puts IC into test mode. Tie to GND for normal operation.                                                                                                                                                                                                                                                                                                                         |  |

| Exposed die pad   | -              | GND    | Connect the exposed die pad to a GND plane. It is used for cooling of the IC and may either be left open or be connected to GND.                                                                                                                                                                                                                                                                  |  |

## 6 <u>SPI™ mode shift register</u>

The TMC389 requires a configuration via SPI prior to operation. Its SPI interface also allows for reading back status flags. The SPI interface can operate up to the half clock frequency. The MSB (bit 19) is transmitted first. See chapter 6.6 and 19.2 for more details.

#### 6.1 Overview (write)

| Register/ | DRVCTRL            | DRVCTRL   | CHOPCONF | SMARTEN | SGCSCONF | DRVCONF |

|-----------|--------------------|-----------|----------|---------|----------|---------|

| Bit       | ( <i>SDOFF</i> =1) | (SDOFF=0) |          |         |          |         |

| 19        | 0                  | 0         | 1        | 1       | 1        | 1       |

| 18        | 0                  | 0         | 0        | 0       | 1        | 1       |

| 17        | PHU                | -         | 0        | 1       | 0        | 1       |

| 16        | CU7                | -         | TBL1     | 0       | SFILT    | TST     |

| 15        | CU6                | -         | TBL0     | SEIMIN  | SSPD     | SLPH1   |

| 14        | CU5                | -         | -        | SEDN1   | SGT6     | SLPH0   |

| 13        | CU4                | -         | RNDTF    | SEDN0   | SGT5     | SLPL1   |

| 12        | CU3                | -         | CSYNC    | -       | SGT4     | SLPL0   |

| 11        | CU2                | -         | CDIR     | SEMAX3  | SGT3     | -       |

| 10        | CU1                | -         | NOSD     | SEMAX2  | SGT2     | DISS2G  |

| 9         | CU0                | INTPOL    | HYST5    | SEMAX1  | SGT1     | TS2G1   |

| 8         | PHV                | DEDGE     | HYST4    | SEMAX0  | SGT0     | TS2G0   |

| 7         | CV7                | -         | HYST3    | -       | -        | SDOFF   |

| 6         | CV6                | -         | HYST2    | SEUP1   | -        | VSENSE  |

| 5         | CV5                | -         | HYST1    | SEUP0   | -        | RDSEL1  |

| 4         | CV4                | -         | HYST0    | -       | CS4      | RDSEL0  |

| 3         | CV3                | MRES3     | TOFF3    | SEMIN3  | CS3      | -       |

| 2         | CV2                | MRES2     | TOFF2    | SEMIN2  | CS2      | -       |

| 1         | CV1                | MRES1     | TOFF1    | SEMIN1  | CS1      | -       |

| 0         | CV0                | MRES0     | TOFF0    | SEMIN0  | CS0      | -       |

## 6.2 Overview (read)

| Bit | RDSEL=00 | RDSEL=01 | RDSEL=10 |

|-----|----------|----------|----------|

| 19  | MSTEP9   | SG9      | SG9      |

| 18  | MSTEP8   | SG8      | SG8      |

| 17  | MSTEP7   | SG7      | SG7      |

| 16  | MSTEP6   | SG6      | SG6      |

| 15  | MSTEP5   | SG5      | SG5      |

| 14  | MSTEP4   | SG4      | SE4      |

| 13  | MSTEP3   | SG3      | SE3      |

| 12  | MSTEP2   | SG2      | SE2      |

| 11  | MSTEP1   | SG1      | SE1      |

| 10  | MSTEP0   | SG0      | SE0      |

| 9   | -        | -        | -        |

| 8   | -        | -        | -        |

| 7   | STST     |          |          |

| 6   | -        |          |          |

| 5   | OL       |          |          |

| 4   | -        |          |          |

| 3   | S2G      |          |          |

| 2   | OTPW     |          |          |

| 1   | OT       |          |          |

| 0   | SG       |          |          |

#### 6.3 Driver control register bit assignment

The driver control register is used to operate the device in SPI mode by setting phase currents for Phase U and Phase V. Phase W is automatically calculated from the formula CW=-(CU+CV). In StepDir mode, it selects Step and Direction interface specific parameters. They need to be initialized once upon power up, and whenever basic parameters are required to be changed. Only write access is possible.

#### Notation of hexadecimal and binary numbers:

0x precedes a hexadecimal number, % precedes a multi-bit binary number

The meaning of register 0 depends on the mode selection between SPI mode and StepDir mode as selected by SDOFF (configuration register 11, bit 7).

| DRV | CTRL | write 0xxx, SDOFF=1           |                                                          |

|-----|------|-------------------------------|----------------------------------------------------------|

| Bit | Name | Function                      | Comment                                                  |

| 19  | CFR  | select configuration register | <b>0</b> : Operation mode dependent settings (see SDOFF) |

| 18  | -    | reserved                      | set to 0                                                 |

| 17  | PHU  | Polarity U                    |                                                          |

| 16  | CU7  | Current U MSB                 | 0 to max. 248 due to hysteresis setting. Depending on    |

| 15  | CU6  |                               | the hysteresis setting, the maximum value becomes        |

| 14  | CU5  |                               | even lower. The resulting value is not allowed to        |

| 13  | CU4  |                               | overflow 255.                                            |

| 12  | CU3  |                               |                                                          |

| 11  | CU2  |                               |                                                          |

| 10  | CU1  |                               |                                                          |

| 9   | CU0  | Current U LSB                 |                                                          |

| 8   | PHV  | Polarity V                    |                                                          |

| 7   | CV7  | Current V MSB                 | 0 to max. 248 due to hysteresis setting. Depending on    |

| 6   | CV6  |                               | the hysteresis setting, the maximum value becomes        |

| 5   | CV5  |                               | even lower. The resulting value is not allowed to        |

| 4   | CV4  |                               | overflow 255.                                            |

| 3   | CV3  |                               |                                                          |

| 2   | CV2  |                               |                                                          |

| 1   | CV1  |                               |                                                          |

| 0   | CV0  | Current V LSB                 |                                                          |

#### 6.3.1 Driver control register bit assignment in SPI mode

| DRV | CTRL   | write 0xxx, SDOFF=0               |                                                                                                            |                                                                                                              |                                                                                                                                                                                                                                                                                      |  |  |

|-----|--------|-----------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit | Name   | Function                          | Comment                                                                                                    |                                                                                                              |                                                                                                                                                                                                                                                                                      |  |  |

| 19  | CFR    | select configuration register     | <b>0</b> : Operation mode dependent settings (see SDOFF)                                                   |                                                                                                              |                                                                                                                                                                                                                                                                                      |  |  |

| 18  | -      | reserved                          | set to 0                                                                                                   |                                                                                                              |                                                                                                                                                                                                                                                                                      |  |  |

| 17  | -      | reserved                          | set to 0                                                                                                   |                                                                                                              |                                                                                                                                                                                                                                                                                      |  |  |

| 16  | -      | reserved                          | set to 0                                                                                                   |                                                                                                              |                                                                                                                                                                                                                                                                                      |  |  |

| 15  | -      | reserved                          | set to 0                                                                                                   |                                                                                                              |                                                                                                                                                                                                                                                                                      |  |  |

| 14  | -      | reserved                          | set to 0                                                                                                   |                                                                                                              |                                                                                                                                                                                                                                                                                      |  |  |

| 13  | -      | reserved                          | set to 0                                                                                                   |                                                                                                              |                                                                                                                                                                                                                                                                                      |  |  |

| 12  | -      | reserved                          | set to 0                                                                                                   |                                                                                                              |                                                                                                                                                                                                                                                                                      |  |  |

| 11  | -      | reserved                          | set to 0                                                                                                   |                                                                                                              |                                                                                                                                                                                                                                                                                      |  |  |

| 10  | -      | reserved                          | set to 0                                                                                                   |                                                                                                              |                                                                                                                                                                                                                                                                                      |  |  |

| 9   | INTPOL | enable step<br>interpolation      | resolution<br>extrapolate<br>starting be                                                                   | 16x microste<br>ed to 256 mic<br>low step dista                                                              | e multiplication by 16. Only in<br>eps, the microstepping becomes<br>crosteps. Interpolation is possible<br>ance of max. 2^20 CLK periods.                                                                                                                                           |  |  |

| 8   | DEDGE  | enable double edge<br>step pulses |                                                                                                            | 1: Enable step impulse at each step edge to reduce<br>step frequency requirement                             |                                                                                                                                                                                                                                                                                      |  |  |

| 7   | -      | reserved                          | set to 0                                                                                                   | 2                                                                                                            |                                                                                                                                                                                                                                                                                      |  |  |

| 6   | -      | reserved                          | set to 0                                                                                                   |                                                                                                              |                                                                                                                                                                                                                                                                                      |  |  |

| 5   | -      | reserved                          | set to 0                                                                                                   |                                                                                                              |                                                                                                                                                                                                                                                                                      |  |  |

| 4   | -      | reserved                          | set to 0                                                                                                   |                                                                                                              |                                                                                                                                                                                                                                                                                      |  |  |

| 3   | MRES3  | micro step resolution             | %0000                                                                                                      | %1000                                                                                                        |                                                                                                                                                                                                                                                                                      |  |  |

| 2   | MRES2  | for step/direction mode           |                                                                                                            |                                                                                                              |                                                                                                                                                                                                                                                                                      |  |  |

| 1   | MRES1  |                                   | MRES                                                                                                       | electrical                                                                                                   | mechanical                                                                                                                                                                                                                                                                           |  |  |

| 0   | MRES0  |                                   | _%0000                                                                                                     | 256                                                                                                          | 170.66                                                                                                                                                                                                                                                                               |  |  |

|     |        |                                   | _%0001                                                                                                     | 128                                                                                                          | 85.33                                                                                                                                                                                                                                                                                |  |  |

|     |        |                                   | _%0010                                                                                                     | 64                                                                                                           | 42.66                                                                                                                                                                                                                                                                                |  |  |

|     |        |                                   | _%0011                                                                                                     | 32                                                                                                           | 21.33                                                                                                                                                                                                                                                                                |  |  |

|     |        |                                   | _%0100                                                                                                     | 16                                                                                                           | 10.66                                                                                                                                                                                                                                                                                |  |  |

|     |        |                                   | _%0101                                                                                                     | 8                                                                                                            | 5.33                                                                                                                                                                                                                                                                                 |  |  |

|     |        |                                   | %0110                                                                                                      | 4                                                                                                            | 2.66                                                                                                                                                                                                                                                                                 |  |  |

|     |        |                                   | %0111                                                                                                      | 2                                                                                                            | 1.33                                                                                                                                                                                                                                                                                 |  |  |

|     |        |                                   | %1000                                                                                                      | 1                                                                                                            | 0.66                                                                                                                                                                                                                                                                                 |  |  |

|     |        |                                   | steps take<br>resulting<br>describes<br>fullsteps is<br>into accou<br>to a lowe<br>patterns.<br>step width | en per elec<br>mechanical<br>the number of<br>2/3 of the c<br>nt, that the m<br>er resolution<br>=2^MRES [el | given describe the number of<br>trical quarter sine wave. The<br>microstep resolution which<br>of microsteps between two motor<br>orresponding value. Please take<br>nicrostep position when switching<br>determines the sequence of<br>ectrical microsteps]<br>S [motor microsteps] |  |  |

#### 6.3.2 Driver control register bit assignment in StepDir mode

## 6.4 Configuration register bit assignment

The configuration registers select the mode of operation and set all motor and application dependent parameters. They need to be initialized once upon power up, and whenever basic parameters are required to be changed. Only write access is possible.

| СНО      | PCONF              | write 100x: Chopper Co        | onfiguratio                                              | on                                                                                                                                                                            |  |  |

|----------|--------------------|-------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit      | Name               | Function                      | Comme                                                    | Comment                                                                                                                                                                       |  |  |

| 19       | CFR                | select configuration register |                                                          | 1: Configuration register                                                                                                                                                     |  |  |

| 18<br>17 | CFRSEL1<br>CFRSEL0 | select configuration register | % <b>00</b> : Ch                                         | nopper configuration register                                                                                                                                                 |  |  |

| 16       | TBL1               | blank time select             | %00 9                                                    | %11:                                                                                                                                                                          |  |  |

| 15       | TBL0               |                               | Set com                                                  | parator blank time to 16, 24, 36 or 54 clocks                                                                                                                                 |  |  |

| 14       | CHM                | chopper mode                  | 0                                                        | Standard mode                                                                                                                                                                 |  |  |

|          |                    |                               | 1                                                        | unused                                                                                                                                                                        |  |  |

| 13       | RNDTF              | random TOFF time              | 0                                                        | Chopper off time is fixed as set by bits t <sub>OFF</sub>                                                                                                                     |  |  |

|          |                    |                               | 1                                                        | Random mode, $t_{OFF}$ is random modulated by $dN_{CLK}$ = -12 +3 clocks.                                                                                                     |  |  |

| 12       | CSYNC              | chopper                       | 0                                                        | Chopper runs freely                                                                                                                                                           |  |  |

|          |                    | synchronization               | 1                                                        | Chopper becomes synchronized to step frequency                                                                                                                                |  |  |

| 11       | CDIR               | chopper direction             | 0                                                        | Chopper direction is WVU with DIR input=0<br>Choose for turn left in SPI operation                                                                                            |  |  |

|          |                    |                               | 1                                                        | Chopper direction is UVW with DIR input=0<br>Choose for turn right $(U \rightarrow V \rightarrow W)$ in SPI<br>operation and for StepDir operation                            |  |  |

| 10       | NOSD               | skip slow decay phase         | 0                                                        | Each chopper on cycle is followed by a slow decay phase as set by TOFF                                                                                                        |  |  |

|          |                    |                               | 1                                                        | Slow decay phases are skipped between the<br>chopper phases, except directly following a<br>short to GND or chopper synchronization.<br>Minimum blank time then is 36 clocks. |  |  |

| 9        | HYST5              | hysteresis value              | DAC hys                                                  | steresis setting:                                                                                                                                                             |  |  |

| 8        | HYST4              |                               | %00000                                                   | 0 %111111.0 63                                                                                                                                                                |  |  |

| 7        | HYST3              |                               | (1/512 of this setting adds to coil current setting)     |                                                                                                                                                                               |  |  |

| 6        | HYST2              |                               | Attention:                                               |                                                                                                                                                                               |  |  |

| 5        | HYST1              |                               | Effective HYST/2 must be ≤ 255-sinewave peak (248 at     |                                                                                                                                                                               |  |  |

| 4        | HYST0              |                               | max. current setting) – Reduce current setting to 28 for |                                                                                                                                                                               |  |  |

|          |                    |                               |                                                          | m hysteresis.                                                                                                                                                                 |  |  |

|          |                    |                               | Do not work with too small setting (poor performance).   |                                                                                                                                                                               |  |  |

| 3        | TOFF3              | off time                      | Off time setting for constant t <sub>OFF</sub> chopper   |                                                                                                                                                                               |  |  |

| 2        | TOFF2              | and driver enable             | $N_{CLK}$ = 12 + 32*TOFF (Minimum is 64 clocks)          |                                                                                                                                                                               |  |  |

| 1        | TOFF1              |                               |                                                          | Driver disable, all bridges off                                                                                                                                               |  |  |

| 0        | TOFF0              |                               |                                                          | not allowed                                                                                                                                                                   |  |  |

|          |                    |                               | %0010.                                                   | %1111: 2 15                                                                                                                                                                   |  |  |

| SMA | RTEN    | write 1010: Smart_energy control coolStep™   |                                                                                                                                                          |  |  |

|-----|---------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit | Name    | Function                                     | Comment                                                                                                                                                  |  |  |

| 19  | CFR     | select configuration register                | 1: configuration register                                                                                                                                |  |  |

| 18  | CFRSEL1 | select configuration                         | %01: coolStep configuration register                                                                                                                     |  |  |

| 17  | CFRSEL0 | register                                     |                                                                                                                                                          |  |  |

| 16  | -       | reserved                                     | set to 0                                                                                                                                                 |  |  |

| 15  | SEIMIN  | minimum current for<br>smart current control | 0: 1/2 of current setting (CS)<br>1: 1/4 of current setting (CS)                                                                                         |  |  |

| 14  | SEDN1   | current down step                            | %00: for each 32 stallGuard values decrease by one                                                                                                       |  |  |

| 13  | SEDN0   | speed                                        | %01: for each 8 stallGuard values decrease by one<br>%10: for each 2 stallGuard values decrease by one<br>%11: for each stallGuard value decrease by one |  |  |

| 12  | -       | reserved                                     | set to 0                                                                                                                                                 |  |  |

| 11  | SEMAX3  | stallGuard hysteresis                        | If the stallGuard result is equal to or above                                                                                                            |  |  |

| 10  | SEMAX2  | value for smart current                      | (SEMIN+SEMAX+1)*32, the motor current becomes                                                                                                            |  |  |

| 9   | SEMAX1  | control                                      | decreased to save energy.                                                                                                                                |  |  |

| 8   | SEMAX0  |                                              | %0000 %1111: 0 15                                                                                                                                        |  |  |

| 7   | -       | reserved                                     | set to 0                                                                                                                                                 |  |  |

| 6   | SEUP1   | current up step width                        | Current steps per measured stallGuard value                                                                                                              |  |  |

| 5   | SEUP0   |                                              | %00 %11: 1, 2, 4, 8                                                                                                                                      |  |  |

| 4   | -       | reserved                                     | set to 0                                                                                                                                                 |  |  |

| 3   | SEMIN3  | minimum stallGuard                           | If the stallGuard result falls below SEMIN*32, the motor                                                                                                 |  |  |

| 2   | SEMIN2  | value for smart current                      | current becomes increased to reduce motor load angle.                                                                                                    |  |  |

| 1   | SEMIN1  | control and                                  | %0000: coolStep current control off                                                                                                                      |  |  |

| 0   | SEMIN0  | smart current enable                         | %0001 %1111: 1 15                                                                                                                                        |  |  |

| SGC | SCONF   | write 110x: Load measurement stallGuard2 and Current Setting |              |                                                                                                               |  |

|-----|---------|--------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------|--|

| Bit | Name    | Function                                                     | Comment      |                                                                                                               |  |

| 19  | CFR     | select configuration register                                | <b>1</b> : C | Configuration register                                                                                        |  |

| 18  | CFRSEL1 | select configuration                                         | %10          | <b>D</b> : stallGuard and current configuration register                                                      |  |

| 17  | CFRSEL0 | register                                                     |              |                                                                                                               |  |

| 16  | SFILT   | stallGuard filter enable                                     | 0            | Standard mode, high time resolution for stallGuard                                                            |  |

|     |         |                                                              | 1            | Filtered mode, stallGuard signal updated for each<br>six fullsteps only to compensate for motor<br>tolerances |  |

| 15  | SSPD    | stallGuard speed                                             | 0            | Standard mode, high time resolution for stallGuard                                                            |  |

|     |         |                                                              | 1            | StallGuard uses more filtering, use for low motor velocity only                                               |  |

| 14  | SGT6    | stallGuard threshold                                         |              | s signed value controls stallGuard level for stall                                                            |  |

| 13  | SGT5    | value                                                        |              | out and sets the optimum measurement range for                                                                |  |

| 12  | SGT4    |                                                              |              | dout. A lower value gives a higher sensitivity. Zero is                                                       |  |

| 11  | SGT3    |                                                              |              | starting value working with most motors.                                                                      |  |

| 10  | SGT2    |                                                              | -64          | to +63: A higher value makes stallGuard less                                                                  |  |

| 9   | SGT1    |                                                              |              | sensitive and requires more torque to                                                                         |  |

| 8   | SGT0    |                                                              |              | indicate a stall.                                                                                             |  |

| 7   | -       | reserved                                                     | set          | to 0                                                                                                          |  |

| 6   | -       | reserved                                                     | set          | to 0                                                                                                          |  |

| 5   | -       | reserved                                                     | set          |                                                                                                               |  |

| 4   | CS4     | current scale                                                |              | rent scaling for SPI and step/direction operation                                                             |  |

| 3   | CS3     | (scales digital currents                                     |              | 0000 %11111: 1/32, 2/32, 3/32, 32/32                                                                          |  |

| 2   | CS2     | A and B)                                                     |              | ention: Maximum possible current scale setting might                                                          |  |

| 1   | CS1     |                                                              | be k         | below 31, depending on hysteresis setting.                                                                    |  |

| 0   | CS0     |                                                              |              |                                                                                                               |  |

| DRV | CONF    | write 111x: Driver Confi                        | guration                                                                                                                                                                                                                                                   |  |  |

|-----|---------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit | Name    | Function                                        | Comment                                                                                                                                                                                                                                                    |  |  |

| 19  | CFR     | select configuration register                   | 1: Configuration register                                                                                                                                                                                                                                  |  |  |

| 18  | CFRSEL1 | select configuration                            | %11: Driver configuration register                                                                                                                                                                                                                         |  |  |

| 17  | CFRSEL0 | register                                        |                                                                                                                                                                                                                                                            |  |  |

| 16  | TST     | reserved TEST mode                              | Set to 0. When 1, SG_TST outputs digital test values,<br>and TEST_ANA outputs analog test values. Selection is<br>done by SGT0 and SGT1 (%00 %10):<br>For TEST_ANA: anatest_2vth, anatest_dac_out,<br>anatest_vdd_half.<br>For SG_TST: comp_A, comp_B, CLK |  |  |

| 15  | SLPH1   | Slope control high side                         | %00: min, %01: min + tc, %10: med + tc, %11: max                                                                                                                                                                                                           |  |  |

| 14  | SLPH0   |                                                 | In temperature compensated mode (tc), the driver<br>strength is increased if the overtemperature prewarning<br>temperature is reached. This compensates for<br>temperature dependence of high side slope control.                                          |  |  |

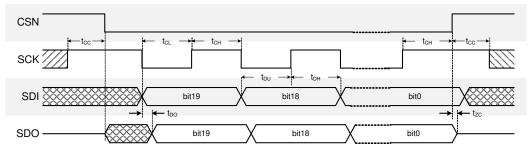

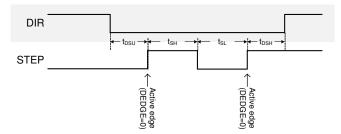

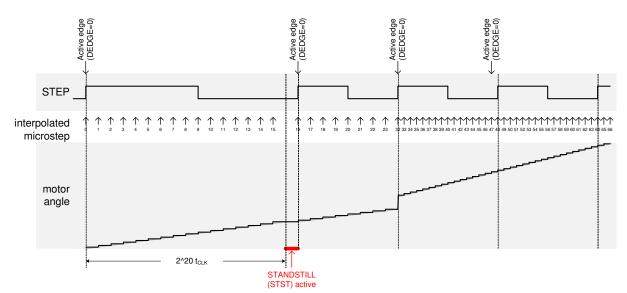

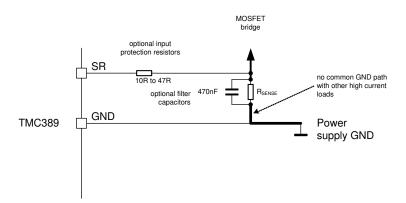

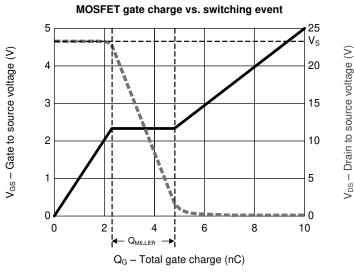

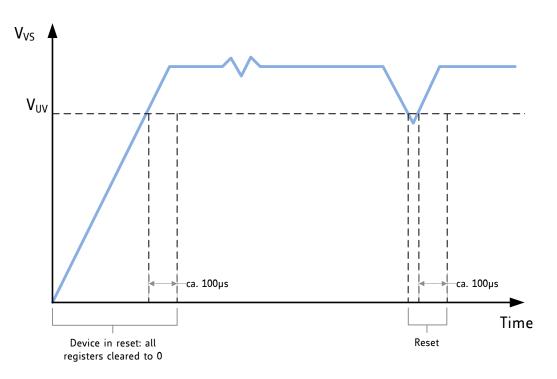

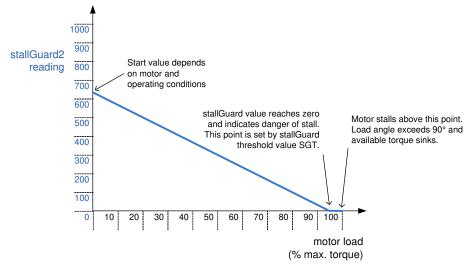

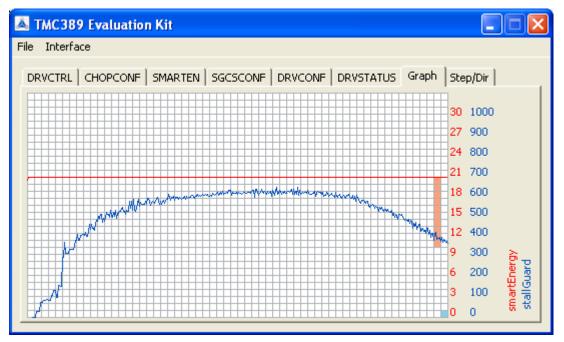

| 13  | SLPL1   | Slope control low side                          | 00, 01: min, 10: med, 11: max                                                                                                                                                                                                                              |  |  |