# **THC7984**

## 10-bit 3-channel Video Signal Digitizer

#### **General Description**

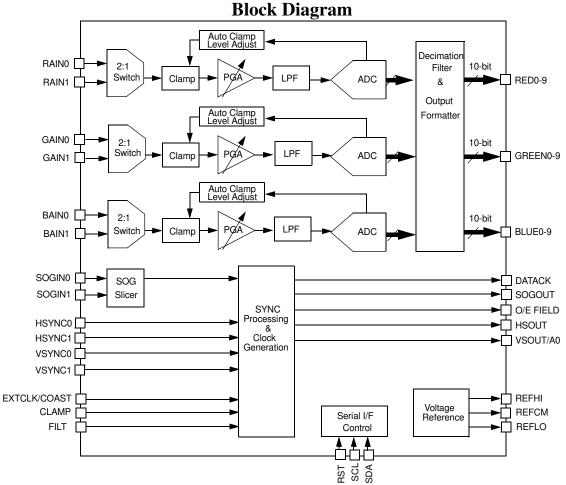

The THC7984 integrates all the functions to digitize analog video signals on a single chip.

#### **Acceptable Signals**

PC Graphics (RGB) : VGA-UXGA

- Separate Sync

- Composite Sync

- Sync on Green

Component Video (YPbPr):

- SDTV (480i / 480p) 2-level Sync

- HDTV (1080i / 720p / 1080p) 3-level Sync

- Protection Signal

### Applications

LCD TV / PDP TV Rear-Projection TV LCD Display / PDP Display Front Projector etc.

## **Features**

- 170 MSPS 10-bit ADC

- Internal 14-bit ADCs

- Oversampling functions (2x, 4x, and 8x)

- Line-locked PLL with low jitter

- Phase adjustment: 64 steps

Fine clamp / preamp

- Pedestal / center clamp

- Clamp level auto adjust

- Very low gain mismatch

- Gain adjustment: 2048 steps

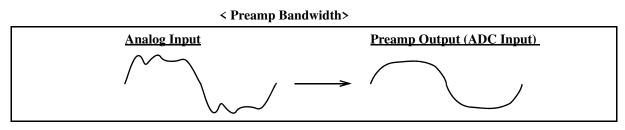

- Video Filter (LPF)

- Bandwidth adjustment: 28 steps (6MHz 310MHz)

Sync Processor

- 2-level / 3-level sync slicer

- Advanced sync detection / measurement

- Automatic sync processing mode

- IRQ Output

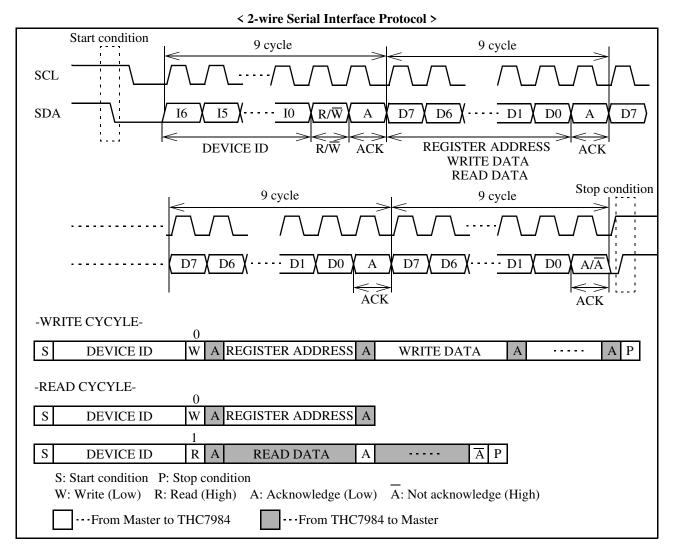

- 2-wire serial interface

- LQFP 80-pin package

## **Specifications**

VD=1.8V, VDD=3.3V, PVD=1.8V, DAVDD=1.8V, ADC Clock=Maximum Conversion Rate, Full Temperature Range=0° C to 70° C Analog Input Voltage=0.5 to 1.0Vpp

|                 |                                                            | T             | Test     | THC               | 7984-17    | 7               | ي: ما ا        |

|-----------------|------------------------------------------------------------|---------------|----------|-------------------|------------|-----------------|----------------|

|                 | Parameter                                                  | Temp          | Level    | Min               | Тур        | Max             | Unit           |

| RESOLUTION      | Number of Bits                                             |               |          |                   | 10         |                 | Bits           |

|                 | LSB Size                                                   |               |          |                   | 0.098      |                 | %FS            |

| DC ACCURACY     | Differential Nonlinearity                                  | 25° C         | I        |                   | $\pm 0.75$ |                 | LSB            |

|                 |                                                            | Full          | VI       |                   |            | -1.0/+1.25      | LSB            |

|                 | Integral Nonlinearity                                      | 25° C         | I        |                   | ± 1.5      | <u>± 3</u>      | LSB            |

|                 | No Mississ Octo                                            | Full          | VI       |                   | <u> </u>   | ± 4             | LSB            |

| ANALOG INPUT    | No Missing Code<br>Minimum Input Voltage                   | 25°C<br>Full  | I<br>VI  | G                 | uarante    |                 | V a a          |

| ANALUG INPUT    | Maximum Input Voltage                                      | Full          | VI       | 1.0               |            | 0.5             | V p-p<br>V p-p |

|                 | Gain Tempco                                                | 25° C         | V        | 1.0               | 100        |                 | ppm/°C         |

|                 | Input Bias Current <sup>*1</sup>                           | 25° C         | ĪV       |                   | 100        | 1               | μΑ             |

|                 | Input Blas Current                                         | Full          | IV       |                   |            | 1               | μΑ             |

|                 | Input Offset Voltage                                       | Full          | VI       |                   | ± 1        |                 | LSB            |

|                 | Input Full-Scale Matching                                  | Full          | VI       |                   | 0.2        | 0.8             | %              |

|                 | Between Channels                                           | Full          | V I      |                   | 0.2        | 0.8             | 70             |

|                 | Offset Adjustment Range                                    | Full          | VI       |                   | 50         |                 | %FS            |

| SWITCHING       | Maximum Conversion Rate                                    | Full          | VI       | 170               |            |                 | MSPS           |

| PERFORMANCE     | Minimum Conversion Rate                                    | Full          | IV       |                   |            | 10              | MSPS           |

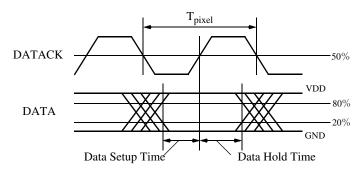

|                 | Data Setup Time to Clock <sup>*2</sup>                     | Full          | IV       | 0.48Tpixel-2.1    |            |                 | ns             |

|                 | Data Hold Time to Clock <sup>*2</sup>                      | Full          | IV       | 0.48Tpixel-0.4    |            |                 | ns             |

|                 | Duty Cycle, DATACK *2                                      | Full          | IV       | 40                | 50         | 60              | %              |

|                 | HSYNC Input Frequency                                      | Full          | IV       | 15                |            | 110             | kHz            |

|                 | Maximum PLL Clock Rate                                     | Full          | VI       | 170               |            |                 | MHz            |

|                 | Minimum PLL Clock Rate                                     | Full          | IV       |                   |            | 10              | MHz            |

|                 | PLL Jitter *3                                              | 25° C         | V        |                   | 500        |                 | ps p-p         |

|                 | Sampling Phase Tempco                                      | Full          | IV       |                   | 15         |                 | ps∕°C          |

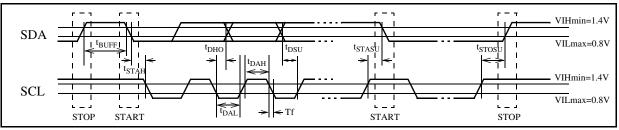

| 2-WIRE SERIAL   | SCL Clock Frequency(fSCL)                                  | Full          | IV       |                   |            | 100             | kHz            |

| INTERFACE       | tBUFF                                                      | Full          | IV       | 4.7               |            |                 | μs             |

|                 | tSTAH                                                      | Full          | IV       | 4.0               |            |                 | μs             |

|                 | tDHO                                                       | Full          | IV       | 0                 |            | 3.45            | μs             |

|                 | tDAL                                                       | Full          | IV       | 4.7               |            |                 | μs             |

|                 | tDAH                                                       | Full          | IV       | 4.0               |            |                 | μs             |

|                 | tDSU<br>tSTASU                                             | Full<br>Full  | IV<br>IV | <u>250</u><br>4.7 |            |                 | ns             |

|                 | tSTASU                                                     | Full          | IV       | 4.0               |            |                 | µs<br>µs       |

|                 | Tr                                                         | Full          | IV       | 4.0               |            | 1000            | µs<br>ns       |

|                 | Tf                                                         | Full          | IV       |                   |            | 150             | ns             |

|                 | Capacitive Load ( Cb )                                     | Full          | IV       |                   |            | 400             | pF             |

|                 | Noise margin at the LOW level (VnL)                        | Full          | IV       | 0.2               |            |                 | V              |

|                 | Noise margin at the HIGH level (VnH)                       | Full          | IV       | 0.25              |            |                 | V              |

| DIGITAL INPUTS  | Input Voltage, High (VIH)                                  | Full          | VI       | 1.4               |            |                 | V              |

|                 | Input Voltage, Low (VIL)                                   | Full          | VI       |                   |            | 0.8             | V              |

|                 | Input Current, High (IIH)                                  | Full          | V        |                   |            | 10              | μA             |

|                 | Input Current, Low (IIL)                                   | Full          | V        |                   |            | 10              | μA             |

|                 | Input Capacitance                                          | 25° C         | V        |                   | 2          |                 | рF             |

| DIGITAL OUTPUTS | Output Voltage, High (VOH)                                 | Full          | VI       | VDD-0.2           |            |                 | V              |

|                 | Output Voltage, Low (VOL)                                  | Full          | VI       |                   |            | 0.2             | V              |

|                 | Output Coding                                              |               |          | · -               | Binary     |                 |                |

| POWER SUPPLY    | VD Supply Voltage                                          | Full          | IV       | 1.7               | 1.8        | 1.9             | V              |

|                 | VDD Supply Voltage                                         | Full          | IV       | 2.3               | 3.3        | 3.45            | V              |

|                 | PVD Supply Voltage                                         | Full          | IV<br>IV | <u>1.7</u><br>1.7 | 1.8<br>1.8 | 1.9             | V<br>V         |

|                 | DAVDD Supply Voltage<br>ID Supply Current (VD)             | Full<br>25°C  | V        | 1.7               | 1.8        | 1.9<br>295      | •              |

|                 |                                                            |               |          |                   |            |                 | m A            |

|                 | IDD Supply Current (VDD) *4                                | 25°C<br>25°C  | V<br>V   |                   |            | 180<br>30       | m A            |

|                 | IPVD Supply Current (PVD)<br>IDAVDD Supply Current (DAVDD) | 25 C<br>25° C | V        |                   |            | <u>30</u><br>65 | m A<br>m A     |

|                 | Total Power Dissipation                                    | Z5 C<br>Full  | VI       |                   |            | 1350            | m A<br>m W     |

|                 | Power-Down Supply Current                                  | Full          | VI       |                   | 10         | 20              | m vv<br>m A    |

|                 | Power-Down Dissipation                                     | Full          | VI       |                   | 20         | 40              | mW             |

| THERMAL         | Operating Ambient Temperature                              | 1 011         | IV       | 0                 | 20         | 70              | °C             |

| CHARACTERISTICS | θ JC Junction-to-Case<br>Thermal Resistance                | 25° C         | V        | Ŭ                 | 4          |                 | ° C/W          |

|                 | θ JA Junction-to-Ambient<br>Thermal Resistance             | 25° C         | V        |                   | 37         |                 | ° C/W          |

|                 | i nermai Resistance                                        |               |          |                   |            |                 |                |

\*1 Input Bias Voltage: 0.05V to VD-0.05V \*2 See "Data/Clock Output Test Condition". \*3 THC7984-17: UXGA@60Hz

\*4 Output Load Capacitance per Pin: 15pF

EXPLANATION OF TEST LEVELS

Test Level

I. 100% production tested.

II. 100% production tested at +25° C and sample tested at specified temperatures.

III. Sample tested only.

IV. Parameter is guaranteed by design and characterization testing.

V. Parameter is a typical value only.

VI. 100% production tested at +25° C; guaranteed by design and characterization testing.

Copyright©2013 THine Electronics, Inc.

< Data Setup/Hold Time to Clock >

### **Absolute Maximum Ratings**

| Parameter                    | Min  | Max                | Unit |

|------------------------------|------|--------------------|------|

| VD                           |      | 2.1                | V    |

| VDD                          |      | 3.8                | V    |

| PVD                          |      | 2.1                | V    |

| DAVDD                        |      | 2.1                | V    |

| Analog Inputs                | -0.2 | VD+0.2 or 2.1 *1   | V    |

| Digital Inputs               | -0.3 | PVD+3.6 or 5.5V *1 | V    |

| Storage Temperature          | -55  | 150                | °C   |

| Maximum Junction Temperature |      | 125                | °C   |

\*1 Smaller Value is adopted.

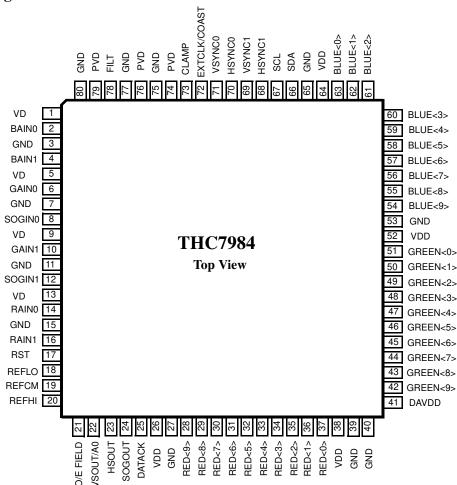

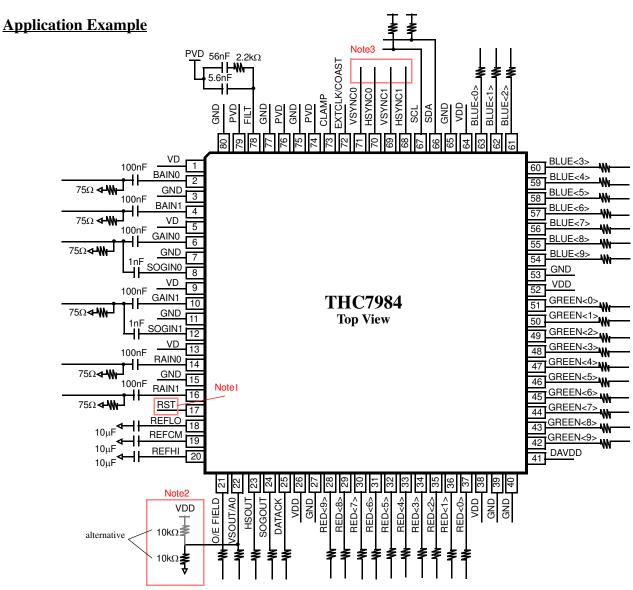

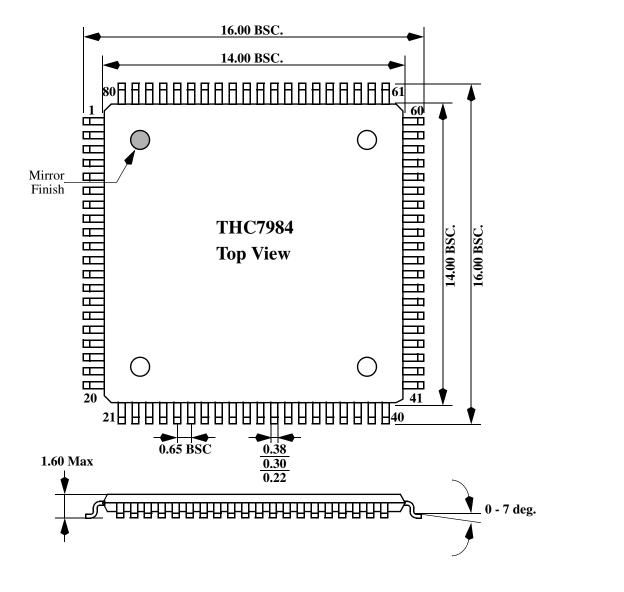

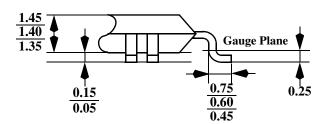

## **Pin Configuration**

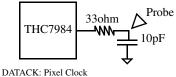

#### < Data /Clock Output Test Condition >

DATACK: PIXel Clock DATACK Phase: 4 Output Format: Normal (not DDR) Output Drive Strength (VDD=3.3V) : Medium

\*DATACK output phase is register programmable.

## Pin List

| Pin Name     | Туре | Function                                                  |

|--------------|------|-----------------------------------------------------------|

| VD           | P    | Analog Power Supply                                       |

| VDD          | P    | Output Power Supply                                       |

| PVD          | P    | PLL Power Supply                                          |

| DAVDD        | P    | Digital Core Power Supply                                 |

| GND          | P    | Ground                                                    |

| BAINO        | ĂI   | B-ch Analog Input, Port 0                                 |

| BAIN1        | AI   | B-ch Analog Input, Port 1                                 |

| GAINO        | AI   | G-ch Analog Input, Port 0                                 |

| SOGINO       | AI   | Sync on Green Input, Port 0                               |

| GAIN1        | AI   | G-ch Analog Input, Port 1                                 |

| SOGIN1       | AI   | Sync on Green Input, Port 1                               |

| RAINO        | AI   | R-ch Analog Input, Port 0                                 |

| RAIN1        | AI   | R-ch Analog Input, Port 1                                 |

| RST          | DI   | Reset Input                                               |

|              | 5.   | Low: Normal Operation                                     |

|              |      | High: Power Down (Stand-by)                               |

|              |      | High -> Low: Chip Reset                                   |

| REFLO        | _    | Connection for External Capacitor                         |

| REFCM        | _    | Connection for External Capacitor                         |

| REFHI        | _    | Connection for External Capacitor                         |

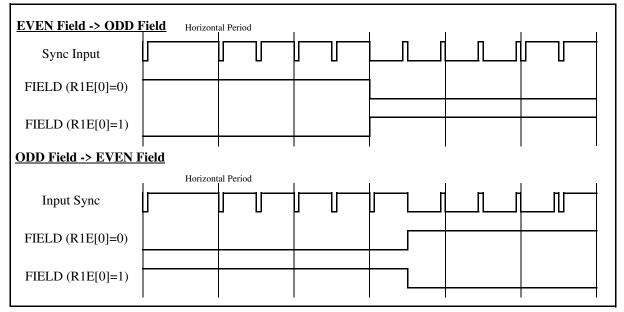

| O/E FIELD    | DO   | Field Parity Output for Interlaced Video                  |

| O/ L TILLD   | 00   | <pre><other function=""></other></pre>                    |

|              |      | Data Enable (DE) Output                                   |

|              |      | Sync Processor IRQ Output                                 |

| VSOUT/A0     | DIO  | VSYNC Output / Serial Interface Device Address bit 0 (A0) |

| HSOUT        | DIO  | HSYNC Output                                              |

| SOGOUT       | DO   | SOG Slicer Output                                         |

| DATACK       | DO   | Data Clock Output                                         |

| RED<9:0>     | DO   | R-ch Data Output                                          |

| GREEN<9:0>   | DO   | G-ch Data Output                                          |

| BLUE<9:0>    | DO   | B-ch Data Output                                          |

| SCL          | DU   | Serial Port Data Clock Input                              |

| SDA          | DIO  | Serial Port Data I/O                                      |

| HSYNC1       | DIO  | HSYNC Input, Port 1                                       |

| VSYNC1       | DI   | VSYNC Input, Port 1                                       |

| HSYNC0       | DI   | HSYNC Input, Port 0                                       |

| VSYNC0       | DI   | VSYNC Input, Port 0                                       |

| EXTCLK/COAST | DI   | External Clock Input / Coast Signal Input                 |

| CLAMP        | DI   | External Clock Input / Coast Signal Input                 |

|              | DI   |                                                           |

|              |      | Reference Clock Input for HSYNC Period Measure            |

| FILT         | _    | Connection for PLL Loop Filter                            |

|              |      | Connection for PLL Loop Filter                            |

P:Power AI:Analog Input DI:Digital Input DO:Digital Output DIO:Digital Input/Output

#### **Digital Input**

- All digital inputs are 5V tolerant during power-on.

#### **Analog Input**

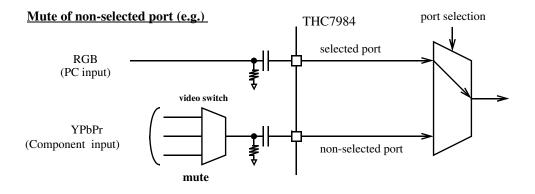

- The THC7984 has two ports that each include three analog inputs for RGB or YPbPr. The input port can be selected by register.

- In case input signals are YPbPr, Y may be input into GAIN0 (or GAIN1) and SOGIN0 (or SOGIN1), Pr into RAIN0 (or RAIN1), and Pb into BAIN0 (or BAIN1).

- The THC7984 accommodates analog signals ranging from 0.5 Vpp to 1.0 Vpp.

#### Video Filter (LPF)

The THC7984 has 2 kinds of low-pass filters.

- 5th-order LPF for YPbPr, whose bandwidth is adjustable from 6 MHz to 92 MHz in 24 steps.

- 2nd-order LPF for RGB, whose bandwidth is adjustable in 4 steps (40 MHz, 90 MHz, 170 MHz, and 310 MHz) .

#### Serial Interface

- The THC7984 is controlled by 2-wire serial interface.

- Serial clock SCL supports up to 100 kHz.

#### Sync Input

- The THC7984 has two ports that each include two digital inputs for the separate sync (HSYNC and VSYNC). The input port can be selected by register.

- The THC7984 can process composite sync (CSYNC) . CSYNC may be input into HSYNC0 or HSYNC1.

#### **Digital Output**

- The digital outputs can operate from 2.5 V to 3.3 V (VDD) .

- The output drive strength is programmable by 2-bit registers (except SDA).

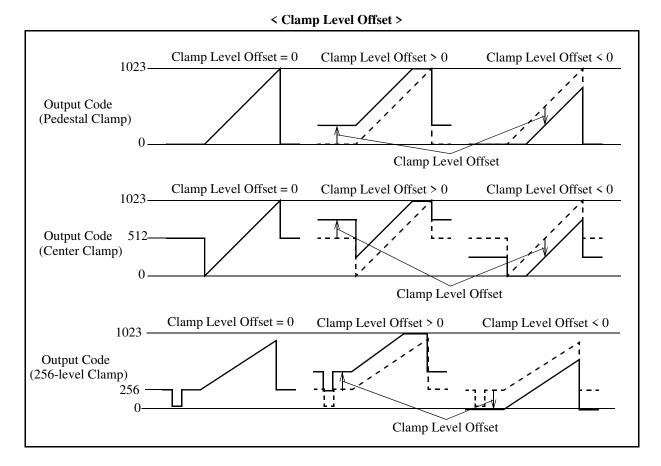

#### Clamp

- Pedestal clamp for RGB and Y (luminance) clamps black level to 0 with automatic offset cancel.

- Midscale clamp for PbPr clamps to 512 with automatic offset cancel.

- 256-level clamp for Y (luminance) clamps to 256 with automatic offset cancel. It can be used for A/D conversion of Y including sync signal. In this case, input signal needs to be attenuated to put it within the input rang of A/D converter.

- Clamp pulses can be input from CLAMP pin when external clamp is selected.

#### Gain, Offset

- Gain is programmable by 11-bit registers (2048 steps) .

- Offset from -256 to +255 can be added to the output code.

- Gain and offset can be adjusted independently.

#### **Reference Voltage**

- The THC7984 has Band Gap Reference inside and doesn't require external voltage reference.

- The internal reference voltages (REFHI, REFCM, and REFLO) must be bypassed to stabilize. Each pin (REFHI, REFCM, and REFLO) is connected to ground through a 10 µF capacitor.

#### Sampling Clock Generation

- The THC7984 has PLL to generate the sampling clock from HSYNC. The sampling clock frequency range is from 10MHz to 170 MHz.

- PLL divider ratio (the number of horizontal total pixels per line) can be set to the value between 200 to 8191.

- The sampling clock Phase can be adjusted in 64 steps of T/64.

- The external clock can be used as the sampling clock.

- It is required to set VCO Frequency Range and Charge Pump Current according to the input signal format (resolution).

#### Oversampling

- Oversampling is the function that enables sampling analog signals with higher rate than the pixel clock and downsampling to the pixel clock rate with decimation filter, which is effective for improving S/N ratio.

- Oversampling ratio can be selected among 1x (normal operation), 2x, 4x, and 8x. Even if any is selected, output frequency of the output clock and data is same as normal operation.

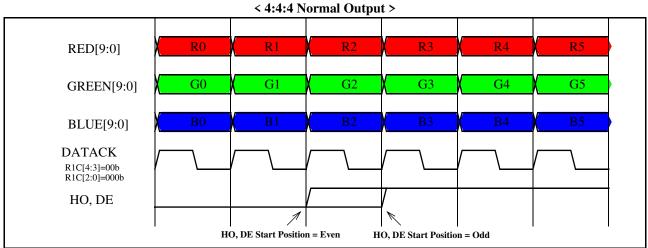

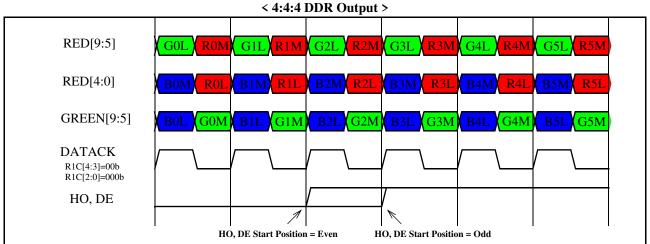

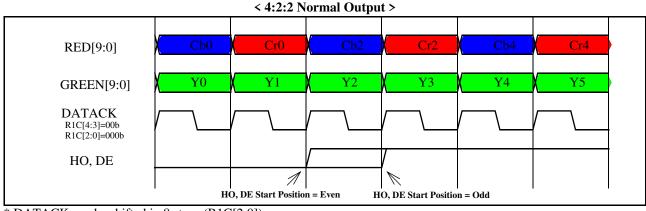

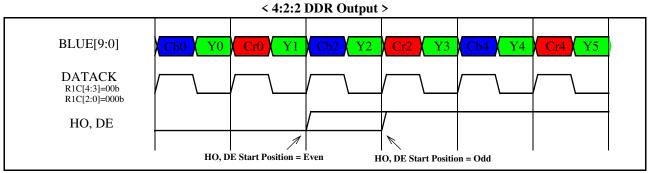

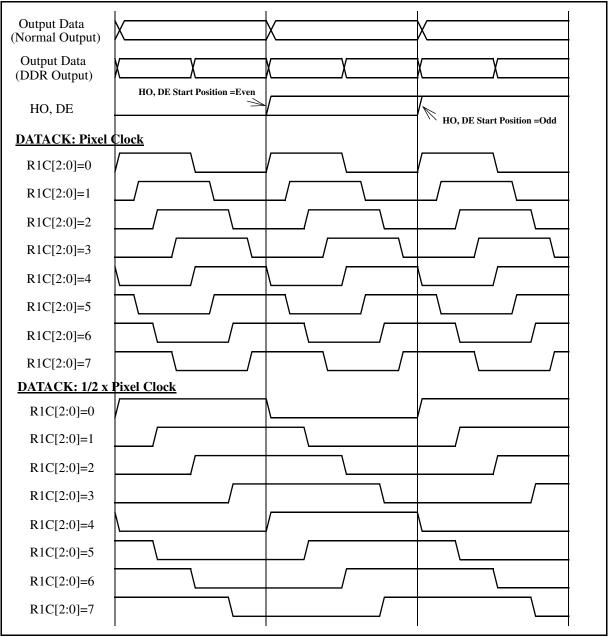

#### Output Clock (DATACK)

- The output clock phase can be selected in 8 steps for the data setup/hold adjustment.

- Divide-by-2 clock can be selected as the output clock for the dual edge data clocking at the subsequent stage. It can not be selected when oversampling.

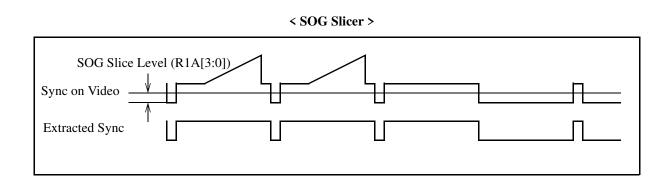

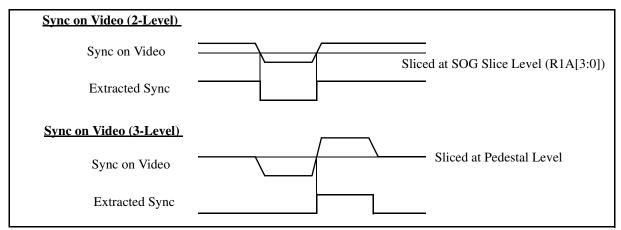

#### SOG Slicer

- Sync on Green (SOG) is sliced at the threshold level above the sync tip to extract the sync signal. The threshold level can be set by a register ranging from 15 mV to 240 mV in steps of 15mV.

- Low pass filer prior to the slicer can be used to reduce high frequency noise, which can be disabled by a register.

- The slicer also has hysteresis (about 30mV), which can be disabled by a register.

- 3-level sync signal can be processed by slicing at the pedestal level.

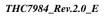

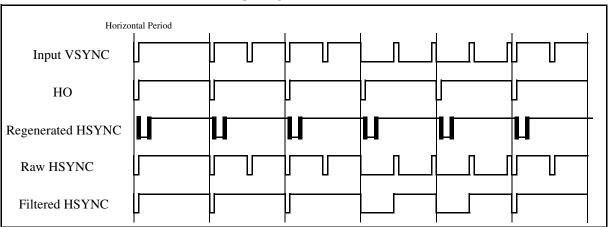

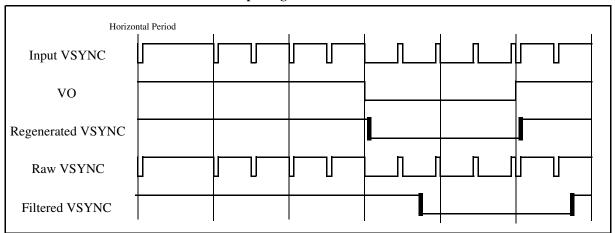

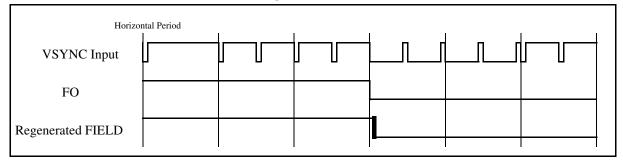

#### Sync Processor

Sync Processor implements VSYNC separation from CSYNC, vertical timing generation, and detection and measurement of the sync signals. The various automatic sync-processing modes are realized by utilizing the sync detection and measurement.

The THC7984 can process the copy protection signal.

(1) VSYNC Separation

Extracting VSYNC from Composite sync (CSYNC) or Sync on Green (SOG).

- (2) Vertical Timing Generation

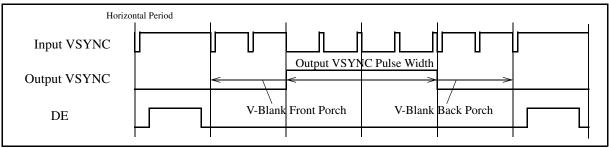

- VSYNC Output Generation

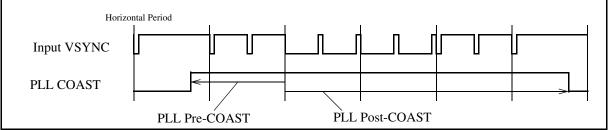

- PLL COAST Generation

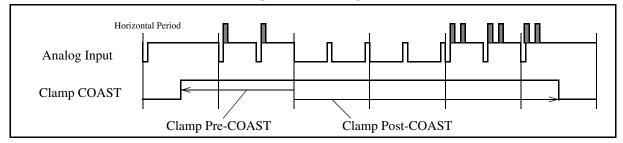

- Clamp COAST Generation

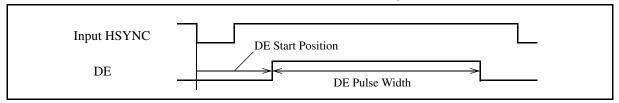

- V-Blank of DE Generation

- (3) Sync Detection/Measurement

- Input Sync Type Detection (Separate sync, Composite sync, Sync on Green, and No input signal)

- HSYNC, VSYNC Input Polarity Detection

- 3-level Sync Detection

- Interlace Detection

- Vertical Total Line Measurement

- VSYNC Input Pulse Width Measurement

- HSYNC Period Measurement (Reference clock needs to be input into CLAMP pin.)

- SYNC Change Detection

- HSYNC Edge Detection

- Sync Processor IRQ Output

(4) Automatic Sync Processing Mode (Manual Setting Modes are also available)

- Auto Output Mode (All outputs are enabled when input signal is active)

- Input Port Auto Select (Selects the port whose input signal is active)

- Input Sync Type Auto Select (HSYNC Input, VSYNC Input)

- HSYNC, VSYNC Input Polarity Auto Select

- HSYNC, VSYNC Output Polarity Auto Select

- VSYNC Output Timing Auto Setting

- PLL COAST Timing Auto Setting

#### **Power Control**

- The THC7984 can be set to stand-by mode by a register or RST-pin.

- In stand-by mode, most of the analog circuits are powered down for low power dissipation.

- In stand-by mode, the sync detection and measurement are available nonetheless because SOG Slicer, Sync Processor, and 2-wire serial interface are still power-on.

- The THC7984 is set to stand-by mode when RST-pin is set to High. If unused, RST-pin must be pull-down to ground with a resistor.

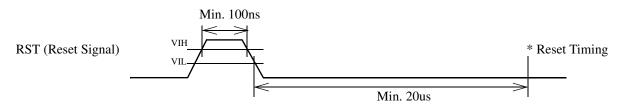

#### Reset

- The logic circuit of the chip is reset when power is applied with RST-pin asserted Low (Power-on Reset) .

- The reset can be also triggered by RST-pin (Manual Reset). The reset is triggered when RST-pin falls from High to Low, that means the reset is triggered whenever the THC7984 gets out of stand-by mode by RST-pin.

- Reset after power-up is necessary to access the serial interface. Please power-up with RST-pin asserted Low or make RST-pin High then Low after power-up. If unused, RST-pin must be pull-down to ground with a resistor.

- The registers are set to the default values by the reset and the chip becomes stand-by mode and output disable (Hi-Z). For normal operation, the registers must be set to power-on and output enable by the serial interface.

- For Manual Reset, keep RST-pin Low more than 20 us after the transition from High to Low.

#### **Device Address**

- The LSB of 7-bit device address of serial interface (A0) is obtained from VSOUT/A0-pin at the reset.

Pull-down to ground with a resistor  $(10 \text{ k}\Omega)$ , then Device Address is set to 1001100 Pull-up to VDD with a resistor  $(10 \text{ k}\Omega)$ , then Device Address is set to 1001101

- The pull-up resistor must be connected to VDD.

## Registers

#### **Register Notation**

The register is notated with "R" added to the head of the address in hexadecimal. e.g. R00: Register of address 0x00 The bit position is notated with "[]". e.g. R04[1:0]: Bit 1 and bit 0 of address 0x04 The register value in hexadecimal is notated with "h" added to the end. e.g. R01=18h The register value in binary is notated with "b" added to the end. e.g. R04[1:0]=11b The register value in decimal is notated without suffix. e.g. R15[7:0]=32

#### **Register Classification**

#### < Register Classification>

| Sign | Category          | Description                                                                                                                                                           | Register                                                                                          |

|------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| R/W  | Read/Write        | Registers for configuration and adjustment                                                                                                                            | except below                                                                                      |

| R    | Read Only         | Registers which report the result of measurement and detection                                                                                                        | R00, R2C~R30, R32~R34                                                                             |

| A    | Auto              |                                                                                                                                                                       | R12[3], R12[1:0], R13[5],<br>R13[4], R13[2], R13[1],<br>R20[6:0], R21[5:0],<br>R22[6:0], R23[6:0] |

| EVRC | Event<br>Recorder | Registers which record the event that has occurred in Sync<br>Processor.<br>- 1 is set when the event occurs.<br>- The value is cleared by writing 1 to the register. | R35                                                                                               |

#### **Default Value**

All registers are set to the default values by the reset (Power-on Reset, Manual Reset) .

#### Minus Number Setting

Some registers can be configured by two's complement.

#### < Minus Number Setting >

| Function                    | Register                  | Range        |

|-----------------------------|---------------------------|--------------|

| Clamp Level Offset          | R0C/R0D, R0E/R0F, R10/R11 | -256 to +255 |

| HSYNC Output Start Position | R14                       | -128 to +127 |

| VSYNC Output Start Position | R20                       | -64 to +63   |

## **Register Map**

| Address | Bit | R/W        | Default    | Function                                                                   | Description                                                    |

|---------|-----|------------|------------|----------------------------------------------------------------------------|----------------------------------------------------------------|

| R 00    | 7   | R          | Value<br>0 |                                                                            | Can be read 21h                                                |

| R 00    |     |            |            | Revision Code                                                              | Can be read 21h                                                |

|         | 6   | R          | 0          |                                                                            |                                                                |

|         | 5   | R          | 1          |                                                                            |                                                                |

|         | 4   | R          | 0          |                                                                            |                                                                |

|         | 3   | R          | 0          |                                                                            |                                                                |

|         | 2   | R          | 0          |                                                                            |                                                                |

|         | 1   | R          | 0          |                                                                            |                                                                |

|         | 0   | R          | 1          |                                                                            |                                                                |

| R 01    | 7   |            |            |                                                                            |                                                                |

|         | 6   |            |            |                                                                            |                                                                |

|         | 5   | D /M       | 0          |                                                                            |                                                                |

|         | 4   | R/W        | 0          | Chip Power-On                                                              | 0: Power-Down (Stand-by Mode) 1: Power-On (Normal Operation)   |

|         | 3   | R/W        |            | Auto Output Enable (All outputs become Enable when input signal is active) | 0: Disable 1: Enable                                           |

|         | 2   | R/W        |            | Output Enable (Except SOGOUT & IRQ)                                        | 0: Disable 1: Enable                                           |

|         | 1   | R/W        | 0          | SOGOUT Output Enable                                                       | 0: Disable 1: Enable                                           |

|         |     | R/W        | 0          | Reserved                                                                   | Must be set to 0 (Default Value)                               |

| R 02    | 7   | D (M)      |            |                                                                            |                                                                |

|         | 6   | R/W        | 0          | Oversampling                                                               | 00b: 1x(Normal Operation) 01b: 2x 10b: 4x 11b: 8x              |

|         | 5   | R/W        | 0          | DU Di dan Data                                                             | Catality much as of the invested to be independent on the      |

|         | 4   | R/W        |            | PLL Divider Ratio                                                          | Set the number of horizontal total pixels per line             |

|         | 3   | R/W        | 0          |                                                                            |                                                                |

|         | 2   | R/W        | 1          |                                                                            |                                                                |

|         | 1   | R/W        | 1          |                                                                            |                                                                |

|         |     | R/W        | 0          |                                                                            |                                                                |

| R 03    | 7   | R/W        | 1          |                                                                            |                                                                |

|         |     | R/W        | 0          |                                                                            |                                                                |

|         | 5   | R/W        | 0          |                                                                            |                                                                |

|         | 4   | R/W        | 1          |                                                                            |                                                                |

|         | 3   | R/W        | 1          |                                                                            |                                                                |

|         | 2   | R/W        | 0          |                                                                            |                                                                |

|         | 1   | R/W        | 0          |                                                                            |                                                                |

|         |     | R/W        | 0          |                                                                            |                                                                |

| R 04    | 7   | R/W        | 1          | Reserved                                                                   | Must be set to 1 (Default Value)                               |

|         |     | R/W        | 1          | VCO Frequency Range                                                        | 00b: 1/8 01b: 1/4 10b: 1/2 11b: 1/1                            |

|         | 5   | R/W        | 1          |                                                                            |                                                                |

|         | 4   | R/W        |            | Charge Pump Current                                                        | 000b: 50uA 001b: 100uA 010b: 150uA 011b: 250uA                 |

|         | 3   | R/W        | 0          |                                                                            | 100b: 350uA 101b: 500uA 110b: 750uA 111b: 1000uA               |

|         | 2   | R/W        | 0          |                                                                            | 00h tatana liQuadi 01h Daaraa d                                |

|         | 1   | R/W        | 0          | Sampling Clock Source                                                      | 00b: Internal Clock 01b: Reserved                              |

| D 05    |     | R/W        | 0          |                                                                            | 10b: External Clock (10–20MHz) 11b: External Clock (20–170MHz) |

| R 05    | 7   |            |            |                                                                            |                                                                |

|         | 6   | D/W/       | 0          | Samalian Clask Dhase                                                       | Set in 64 store of T/64                                        |

|         |     | R/W        | 0          | Sampling Clock Phase                                                       | Set in 64 steps of T/64                                        |

|         |     | R/W        | 0          |                                                                            | *Bigger values mean more delay.                                |

|         | 3   | R/W        | 0          |                                                                            |                                                                |

|         | 2   | R/W        | 0          |                                                                            |                                                                |

|         | 1   | R/W        | 0          |                                                                            |                                                                |

| D 00    |     | R/W        | U          |                                                                            |                                                                |

| R 06    | 7   |            |            |                                                                            |                                                                |

|         | 6   |            |            |                                                                            |                                                                |

|         | 5   |            |            |                                                                            |                                                                |

|         |     |            |            |                                                                            |                                                                |

|         | 3   | R/W        | 1          | R-ch Gain                                                                  | Gain = (Register Value + 1024) / 2048                          |

|         | 2   |            |            |                                                                            |                                                                |

|         | 1   | R/W<br>R/W | 0          |                                                                            | 2048 steps from x0.5 to x1.5                                   |

| D 07    |     |            |            |                                                                            | *Bigger values mean higher gain.                               |

| R 07    | 7   | R/W        | 0          |                                                                            |                                                                |

|         | 6   | R/W        | 0          |                                                                            |                                                                |

|         | 5   | R/W        | 0          |                                                                            |                                                                |

|         | 4   | R/W        | 0          |                                                                            |                                                                |

|         | 3   | R/W        | 0          |                                                                            |                                                                |

|         | 2   | R/W        | 0          |                                                                            |                                                                |

|         | 1   | R/W        | 0          |                                                                            |                                                                |

|         |     | R/W        | 0          |                                                                            |                                                                |

| R 08   | 7       |                          |                                                      |

|--------|---------|--------------------------|------------------------------------------------------|

|        | 6       |                          |                                                      |

|        |         |                          |                                                      |

|        | 5       |                          |                                                      |

|        | 4       |                          |                                                      |

|        | 3       |                          |                                                      |

|        |         | G−ch Gain                | Gain = (Register Value + 1024) / 2048                |

|        |         | d-cri dain               |                                                      |

|        | 1 R/W 0 |                          | 2048 steps from x0.5 to x1.5                         |

|        | 0 R/W 0 |                          | *Bigger values mean higher gain.                     |

| R 09   | 7 R/W 0 |                          |                                                      |

|        | 6 R/W 0 |                          |                                                      |

|        |         |                          |                                                      |

|        | 5 R/W 0 |                          |                                                      |

|        | 4 R/W 0 |                          |                                                      |

|        | 3 R/W 0 |                          |                                                      |

|        | 2 R/W 0 |                          |                                                      |

|        |         |                          |                                                      |

|        | 1 R/W 0 |                          |                                                      |

|        | 0 R/W 0 |                          |                                                      |

| R 0A   | 7       |                          |                                                      |

| 11.071 |         |                          |                                                      |

| 1      | 6       |                          |                                                      |

| 1      | 5       |                          |                                                      |

|        | 4       |                          |                                                      |

|        | 3       |                          |                                                      |

|        |         |                          | $O_{\text{ris}} = (D_{\text{ris}} + 1004) / (2040)$  |

|        |         | B−ch Gain                | Gain = (Register Value + 1024) / 2048                |

|        | 1 R/W 0 |                          | 2048 steps from x0.5 to x1.5                         |

|        | 0 R/W 0 |                          | *Bigger values mean higher gain.                     |

| R 0B   | 7 R/W 0 |                          |                                                      |

| RUD    |         |                          |                                                      |

|        | 6 R/W 0 |                          |                                                      |

|        | 5 R/W 0 |                          |                                                      |

|        | 4 R/W 0 |                          |                                                      |

|        |         |                          |                                                      |

|        |         |                          |                                                      |

|        | 2 R/W 0 |                          |                                                      |

|        | 1 R/W 0 |                          |                                                      |

|        | 0 R/W 0 |                          |                                                      |

|        |         |                          |                                                      |

| R 0C   | 7       |                          |                                                      |

|        | 6       |                          |                                                      |

|        | 5       |                          |                                                      |

|        | 4       |                          |                                                      |

|        |         |                          |                                                      |

|        | 3       |                          |                                                      |

|        | 2       |                          |                                                      |

|        | 1       |                          |                                                      |

|        |         | R-ch Clamp Level Offset  | 1 LSB of offset corresponds to 1 LSB of output code. |

|        |         | R-ch Clamp Level Onset   |                                                      |

| R 0D   | 7 R/W 0 |                          | -256 to +255                                         |

|        | 6 R/W 0 |                          | *Set in two's complement.                            |

|        | 5 R/W 0 |                          |                                                      |

|        | 4 R/W 0 |                          |                                                      |

|        |         |                          |                                                      |

| 1      | 3 R/W 0 |                          |                                                      |

|        | 2 R/W 0 |                          |                                                      |

|        | 1 R/W 0 |                          |                                                      |

| 1      | 0 R/W 0 | 1                        |                                                      |

| D 05   |         |                          |                                                      |

| R 0E   | 7       |                          |                                                      |

|        | 6       |                          |                                                      |

|        | 5       |                          |                                                      |

|        | 4       |                          |                                                      |

| 1      |         |                          |                                                      |

| 1      | 3       |                          |                                                      |

|        | 2       |                          |                                                      |

| 1      | 1       |                          |                                                      |

|        |         | 0. sh 0lann Lauri Offert | 11 CD of effect commenced to 11 CD of the time       |

|        | 0 R/W 0 | G-ch Clamp Level Offset  | 1 LSB of offset corresponds to 1 LSB of output code. |

| R 0F   | 7 R/W 0 |                          | -256 to +255                                         |

|        | 6 R/W 0 |                          | *Set in two's complement.                            |

|        | 5 R/W 0 | 1                        | ,                                                    |

| 1      |         | 4                        |                                                      |

|        | 4 R/W 0 |                          |                                                      |

| 1      | 3 R/W 0 |                          |                                                      |

|        | 2 R/W 0 | 1                        |                                                      |

|        |         |                          |                                                      |

|        | 1 R/W 0 | 1                        | 1                                                    |

|        |         |                          |                                                      |

|        | 0 R/W 0 |                          |                                                      |

| R 10        | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| R 11        | 0 R/W 0<br>7 R/W 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | B-ch Clamp Level Offset                                                                                                                                                                                                                                                                             | 1 LSB of offset corresponds to 1 LSB of output code.<br>-256 to +255                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RII         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             | 6 R/W 0<br>5 R/W 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                                                                                                                                                                                                                                                                                   | *Set in two's complement.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             | 3 R/W 0<br>2 R/W 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |