# 28 V / 5 A Rated OVP with Low On-resistance and Integrated TVS

# **FPF3381**

# Description

FPF3381UCX is an OVP with integrated ultra-low on-resistance single channel switch. The device contains an N-MOSFET that can operate over an input voltage range of 2.8 V to 23 V and can support a maximum continuous current of 5 A.

When the input voltage exceeds the over-voltage threshold, the internal FET is turned off immediately to prevent damage to the protected downstream components.

The device has integrated  $\pm 110~V$  surge protection TVS base on IEC61000-4-5 standards.

FPF3381 is available in a small 12-bumps WLCSP package and operate over the free-air temperature range of -40°C to +85°C.

# **Features**

- Over-voltage Protection Up to +28 V

- Integrated TVS: ±110 V for IEC61000-4-5

- Internal Low RDS(on) NMOS Transistors: Typical 15 m $\Omega$

- Programmable Over-voltage Lockout (OVLO)

- Externally Adjustable via OVLO Pin

- Active-low Enable Pin (OVLO) for Device

- Super-fast OVLO Response Time: Typical 40 ns

- Over Temperature Protection (Thermal Shutdown)

- Robust ESD Performance

- ±4 kV Human Body Model (HBM)

- ±2 kV Charged Device Model (CDM)

- System Level ESD (IEC61000-4-2)

- ◆ ±10 kV Contact Discharge

- ±15 kV Air Gap Discharge

# **Typical Applications**

- Mobile Phones

- PDAs

- GPS

# ON Semiconductor®

www.onsemi.com

WLCSP-12 CASE 567WP

# **MARKING DIAGRAM**

3RZZ YWA

3R = Specific Device Code ZZ = Assembly Lot Code

Y = Year

W = Work Week

A = Assembly Location

(Note: Microdot may be in either location)

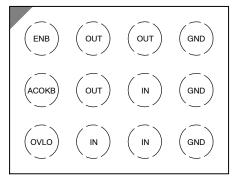

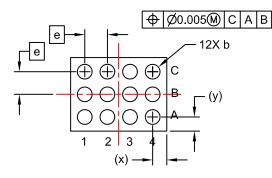

# **PIN ASSIGNMENT**

(Top View)

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 2 of this data sheet.

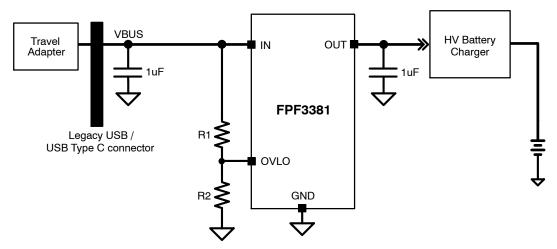

Figure 1. Application Schematic – Adjustable Option

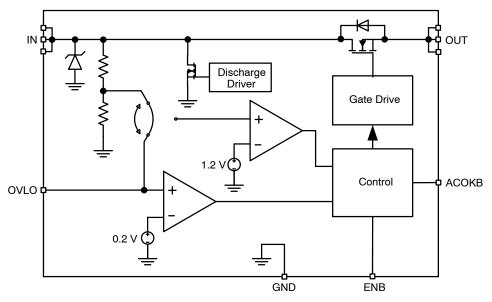

Figure 2. Simplified Block Diagram

# PIN FUNCTION DESCRIPTION

| Pin #      | Name  | Description                                                                                          |

|------------|-------|------------------------------------------------------------------------------------------------------|

| B3, C2, C3 | IN    | Power Input: Switch Input and Device Supply                                                          |

| A2, A3, B2 | OUT   | Power Output: Switch Output to Load                                                                  |

| A1         | ENB   | Enable Input: Active Low. 0: Switch enabled. 1: Switch disabled. 1 MΩ Pull-down resistor integrated. |

| B1         | ACOKB | Power Good Acknowledge Output: Open-drain output to indicate Power Good condition                    |

| C1         | OVLO  | OVLO Input: Over Voltage Lockout Adjustment Input                                                    |

| A4, B4, C4 | GND   | Ground                                                                                               |

# ORDERING INFORMATION

| Device     | Marking | Package   | Shipping <sup>†</sup> |

|------------|---------|-----------|-----------------------|

| FPF3381UCX | 3R      | WLCSP-12L | 4000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

**Table 1. MAXIMUM RATINGS**

| Rating                                                                         | Symbol              | Value                           | Unit |

|--------------------------------------------------------------------------------|---------------------|---------------------------------|------|

| Input Voltage Range (Note 1)                                                   | V <sub>in</sub>     | -0.3 to +28                     | V    |

| Output Voltage Range                                                           | V <sub>out</sub>    | -0.3 to (V <sub>in</sub> + 0.3) | V    |

| Adjustable Input Range                                                         | V <sub>OVLO</sub>   | -0.3 to +24                     | V    |

| Internal FET Continuous Current                                                | I <sub>OUT</sub>    | 0 to 6.25                       | Α    |

| Internal FET Peak Current (pulse width no longer than 100 μs)                  | I <sub>PEAK</sub>   | 7                               | Α    |

| Maximum Junction Temperature                                                   | T <sub>J(max)</sub> | 150                             | °C   |

| Storage Temperature Range                                                      | T <sub>STG</sub>    | -65 to 150                      | °C   |

| ESD Capability, Human Body Model (Note 2)                                      | ESD <sub>HBM</sub>  | 4                               | kV   |

| ESD Capability, Charged Device Model (Note 2)                                  | ESD <sub>CDM</sub>  | 2                               |      |

| IEC 61000-4-2 SYSTEM Level ESD                                                 | Contact             | 10                              |      |

|                                                                                | Air Gap             | 15                              |      |

| Lead Temperature Soldering Reflow (SMD Styles Only), Pb-Free Versions (Note 3) | T <sub>SLD</sub>    | 260                             | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Refer to <u>ELECTRICAL CHARACTERISTICS</u>, <u>RECOMMENDED OPERATING RANGES</u> and/or <u>APPLICATION INFORMATION</u> for Safe Operating parameters.

- 2. This device series incorporates ESD protection and is tested by the following methods:

- ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114)

- ESD Charged Device Model tested per AEC-Q100-011 (EIA/JESD22-C101)

- Latch-up Current Maximum Rating: ≤150 mA per JEDEC standard: JESD78

- 3. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### **Table 2. THERMAL CHARACTERISTICS**

| Rating                                                                                  | Symbol          | Value | Unit |

|-----------------------------------------------------------------------------------------|-----------------|-------|------|

| Thermal Characteristics, WLCSP-12 (Note 4) Thermal Resistance, Junction-to-Air (Note 5) | $R_{\theta JA}$ | 84.1  | °C/W |

<sup>4.</sup> Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

# **Table 3. RECOMMENDED OPERATING RANGES**

| Rating                  | Symbol            | Min | Max | Unit |

|-------------------------|-------------------|-----|-----|------|

| Supply Voltage on VIN   | V <sub>in</sub>   | 2.8 | 25  | V    |

| I/O pins                | V <sub>OVLO</sub> | 0   | 5.5 | V    |

| Output Current (Note 6) | I <sub>out</sub>  | 0   | 5   | Α    |

| IN Capacitor            | C <sub>in</sub>   | 0.1 |     | μF   |

| OUT Capacitor           | C <sub>out</sub>  | 0.1 |     | μF   |

| Ambient Temperature     | T <sub>A</sub>    | -40 | 85  | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

6. Life time, under maximum current, > 5 years base on Temperature < 85°C and no longer than 12 hours per day.

<sup>5.</sup> Values based on 2S2P JEDEC std. PCB.

**Table 4. ELECTRICAL CHARACTERISTICS**  $V_{IN}=2.8$  to 23 V,  $C_{IN}=0.1~\mu\text{F}$ ,  $C_{OUT}=0.1~\mu\text{F}$ ,  $T_{A}=-40$  to  $85^{\circ}\text{C}$ ; For typical values  $V_{IN}=5.0~\text{V}$ ,  $I_{IN}\leq3~\text{A}$ ,  $C_{IN}=0.1~\mu\text{F}$ ,  $T_{A}=25^{\circ}\text{C}$ , for min/max values  $T_{A}=-40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$ ; unless otherwise noted.

| Parameter                                                                                       | Test Conditions                                                                                                                                                                | Symbol                                       | Min   | Тур  | Max   | Unit |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------|------|-------|------|

| LEAKAGE AND QUIESCENT CURRENTS                                                                  | 3                                                                                                                                                                              |                                              |       |      |       |      |

| Input Quiescent Current on IN                                                                   | V <sub>IN</sub> = 5 V, V <sub>OVLO</sub> = 0.6 V, V <sub>ENB</sub> = 0 V                                                                                                       | ΙQ                                           |       | 90   |       | μА   |

|                                                                                                 | V <sub>IN</sub> = 23 V, V <sub>OVLO</sub> = 0.6 V, V <sub>ENB</sub> = 0 V                                                                                                      | 1                                            |       | 150  |       |      |

| Supply Current during Over Voltage                                                              | V <sub>IN</sub> = 23 V, V <sub>OVLO</sub> = 1.8 V, V <sub>OUT</sub> = V <sub>ENB</sub> = 0 V                                                                                   | I <sub>IN_Q</sub>                            |       | 150  |       | μΑ   |

| OVLO Input Leakage Current                                                                      | V <sub>OVLO</sub> = V <sub>OVLO_TH</sub>                                                                                                                                       | I <sub>OVLO</sub>                            | -100  |      | 100   | nA   |

| OVER VOLTAGE AND UNDER VOLTAGE                                                                  | LOCKOUT, I/O                                                                                                                                                                   |                                              |       |      |       |      |

| Input Clamping Voltage                                                                          | I <sub>IN</sub> = 10 mA                                                                                                                                                        | $V_{IN\_CLAMP}$                              |       | 32   |       | V    |

|                                                                                                 | I <sub>IN</sub> = 30A (Note 7)                                                                                                                                                 |                                              |       | 37   |       |      |

| Under-Voltage Rising Trip Level for VIN                                                         | V <sub>IN</sub> rising, T <sub>A</sub> = -40 to 85°C                                                                                                                           | $V_{IN\_UV\_R}$                              | 2.4   | 2.55 | 2.7   | V    |

| Under-Voltage Falling Trip Level for VIN                                                        | V <sub>IN</sub> falling, T <sub>A</sub> = -40 to 85°C                                                                                                                          | $V_{IN\_UV\_F}$                              |       | 2.45 |       | V    |

| Default Over-Voltage Trip Level                                                                 | V <sub>IN</sub> rising, V <sub>OVLO</sub> = GND                                                                                                                                | $V_{IN\_OVLO}$                               | 13.5  | 14.0 | 14.5  | V    |

| OVLO Set Threshold                                                                              | V <sub>OVLO</sub> = 1.1 V to 1.3 V, the voltage of OVLO pin to trigger Over Voltage condition                                                                                  | V <sub>OVLO_TH</sub>                         | 1.165 | 1.20 | 1.235 | V    |

| OVLO Threshold Hysteresis                                                                       |                                                                                                                                                                                | V <sub>HYS_OVLO</sub>                        |       | 3    |       | %    |

| OVLO Input Threshold Voltage<br>Voltage Increasing, Logic High<br>Voltage Decreasing, Logic Low | High<br>Low                                                                                                                                                                    | V <sub>IH_OVLO</sub><br>V <sub>IL_OVLO</sub> | 0.2   |      | 0.1   | ٧    |

| ENB Input Threshold Voltage<br>Voltage Increasing, Logic High<br>Voltage Decreasing, Logic Low  | High<br>Low                                                                                                                                                                    | V <sub>IH_ENB</sub><br>V <sub>IL_ENB</sub>   | 0.9   |      | 0.3   | ٧    |

| Output Low Voltage of ACOKB                                                                     | I <sub>ACOKB</sub> = 1 mA, Logic Low Asserted                                                                                                                                  | $V_{OL}$                                     |       |      | 0.4   | V    |

| ACOKB Leakage Current                                                                           | $V_{I/O}$ = 3.3 V, ACOKB De–asserted, $V_{ENB}$ = 0 V                                                                                                                          | I <sub>ACOKB</sub>                           | -0.5  |      | 0.5   | uA   |

| RESISTANCE                                                                                      |                                                                                                                                                                                |                                              |       |      |       |      |

| On-resistance of Power FET                                                                      | V <sub>IN</sub> = 5 V, I <sub>OUT</sub> = 200 mA, T <sub>A</sub> = 25°C                                                                                                        | r <sub>ON</sub>                              |       | 15   | 20    | mΩ   |

|                                                                                                 | V <sub>IN</sub> = 5 V to 23 V, I <sub>OUT</sub> = 0.1 A to 5 A (Note 10)                                                                                                       | ]                                            |       |      | 25    |      |

| Pull-down Resistor on ENB                                                                       |                                                                                                                                                                                |                                              |       | 1    |       | МΩ   |

| Discharge on IN                                                                                 | V <sub>IN</sub> = 5 V, V <sub>ENB</sub> = 1.8 V                                                                                                                                |                                              |       | 800  |       | Ω    |

| TIMING                                                                                          |                                                                                                                                                                                |                                              |       |      |       |      |

| De-bounce Time of Power FET<br>Turned On                                                        | Time from 2.5 V < $V_{IN}$ < $V_{IN\_OVLO}$ to $V_{OUT}$ = 0.1 × $V_{IN}$                                                                                                      | t <sub>SW_DEB</sub>                          |       | 15   |       | ms   |

| Soft-Start Time of Power FET<br>Turned On                                                       | Time from 2.5 V < V <sub>IN</sub> < V <sub>IN</sub> $_{OVLO}$ to V <sub>AOCKB</sub> = 0.2 × V <sub>I/O</sub> with V <sub>I/O</sub> = 1.8 V and R <sub>PU</sub> = 10 k $\Omega$ | t <sub>SS</sub>                              |       | 30   |       | ms   |

| Switch Turn-On Rising Time (Note 10)                                                            | $V_{IN}$ = 5 V, $R_L$ = 100 $\Omega,$ $C_L$ = 22 $\mu F,$ $V_{OUT}$ from 0.1 $\times$ $V_{IN}$ to 0.9 $\times$ $V_{IN}$                                                        | t <sub>R</sub>                               |       | 2    |       | ms   |

| Switch Turn-Off Time (Note 10)                                                                  | $R_L$ = 10 Ω, $C_L$ = 0 μF, time from $V_{IN}$ > $V_{OVLO}$ to $V_{OUT}$ = 0.9 × $V_{IN}$ (Note 11)                                                                            | t <sub>OVP</sub>                             |       | 40   |       | ns   |

|                                                                                                 | time from $V_{ENB} > V_{IH\_ENB}$ to $V_{OUT} = 0.9 \times V_{IN}$                                                                                                             | t <sub>OFF</sub>                             |       |      | 2     | μs   |

| THERMAL SHUTDOWN                                                                                |                                                                                                                                                                                |                                              |       |      |       |      |

| Thermal Shutdown Temperature (Note 10)                                                          |                                                                                                                                                                                | T <sub>SD</sub>                              | _     | 130  | _     | °C   |

| Thermal Shutdown Hysteresis (Note 10)                                                           |                                                                                                                                                                                | T <sub>SH</sub>                              | _     | 20   | -     | °C   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

<sup>7.</sup> The spec is only for surge event. Guaranteed by design and characterization.

<sup>8.</sup> Performance guaranteed over the indicated operating temperature range by design and/or characterization tested at T<sub>J</sub> = T<sub>A</sub> = 25°C. Low duty cycle pulse techniques are used during testing to maintain the junction temperature as close to ambient as possible.

<sup>9.</sup> Refer to the <u>APPLICATION INFORMATION</u> section.

<sup>10.</sup> Values based on design and/or characterization.

<sup>11.</sup> Depends on the capacitance on OVLO pin.

# **FUNCTION DESCRIPTION**

#### General

FPF3381 is an OVP power switch to protect next stage system which is optimized to lower voltage working condition. The device includes ultra-low on-resistance power FET (15 m $\Omega$ ) and internal TVS for surge event protection base on IEC61000-4-5. The super-fast OVP response time is only 40 ns for default OVP condition.

# **Power MOSFET**

The FPF3381 integrates an N–type MOSFET with 15 m $\Omega$  resistance. The power FET can work under 2.8 V ~ 25 V and up to 5 A DC current capability.

# **Power Supply**

The FPF3381 is supplied by IN.

IN will be firstly supplied by OUT when the device is working under USB On-The-Go (OTG) condition.

# **Enable Control**

FPF3381 has an active low enable pin ENB. When ENB pin is connected to a high level, the internal FET will be turned off. When ENB pin is connected to low level, the FET will be turned on as long as  $V_{\rm IN}$  is not higher than Over–Voltage threshold.

# **Under Voltage Lockout**

FPF3381 power switch will be turned off when the voltage on IN is lower than the UVLO threshold  $V_{\rm IN\ UV\ F}$

Whenever VIN voltage ramps up to higher than  $V_{IN\_UV\_R}$ , the power FET will be turned on automatically after  $t_{DEB}$  de-bounce time if there is no OV or OT condition.

# **Over Voltage Lockout**

The power FET will be turned off whenever IN voltage higher than  $V_{IN\_OVLO}$ . The value of  $V_{IN\_OVLO}$  can be set by external resistor ladder or just be default value  $V_{IN\_OVLO}$ .

When  $V_{OVLO}$  is smaller than  $V_{IL\_OVLO}$ ,  $V_{OVLO}$  will be decided by default value. When  $\bar{V}_{OVLO}$  is larger than  $V_{IH\_OVLO}$ , the power switch will be turned off once  $V_{OVLO}$  >  $V_{OVLO\_TH}$ . The external resistor ladder can be decided according to the following equation:

$$V_{IN OVLO} = V_{OVLO TH} \times (1 + R1/R2)$$

(eq. 1)

where R1 and R2 are the resistors in Figure 1.

# **Power OK indicator**

FPF3381 has an Open–Drain output ACOKB. By implement connection to external supply through a resistor, ACOKB can indicate the status on IN (or VBUS). When VIN is between  $V_{IN\_UV\_R}$  and  $V_{IN\_OVLO}$  more than 30 ms, ACOKB will be pulled down to ground. If the input voltage is out of this range, ACOKB will present as a floating node and the voltage will be pulled high by external power supply.

#### **Thermal Shutdown**

When the device is in the switch mode, to protect the device from over temperature, the power switch will be turned off when the junction temperature exceeds  $T_{SD}$ . The switch will be turned on again when temperature drop below  $T_{SD}-T_{SH}$ .

# **APPLICATIONS INFORMATION**

#### Input Decoupling (Cin)

A ceramic or tantalum at least  $0.1\,\mu F$  capacitor is recommended and should be connected close to the FPF338x package. Higher capacitance and lower ESR will improve the overall line and load transient response.

# Output Decoupling (Cout)

The FPF3381 is a stable component and does not require a minimum Equivalent Series Resistance (ESR) for the output capacitor. The minimum output decoupling value is  $0.1~\mu F$  and can be augmented to fulfill stringent load transient requirements.

# **Thermal Considerations**

As power in the FPF3381 increases, it might become necessary to provide some thermal relief. The maximum power dissipation supported by the device is dependent upon board design and layout. Mounting pad configuration on the PCB, the board material, and the ambient temperature affect the rate of junction temperature rise for the part. When the FPF3381 has good thermal conductivity through

the PCB, the junction temperature will be relatively low with high power applications. The maximum dissipation the FPF3381 can handle is given by:

$$P_{D(MAX)} = \frac{\left[T_{J(MAX)} - T_{A}\right]}{R_{A,IA}}$$

(eq. 2)

Since  $T_J$  is not recommended to exceed 125°C, then the FPF3381 soldered on 645 mm<sup>2</sup>, 1 oz copper area, and the ambient temperature ( $T_A$ ) is 25°C. The power dissipated by the FPF3381 can be calculated from the following equations:

$$P_{D} \approx V_{in} \cdot (I_{Q}@I_{out}) + I_{out}^{2} \cdot r_{ON}$$

(eq. 3)

# Hints

$V_{in}$  and  $V_{out}$  printed circuit board traces should be as wide as possible. Place external components, especially the input capacitor and TVS, as close as possible to the FPF3381, and make traces as short as possible.

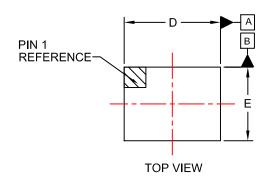

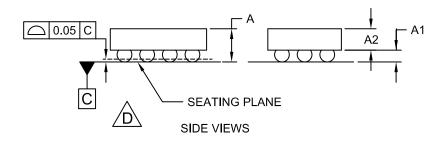

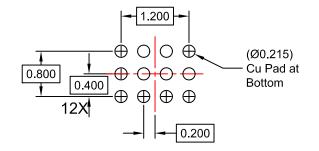

# WLCSP12 1.828x1.288x0.574 CASE 567WP ISSUE O

**DATE 25 JUN 2018**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 2009.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- 3. DATUM C APPLIES TO THE SPHERICAL CROWN OF THE SOLDER BALLS

|     | MILLIMETERS |       |       |  |

|-----|-------------|-------|-------|--|

| DIM | MIN.        | NOM.  | MAX.  |  |

| Α   | 0.536       | 0.574 | 0.612 |  |

| A1  | 0.176       | 0.196 | 0.216 |  |

| A2  | 0.360       | 0.378 | 0.396 |  |

| b   | 0.240       | 0.260 | 0.280 |  |

| D   | 1.798       | 1.828 | 1.858 |  |

| E   | 1.258       | 1.288 | 1.318 |  |

| е   | 0.40 BSC    |       |       |  |

| Х   | 0.299       | 0.314 | 0.329 |  |

| у   | 0.229       | 0.244 | 0.259 |  |

**BOTTOM VIEW**

RECOMMENDED MOUNTING FOOTPRINT (NSMD PAD TYPE)

| DOCUMENT NUMBER: | 98AON93136G               | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | WLCSP12 1.828x1.288x0.574 |                                                                                                                                                                                     | PAGE 1 OF 1 |  |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI., and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems. or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales