# TLE8110ED

Smart Multichannel Low Side Switch with Parallel Control and SPI Interface

# AEC<sup>®</sup> RoHS

1 Overview

## Features

- Overvoltage, Overtemperature, ESD-Protection

- Direct Parallel PWM Control of all Channels

- safeCOMMUNICATION (SPI and Parallel)

- Efficient Communication Mode: compactCONTROL

- Compatible with 3.3V- and 5V- Micro Controllers I/O ports

- clampSAFE for highly efficient parallel use of the channels

- Green Product

- AEC Qualified

# **Potential applications**

• Power Switch Automotive and Industrial Systems switching Solenoids, Relays and Resistive Loads

# **Product validation**

Qualified for Automotive Applications. Product Validation according to AEC-Q100/101.

# Description

10-channel Low-Side Switch in Smart Power Technology [SPT] with **S**erial **P**eripheral Interface [SPI] and 10 open drain DMOS output stages. The TLE8110ED is protected by embedded protection functions and designed for automotive and industrial applications. The output stages are controlled via Parallel Input Pins for PWM use or SPI Interface. The TLE8110ED is particularly suitable for Engine Management and Powertrain Systems.

| Туре      | Package      | Marking   |

|-----------|--------------|-----------|

| TLE8110ED | PG-DSO-36-72 | TLE8110ED |

#### Overview

#### Table 1 Product Summary

| Parameter                                                     | Symbol                     | Value                                                                                                                                                                                                                                 | Unit |

|---------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Analogue Suppy Voltage                                        | V <sub>DD</sub>            | 4.50 5.50                                                                                                                                                                                                                             | V    |

| Digital Supply Voltage                                        | V <sub>cc</sub>            | 3.00 5.50                                                                                                                                                                                                                             | V    |

| Clamping Voltage (CH 1-10)                                    | V <sub>DS(CL)typ</sub>     | 55                                                                                                                                                                                                                                    | V    |

| On Resistance maximum at $T_j = 25^{\circ}$ C and $I_{Dnom}$  | R <sub>ON1-4</sub>         | 0.30                                                                                                                                                                                                                                  | Ω    |

|                                                               | R <sub>ON5-6</sub>         | 0.25                                                                                                                                                                                                                                  | Ω    |

|                                                               | <i>R</i> <sub>ON7-10</sub> | $V_{DD}$ 4.50 5.50 $V_{CC}$ 3.00 5.50 $V_{DS(CL)typ}$ 55 $R_{ON1-4}$ 0.30 $R_{ON5-6}$ 0.25 $R_{ON7-10}$ 0.60 $R_{ON5-6}$ 0.50 $R_{ON5-6}$ 0.50 $R_{ON5-6}$ 0.50 $R_{ON7-10}$ 1.20 $I_{Dnom}$ 1.50 $I_{Dnom}$ 0.75 $I_{DSD(low)}$ 3.70 | Ω    |

| On Resistance maximum at $T_j = 150^{\circ}$ C and $I_{Dnom}$ | R <sub>ON1-4</sub>         | 0.60                                                                                                                                                                                                                                  | Ω    |

|                                                               | R <sub>ON5-6</sub>         | 0.50                                                                                                                                                                                                                                  | Ω    |

|                                                               | <i>R</i> <sub>ON7-10</sub> | 1.20                                                                                                                                                                                                                                  | Ω    |

| Nominal Output current (CH 1-4)                               | I <sub>Dnom</sub>          | 1.50                                                                                                                                                                                                                                  | А    |

| Nominal Output current (CH 5-6)                               | I <sub>Dnom</sub>          | 1.70                                                                                                                                                                                                                                  | А    |

| Nominal Output current (CH 7-10)                              | I <sub>Dnom</sub>          | 0.75                                                                                                                                                                                                                                  | А    |

| Output Current Shut-down Threshold (CH 1-4) min.              | I <sub>DSD(low)</sub>      | 2.60                                                                                                                                                                                                                                  | Α    |

| Output Current Shut-down Threshold (CH 5-6) min.              | I <sub>DSD(low)</sub>      | 3.70                                                                                                                                                                                                                                  | А    |

| Output Current Shut-down Threshold (CH 7-10) min.             | I <sub>DSD(low)</sub>      | 1.70                                                                                                                                                                                                                                  | А    |

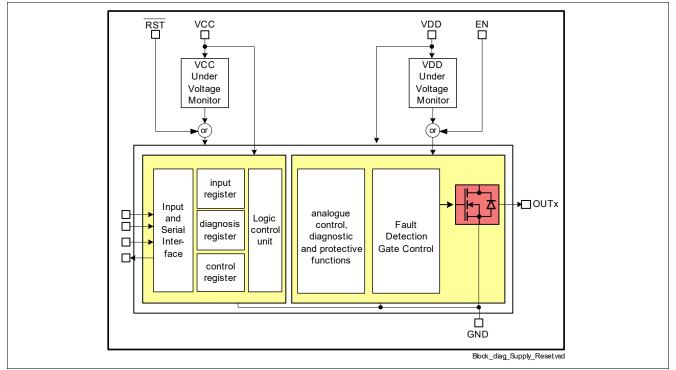

Figure 1 Block Diagram TLE8110ED

# **Table of Contents**

| 1                                                       | Overview                                                                                                                                                   | , 1                  |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 2                                                       | Block Diagram                                                                                                                                              | , 5                  |

| 2.1                                                     | Description                                                                                                                                                | 5                    |

| <b>3</b><br>3.1                                         | Pin Configuration                                                                                                                                          | . 7                  |

| 3.2<br>3.3                                              | Pin Definitions and Functions                                                                                                                              |                      |

|                                                         |                                                                                                                                                            |                      |

| <b>4</b><br>4.1<br>4.2<br>4.3                           | General Product Characteristics         Absolute Maximum Ratings         Functional Range         Thermal Resistance                                       | 10<br>11             |

| <b>5</b><br>5.1<br>5.2                                  | Power SupplyDescription Power SupplyElectrical Characteristics Power Supply                                                                                | 13                   |

| <b>6</b><br>6.1<br>6.2                                  | Reset and Enable InputsDescription Reset and Enable InputsElectrical Characteristics Reset Inputs                                                          | 16                   |

| <b>7</b><br>7.1<br>7.2<br>7.3<br>7.4                    | Power OutputsDescription Power OutputsDescription of the Clamping StructureElectrical Characteristics Power OutputsParallel Connection of the Power Stages | 18<br>19<br>21       |

| <b>8</b><br>8.1<br>8.1.1<br>8.1.2<br>8.2                | Diagnosis<br>Diagnosis Description<br>Open Load diagnosis<br>Overcurrent / Overtemperature diagnosis<br>Electrical Characteristics Diagnosis               | 28<br>28<br>29       |

| <b>9</b><br>9.1<br>9.2                                  | Parallel InputsDescription Parallel InputsElectrical Characteristics Parallel Inputs                                                                       | 33                   |

| <b>10</b><br>10.1                                       | Protection Functions                                                                                                                                       |                      |

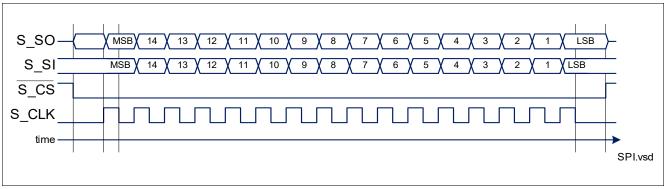

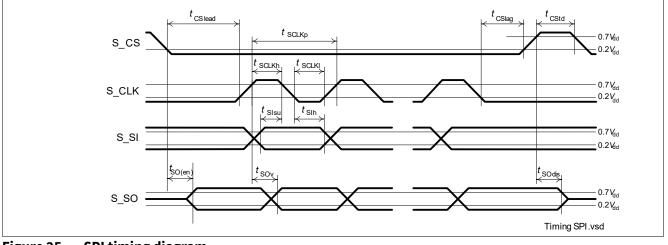

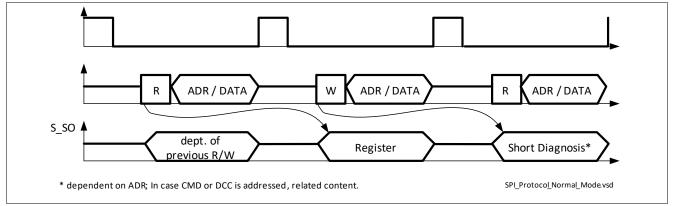

| <b>11</b><br>11.1<br>11.2<br>11.3                       | 16 bit SPI InterfaceDescription 16 bit SPI InterfaceTiming DiagramsElectrical Characteristics 16 bit SPI Interface                                         | 39<br>39             |

| <b>12</b><br>12.1<br>12.2<br>12.2.1<br>12.2.2<br>12.2.2 | Control of the device<br>Internal Clock<br>SPI Interface. Signals and Protocol<br>Description 16 bit SPI Interface Signals<br>Daisy Chain<br>SPI Protocol  | 42<br>42<br>42<br>43 |

| 14       | Revision History                                               | 73 |

|----------|----------------------------------------------------------------|----|

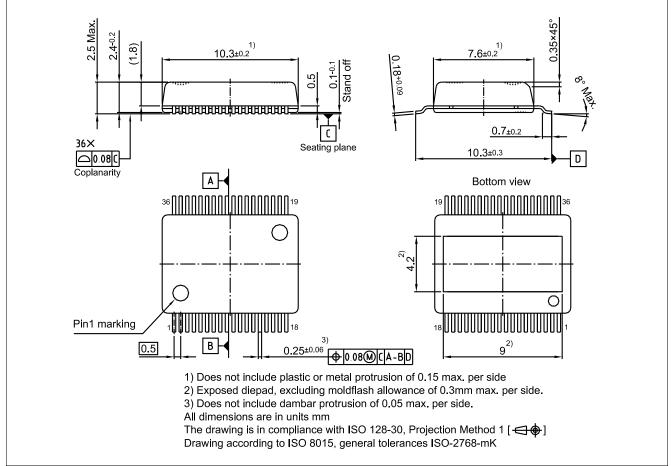

| 13       | Package Outlines                                               | 72 |

| 12.3.6   | DEVS - Device Settings                                         | 71 |

| 12.3.5   | PMx - Parallel Mode Register CHx                               |    |

| 12.3.4   | ISx - INPUT or Serial Mode Control Register, Bank A and Bank B |    |

| 12.3.3   | OUTx - Output Control Register CHx                             | 68 |

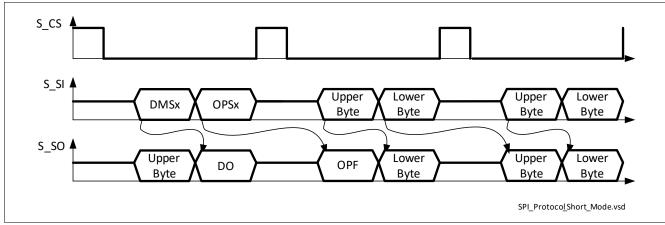

| 12.3.2.3 | DMSx/OPSx - Diagnosis Mode Set / Output Pin Set Commands       |    |

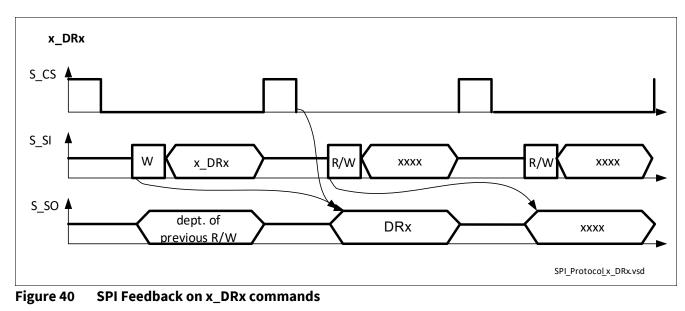

| 12.3.2.2 | DRx - Return on DRx Commands                                   |    |

| 12.3.2.1 | DRx - Diagnosis Registers Contents                             | 63 |

| 12.3.2   | DCC - Diagnosis Registers and compactCONTROL                   | 60 |

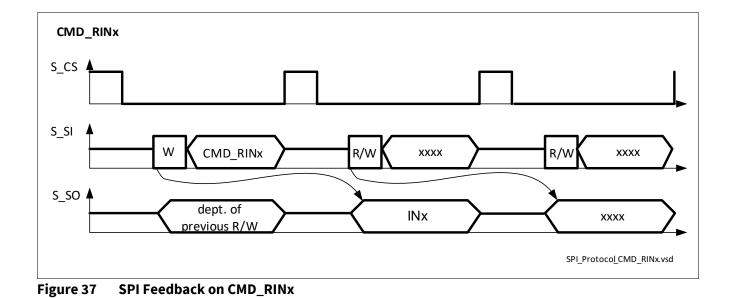

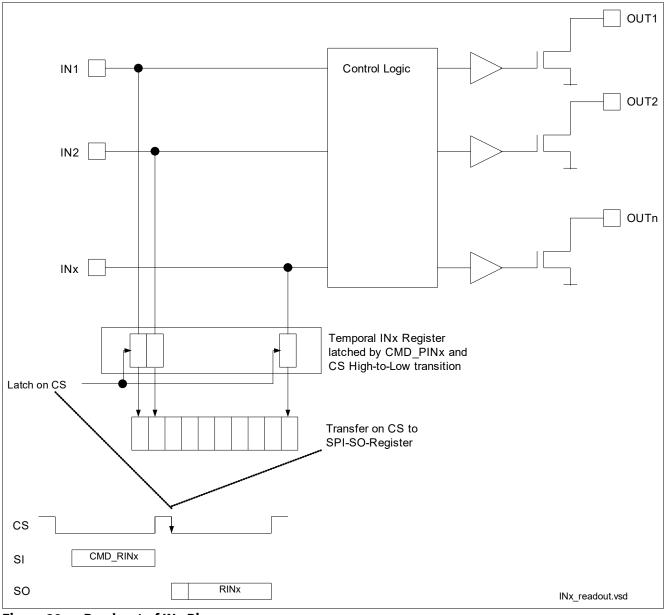

| 12.3.1.4 | CMD_RINx - Command: Return Input Pin (INx) - Status            | 57 |

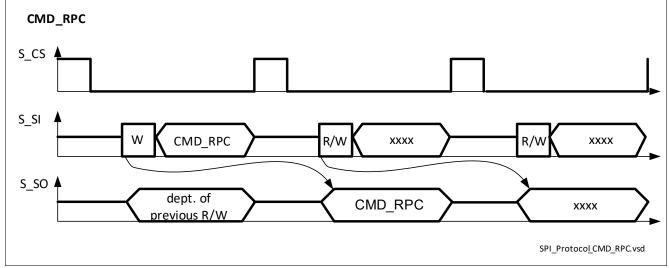

| 12.3.1.3 | CMD_RPC - Command: Return Pattern Check                        | 56 |

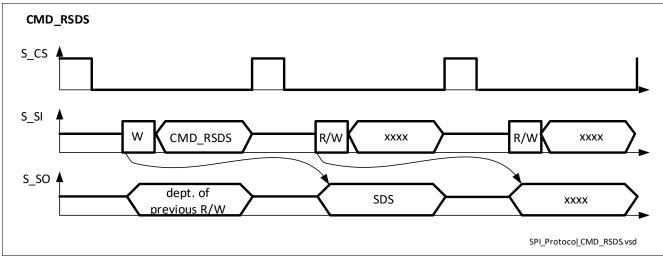

| 12.3.1.2 | CMD_RSDS - Command: Return Short Diagnosis and Device Status   | 54 |

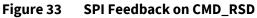

| 12.3.1.1 | CMD_RSD - Command: Return Short Diagnosis                      | 53 |

| 12.3.1   | CMD - Commands                                                 | 52 |

| 12.3     | Register and Command - Overview                                | 49 |

| 12.2.4.2 | Modulo-8 Counter                                               | 48 |

| 12.2.4.1 | Encoding of the commands                                       | 48 |

| 12.2.4   | safeCOMMUNICATION                                              |    |

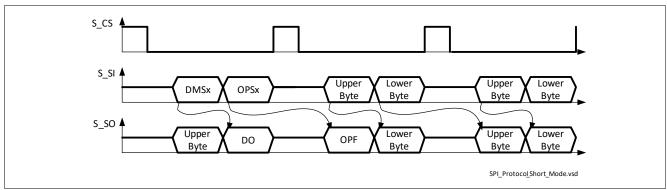

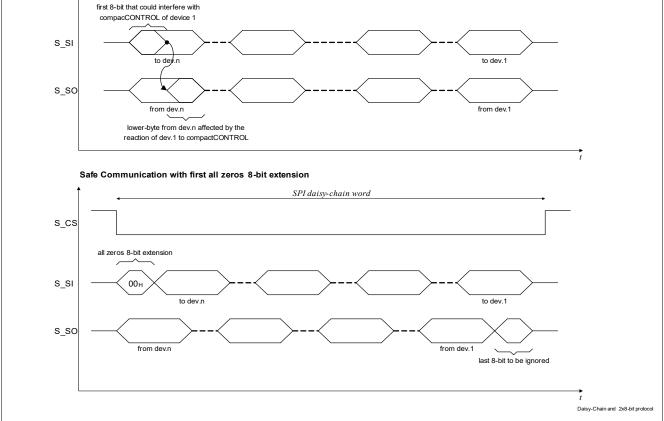

| 12.2.3.4 | Daisy-Chain and 2x8-bit protocol                               |    |

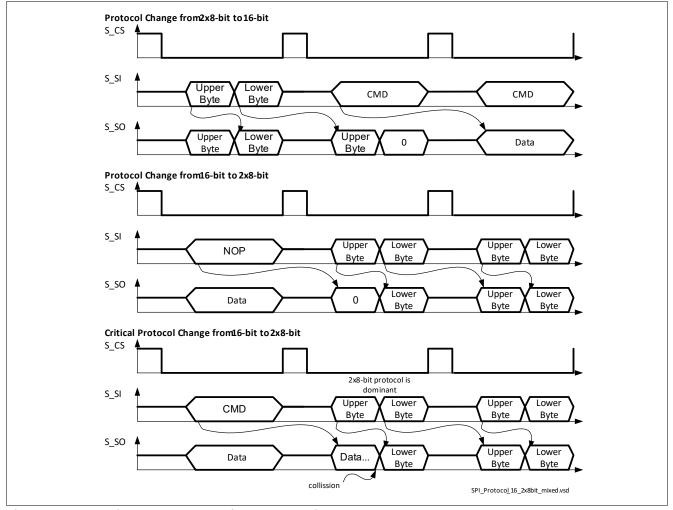

| 12.2.3.3 | 16- and 2x8-bit protocol mixed                                 |    |

| 12.2.3.2 | 2x8-bit protocol                                               | 45 |

| 12.2.3.1 | 16-bit protocol                                                | 43 |

|          |                                                                |    |

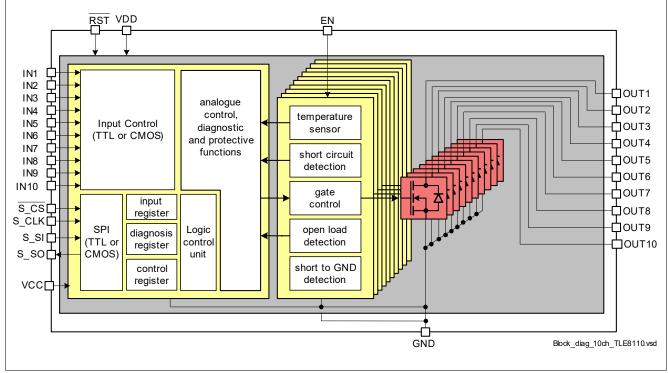

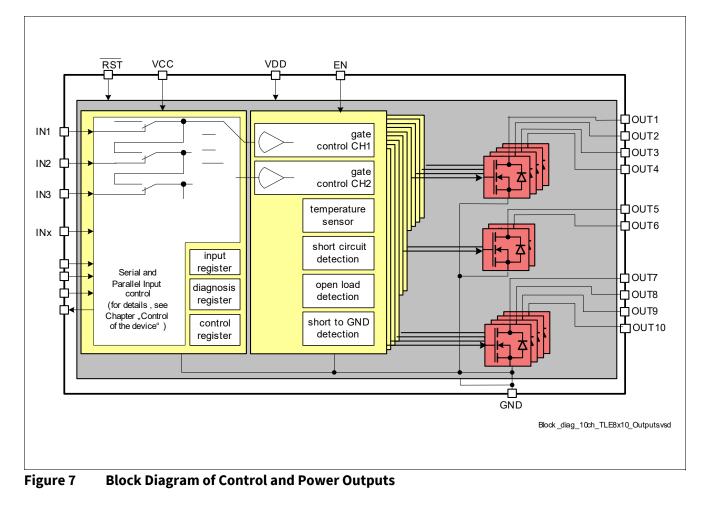

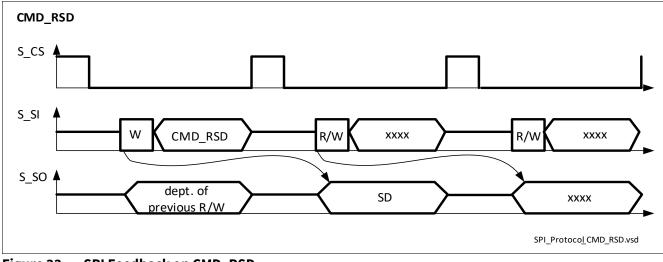

Block Diagram

## 2 Block Diagram

Figure 2 Block Diagram

## 2.1 Description

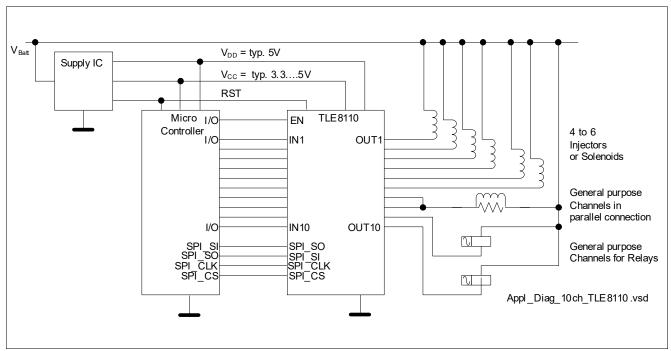

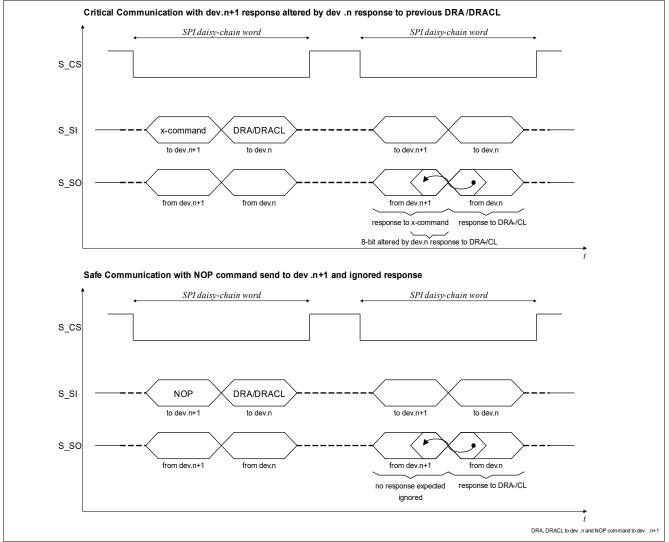

## Communication

The TLE8110ED is a 10-channel low-side switch in PG-DSO-36-72 package providing embedded protection functions. The 16-bit serial peripheral interface (SPI) can be utilized for control and diagnosis of the device and the loads. The SPI interface provides daisy-chain capability in order to assemble multiple devices in one SPI chain by using the same number of micro-controller pins<sup>1)</sup>.

The analogue and the digital part of the device is supplied by 5V. Logic Input and Output Signals are then compatible to 5V logic level [TTL - level]. Optionally, the logic part can be supplied with lower voltages to achieve signal compatibility with e.g. 3.3V logic level [CMOS - level].

The TLE8110ED is equipped with 10 parallel input pins that are routed to each output channel. This allows control of the channels for loads driven by Pulse Width Modulation (PWM). The output channels can also be controlled by SPI.

## Reset

The device is equipped with one Reset Pin and one Enable. Reset [RST] serves the whole device, Enable [EN] serves only the Output Control Unit and the Power Stages.

<sup>1)</sup> Daisy Chain

#### **Block Diagram**

#### Diagnosis

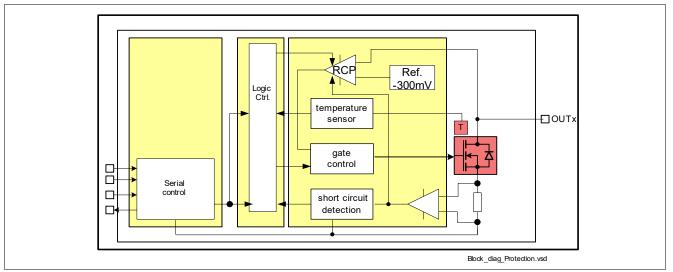

The device provides diagnosis of the load, including open load, short to GND as well as short circuit to VBatt detection and over-load/ over-temperature indication. The SPI diagnosis flags indicates if latched fault conditions may have occurred.

#### Protection

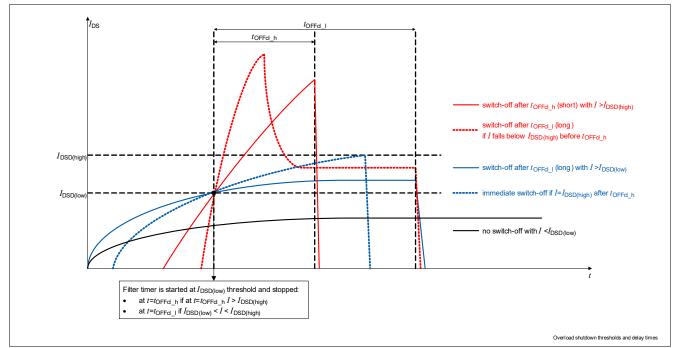

Each output stage is protected against short circuit. In case of over load, the affected channel is switched off. The switching off reaction time is dependent on two switching thresholds. Restart of the channel is done by clearing the Diagnosis Register <sup>1)</sup>. This feature protects the device against uncontrolled repetitive short circuits.

There is a temperature sensor available for each channel to protect the device in case of over temperature. In case of over temperature the affected channel is switched off and the Over-Temperature Flag is set. Restart of the channel is done by deleting the Flag. This feature protects the device against uncontrolled temperature toggling.

#### **Parallel Connection of Channels**

The device is featured with a central clamping structure, so-called CLAMPsafe. This feature ensures a balanced clamping between the channels and allows in case of parallel connection of channels a high efficient usage of the channel capabilities. This parallel mode is additionally featured by best possible parameter- and thermal matching of the channels and by controlling the channels accordingly.

<sup>1)</sup> Restart after Clear

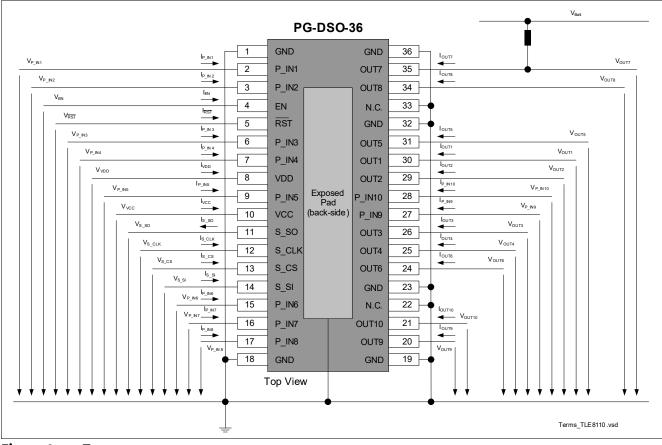

**Pin Configuration**

# 3 Pin Configuration

## 3.1 Pin Assignment

| 1  | GND   |             | GND    | 36 |

|----|-------|-------------|--------|----|

| 2  | P_IN1 |             | OUT7   | 35 |

| 3  | P_IN2 |             | OUT8   | 34 |

| 4  | EN    |             | N.C.   | 33 |

| 5  | RST   |             | GND    | 32 |

| 6  | P_IN3 |             | OUT5   | 31 |

| 7  | P_IN4 |             | OUT1   | 30 |

| 8  | VDD   |             | OUT2   | 29 |

| 9  | P_IN5 | Exposed Pad | P_IN10 | 28 |

| 10 | VCC   | (back-side) | P_IN9  | 27 |

| 11 | S_SO  |             | OUT3   | 26 |

| 12 | S_CLK |             | OUT4   | 25 |

| 13 | s_cs  |             | OUT6   | 24 |

| 14 | S_SI  |             | GND    | 23 |

| 15 | P_IN6 |             | N.C.   | 22 |

| 16 | P_IN7 |             | OUT10  | 21 |

| 17 | P_IN8 |             | OUT9   | 20 |

| 18 | GND   |             | GND    | 19 |

|    |       |             |        |    |

## Figure 3 Pin Configuration

## 3.2 Pin Definitions and Functions

| Pin | Symbol | Function                                                                          |

|-----|--------|-----------------------------------------------------------------------------------|

| 1   | GND    | Ground                                                                            |

| 2   | P_IN1  | Parallel Input Pin 1. Default assignment to Output Channel 1                      |

| 3   | P_IN2  | Parallel Input Pin 2. Default assignment to Output Channel 2                      |

| 4   | EN     | Enable Input Pin. If not needed, connect with Pull-up resistor to VCC             |

| 5   | RST    | Reset Input Pin (active low). If not needed, connect with Pull-up resistor to VCC |

| 6   | P_IN3  | Parallel Input Pin 3. Default assignment to Output Channel 3                      |

| 7   | P_IN4  | Parallel Input Pin 4. Default assignment to Output Channel 4                      |

| 8   | VDD    | Analogue Supply Voltage                                                           |

| 9   | P_IN5  | Parallel Input Pin 5. Default assignment to Output Channel 5                      |

| 10  | VCC    | Digital Supply Voltage                                                            |

| 11  | S_SO   | Serial Peripheral Interface [SPI], Serial Output                                  |

| 12  | S_CLK  | Serial Peripheral Interface [SPI], Clock Input                                    |

| 13  | S_CS   | Serial Peripheral Interface [SPI], Chip Select (active low)                       |

| 14  | S_SI   | Serial Peripheral Interface [SPI], Serial Input                                   |

| 15  | P_IN6  | Parallel Input Pin 6. Default assignment to Output Channel 6                      |

#### **Pin Configuration**

| Pin            | Symbol | Function                                                       |

|----------------|--------|----------------------------------------------------------------|

| 16             | P_IN7  | Parallel Input Pin 7. Default assignment to Output Channel 7   |

| 17             | P_IN8  | Parallel Input Pin 8. Default assignment to Output Channel 8   |

| 18             | GND    | Ground                                                         |

| 19             | GND    | Ground                                                         |

| 20             | OUT9   | Drain of Power Transistor Channel 9                            |

| 21             | OUT10  | Drain of Power Transistor Channel 10                           |

| 22             | N.C.   | internally not connected, connect to Ground                    |

| 23             | GND    | Ground                                                         |

| 24             | OUT6   | Drain of Power Transistor Channel 6                            |

| 25             | OUT4   | Drain of Power Transistor Channel 4                            |

| 26             | OUT3   | Drain of Power Transistor Channel 3                            |

| 27             | P_IN9  | Parallel Input Pin 9. Default assignment to Output Channel 9   |

| 28             | P_IN10 | Parallel Input Pin 10. Default assignment to Output Channel 10 |

| 29             | OUT2   | Drain of Power Transistor Channel 2                            |

| 30             | OUT1   | Drain of Power Transistor Channel 1                            |

| 31             | OUT5   | Drain of Power Transistor Channel 5                            |

| 32             | GND    | Ground                                                         |

| 33             | N.C.   | internally not connected, connect to Ground                    |

| 34             | OUT8   | Drain of Power Transistor Channel 8                            |

| 35             | OUT7   | Drain of Power Transistor Channel 7                            |

| 36             | GND    | Ground                                                         |

| Exposed<br>Pad |        | internally not connected, connect to Ground                    |

*Note:* The exposed pad of TLE8110ED is not connected to ground pins internally. It is highly recommended to connect the exposed pad to GND pins on the PCB.

## **Pin Configuration**

## 3.3 Terms

9

Figure 4 Terms

**General Product Characteristics**

# 4 General Product Characteristics

## 4.1 Absolute Maximum Ratings

## Table 2 Absolute Maximum Ratings <sup>1)</sup>

$T_j$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                              | Symbol           | · ۱                    | /alues | 5                     | Unit | Note or                                  | Number   |

|--------------------------------------------------------|------------------|------------------------|--------|-----------------------|------|------------------------------------------|----------|

|                                                        |                  | Min.                   | Тур.   | Max.                  |      | Test Condition                           |          |

| Supply Voltages                                        |                  |                        |        |                       |      |                                          | ·        |

| Digital Supply voltage                                 | V <sub>cc</sub>  | -0.3                   | -      | 5.5                   | V    | permanent                                | P_4.1.1  |

| Digital Supply voltage                                 | V <sub>cc</sub>  | -0.3                   | -      | 6.2                   | V    | t < 10s                                  | P_4.1.2  |

| Analogue Supply voltage                                | V <sub>DD</sub>  | -0.3                   | -      | 5.5                   | V    | permanent                                | P_4.1.3  |

| Analogue Supply voltage                                | V <sub>DD</sub>  | -0.3                   | -      | 6.2                   | V    | t < 10s                                  | P_4.1.4  |

| Power Stages                                           |                  |                        |        |                       |      |                                          |          |

| Load Current (CH 1 to 10)                              | I <sub>Dn</sub>  | -                      | -      | I <sub>DSD(low)</sub> | А    | -                                        | P_4.1.5  |

| Reverse Current Output (CH 1- 10)                      | I <sub>Dn</sub>  | -I <sub>DSD(low)</sub> | -      | -                     | А    | -                                        | P_4.1.6  |

| Total Ground Current                                   | I <sub>GND</sub> | -20                    | -      | 20                    | А    | -                                        | P_4.1.7  |

| Continuous Drain Source Voltage<br>(Channel 1 to 10)   | V <sub>DSn</sub> | -0.3                   | -      | 45                    | V    | -                                        | P_4.1.8  |

| maximum Voltage for short circuit protection on Output | V <sub>DSn</sub> | -                      | -      | 24                    | V    | one event on one single channel          | P_4.1.9  |

| Clamping Energy - Single Pulse <sup>2) 3</sup>         | 3)               | 1                      |        |                       |      |                                          | I        |

| Single Clamping Energy<br>Channel Group 1-4            | E <sub>AS</sub>  | -                      | -      | 29                    | mJ   | I <sub>D</sub> = 2.6A,<br>1 single pulse | P_4.1.10 |

| Single Clamping Energy<br>Channel Group 5-6            | E <sub>AS</sub>  | -                      | -      | 31                    | mJ   | I <sub>D</sub> = 3.7A,<br>1 single pulse | P_4.1.11 |

| Single Clamping Energy<br>Channel Group 7-10           | E <sub>AS</sub>  | -                      | -      | 11                    | mJ   | I <sub>D</sub> = 1.7A,<br>1 single pulse | P_4.1.12 |

| Logic Pins (SPI, INn, EN, RST)                         |                  |                        | 1      |                       | 1    |                                          |          |

| Input Voltage at all Logic Pin                         | V <sub>x</sub>   | -0.3                   | -      | 5.5                   | V    | permanent                                | P_4.1.13 |

| Input Voltage at all Logic Pin                         | V <sub>x</sub>   | -0.3                   | -      | 6.2                   | V    | t < 10s                                  | P_4.1.14 |

| Input Voltage at Pin 27, 28 (IN9, 10)                  | V <sub>x</sub>   | -0.3                   | -      | 45                    | V    | permanent                                | P_4.1.15 |

| Temperatures                                           |                  |                        |        |                       |      |                                          | I        |

| Junction Temperature                                   | T <sub>j</sub>   | -40                    | -      | 150                   | °C   | -                                        | P_4.1.16 |

| Junction Temperature                                   | T <sub>j</sub>   | -40                    | -      | 175                   | °C   | max. 100hrs<br>cumulative                | P_4.1.17 |

| Storage Temperature                                    | T <sub>stg</sub> | -55                    | -      | 150                   | °C   | _                                        | P_4.1.18 |

| ESD Robustness                                         | <u> </u>         |                        |        |                       |      |                                          |          |

## **General Product Characteristics**

## Table 2Absolute Maximum Ratings 1) (cont'd)

$T_j$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                                        | Symbol           |      | Values | ;    | Unit | Note or                                                 | Number   |

|------------------------------------------------------------------|------------------|------|--------|------|------|---------------------------------------------------------|----------|

|                                                                  |                  | Min. | Тур.   | Max. |      | Test Condition                                          |          |

| Electro Static Discharge Voltage<br>"Human Body Model - HBM"     | V <sub>ESD</sub> | -4   | -      | 4    | kV   | All Pins<br>HBM, <sup>4)</sup><br>1.5KOhm, 100pF        | P_4.1.19 |

| Electro Static Discharge Voltage<br>"Charged Device Model - CDM" | V <sub>ESD</sub> | -500 | -      | 500  | V    | All Pins<br>CDM <sup>5)</sup>                           | P_4.1.20 |

| Electro Static Discharge Voltage<br>"Charged Device Model - CDM" | V <sub>ESD</sub> | -750 | -      | 750  | V    | Pin 1, 18, 19, 36<br>(corner pins)<br>CDM <sup>5)</sup> | P_4.1.21 |

1) Not subject to production test, specified by design.

2) One single channel per time.

3) Triangular Pulse Shape (inductance discharge):  $I_D(t) = I_D(0) \cdot (1 - t / t_{pulse}); 0 < t < t_{pulse}$ .

4) ESD susceptibility, HBM according to EIA/JESD 22-A114-B.

5) ESD susceptibility, Charged Device Model "CDM" EIA/JESD22-C101-C.

1. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

## 4.2 Functional Range

#### Table 3Functional Range

| Parameter               | Symbol               | Values          |              |                 | Unit | Note or Test Condition                                                        | Number  |  |

|-------------------------|----------------------|-----------------|--------------|-----------------|------|-------------------------------------------------------------------------------|---------|--|

|                         |                      | Min.            | n. Typ. Max. |                 |      |                                                                               |         |  |

| Supply Voltages         | I                    | 1               | 1            |                 | 1    | 1                                                                             |         |  |

| Analogue Supply Voltage | V <sub>DD</sub>      | 4.5             | _            | 5.5             | V    | -                                                                             | P_4.2.1 |  |

| Digital Supply Voltage  | V <sub>cc</sub>      | 3               | _            | V <sub>DD</sub> | V    | -                                                                             | P_4.2.2 |  |

| Digital Supply Voltage  | V <sub>cc</sub>      | V <sub>DD</sub> | _            | 5.5             | V    | leakage Currents (ICC) might<br>increase if V <sub>CC</sub> > V <sub>DD</sub> | P_4.2.3 |  |

| Power Stages            | ł                    | 1               | 1            | 1               | 1    |                                                                               |         |  |

| Ground Current          | I <sub>GND_typ</sub> |                 | 9            |                 | А    | resistive loads 1)                                                            | P_4.2.4 |  |

| Temperatures            |                      |                 |              |                 |      |                                                                               |         |  |

| Junction Temperature    | T <sub>j</sub>       | -40             | -            | 150             | °C   | -                                                                             | P_4.2.5 |  |

| Junction Temperature    | T <sub>i</sub>       | -40             | -            | 175             | °C   | for 100hrs <sup>1)</sup>                                                      | P_4.2.6 |  |

1) Not subject to production test, specified by design

*Note:* Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **General Product Characteristics**

*Note:* Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

## 4.3 Thermal Resistance

#### Table 4Thermal Resistance

| Parameter                   | Symbol             | Values |      |      | Unit | Note or                  | Number  |

|-----------------------------|--------------------|--------|------|------|------|--------------------------|---------|

|                             |                    | Min.   | Тур. | Max. |      | Test Condition           |         |

| Junction to Soldering Point | R <sub>thJC</sub>  |        | 1    | 1.50 | K/W  | $P_{vtot} = 3W^{(1)(2)}$ | P_4.3.1 |

| Junction to ambient         | R <sub>th_JA</sub> |        | 21.5 | 22   | K/W  | 3)                       | P_4.3.2 |

1) Not subject to production test, specified by design.

2) Homogenous power distribution over all channels (all power stages equally heated), dependent on cooling set-up.

Specified R<sub>th\_JA</sub>value is according to JEDEC JESD51 -5, -7 at natural convection on FR4 2s2p board; the product (chip and package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70 μm, 2 x 35 μm CU).

Power Supply

## 5 Power Supply

## 5.1 Description Power Supply

The TLE8110ED is supplied by analogue power supply line  $V_{DD}$  which is used for the analogue functions of the device, such as the gate control of the power stages. The digital power supply line  $V_{CC}$  is used to supply the digital part and offers the possibility to adapt the logic level of the serial output pins to lower logic levels.

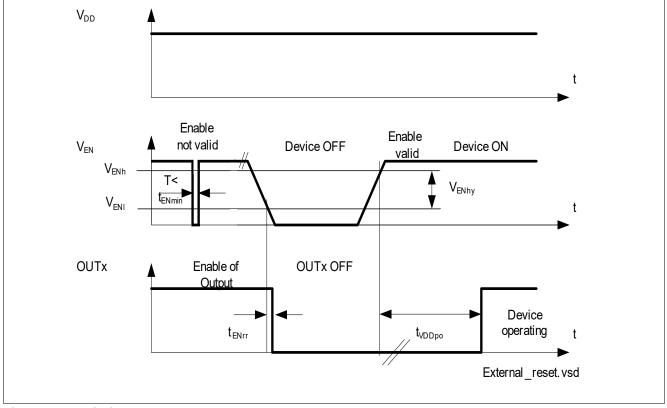

Figure 5 Block Diagram Supply and Reset

## **Description Supply**

The Supply Voltage Pins are monitored during the power-on phase and under normal operating conditions for under voltage.

If during Power-on the increasing supply voltage exceeds the Supply Power-on Switching Threshold, the internal Reset is released after an internal delay has expired.

In case of under voltage, a device internal reset is performed. The Switching Threshold for this case is the Power-on Switching threshold minus the Switching Hysteresis.

In case of under voltage on the analogue supply line  $V_{DD}$  the outputs are turned off but the content of the registers and the functionality of the logic part is kept alive. In case of under voltage on the digital supply  $V_{CC}$  line, a complete reset including the registers is performed.

After returning back to normal supply voltage and an internal delay, the related functional blocks are turned on again. For more details, refer to the chapter "Reset".

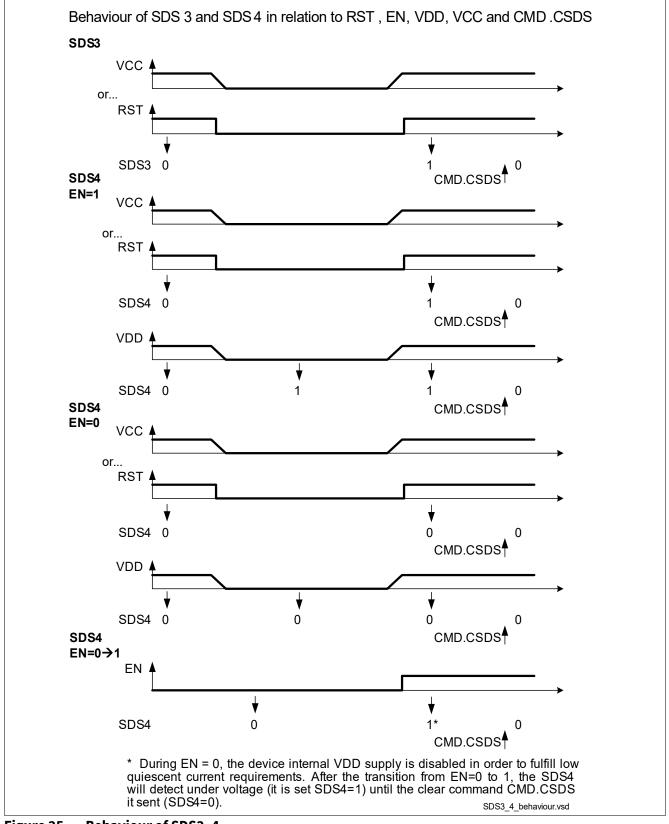

The device internal under-voltage set will set the related bits in SDS (Short Diagnosis and Device Status) to allow the micro controller to detect this reset. For more information, refer to the chapter "Control of the Device".

Infineon

#### **Power Supply**

## 5.2 Electrical Characteristics Power Supply

## Table 5 Electrical Characteristics: Power Supply

$3.0V < V_{CC} < 5.5V$ ;  $4.5V < V_{DD} < 5.5V$ ,  $T_j = -40^{\circ}$ C to +150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                                                     | Symbol             | Values |      |      | Unit | Note or                                                                                                        | Number        |

|-------------------------------------------------------------------------------|--------------------|--------|------|------|------|----------------------------------------------------------------------------------------------------------------|---------------|

|                                                                               |                    | Min.   | Тур. | Max. |      | <b>Test Condition</b>                                                                                          |               |

| Digital Supply and Power-on Reset                                             |                    |        |      |      |      |                                                                                                                | ·             |

| Digital Supply Voltage                                                        | V <sub>cc</sub>    | 3      | -    | 5.5  | V    | -                                                                                                              | P_5.2.1       |

| Digital Supply Current during Reset<br>(V <sub>CC</sub> < V <sub>CCpo</sub> ) | I <sub>CCstb</sub> | -      | 15   | 20   | μΑ   | $f_{SCLK} = 0Hz,$<br>$S_CS = V_{CC},$<br>$T_j = 85^{\circ}C,$<br>$V_{CC} = 2.0 V,$<br>$V_{DD} > V_{CC},$<br>1) | P_5.2.2<br>a) |

|                                                                               |                    | -      | 20   | 40   | μΑ   | $f_{SCLK} = 0Hz,$<br>$S_{CS} = V_{CC},$<br>$Tj = 150^{\circ}C,$<br>$V_{CC} = 2.0V,$<br>$V_{DD} > V_{CC}$       | b)            |

| Digital Supply Current during Reset<br>( <i>V</i> RST > VRSTI)                | I <sub>CCstb</sub> | -      | 2    | 5    | μΑ   | $f_{SCLK} = 0Hz,$<br>$S_CS = V_{CC},$<br>$T_j = 85^{\circ}C,$<br>$V_{DD} > V_{CC},$<br>1)                      | P_5.2.3<br>a) |

|                                                                               |                    | -      | 5    | 15   | μΑ   | $f_{SCLK} = 0Hz,$<br>$S_CS = V_{CC},$<br>$T_j = 150^{\circ}C,$<br>$V_{DD} > V_{CC}$                            | b)            |

| Digital Supply Operating Current<br>V <sub>CC</sub> = 3.3V                    | I <sub>cc</sub>    | -      | 0.15 | 2    | mA   | $f_{SCLK} = 0Hz,$<br>$T_j = 150^{\circ}C,$<br>all Channels ON,<br>1)                                           | P_5.2.4<br>a) |

|                                                                               |                    | -      | 0.5  | 5    | mA   | $f_{SCLK}$ = 5MHz,<br>$T_{j}$ = 150°C,<br>all Channels ON,<br><sup>1) 2)</sup>                                 | b)            |

| Digital Supply Operating Current<br>V <sub>CC</sub> = 5.5V                    | I <sub>cc</sub>    | -      | 0.25 | 2    | mA   | f <sub>SCLK</sub> = 0Hz,<br>T <sub>j</sub> = 150°C,<br>all Channels ON                                         | P_5.2.5<br>a) |

|                                                                               |                    | _      | 0.8  | 10   | mA   | $f_{SCLK} = 5MHz,$<br>$T_j = 150^{\circ}C,$<br>all Channels ON,<br>$\frac{1}{2}$                               | b)            |

| Digital Supply Power-on Switching<br>Threshold                                | V <sub>CCpo</sub>  | 1.9    | 2.8  | 3    | V    | V <sub>cc</sub> increasing                                                                                     | P_5.2.6       |

#### **Power Supply**

#### Table 5 Electrical Characteristics: Power Supply

$3.0V < V_{CC} < 5.5V$ ;  $4.5V < V_{DD} < 5.5V$ ,  $T_j = -40^{\circ}$ C to +150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                                                      | Symbol             |      | Value | S    | Unit | Note or                                                             | Number         |

|--------------------------------------------------------------------------------|--------------------|------|-------|------|------|---------------------------------------------------------------------|----------------|

|                                                                                |                    | Min. | Тур.  | Max. | -    | Test Condition                                                      |                |

| Digital Supply Switching Hysteresis                                            | V <sub>CChy</sub>  | 100  | 300   | 500  | mV   | 1)                                                                  | P_5.2.7        |

| Analogue Supply and Power-on Reset                                             |                    |      |       |      |      |                                                                     |                |

| Analogue Supply Voltage                                                        | V <sub>DD</sub>    | 4.5  | -     | 5.5  | V    | -                                                                   | P_5.2.8        |

| Analogue Supply Current during Reset<br>(V <sub>DD</sub> < V <sub>DDpo</sub> ) | / <sub>DDstb</sub> | _    | 10    | 20   | μA   | $f_{SCLK} = 0Hz,$<br>$T_{j} = 85^{\circ}C,$<br>$V_{DD} = 2V,$<br>1) | P_5.2.9<br>a)  |

|                                                                                |                    | -    | 15    | 40   | μΑ   | $f_{SCLK} = 0Hz,$<br>$T_j = 150^{\circ}C,$<br>$V_{DD} = 2V$         | b)             |

| Analogue Supply Current during Reset<br>( V <sub>EN</sub> < V <sub>ENI</sub> ) | / <sub>DDstb</sub> | -    | 1     | 5    | μA   | $f_{SCLK} = 0Hz,$<br>$T_{j} = 85^{\circ}C,$                         | P_5.2.10<br>a) |

|                                                                                |                    | -    | 2     | 15   | μA   | f <sub>SCLK</sub> = 0Hz,<br>T <sub>j</sub> = 150°C                  | b)             |

| Analogue Supply Operating Current                                              | I <sub>DD</sub>    | -    | 8     | 25   | mA   | $f_{SCLK} = 05MHz,$<br>$T_j = 150^{\circ}C,$<br>all Channels ON,    | P_5.2.11       |

| Analogue Supply Power-on Switching<br>Threshold                                | V <sub>DDpo</sub>  | 3    | 4.2   | 4.5  | V    | V <sub>DD</sub> increasing                                          | P_5.2.12       |

| Analogue Supply Switching Hysteresis                                           | V <sub>DDhy</sub>  | 100  | 200   | 400  | mV   | 1)                                                                  | P_5.2.13       |

| Analogue Supply Power-on Delay Time                                            | t <sub>VDDpo</sub> | -    | 100   | 200  | μs   | $V_{\text{DD}}$ increasing,                                         | P_5.2.14       |

1) Parameter not subject to production test. Specified by design.

2) C = 50 pF connected to S\_SO.

**Reset and Enable Inputs**

# 6 Reset and Enable Inputs

## 6.1 Description Reset and Enable Inputs

The TLE8110ED contains one Reset- and one Enable Input Pin as can be seen in Figure 5.

Description:

Reset Pin [RST] is the main reset and acts as the internal under voltage reset monitoring of the digital supply voltage V<sub>cc</sub>: As soon as RST is pulled low, the whole device including the control registers is reset.

The Enable Pin [EN] resets only the Output channels and the control circuits. The content of the all registers is kept. This functions offers the possibility of a "soft" reset turning off only the Output lines but keeping alive the SPI communication and the contents of the control registers. This allows the read out of the diagnosis and setting up the device during or directly after Reset.

## 6.2 Electrical Characteristics Reset Inputs

## Table 6 Electrical Characteristics: Reset Inputs

$3.0V < V_{CC} < 5.5V$ ;  $4.5V < V_{DD} < 5.5V$ ,  $T_j = -40^{\circ}$ C to +150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                  | Symbol               |                      | Value | s                    | Unit                 | Note or                     | Number   |

|--------------------------------------------|----------------------|----------------------|-------|----------------------|----------------------|-----------------------------|----------|

|                                            |                      | Min.                 | Тур.  | Max.                 |                      | <b>Test Condition</b>       |          |

| Reset Input Pin [RST]                      |                      |                      |       |                      |                      |                             |          |

| Low Level of RST                           | V <sub>RSTI</sub>    | -0.3                 | -     | V <sub>cc</sub> *0.2 | V                    | -                           | P_6.2.1  |

| High Level of RST                          | V <sub>RSTh</sub>    | V <sub>CC</sub> *0.4 | -     | V <sub>cc</sub>      | V                    | -                           | P_6.2.2  |

| RST Switching Hysteresis                   | V <sub>RSThy</sub>   | 20                   | 100   | 300                  | mV                   | 1)                          | P_6.2.3  |

| Reset Pin pull-down Current                | I <sub>RSTresh</sub> | 20                   | 40    | 85                   | μΑ                   | $V_{\overline{RST}} = 5V$   | P_6.2.4  |

|                                            | I <sub>RSTresl</sub> | 2.4                  | -     | -                    | μΑ                   | $V_{RST} = 0.6 V,$          | *        |

| Required Reset Duration time RST           | t <sub>RSTmin</sub>  | 2                    | -     | _                    | μs                   | 1)                          | P_6.2.5  |

| Enable Input Pin [EN]                      |                      | I                    | -1    |                      |                      |                             |          |

| Low Level of EN                            | V <sub>ENI</sub>     | -0.3                 | -     | V *0.2               | V <sub>CC</sub> *0.2 | -                           | P_6.2.6  |

| High Level of EN                           | V <sub>ENh</sub>     | V <sub>CC</sub> *0.4 | -     | VCC                  | V                    | -                           | P_6.2.7  |

| EN Switching Hysteresis                    | V <sub>ENhy</sub>    | 20                   | 60    | 300                  | mV                   | 1)                          | P_6.2.8  |

| Enable Pin pull-down Current               | I <sub>ENresh</sub>  | 5                    | 35    | 85                   | μΑ                   | $V_{\overline{EN}} = 5V$    | P_6.2.9  |

|                                            | I <sub>ENresl</sub>  | 2.4                  | -     | -                    | μΑ                   | $V_{\overline{EN}} = 0.6V,$ | *        |

| Enable Reaction Time<br>(reaction of OUTx) | t <sub>ENrr</sub>    | -                    | 4     | -                    | μs                   | 1)                          | P_6.2.10 |

| Required Enable Duration time EN           | t <sub>ENmin</sub>   | 2                    | -     | -                    | μs                   | 1)                          | P_6.2.11 |

1) Parameter not subject to production test. Specified by design.

#### **Reset and Enable Inputs**

Figure 6 Timing

Power Outputs

## 7 Power Outputs

## 7.1 Description Power Outputs

The TLE8110ED is a 10 channel low-side powertrain switch. The power stages are built by N-channel power MOSFET transistors. The device is a universal multichannel switch but mostly suited for the use in Engine Management Systems [EMS]. Within an EMS, the best fit of the channels to the typical loads is:

- Channel 1 to 4 for Injector valves or mid-sized solenoids with a nominal current requirement of 1.5A,

- Channel 5 to 6 for mid-sized solenoids or Injector valves with nominal current requirement of 1.7A,

- Channel 7 to 10 for small solenoids or relays with a nominal current requirement of 0.75A.

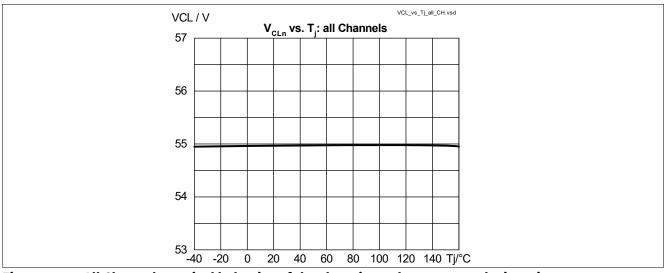

Channel 1 to 10 provide enhanced clamping capabilities of typically 55V best suited for inductive loads such as injectors and valves. It is recommended in case of an inductive load, to connect an external free wheelingor clamping diode, where-ever possible to reduce power dissipation.

All channels can be connected in parallel. Channels 1 to 4, 5 to 6 and 7 to 10 are prepared by matching for parallel connection with the possibility to use a high portion of the capability of each single channel also in parallel mode (refer to **Chapter 7.4**).

Channel 5 and 6 have a higher current shut down threshold to allow to connect in parallel mode a load with high inrush-current, such as a lambda sensor heater.

#### **Power Outputs**

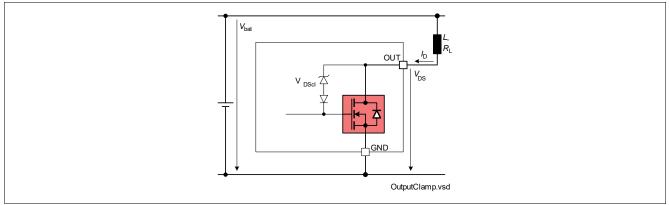

## 7.2 Description of the Clamping Structure

When switching off inductive loads, the potential at pin OUT rises to  $V_{DS(CL)}$  potential, because the inductance intends to continue driving the current. The clamping voltage is necessary to prevent destruction of the device, see **Figure 8** for the clamping circuit principle. Nevertheless, the maximum allowed load inductance is limited.

Figure 8 Internal Clamping Principle

## **Clamping Energy**

During demagnetization of inductive loads, energy has to be dissipated in the device. This energy can be calculated with following equation:

$$E = V_{DS(CL)} \cdot \frac{L_L}{R_L} \cdot \left[ I_L - \frac{V_{DS(CL)} - V_{BAT}}{R_L} \cdot \ln\left(1 + \frac{R_L \cdot I_L}{V_{DS(CL)} - V_{BAT}}\right) \right]$$

(7.1)

The maximum energy, which is converted into heat, is limited by the thermal design of the component.

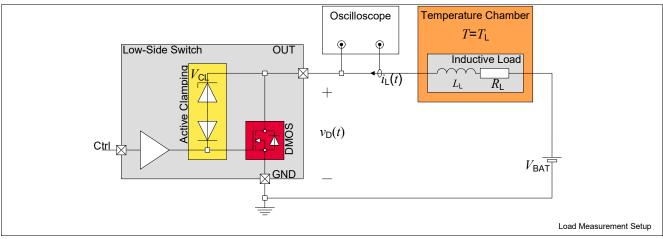

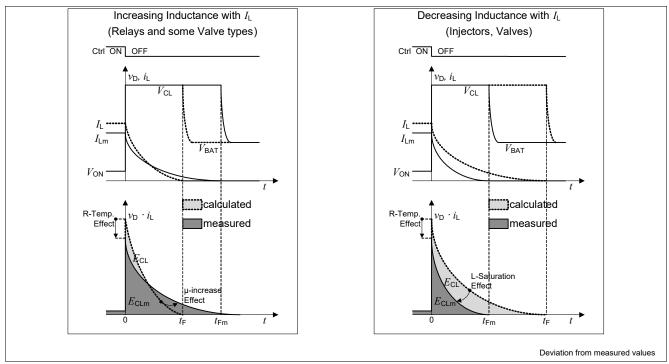

Attention: It is strongly recommended to measure the load Energy and Current under operating conditions, example of measurement setup is shown in Figure 9. Load small-signal parameters might not reflect the real load behavior under operating conditions, see Figure 10. For more details please refer to the Application Note "Switching Inductive Loads".

#### **Power Outputs**

#### **Figure 9** *E*<sub>CL</sub> measurement setup

Figure 10 Deviation of calculation from measurement

#### **Power Outputs**

## 7.3 Electrical Characteristics Power Outputs

## Table 7 Electrical Characteristics: Power Outputs

$3.0V < V_{CC} < 5.5V$ ;  $4.5V < V_{DD} < 5.5V$ ,  $T_j = -40^{\circ}$ C to +150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                                         | Symbol            |      | Value | S    | Unit | Note or                                                                  | Number  |

|-------------------------------------------------------------------|-------------------|------|-------|------|------|--------------------------------------------------------------------------|---------|

|                                                                   |                   | Min. | Тур.  | Max. |      | <b>Test Condition</b>                                                    |         |

| Output Channel Resistance                                         |                   |      |       |      |      |                                                                          |         |

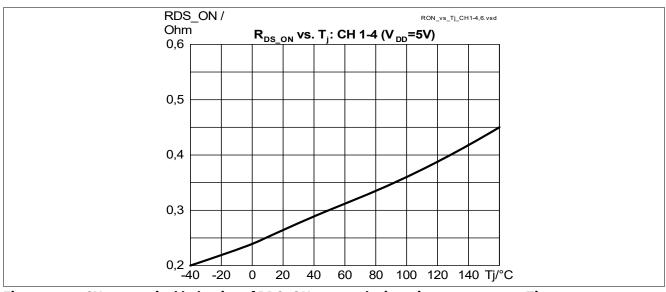

| On State Resistance<br>Channel Group 1-4                          | R <sub>DSon</sub> | -    | 0.3   | -    | Ohm  | <i>I</i> <sub>Dnom</sub> = 1.5A,<br>Tj = 25°C <sup>1)</sup>              | P_7.3.1 |

|                                                                   |                   | -    | 0.45  | 0.6  | Ohm  | I <sub>Dnom</sub> = 1.5A,<br>T <sub>j</sub> = 150°C                      |         |

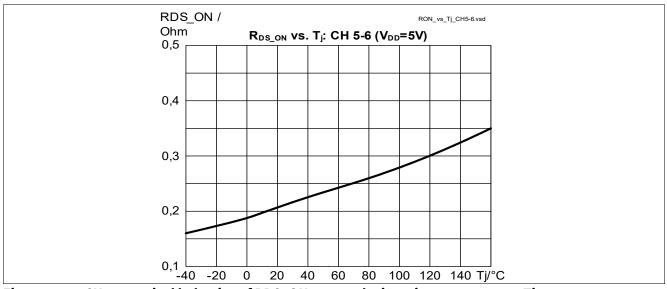

| On State Resistance<br>Channel Group 5-6                          | R <sub>DSon</sub> | -    | 0.25  | -    | Ohm  | $I_{\rm Dnom} = 1.7 \text{A},$<br>$T_{\rm j} = 25^{\circ} \text{C}^{-1}$ | P_7.3.2 |

|                                                                   |                   | -    | 0.35  | 0.5  | Ohm  | I <sub>Dnom</sub> = 1.7A,<br>T <sub>j</sub> = 150°C                      |         |

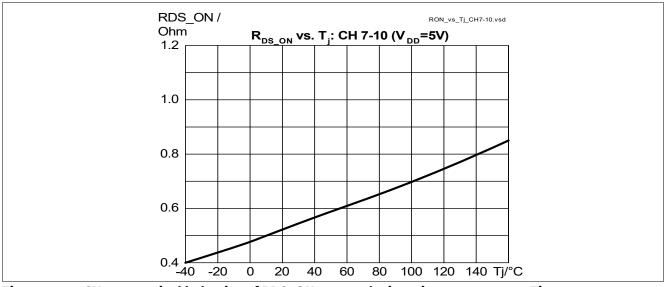

| On State Resistance<br>Channel Group 7-10                         | R <sub>DSon</sub> | -    | 0.6   | -    | Ohm  | $I_{\rm Dnom} = 0.75 {\rm A},$<br>$T_{\rm j} = 25^{\circ} {\rm C}^{1)}$  | P_7.3.3 |

| ALCICIC 1101214                                                   |                   | -    | 0.85  | 1.2  | Ohm  | I <sub>Dnom</sub> =0.75A,<br>T <sub>j</sub> = 150°C                      |         |

| Clamping Energy - Repetitive <sup>1)2)</sup><br>Channel Group 1-4 | 3)4)              |      |       |      |      |                                                                          |         |

| Repetitive Clamping Energy                                        | E <sub>AR</sub>   | -    | -     | 11   | mJ   | <i>I</i> <sub>D</sub> = 1.0A,<br>10 <sup>9</sup> cycles                  | P_7.3.4 |

|                                                                   |                   | -    | -     | 12   | mJ   | <i>I</i> <sub>D</sub> = 2.1A,<br>10 <sup>4</sup> cycles                  |         |

|                                                                   |                   | -    | -     | 15   | mJ   | <i>I</i> <sub>D</sub> = 2.6A,<br>10 cycles <sup>5)</sup>                 |         |

| Channel 5-6                                                       |                   |      |       |      |      |                                                                          |         |

| Repetitive Clamping Energy                                        | E <sub>AR</sub>   | -    | -     | 13   | mJ   | <i>I</i> <sub>D</sub> = 1.3A,<br>10 <sup>9</sup> cycles                  | P_7.3.5 |

|                                                                   |                   | -    | -     | 15   | mJ   | <i>I</i> <sub>D</sub> = 2.7A,<br>10 <sup>4</sup> cycles                  |         |

|                                                                   |                   | -    | -     | 20   | mJ   | <i>I</i> <sub>D</sub> = 3.2A,<br>10 cycles <sup>5)</sup>                 |         |

| Channel 7-10                                                      | 1                 |      |       |      |      |                                                                          |         |

| Repetitive Clamping Energy                                        | E <sub>AR</sub>   | -    | -     | 4    | mJ   | I <sub>D</sub> = 0.7A,<br>10 <sup>9</sup> cycles                         | P_7.3.6 |

|                                                                   |                   | -    | -     | 4    | mJ   | <i>I</i> <sub>D</sub> = 1.4A,<br>10 <sup>4</sup> cycles                  |         |

|                                                                   |                   |      |       | +    | +    | +                                                                        |         |

$I_{\rm D} = 1.7 {\rm A},$

10 cycles <sup>5)</sup>

\_

5

mJ

#### **Power Outputs**

#### Table 7 Electrical Characteristics: Power Outputs (cont'd)

$3.0V < V_{CC} < 5.5V$ ;  $4.5V < V_{DD} < 5.5V$ ,  $T_j = -40^{\circ}$ C to +150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                                  | Symbol            |      | Value | S    | Unit | Note or                                                                                                                                                        | Number   |

|------------------------------------------------------------|-------------------|------|-------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                            |                   | Min. | Тур.  | Max. |      | <b>Test Condition</b>                                                                                                                                          |          |

| Leakage Current                                            |                   |      |       |      |      |                                                                                                                                                                |          |

| Output Leakage Current in standby mode, Channel 1 to 4     | I <sub>Doff</sub> | -    | -     | 3    | μA   | $V_{\rm DS} = 13.5 V,$<br>$V_{\rm DD} = 5 V,$<br>$T_{\rm j} = 85^{\circ} {\rm C}^{-1}$                                                                         | P_7.3.7  |

|                                                            |                   | -    | _     | 8    | μΑ   | V <sub>DS</sub> = 13.5V,<br>V <sub>DD</sub> = 5V,<br>T <sub>j</sub> = 150°C                                                                                    |          |

| Output Leakage Current in standby<br>mode, Channel 5 to 6  | I <sub>Doff</sub> | -    | -     | 6    | μA   | $V_{DS} = 13.5V,$<br>$V_{DD} = 5V,$<br>$T_{j} = 85^{\circ}C^{1)}$                                                                                              | P_7.3.8  |

|                                                            |                   | -    | -     | 12   | μA   | V <sub>DS</sub> = 13.5V,<br>V <sub>DD</sub> = 5V,<br>T <sub>j</sub> = 150°C                                                                                    |          |

| Output Leakage Current in standby<br>mode, Channel 7 to 10 | I <sub>Doff</sub> | -    | -     | 2    | μA   | $V_{DS} = 13.5V,$<br>$V_{DD} = 5V,$<br>$T_{j} = 85^{\circ}C^{1)}$                                                                                              | P_7.3.9  |

|                                                            |                   | -    | -     | 5    | μΑ   | $V_{DS} = 13.5V,$<br>$V_{DD} = 5V,$<br>$T_{j} = 150^{\circ}C$                                                                                                  |          |

| Clamping Voltage                                           |                   |      |       |      |      |                                                                                                                                                                |          |

| Output Clamping Voltage, Channel 1 to<br>10                | V <sub>DScl</sub> | 45   | 55    | 60   | V    | _                                                                                                                                                              | P_7.3.10 |

| Timing                                                     |                   | 1    |       |      |      |                                                                                                                                                                |          |

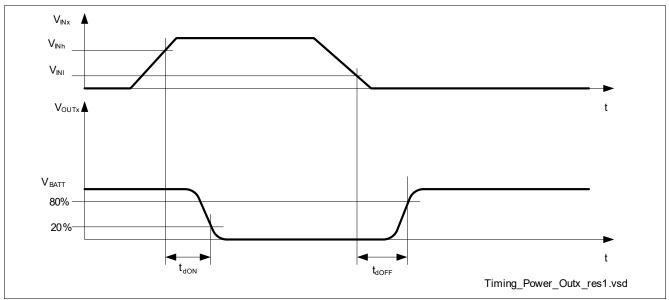

| Output Switching Frequency                                 | f <sub>outx</sub> | -    | -     | 20   | kHz  | <sup>1)</sup><br>resistive load,<br>duty cycle > 25%                                                                                                           | P_7.3.11 |

| Turn-on Time                                               | t <sub>don</sub>  | _    | 5     | 10   | μs   | $V_{DS} = 20\%$ of Vbatt<br>$V_{batt} = 13.5V$ ,<br>$I_{DS1}$ to $I_{DS6} = 1A$ ,<br>$I_{DS7}$ to $I_{DS10} = 0.5A$ ,<br>resistive load                        | P_7.3.12 |

| Turn-off Time                                              | t <sub>doff</sub> | -    | 5     | 10   | μs   | $V_{DS} = 80\% \text{ of } V_{batt}$<br>$V_{batt} = 13.5V,$<br>$I_{DS1} \text{ to } I_{DS6} = 1A,$<br>$I_{DS7} \text{ to } I_{DS10} = 0.5A,$<br>resistive load | P_7.3.13 |

1) Parameter is not subject to production test, specified by design.

<sup>2)</sup> Either one of the values has to be considered as worst case limitation. Cumulative scenario and wide range of operating conditions are treated in the Application Note "Switching Inductive Loads - TLE8110 addendum".

#### **Power Outputs**

- 3) This lifetime statement is an anticipation based on an extrapolation of Infineon's qualification test results. The actual lifetime of a component depends on its form of application and type of use etc. and may deviate from such statement. The lifetime statement shall in no event extend the agreed warranty period.

- 4) Triangular Pulse Shape (inductance discharge):  $I_D(t) = I_D(0) \cdot (1 t / t_{pulse}); 0 < t < t_{pulse}$ .

- 5) Repetitive operation not allowed. Starting *T*<sub>j</sub> must be kept within specs. In case of high energy pulse an immediate switch-off strategy is recommended.

Figure 11 CH 1-4: typical behavior of RDS\_ON versus the junction temperature Tj

## **Power Outputs**

Figure 13 CH7-10: typical behavior of RDS\_ON versus the junction temperature Tj

Figure 14 All Channels: typical behavior of the clamping voltage versus the junction temperature

#### **Power Outputs**

Figure 15 Timing of Output Channel switching (resistive load)

## 7.4 Parallel Connection of the Power Stages

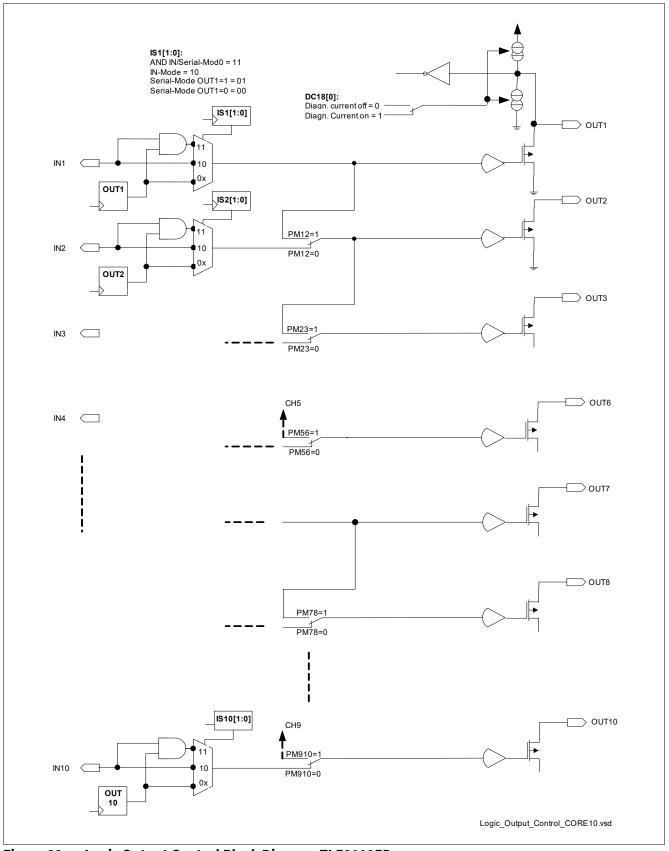

The TLE8110ED is equipped with a structure which improves the capability of parallel-connected channels. The device can be "informed" via the PMx.PMx - bits (see chapter "Control of the device") which of the channels are connected in parallel. The input channels can be mapped to the parallel connected output channels in order to apply the PWM signals. This feature allows a flexible adaptation to different load situations within the same hardware setup.

In case of overload the ground current and the power dissipation is increasing. The application has to take into account that all maximum ratings are observed (e.g. operating temperature  $T_J$  and total ground current  $I_{GND}$ , see Maximum Ratings). In case of parallel connection of channels with or w/o PM-bit set, the defined maximum clamping energy must not be exceeded.

All stages are switched on and off simultaneously. The µC has to ensure that the stages which are connected in parallel have always the same state (on or off). The PM-bit should be set according to the parallel connected power stages in order to achieve the best possible performance.

The PM-bit is set to its default value in case of a Reset event (Reset pin Low or at Digital Supply undervoltage), that means the improved Parallel Mode is no longer active. In the event of reset the channels will be switched off causing the clamping energy to be dissipated with low performance of the current sharing as without PM-bit set, for more details please refer to the Application Note *Switching Inductive Loads - TLE8110 addendum*.

The performance during parallel connection of channels is specified by design and not subject to the production test. All channels at the same junction temperature level.

## **ON-Resistance**

The typical ON-Resistance  $R_{DSsum(typ)}$  of parallel connected channels is given by:

$$R_{DSsum(typ)} = \left[\frac{1}{R_{DSon, n(typ)}} + \frac{1}{R_{DSon, n+1(typ)}}\right]^{-1}$$

(7.2)

#### **Power Outputs**

| Parameter                                                     | Symbol                    | Cha | nnels in | Parallel | Unit | Conditions                                              | Numbe   |

|---------------------------------------------------------------|---------------------------|-----|----------|----------|------|---------------------------------------------------------|---------|

|                                                               |                           | 2x  | 3x       | 4x       |      |                                                         |         |

| Channel Group 1-4                                             |                           | -   |          | <u>I</u> | !    |                                                         |         |

| Maximum overall current before reaching lower limit threshold | I <sub>Dsum(low)</sub>    | 5.1 | 7.6      | 10.1     | A    |                                                         | P_7.4.1 |

| Maximum overall Repetitive<br>Clamping Energy                 | <i>E</i> <sub>ARsum</sub> | 37  | -        | -        | mJ   | / <sub>D</sub> = 1.0A,<br>10 <sup>9</sup> cycles        | P_7.4.2 |

|                                                               |                           | 17  | 38       | 69       | mJ   | / <sub>D</sub> = 1.75A,<br>10 <sup>9</sup> cycles       |         |

|                                                               |                           | -   | 23       | 42       | mJ   | / <sub>D</sub> = 2.5A,<br>10 <sup>9</sup> cycles        |         |

|                                                               |                           | -   | -        | 33       | mJ   | / <sub>D</sub> = 3.0A,<br>10 <sup>9</sup> cycles        |         |

| Channel Group 5-6                                             | 1                         |     |          |          |      |                                                         | I       |

| Maximum overall current before reaching lower limit threshold | I <sub>Dsum(low)</sub>    | 7.2 | -        | -        | A    | -                                                       | P_7.4.3 |

| Maximum overall Repetitive<br>Clamping Energy                 | E <sub>ARsum</sub>        | 43  | -        | -        | mJ   | $I_{\rm D} = 1.3$ A,<br>10 <sup>9</sup> cycles          | P_7.4.4 |

|                                                               |                           | 21  | -        | -        | mJ   | $I_{\rm D} = 2.2 {\rm A},$<br>10 <sup>9</sup> cycles    |         |

| Channel Group 7-10                                            |                           | 1   |          | <b>I</b> |      |                                                         | I       |

| Maximum overall current before reaching lower limit threshold | I <sub>Dsum(low)</sub>    | 3.3 | 5.0      | 6.6      | A    | -                                                       | P_7.4.5 |

| Maximum overall Repetitive<br>Clamping Energy                 | E <sub>ARsum</sub>        | 15  | -        | -        | mJ   | / <sub>D</sub> = 0.7A,<br>10 <sup>9</sup> cycles        | P_7.4.6 |

|                                                               |                           | 6   | 15       | 30       | mJ   | / <sub>D</sub> = 1.2A,<br>10 <sup>9</sup> cycles        |         |

|                                                               |                           | -   | 9        | 18       | mJ   | <i>I</i> <sub>D</sub> = 1.6A,<br>10 <sup>9</sup> cycles |         |

|                                                               |                           | -   | -        | 11       | mJ   | $I_{\rm D} = 2.1 {\rm A},$<br>10 <sup>9</sup> cycles    |         |

Homogenous power distribution over all channels (all power stages equally heated), dependent on cooling set-up.

3) This lifetime statement is an anticipation based on an extrapolation of Infineon's qualification test results. The actual lifetime of a component depends on its form of application and type of use etc. and may deviate from such statement. The lifetime statement shall in no event extend the agreed warranty period.

4) Triangular Pulse Shape (inductance discharge):  $I_D(t) = I_D(0) \cdot (1 - t / t_{pulse}); 0 < t < t_{pulse}$ .

#### **Power Outputs**

| Parameter                                                     | Symbol                    | Cha | nnels in | Parallel | Unit | Conditions                                           | Numbe   |

|---------------------------------------------------------------|---------------------------|-----|----------|----------|------|------------------------------------------------------|---------|

|                                                               |                           | 2x  | 3x       | 4x       |      |                                                      |         |

| Channel Group 1-4                                             |                           |     | <u> </u> |          |      |                                                      |         |

| Maximum overall current before reaching lower limit threshold | I <sub>Dsum(low)</sub>    | 5.1 | 7.6      | 10.1     | A    |                                                      | P_7.5.1 |

| Maximum overall Repetitive<br>Clamping Energy                 | <i>E</i> <sub>ARsum</sub> | 18  | -        | -        | mJ   | / <sub>D</sub> = 1.0A,<br>10 <sup>9</sup> cycles     | P_7.5.2 |

|                                                               |                           | 8   | 13       | 19       | mJ   | / <sub>D</sub> = 1.75A,<br>10 <sup>9</sup> cycles    |         |

|                                                               |                           | -   | 8        | 11       | mJ   | / <sub>D</sub> = 2.5A,<br>10 <sup>9</sup> cycles     |         |

|                                                               |                           | -   | -        | 9        | mJ   | / <sub>D</sub> = 3.0A,<br>10 <sup>9</sup> cycles     |         |

| Channel Group 5-6                                             |                           |     | <u>.</u> |          |      |                                                      |         |

| Maximum overall current before reaching lower limit threshold | I <sub>Dsum(low)</sub>    | 7.2 | -        | -        | A    | _                                                    | P_7.5.3 |

| Maximum overall Repetitive<br>Clamping Energy                 | <i>E</i> <sub>ARsum</sub> | 22  | -        | -        | mJ   | / <sub>D</sub> = 1.3A,<br>10 <sup>9</sup> cycles     | P_7.5.4 |

|                                                               |                           | 11  | -        | -        | mJ   | $I_{\rm D} = 2.2 {\rm A},$<br>10 <sup>9</sup> cycles |         |

| Channel Group 7-10                                            |                           |     |          |          |      |                                                      |         |

| Maximum overall current before reaching lower limit threshold | I <sub>Dsum(low)</sub>    | 3.3 | 5.0      | 6.6      | A    | _                                                    | P_7.5.5 |

| Maximum overall Repetitive<br>Clamping Energy                 | E <sub>ARsum</sub>        | 7   | -        | -        | mJ   | / <sub>D</sub> = 0.7A,<br>10 <sup>9</sup> cycles     | P_7.5.6 |

|                                                               |                           | 3   | 4        | 7        | mJ   | $I_{\rm D} = 1.2$ A,<br>10 <sup>9</sup> cycles       |         |

|                                                               |                           | -   | 3        | 4        | mJ   | / <sub>D</sub> = 1.6A,<br>10 <sup>9</sup> cycles     |         |

|                                                               |                           | -   | -        | 3        | mJ   | $I_{\rm D} = 2.1$ A,<br>10 <sup>9</sup> cycles       |         |

Homogenous power distribution over all channels (all power stages equally heated), dependent on cooling set-up.

3) This lifetime statement is an anticipation based on an extrapolation of Infineon's qualification test results. The actual lifetime of a component depends on its form of application and type of use etc. and may deviate from such statement. The lifetime statement shall in no event extend the agreed warranty period.

4) Triangular Pulse Shape (inductance discharge):  $I_D(t) = I_D(0) \cdot (1 - t / t_{pulse}); 0 < t < t_{pulse}$ .

Infineon

Diagnosis

TLE8110ED

#### **Diagnosis** 8

#### 8.1 **Diagnosis Description**

The TLE8110ED provides diagnosis information about the device and about the load. Following diagnosis flags have been implemented for each channel:

| Diagnosis <sup>1)</sup> | Symbol | <b>DRn[1:0]x</b><br>2) | Device reaction | Confirmation<br>Procedure <sup>3)</sup> |

|-------------------------|--------|------------------------|-----------------|-----------------------------------------|

|-------------------------|--------|------------------------|-----------------|-----------------------------------------|

| Short to Ground                 | SCG | 00 <sub>B</sub> | -                             | -             |

|---------------------------------|-----|-----------------|-------------------------------|---------------|

| No Fault                        | ОК  | 11 <sub>B</sub> | -                             | -             |

| Open Load                       | OL  | 01 <sub>B</sub> | -                             | Chapter 8.1.1 |

| Overcurrent/<br>Overtemperature | ОСТ | 10 <sub>B</sub> | Switch-off of related channel | Chapter 8.1.2 |

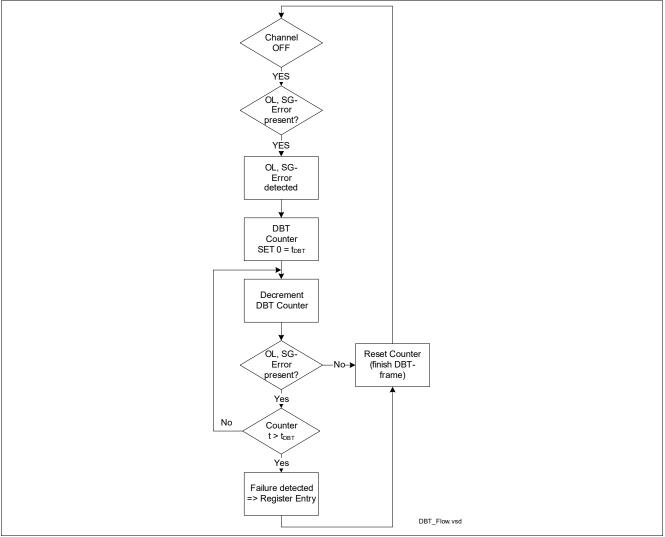

No priority scheme is implemented for the diagnosis detection, any new diagnosis entry will override the previous one. 1)

Diagnosis Register (A/B banks) bit configuration, see **Chapter 12.3.2.1**. 2)

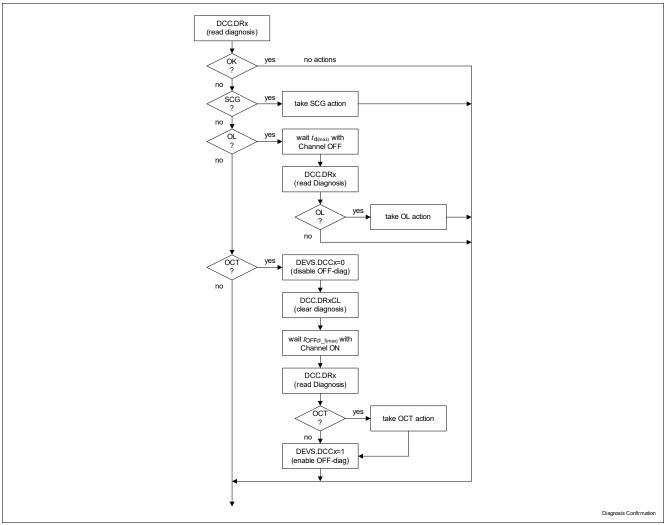

For some diagnosis a confirmation procedure is required for a safe operation of the device, refer to Figure 16. 3)

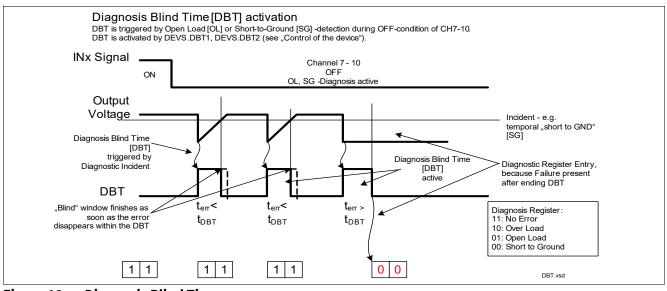

Updating of the Diagnosis is based on a filter-dependent standard delay time ( $t_d$ ) of 220µs max. This value is set as a default. Refer to Figure 17 for details.

If SCG or OL condition is asserted and before the Diagnosis Delay Time  $(t_d)$  is elapsed a condition change occurs, OL-to-SCG or SCG-to-OL, filter timer is not reset and latest condition before t<sub>d</sub> expiration will be stored into the diagnosis register.

- Application Hint: It is recommended to avoid OFF periods of the channel shorter than  $t_{d(max)}$  (220µs) in order to ensure the filter time is expired and the correct diagnosis information is stored.

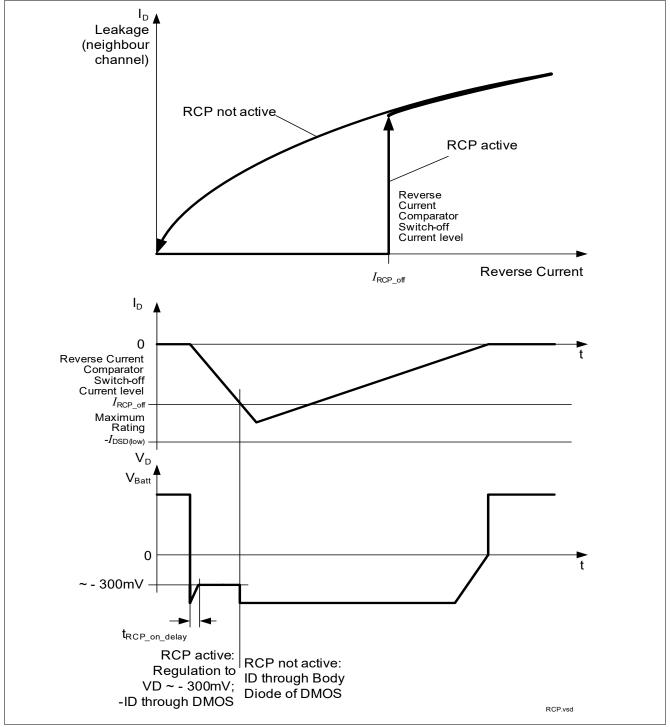

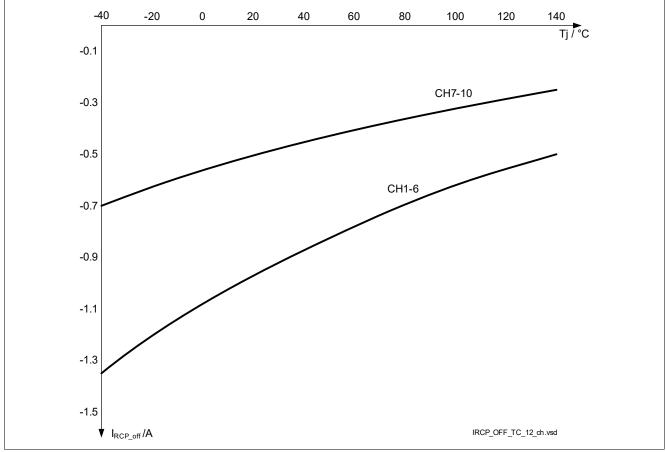

- Application Hint: In specific application cases such as driving Uni-Polar Stepper Motor it might be possible, that reverse currents flow for a short time, which possibly can disturb the diagnosis circuit at neighboring channels and cause wrong diagnosis results of those channels. To reduce the possibility, that this effect appears in a certain timing range, the filter time of Channels 7 to 10 can be extended to typ. 2.5ms or typ. 5ms by setting the "Diagnosis Blind Time" - Bits (DBTx). If Channels 7 to 10 are used for driving loads causing reverse currents, they influence each other and additionally might affect Channels 5 and 6. It is recommended to use the channels 7 + 8 and 9 + 10 as pairs for anti-parallel control signals, such as for the stepper motors. For logic setting details, see chapter "Control of the Device".

#### 8.1.1 **Open Load diagnosis**

If an OL is read out of the Diagnosis Register, the following procedure is required in order to confirm the channel status and ensure a safe operation of the device:

After reading the OL  $[01_B]$  in the diagnosis register (Chapter 12.3.2)

- 1. Switch-OFF for  $t \ge t_{d(max)}$  the related channel (via serial or direct control, see (Chapter 12.3.3) and (Chapter 12.3.4),

- 2. Read again the diagnosis register

- a) If OL is confirmed Then take actions according to system implementation,

- 3. Continue normal operation.

## Diagnosis

Refer to **Figure 16** for the procedure flow-chart.

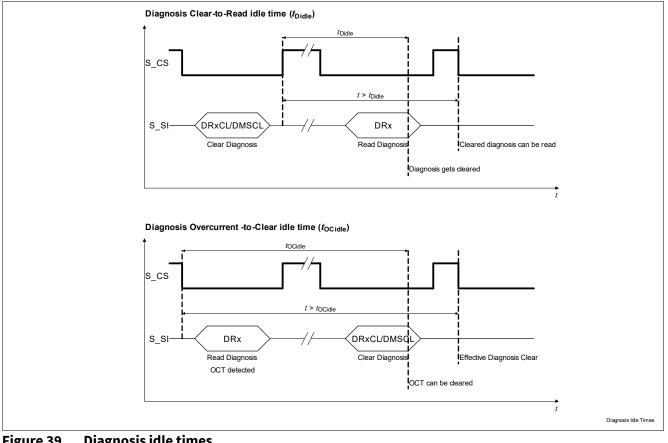

## 8.1.2 Overcurrent / Overtemperature diagnosis

After an OCT assertion the related channel is switched OFF for safety reasons. If an OCT is read out of the Diagnosis Register, the following procedure is required in order to confirm the channel status and ensure a safe operation of the device:

After reading the OCT  $[10_B]$  in the diagnosis register (Chapter 12.3.2)

- 1. Set related bit DEVS.DCCx = 0 to disable OFF-diagnosis, see (Chapter 12.3.6),

- 2. Clear the Diagnosis issuing a DCC.DRxCL command, see (Chapter 12.3.2),

- 3. Switch-ON for  $t \ge t_{OFFcl}$  (max) the related channel,

- 4. Read again the diagnosis register

- a) If OCT is confirmed Then take actions according to system implementation,

- 5. Set related bit DEVS.DCCx = 1 to enable OFF-diagnosis,

- 6. Continue normal operation.

Refer to **Figure 16** for the procedure flow-chart.

Figure 16 Diagnosis Confirmation procedure

## Diagnosis

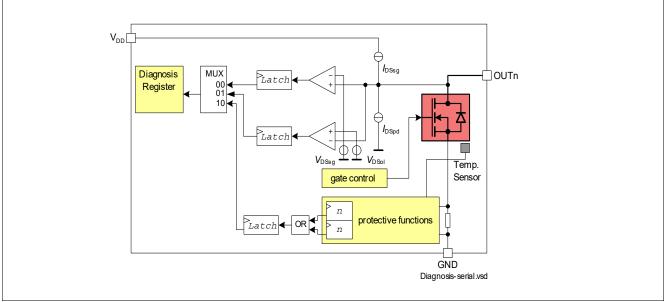

## Figure 17 Block Diagram of Diagnosis

## 8.2 Electrical Characteristics Diagnosis

## Table 10 Electrical Characteristics: Diagnosis

$3.0V < V_{CC} < 5.5V$ ;  $4.5V < V_{DD} < 5.5V$ ,  $T_j = -40^{\circ}$ C to +150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                                                    | Symbol            |      | Value | S    | Unit | Note or<br>Test Condition              | Number              |

|------------------------------------------------------------------------------|-------------------|------|-------|------|------|----------------------------------------|---------------------|

|                                                                              |                   | Min. | Тур.  | Max. |      |                                        |                     |

| Open Load Diagnosis                                                          | 1                 |      |       |      |      | 1                                      |                     |

| Open load detection threshold voltage                                        | V <sub>DSol</sub> | 2.00 | 2.60  | 3.20 | V    | -                                      | P_8.2.1             |

| Output pull-down diagnosis current per channel (low level)                   | I <sub>Dpd</sub>  | 50   | 90    | 150  | μA   | V <sub>DS</sub> = 13.5 V               | P_8.2.2             |

| Open Load Diagnosis Delay Time<br>(all channels)                             | t <sub>d</sub>    | 100  | -     | 220  | μs   | DEVS.DBT1 = 0<br>DEVS.DBT2<br>= 1 or 0 | P_8.2.3             |

| Channel 7-10:<br>Open Load Diagnosis Delay Time "Diagnosis                   | t <sub>d</sub>    | 1.65 | 2.5   | 3.45 | ms   | DEVS.DBT1 = 1<br>DEVS.DBT2 = 0         | P_8.2.4<br>a)<br>b) |

| Blind Time" see chapter "Control of the device", <b>Figure 18, Figure 19</b> |                   | 3.3  | 5     | 7.3  | ms   | DEVS.DBT1 = 1<br>DEVS.DBT2 = 1         |                     |